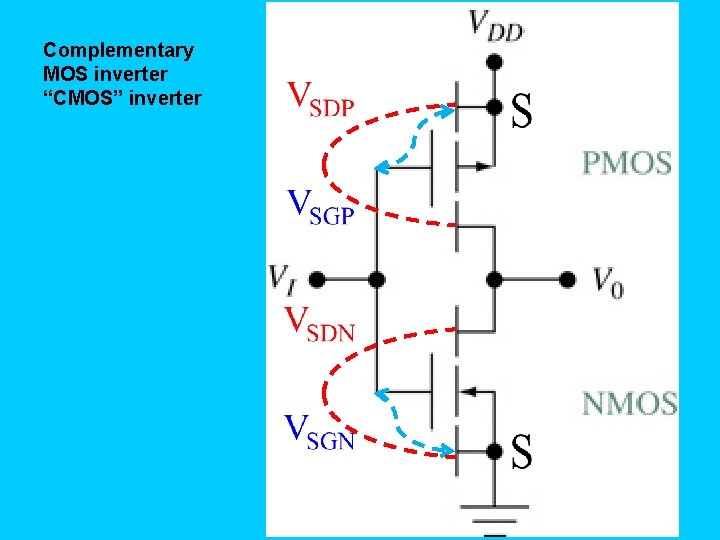

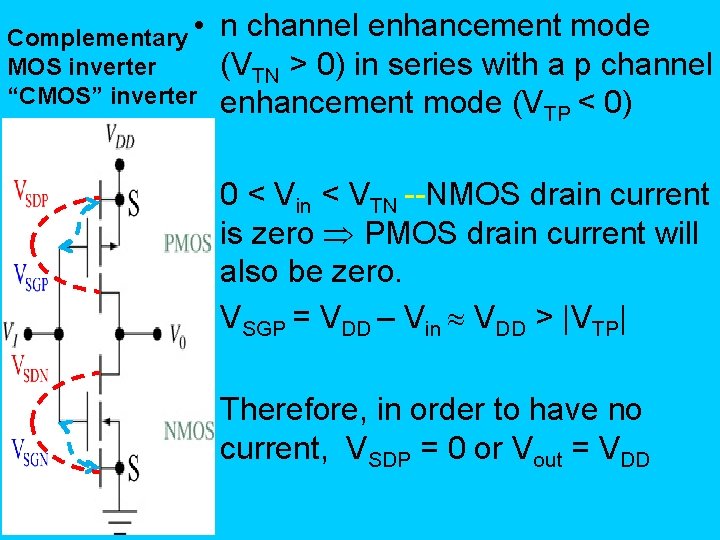

Complementary MOS inverter CMOS inverter Complementary MOS inverter

- Slides: 101

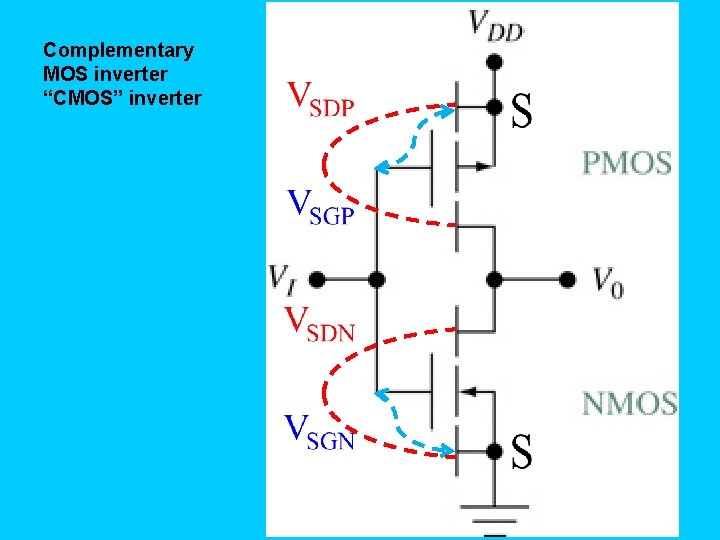

Complementary MOS inverter “CMOS” inverter

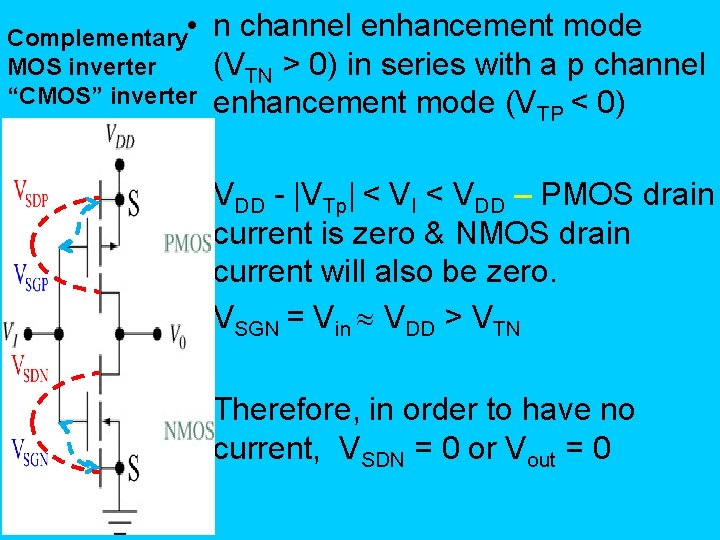

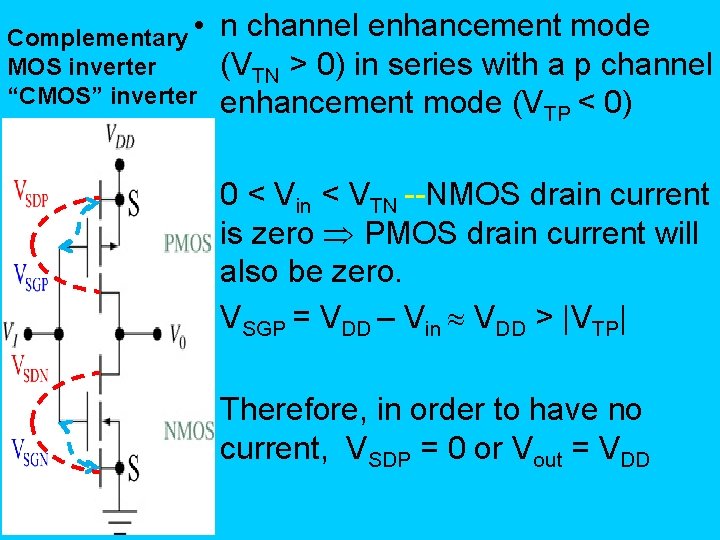

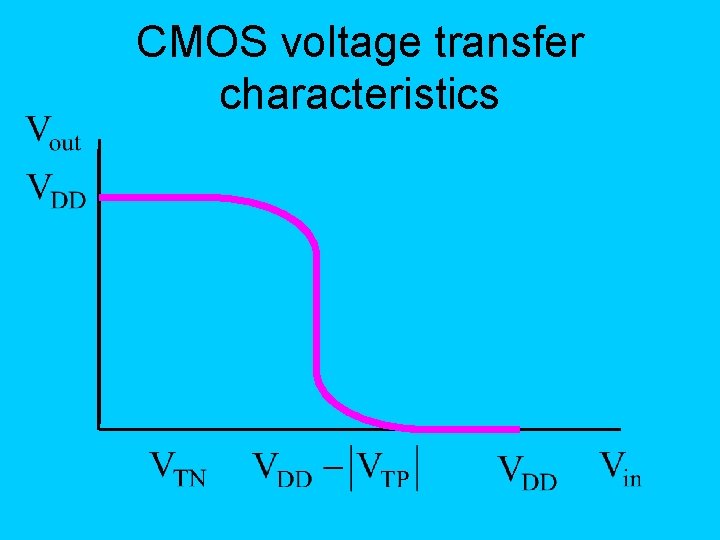

Complementary • MOS inverter “CMOS” inverter n channel enhancement mode (VTN > 0) in series with a p channel enhancement mode (VTP < 0) • 0 < Vin < VTN --NMOS drain current is zero PMOS drain current will also be zero. • VSGP = VDD – Vin VDD > |VTP| • Therefore, in order to have no current, VSDP = 0 or Vout = VDD

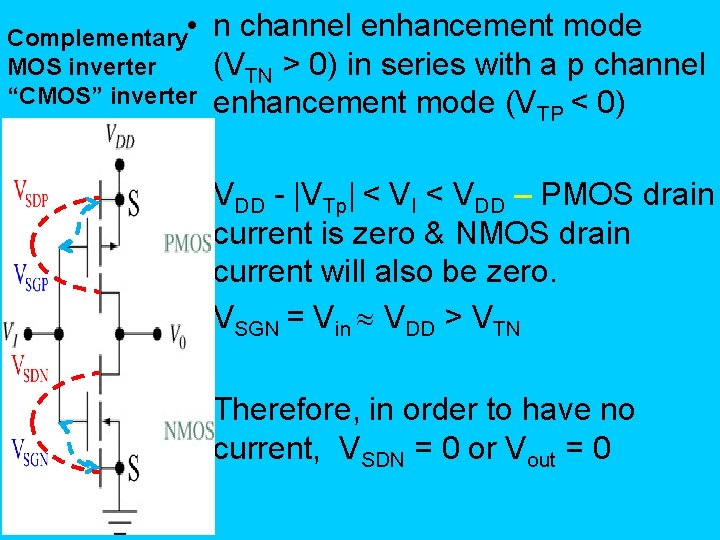

Complementary • MOS inverter “CMOS” inverter n channel enhancement mode (VTN > 0) in series with a p channel enhancement mode (VTP < 0) • VDD - |VTp| < VI < VDD – PMOS drain current is zero & NMOS drain current will also be zero. • VSGN = Vin VDD > VTN • Therefore, in order to have no current, VSDN = 0 or Vout = 0

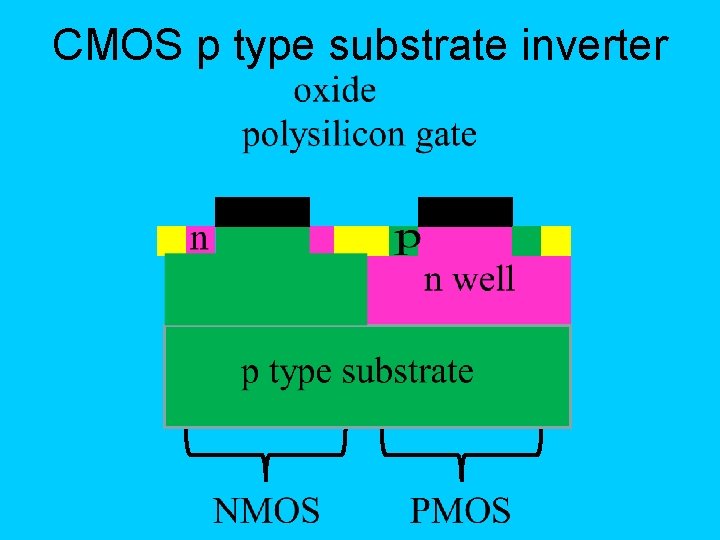

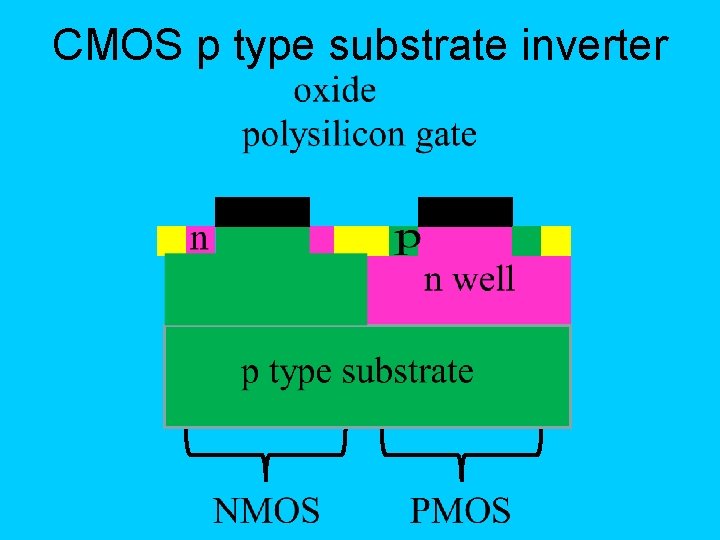

CMOS p type substrate inverter

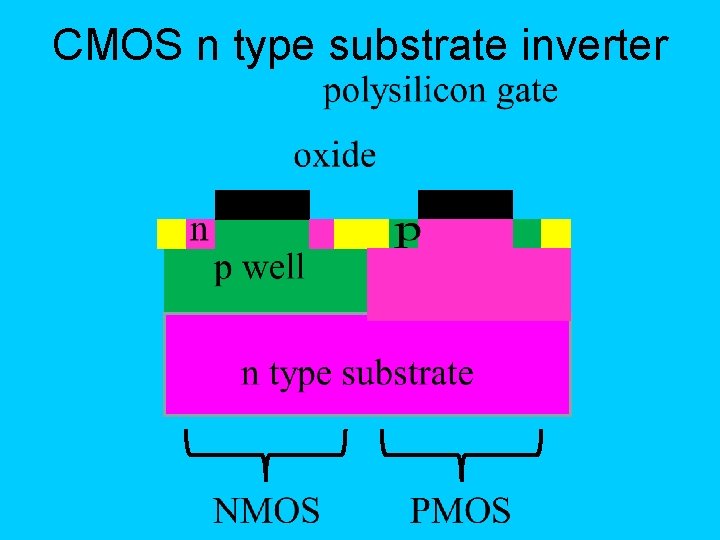

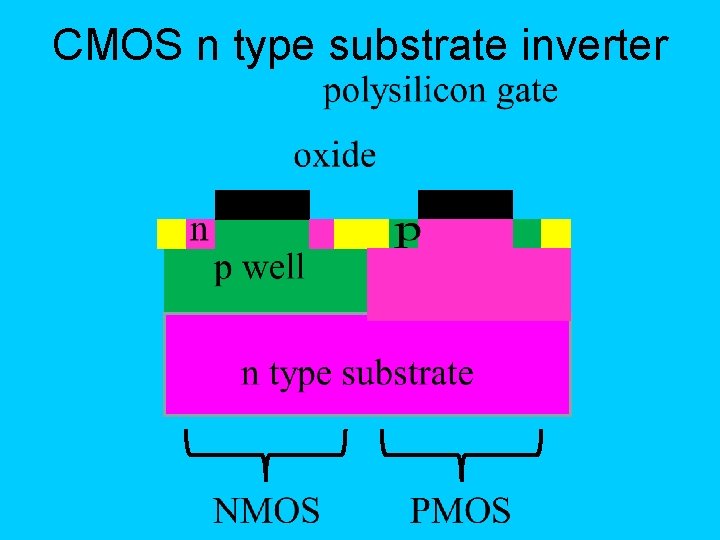

CMOS n type substrate inverter

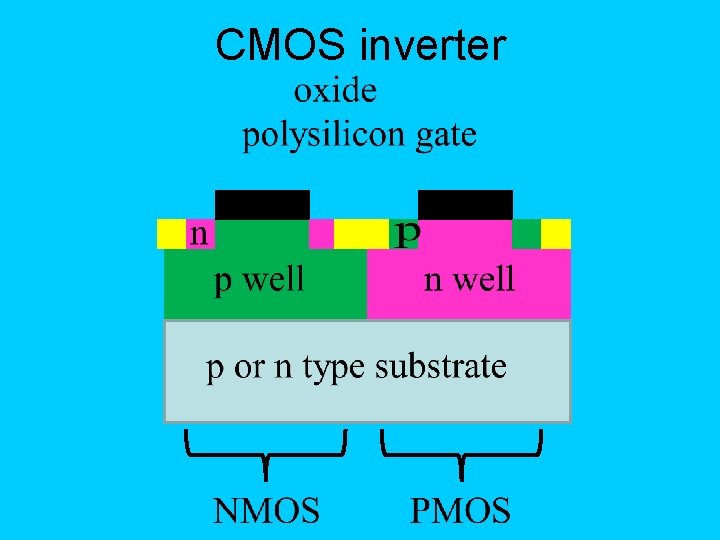

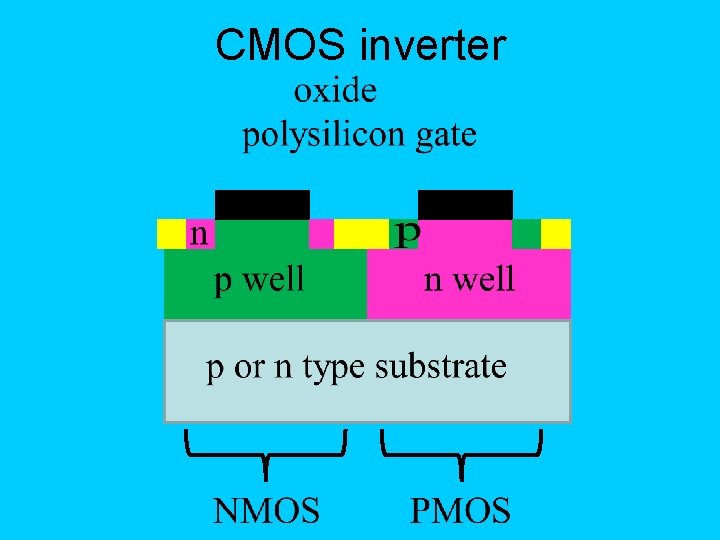

CMOS inverter

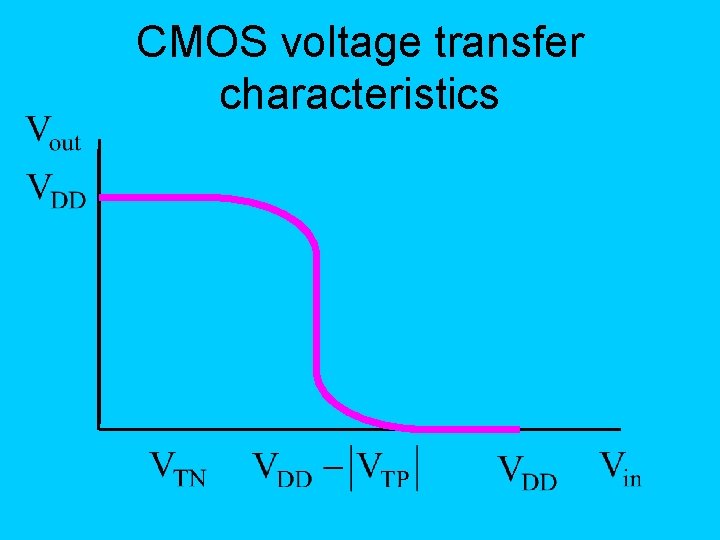

CMOS voltage transfer characteristics

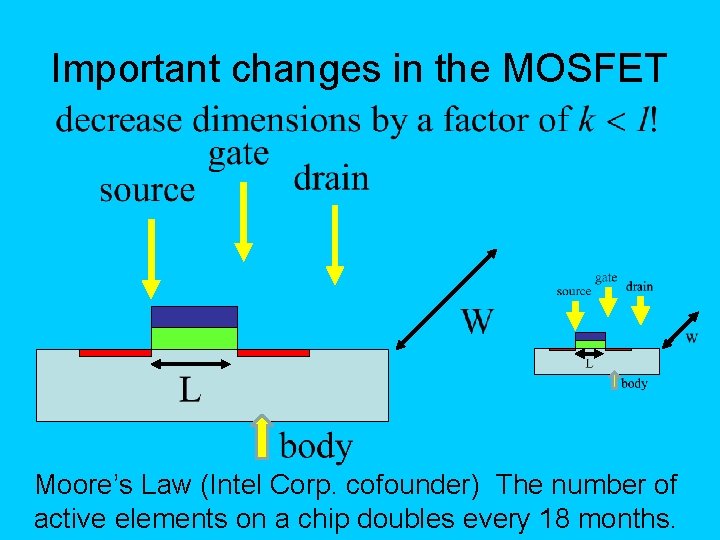

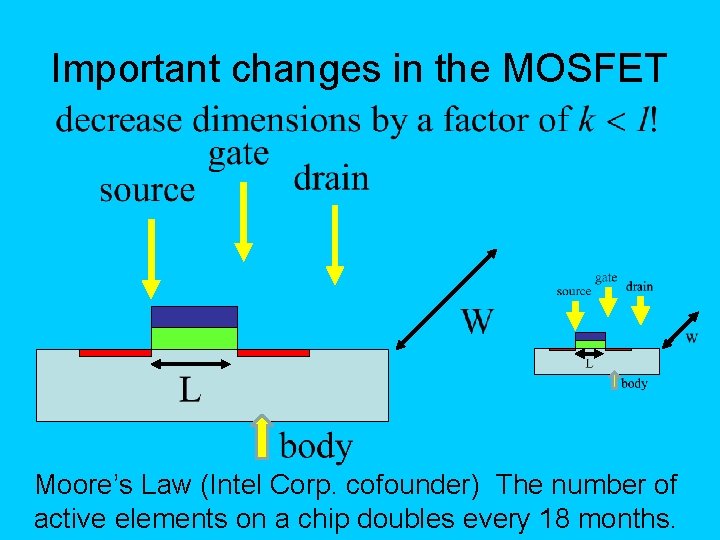

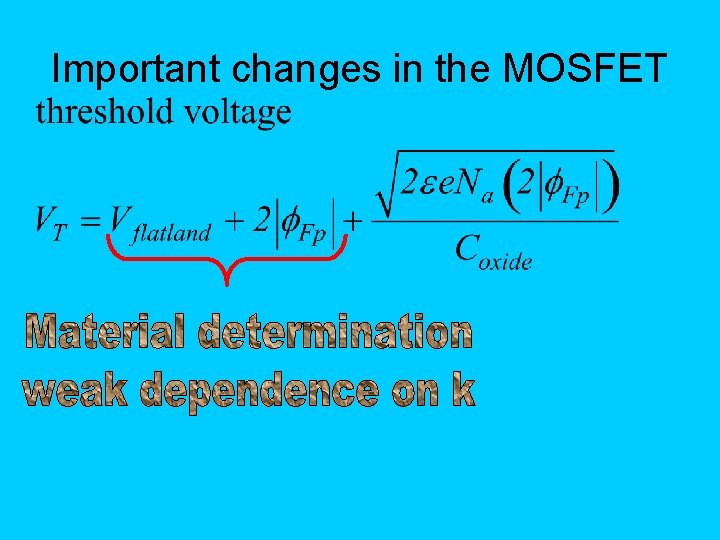

Important changes in the MOSFET Moore’s Law (Intel Corp. cofounder) The number of active elements on a chip doubles every 18 months.

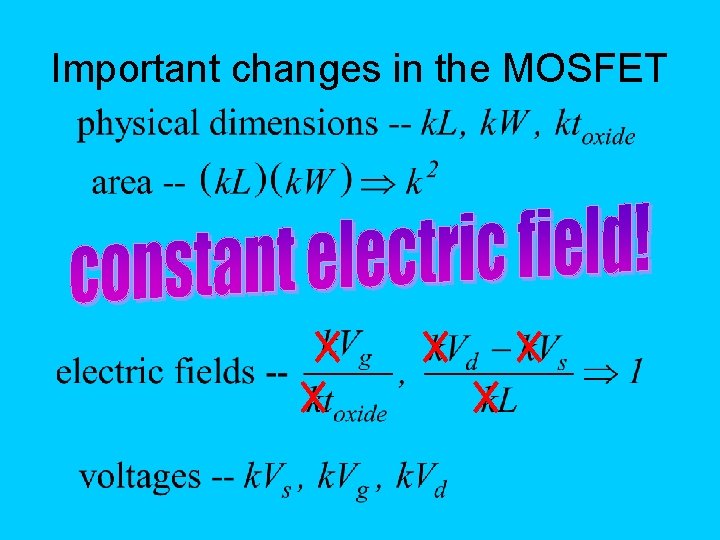

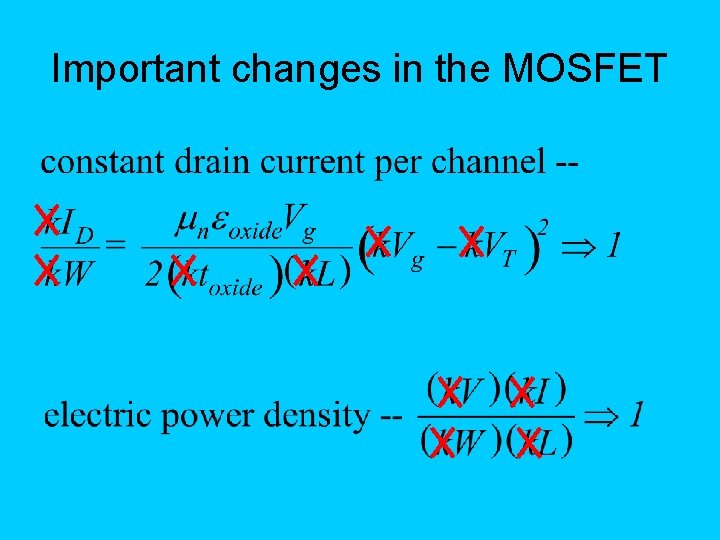

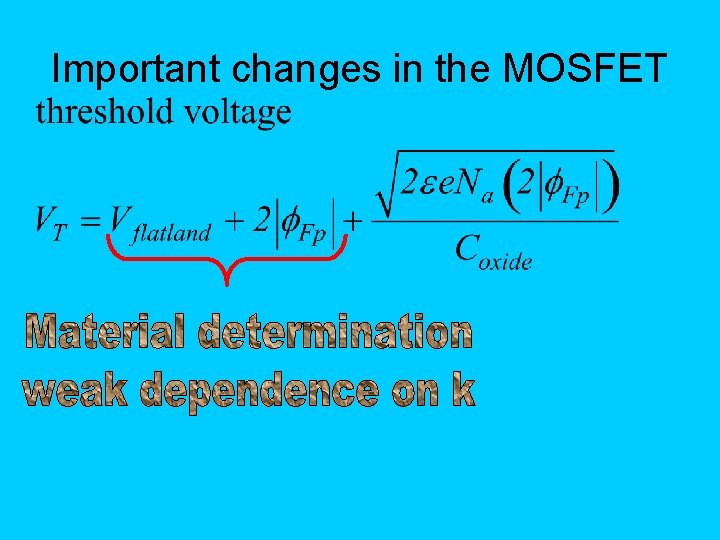

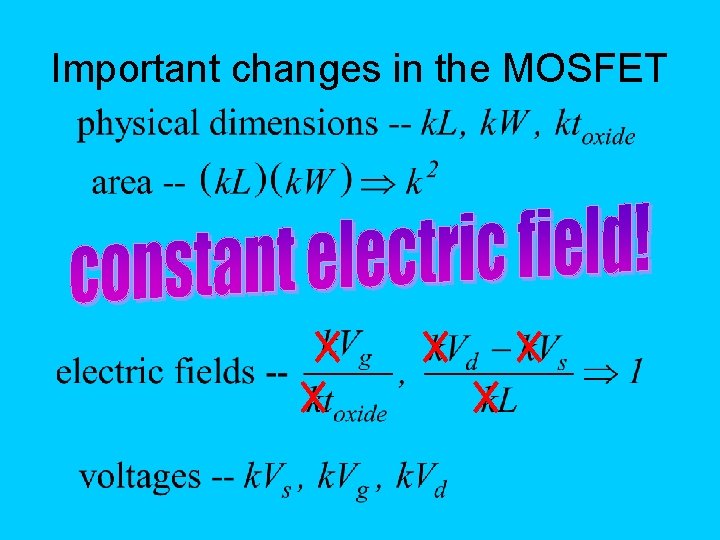

Important changes in the MOSFET

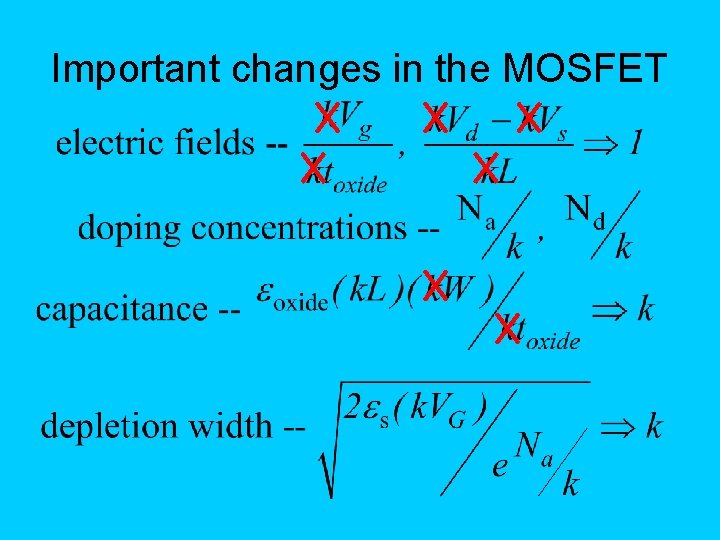

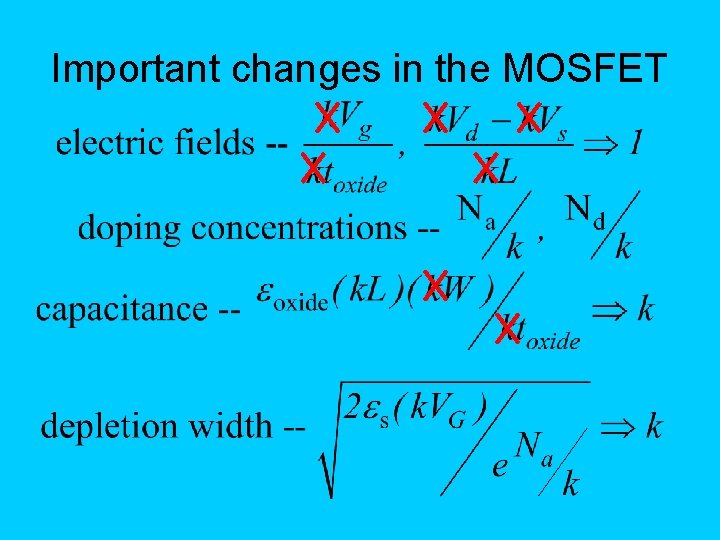

Important changes in the MOSFET

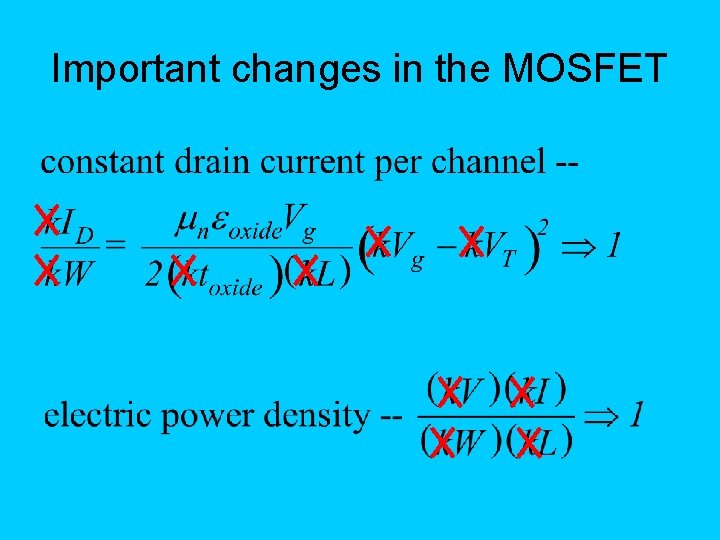

Important changes in the MOSFET

Important changes in the MOSFET

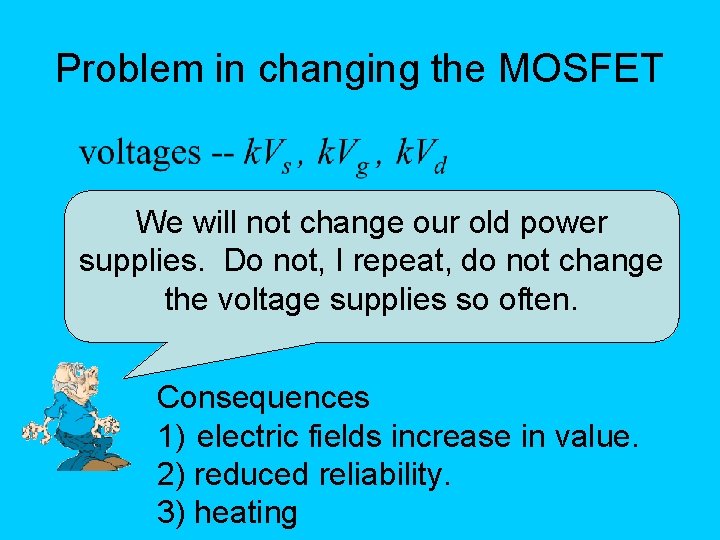

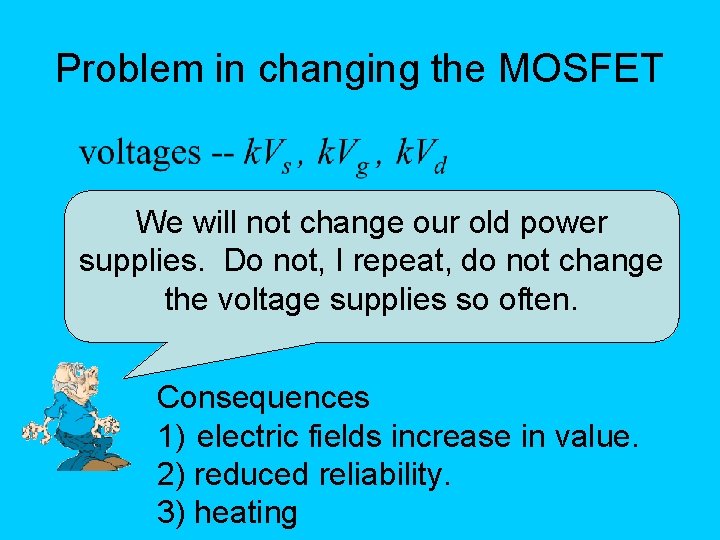

Problem in changing the MOSFET We will not change our old power supplies. Do not, I repeat, do not change the voltage supplies so often. Consequences 1) electric fields increase in value. 2) reduced reliability. 3) heating

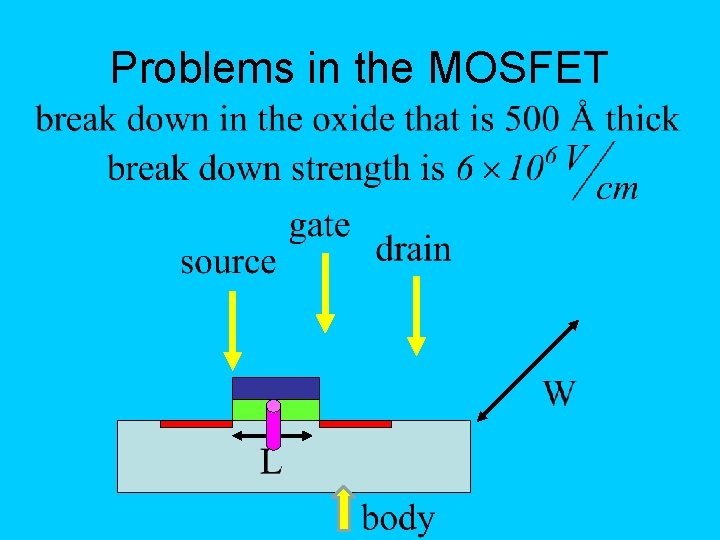

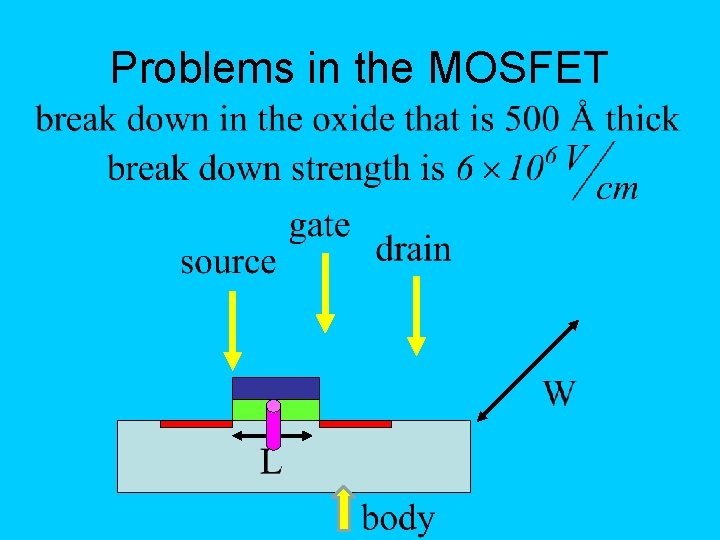

Problems in the MOSFET

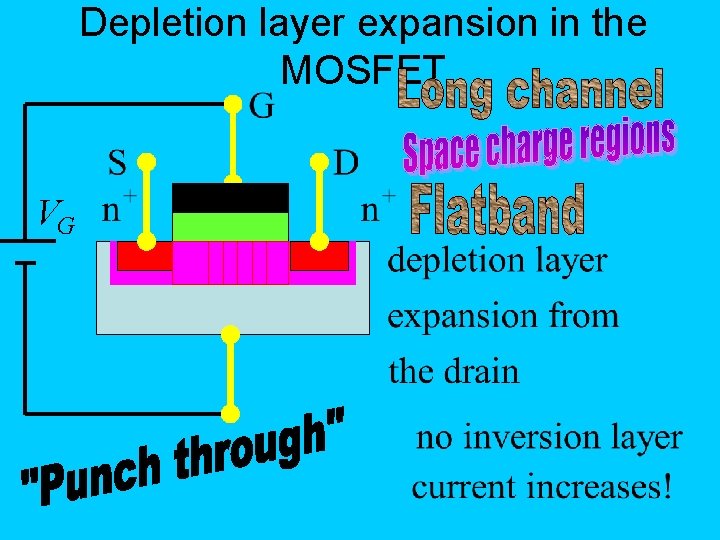

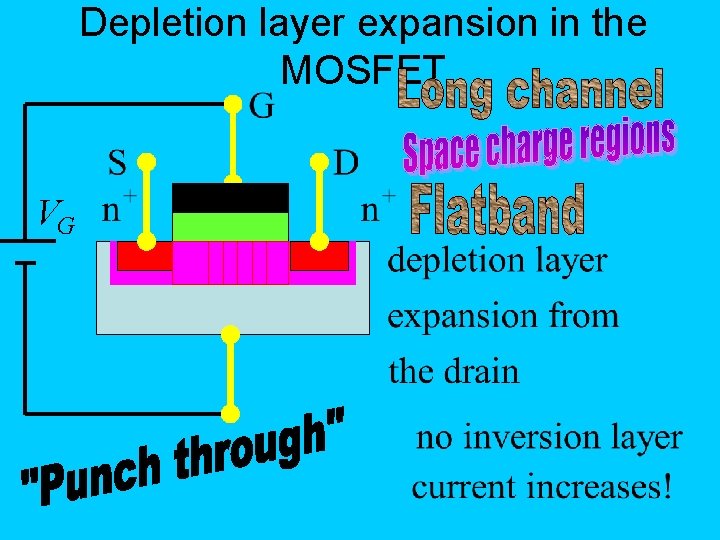

Depletion layer expansion in the MOSFET VG

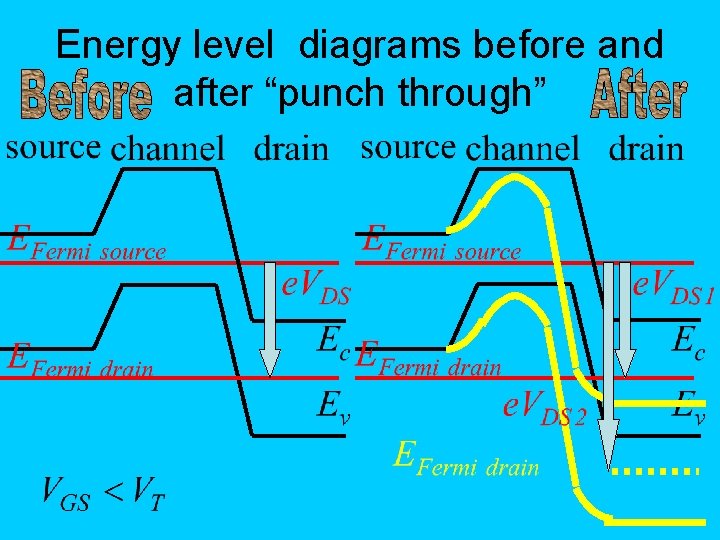

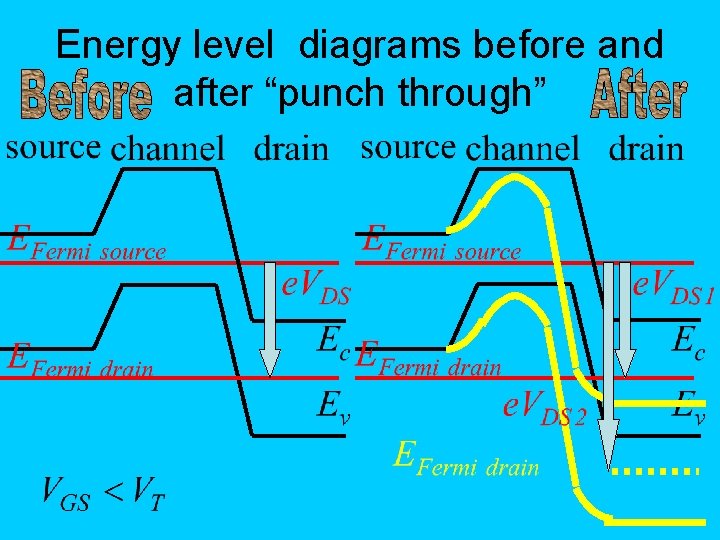

Energy level diagrams before and after “punch through”

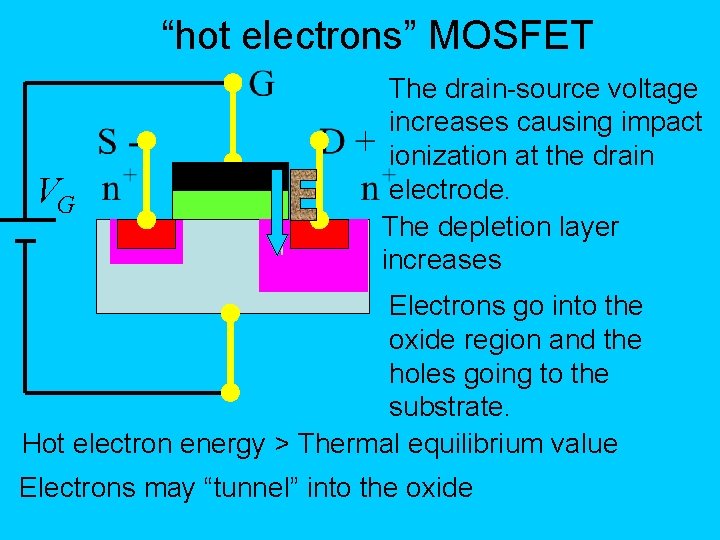

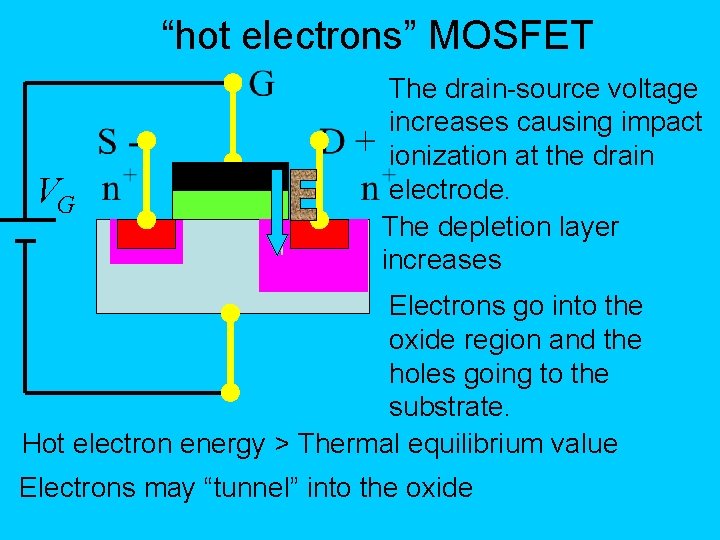

“hot electrons” MOSFET VG The drain-source voltage increases causing impact ionization at the drain electrode. The depletion layer increases Electrons go into the oxide region and the holes going to the substrate. Hot electron energy > Thermal equilibrium value Electrons may “tunnel” into the oxide

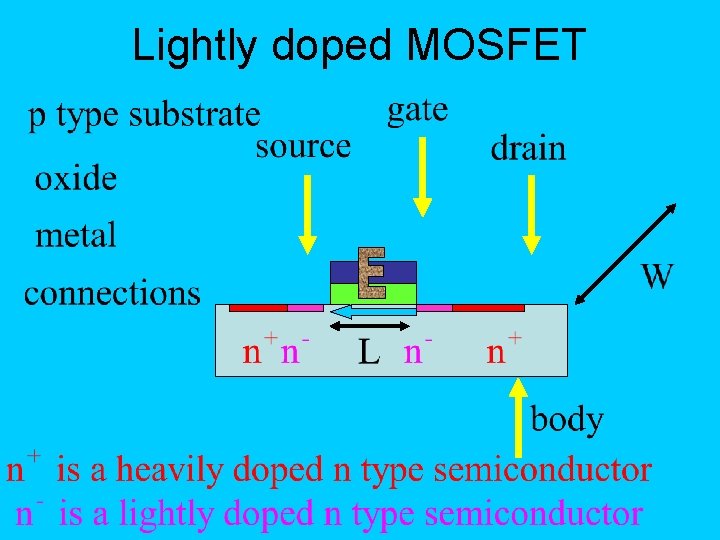

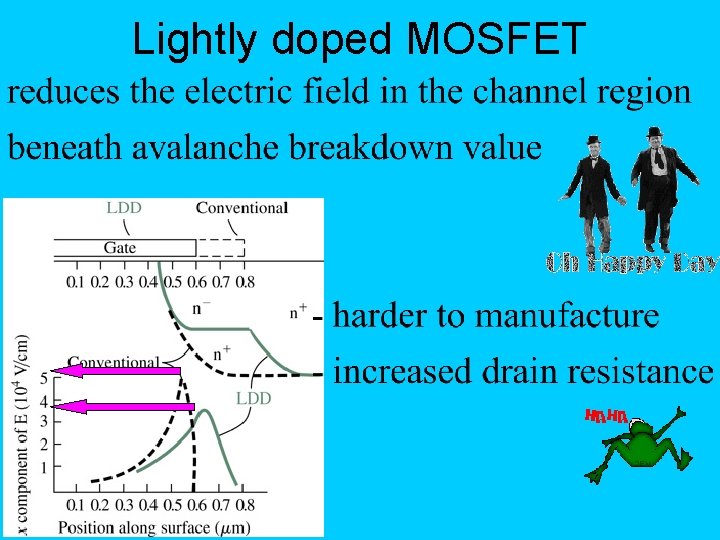

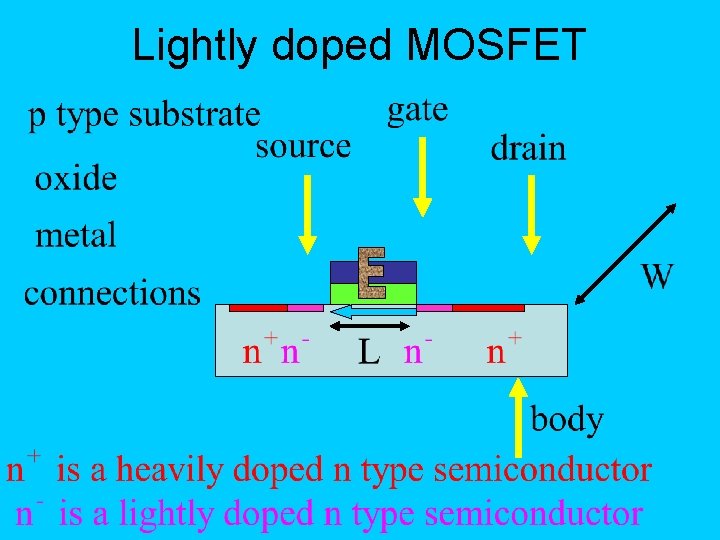

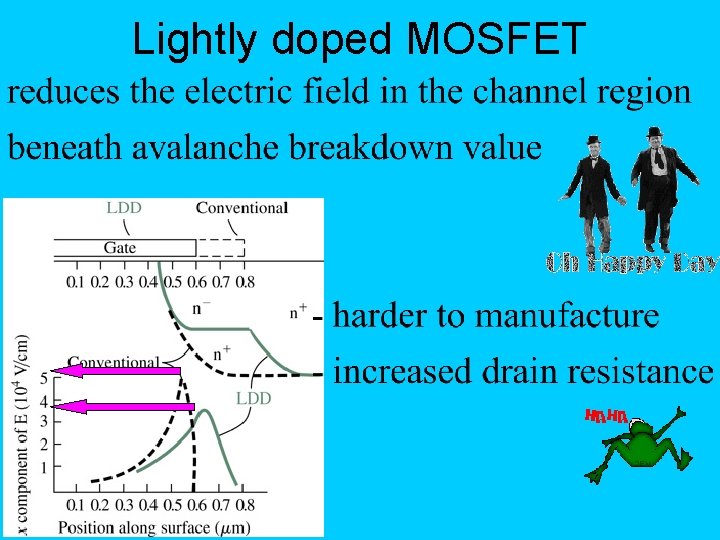

Lightly doped MOSFET

Lightly doped MOSFET

Transmission Lines Demonstration High Frequency Electronics Course EE 527 Andrew Rusek Oakland University Winter 2007 Demonstration is based on the materials collected from measurement set up to show sinusoidal and step responses of a transmission line with various terminations. Results of selected simulations are included.

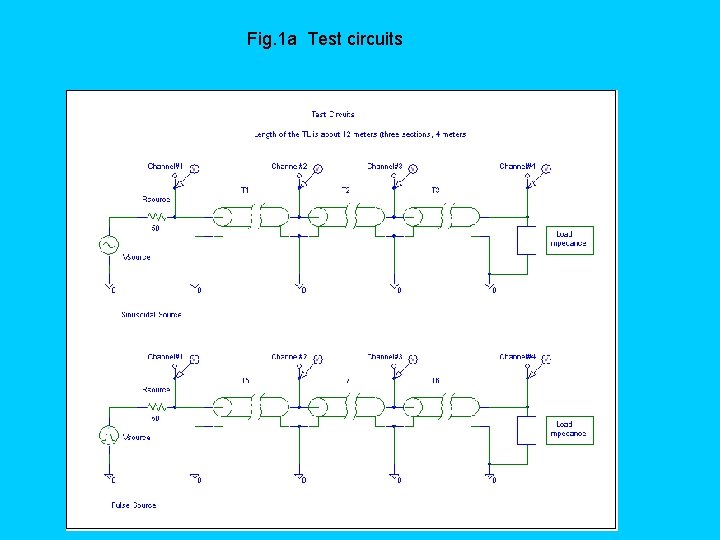

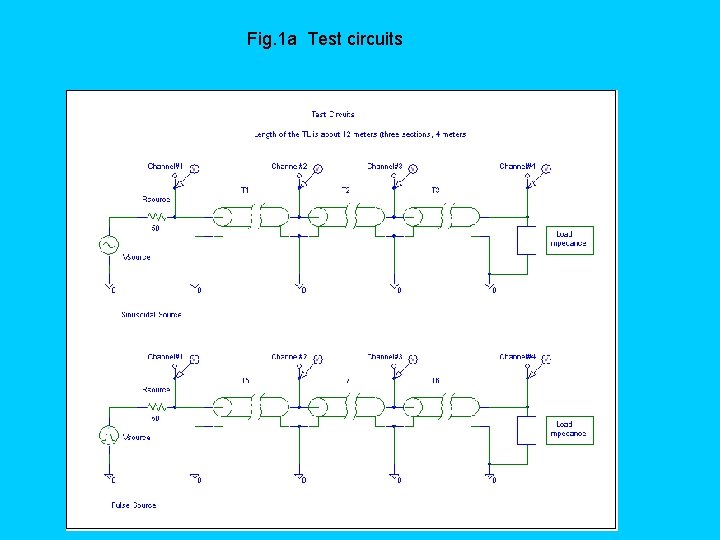

Fig. 1 a Test circuits

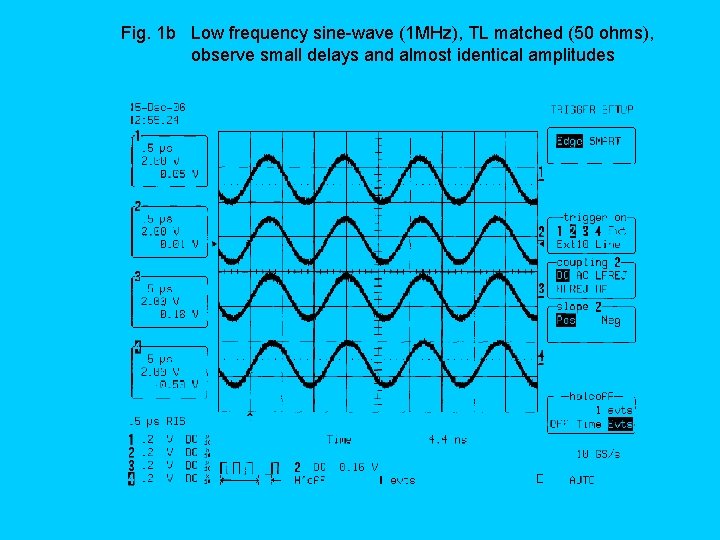

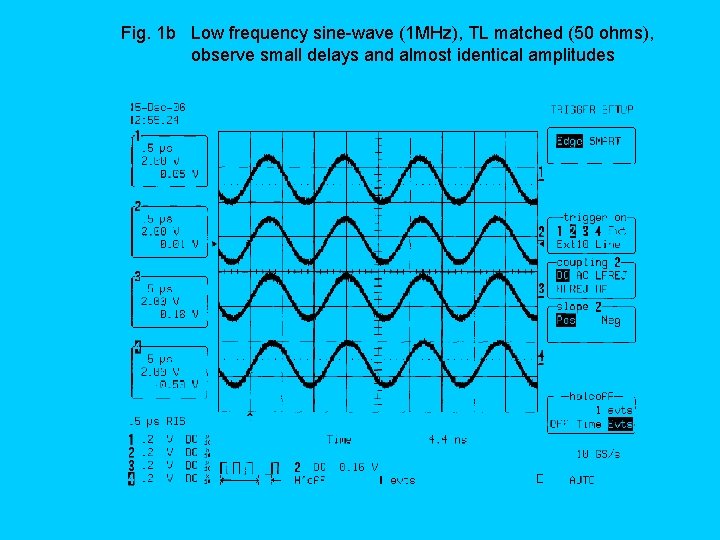

Fig. 1 b Low frequency sine-wave (1 MHz), TL matched (50 ohms), observe small delays and almost identical amplitudes

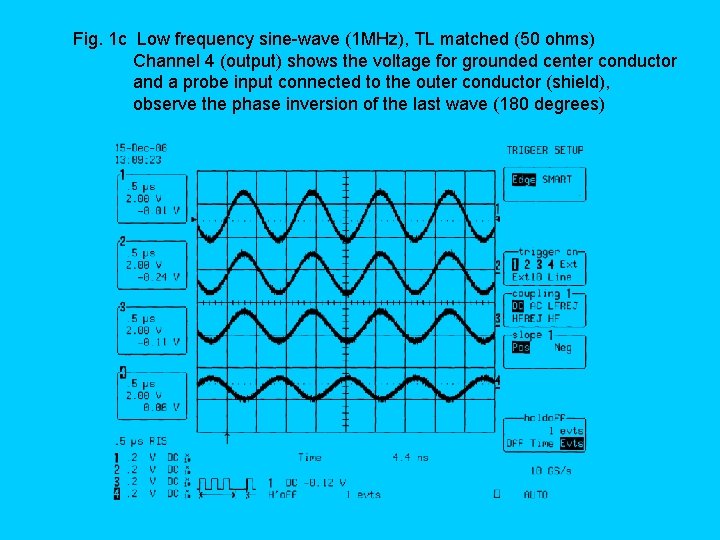

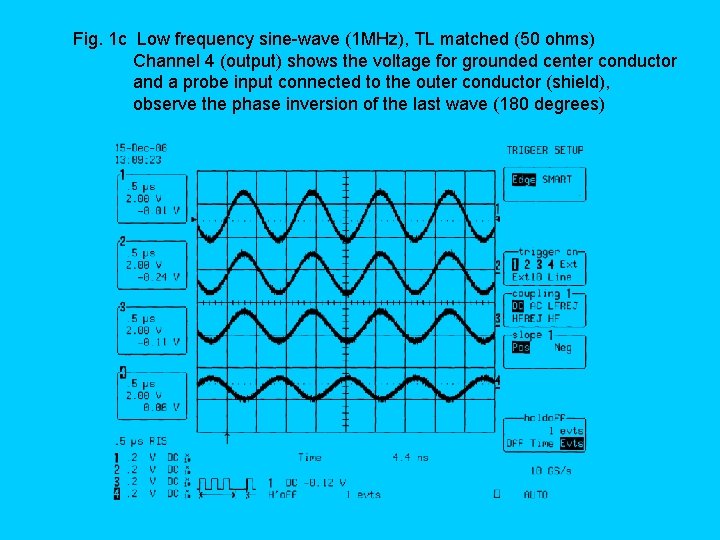

Fig. 1 c Low frequency sine-wave (1 MHz), TL matched (50 ohms) Channel 4 (output) shows the voltage for grounded center conductor and a probe input connected to the outer conductor (shield), observe the phase inversion of the last wave (180 degrees)

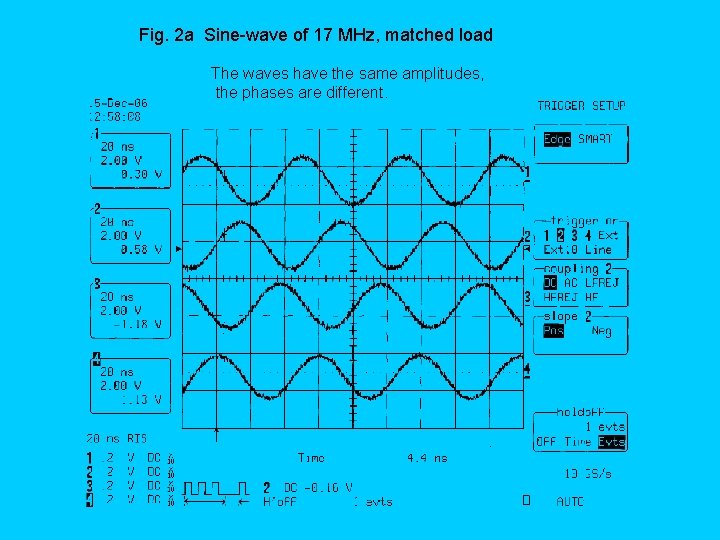

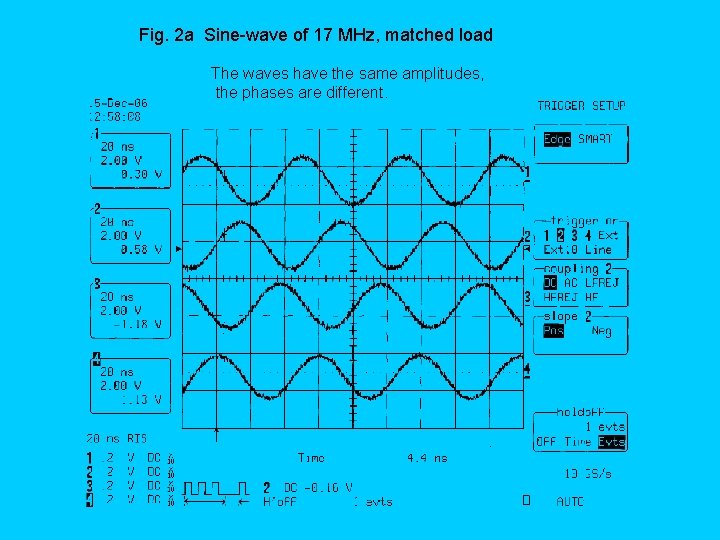

Fig. 2 a Sine-wave of 17 MHz, matched load The waves have the same amplitudes, the phases are different.

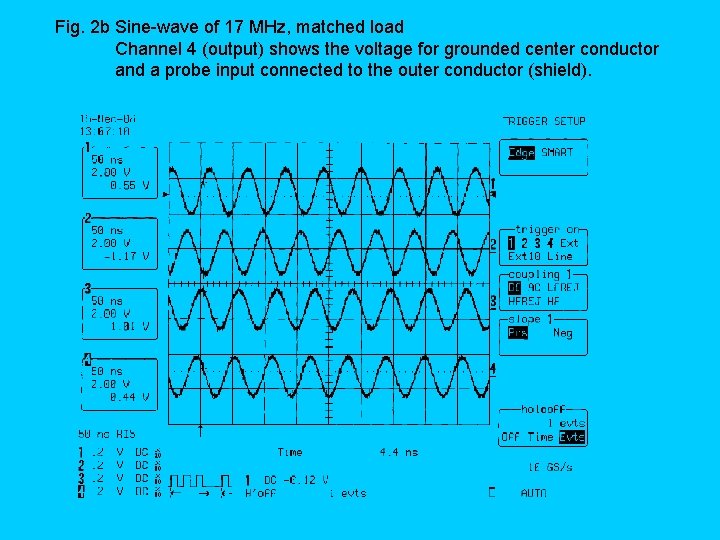

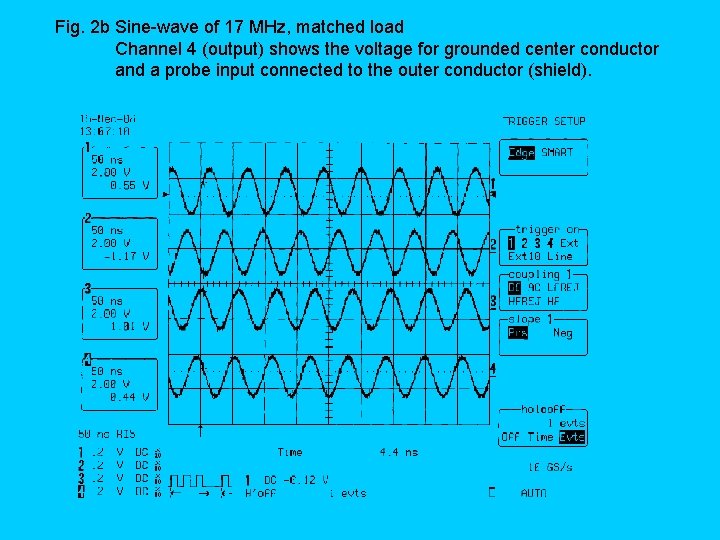

Fig. 2 b Sine-wave of 17 MHz, matched load Channel 4 (output) shows the voltage for grounded center conductor and a probe input connected to the outer conductor (shield).

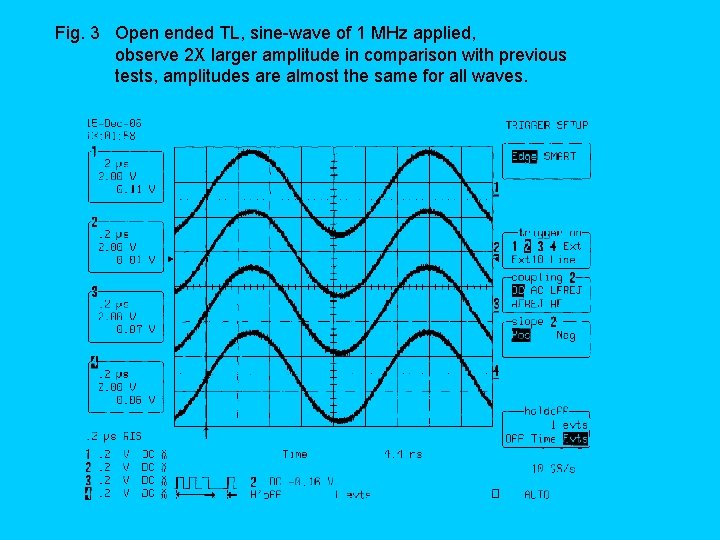

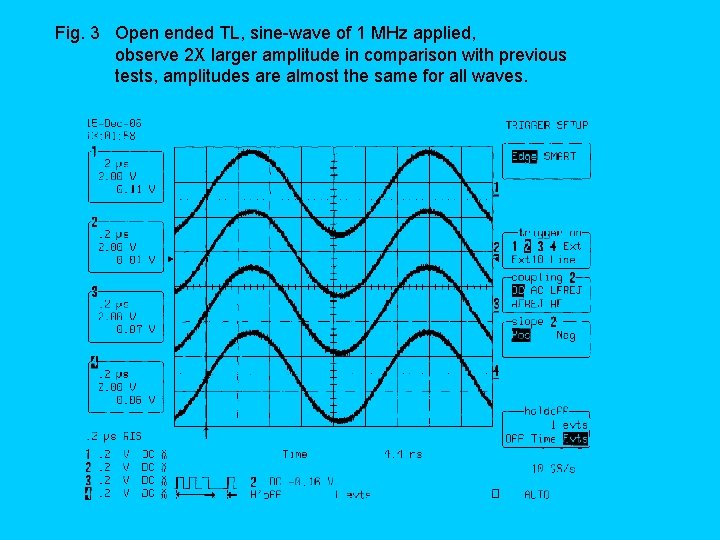

Fig. 3 Open ended TL, sine-wave of 1 MHz applied, observe 2 X larger amplitude in comparison with previous tests, amplitudes are almost the same for all waves.

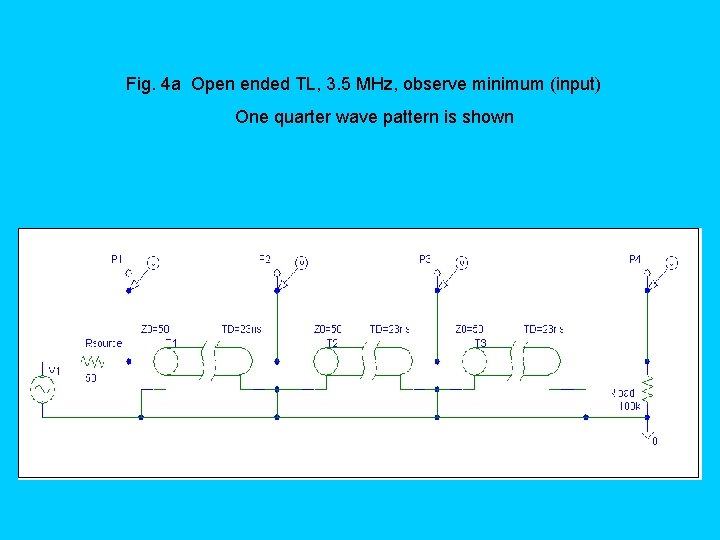

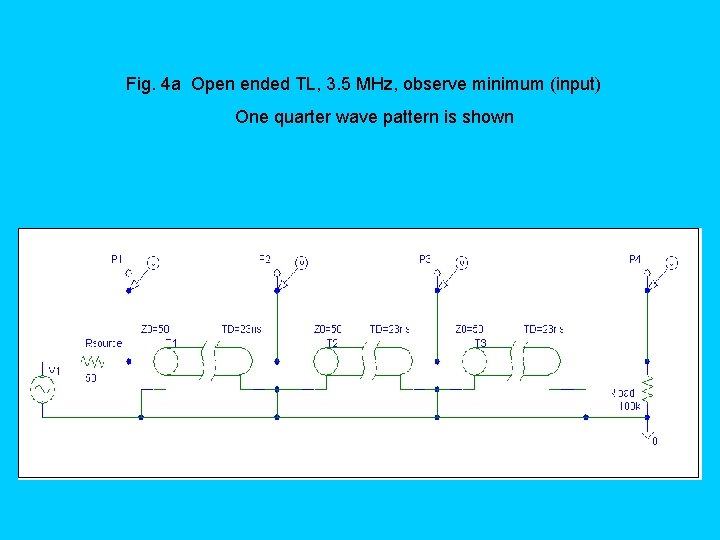

Fig. 4 a Open ended TL, 3. 5 MHz, observe minimum (input) One quarter wave pattern is shown

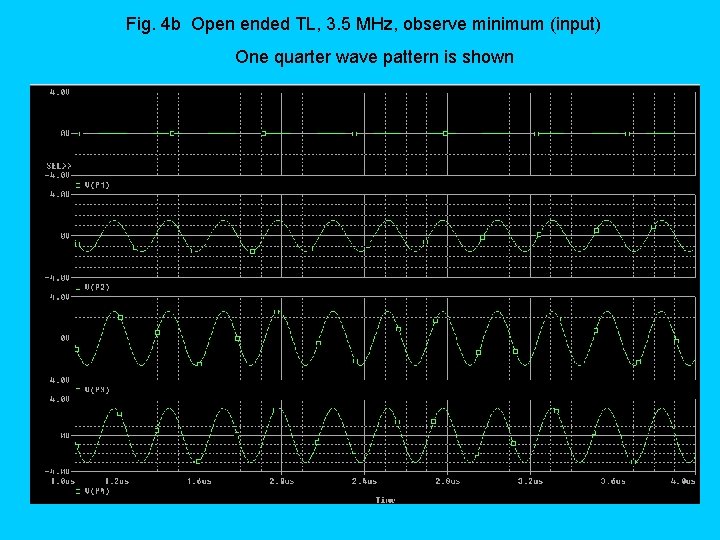

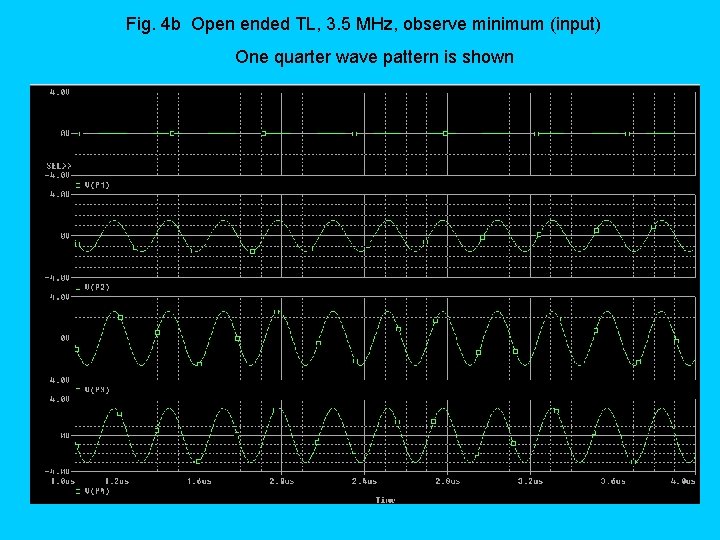

Fig. 4 b Open ended TL, 3. 5 MHz, observe minimum (input) One quarter wave pattern is shown

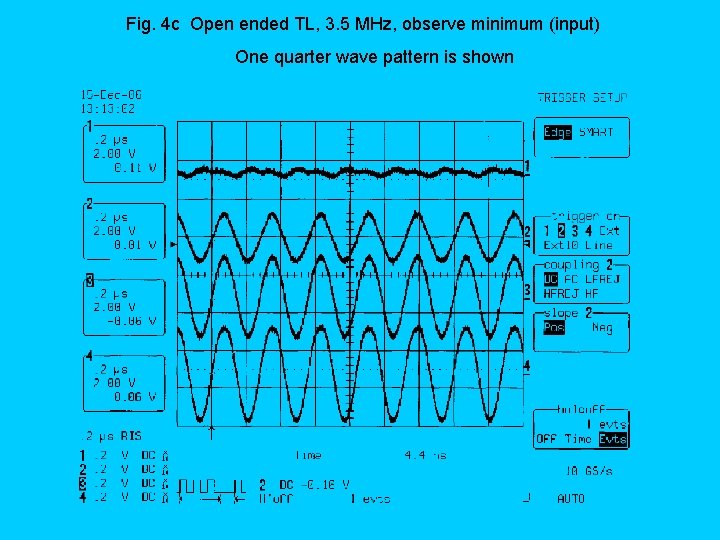

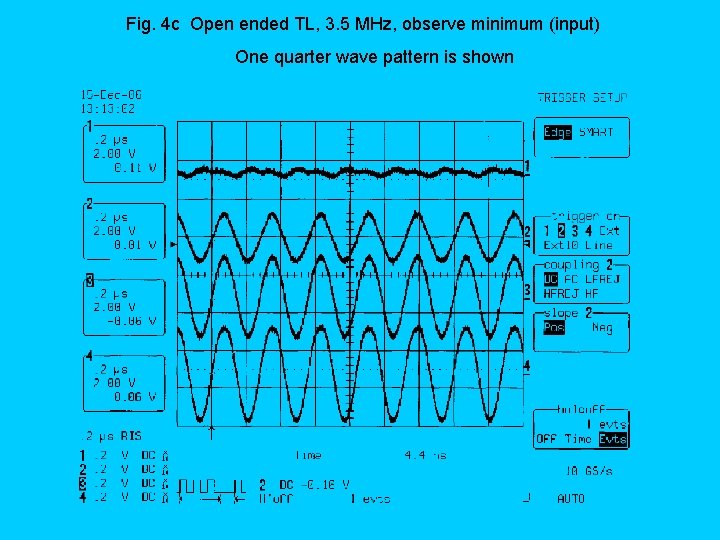

Fig. 4 c Open ended TL, 3. 5 MHz, observe minimum (input) One quarter wave pattern is shown

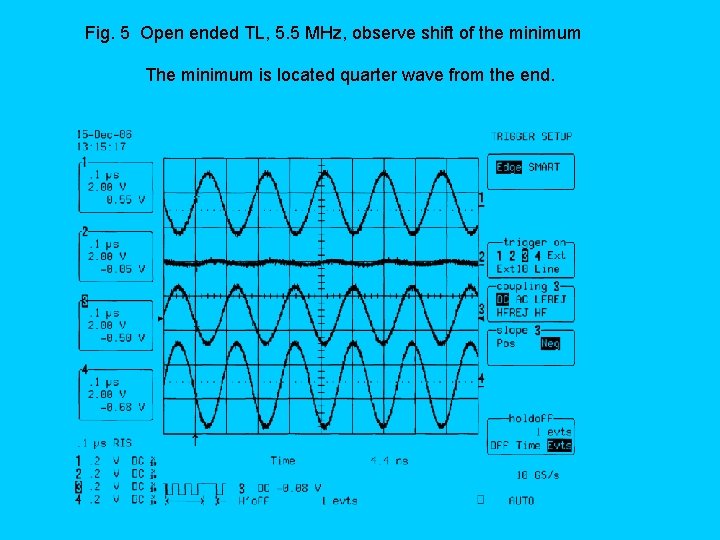

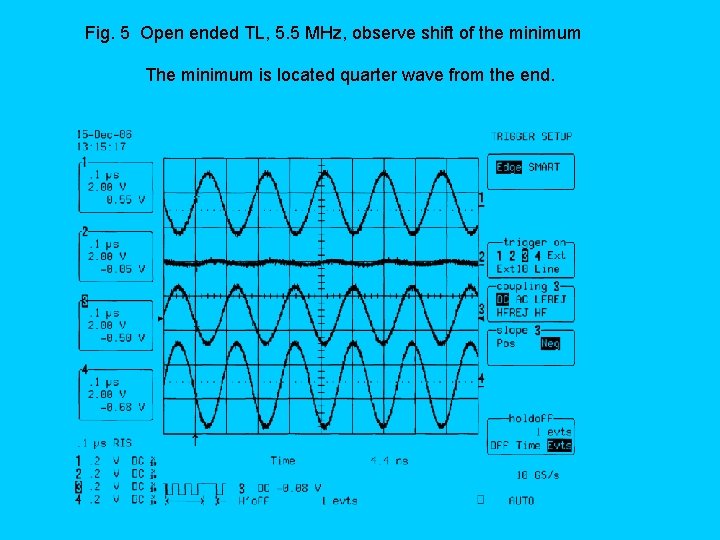

Fig. 5 Open ended TL, 5. 5 MHz, observe shift of the minimum The minimum is located quarter wave from the end.

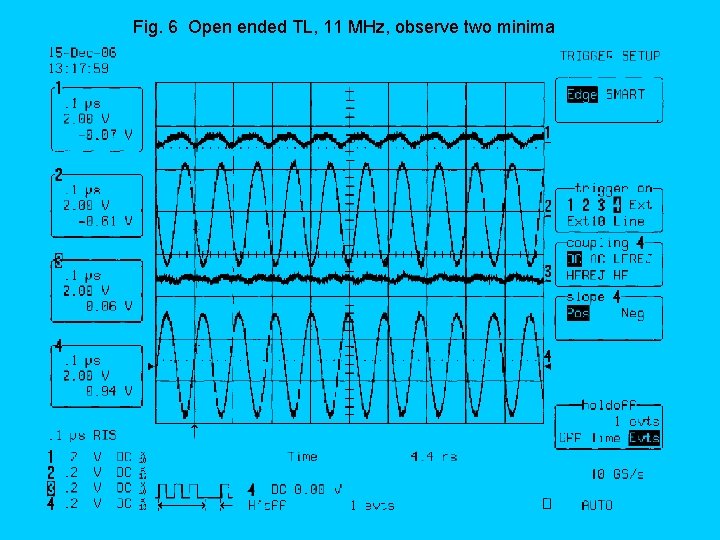

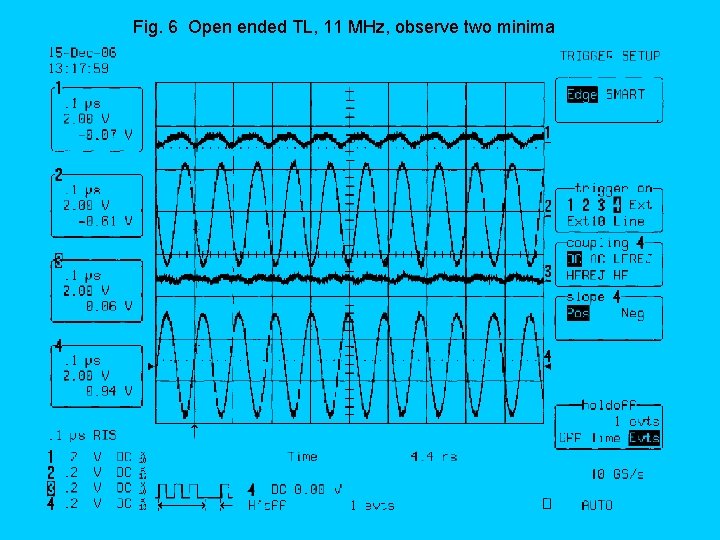

Fig. 6 Open ended TL, 11 MHz, observe two minima

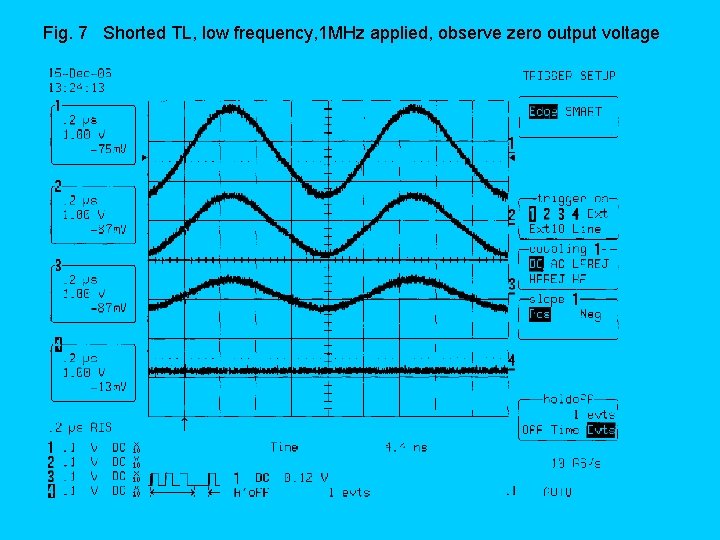

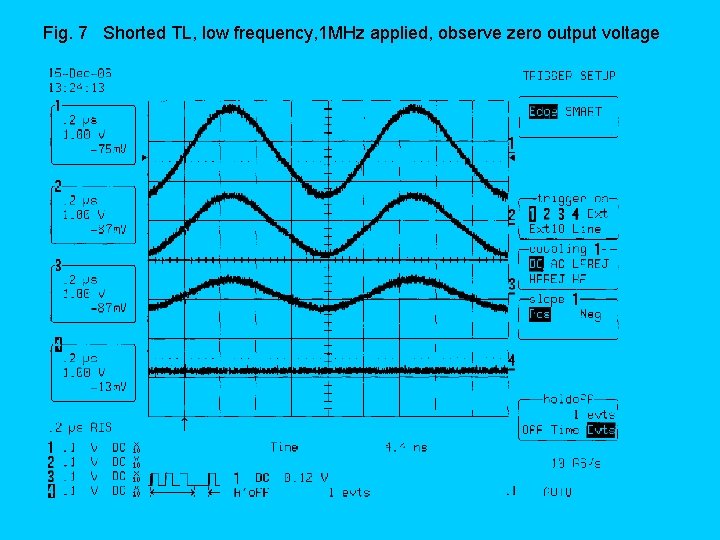

Fig. 7 Shorted TL, low frequency, 1 MHz applied, observe zero output voltage

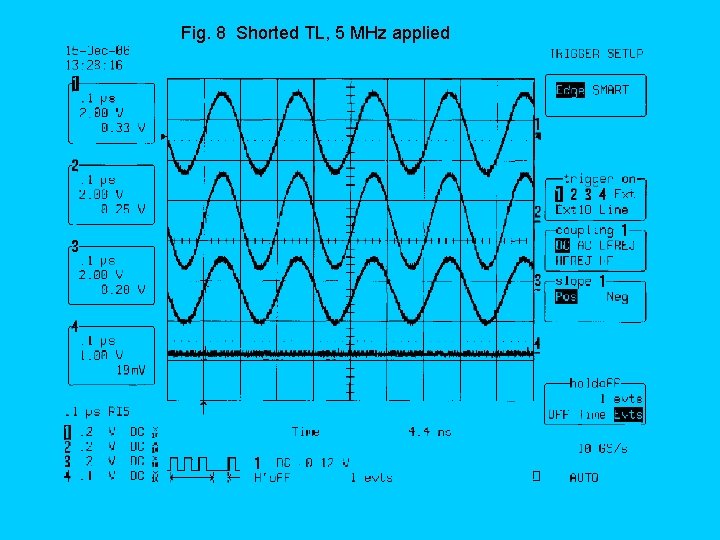

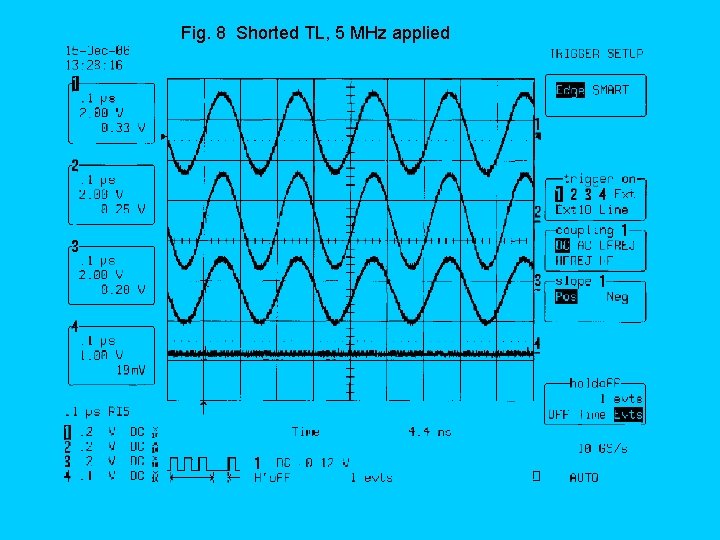

Fig. 8 Shorted TL, 5 MHz applied

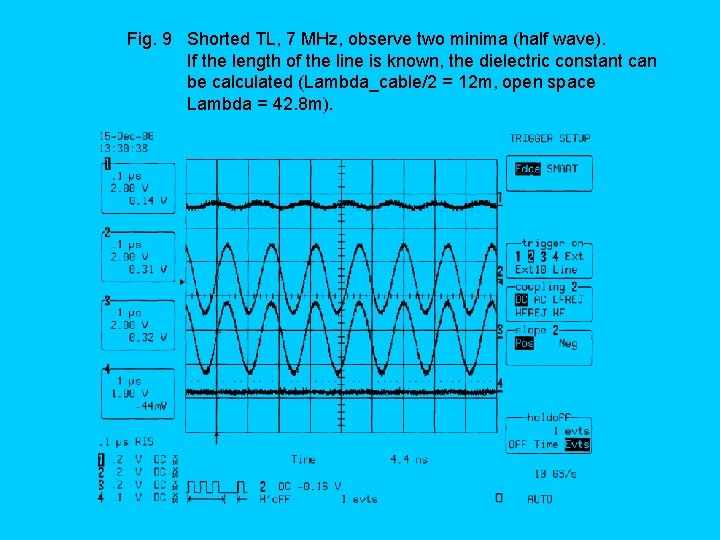

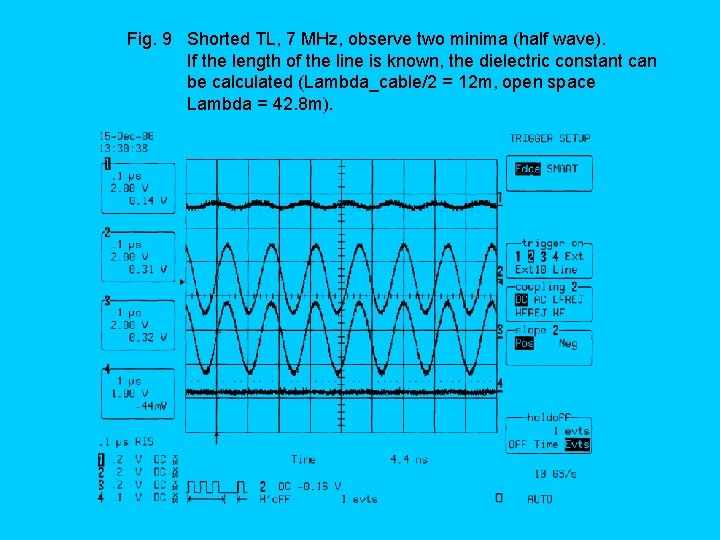

Fig. 9 Shorted TL, 7 MHz, observe two minima (half wave). If the length of the line is known, the dielectric constant can be calculated (Lambda_cable/2 = 12 m, open space Lambda = 42. 8 m).

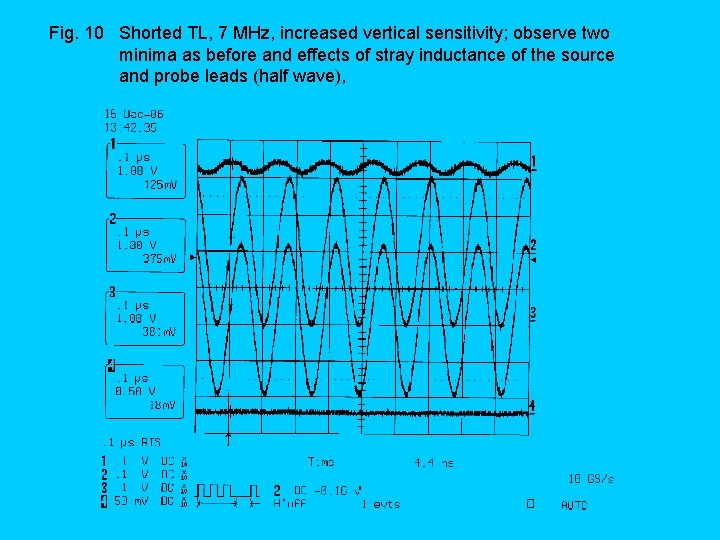

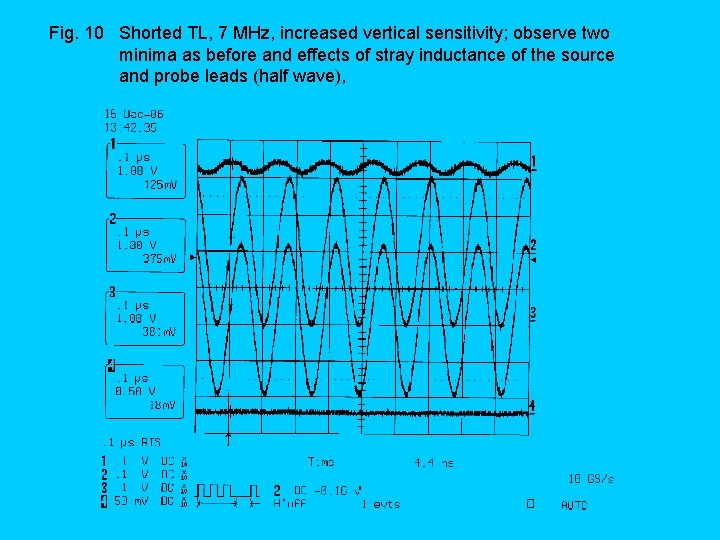

Fig. 10 Shorted TL, 7 MHz, increased vertical sensitivity; observe two minima as before and effects of stray inductance of the source and probe leads (half wave),

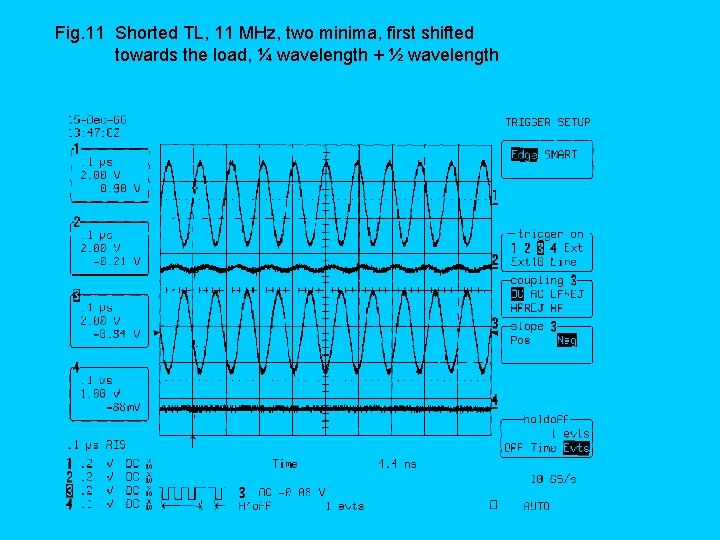

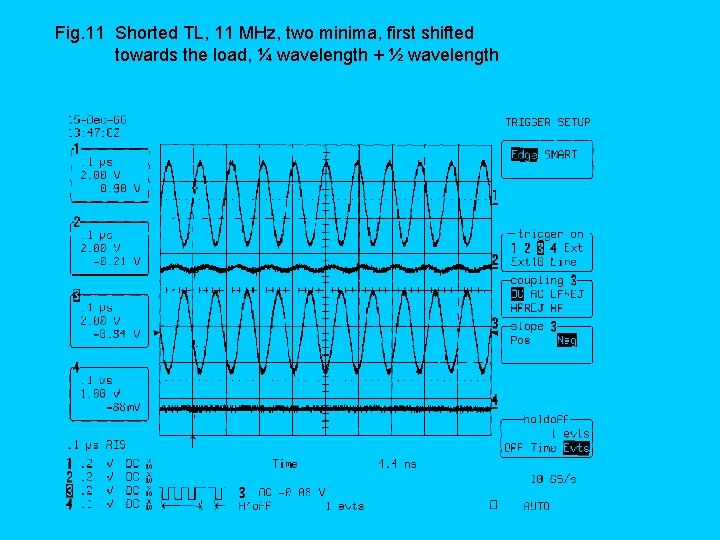

Fig. 11 Shorted TL, 11 MHz, two minima, first shifted towards the load, ¼ wavelength + ½ wavelength

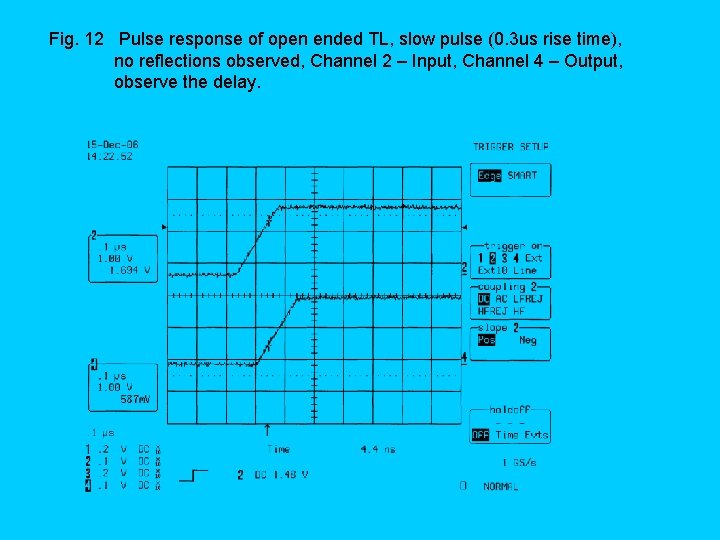

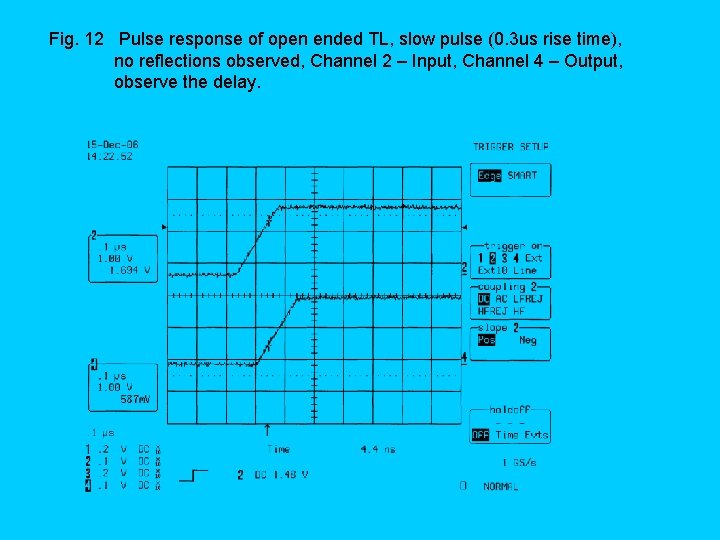

Fig. 12 Pulse response of open ended TL, slow pulse (0. 3 us rise time), no reflections observed, Channel 2 – Input, Channel 4 – Output, observe the delay.

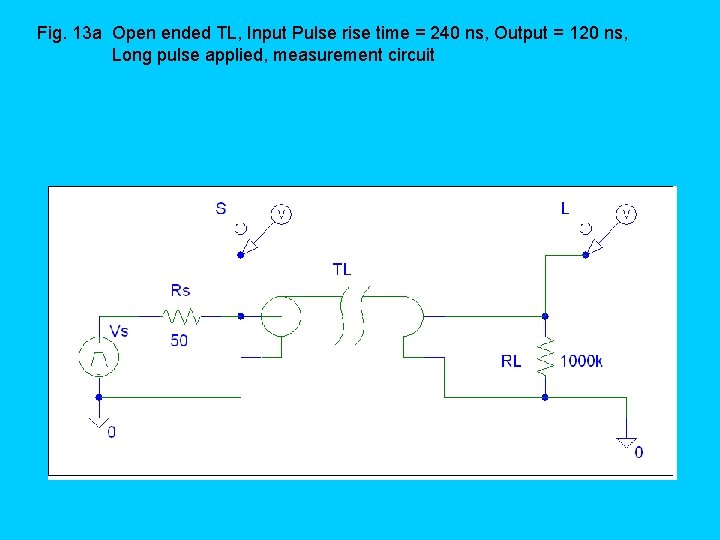

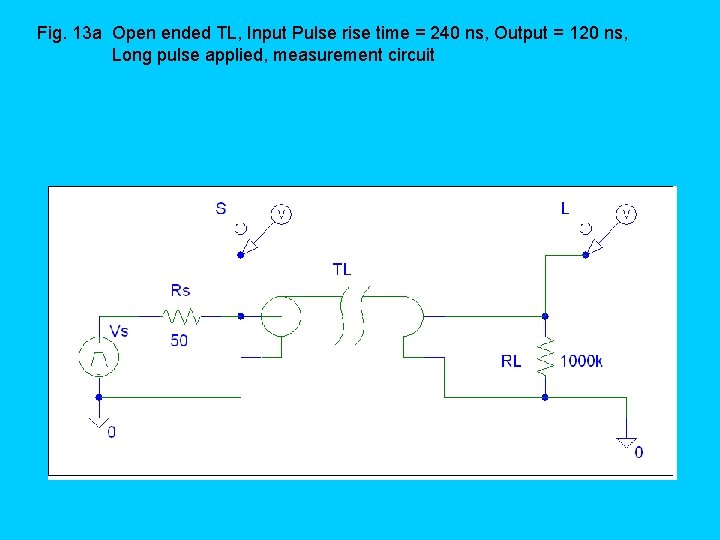

Fig. 13 a Open ended TL, Input Pulse rise time = 240 ns, Output = 120 ns, Long pulse applied, measurement circuit

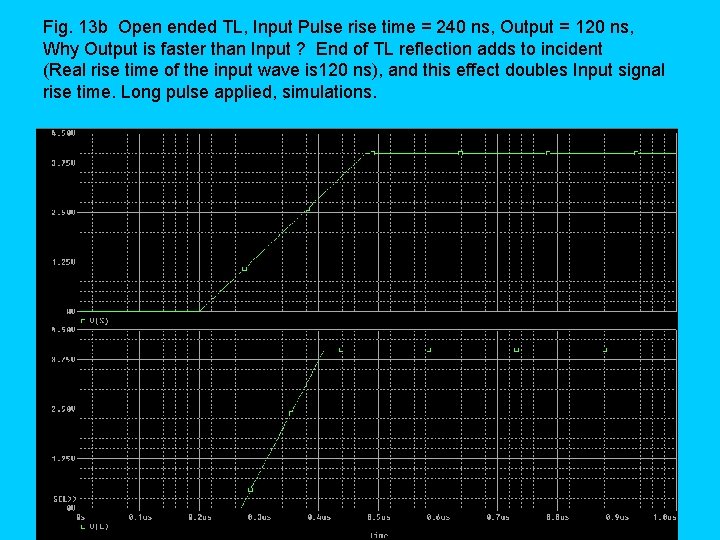

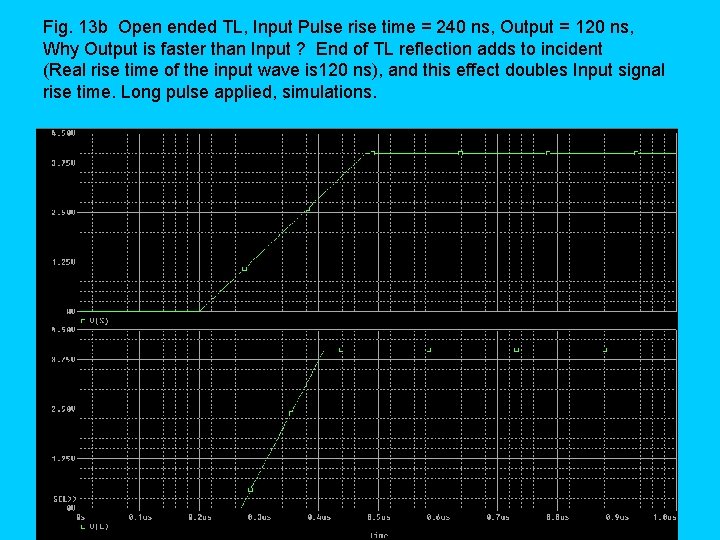

Fig. 13 b Open ended TL, Input Pulse rise time = 240 ns, Output = 120 ns, Why Output is faster than Input ? End of TL reflection adds to incident (Real rise time of the input wave is 120 ns), and this effect doubles Input signal rise time. Long pulse applied, simulations.

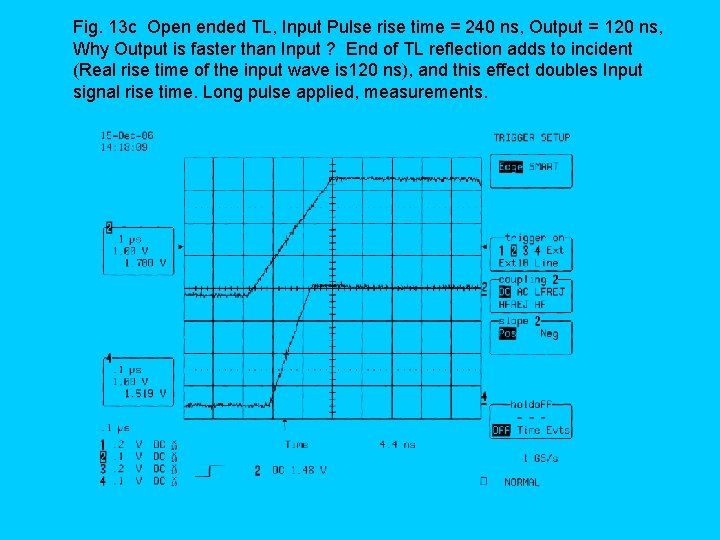

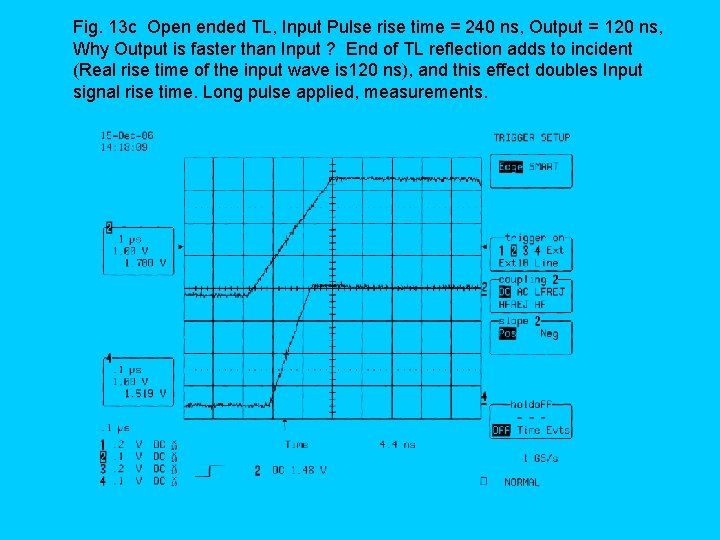

Fig. 13 c Open ended TL, Input Pulse rise time = 240 ns, Output = 120 ns, Why Output is faster than Input ? End of TL reflection adds to incident (Real rise time of the input wave is 120 ns), and this effect doubles Input signal rise time. Long pulse applied, measurements.

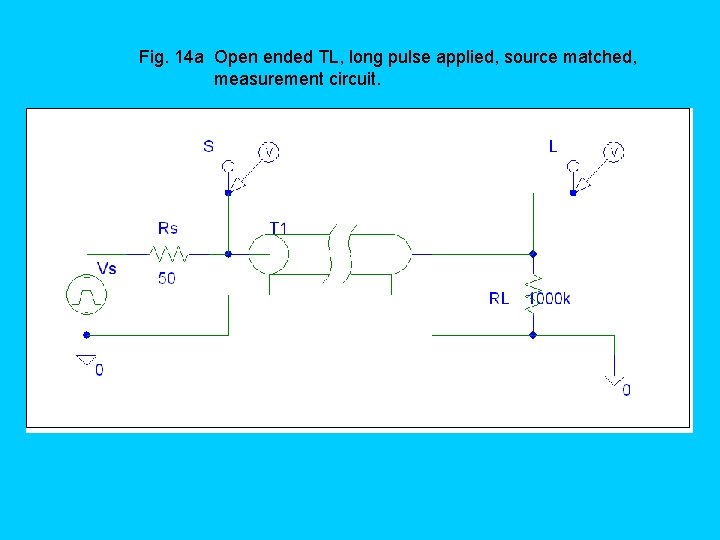

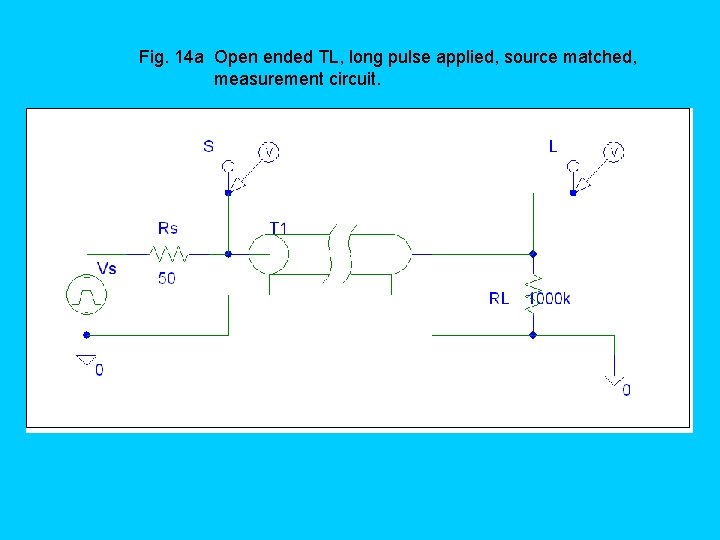

Fig. 14 a Open ended TL, long pulse applied, source matched, measurement circuit.

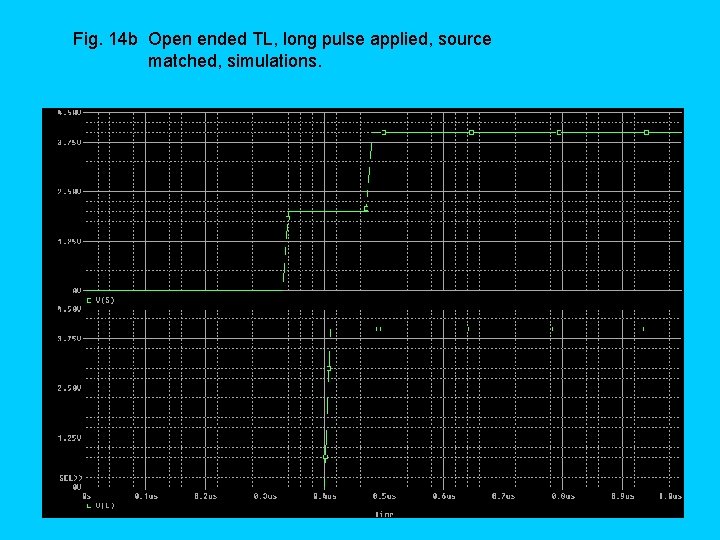

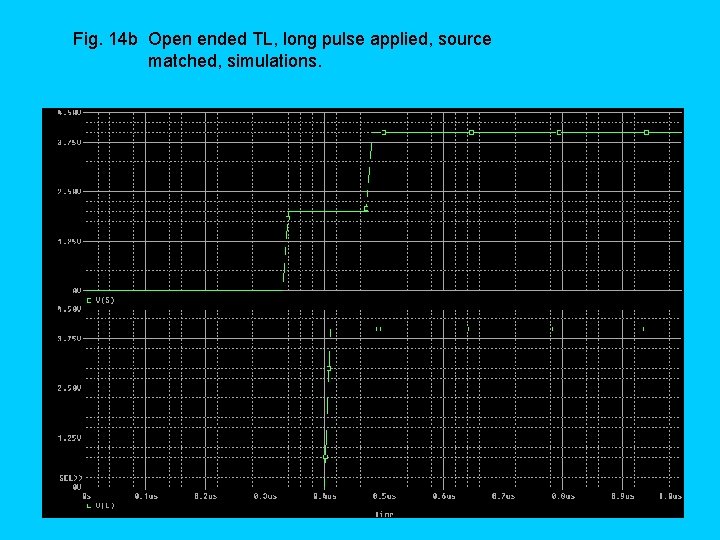

Fig. 14 b Open ended TL, long pulse applied, source matched, simulations.

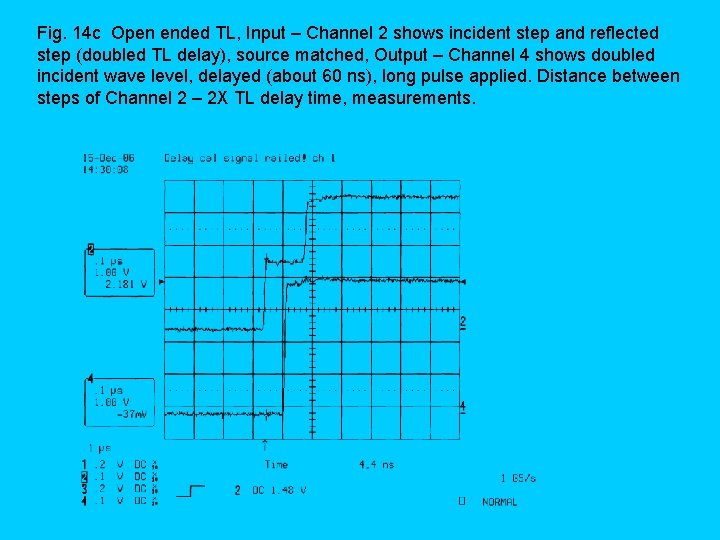

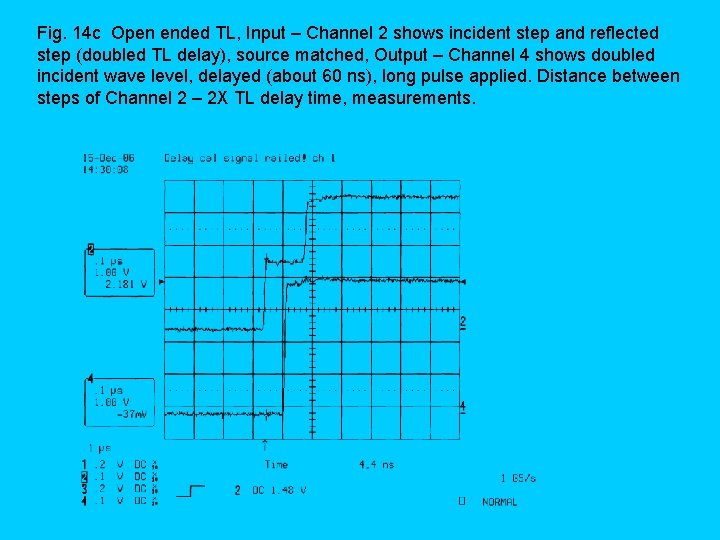

Fig. 14 c Open ended TL, Input – Channel 2 shows incident step and reflected step (doubled TL delay), source matched, Output – Channel 4 shows doubled incident wave level, delayed (about 60 ns), long pulse applied. Distance between steps of Channel 2 – 2 X TL delay time, measurements.

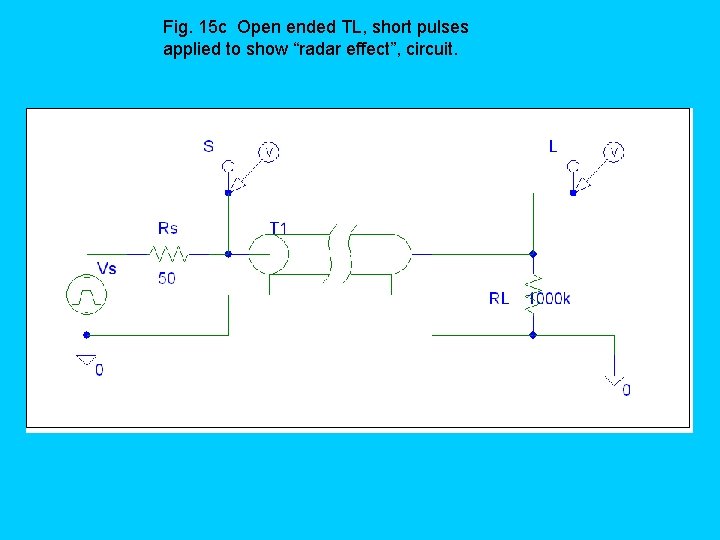

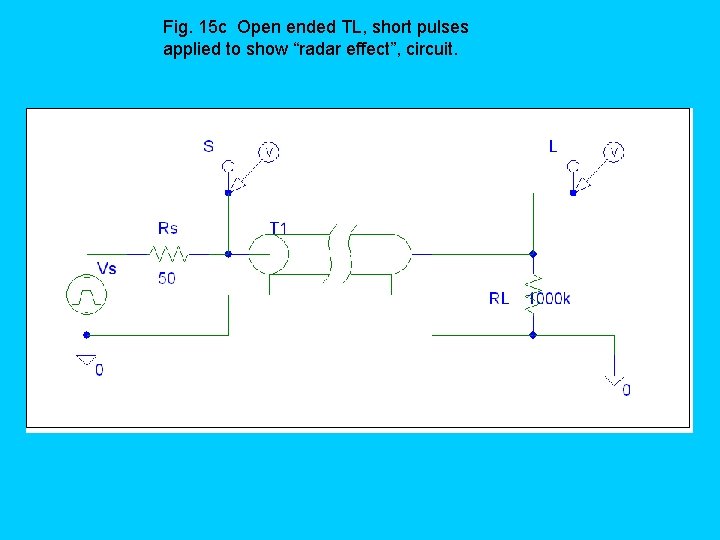

Fig. 15 c Open ended TL, short pulses applied to show “radar effect”, circuit.

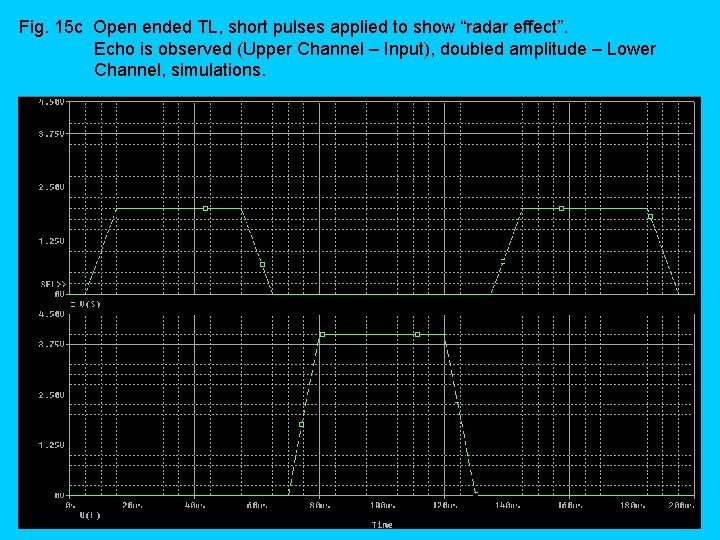

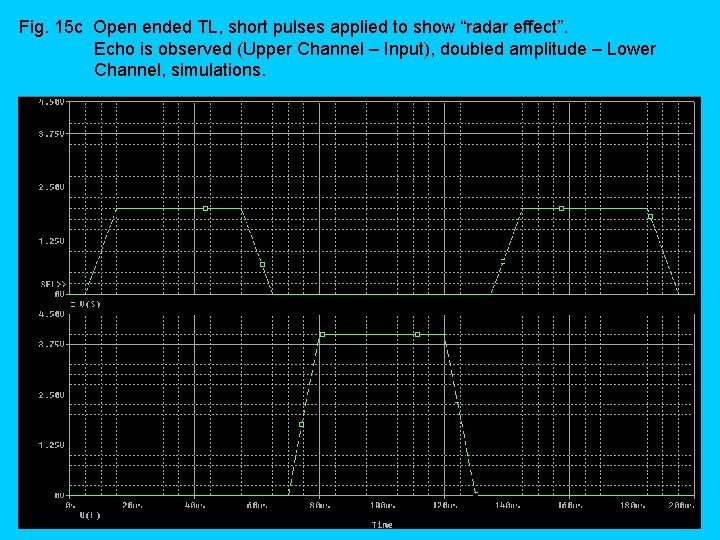

Fig. 15 c Open ended TL, short pulses applied to show “radar effect”. Echo is observed (Upper Channel – Input), doubled amplitude – Lower Channel, simulations.

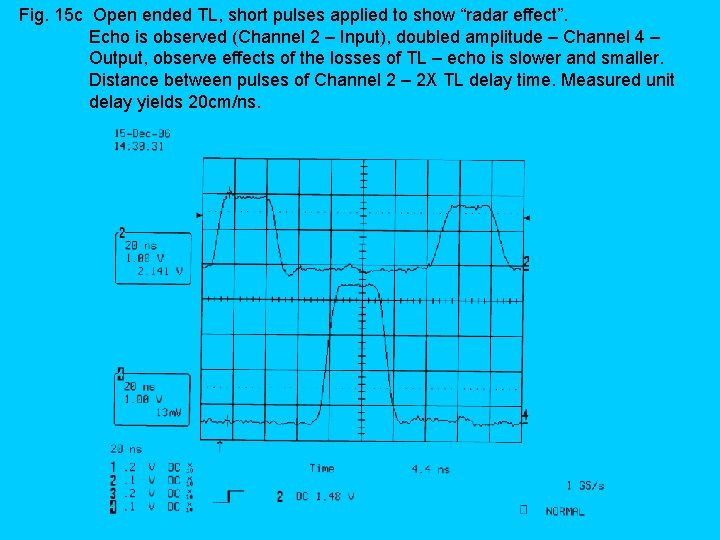

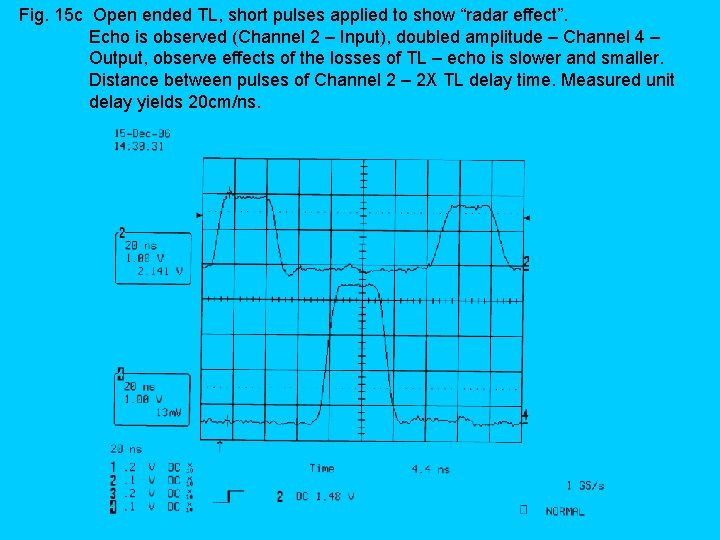

Fig. 15 c Open ended TL, short pulses applied to show “radar effect”. Echo is observed (Channel 2 – Input), doubled amplitude – Channel 4 – Output, observe effects of the losses of TL – echo is slower and smaller. Distance between pulses of Channel 2 – 2 X TL delay time. Measured unit delay yields 20 cm/ns.

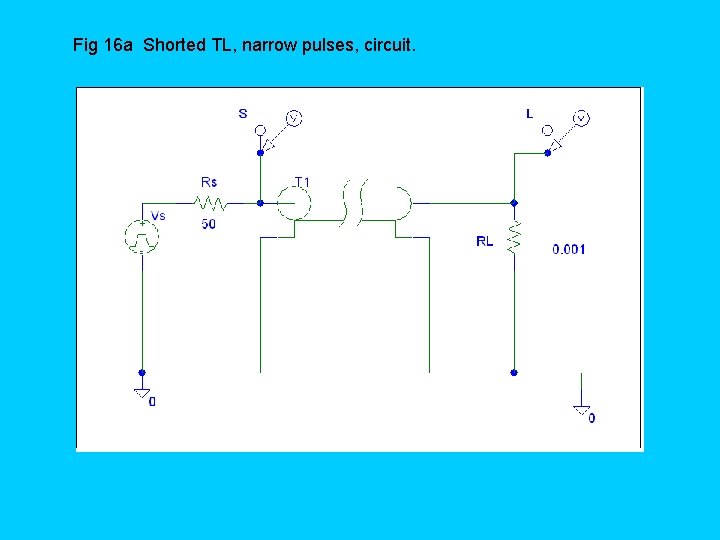

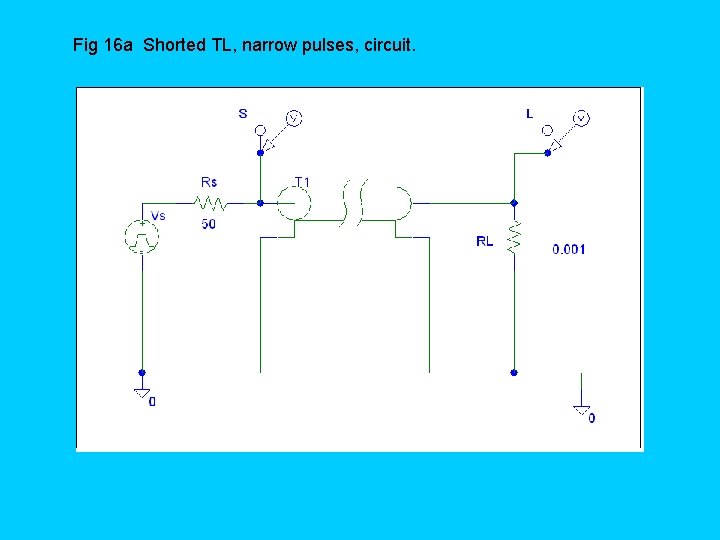

Fig 16 a Shorted TL, narrow pulses, circuit.

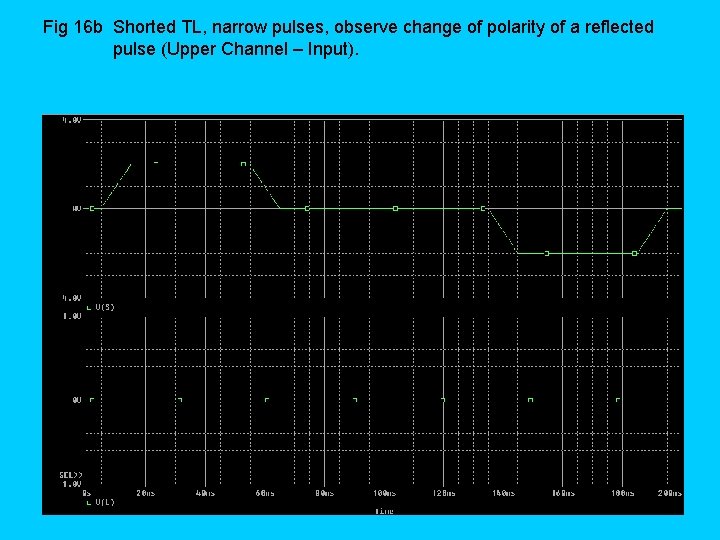

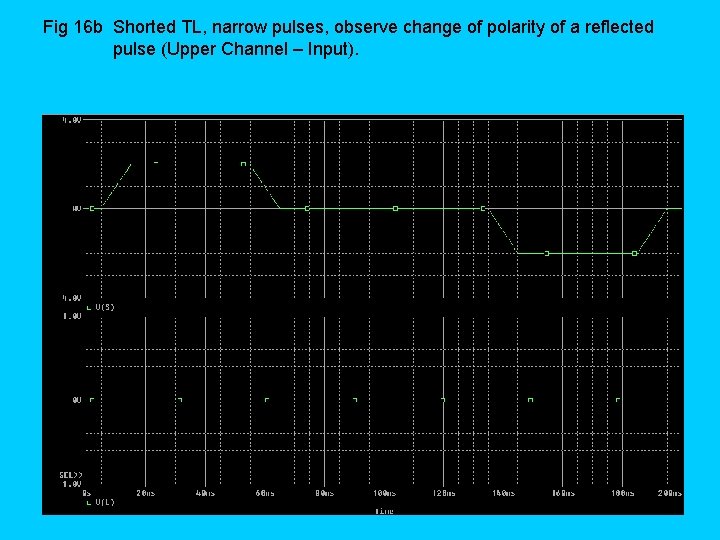

Fig 16 b Shorted TL, narrow pulses, observe change of polarity of a reflected pulse (Upper Channel – Input).

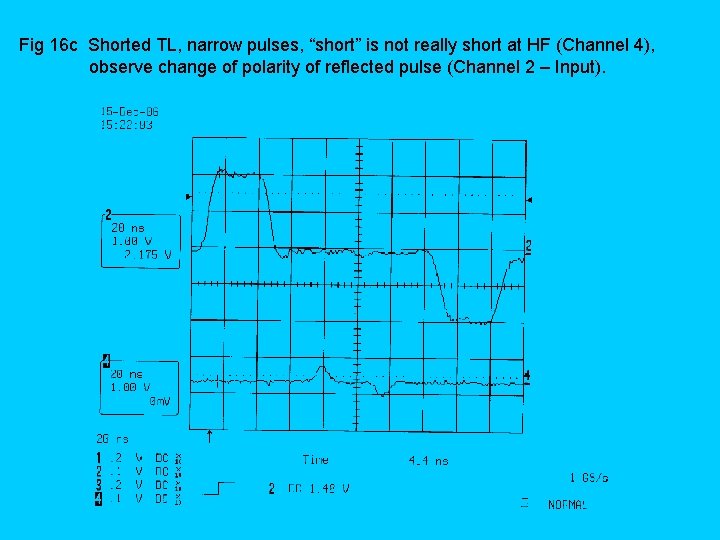

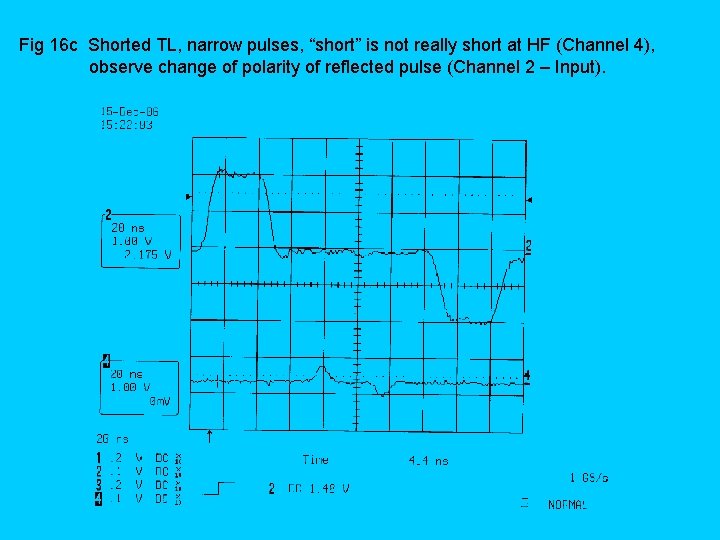

Fig 16 c Shorted TL, narrow pulses, “short” is not really short at HF (Channel 4), observe change of polarity of reflected pulse (Channel 2 – Input).

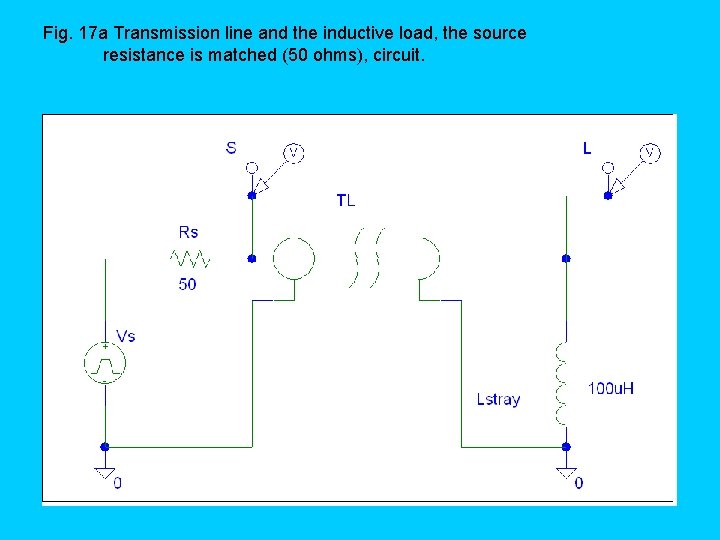

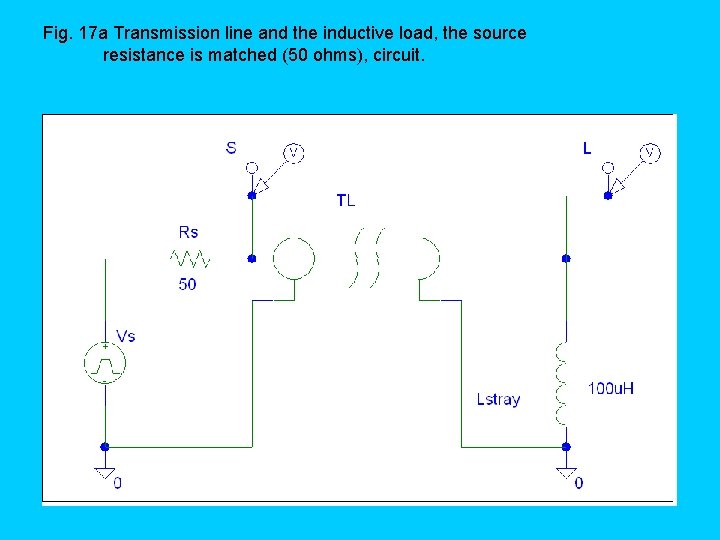

Fig. 17 a Transmission line and the inductive load, the source resistance is matched (50 ohms), circuit.

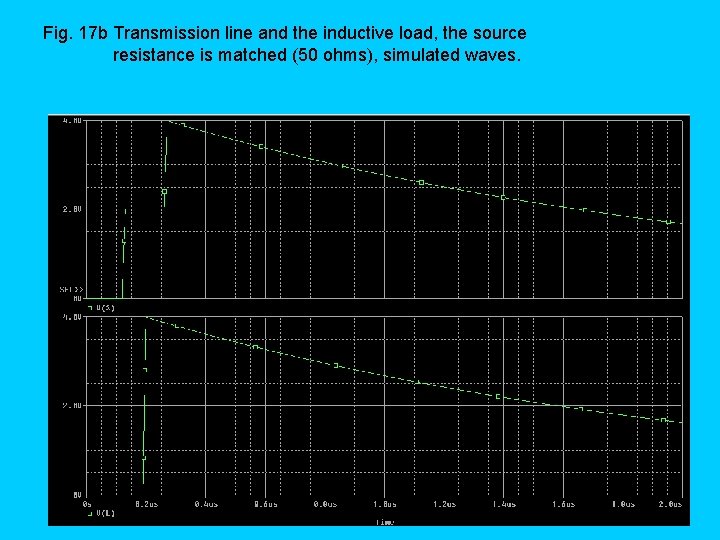

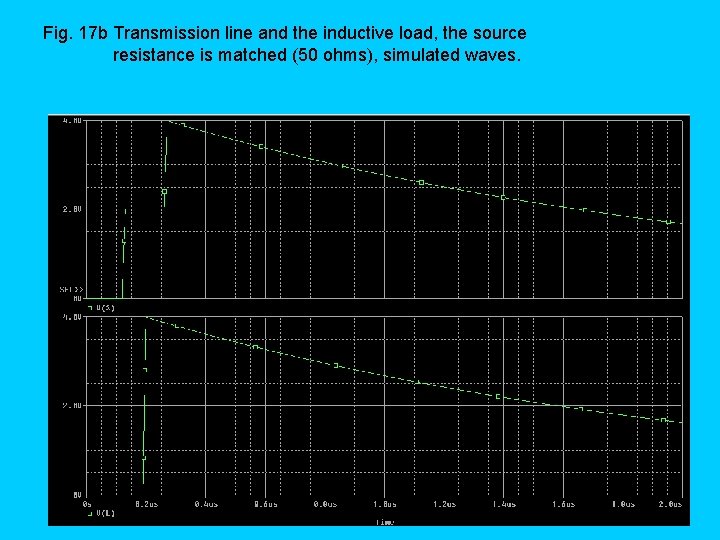

Fig. 17 b Transmission line and the inductive load, the source resistance is matched (50 ohms), simulated waves.

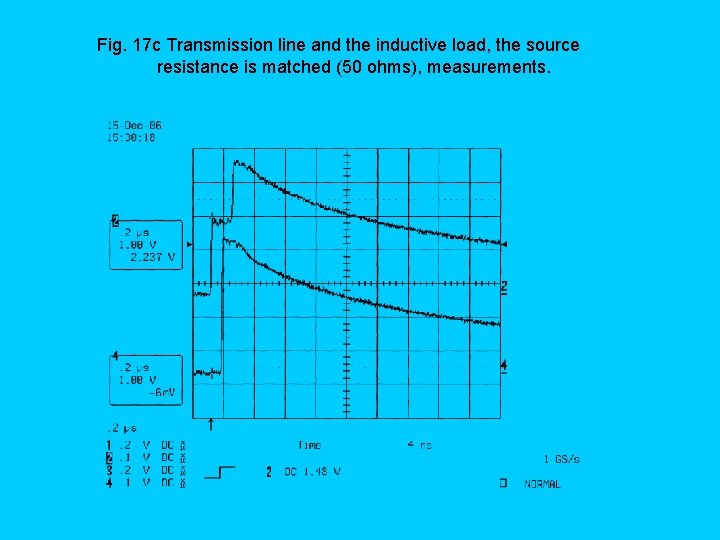

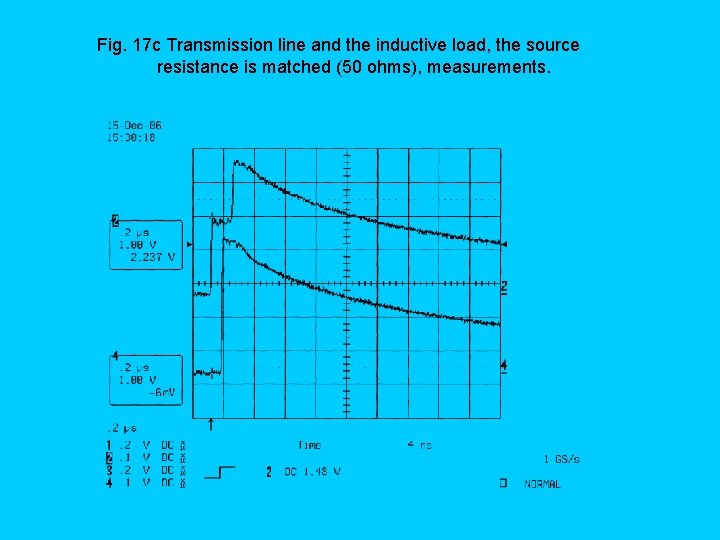

Fig. 17 c Transmission line and the inductive load, the source resistance is matched (50 ohms), measurements.

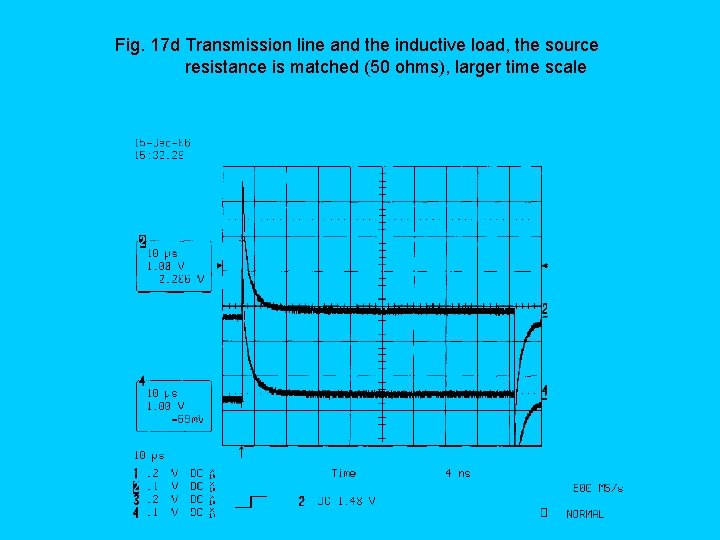

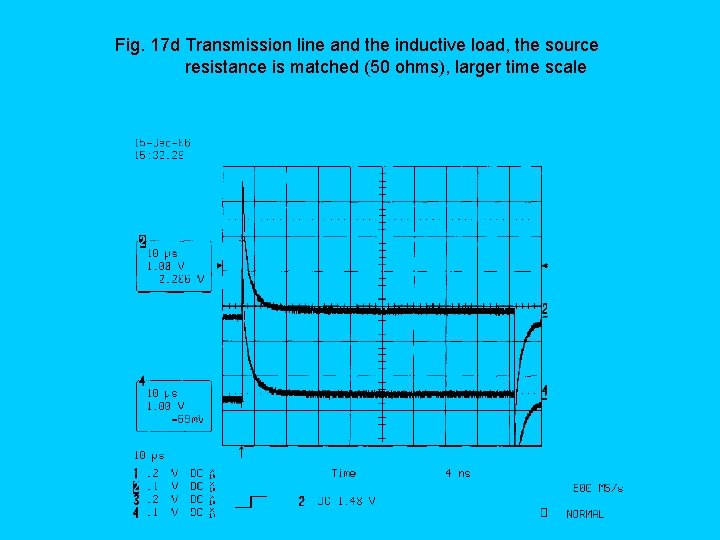

Fig. 17 d Transmission line and the inductive load, the source resistance is matched (50 ohms), larger time scale

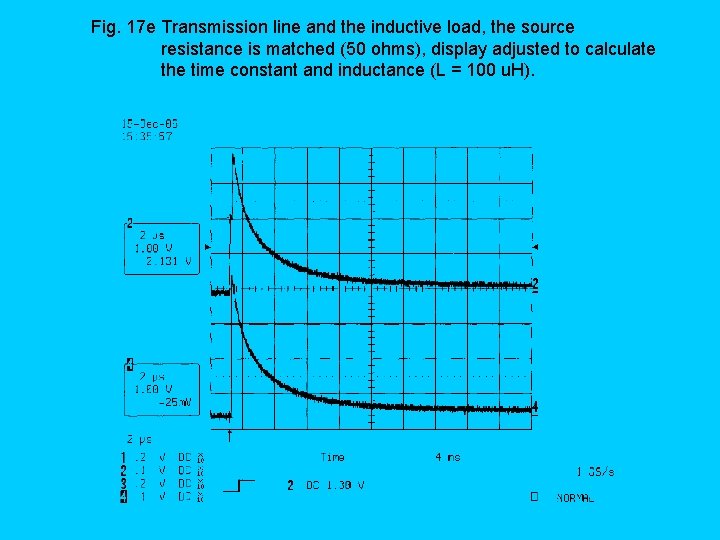

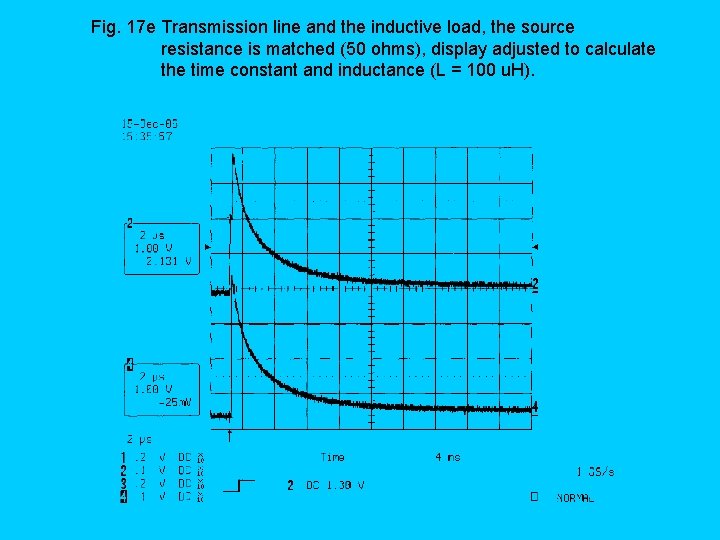

Fig. 17 e Transmission line and the inductive load, the source resistance is matched (50 ohms), display adjusted to calculate the time constant and inductance (L = 100 u. H).

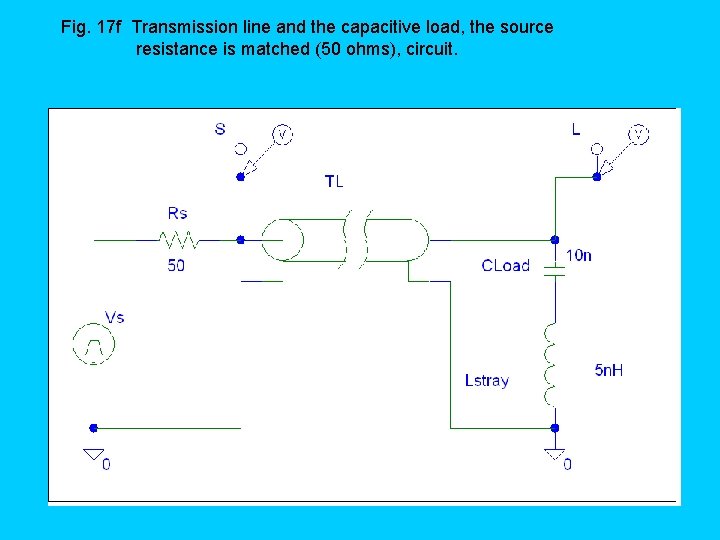

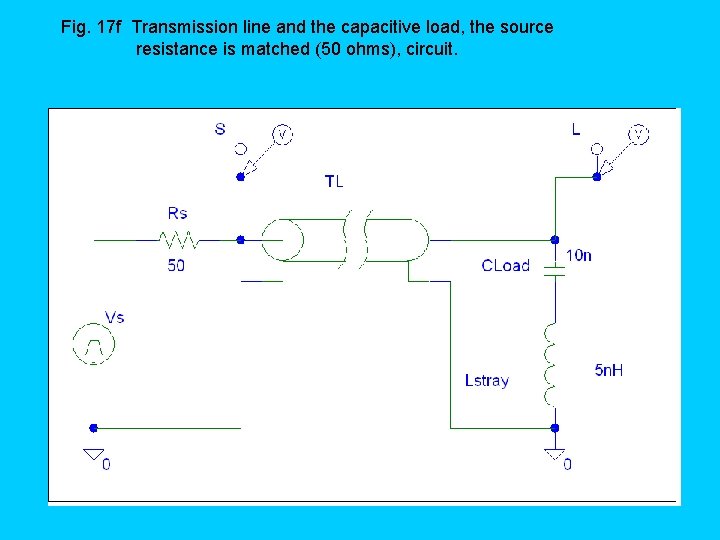

Fig. 17 f Transmission line and the capacitive load, the source resistance is matched (50 ohms), circuit.

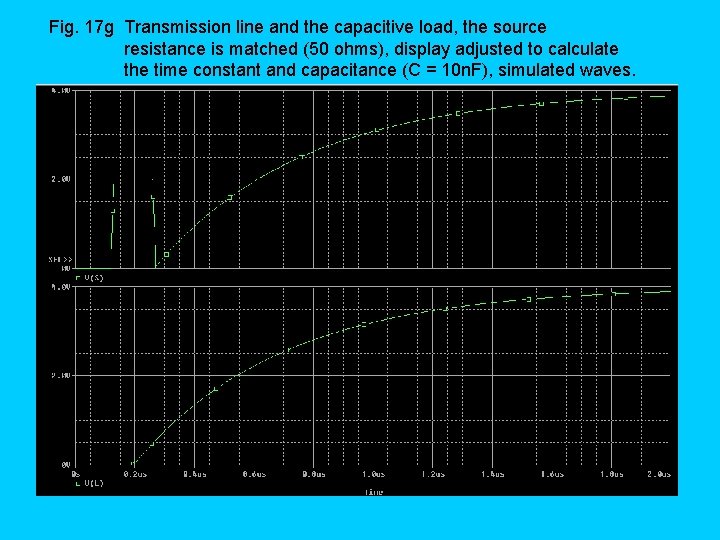

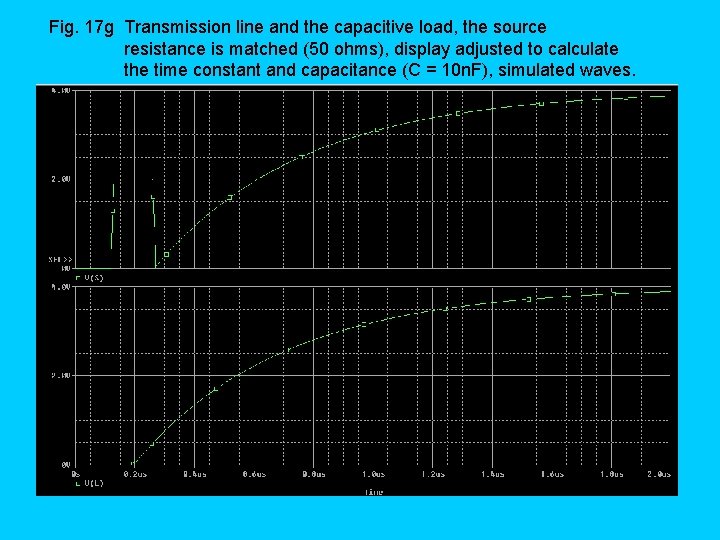

Fig. 17 g Transmission line and the capacitive load, the source resistance is matched (50 ohms), display adjusted to calculate the time constant and capacitance (C = 10 n. F), simulated waves.

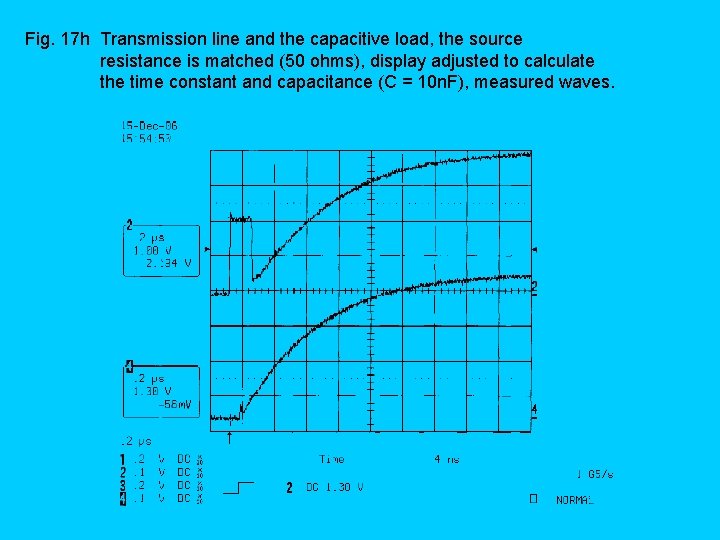

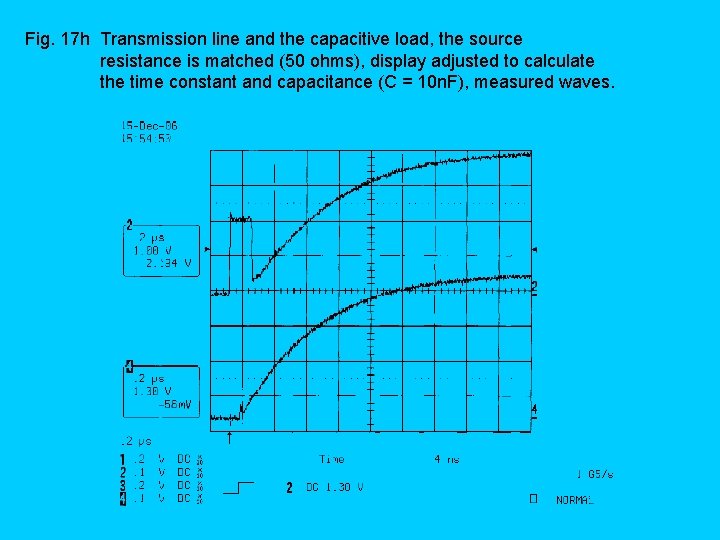

Fig. 17 h Transmission line and the capacitive load, the source resistance is matched (50 ohms), display adjusted to calculate the time constant and capacitance (C = 10 n. F), measured waves.

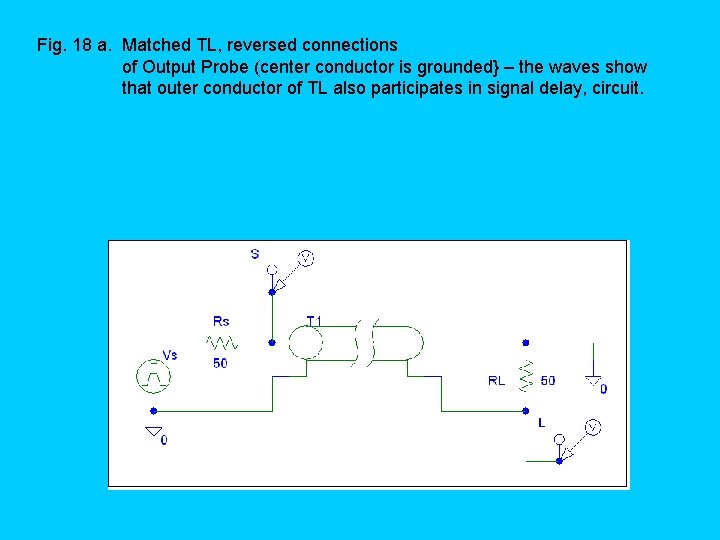

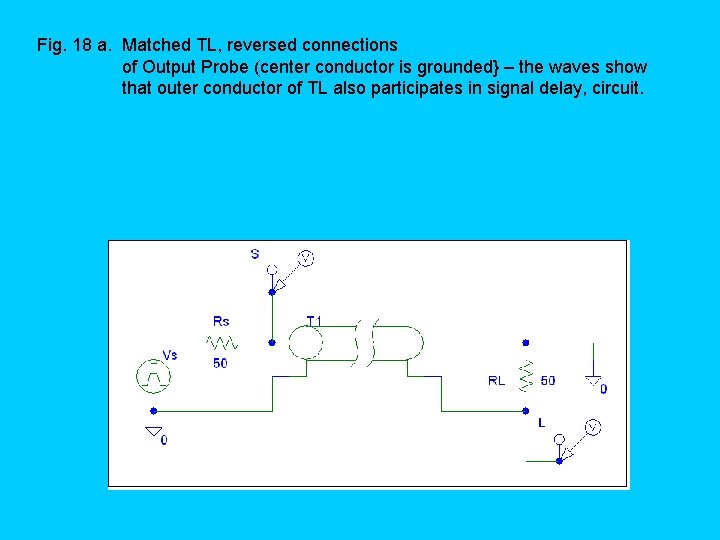

Fig. 18 a. Matched TL, reversed connections of Output Probe (center conductor is grounded} – the waves show that outer conductor of TL also participates in signal delay, circuit.

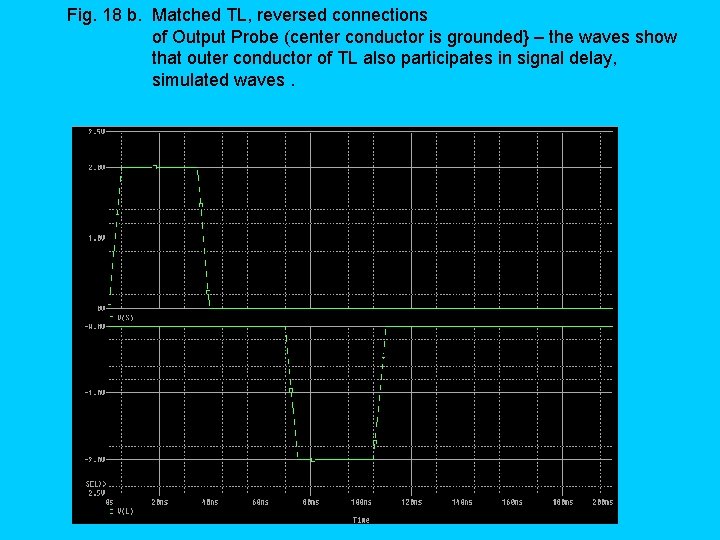

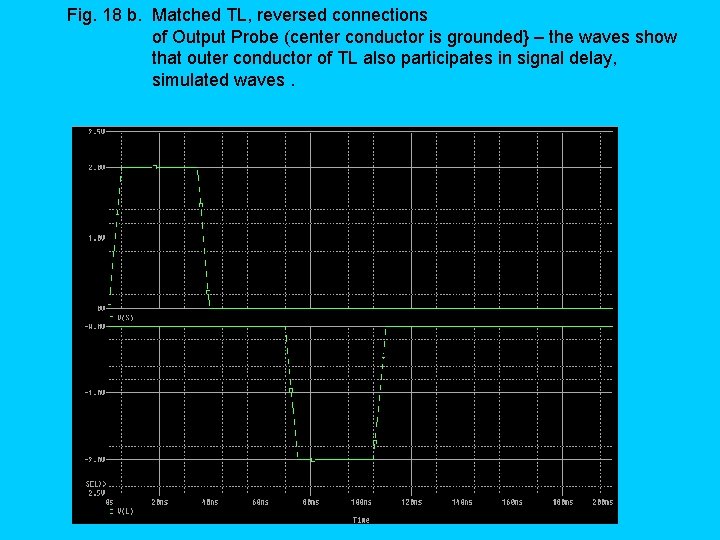

Fig. 18 b. Matched TL, reversed connections of Output Probe (center conductor is grounded} – the waves show that outer conductor of TL also participates in signal delay, simulated waves.

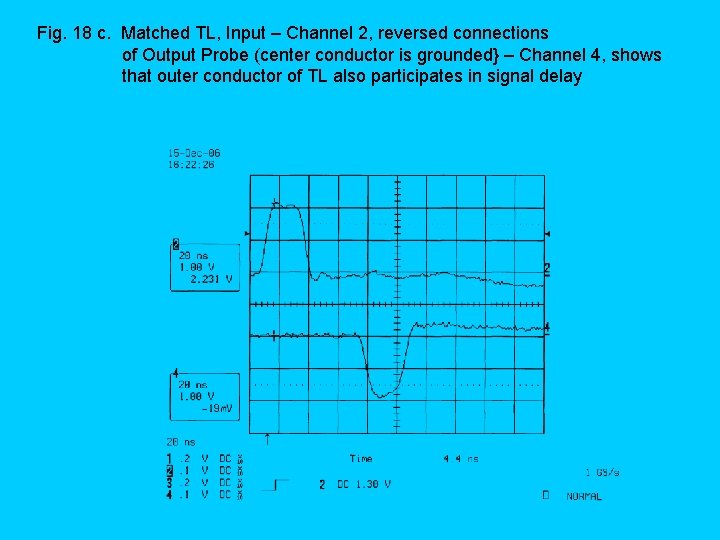

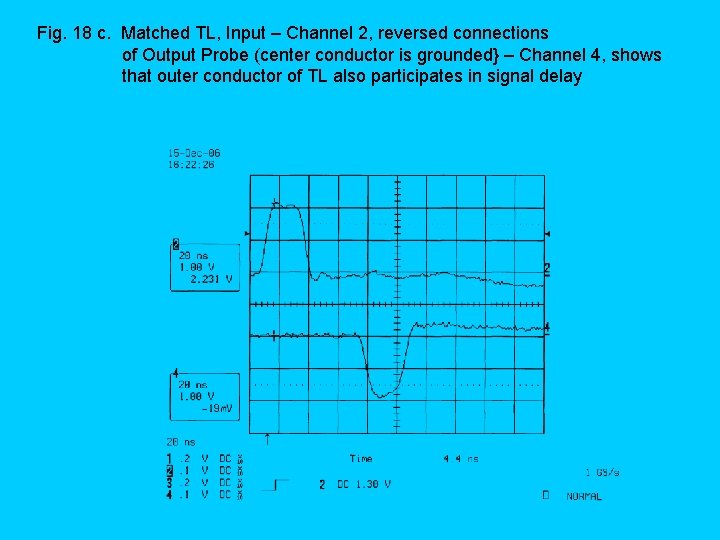

Fig. 18 c. Matched TL, Input – Channel 2, reversed connections of Output Probe (center conductor is grounded} – Channel 4, shows that outer conductor of TL also participates in signal delay

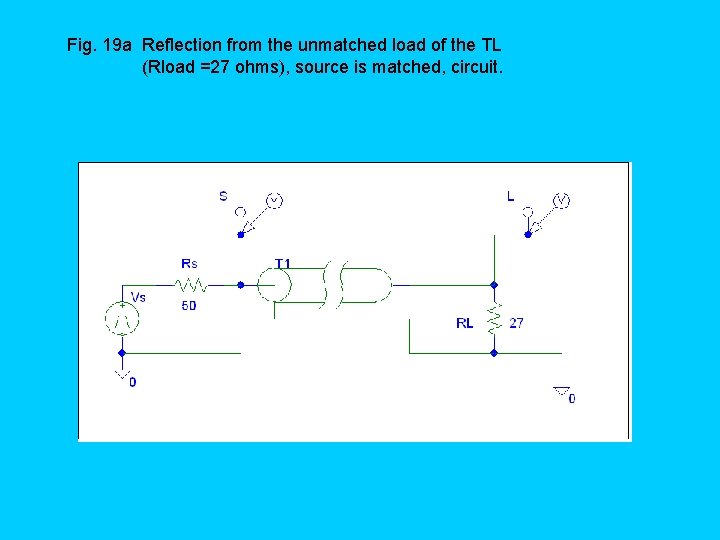

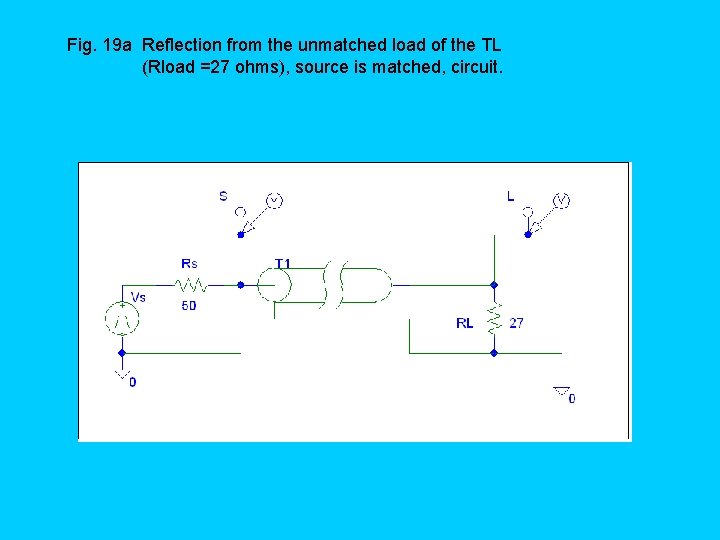

Fig. 19 a Reflection from the unmatched load of the TL (Rload =27 ohms), source is matched, circuit.

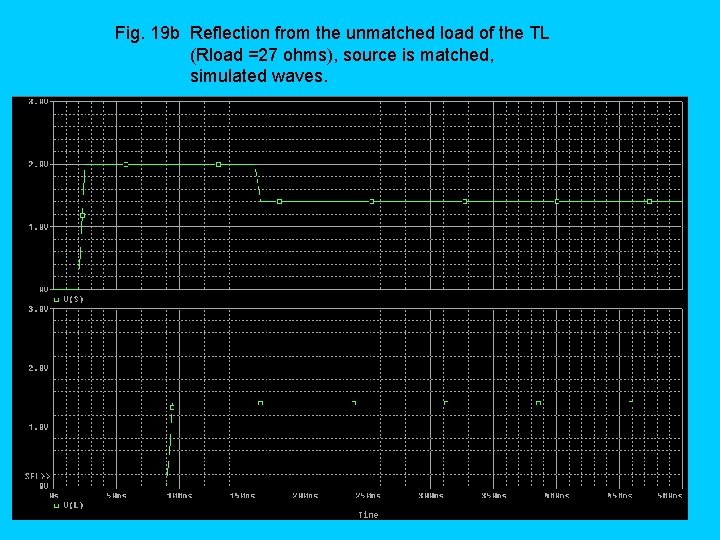

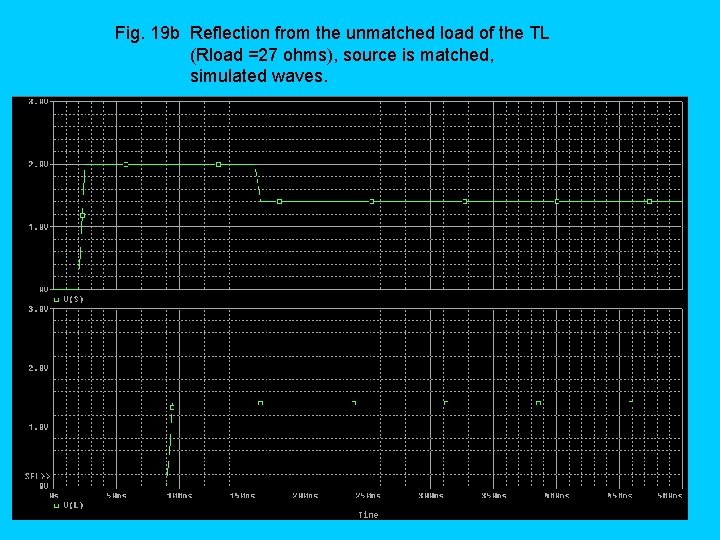

Fig. 19 b Reflection from the unmatched load of the TL (Rload =27 ohms), source is matched, simulated waves.

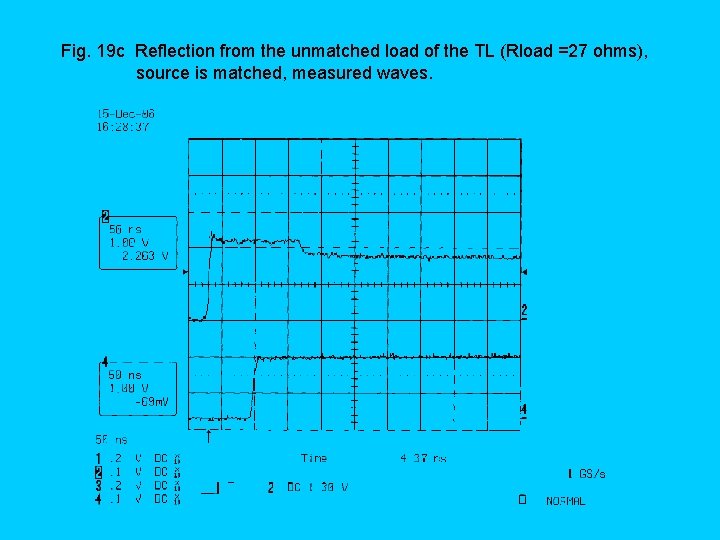

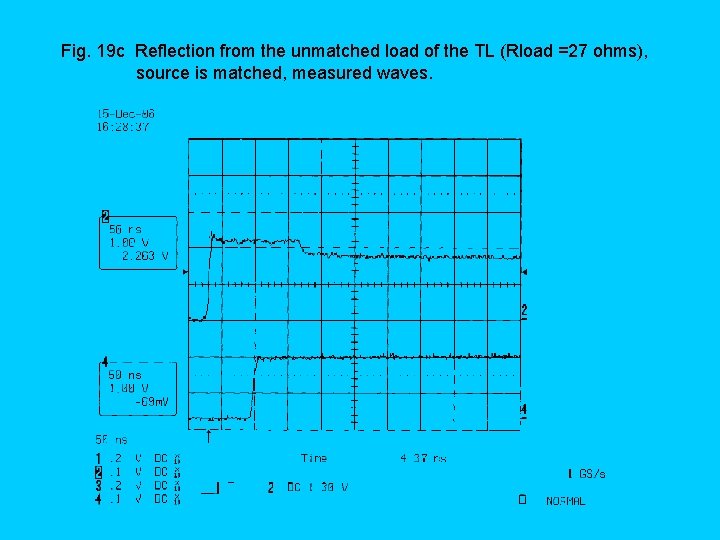

Fig. 19 c Reflection from the unmatched load of the TL (Rload =27 ohms), source is matched, measured waves.

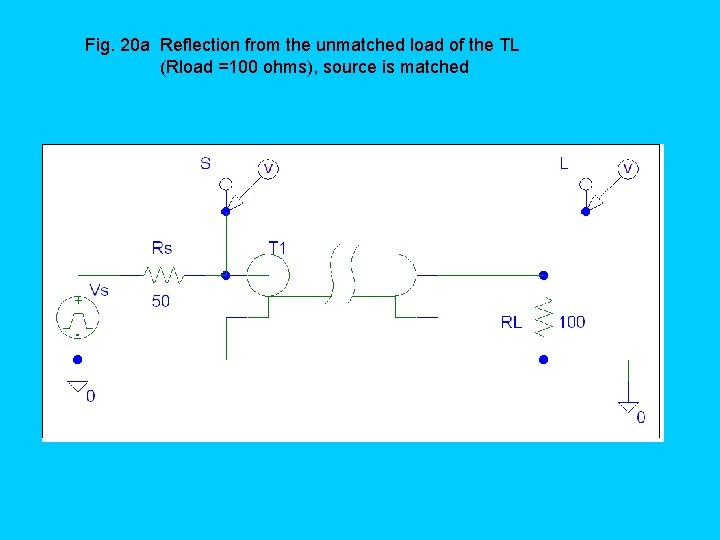

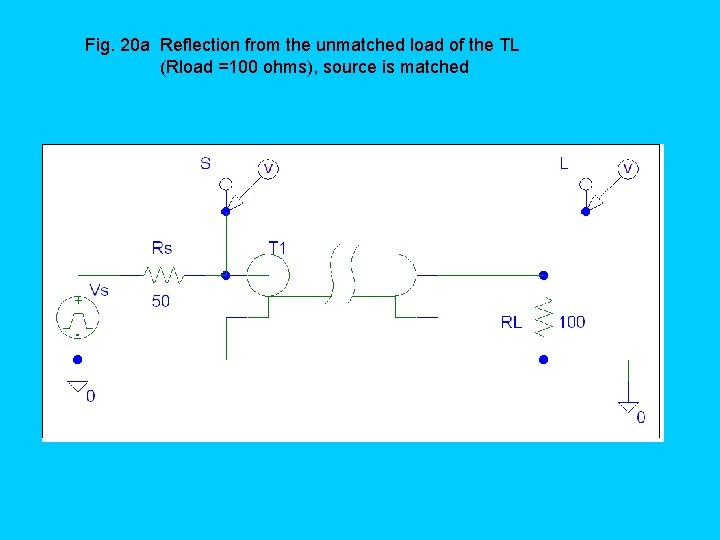

Fig. 20 a Reflection from the unmatched load of the TL (Rload =100 ohms), source is matched

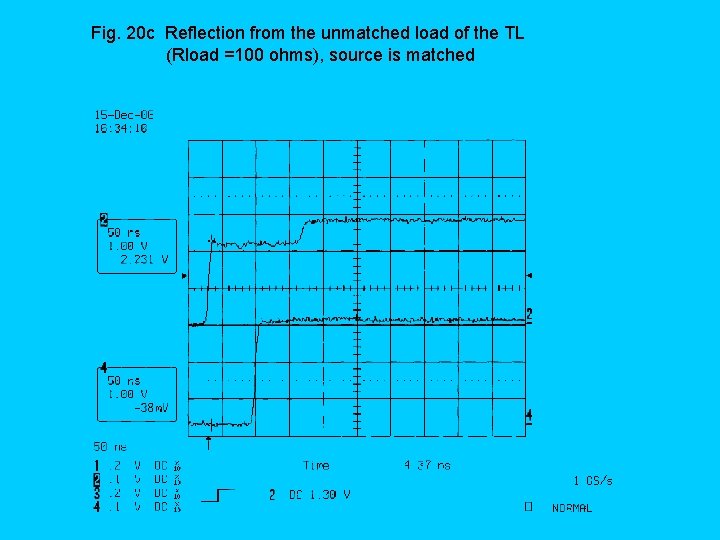

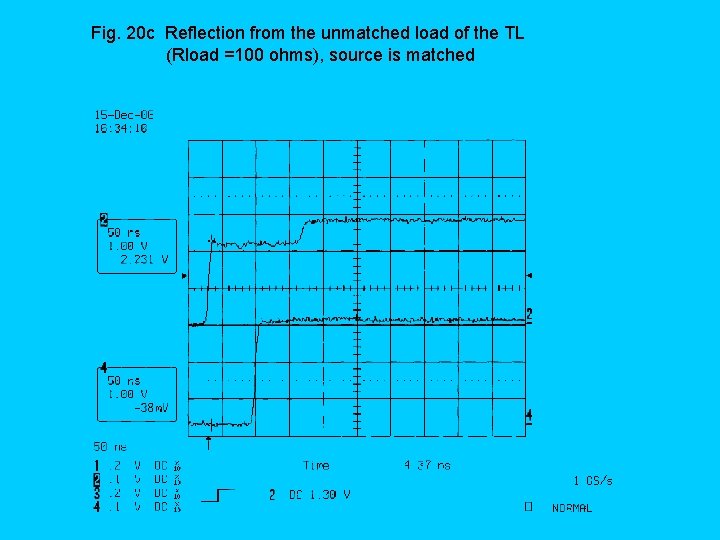

Fig. 20 c Reflection from the unmatched load of the TL (Rload =100 ohms), source is matched

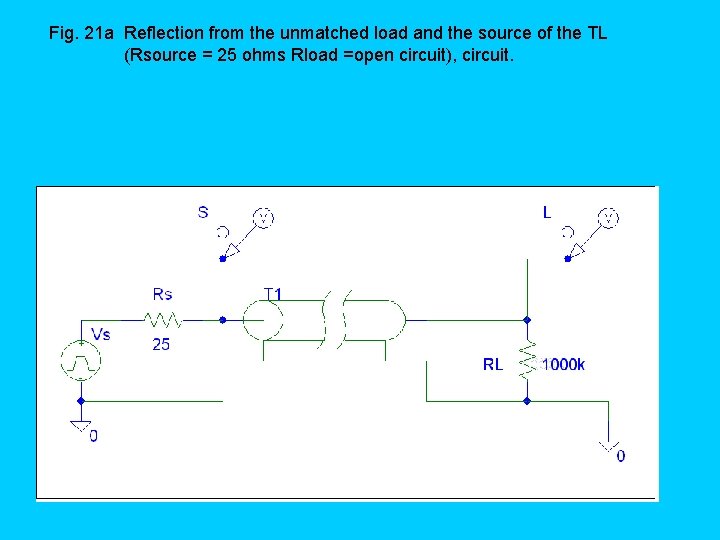

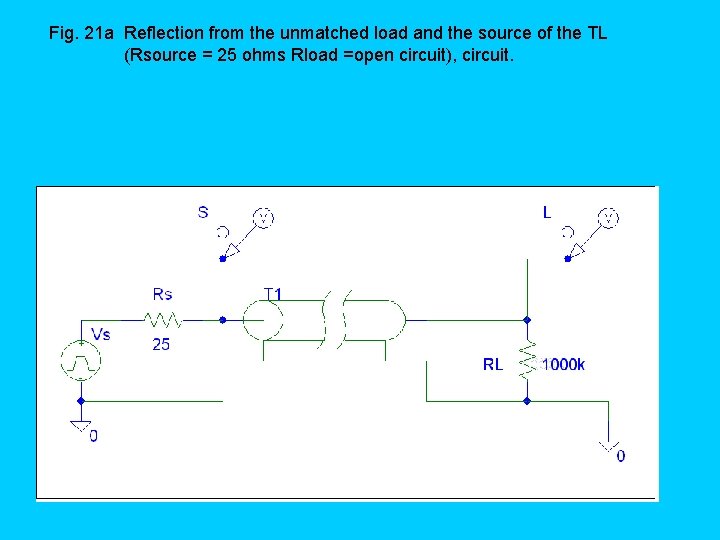

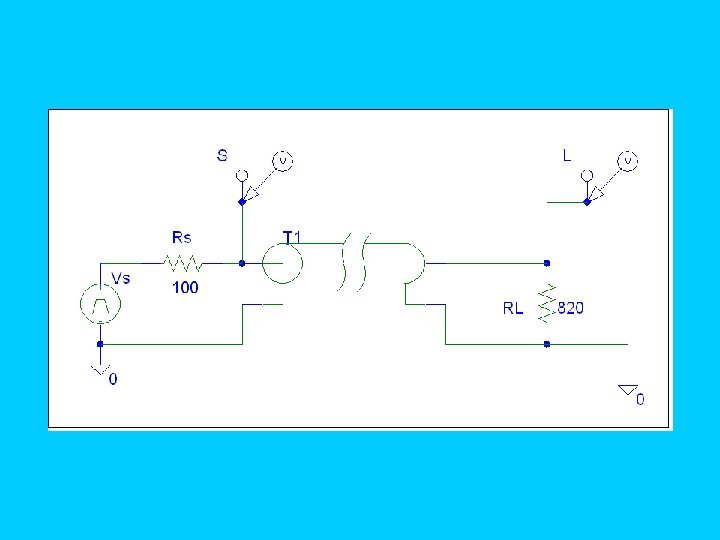

Fig. 21 a Reflection from the unmatched load and the source of the TL (Rsource = 25 ohms Rload =open circuit), circuit.

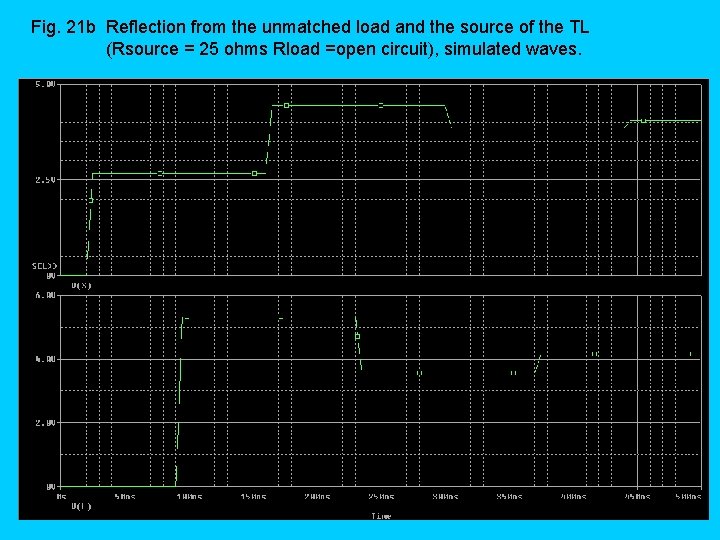

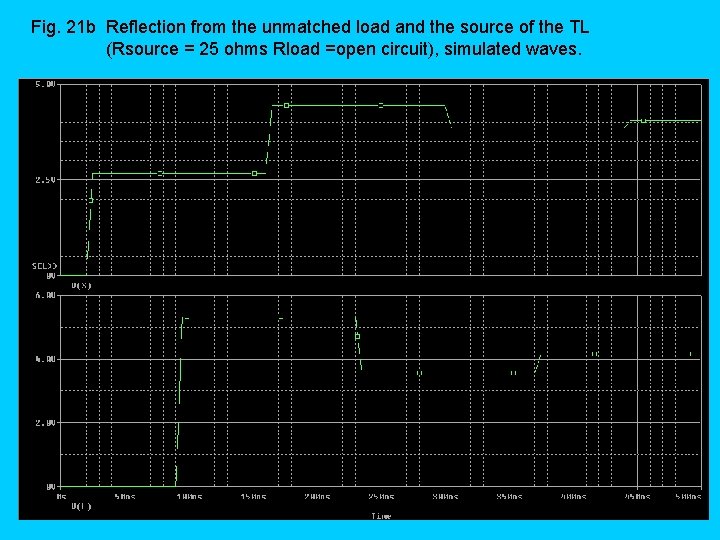

Fig. 21 b Reflection from the unmatched load and the source of the TL (Rsource = 25 ohms Rload =open circuit), simulated waves.

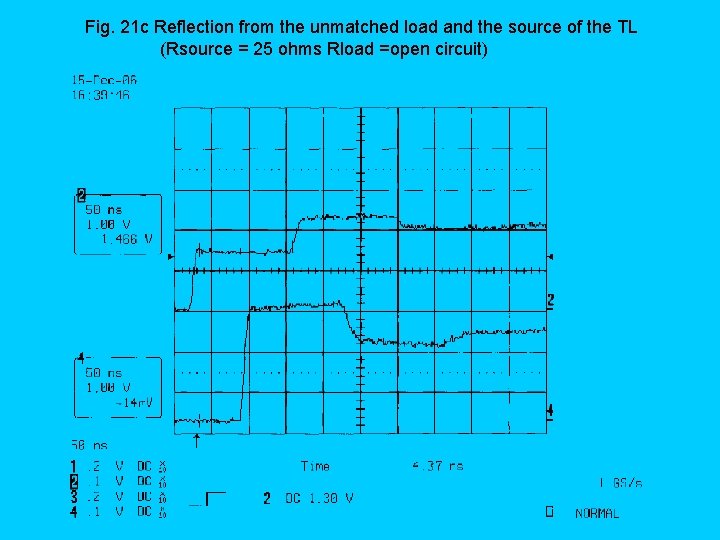

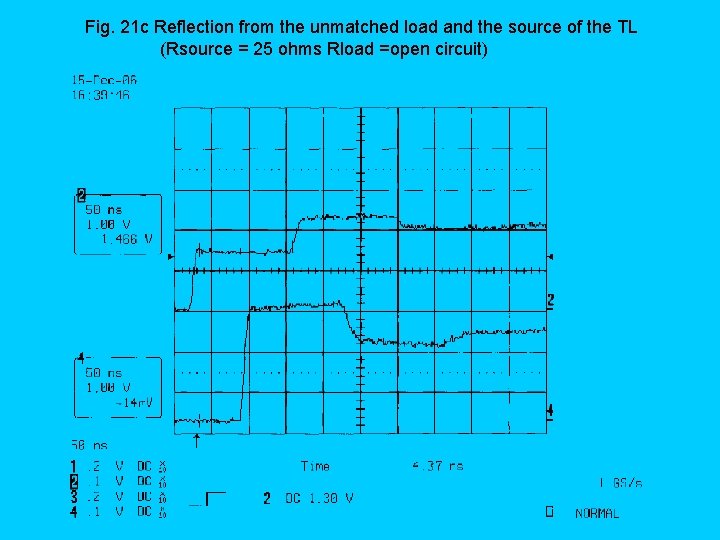

Fig. 21 c Reflection from the unmatched load and the source of the TL (Rsource = 25 ohms Rload =open circuit)

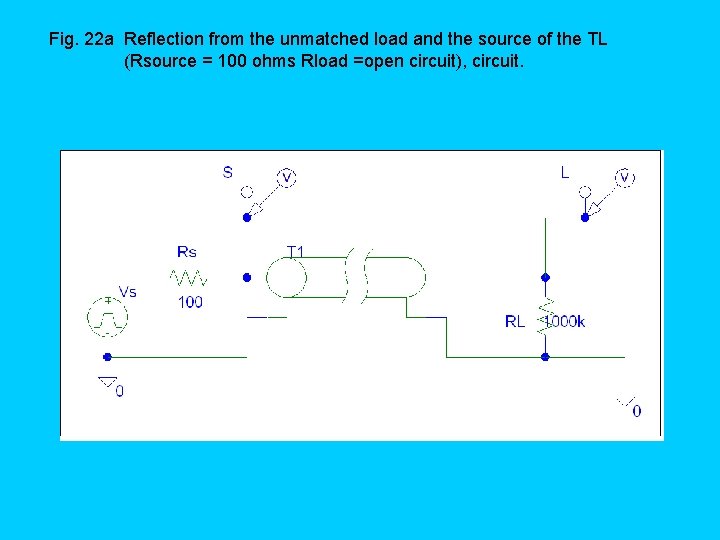

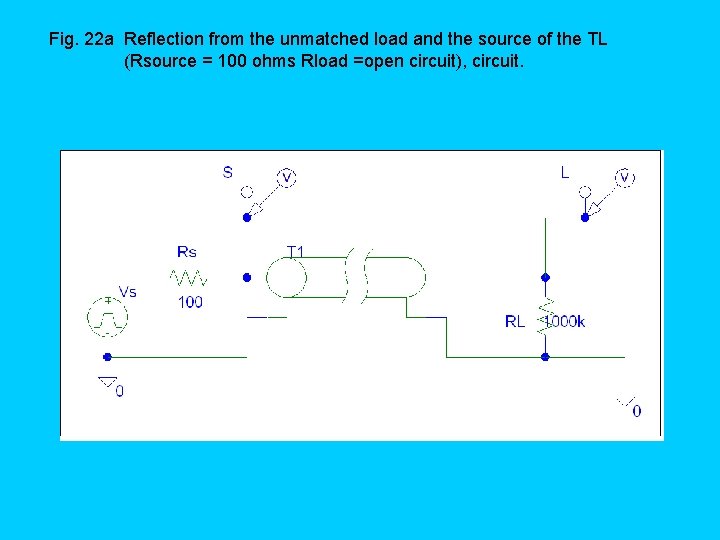

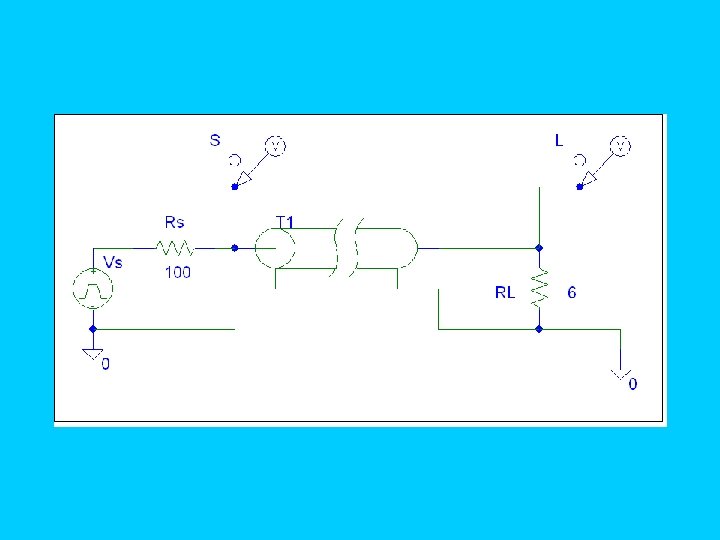

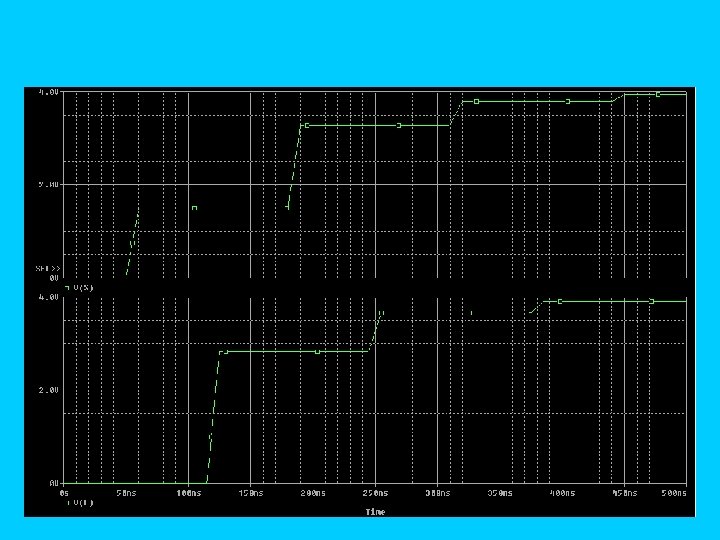

Fig. 22 a Reflection from the unmatched load and the source of the TL (Rsource = 100 ohms Rload =open circuit), circuit.

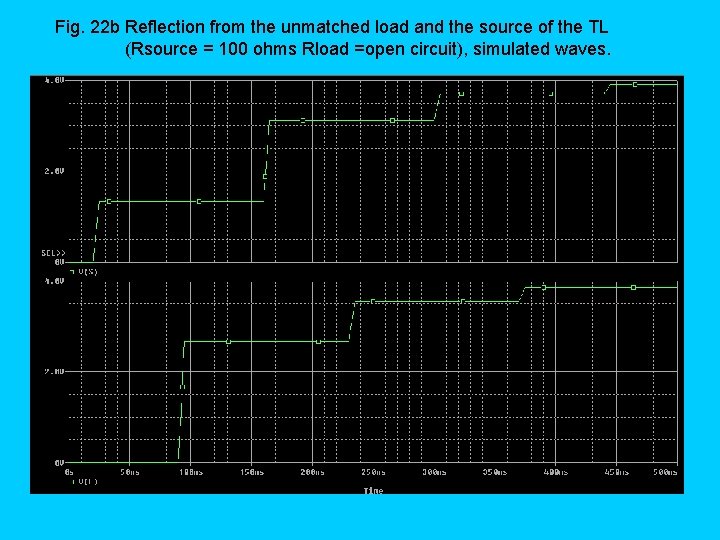

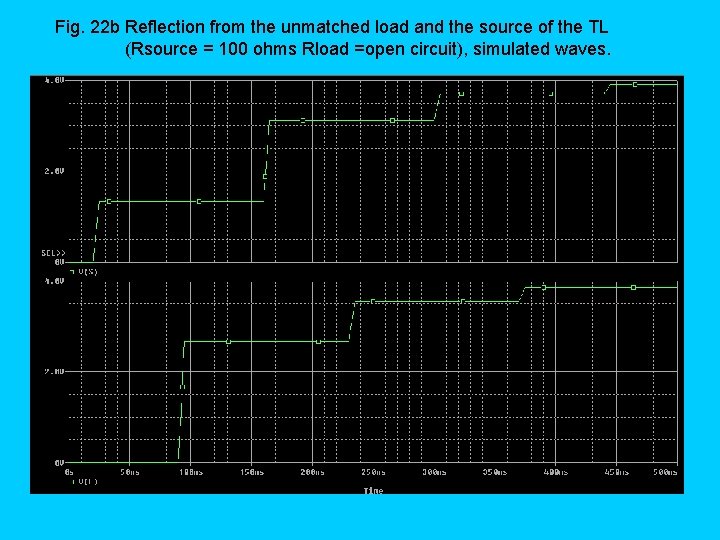

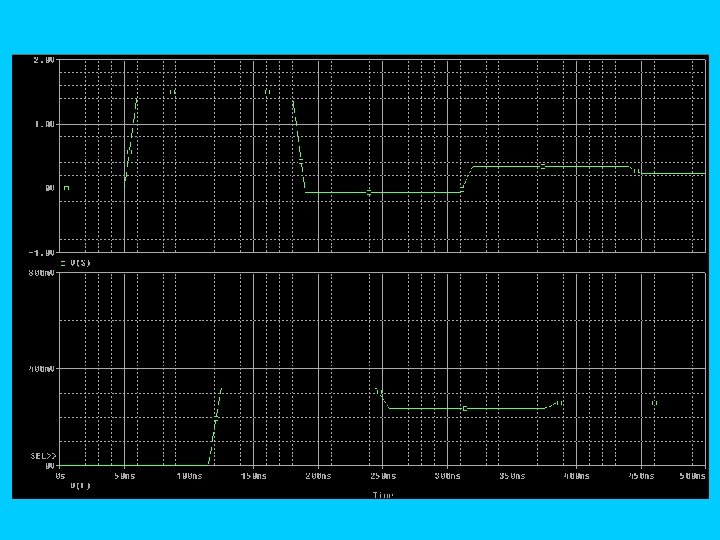

Fig. 22 b Reflection from the unmatched load and the source of the TL (Rsource = 100 ohms Rload =open circuit), simulated waves.

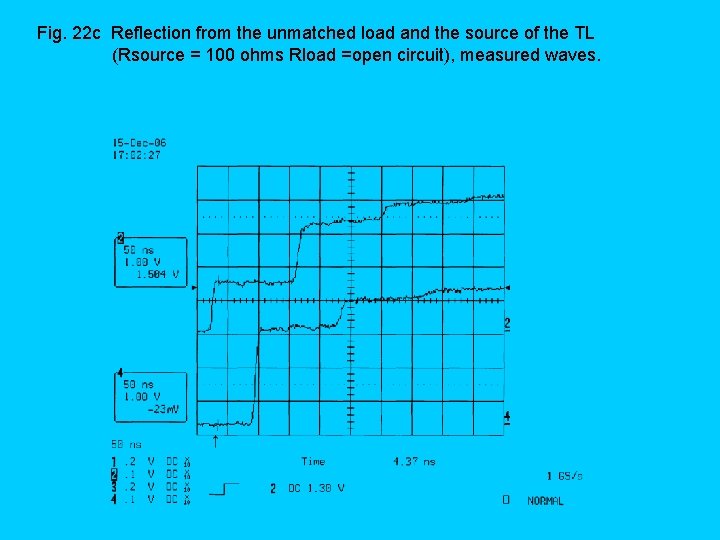

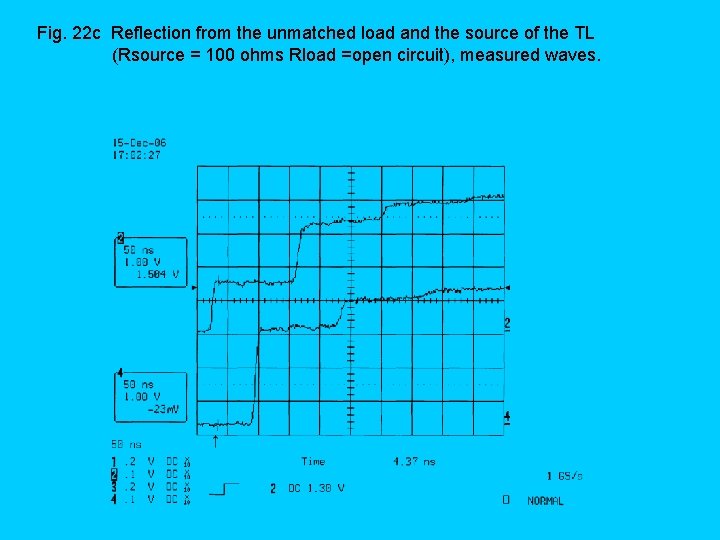

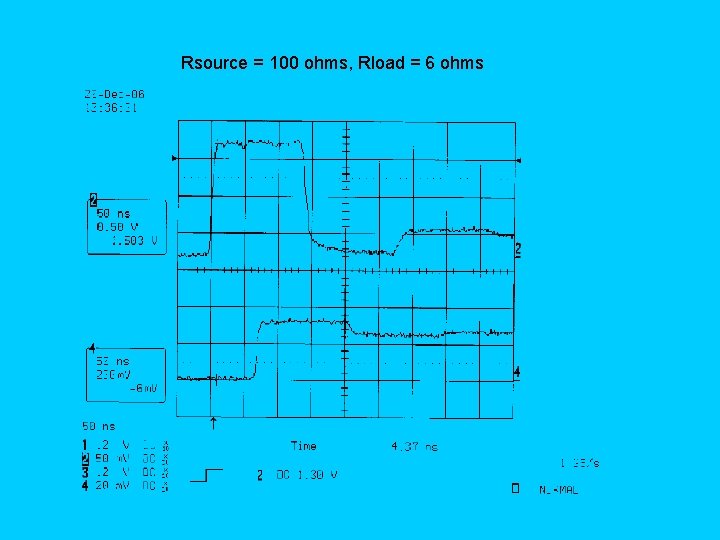

Fig. 22 c Reflection from the unmatched load and the source of the TL (Rsource = 100 ohms Rload =open circuit), measured waves.

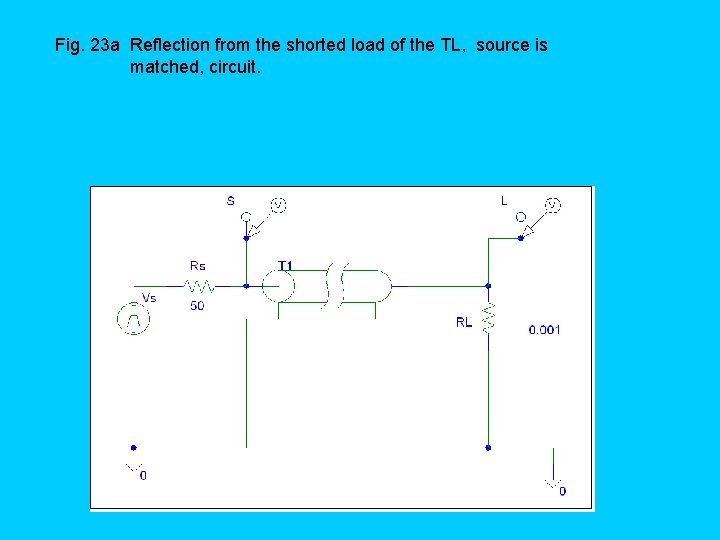

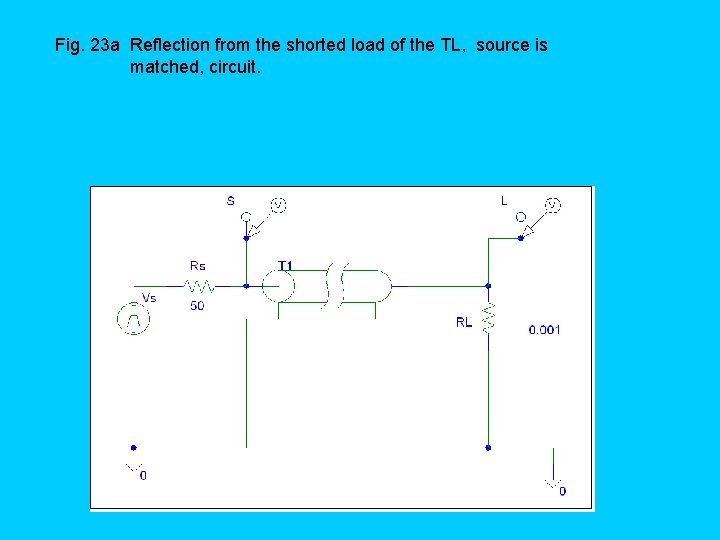

Fig. 23 a Reflection from the shorted load of the TL, source is matched, circuit.

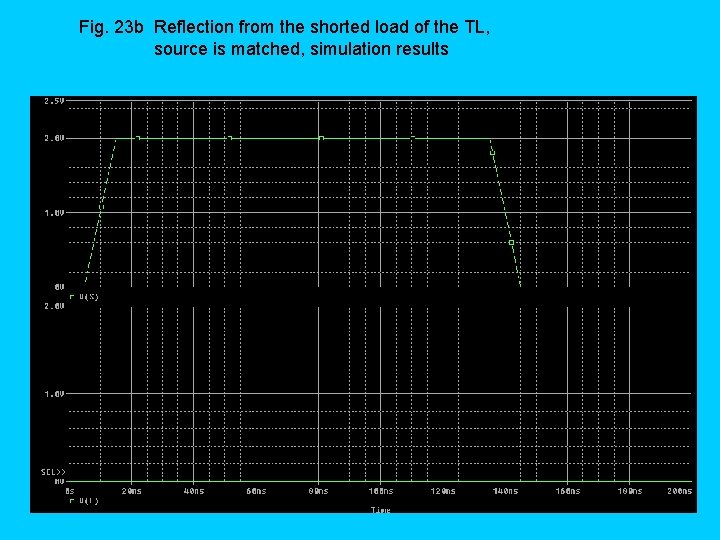

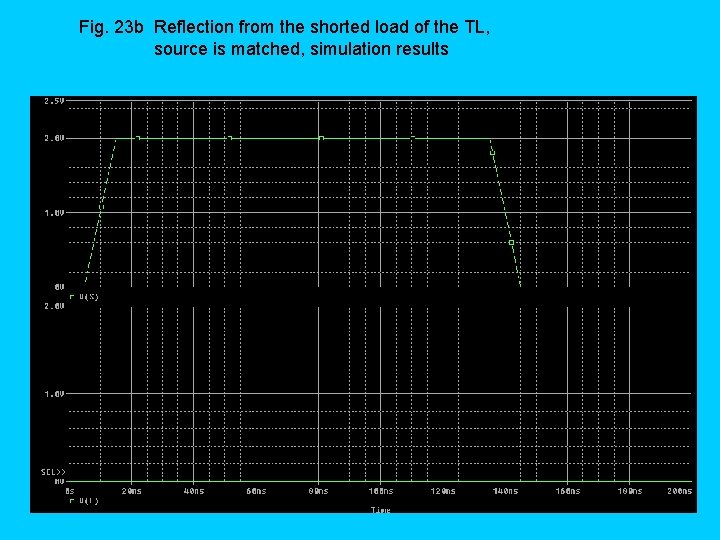

Fig. 23 b Reflection from the shorted load of the TL, source is matched, simulation results

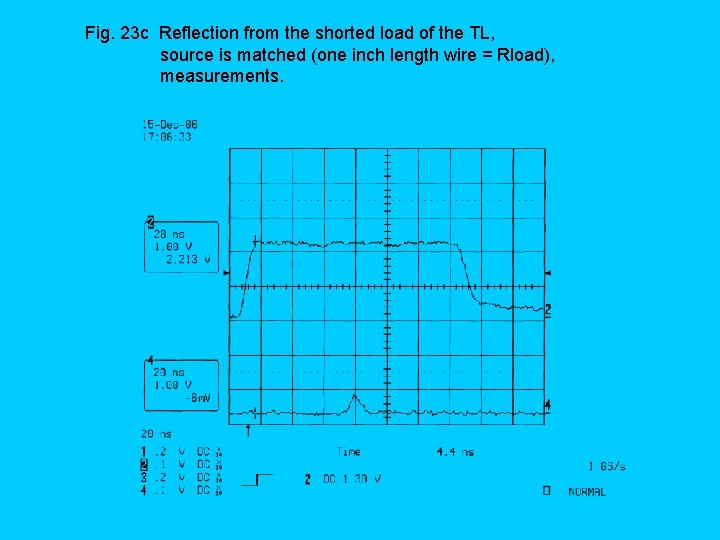

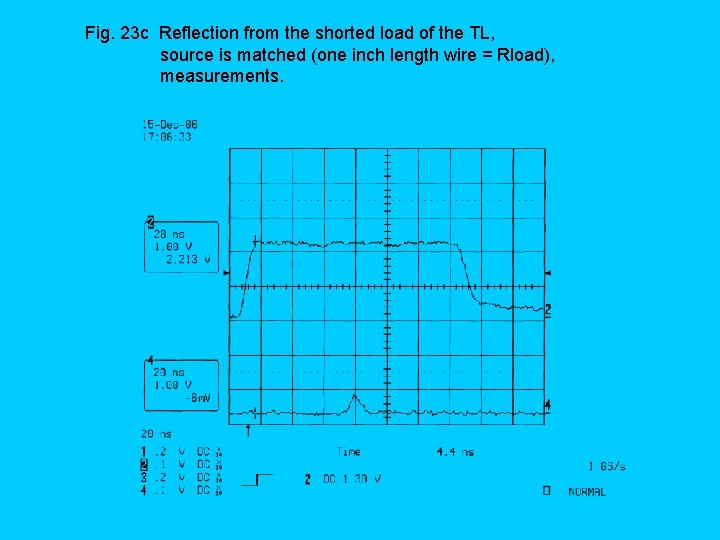

Fig. 23 c Reflection from the shorted load of the TL, source is matched (one inch length wire = Rload), measurements.

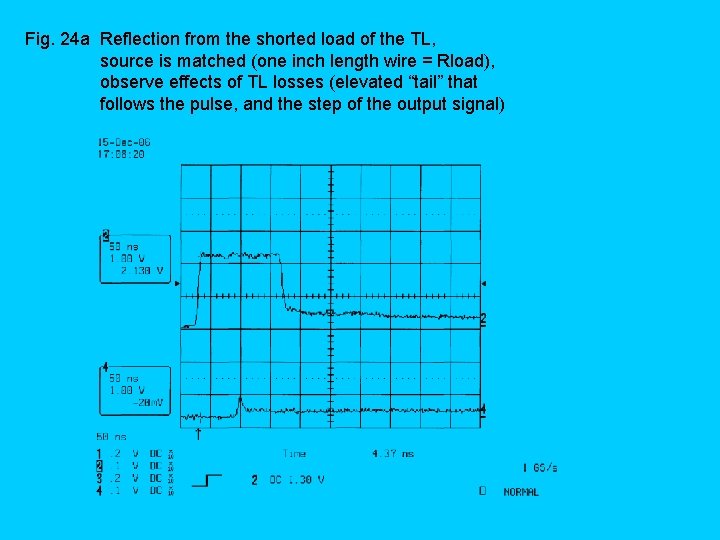

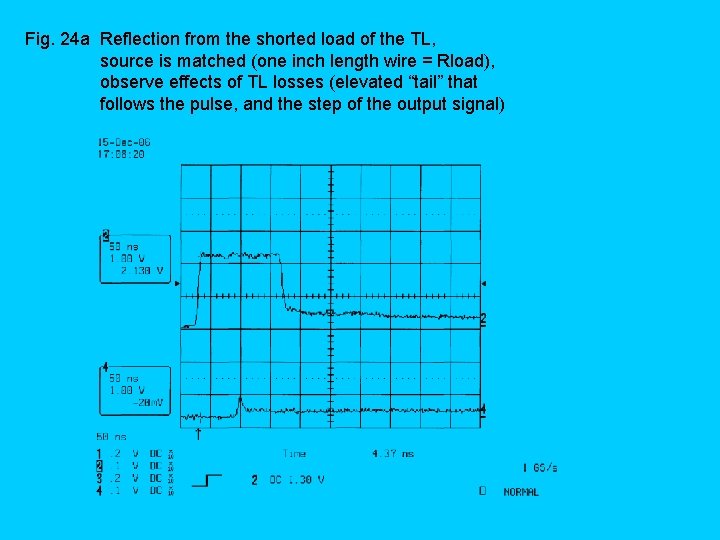

Fig. 24 a Reflection from the shorted load of the TL, source is matched (one inch length wire = Rload), observe effects of TL losses (elevated “tail” that follows the pulse, and the step of the output signal)

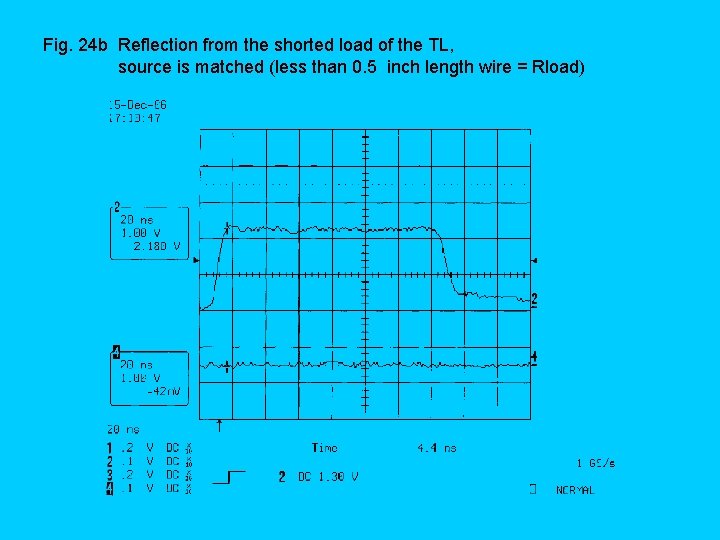

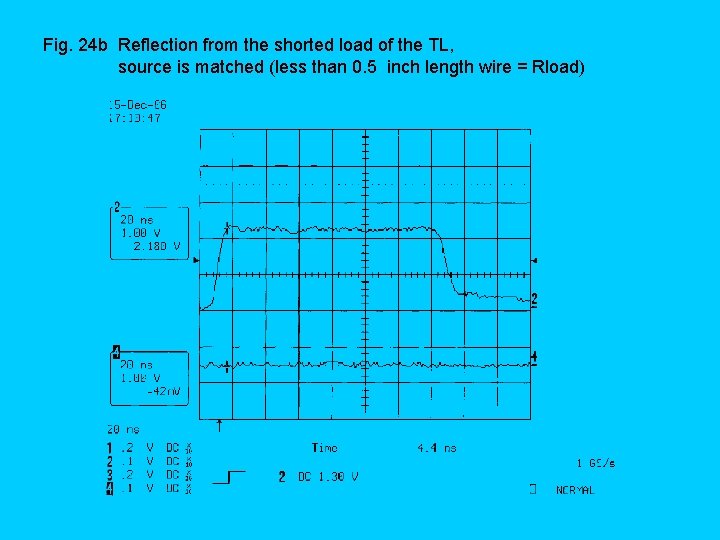

Fig. 24 b Reflection from the shorted load of the TL, source is matched (less than 0. 5 inch length wire = Rload)

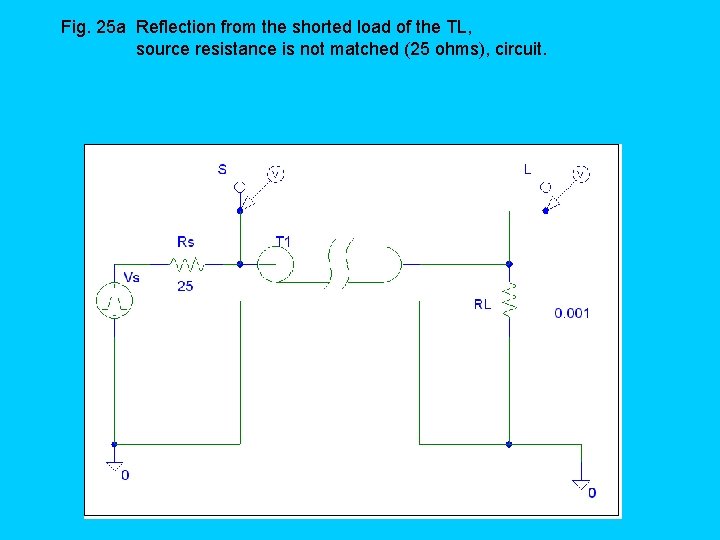

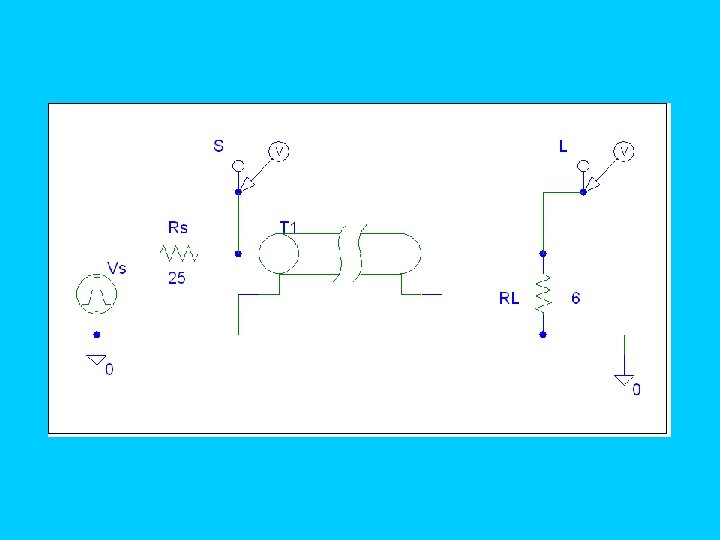

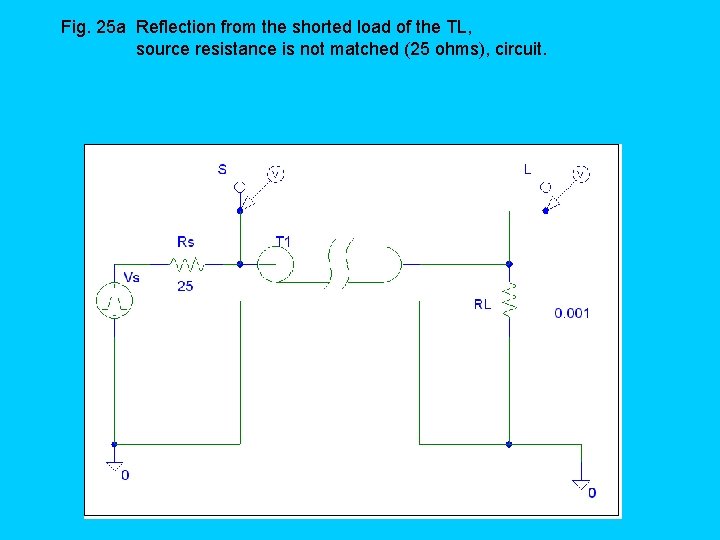

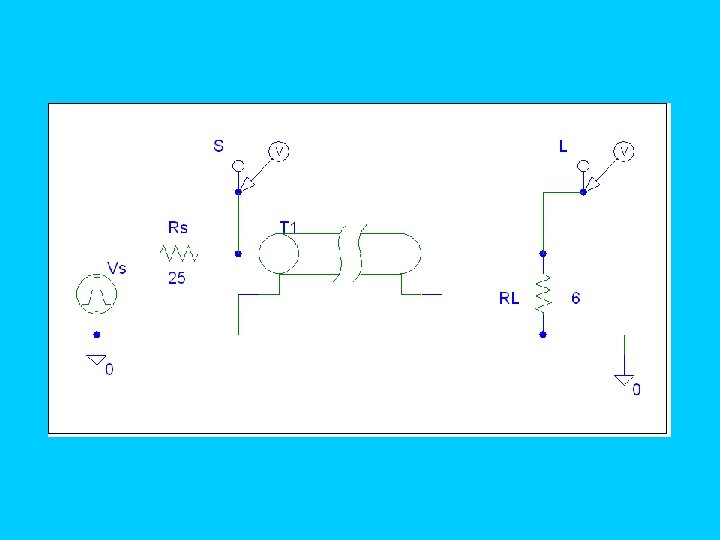

Fig. 25 a Reflection from the shorted load of the TL, source resistance is not matched (25 ohms), circuit.

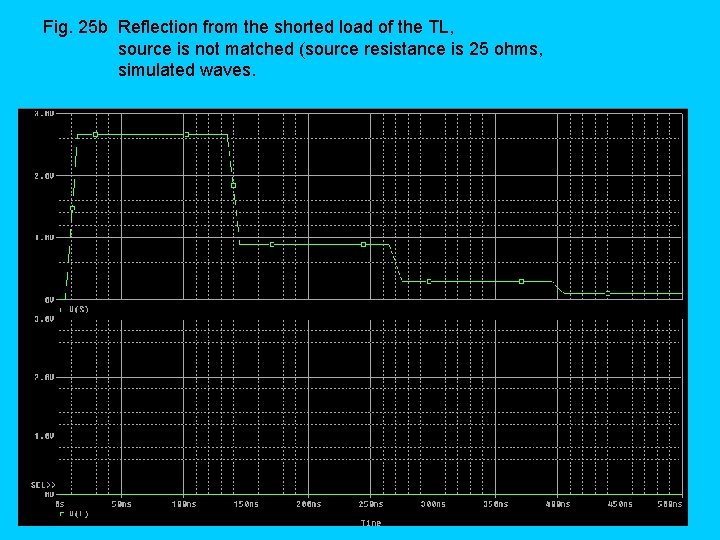

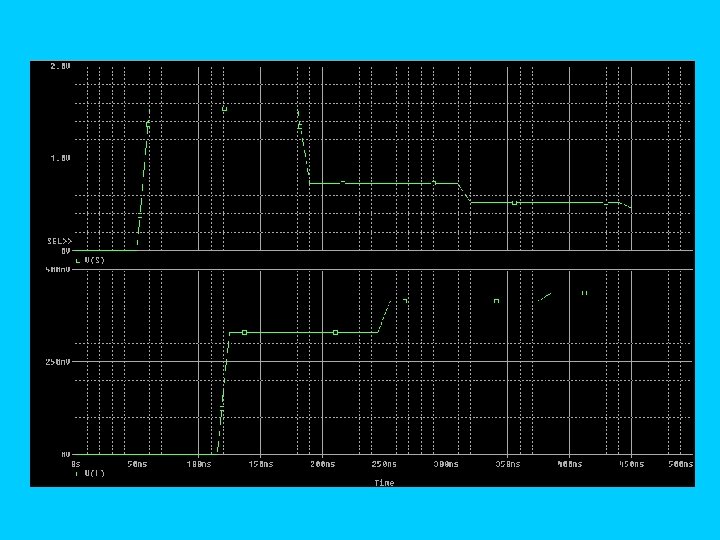

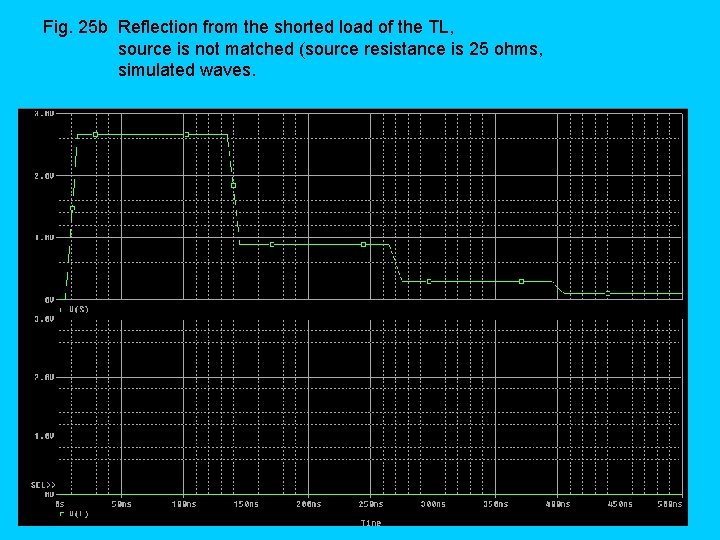

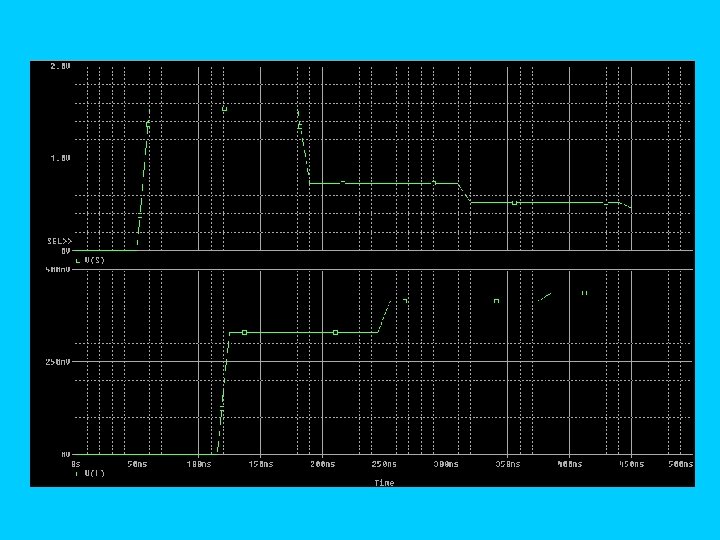

Fig. 25 b Reflection from the shorted load of the TL, source is not matched (source resistance is 25 ohms, simulated waves.

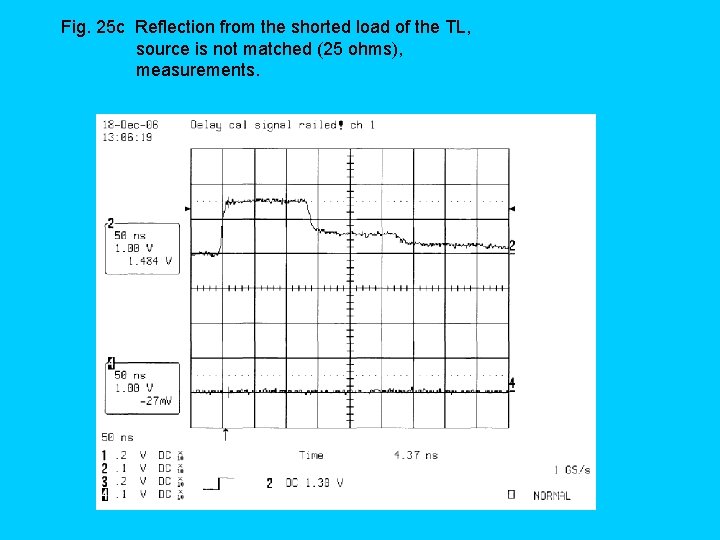

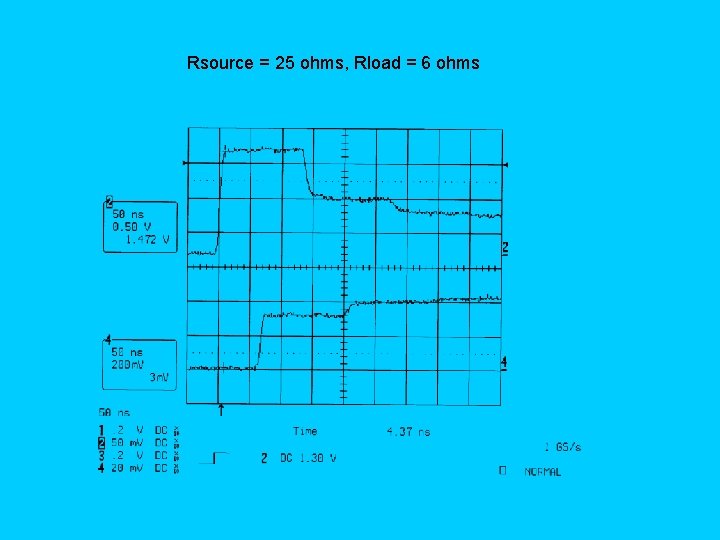

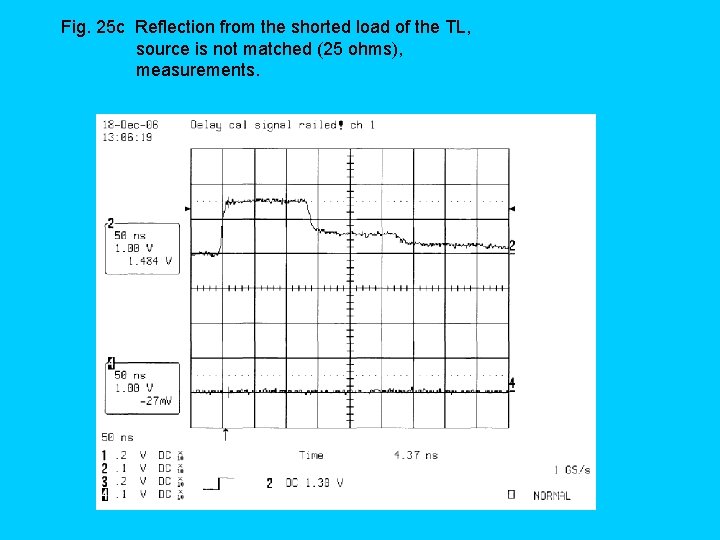

Fig. 25 c Reflection from the shorted load of the TL, source is not matched (25 ohms), measurements.

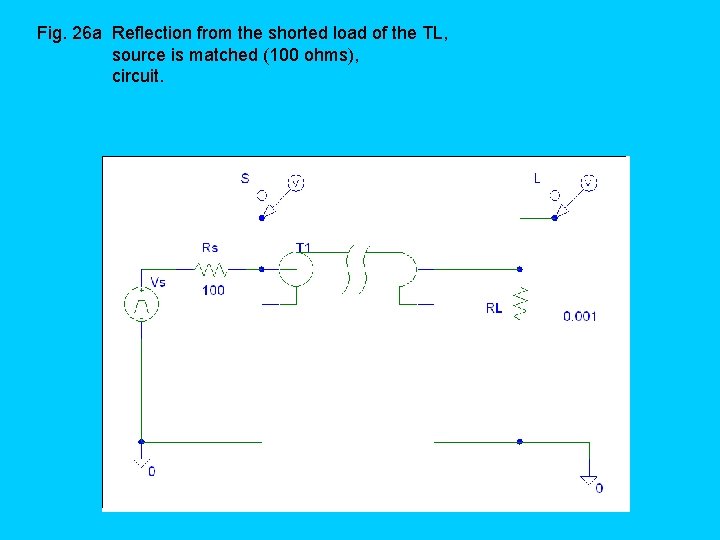

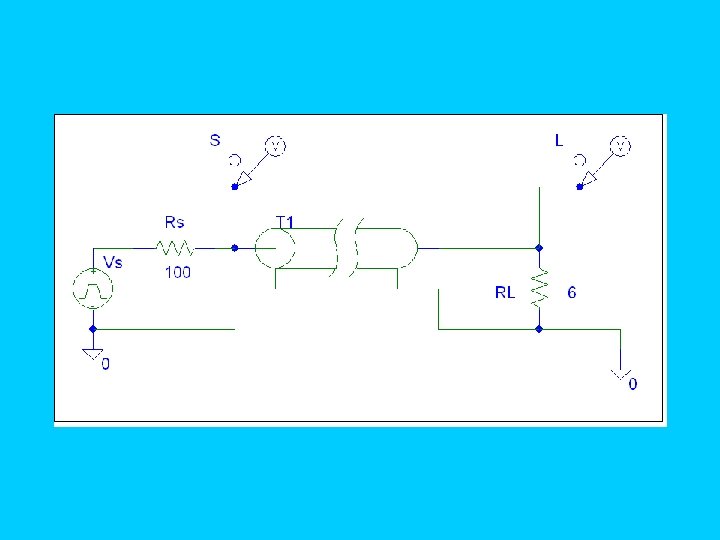

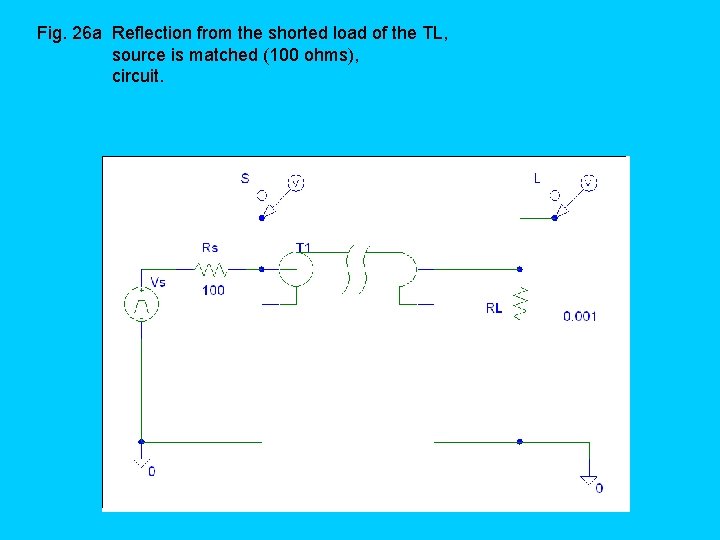

Fig. 26 a Reflection from the shorted load of the TL, source is matched (100 ohms), circuit.

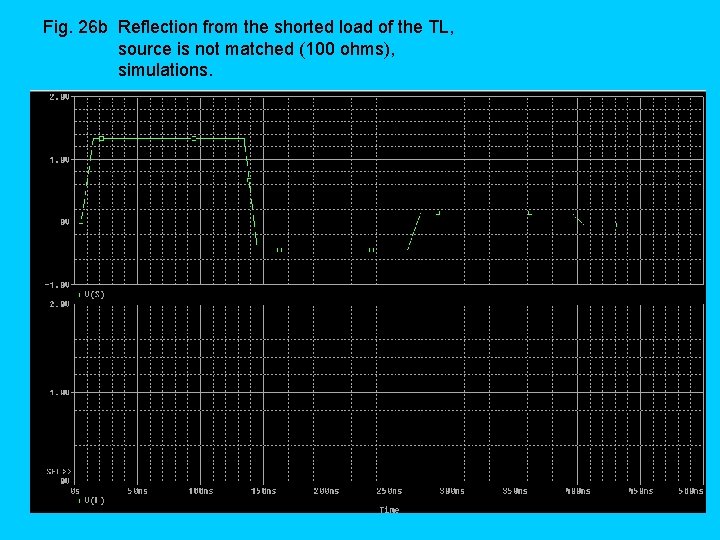

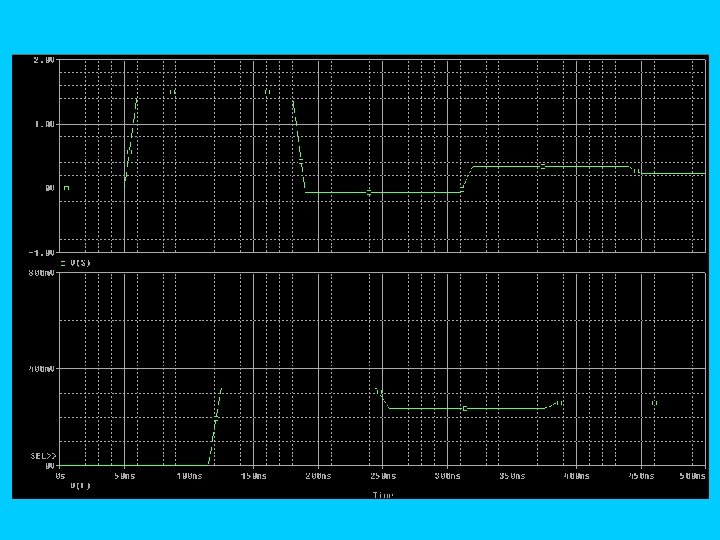

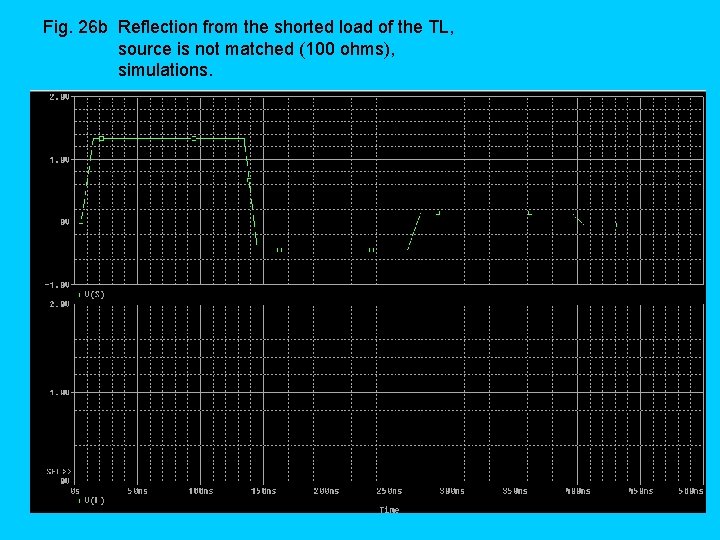

Fig. 26 b Reflection from the shorted load of the TL, source is not matched (100 ohms), simulations.

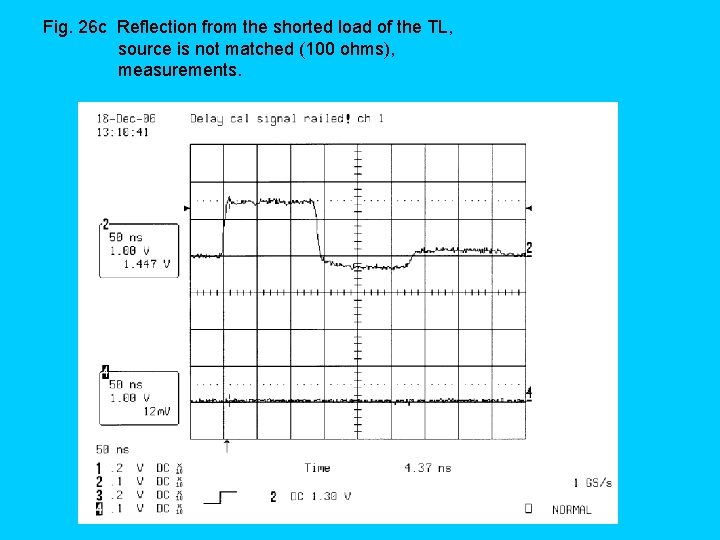

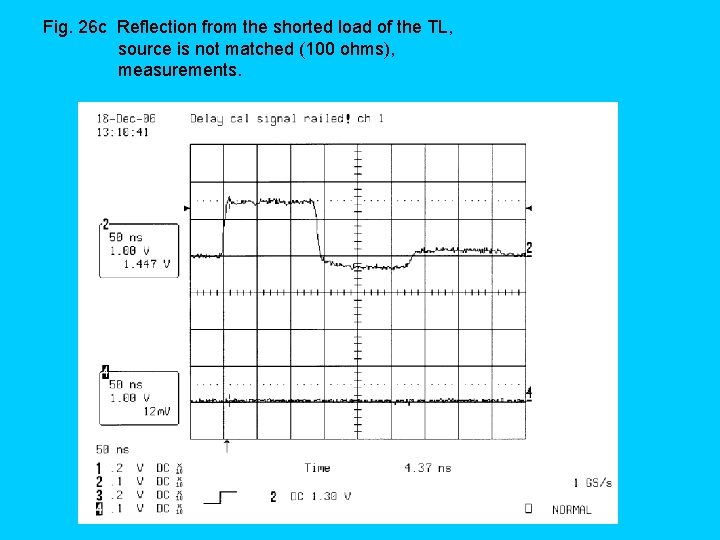

Fig. 26 c Reflection from the shorted load of the TL, source is not matched (100 ohms), measurements.

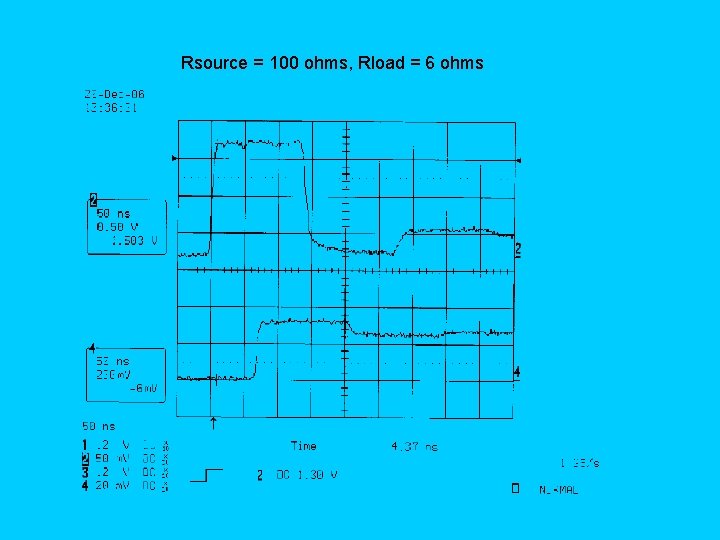

Rsource = 100 ohms, Rload = 6 ohms

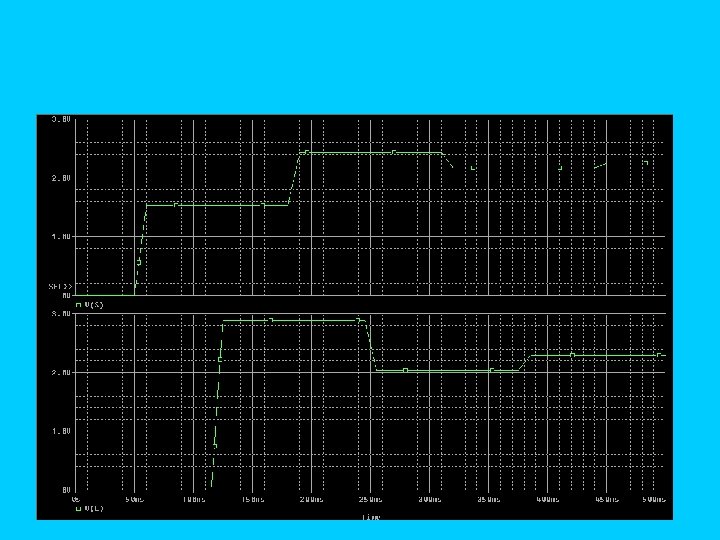

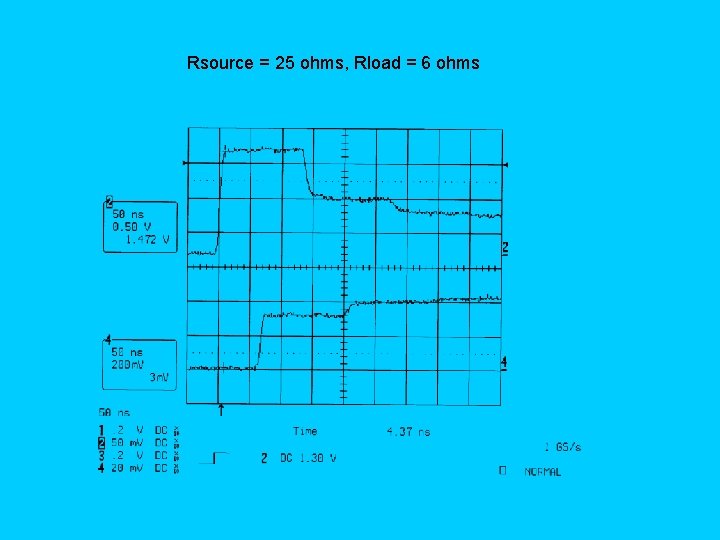

Rsource = 25 ohms, Rload = 6 ohms

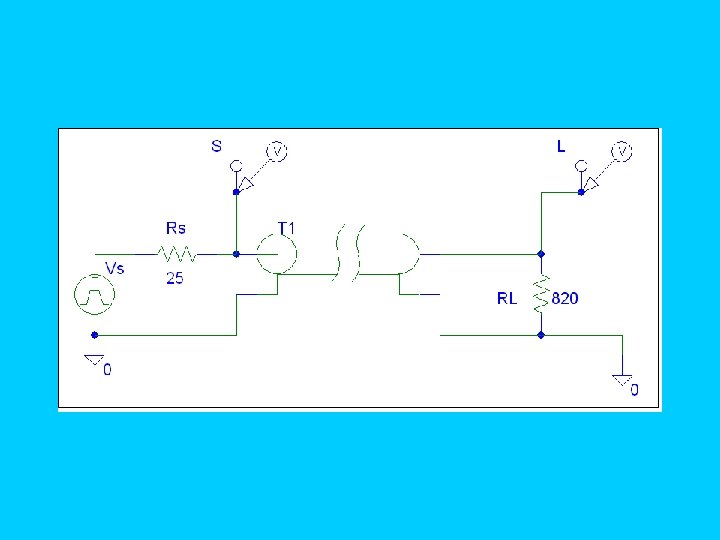

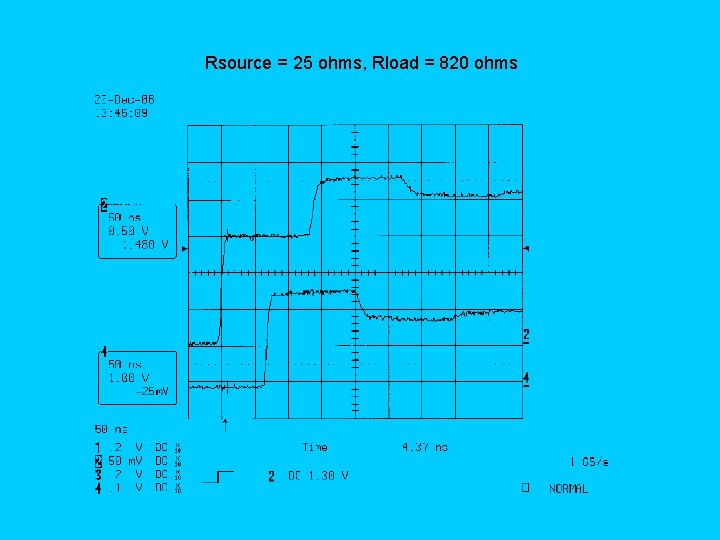

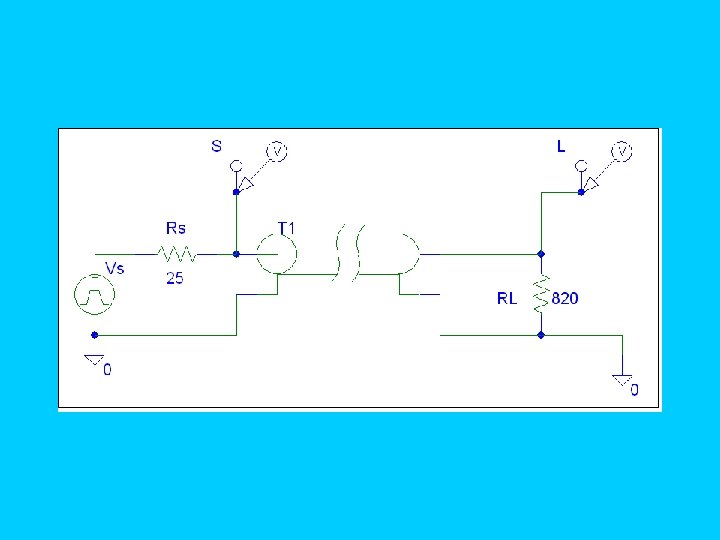

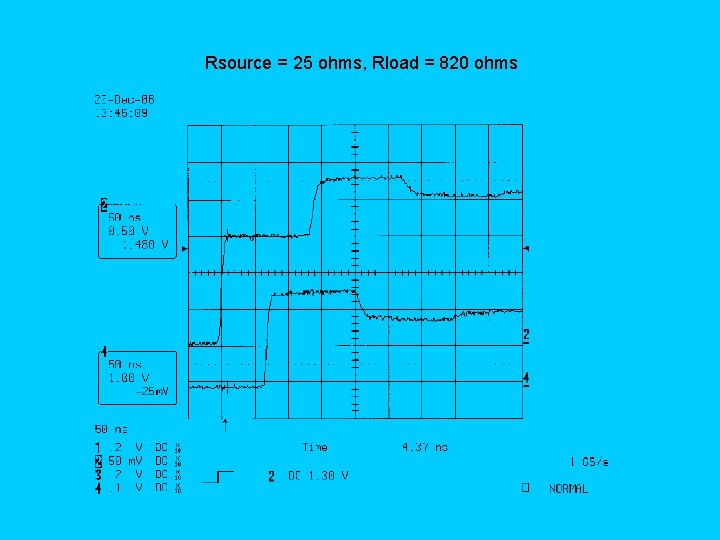

Rsource = 25 ohms, Rload = 820 ohms

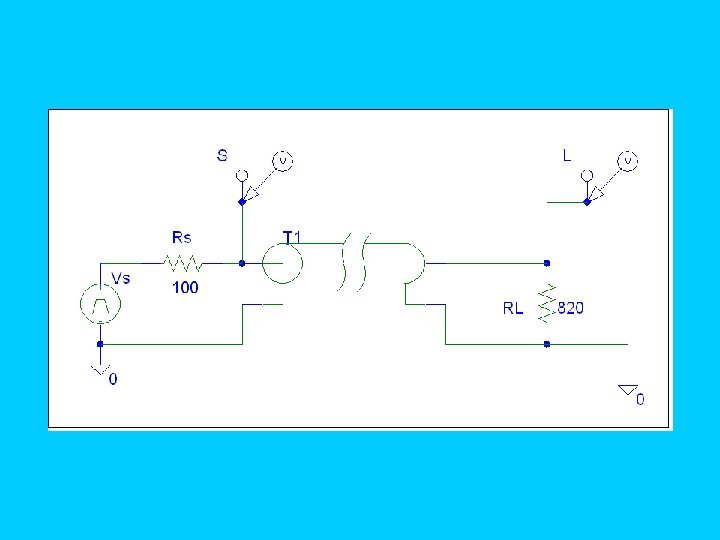

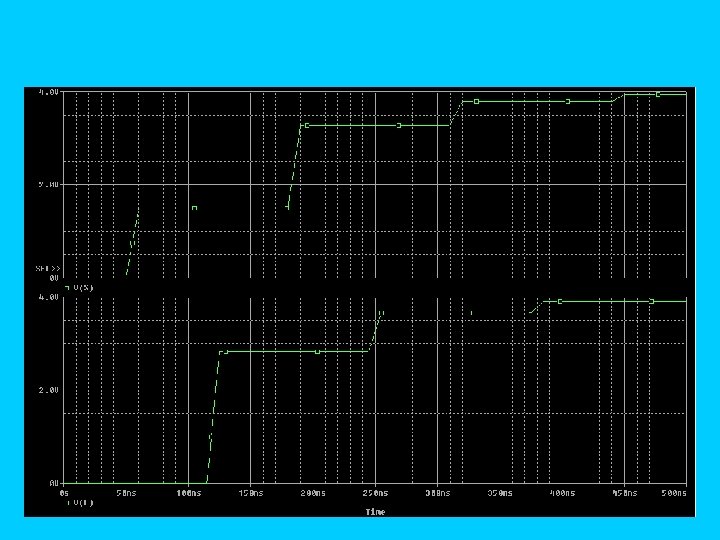

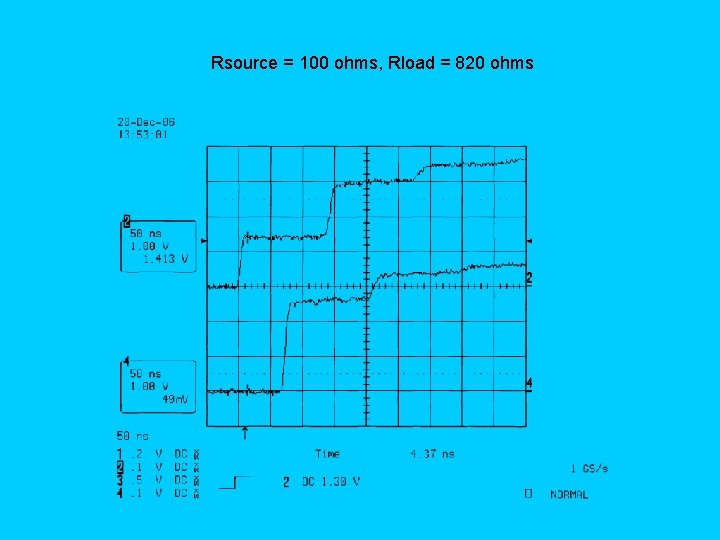

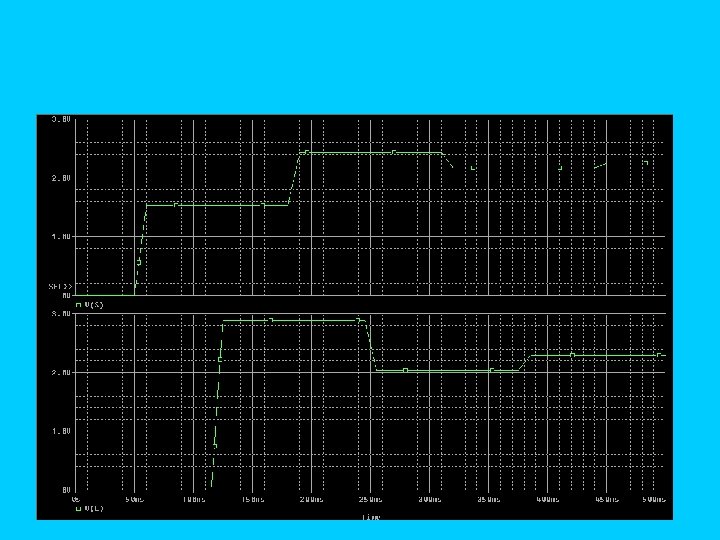

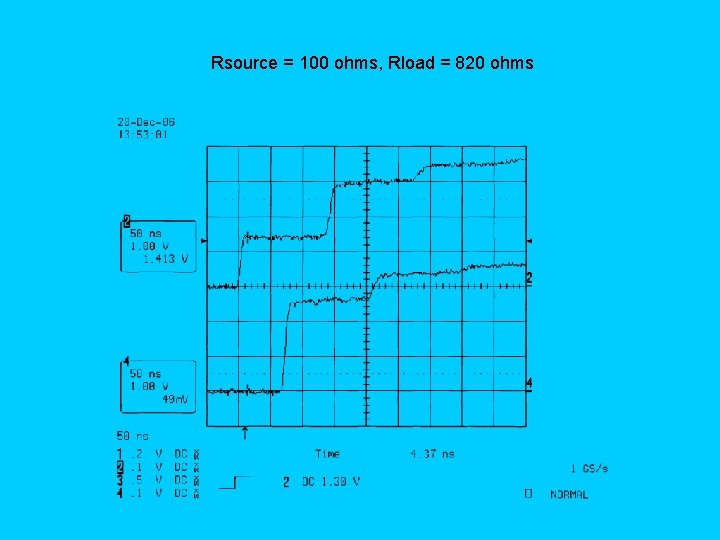

Rsource = 100 ohms, Rload = 820 ohms

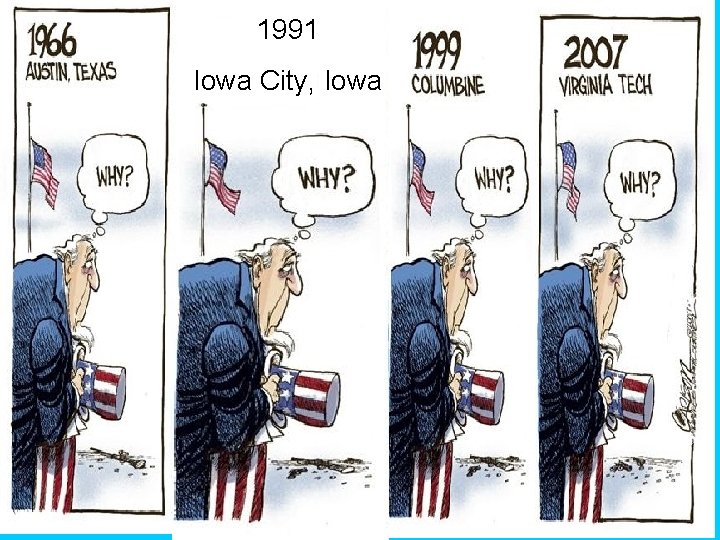

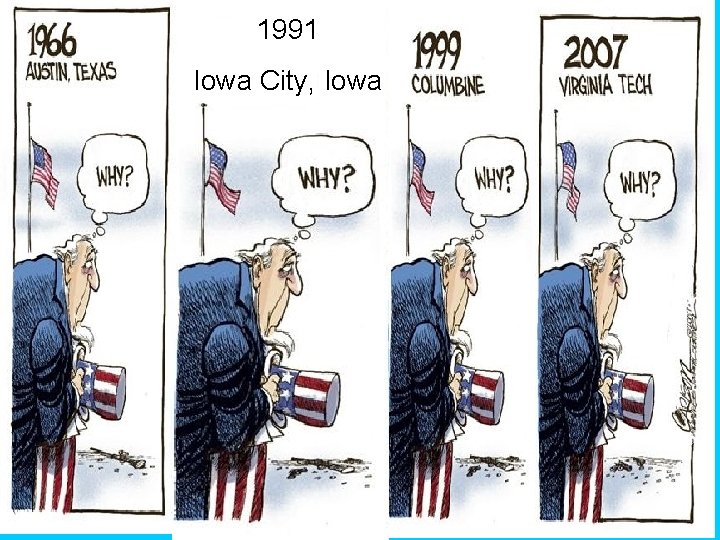

1991 Iowa City, Iowa

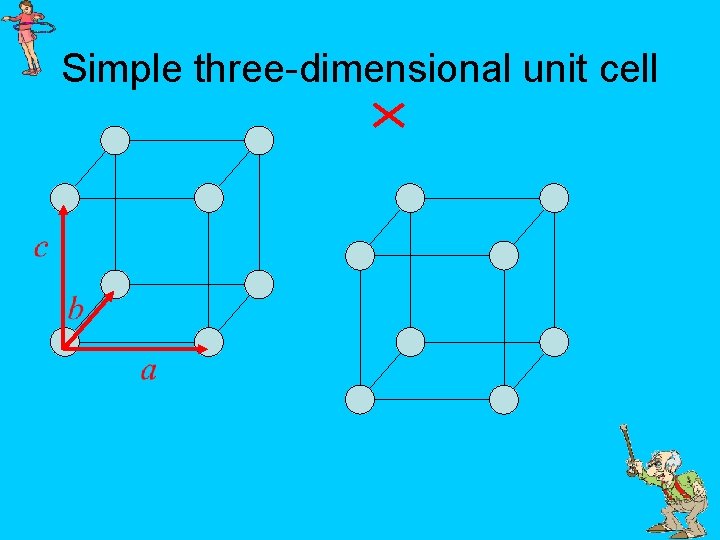

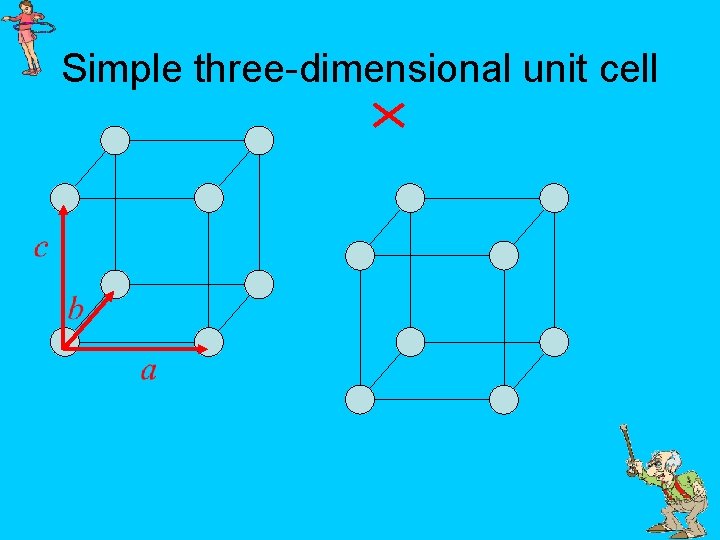

Simple three-dimensional unit cell