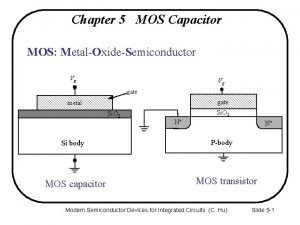

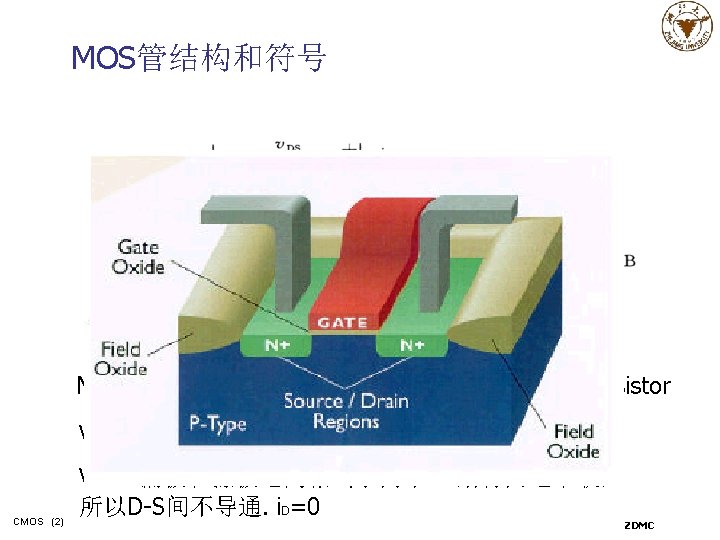

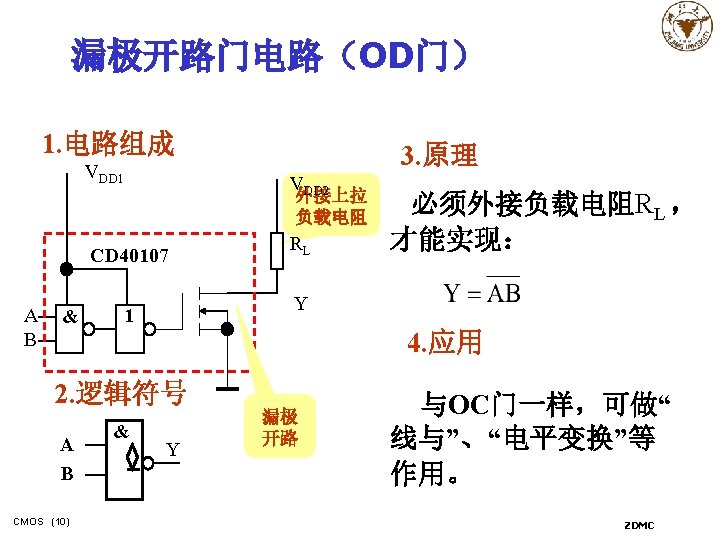

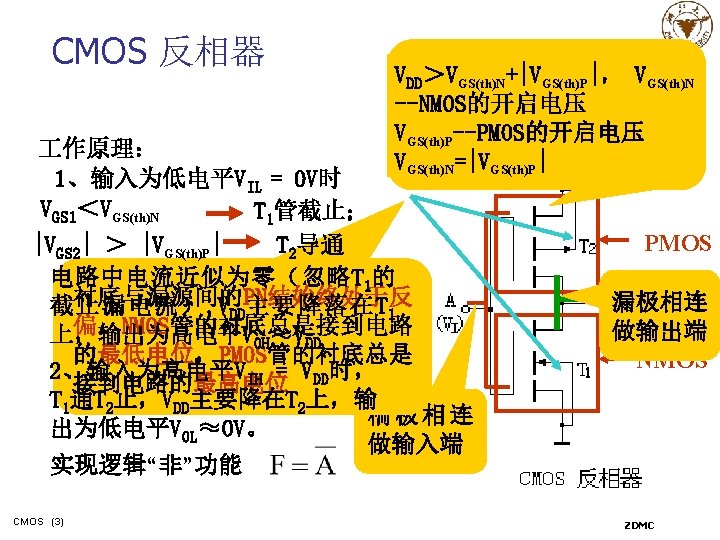

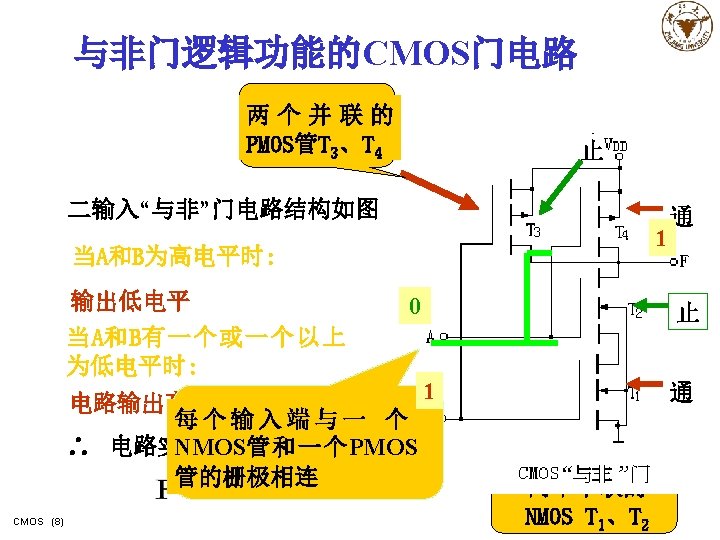

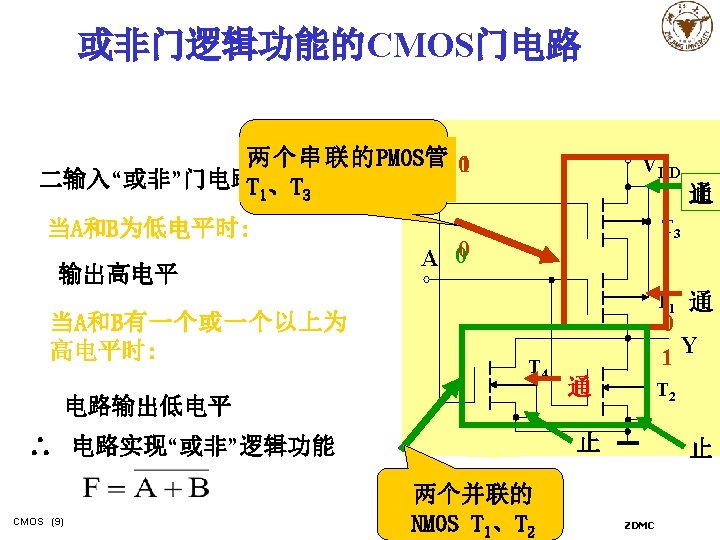

MOS MOS MetalOxideSemiconductor FieldEffect Transistor VGSthMOS CMOS 2

- Slides: 17

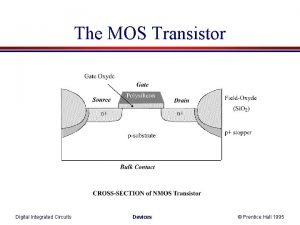

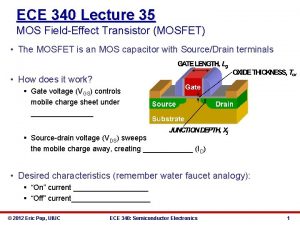

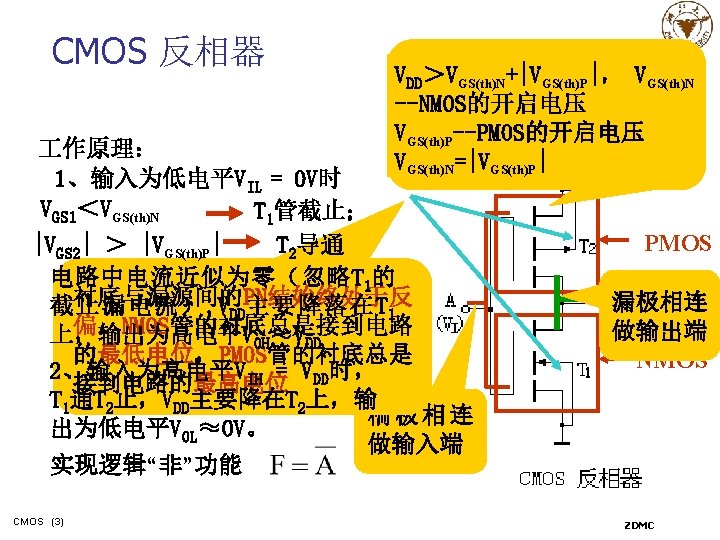

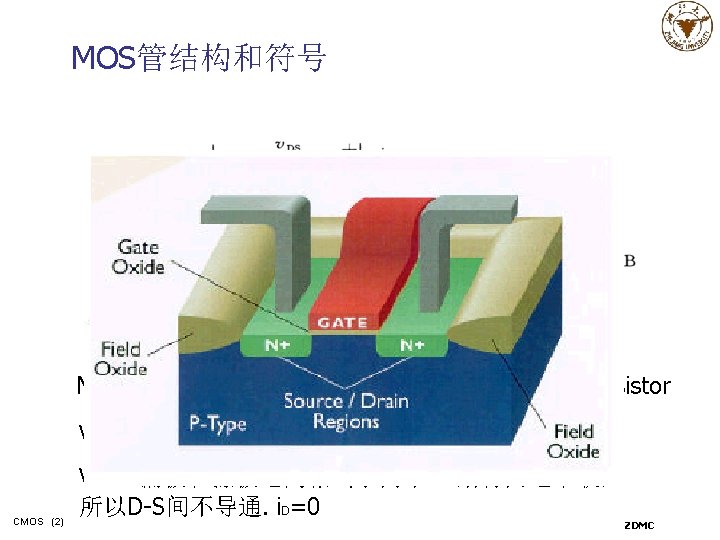

MOS管结构和符号 MOS: Metal-Oxide-Semiconductor Field-Effect Transistor VGS(th)称为MOS管的开启电压 CMOS (2) VGS=0漏极和源极之间相当于两个PN结背向地串联, 所以D-S间不导通. i. D=0 ZDMC

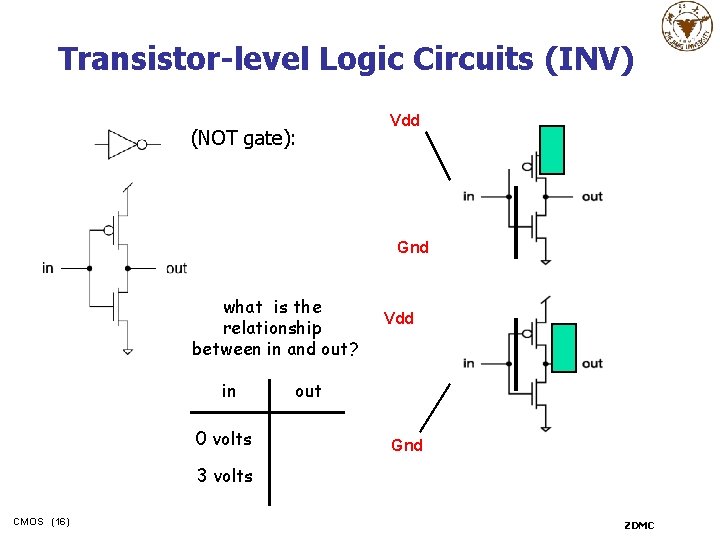

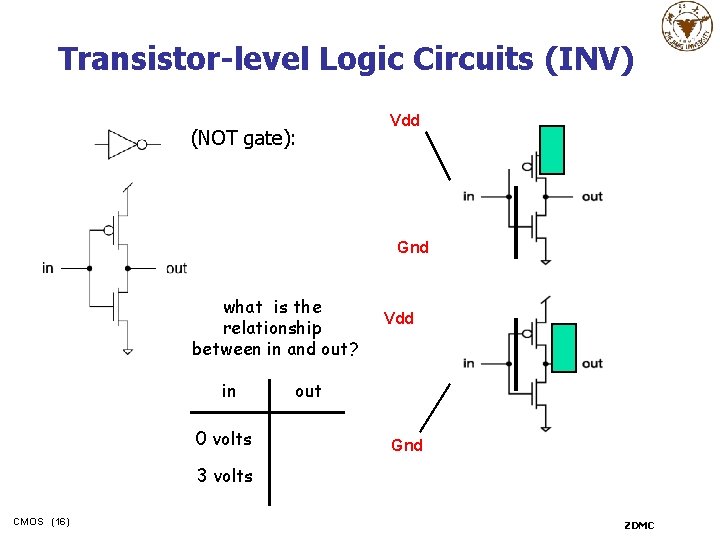

Transistor-level Logic Circuits (INV) n Inverter (NOT gate): Vdd Gnd what is the relationship between in and out? in 0 volts Vdd out Gnd 3 volts CMOS (16) ZDMC

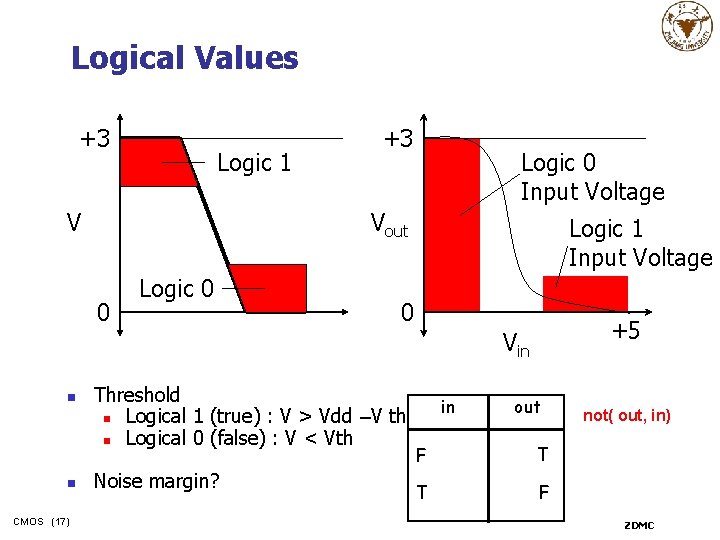

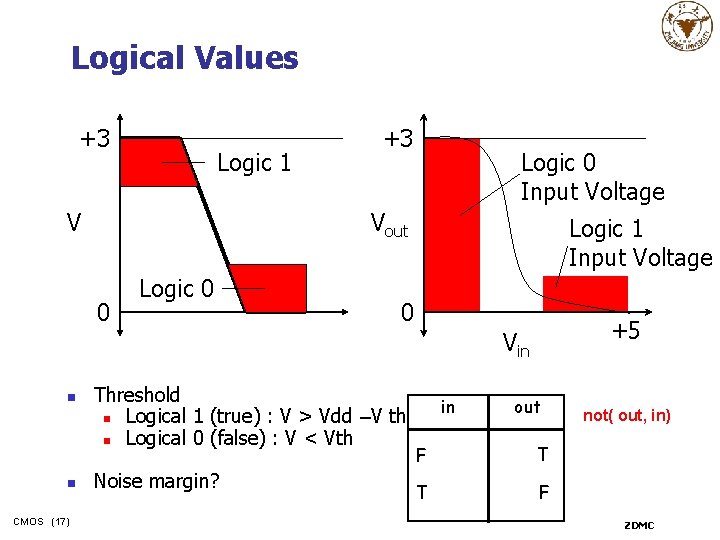

Logical Values +3 Logic 1 V +3 Logic 0 Input Voltage Vout 0 Logic 1 Input Voltage 0 +5 Vin n n CMOS (17) Threshold n Logical 1 (true) : V > Vdd –V th n Logical 0 (false) : V < Vth Noise margin? in out F T T F not( out, in) ZDMC

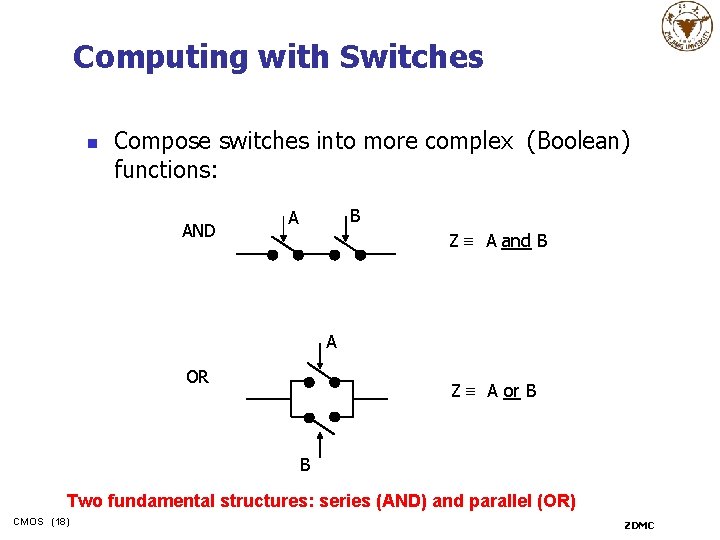

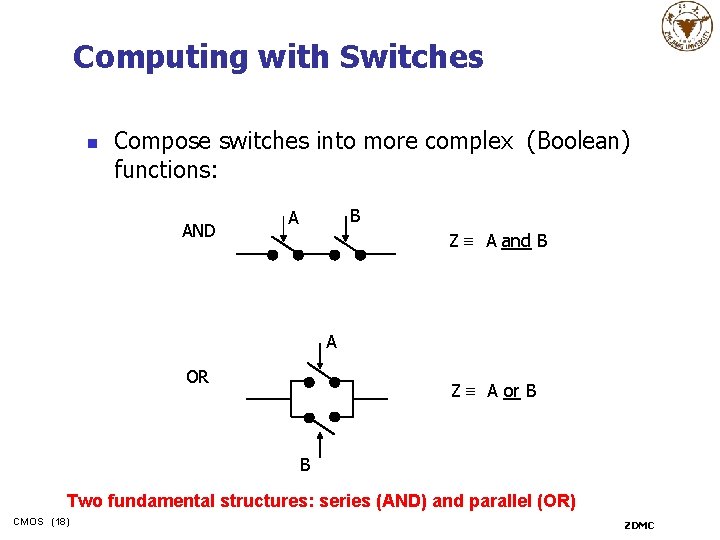

Computing with Switches n Compose switches into more complex (Boolean) functions: AND B A Z A and B A OR Z A or B B Two fundamental structures: series (AND) and parallel (OR) CMOS (18) ZDMC

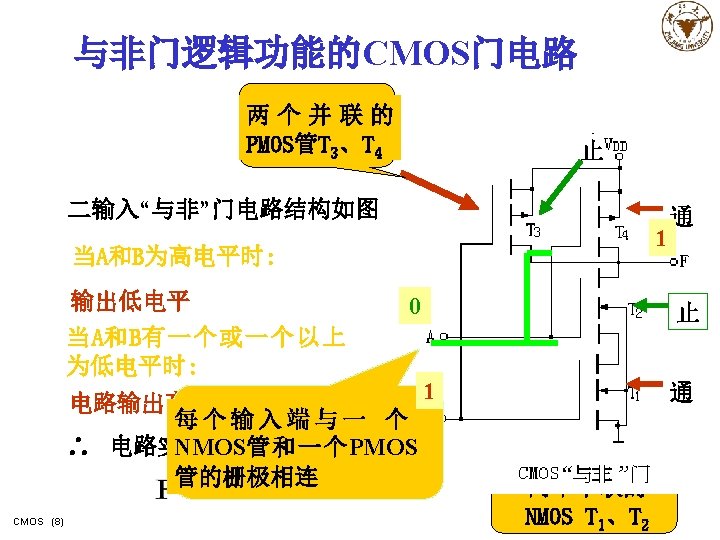

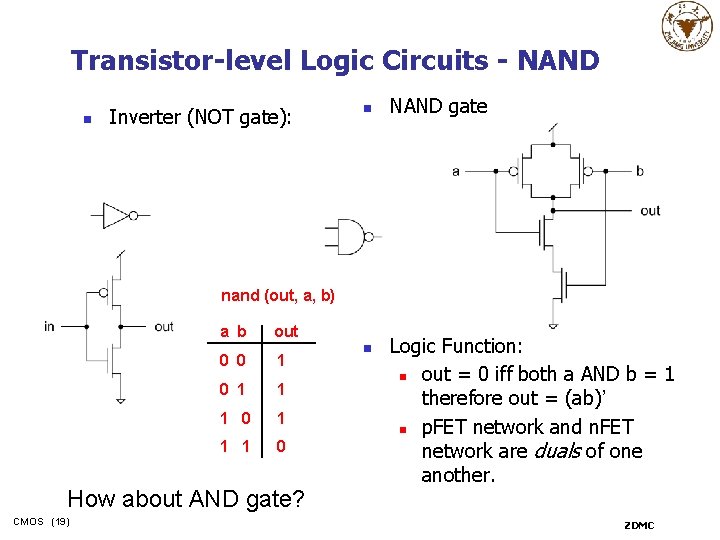

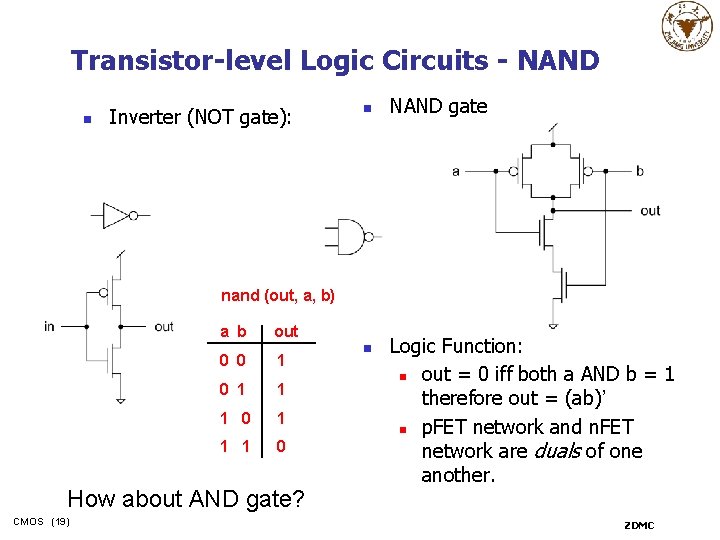

Transistor-level Logic Circuits - NAND n Inverter (NOT gate): n NAND gate nand (out, a, b) a b out 0 0 1 1 1 0 How about AND gate? CMOS (19) n Logic Function: n out = 0 iff both a AND b = 1 therefore out = (ab)’ n p. FET network and n. FET network are duals of one another. ZDMC

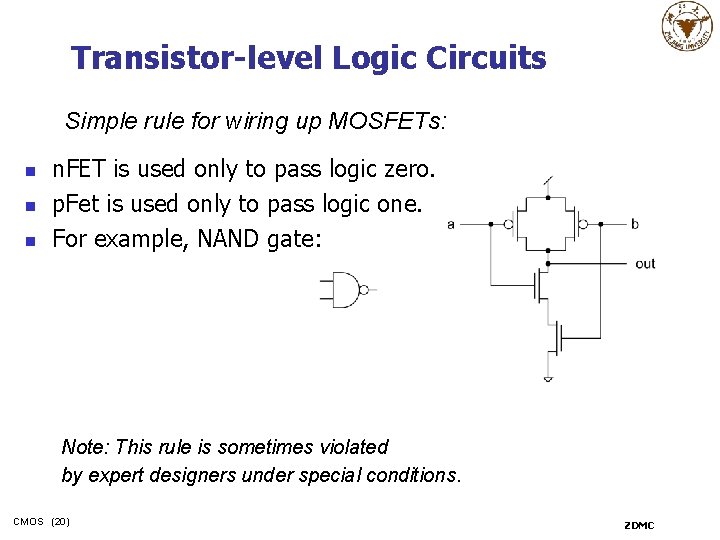

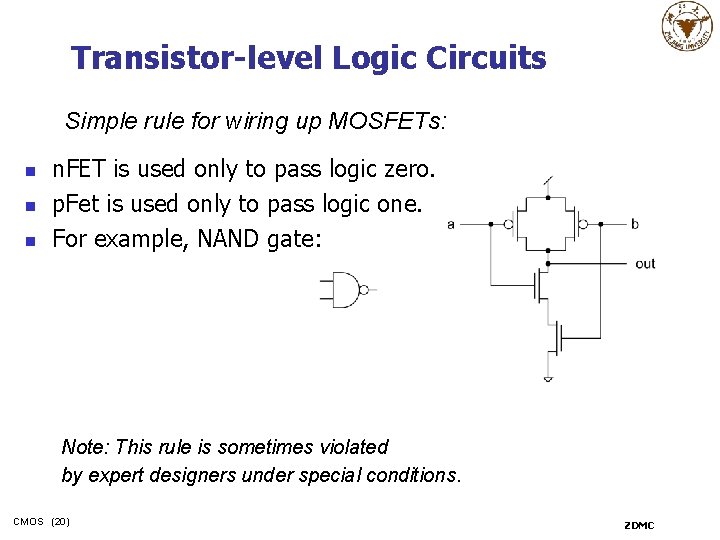

Transistor-level Logic Circuits Simple rule for wiring up MOSFETs: n n. FET is used only to pass logic zero. p. Fet is used only to pass logic one. For example, NAND gate: Note: This rule is sometimes violated by expert designers under special conditions. CMOS (20) ZDMC

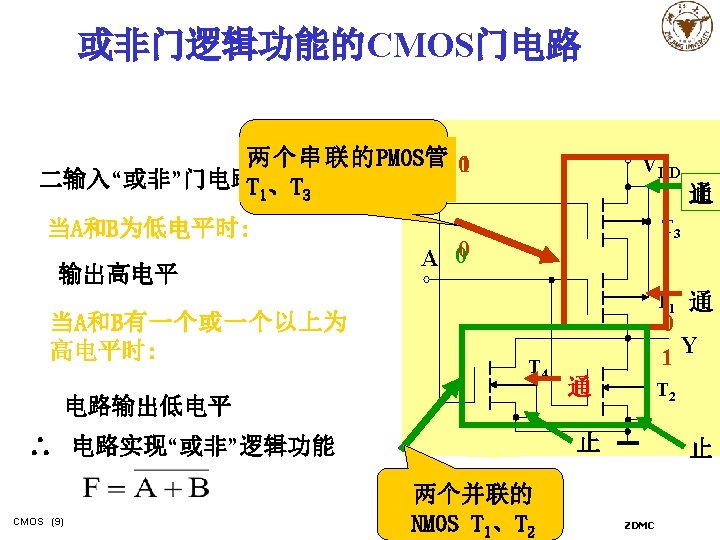

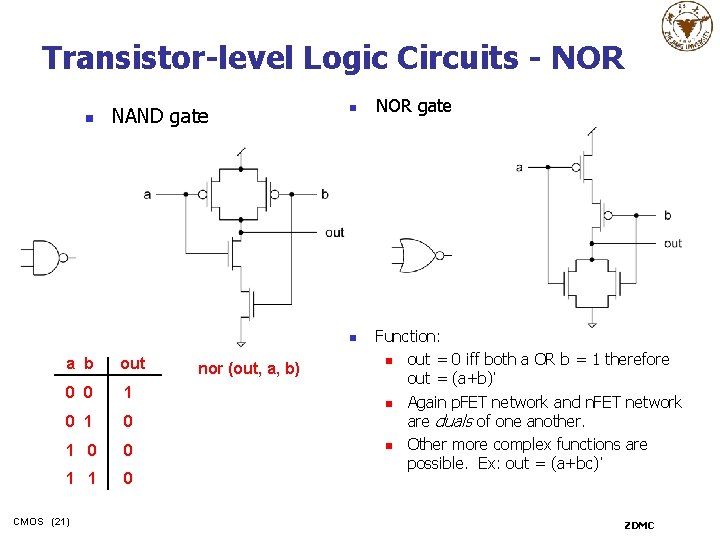

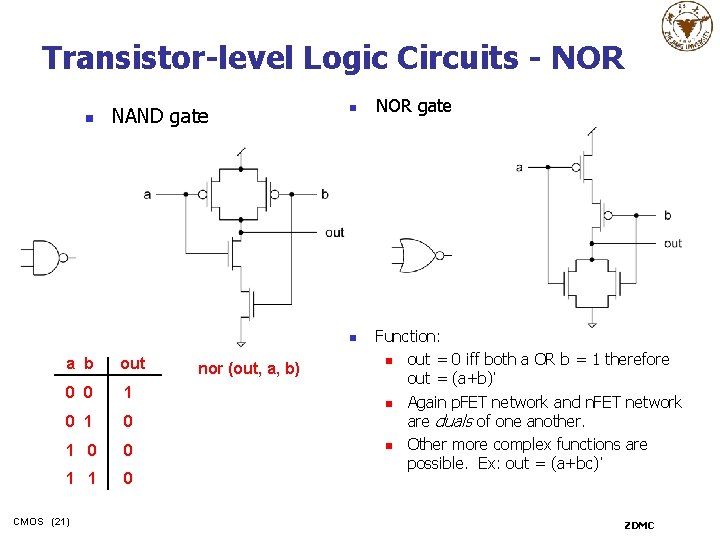

Transistor-level Logic Circuits - NOR n NAND gate n n a b out 0 0 1 0 1 0 0 1 1 0 CMOS (21) nor (out, a, b) NOR gate Function: n out = 0 iff both a OR b = 1 therefore out = (a+b)’ n Again p. FET network and n. FET network are duals of one another. n Other more complex functions are possible. Ex: out = (a+bc)’ ZDMC

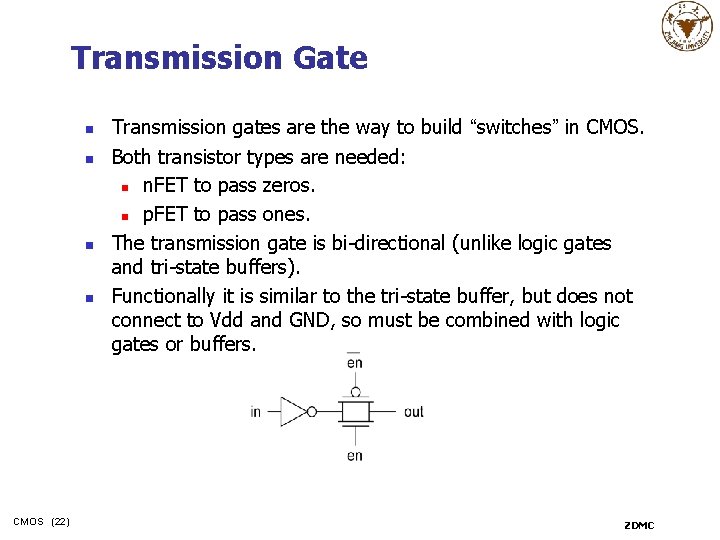

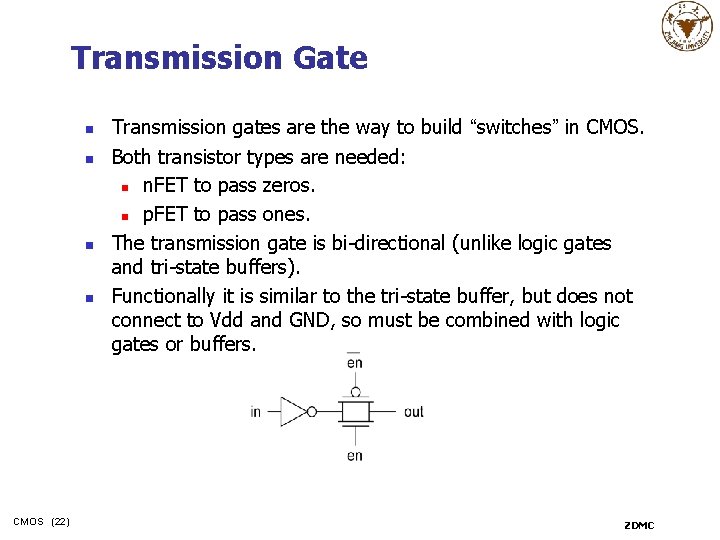

Transmission Gate n n CMOS (22) Transmission gates are the way to build “switches” in CMOS. Both transistor types are needed: n n. FET to pass zeros. n p. FET to pass ones. The transmission gate is bi-directional (unlike logic gates and tri-state buffers). Functionally it is similar to the tri-state buffer, but does not connect to Vdd and GND, so must be combined with logic gates or buffers. ZDMC

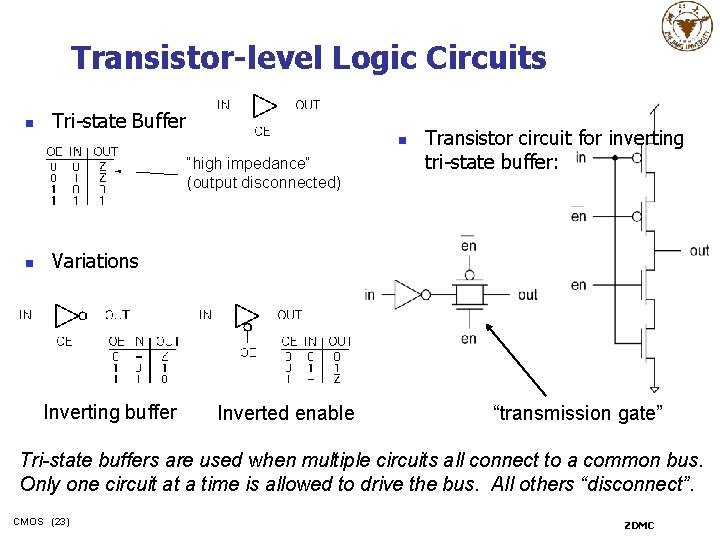

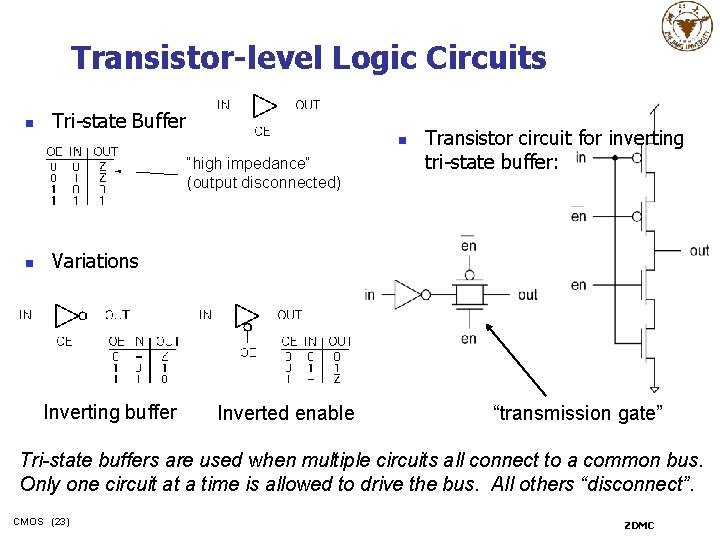

Transistor-level Logic Circuits n Tri-state Buffer n “high impedance” (output disconnected) n Transistor circuit for inverting tri-state buffer: Variations Inverting buffer Inverted enable “transmission gate” Tri-state buffers are used when multiple circuits all connect to a common bus. Only one circuit at a time is allowed to drive the bus. All others “disconnect”. CMOS (23) ZDMC

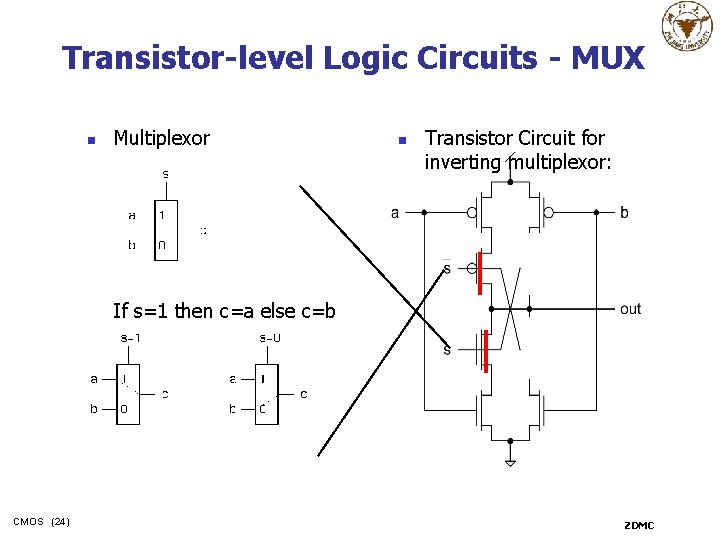

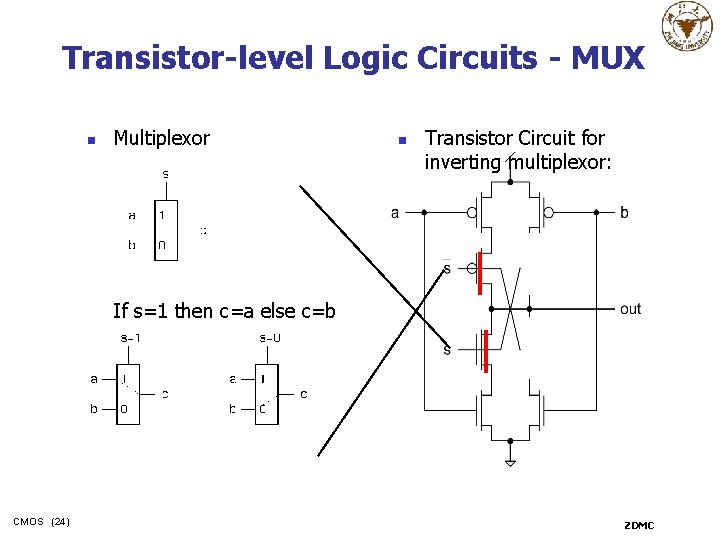

Transistor-level Logic Circuits - MUX n Multiplexor n Transistor Circuit for inverting multiplexor: If s=1 then c=a else c=b CMOS (24) ZDMC

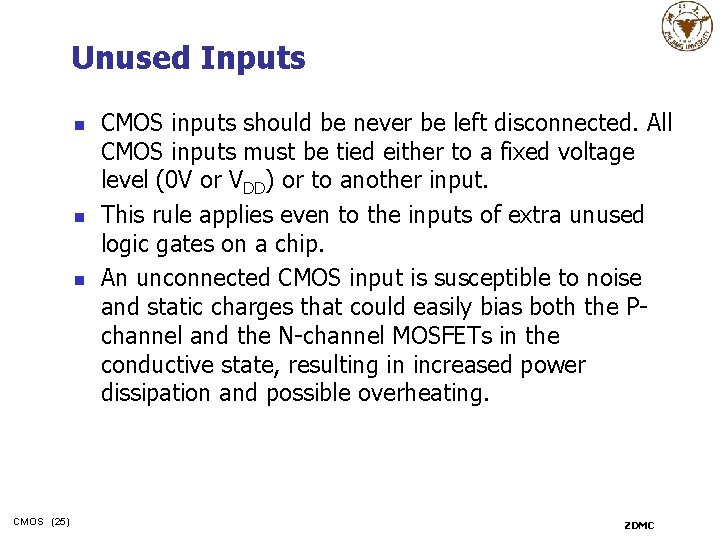

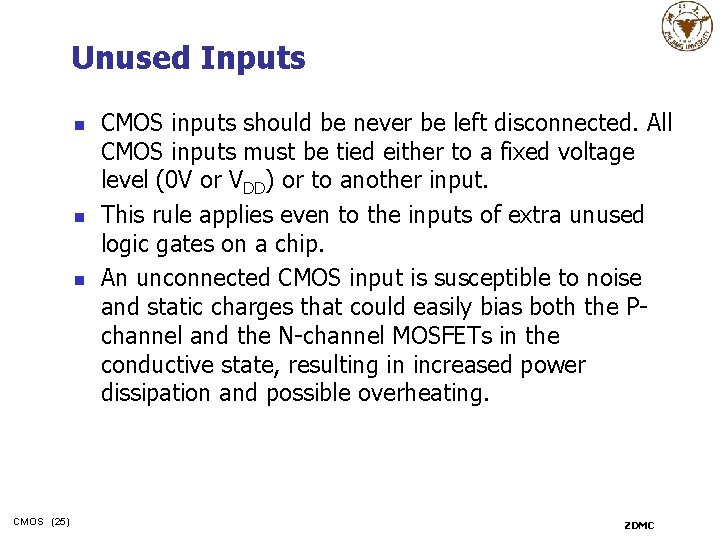

Unused Inputs n n n CMOS (25) CMOS inputs should be never be left disconnected. All CMOS inputs must be tied either to a fixed voltage level (0 V or VDD) or to another input. This rule applies even to the inputs of extra unused logic gates on a chip. An unconnected CMOS input is susceptible to noise and static charges that could easily bias both the Pchannel and the N-channel MOSFETs in the conductive state, resulting in increased power dissipation and possible overheating. ZDMC