5 Deviation from Ideal MOS Capacitor Behaviour 5

5. Deviation from Ideal MOS Capacitor Behaviour 5. 1. Work function difference q In the ideal MOS capacitor, it is assumed that there is no difference between the metal work function and the semiconductor work function. q So, when the MOS system is first brought into contact at equilibrium, there is no movement of the metal and semiconductor Fermi levels relative to each other (since both are at the same level), and there is no transfer of charges between the metal and the semiconductor. q The energy bands, EC, EV, Ei in the semiconductor are then flat when no voltage is applied to the gate. This is referred to as the flat band condition. q However, this is generally not true for all MOS systems. There is, generally, a difference in the work functions of the metal and the semiconductor in a MOS system. L S Tan - 2011 EE 2004 1

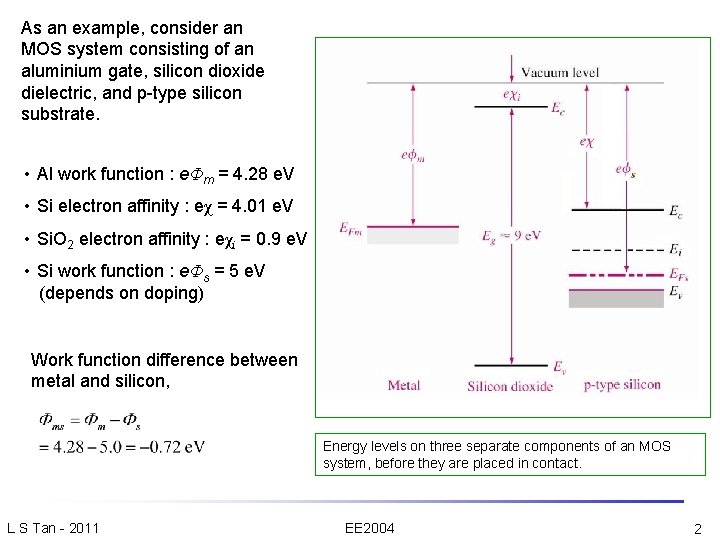

As an example, consider an MOS system consisting of an aluminium gate, silicon dioxide dielectric, and p-type silicon substrate. • Al work function : eΦm = 4. 28 e. V • Si electron affinity : eχ = 4. 01 e. V • Si. O 2 electron affinity : eχi = 0. 9 e. V • Si work function : eΦs = 5 e. V (depends on doping) Work function difference between metal and silicon, Energy levels on three separate components of an MOS system, before they are placed in contact. L S Tan - 2011 EE 2004 2

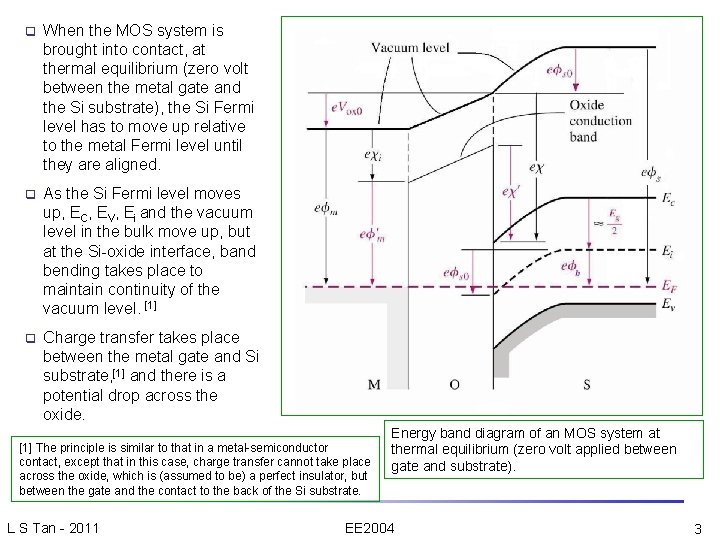

q When the MOS system is brought into contact, at thermal equilibrium (zero volt between the metal gate and the Si substrate), the Si Fermi level has to move up relative to the metal Fermi level until they are aligned. q As the Si Fermi level moves up, EC, EV, Ei and the vacuum level in the bulk move up, but at the Si-oxide interface, band bending takes place to maintain continuity of the vacuum level. [1] q Charge transfer takes place between the metal gate and Si substrate, [1] and there is a potential drop across the oxide. [1] The principle is similar to that in a metal-semiconductor contact, except that in this case, charge transfer cannot take place across the oxide, which is (assumed to be) a perfect insulator, but between the gate and the contact to the back of the Si substrate. L S Tan - 2011 Energy band diagram of an MOS system at thermal equilibrium (zero volt applied between gate and substrate). EE 2004 3

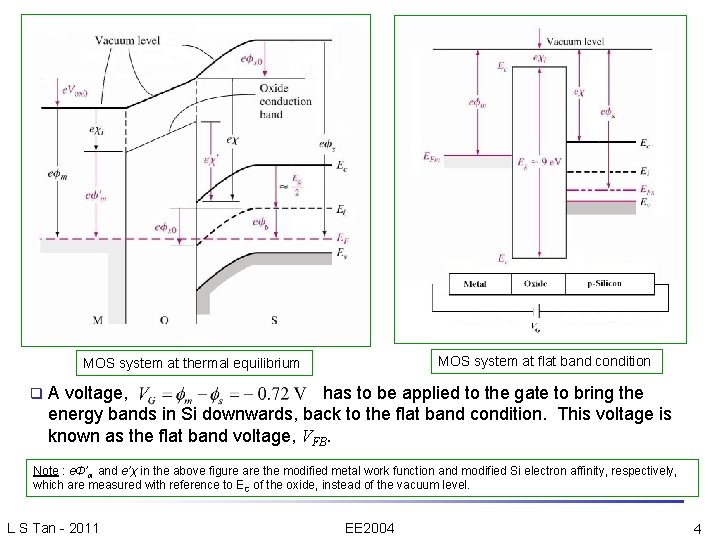

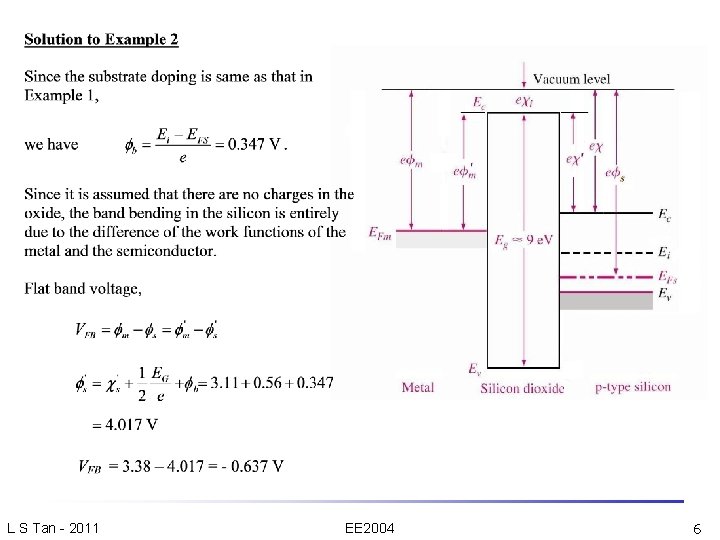

MOS system at flat band condition MOS system at thermal equilibrium q A voltage, has to be applied to the gate to bring the energy bands in Si downwards, back to the flat band condition. This voltage is known as the flat band voltage, VFB. Note : eΦ’m and e’χ in the above figure are the modified metal work function and modified Si electron affinity, respectively, which are measured with reference to EC of the oxide, instead of the vacuum level. L S Tan - 2011 EE 2004 4

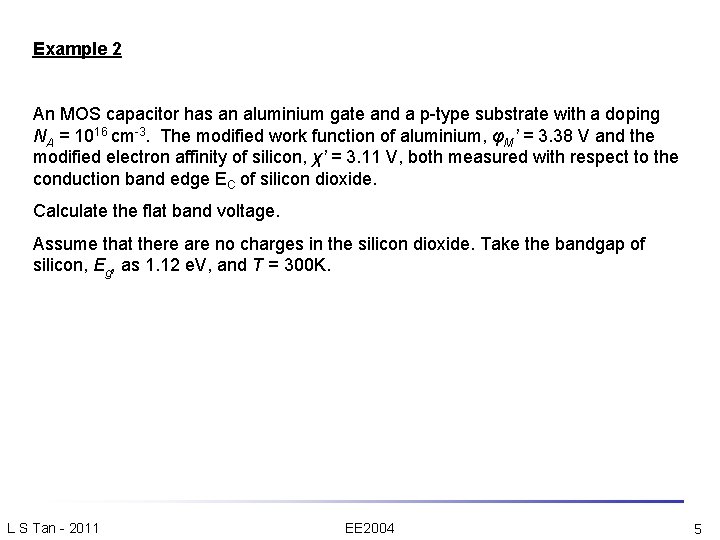

Example 2 An MOS capacitor has an aluminium gate and a p-type substrate with a doping NA = 1016 cm-3. The modified work function of aluminium, φM’ = 3. 38 V and the modified electron affinity of silicon, χ’ = 3. 11 V, both measured with respect to the conduction band edge EC of silicon dioxide. Calculate the flat band voltage. Assume that there are no charges in the silicon dioxide. Take the bandgap of silicon, Eg, as 1. 12 e. V, and T = 300 K. L S Tan - 2011 EE 2004 5

L S Tan - 2011 EE 2004 6

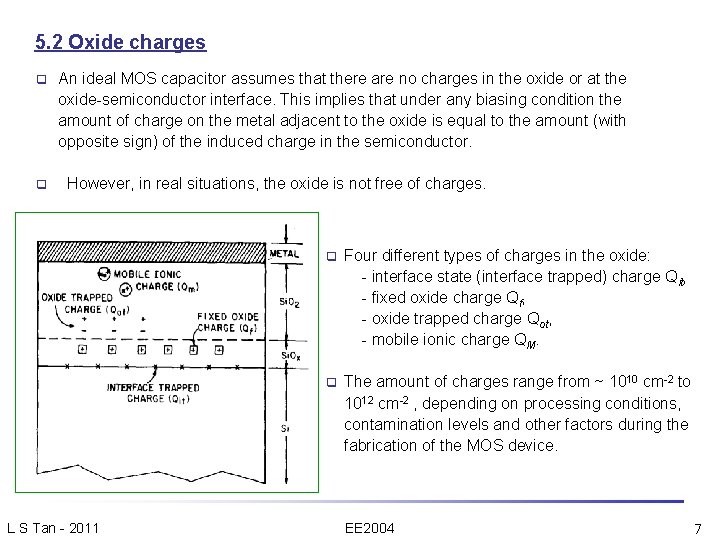

5. 2 Oxide charges q q An ideal MOS capacitor assumes that there are no charges in the oxide or at the oxide-semiconductor interface. This implies that under any biasing condition the amount of charge on the metal adjacent to the oxide is equal to the amount (with opposite sign) of the induced charge in the semiconductor. However, in real situations, the oxide is not free of charges. L S Tan - 2011 q Four different types of charges in the oxide: - interface state (interface trapped) charge Qit, - fixed oxide charge Qf, - oxide trapped charge Qot, - mobile ionic charge QM. q The amount of charges range from ~ 1010 cm-2 to 1012 cm-2 , depending on processing conditions, contamination levels and other factors during the fabrication of the MOS device. EE 2004 7

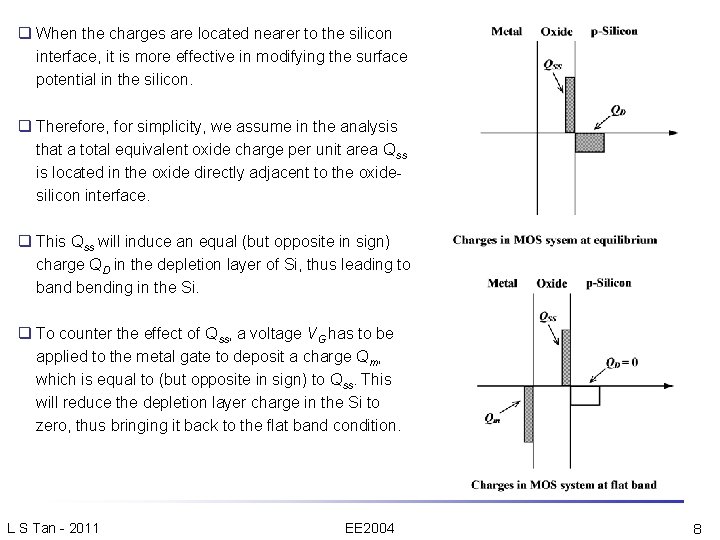

q When the charges are located nearer to the silicon interface, it is more effective in modifying the surface potential in the silicon. q Therefore, for simplicity, we assume in the analysis that a total equivalent oxide charge per unit area Qss is located in the oxide directly adjacent to the oxidesilicon interface. q This Qss will induce an equal (but opposite in sign) charge QD in the depletion layer of Si, thus leading to band bending in the Si. q To counter the effect of Qss, a voltage VG has to be applied to the metal gate to deposit a charge Qm, which is equal to (but opposite in sign) to Qss. This will reduce the depletion layer charge in the Si to zero, thus bringing it back to the flat band condition. L S Tan - 2011 EE 2004 8

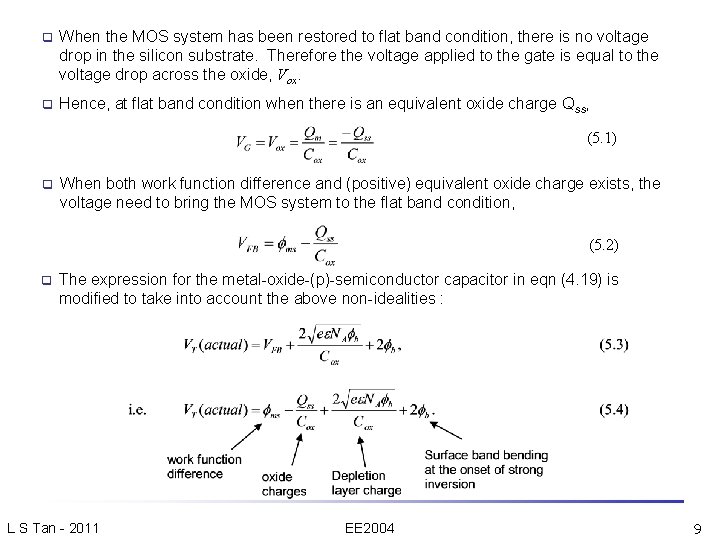

q When the MOS system has been restored to flat band condition, there is no voltage drop in the silicon substrate. Therefore the voltage applied to the gate is equal to the voltage drop across the oxide, Vox. q Hence, at flat band condition when there is an equivalent oxide charge Qss, (5. 1) q When both work function difference and (positive) equivalent oxide charge exists, the voltage need to bring the MOS system to the flat band condition, (5. 2) q The expression for the metal-oxide-(p)-semiconductor capacitor in eqn (4. 19) is modified to take into account the above non-idealities : L S Tan - 2011 EE 2004 9

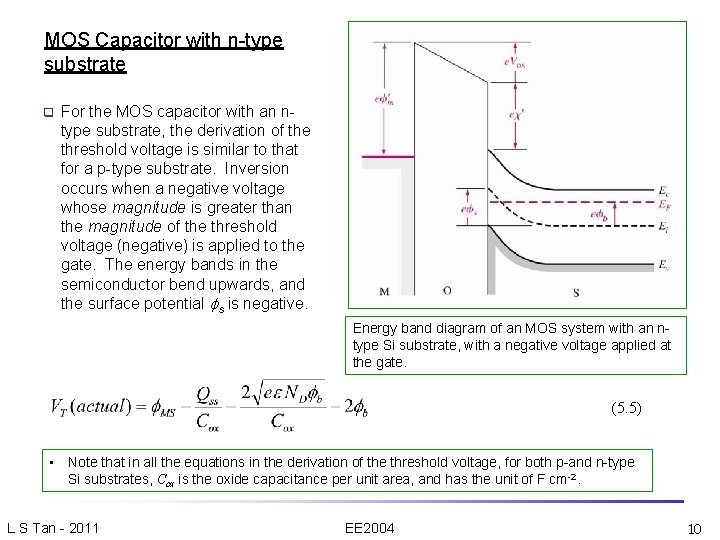

MOS Capacitor with n-type substrate q For the MOS capacitor with an ntype substrate, the derivation of the threshold voltage is similar to that for a p-type substrate. Inversion occurs when a negative voltage whose magnitude is greater than the magnitude of the threshold voltage (negative) is applied to the gate. The energy bands in the semiconductor bend upwards, and the surface potential s is negative. Energy band diagram of an MOS system with an ntype Si substrate, with a negative voltage applied at the gate. (5. 5) • Note that in all the equations in the derivation of the threshold voltage, for both p-and n-type Si substrates, Cox is the oxide capacitance per unit area, and has the unit of F cm-2. L S Tan - 2011 EE 2004 10

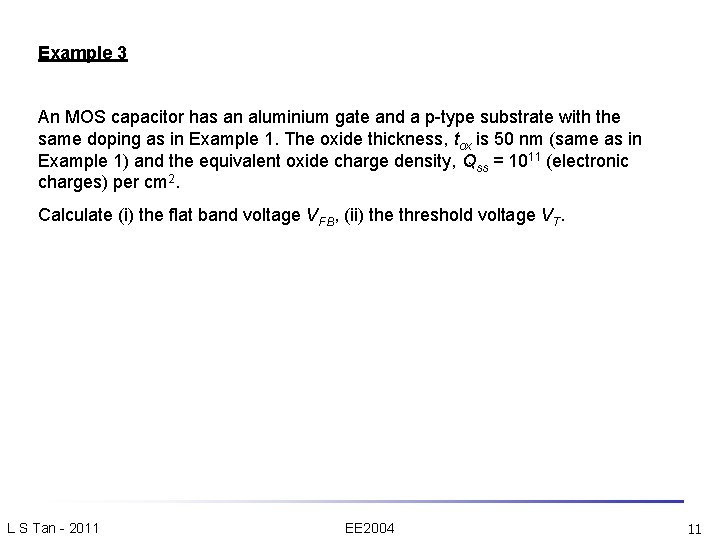

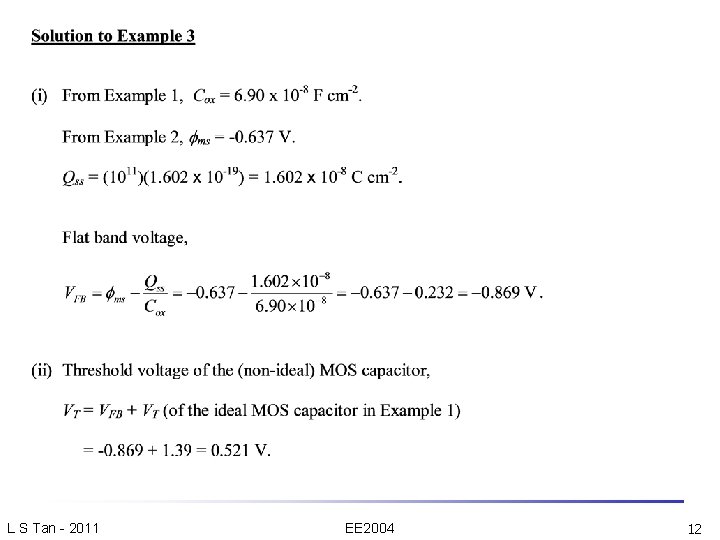

Example 3 An MOS capacitor has an aluminium gate and a p-type substrate with the same doping as in Example 1. The oxide thickness, tox is 50 nm (same as in Example 1) and the equivalent oxide charge density, Qss = 1011 (electronic charges) per cm 2. Calculate (i) the flat band voltage VFB, (ii) the threshold voltage VT. L S Tan - 2011 EE 2004 11

L S Tan - 2011 EE 2004 12

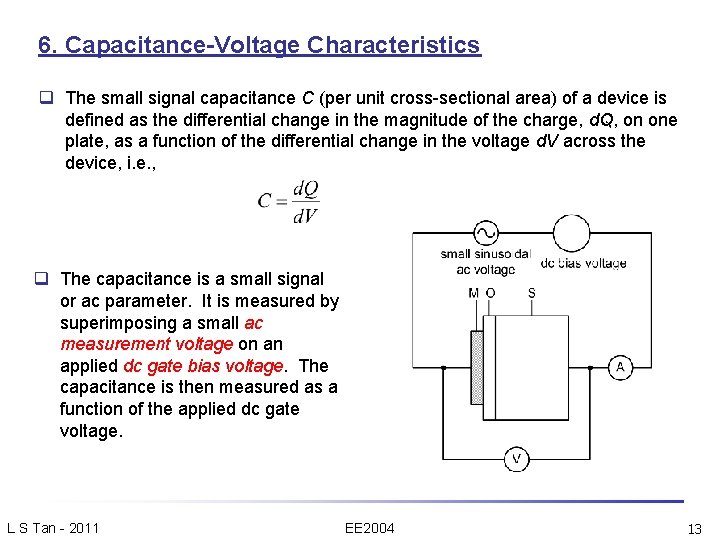

6. Capacitance-Voltage Characteristics q The small signal capacitance C (per unit cross-sectional area) of a device is defined as the differential change in the magnitude of the charge, d. Q, on one plate, as a function of the differential change in the voltage d. V across the device, i. e. , q The capacitance is a small signal or ac parameter. It is measured by superimposing a small ac measurement voltage on an applied dc gate bias voltage. The capacitance is then measured as a function of the applied dc gate voltage. L S Tan - 2011 EE 2004 13

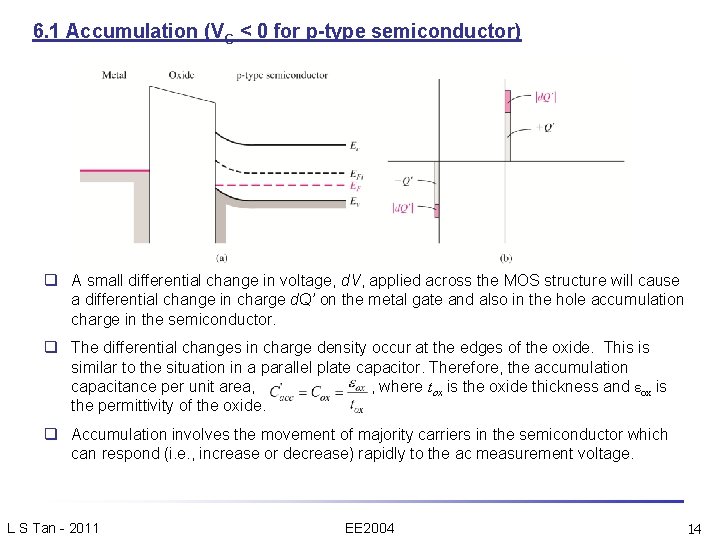

6. 1 Accumulation (VG < 0 for p-type semiconductor) q A small differential change in voltage, d. V, applied across the MOS structure will cause a differential change in charge d. Q’ on the metal gate and also in the hole accumulation charge in the semiconductor. q The differential changes in charge density occur at the edges of the oxide. This is similar to the situation in a parallel plate capacitor. Therefore, the accumulation capacitance per unit area, , where tox is the oxide thickness and εox is the permittivity of the oxide. q Accumulation involves the movement of majority carriers in the semiconductor which can respond (i. e. , increase or decrease) rapidly to the ac measurement voltage. L S Tan - 2011 EE 2004 14

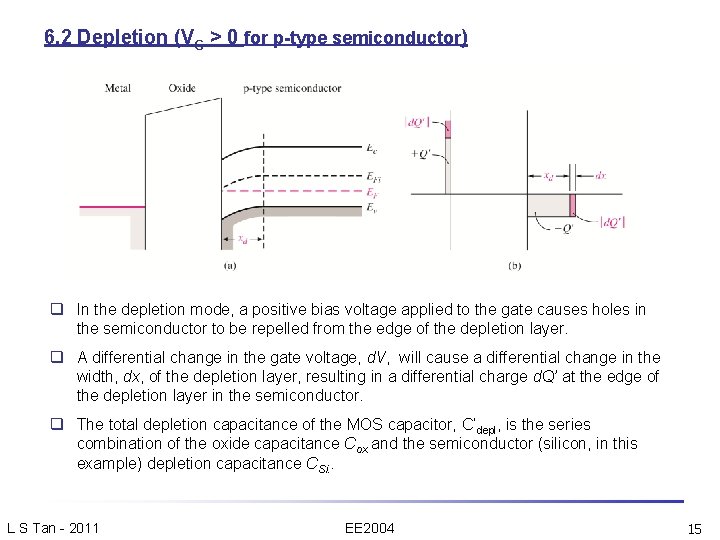

6. 2 Depletion (VG > 0 for p-type semiconductor) q In the depletion mode, a positive bias voltage applied to the gate causes holes in the semiconductor to be repelled from the edge of the depletion layer. q A differential change in the gate voltage, d. V, will cause a differential change in the width, dx, of the depletion layer, resulting in a differential charge d. Q’ at the edge of the depletion layer in the semiconductor. q The total depletion capacitance of the MOS capacitor, C’depl, is the series combination of the oxide capacitance Cox and the semiconductor (silicon, in this example) depletion capacitance CSi. . L S Tan - 2011 EE 2004 15

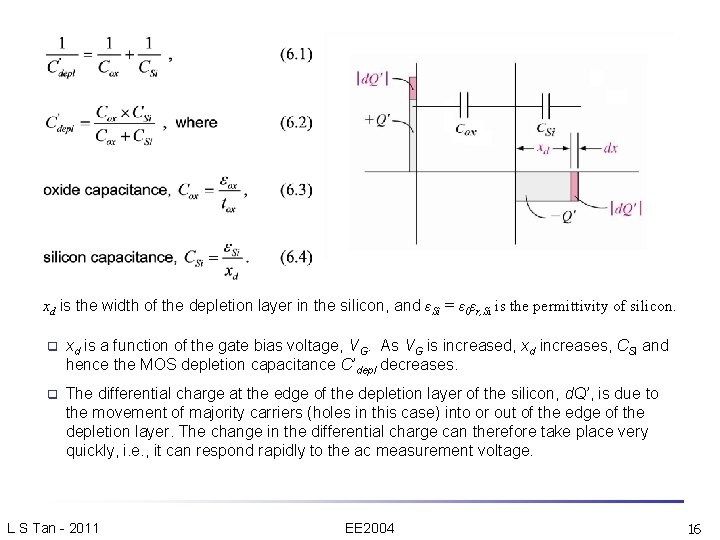

xd is the width of the depletion layer in the silicon, and εSi = ε 0εr, Si is the permittivity of silicon. q xd is a function of the gate bias voltage, VG. As VG is increased, xd increases, CSi and hence the MOS depletion capacitance C’depl decreases. q The differential charge at the edge of the depletion layer of the silicon, d. Q’, is due to the movement of majority carriers (holes in this case) into or out of the edge of the depletion layer. The change in the differential charge can therefore take place very quickly, i. e. , it can respond rapidly to the ac measurement voltage. L S Tan - 2011 EE 2004 16

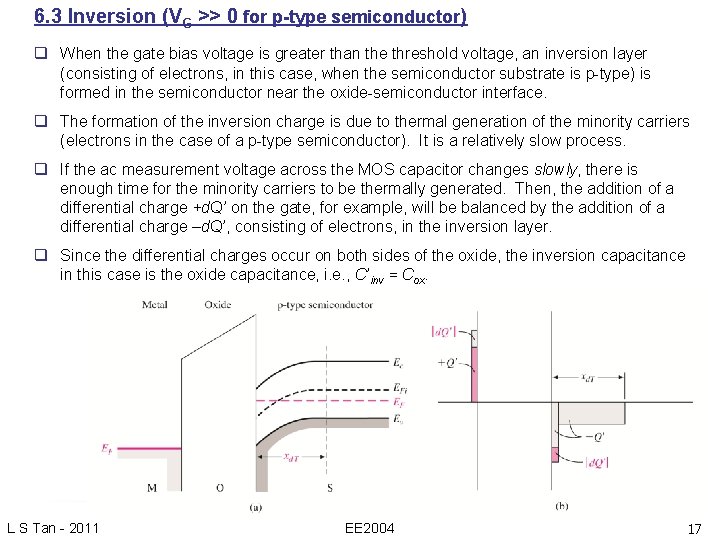

6. 3 Inversion (VG >> 0 for p-type semiconductor) q When the gate bias voltage is greater than the threshold voltage, an inversion layer (consisting of electrons, in this case, when the semiconductor substrate is p-type) is formed in the semiconductor near the oxide-semiconductor interface. q The formation of the inversion charge is due to thermal generation of the minority carriers (electrons in the case of a p-type semiconductor). It is a relatively slow process. q If the ac measurement voltage across the MOS capacitor changes slowly, there is enough time for the minority carriers to be thermally generated. Then, the addition of a differential charge +d. Q’ on the gate, for example, will be balanced by the addition of a differential charge –d. Q’, consisting of electrons, in the inversion layer. q Since the differential charges occur on both sides of the oxide, the inversion capacitance in this case is the oxide capacitance, i. e. , C’inv = Cox. L S Tan - 2011 EE 2004 17

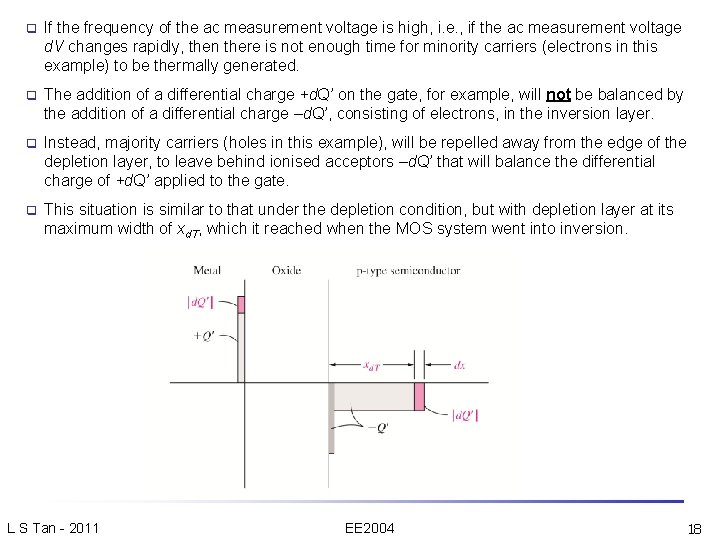

q If the frequency of the ac measurement voltage is high, i. e. , if the ac measurement voltage d. V changes rapidly, then there is not enough time for minority carriers (electrons in this example) to be thermally generated. q The addition of a differential charge +d. Q’ on the gate, for example, will not be balanced by the addition of a differential charge –d. Q’, consisting of electrons, in the inversion layer. q Instead, majority carriers (holes in this example), will be repelled away from the edge of the depletion layer, to leave behind ionised acceptors –d. Q’ that will balance the differential charge of +d. Q’ applied to the gate. q This situation is similar to that under the depletion condition, but with depletion layer at its maximum width of xd. T, which it reached when the MOS system went into inversion. L S Tan - 2011 EE 2004 18

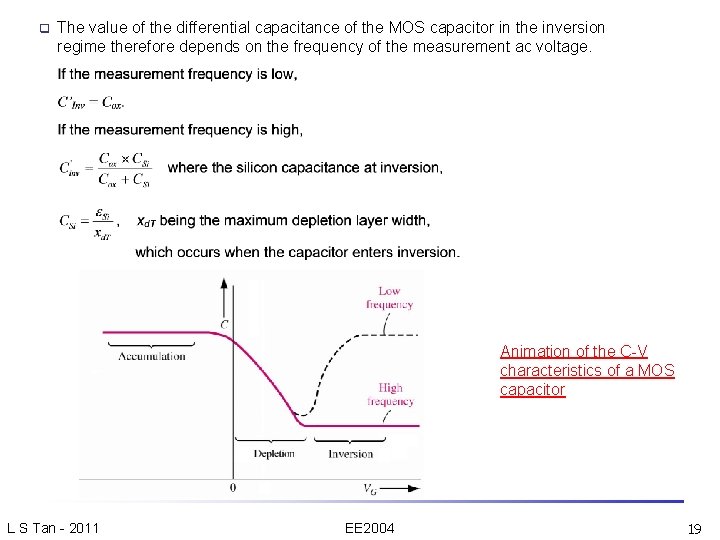

q The value of the differential capacitance of the MOS capacitor in the inversion regime therefore depends on the frequency of the measurement ac voltage. Animation of the C-V characteristics of a MOS capacitor L S Tan - 2011 EE 2004 19

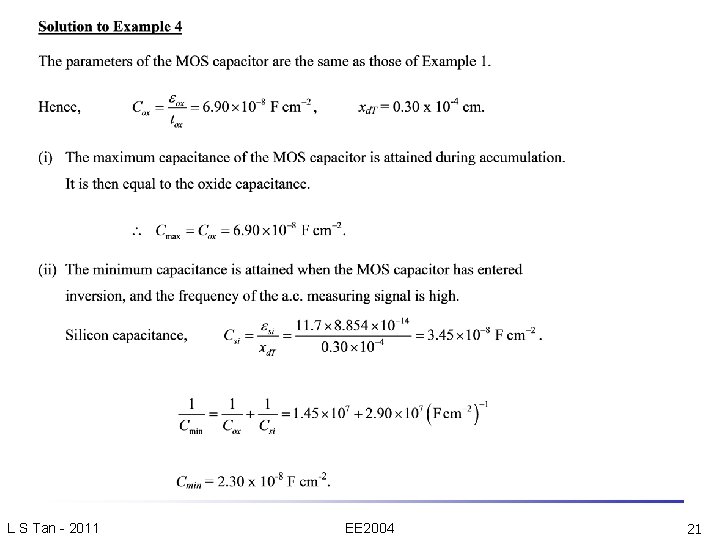

Example 4 The oxide thickness and substrate doping of a MOS capacitor are : tox = 50 nm, NA = 1016 cm-3 (p-type), respectively. Calculate (i) the maximum capacitance Cmax, (ii) the minimum capacitance Cmin, (per unit area of the capacitor) in the C-V characteristic of the MOS capacitor. Take T = 300 K, Vt = 0. 0259 V, ni = 1. 5 x 1010 cm-3. L S Tan - 2011 EE 2004 20

L S Tan - 2011 EE 2004 21

- Slides: 21