The CMOS Inverter Lecture 3 Static properties voltage

- Slides: 35

The CMOS Inverter Lecture 3 Static properties = voltage transfer curves (VTC) and noise margins

Week 2: The CMOS inverter • Tuesday – Static properties • Voltage transfer curves (VTC) • Noise margins – Exercise (Kjell, 1 hour) • Thursday – Dynamic properties • Propagation delay • Driving large capacitive loads w. optimal propagation delay – Exercise POTW (Victor, 2 hours) • Friday – Prelab 1 deadline 1 PM 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 2

What happened last week? • Let’s do a quiz about the transistor: – Go to socrative. com – Select Student login – Go to room: “MCC 0922018” 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 3

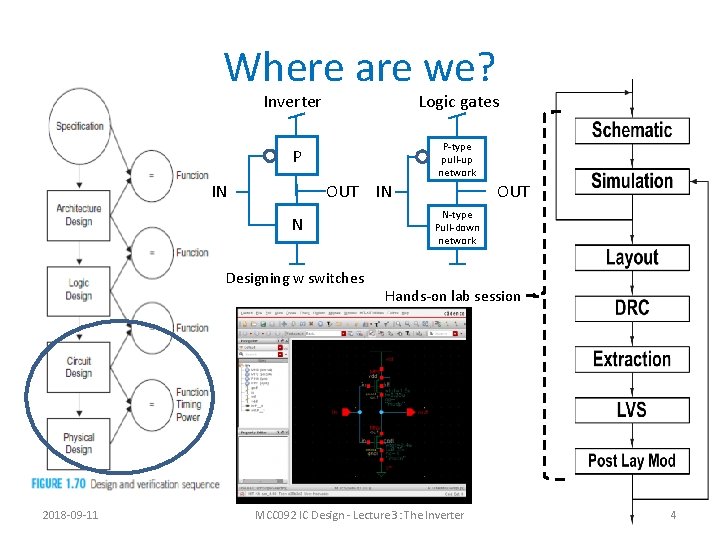

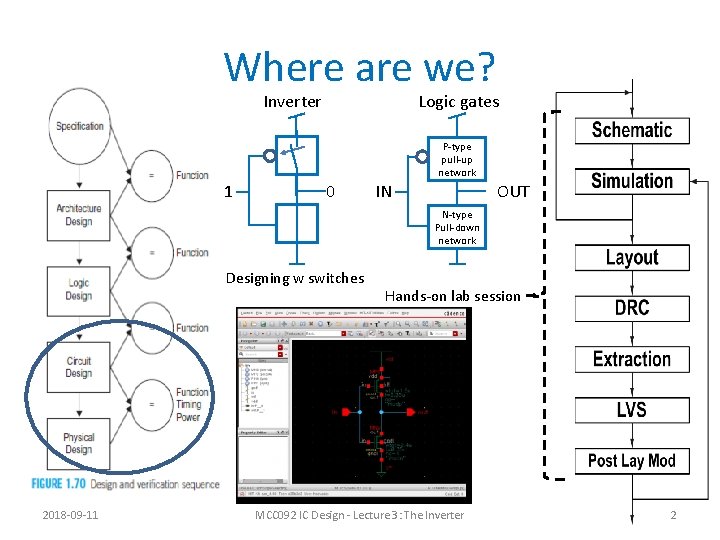

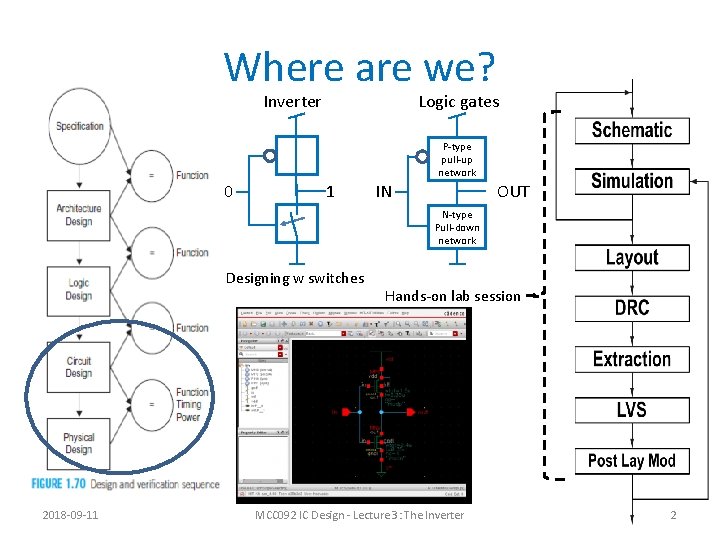

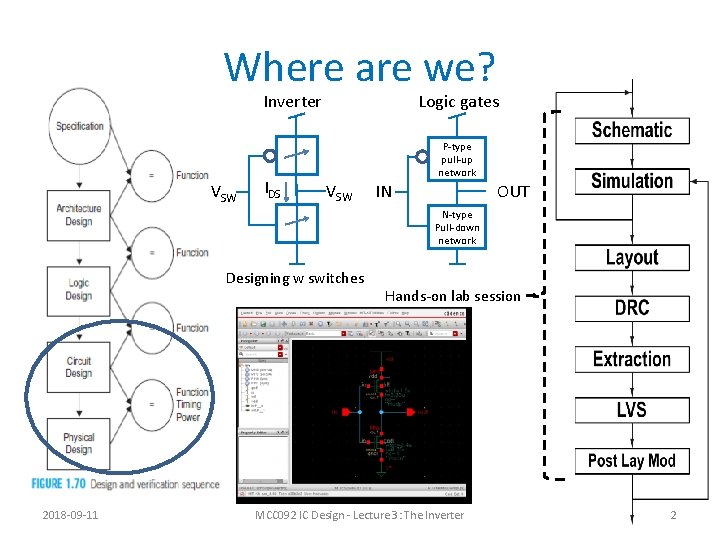

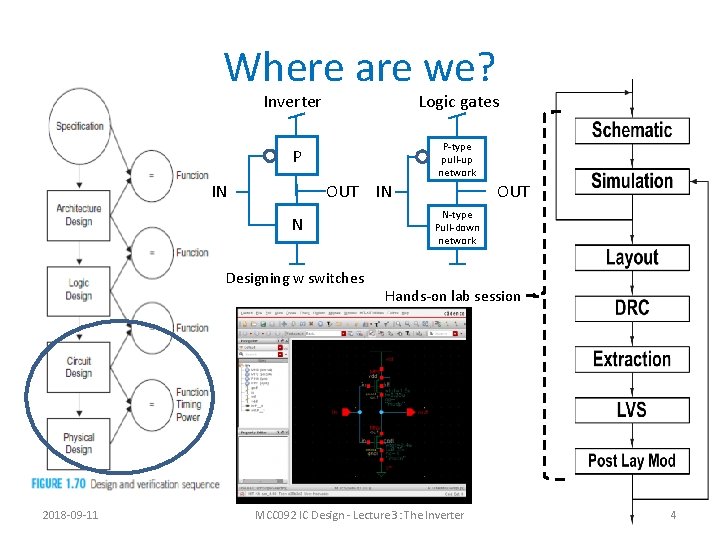

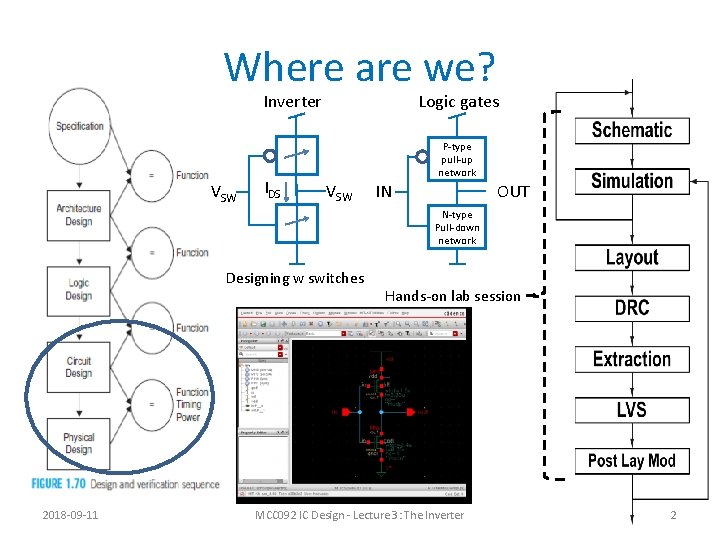

Where are we? Inverter Logic gates P-type pull-up network P OUT IN IN N Designing w switches 2018 -09 -11 OUT N-type Pull-down network Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 4

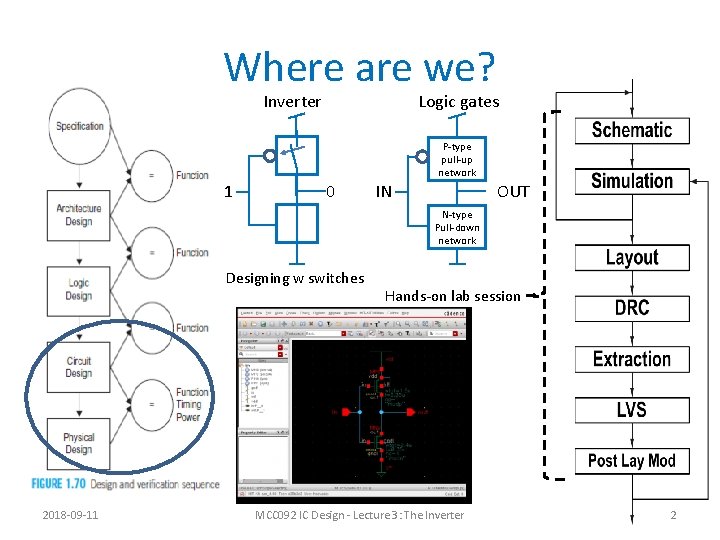

Where are we? Inverter Logic gates P-type pull-up network 1 0 OUT IN N-type Pull-down network Designing w switches 2018 -09 -11 Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

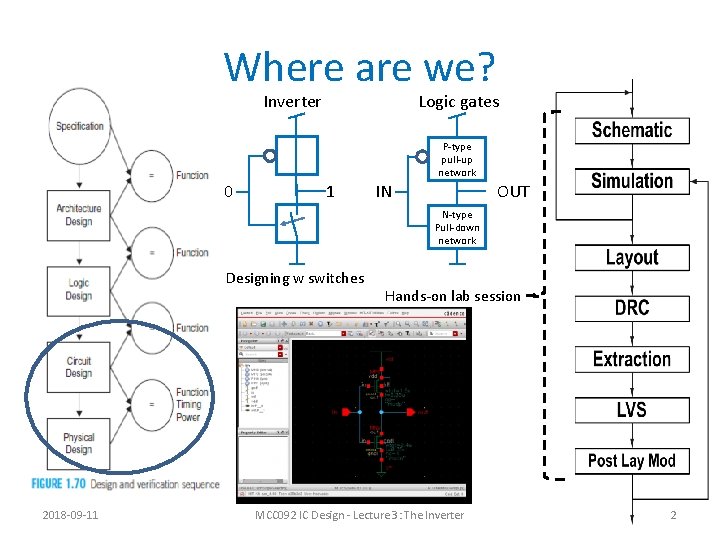

Where are we? Inverter Logic gates P-type pull-up network 0 1 OUT IN N-type Pull-down network Designing w switches 2018 -09 -11 Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

Where are we? Inverter VSW IDS Logic gates P-type pull-up network VSW OUT IN N-type Pull-down network Designing w switches 2018 -09 -11 Hands-on lab session MCC 092 IC Design - Lecture 3: The Inverter 2

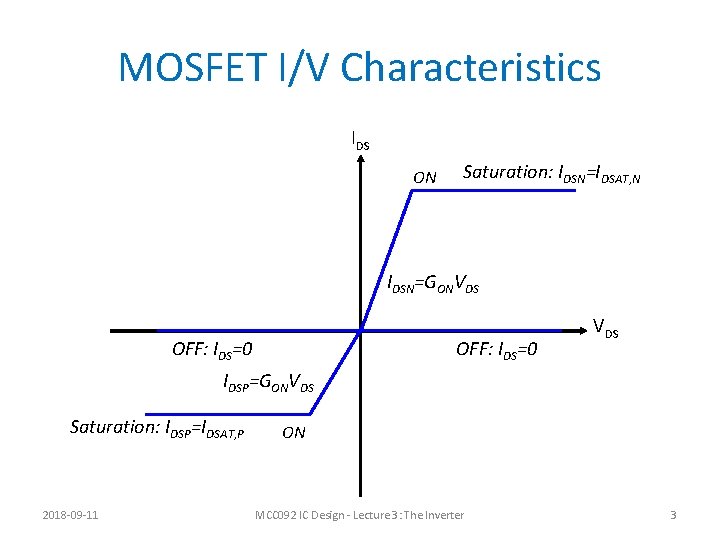

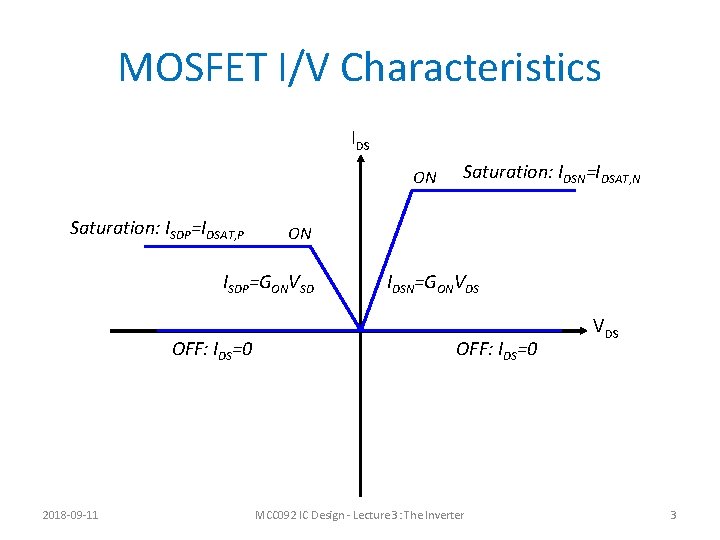

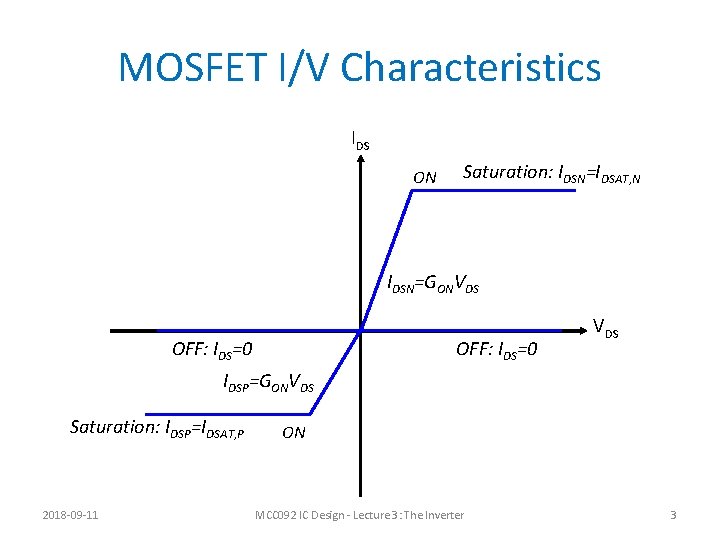

MOSFET I/V Characteristics IDS ON Saturation: IDSN=IDSAT, N IDSN=GONVDS OFF: IDS=0 VDS IDSP=GONVDS Saturation: IDSP=IDSAT, P 2018 -09 -11 ON MCC 092 IC Design - Lecture 3: The Inverter 3

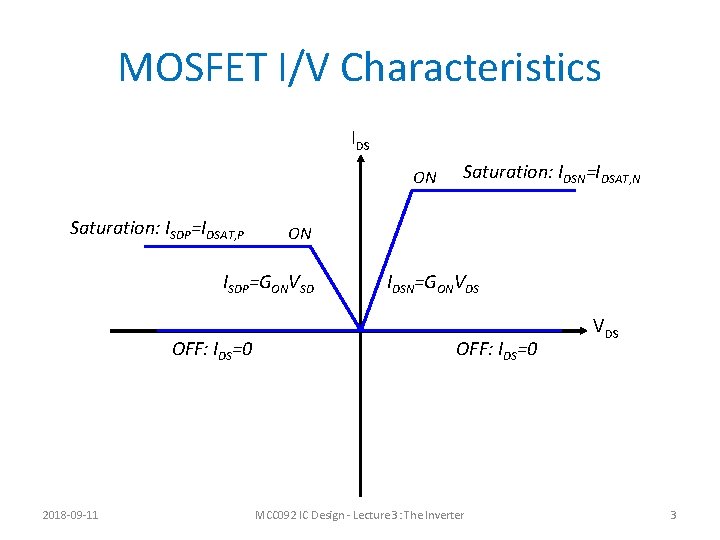

MOSFET I/V Characteristics IDS ON Saturation: ISDP=IDSAT, P ON ISDP=GONVSD OFF: IDS=0 2018 -09 -11 Saturation: IDSN=IDSAT, N IDSN=GONVDS OFF: IDS=0 MCC 092 IC Design - Lecture 3: The Inverter VDS 3

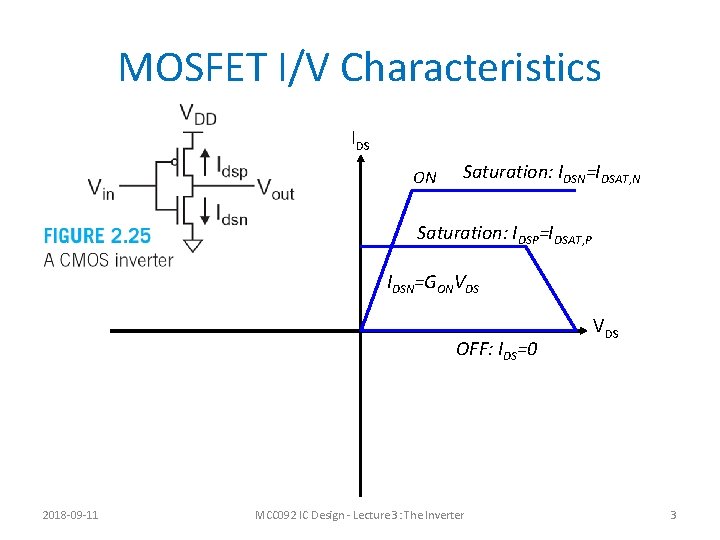

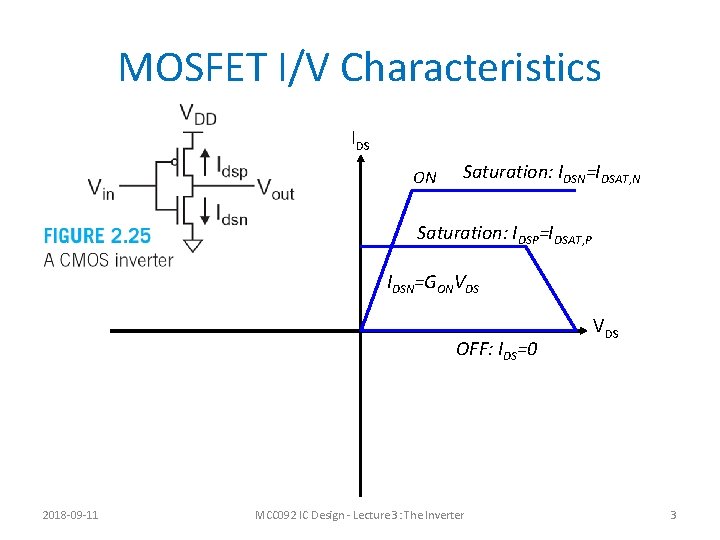

MOSFET I/V Characteristics IDS ON Saturation: IDSN=IDSAT, N Saturation: IDSP=IDSAT, P IDSN=GONVDS OFF: IDS=0 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter VDS 3

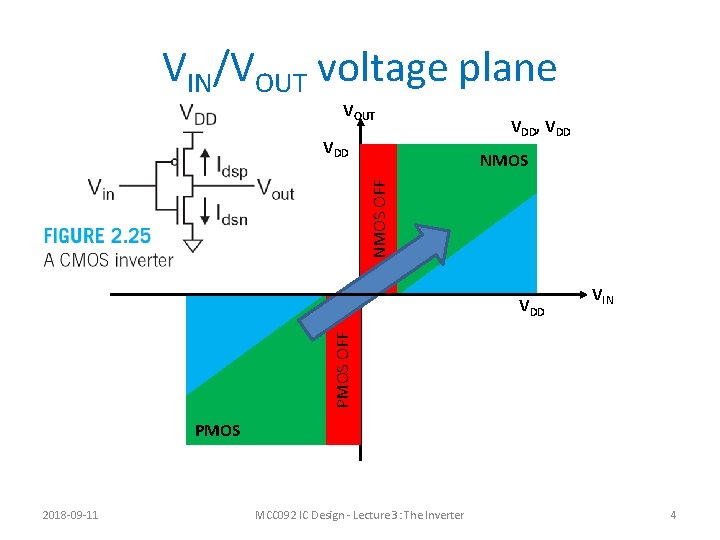

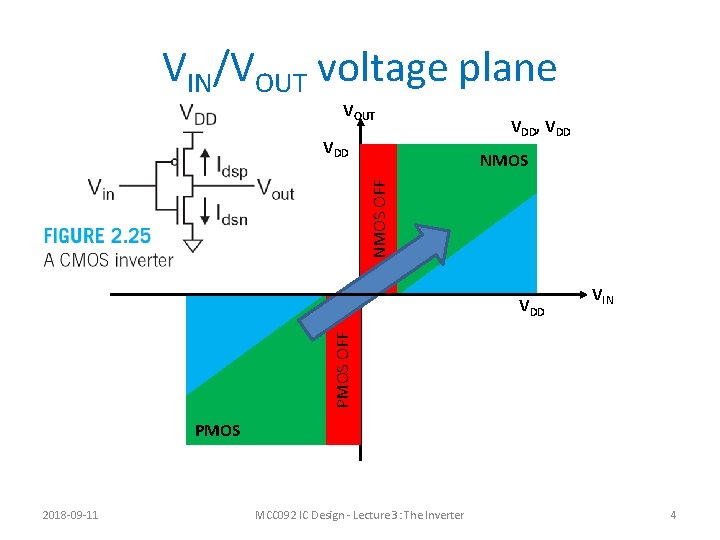

VIN/VOUT voltage plane VOUT VDD, VDD NMOS OFF NMOS VIN PMOS OFF VDD PMOS 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 4

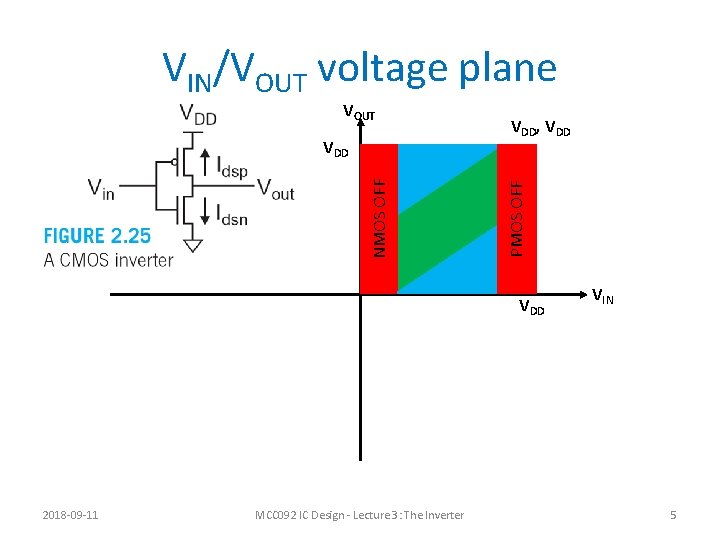

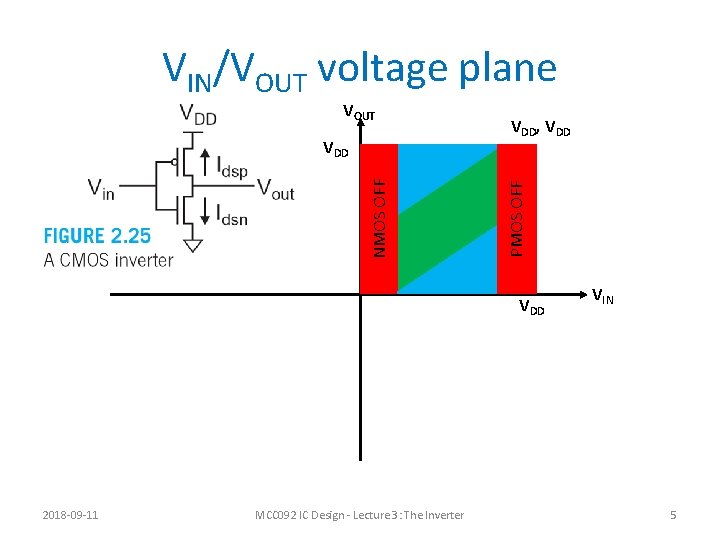

VIN/VOUT voltage plane NMOS OFF VDD, VDD PMOS OFF VOUT VDD 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter VIN 5

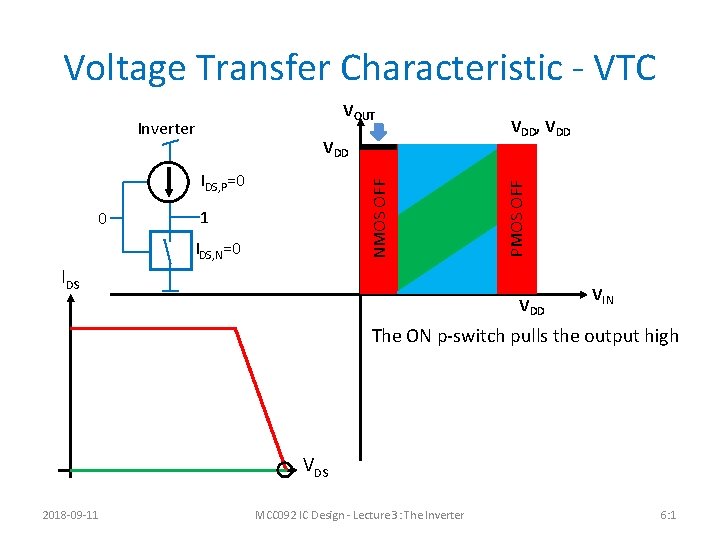

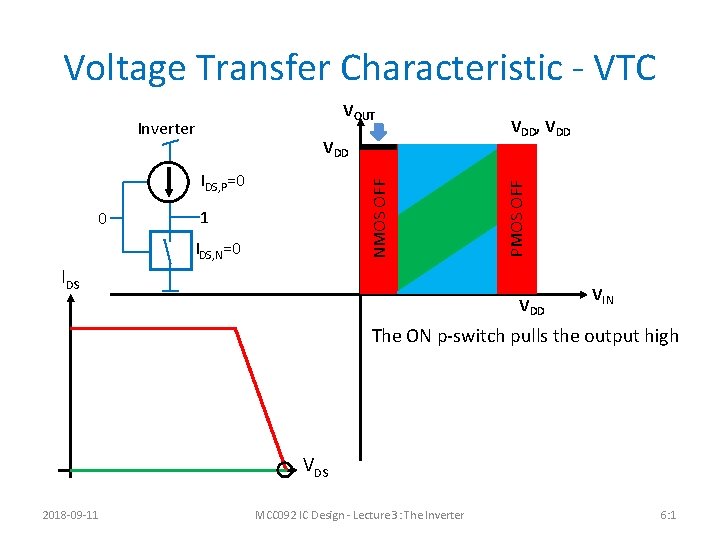

Voltage Transfer Characteristic - VTC Inverter VDD 0 NMOS OFF IDS, P=0 1 IDS, N=0 VDD, VDD PMOS OFF VOUT IDS VDD VIN The ON p-switch pulls the output high VDS 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 6: 1

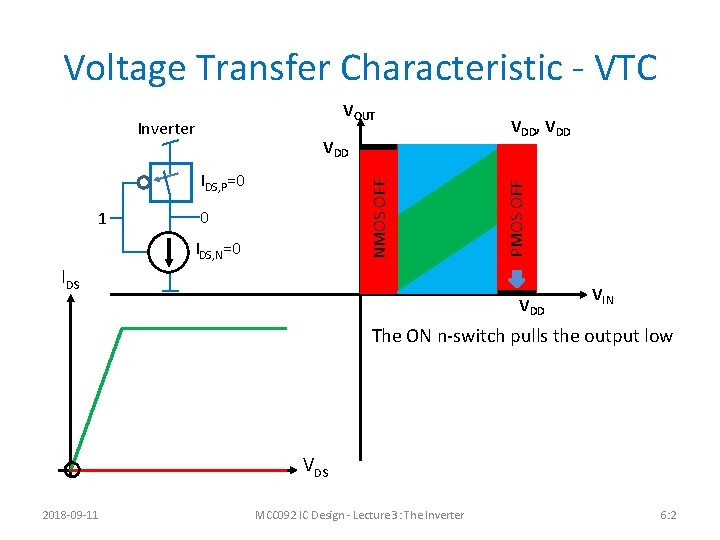

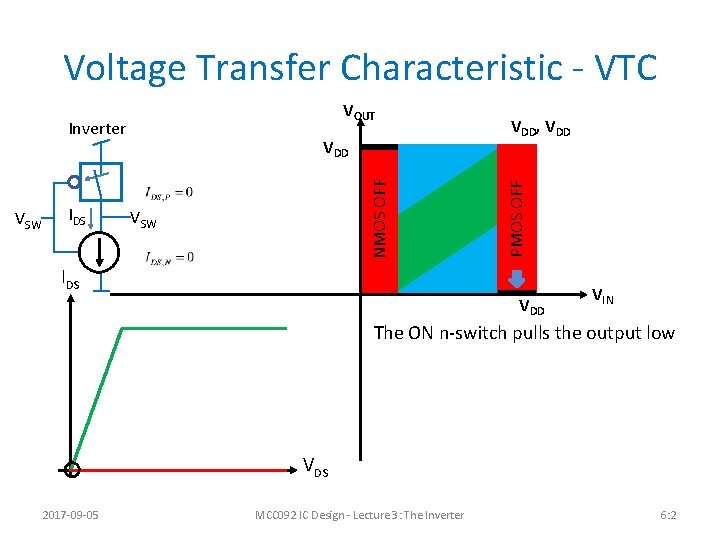

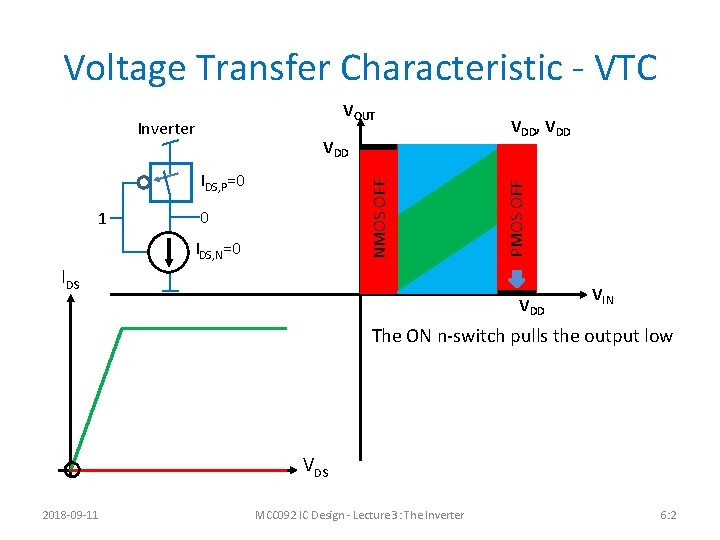

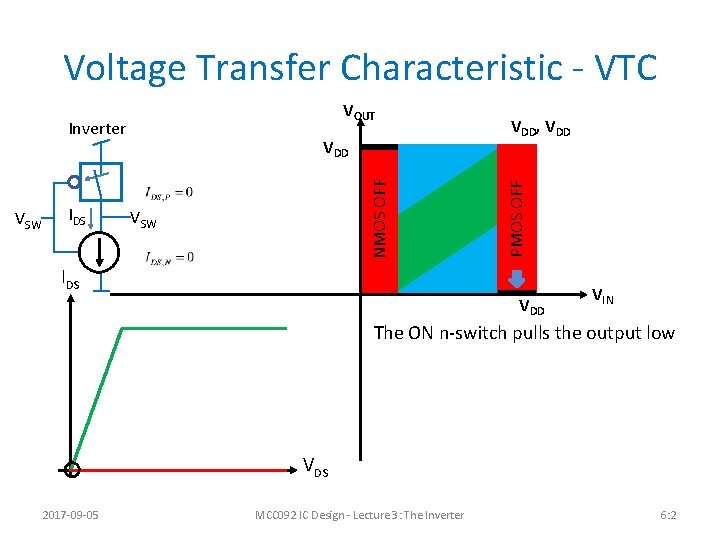

Voltage Transfer Characteristic - VTC Inverter VDD 1 NMOS OFF IDS, P=0 0 IDS, N=0 VDD, VDD PMOS OFF VOUT IDS VDD VIN The ON n-switch pulls the output low VDS 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 6: 2

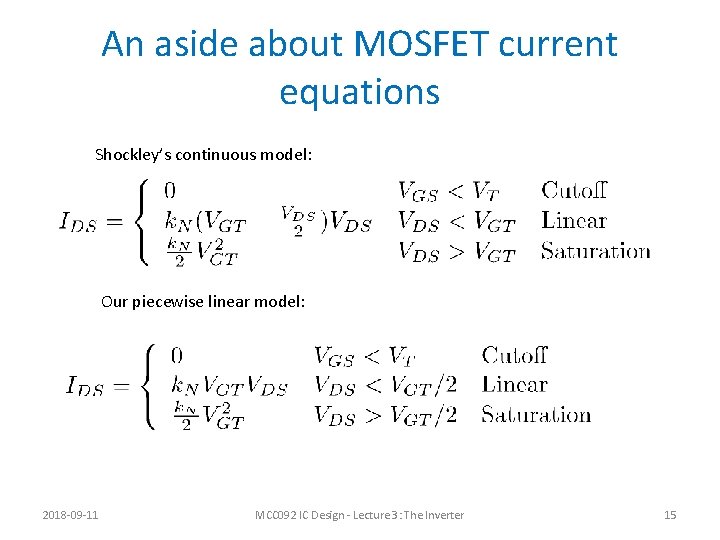

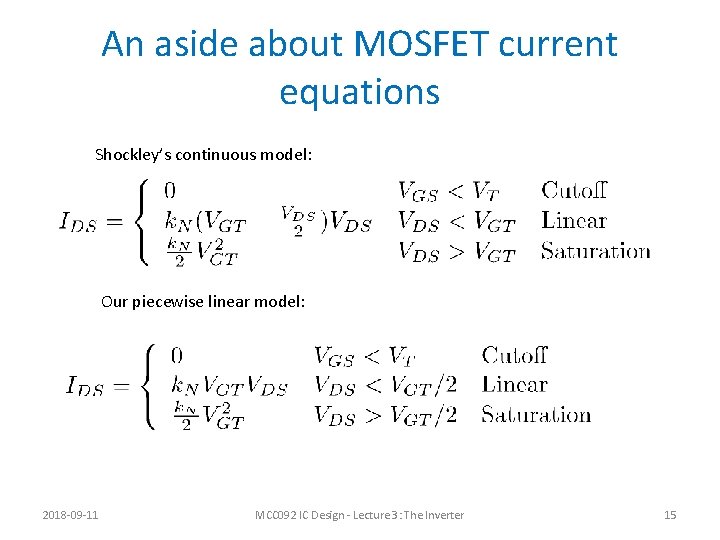

An aside about MOSFET current equations Shockley’s continuous model: Our piecewise linear model: 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 15

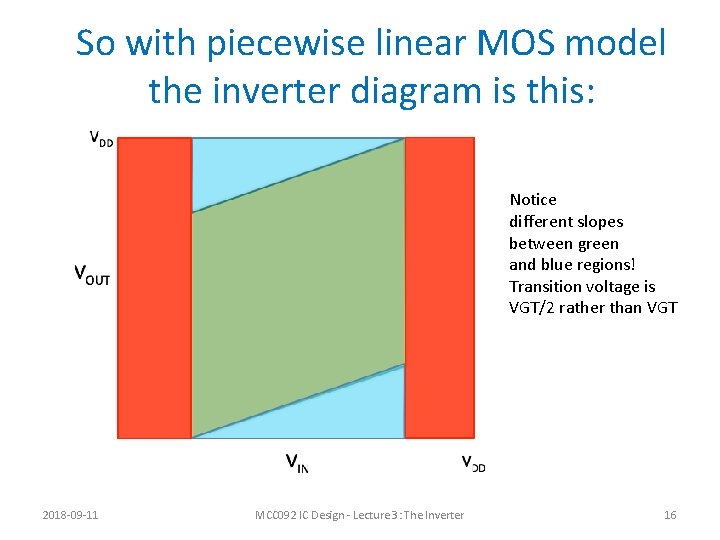

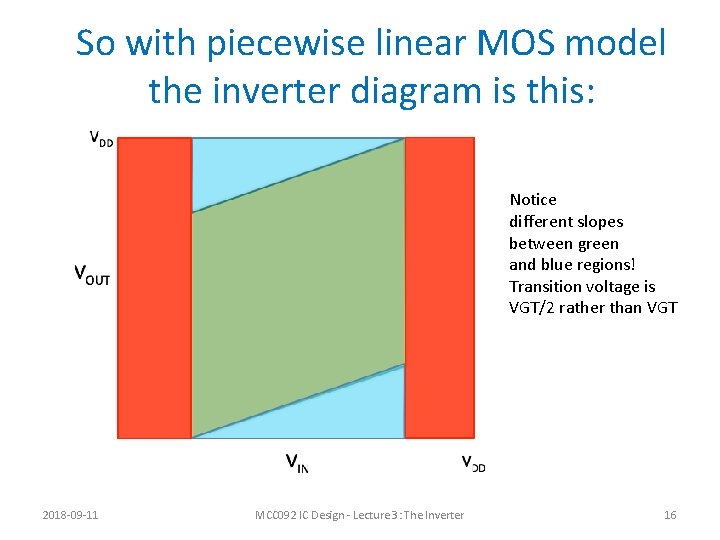

So with piecewise linear MOS model the inverter diagram is this: Notice different slopes between green and blue regions! Transition voltage is VGT/2 rather than VGT 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 16

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN The ON n-switch pulls the output low VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 2

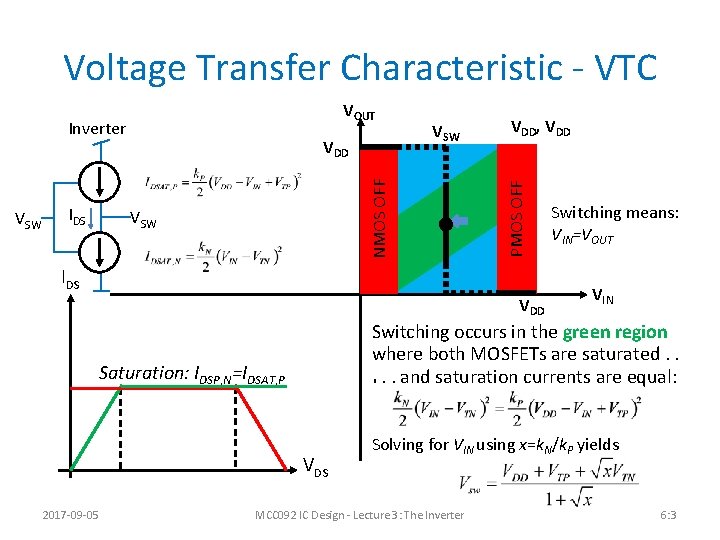

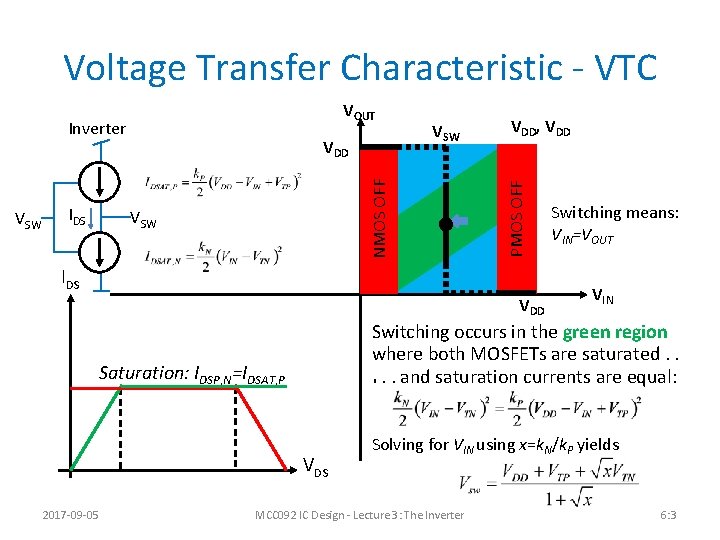

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN Switching occurs in the green region where both MOSFETs are saturated. . . and saturation currents are equal: Saturation: IDSP, N=IDSAT, P VDS 2017 -09 -05 Switching means: VIN=VOUT Solving for VIN using x=k. N/k. P yields MCC 092 IC Design - Lecture 3: The Inverter 6: 3

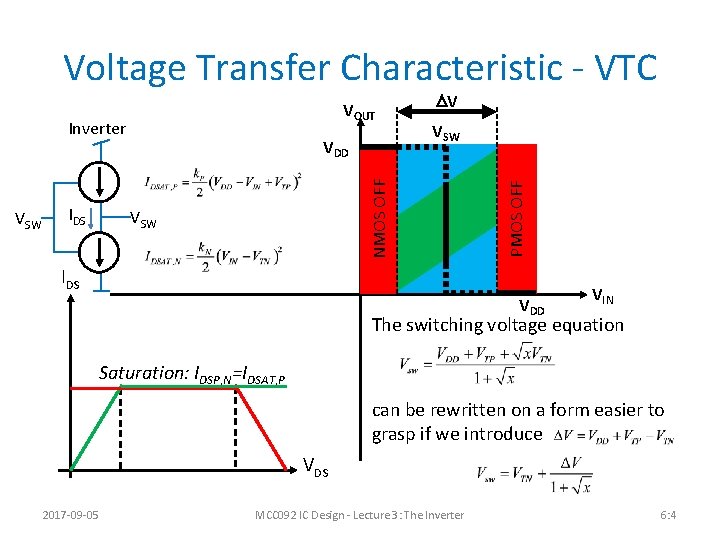

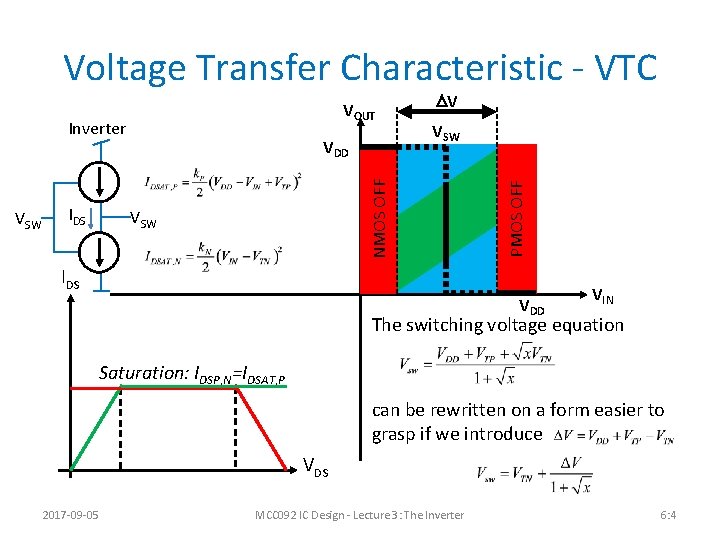

Voltage Transfer Characteristic - VTC Inverter IDS VSW NMOS OFF VSW VDD DV VSW PMOS OFF VOUT IDS VDD VIN The switching voltage equation Saturation: IDSP, N=IDSAT, P can be rewritten on a form easier to grasp if we introduce VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 4

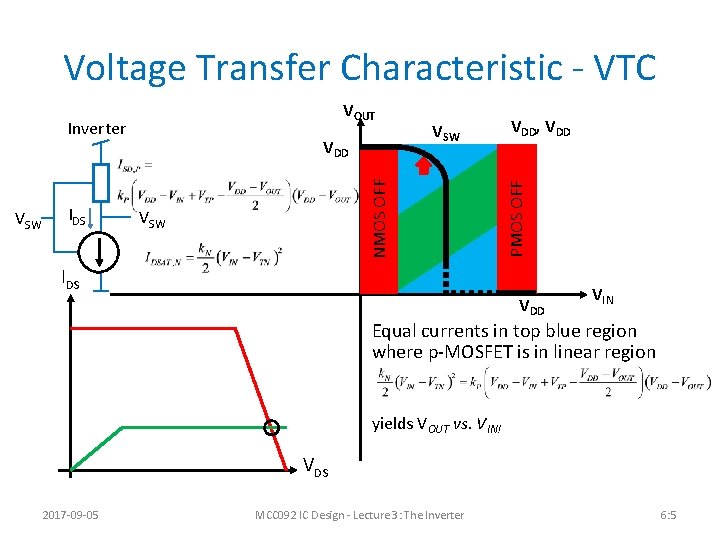

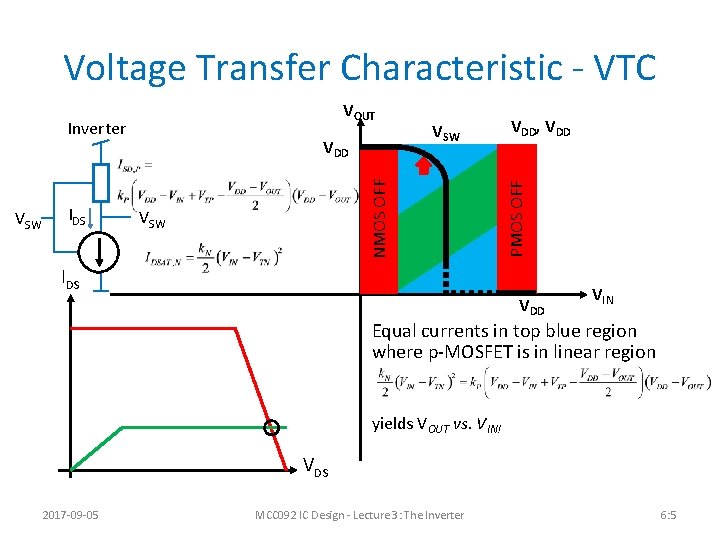

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN Equal currents in top blue region where p-MOSFET is in linear region yields VOUT vs. VIN! VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 5

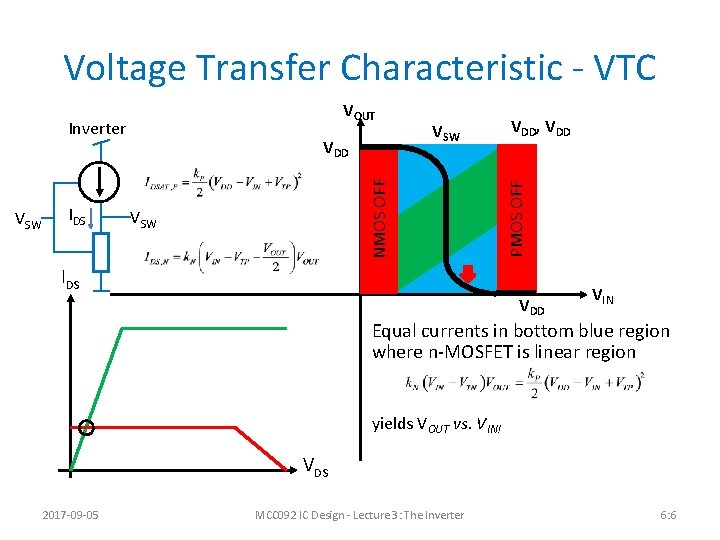

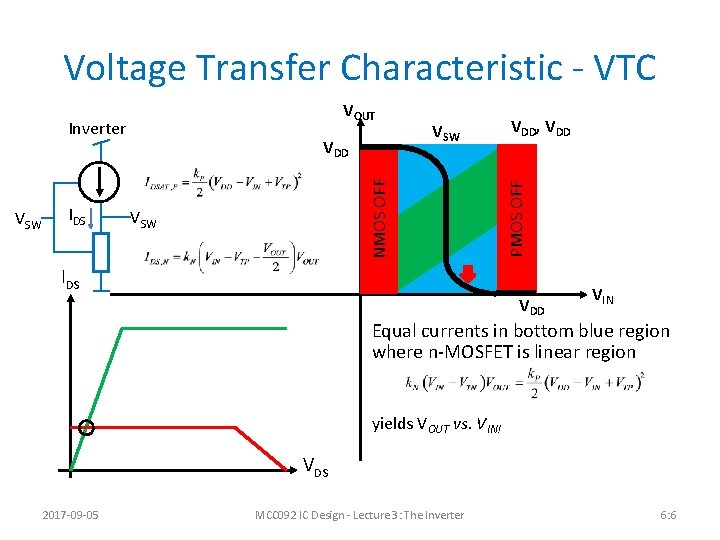

Voltage Transfer Characteristic - VTC Inverter IDS NMOS OFF VSW VDD, VDD PMOS OFF VOUT IDS VDD VIN Equal currents in bottom blue region where n-MOSFET is linear region yields VOUT vs. VIN! VDS 2017 -09 -05 MCC 092 IC Design - Lecture 3: The Inverter 6: 6

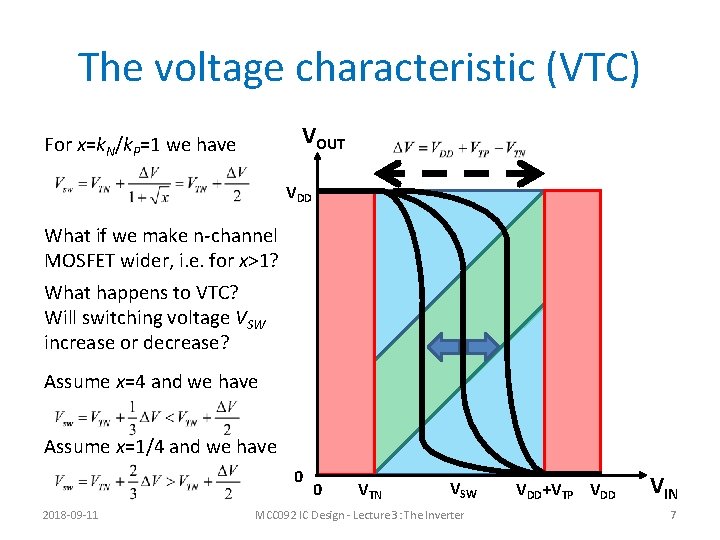

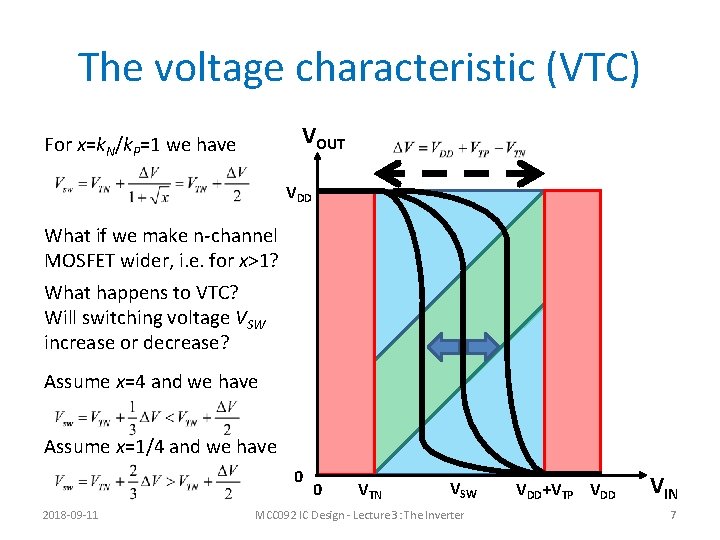

The voltage characteristic (VTC) VOUT For x=k. N/k. P=1 we have VDD What if we make n-channel MOSFET wider, i. e. for x>1? What happens to VTC? Will switching voltage VSW increase or decrease? Assume x=4 and we have Assume x=1/4 and we have 0 2018 -09 -11 0 VTN VSW MCC 092 IC Design - Lecture 3: The Inverter VDD+VTP VDD VIN 7

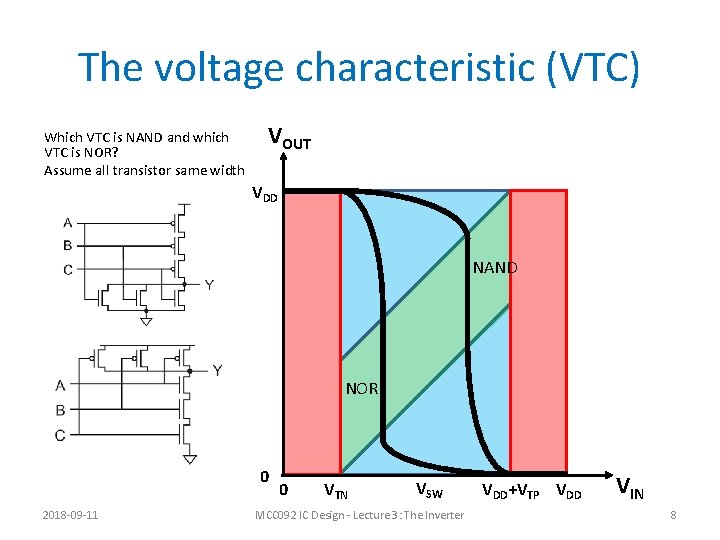

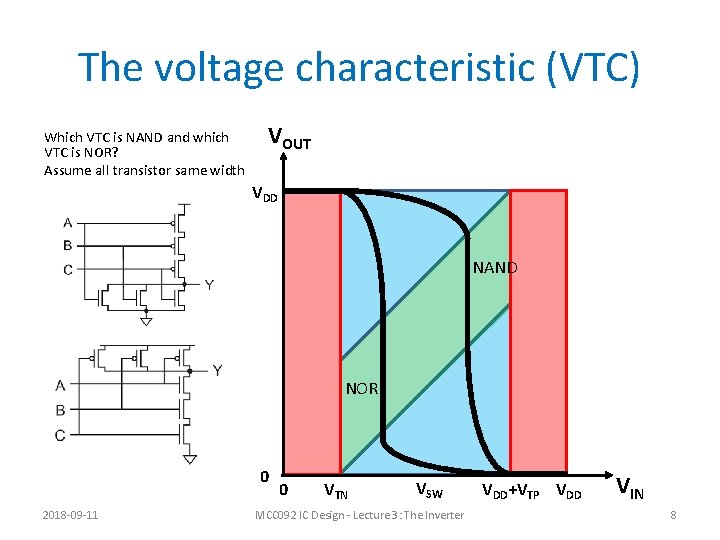

The voltage characteristic (VTC) Which VTC is NAND and which VTC is NOR? Assume all transistor same width VOUT VDD NAND NOR 0 2018 -09 -11 0 VTN VSW MCC 092 IC Design - Lecture 3: The Inverter VDD+VTP VDD VIN 8

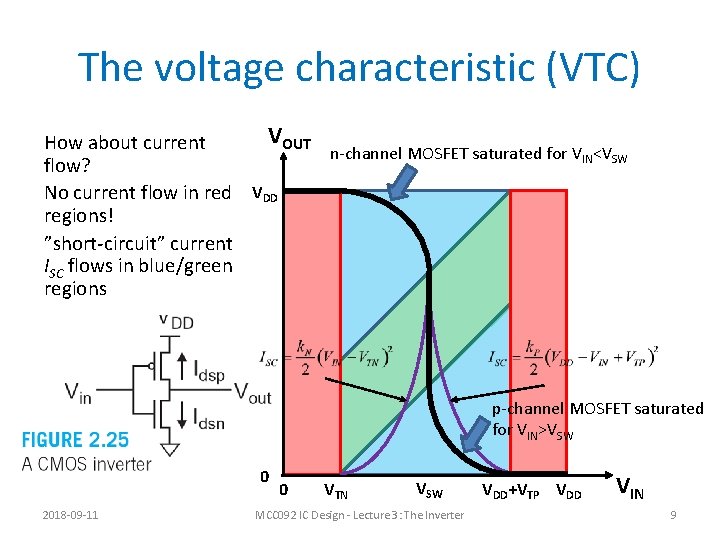

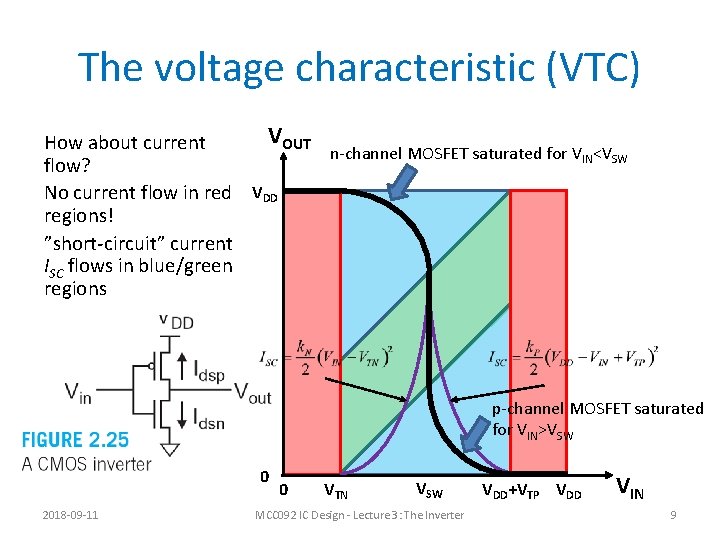

The voltage characteristic (VTC) VOUT How about current n-channel MOSFET saturated for VIN<VSW flow? No current flow in red VDD regions! ”short-circuit” current ISC flows in blue/green regions p-channel MOSFET saturated for VIN>VSW 0 2018 -09 -11 0 VTN VSW MCC 092 IC Design - Lecture 3: The Inverter VDD+VTP VDD VIN 9

Noise margins • What are they? • Why are they important? Answers the question: How much noise can the circuit tolerate? 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 25

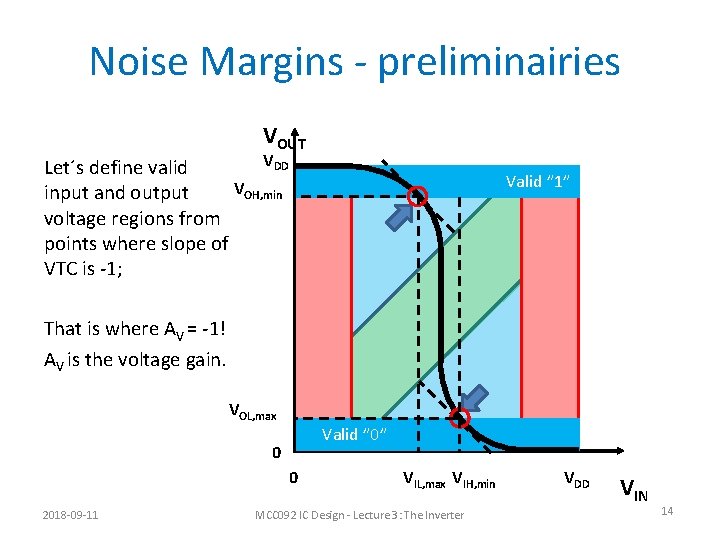

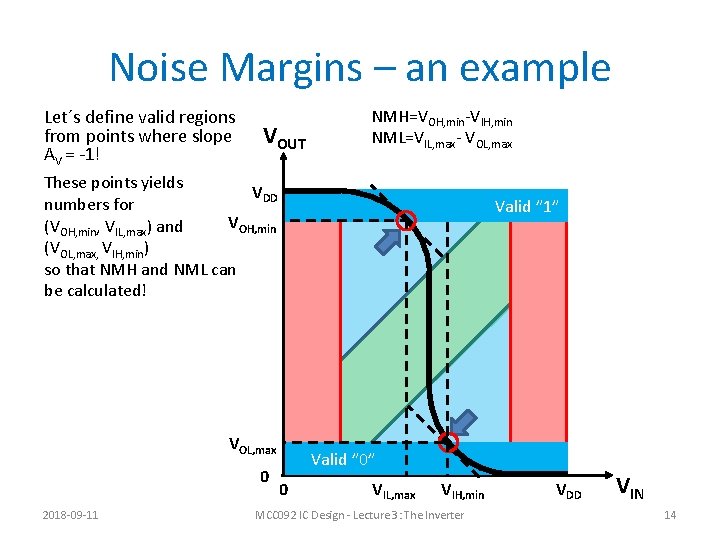

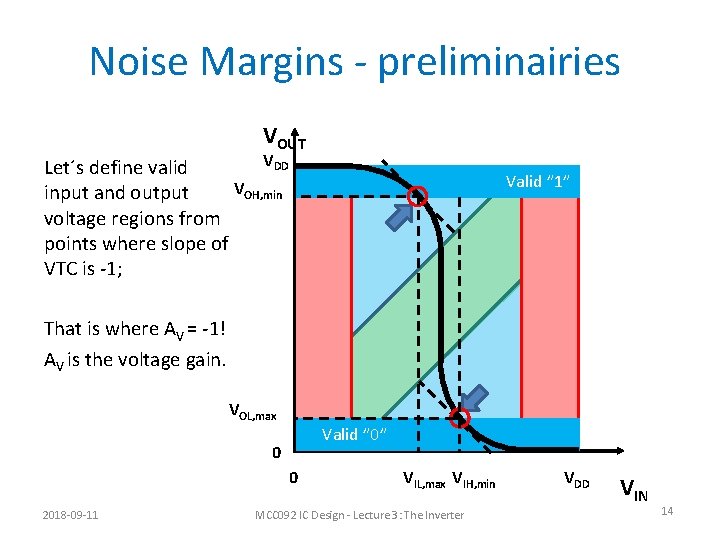

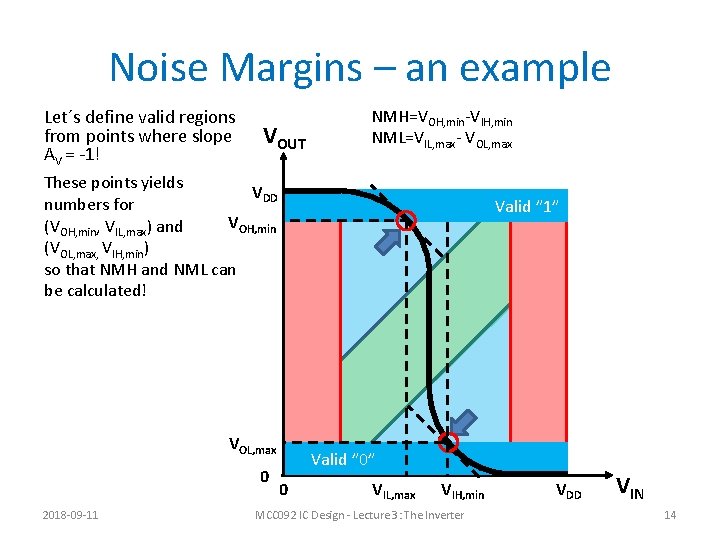

Noise Margins - preliminairies VOUT VDD Let´s define valid VOH, min input and output voltage regions from points where slope of VTC is -1; Valid ” 1” That is where AV = -1! AV is the voltage gain. VOL, max Valid ” 0” 0 0 2018 -09 -11 VIL, max VIH, min MCC 092 IC Design - Lecture 3: The Inverter VDD VIN 14

Noise margins - NMH VDD Valid ” 1” VDD VIN VOUT VOH, min VIL, max Valid ” 1” Valid ” 0” VIN not valid NMH VOL, max Valid ” 0” VIL, max 2018 -09 -11 VIH, min VIN MCC 092 IC Design - Lecture 3: The Inverter 10 VOUT 0

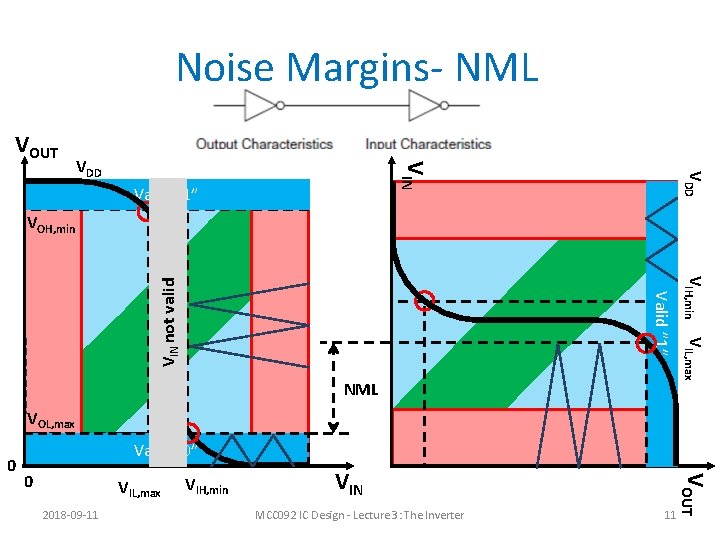

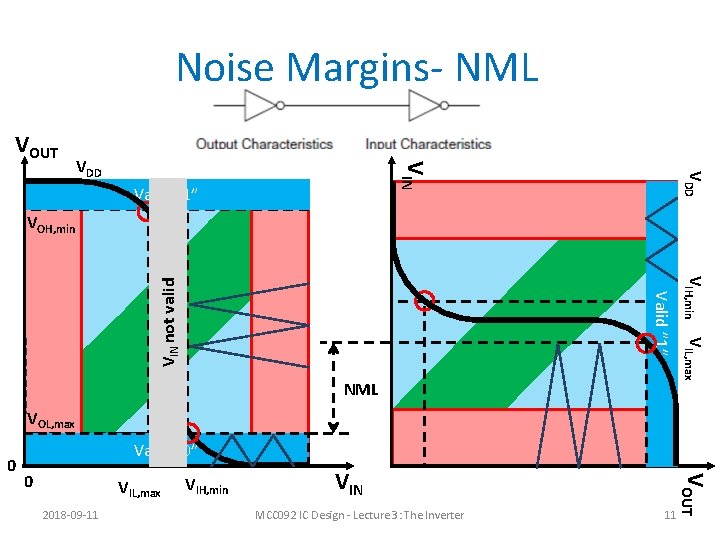

Noise Margins- NML VDD Valid ” 1” VDD VIN VOUT VIL, max NML VIH, min Valid ” 1” VIN not valid VOH, min VOL, max 0 VIL, max 2018 -09 -11 VIH, min VIN MCC 092 IC Design - Lecture 3: The Inverter 11 VOUT 0 Valid ” 0”

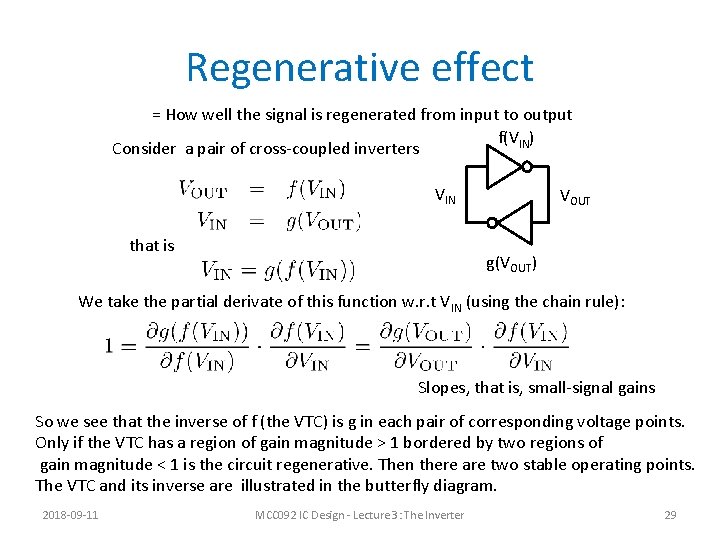

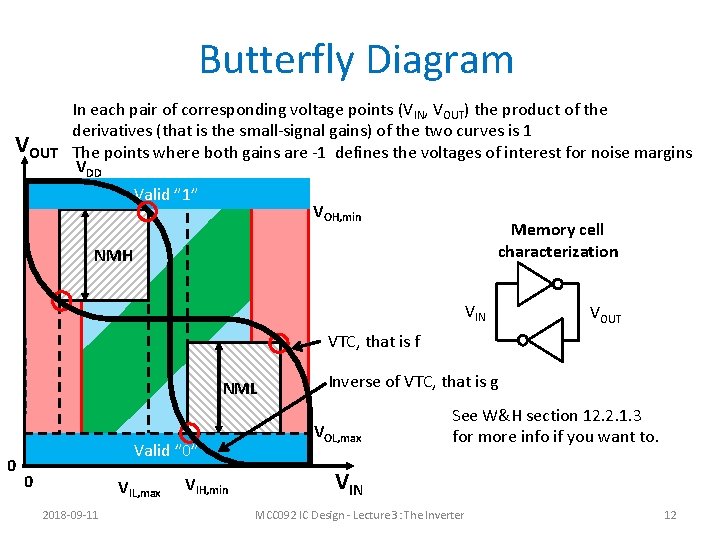

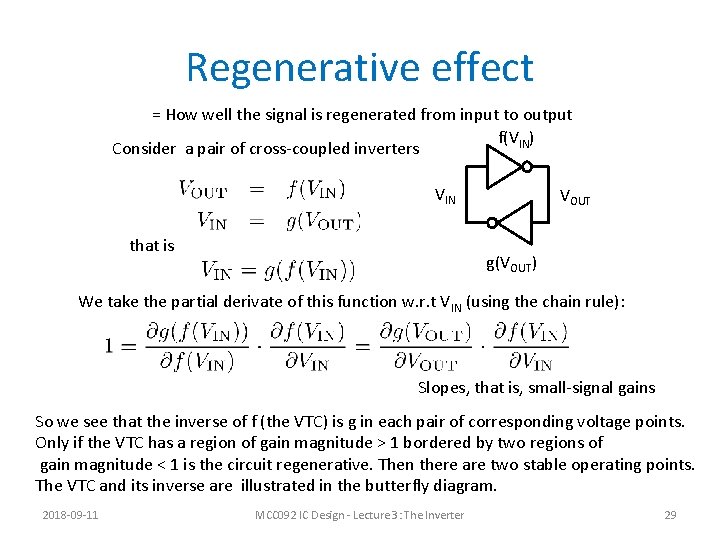

Regenerative effect = How well the signal is regenerated from input to output f(VIN) Consider a pair of cross-coupled inverters VIN that is VOUT g(VOUT) We take the partial derivate of this function w. r. t VIN (using the chain rule): Slopes, that is, small-signal gains So we see that the inverse of f (the VTC) is g in each pair of corresponding voltage points. Only if the VTC has a region of gain magnitude > 1 bordered by two regions of gain magnitude < 1 is the circuit regenerative. Then there are two stable operating points. The VTC and its inverse are illustrated in the butterfly diagram. 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 29

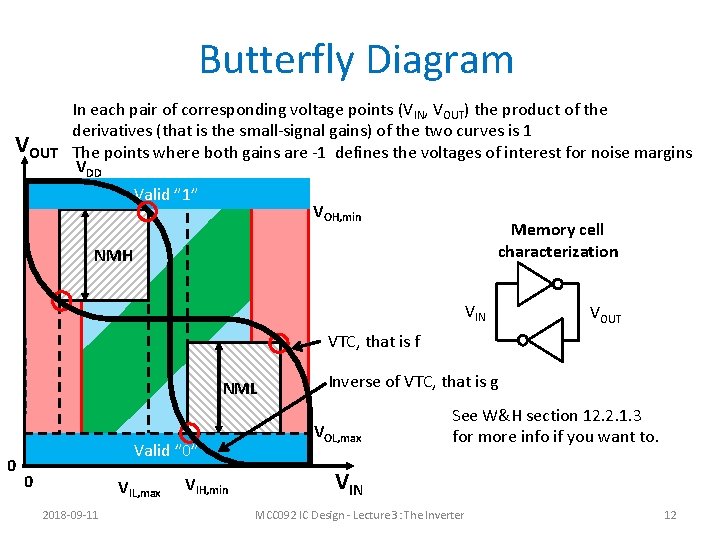

Butterfly Diagram In each pair of corresponding voltage points (VIN, VOUT) the product of the derivatives (that is the small-signal gains) of the two curves is 1 VOUT The points where both gains are -1 defines the voltages of interest for noise margins VDD Valid ” 1” VOH, min Memory cell characterization NMH VIN VOUT VTC, that is f NML 0 Valid ” 0” 0 VIL, max 2018 -09 -11 VIH, min Inverse of VTC, that is g VOL, max See W&H section 12. 2. 1. 3 for more info if you want to. VIN MCC 092 IC Design - Lecture 3: The Inverter 12

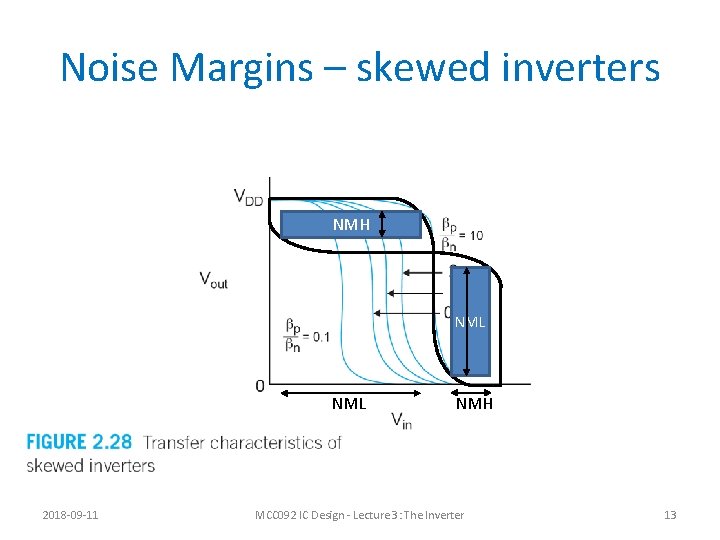

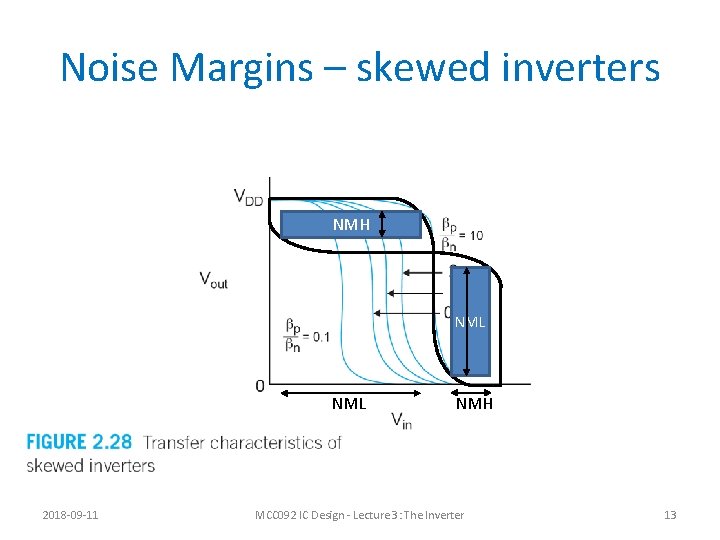

Noise Margins – skewed inverters NMH NML 2018 -09 -11 NMH MCC 092 IC Design - Lecture 3: The Inverter 13

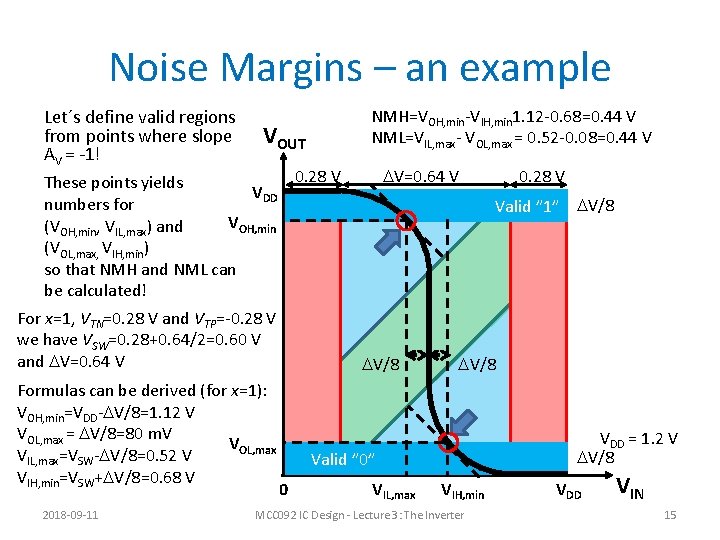

Noise Margins – an example Let´s define valid regions from points where slope AV = -1! VOUT NMH=VOH, min-VIH, min NML=VIL, max- VOL, max These points yields VDD numbers for VOH, min (VOH, min, VIL, max) and (VOL, max, VIH, min) so that NMH and NML can be calculated! Valid ” 1” VOL, max 0 2018 -09 -11 Valid ” 0” 0 VIL, max VIH, min MCC 092 IC Design - Lecture 3: The Inverter VDD VIN 14

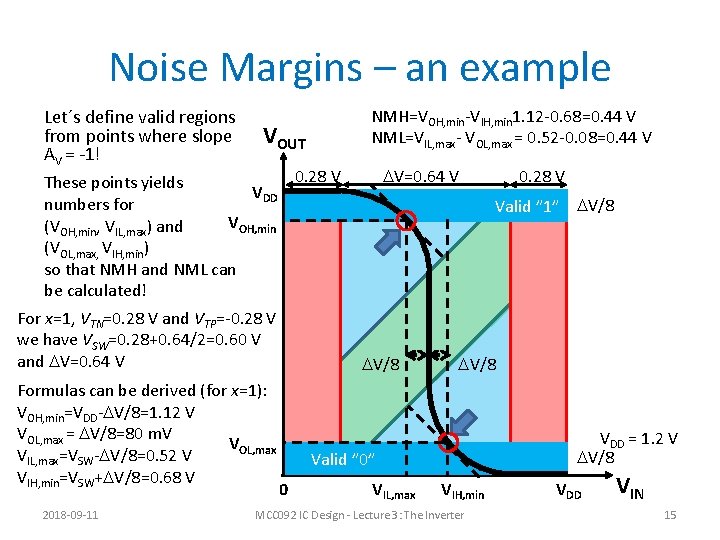

Noise Margins – an example Let´s define valid regions from points where slope AV = -1! NMH=VOH, min-VIH, min 1. 12 -0. 68=0. 44 V NML=VIL, max- VOL, max = 0. 52 -0. 08=0. 44 V VOUT DV=0. 64 V 0. 28 V These points yields VDD numbers for VOH, min (VOH, min, VIL, max) and (VOL, max, VIH, min) so that NMH and NML can be calculated! For x=1, VTN=0. 28 V and VTP=-0. 28 V we have VSW=0. 28+0. 64/2=0. 60 V and DV=0. 64 V Formulas can be derived (for x=1): VOH, min=VDD-DV/8=1. 12 -DV/8 V VOL, max = DV/8=80 DV/8 m. V VOL, max VIL, max=VSW-DV/8=0. 52 -DV/8 V 0 VIH, min=VSW+DV/8=0. 68 +DV/8 V 2018 -09 -11 Valid ” 1” DV/8 VDD = 1. 2 V DV/8 Valid ” 0” 0 0. 28 V VIL, max VIH, min MCC 092 IC Design - Lecture 3: The Inverter VDD VIN 15

What about lab 1 • Calculate VSW and find from simulation in lab • Calculate noise margins and find from simulation 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 34

Summary • CMOS inverter – schematic • Voltage transfer characteristics (VTC) – Regions of operation – How to calculate switching voltage VSW – VSW dependence on k. N/k. P (that is, transistor widths) – Understand switching current (ISC) flow • Noise margins: NMH and NML – Why important? – Definition – Butterfly diagram 2018 -09 -11 MCC 092 IC Design - Lecture 3: The Inverter 16