UNIT V CMOS LOGIC CMOS logic levels MOS

- Slides: 22

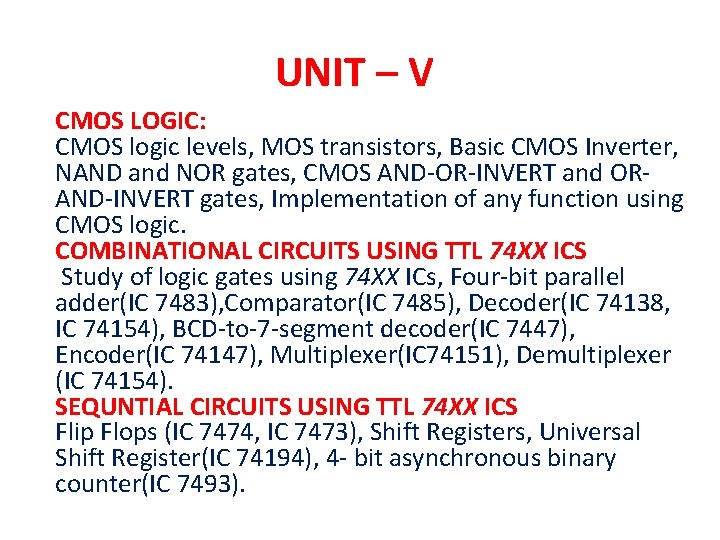

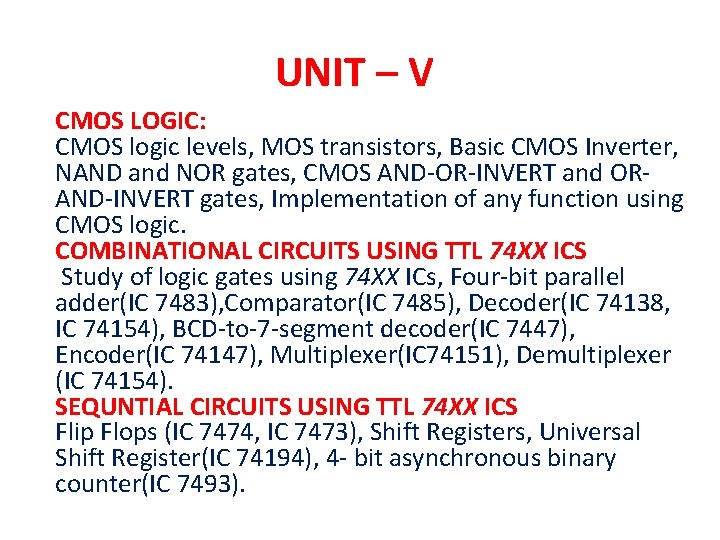

UNIT – V CMOS LOGIC: CMOS logic levels, MOS transistors, Basic CMOS Inverter, NAND and NOR gates, CMOS AND-OR-INVERT and ORAND-INVERT gates, Implementation of any function using CMOS logic. COMBINATIONAL CIRCUITS USING TTL 74 XX ICS Study of logic gates using 74 XX ICs, Four-bit parallel adder(IC 7483), Comparator(IC 7485), Decoder(IC 74138, IC 74154), BCD-to-7 -segment decoder(IC 7447), Encoder(IC 74147), Multiplexer(IC 74151), Demultiplexer (IC 74154). SEQUNTIAL CIRCUITS USING TTL 74 XX ICS Flip Flops (IC 7474, IC 7473), Shift Registers, Universal Shift Register(IC 74194), 4 - bit asynchronous binary counter(IC 7493).

CMOS LOGIC • • CMOS logic levels MOS transistors Basic CMOS Inverter NAND and NOR gates CMOS AND-OR-INVERT OR-AND-INVERT gates Implementation of any function using CMOS logic

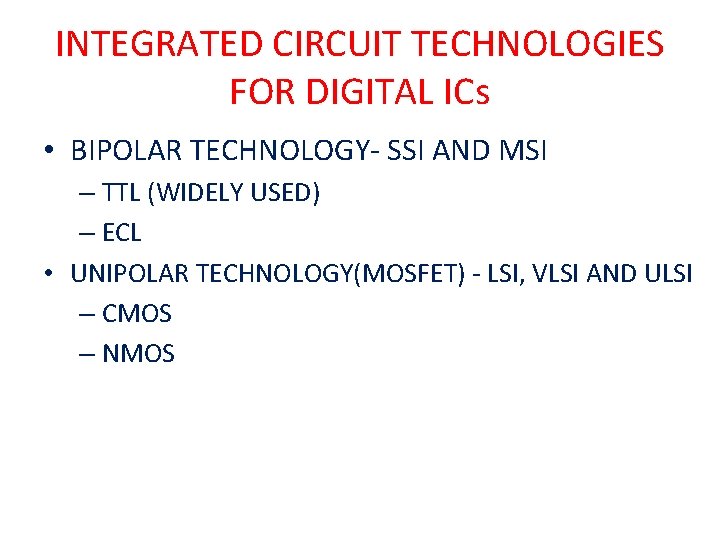

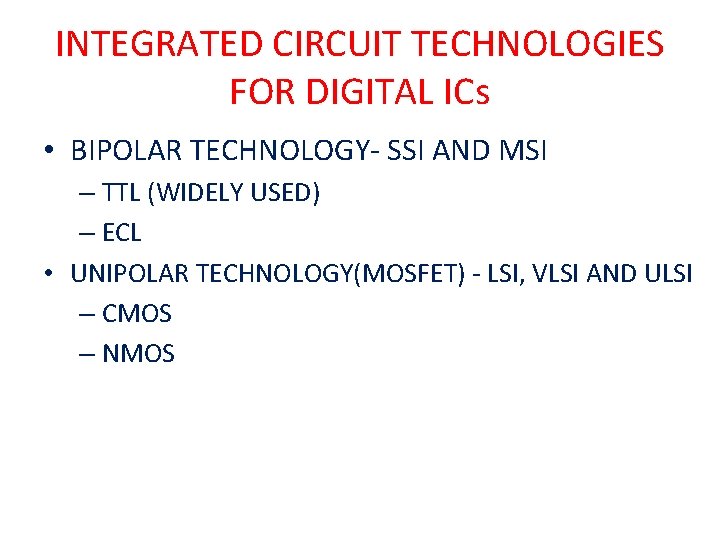

INTEGRATED CIRCUIT TECHNOLOGIES FOR DIGITAL ICs • BIPOLAR TECHNOLOGY- SSI AND MSI – TTL (WIDELY USED) – ECL • UNIPOLAR TECHNOLOGY(MOSFET) - LSI, VLSI AND ULSI – CMOS – NMOS

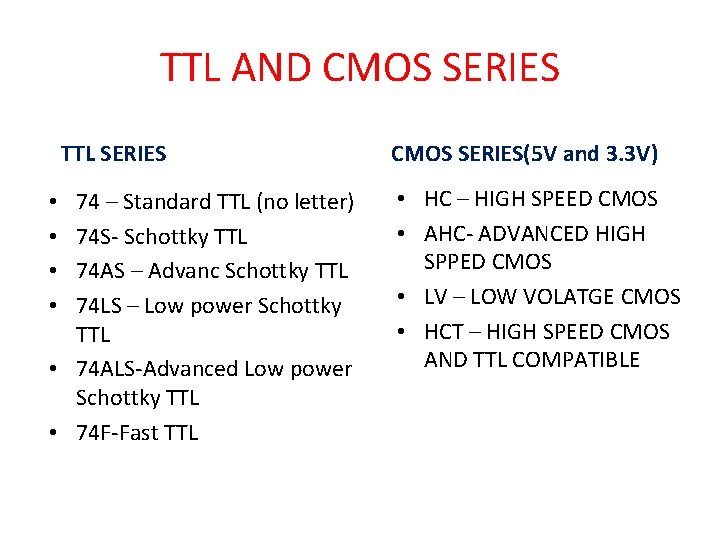

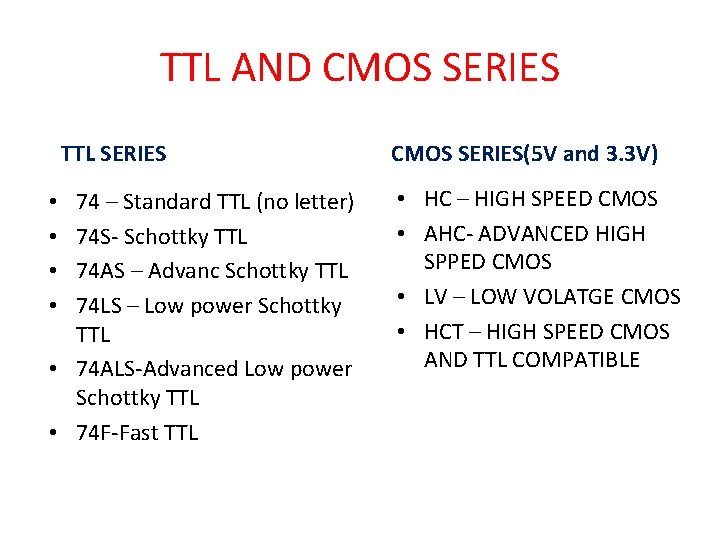

TTL AND CMOS SERIES TTL SERIES 74 – Standard TTL (no letter) 74 S- Schottky TTL 74 AS – Advanc Schottky TTL 74 LS – Low power Schottky TTL • 74 ALS-Advanced Low power Schottky TTL • 74 F-Fast TTL • • CMOS SERIES(5 V and 3. 3 V) • HC – HIGH SPEED CMOS • AHC- ADVANCED HIGH SPPED CMOS • LV – LOW VOLATGE CMOS • HCT – HIGH SPEED CMOS AND TTL COMPATIBLE

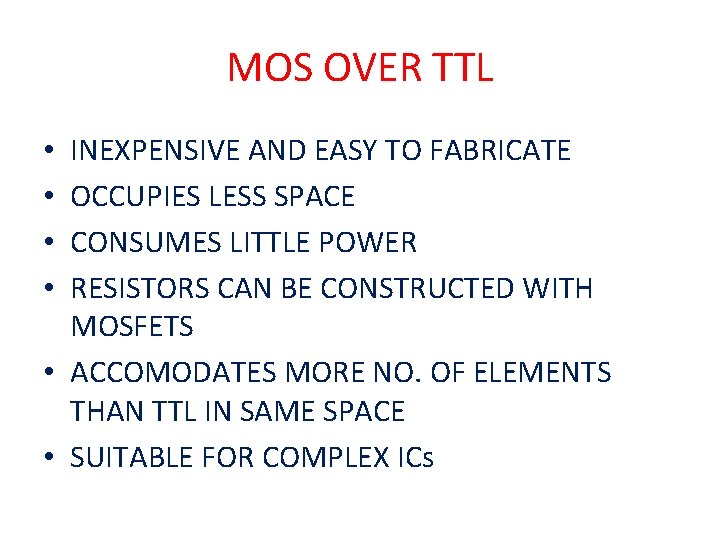

MOS OVER TTL INEXPENSIVE AND EASY TO FABRICATE OCCUPIES LESS SPACE CONSUMES LITTLE POWER RESISTORS CAN BE CONSTRUCTED WITH MOSFETS • ACCOMODATES MORE NO. OF ELEMENTS THAN TTL IN SAME SPACE • SUITABLE FOR COMPLEX ICs • •

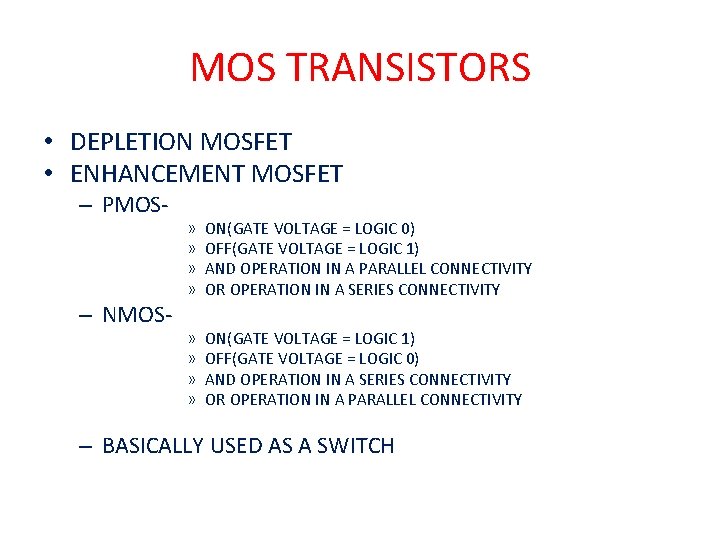

MOS TRANSISTORS • DEPLETION MOSFET • ENHANCEMENT MOSFET – PMOS- – NMOS- » » ON(GATE VOLTAGE = LOGIC 0) OFF(GATE VOLTAGE = LOGIC 1) AND OPERATION IN A PARALLEL CONNECTIVITY OR OPERATION IN A SERIES CONNECTIVITY » » ON(GATE VOLTAGE = LOGIC 1) OFF(GATE VOLTAGE = LOGIC 0) AND OPERATION IN A SERIES CONNECTIVITY OR OPERATION IN A PARALLEL CONNECTIVITY – BASICALLY USED AS A SWITCH

MOS TRANSISTORS • NMOS • PMOS • CMOS

NMOS OVER PMOS • PACKAGE DENSITY IS MORE • ABOUT THREE TIMES FASTER • MOSTLY MEMORIES, PROCESSORS AND PERIPHERAL DEVICES ARE AVALIABLE IN NMOS • PMOS AND NMOS ARE ECONOMICAL THAN CMOS

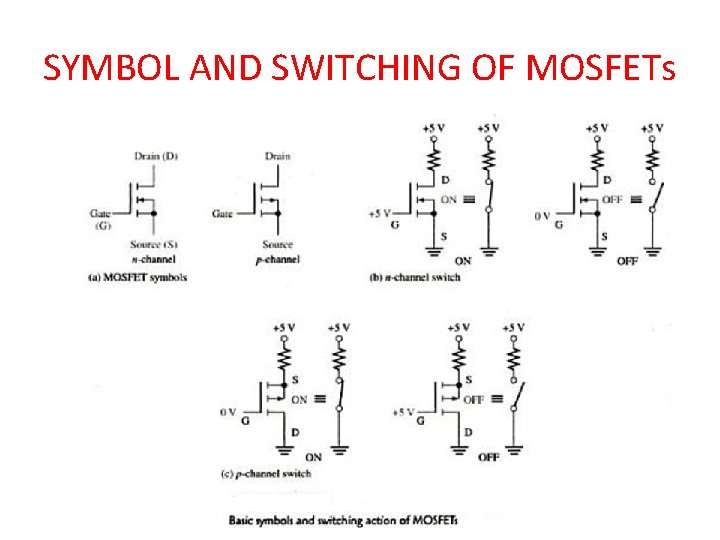

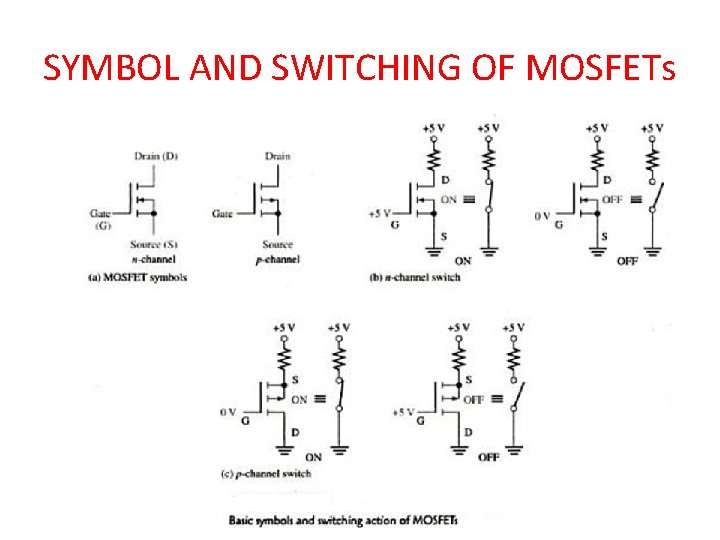

SYMBOL AND SWITCHING OF MOSFETs

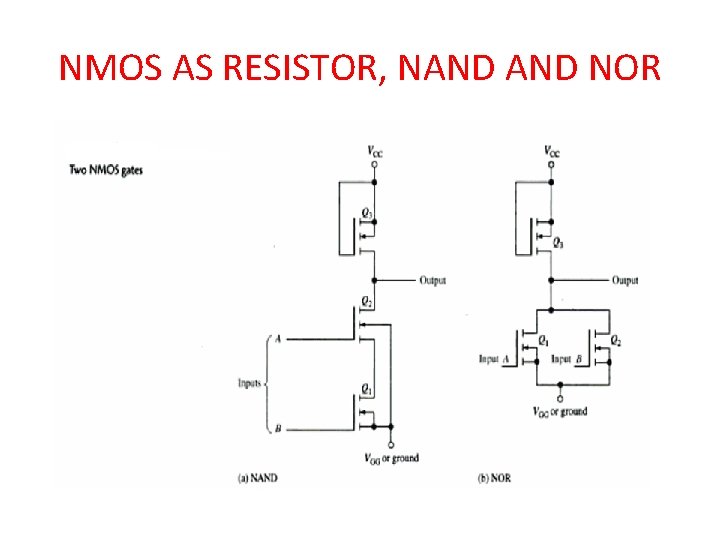

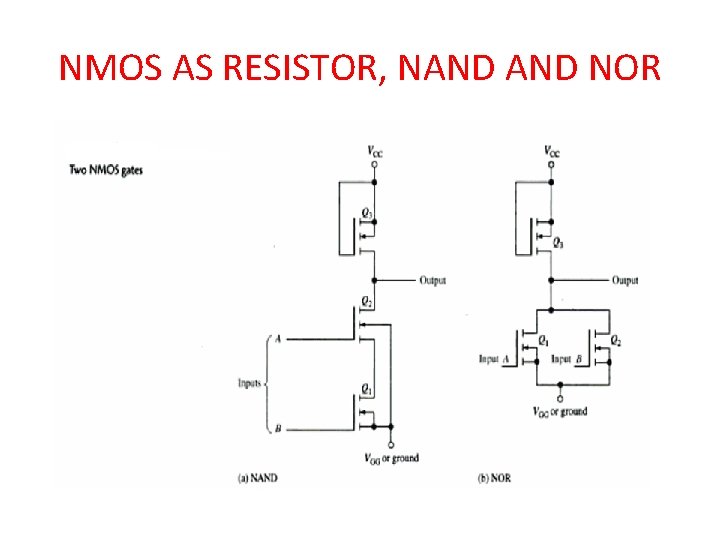

NMOS AS RESISTOR, NAND NOR

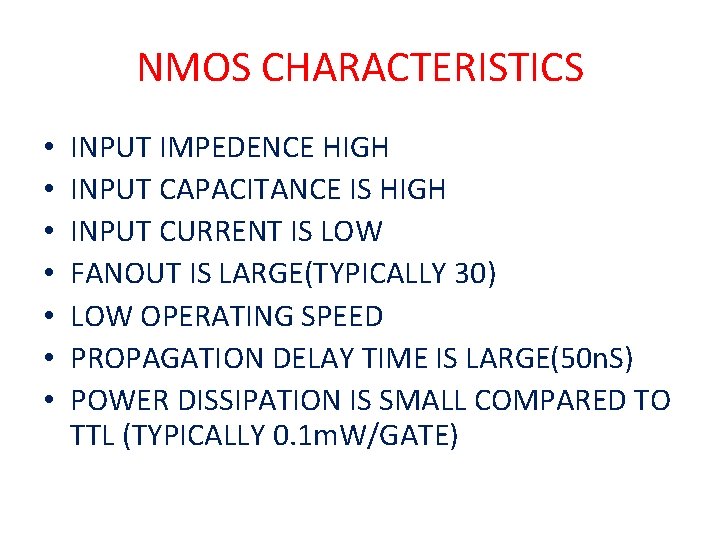

NMOS CHARACTERISTICS • • INPUT IMPEDENCE HIGH INPUT CAPACITANCE IS HIGH INPUT CURRENT IS LOW FANOUT IS LARGE(TYPICALLY 30) LOW OPERATING SPEED PROPAGATION DELAY TIME IS LARGE(50 n. S) POWER DISSIPATION IS SMALL COMPARED TO TTL (TYPICALLY 0. 1 m. W/GATE)

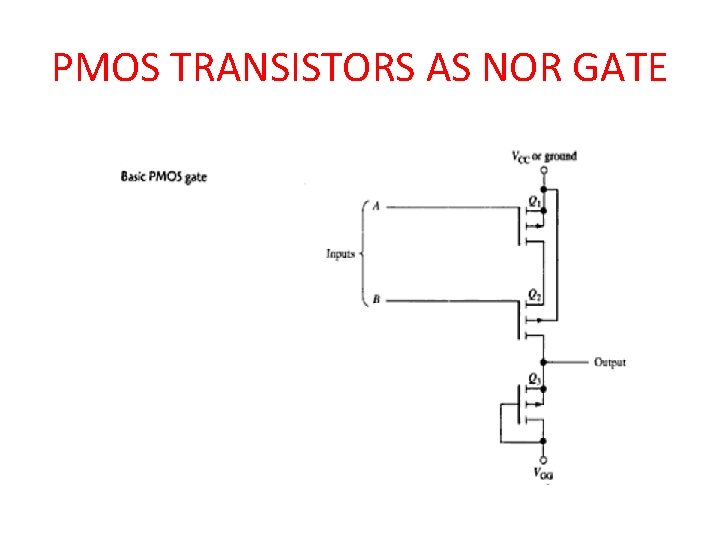

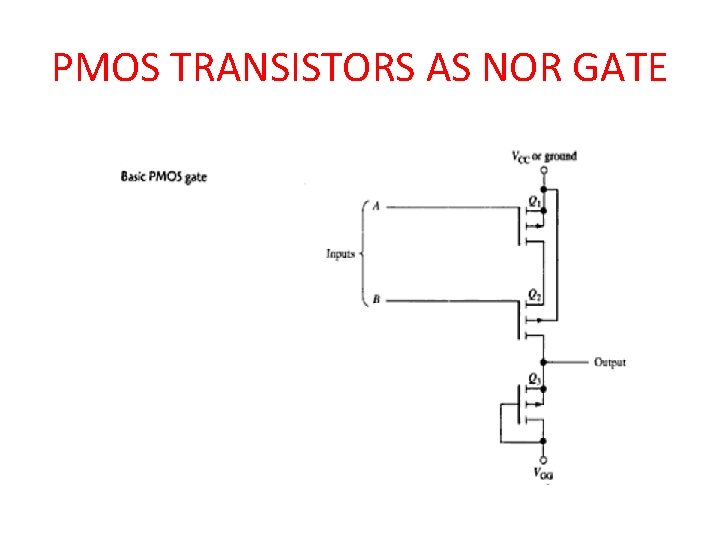

PMOS TRANSISTORS AS NOR GATE

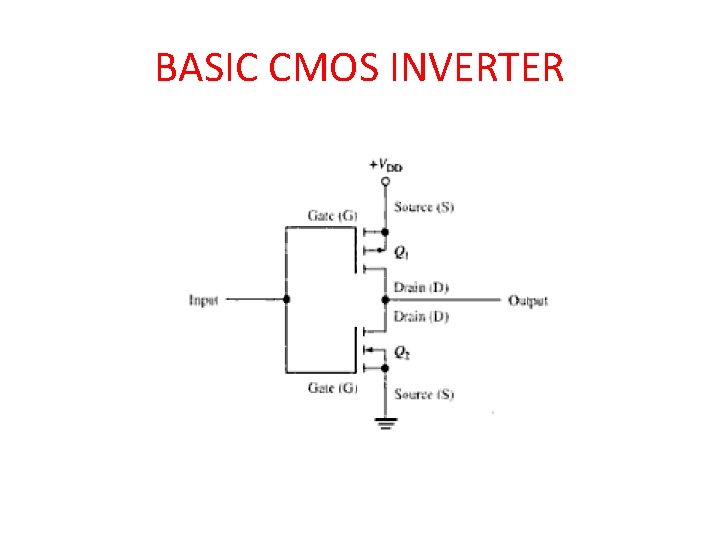

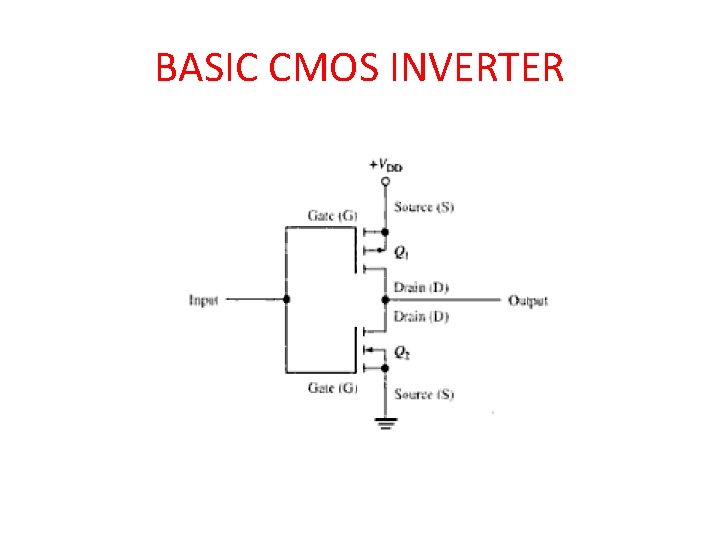

BASIC CMOS INVERTER

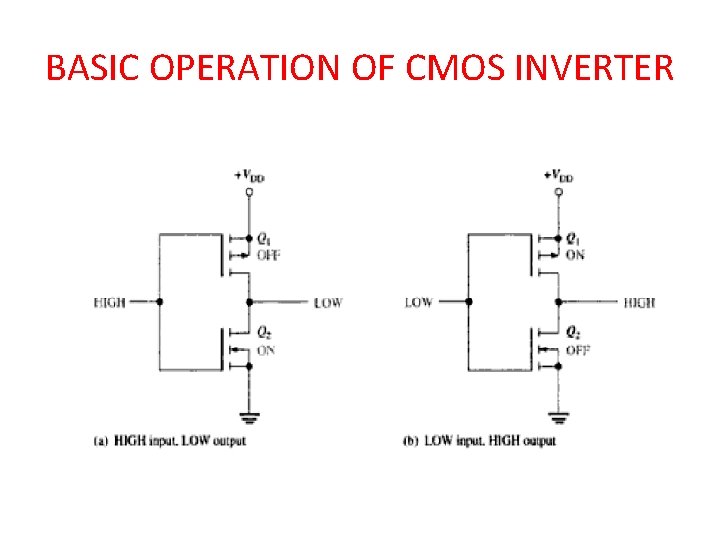

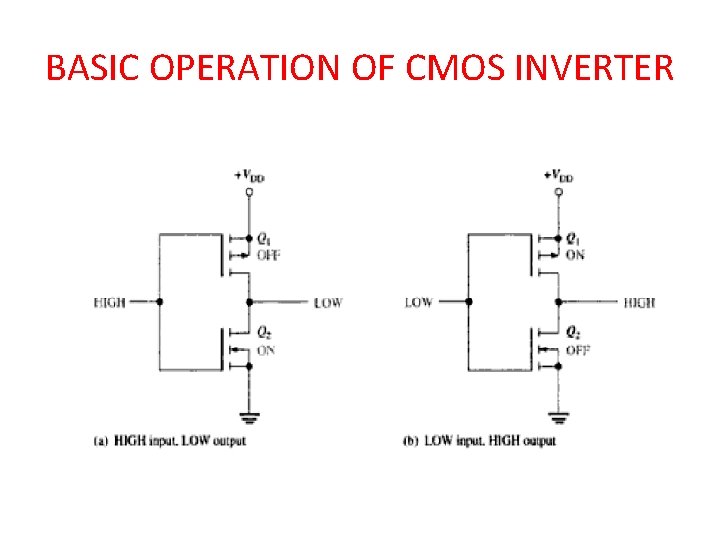

BASIC OPERATION OF CMOS INVERTER

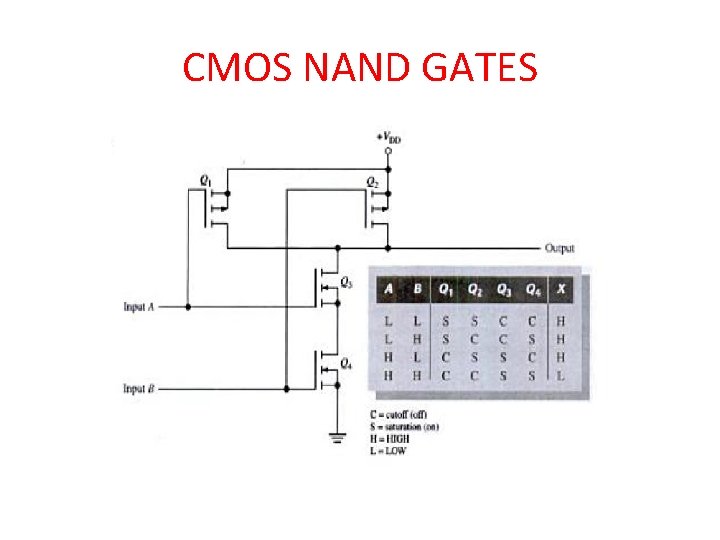

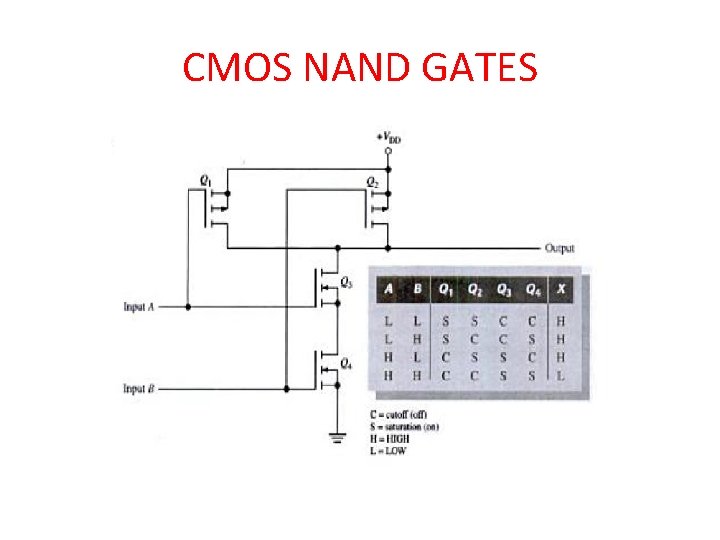

CMOS NAND GATES

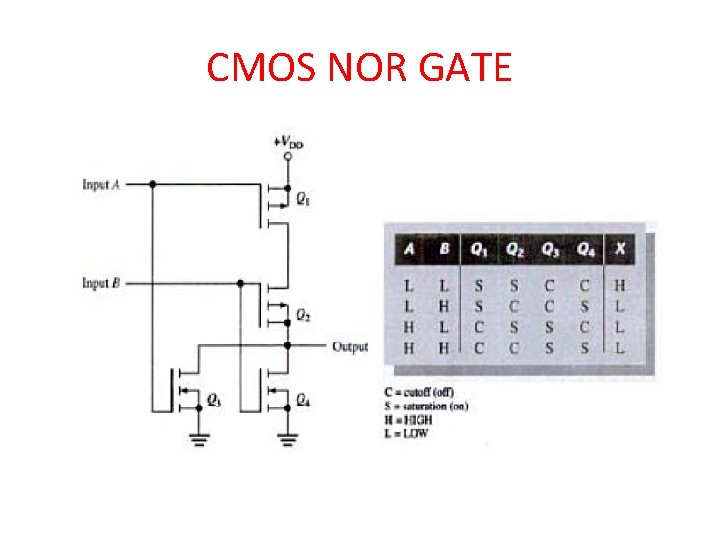

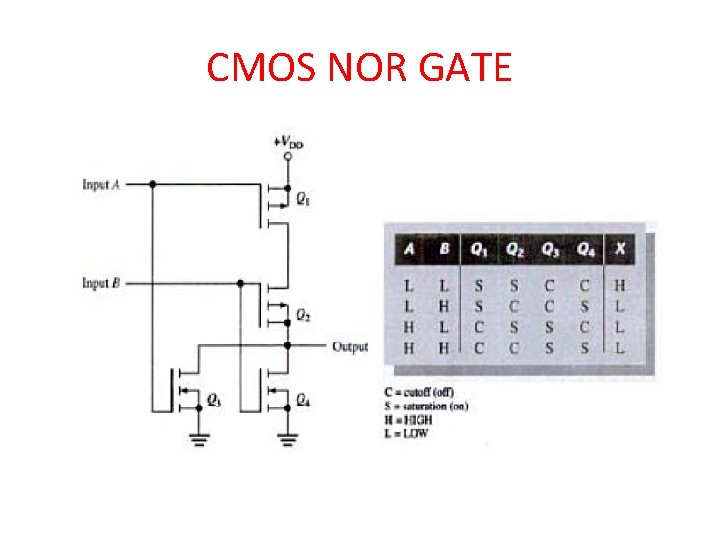

CMOS NOR GATE

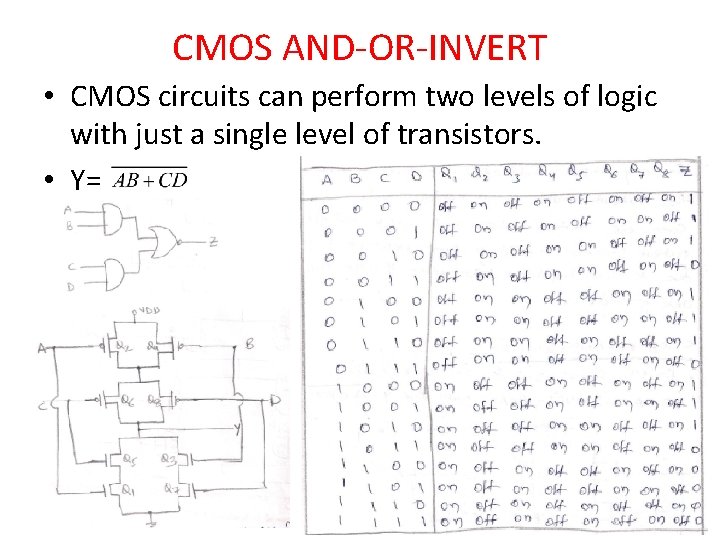

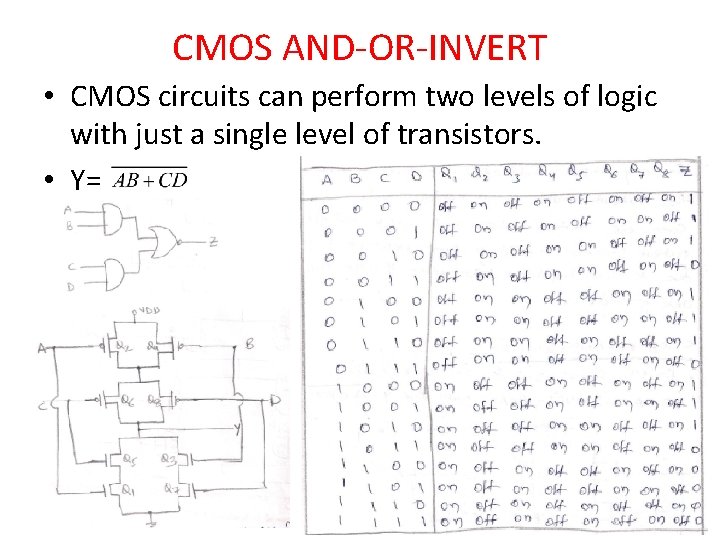

CMOS AND-OR-INVERT • CMOS circuits can perform two levels of logic with just a single level of transistors. • Y=

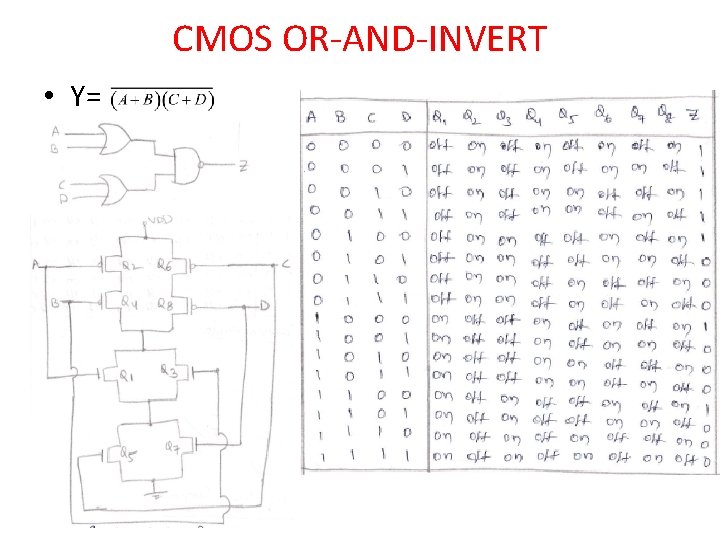

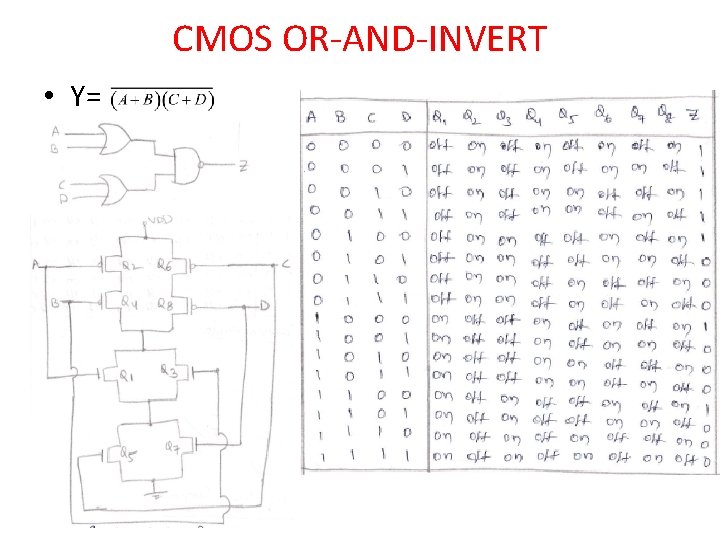

CMOS OR-AND-INVERT • Y=

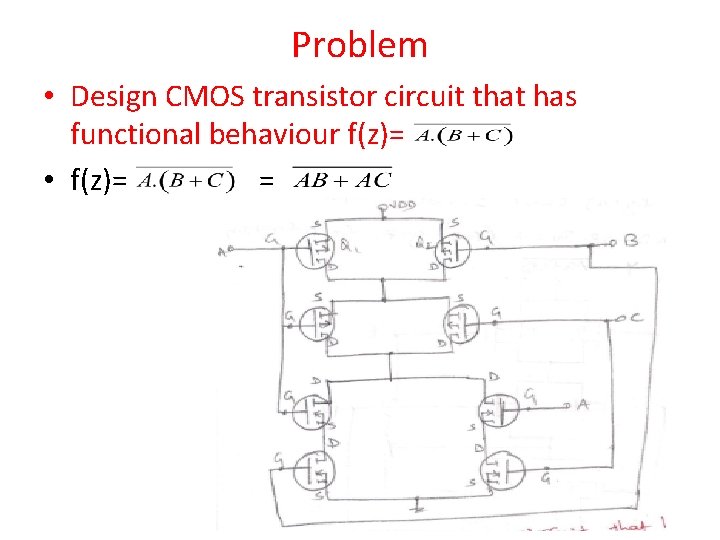

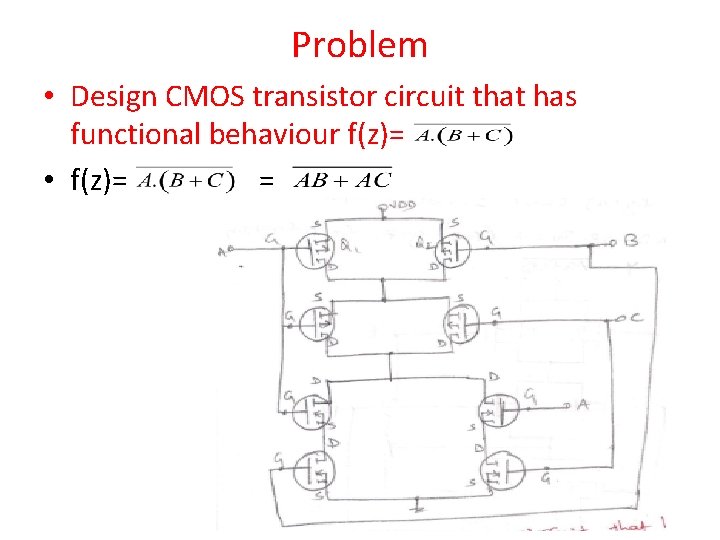

Problem • Design CMOS transistor circuit that has functional behaviour f(z)= • f(z)= =

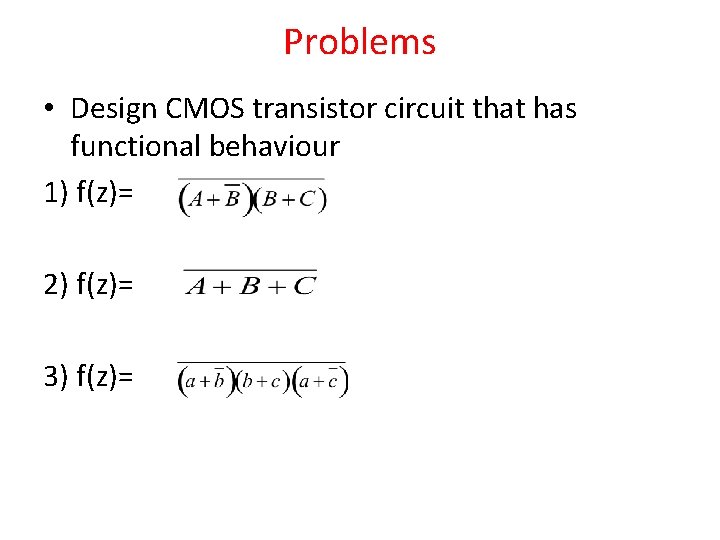

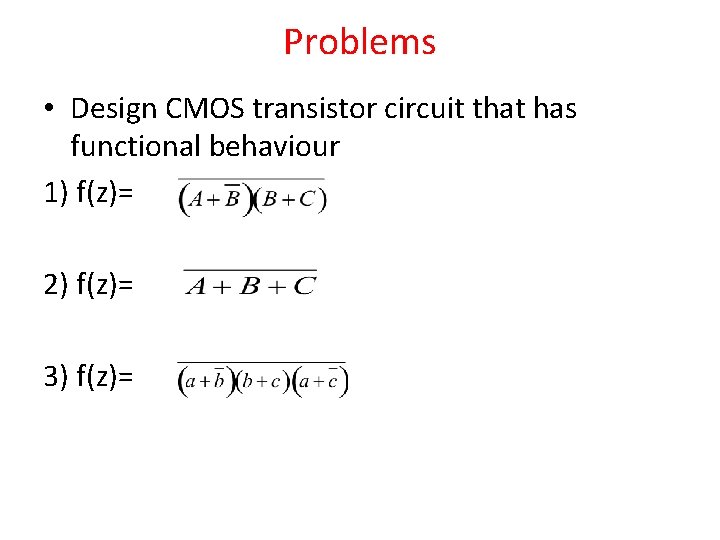

Problems • Design CMOS transistor circuit that has functional behaviour 1) f(z)= 2) f(z)= 3) f(z)=

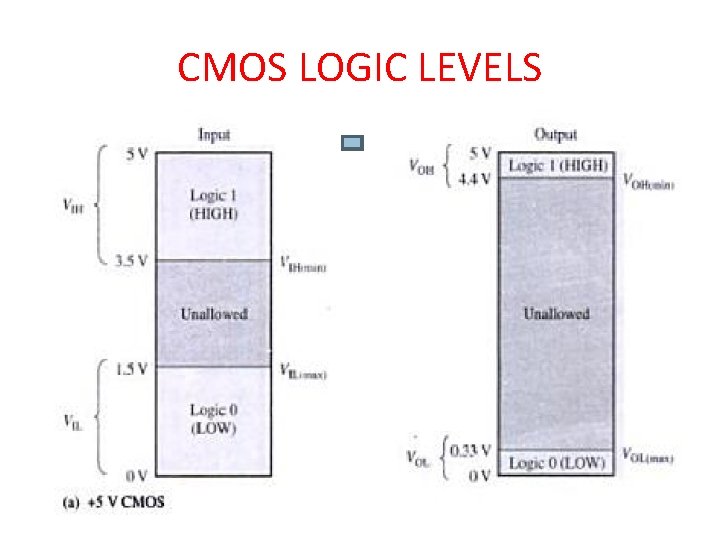

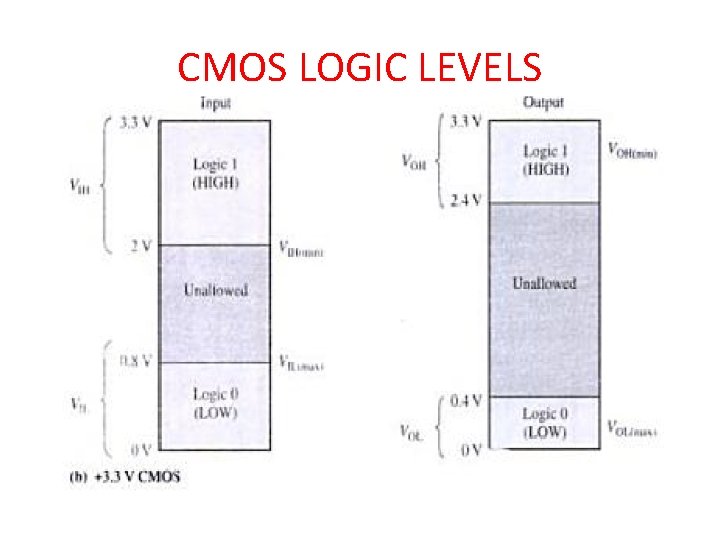

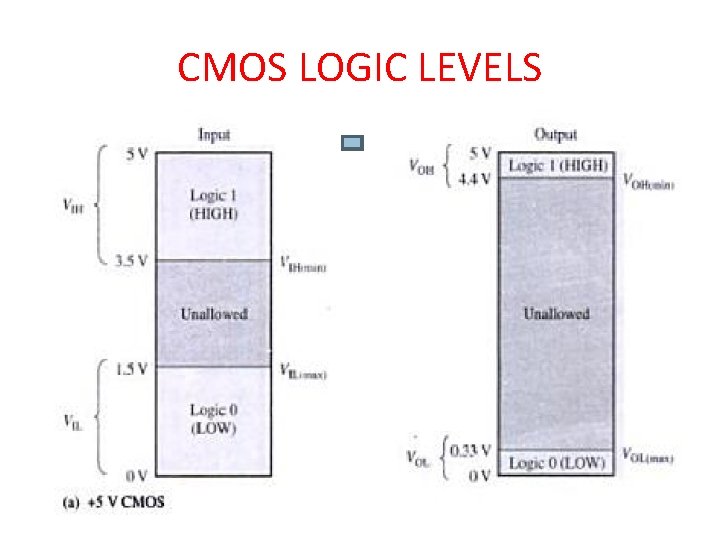

CMOS LOGIC LEVELS

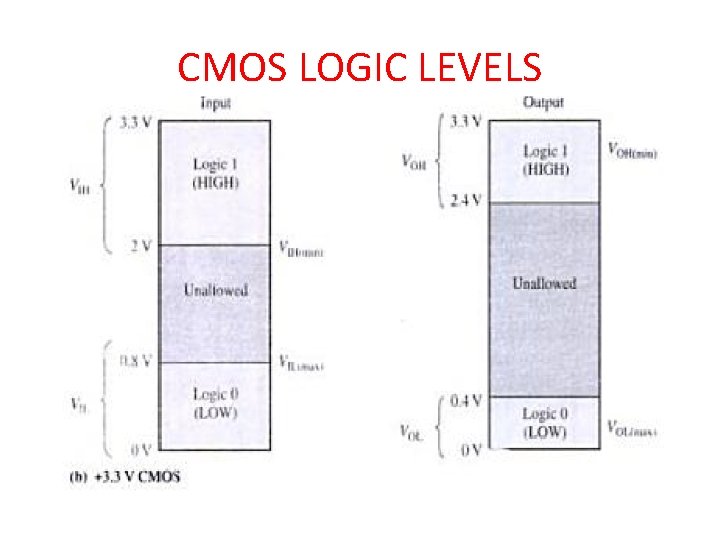

CMOS LOGIC LEVELS