Chapter 4 CMOS Process Technology Boonchuay Supmonchai Integrated

Chapter 4 CMOS Process Technology Boonchuay Supmonchai Integrated Design Application Research (IDAR) Laboratory July 5 th, 2004; Revised - June 26 th, 2006 2102 -545 Digital ICs

B. Supmonchai Outlines q Chip-Making Process q Photolithography q CMOS IC Fabrication Processes § Simple Process § Modern Process q Packaging Technology 2102 -545 Digital ICs CMOS Process Technology 2

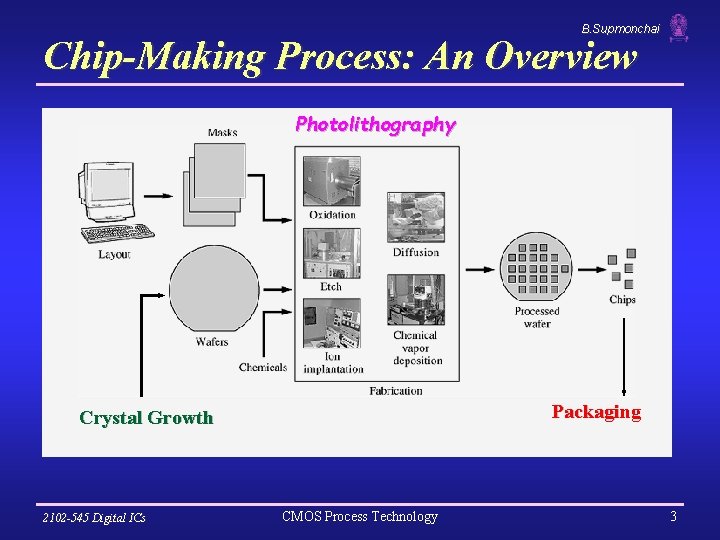

B. Supmonchai Chip-Making Process: An Overview Photolithography Packaging Crystal Growth 2102 -545 Digital ICs CMOS Process Technology 3

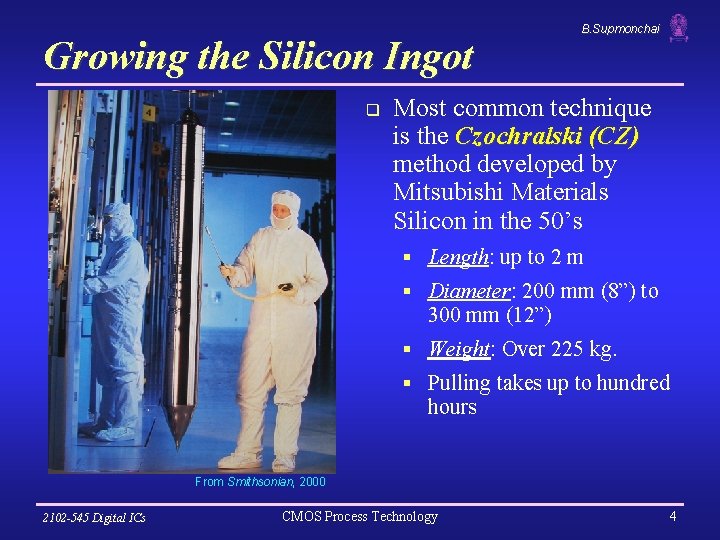

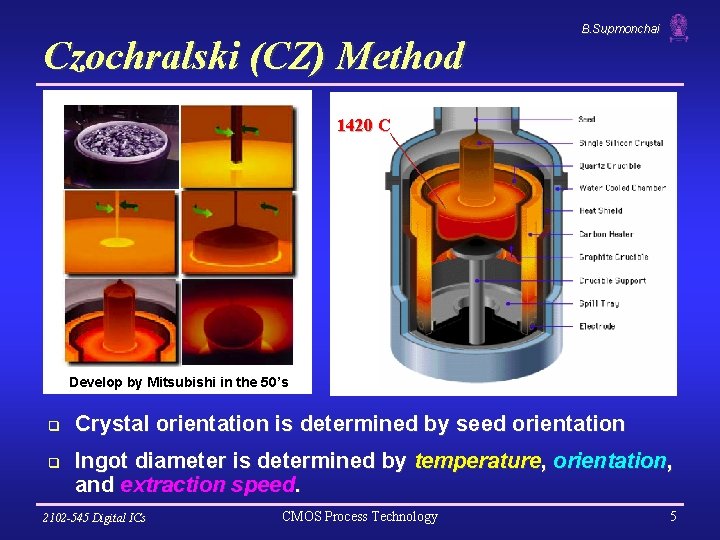

Growing the Silicon Ingot q B. Supmonchai Most common technique is the Czochralski (CZ) method developed by Mitsubishi Materials Silicon in the 50’s § Length: up to 2 m § Diameter: 200 mm (8”) to 300 mm (12”) § Weight: Over 225 kg. § Pulling takes up to hundred hours From Smithsonian, 2000 2102 -545 Digital ICs CMOS Process Technology 4

Czochralski (CZ) Method B. Supmonchai 1420 C Develop by Mitsubishi in the 50’s q q Crystal orientation is determined by seed orientation Ingot diameter is determined by temperature, orientation, and extraction speed. 2102 -545 Digital ICs CMOS Process Technology 5

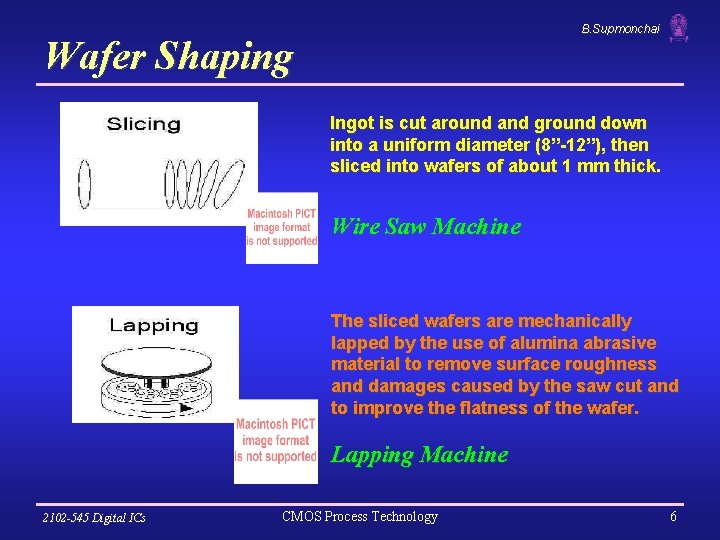

B. Supmonchai Wafer Shaping Ingot is cut around and ground down into a uniform diameter (8”-12”), then sliced into wafers of about 1 mm thick. Wire Saw Machine The sliced wafers are mechanically lapped by the use of alumina abrasive material to remove surface roughness and damages caused by the saw cut and to improve the flatness of the wafer. Lapping Machine 2102 -545 Digital ICs CMOS Process Technology 6

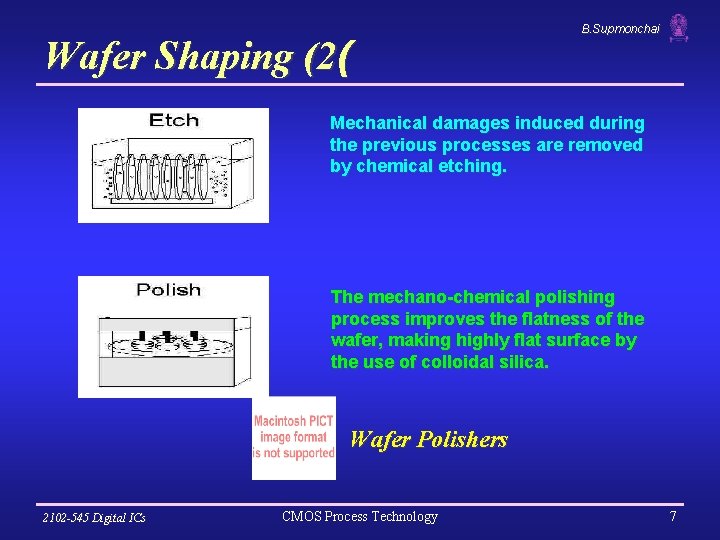

Wafer Shaping (2( B. Supmonchai Mechanical damages induced during the previous processes are removed by chemical etching. The mechano-chemical polishing process improves the flatness of the wafer, making highly flat surface by the use of colloidal silica. Wafer Polishers 2102 -545 Digital ICs CMOS Process Technology 7

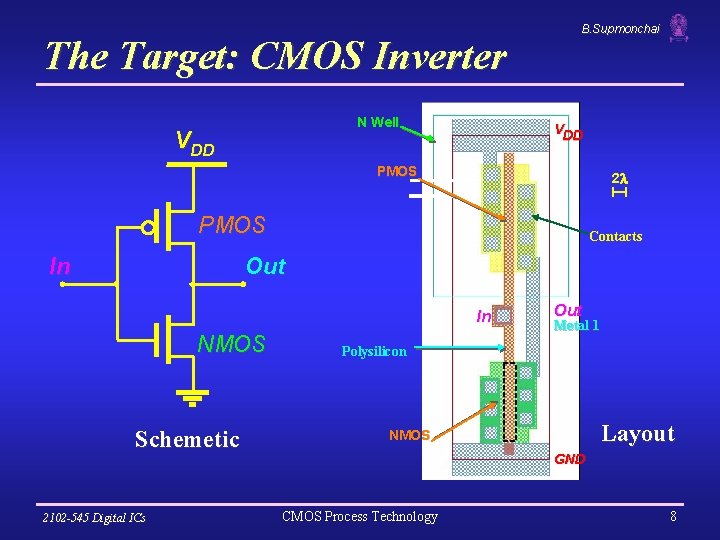

The Target: CMOS Inverter N Well VDD B. Supmonchai VDD PMOS 2 l PMOS In Contacts Out In NMOS Schemetic 2102 -545 Digital ICs Out Metal 1 Polysilicon Layout NMOS GND CMOS Process Technology 8

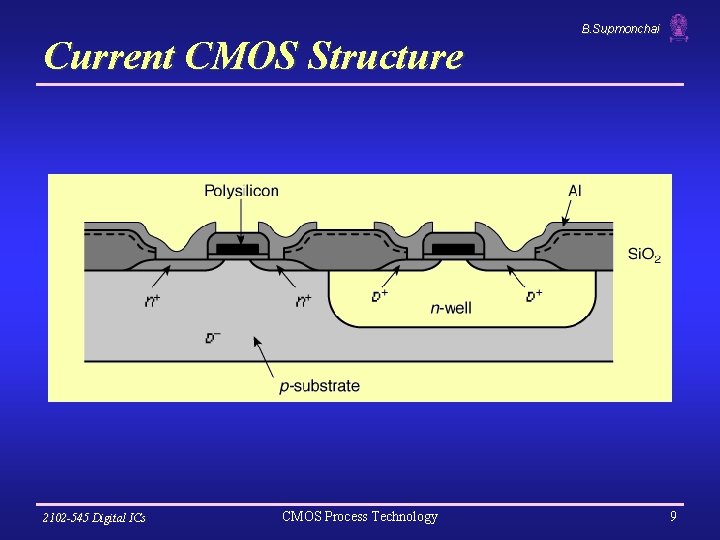

Current CMOS Structure 2102 -545 Digital ICs CMOS Process Technology B. Supmonchai 9

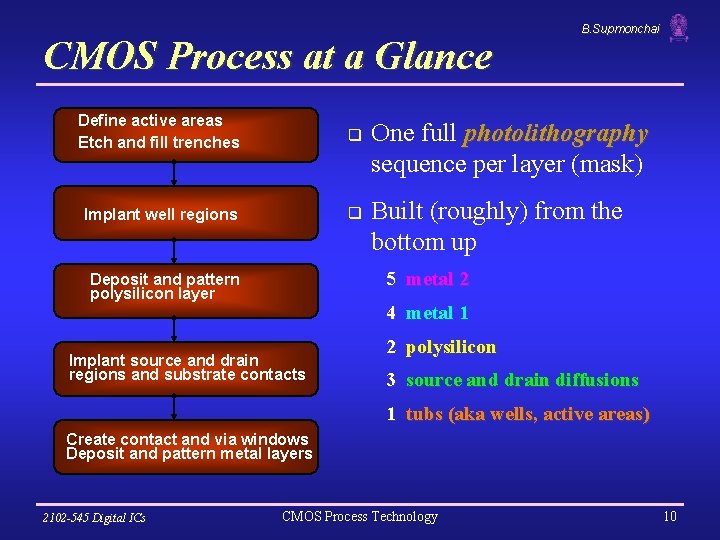

CMOS Process at a Glance Define active areas Etch and fill trenches q Implant well regions q B. Supmonchai One full photolithography sequence per layer (mask) Built (roughly) from the bottom up 5 metal 2 Deposit and pattern polysilicon layer 4 metal 1 Implant source and drain regions and substrate contacts 2 polysilicon 3 source and drain diffusions 1 tubs (aka wells, active areas) Create contact and via windows Deposit and pattern metal layers 2102 -545 Digital ICs CMOS Process Technology 10

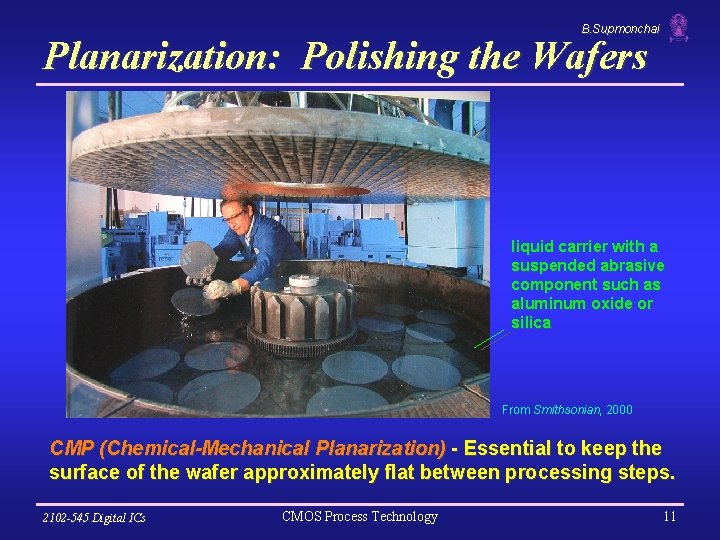

B. Supmonchai Planarization: Polishing the Wafers liquid carrier with a suspended abrasive component such as aluminum oxide or silica From Smithsonian, 2000 CMP (Chemical-Mechanical Planarization) - Essential to keep the surface of the wafer approximately flat between processing steps. 2102 -545 Digital ICs CMOS Process Technology 11

B. Supmonchai Outlines q Chip-Making Process q Photolithography q CMOS IC Fabrication Processes § Simple Process § Modern Process q Packaging Technology 2102 -545 Digital ICs CMOS Process Technology 12

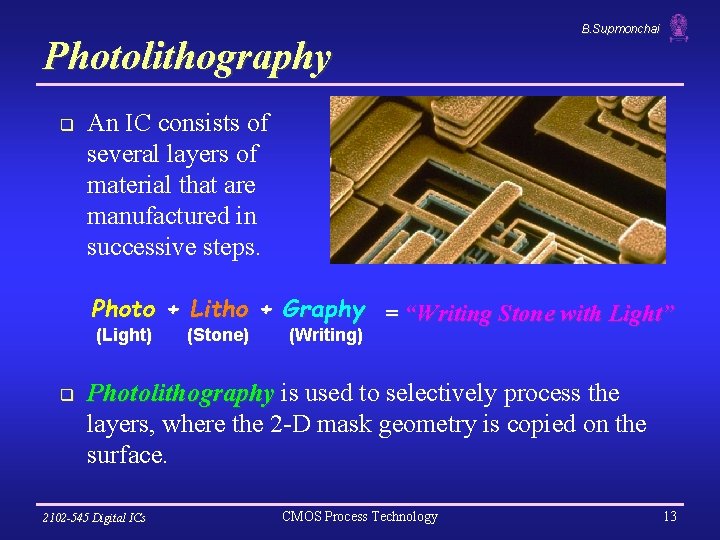

Photolithography q B. Supmonchai An IC consists of several layers of material that are manufactured in successive steps. Photo + Litho + Graphy = “Writing Stone with Light” (Light) q (Stone) (Writing) Photolithography is used to selectively process the layers, where the 2 -D mask geometry is copied on the surface. 2102 -545 Digital ICs CMOS Process Technology 13

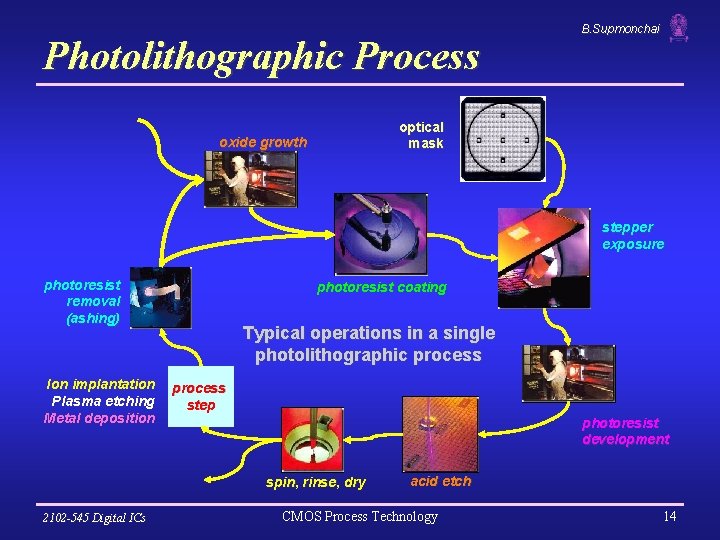

Photolithographic Process B. Supmonchai optical mask oxide growth stepper exposure photoresist removal (ashing) Ion implantation Plasma etching Metal deposition photoresist coating Typical operations in a single photolithographic process step photoresist development spin, rinse, dry 2102 -545 Digital ICs acid etch CMOS Process Technology 14

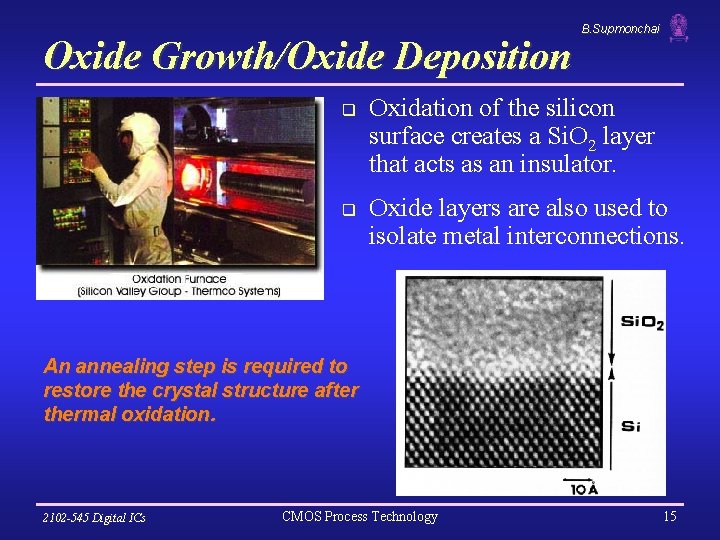

Oxide Growth/Oxide Deposition q q B. Supmonchai Oxidation of the silicon surface creates a Si. O 2 layer that acts as an insulator. Oxide layers are also used to isolate metal interconnections. An annealing step is required to restore the crystal structure after thermal oxidation. 2102 -545 Digital ICs CMOS Process Technology 15

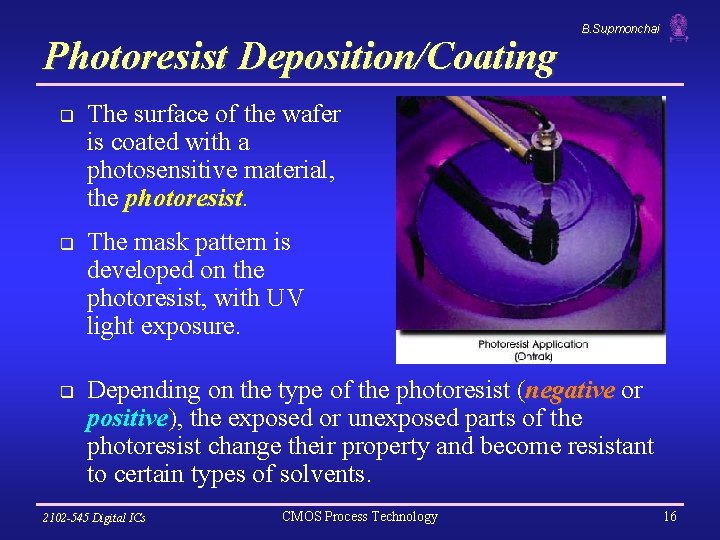

Photoresist Deposition/Coating q q q B. Supmonchai The surface of the wafer is coated with a photosensitive material, the photoresist The mask pattern is developed on the photoresist, with UV light exposure. Depending on the type of the photoresist (negative or positive), positive the exposed or unexposed parts of the photoresist change their property and become resistant to certain types of solvents. 2102 -545 Digital ICs CMOS Process Technology 16

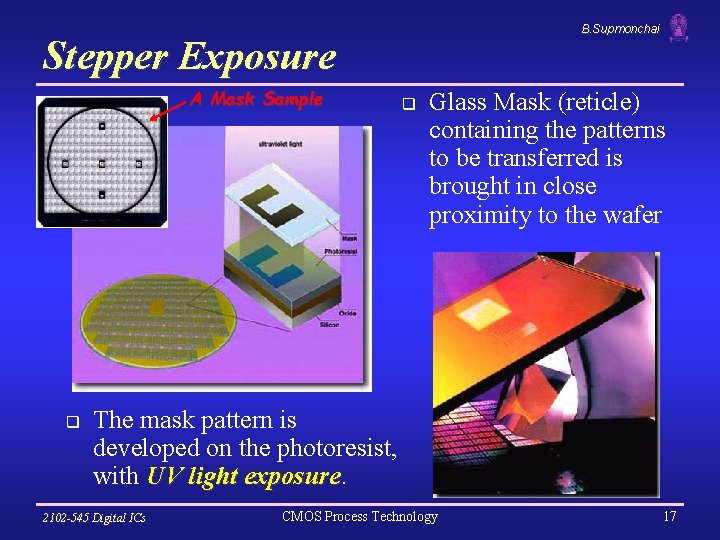

B. Supmonchai Stepper Exposure A Mask Sample q q Glass Mask (reticle) containing the patterns to be transferred is brought in close proximity to the wafer The mask pattern is developed on the photoresist, with UV light exposure 2102 -545 Digital ICs CMOS Process Technology 17

Photoresist Devolopment q q B. Supmonchai The wafers are developed in either an acid or base solution to remove the nonexposed (exposed) areas of the photoresist. Once the exposed photoresist is removed, the wafer is “soft baked” at a low temperature to harden the photoresist. 2102 -545 Digital ICs CMOS Process Technology 18

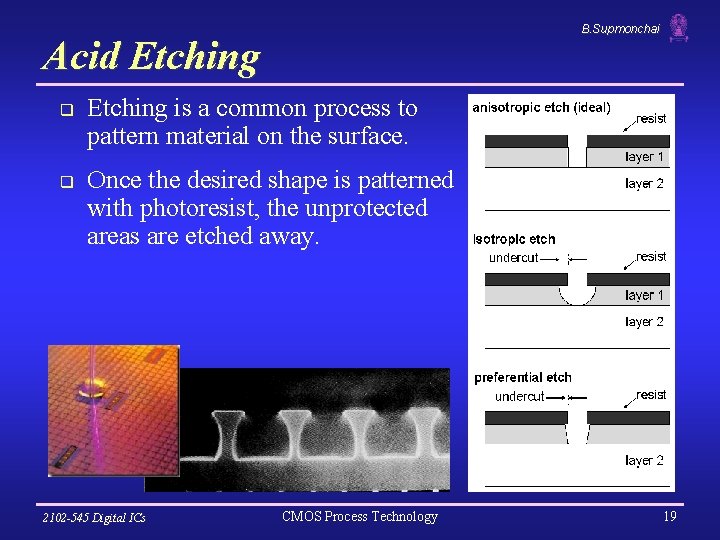

B. Supmonchai Acid Etching q q Etching is a common process to pattern material on the surface. Once the desired shape is patterned with photoresist, the unprotected areas are etched away. 2102 -545 Digital ICs CMOS Process Technology 19

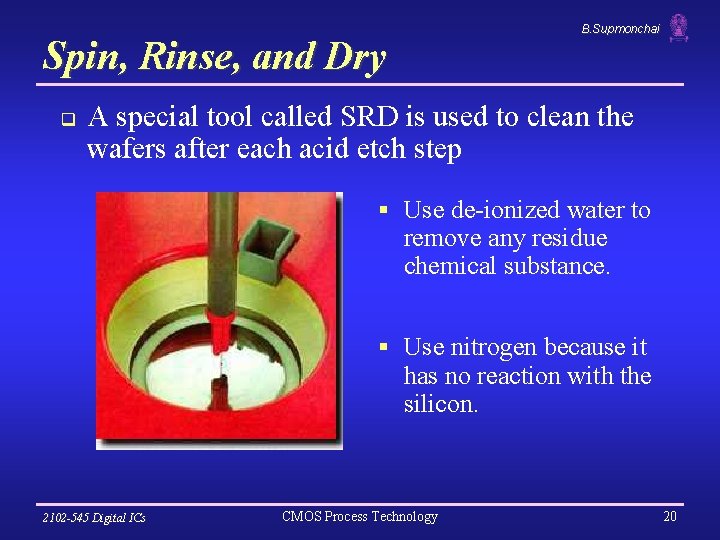

B. Supmonchai Spin, Rinse, and Dry q A special tool called SRD is used to clean the wafers after each acid etch step § Use de-ionized water to remove any residue chemical substance. § Use nitrogen because it has no reaction with the silicon. 2102 -545 Digital ICs CMOS Process Technology 20

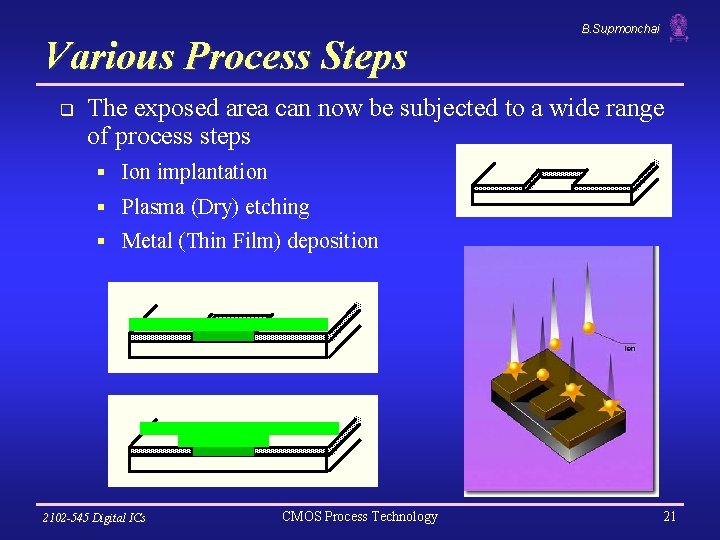

Various Process Steps q B. Supmonchai The exposed area can now be subjected to a wide range of process steps § Ion implantation § Plasma (Dry) etching § Metal (Thin Film) deposition 2102 -545 Digital ICs CMOS Process Technology 21

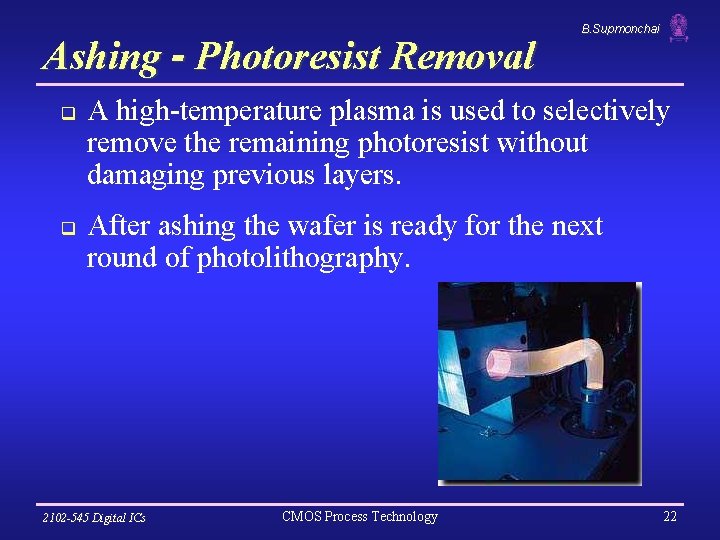

Ashing - Photoresist Removal q q B. Supmonchai A high-temperature plasma is used to selectively remove the remaining photoresist without damaging previous layers. After ashing the wafer is ready for the next round of photolithography. 2102 -545 Digital ICs CMOS Process Technology 22

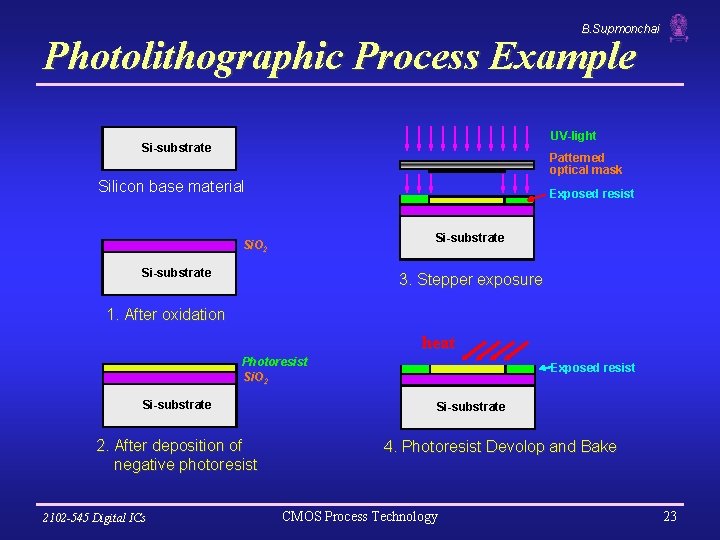

B. Supmonchai Photolithographic Process Example UV-light Si-substrate Patterned optical mask Silicon base material Exposed resist Si-substrate Si. O 2 Si-substrate 3. Stepper exposure 1. After oxidation heat Photoresist Si. O 2 Si-substrate 2. After deposition of negative photoresist 2102 -545 Digital ICs Exposed resist Si-substrate 4. Photoresist Devolop and Bake CMOS Process Technology 23

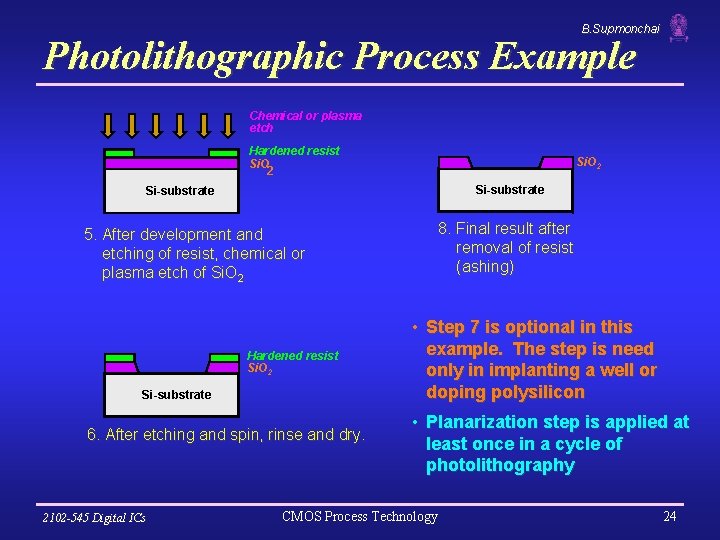

B. Supmonchai Photolithographic Process Example Chemical or plasma etch Hardened resist Si. O 2 Si-substrate 5. After development and etching of resist, chemical or plasma etch of Si. O 2 Hardened resist Si. O 2 Si-substrate 6. After etching and spin, rinse and dry. 2102 -545 Digital ICs 8. Final result after removal of resist (ashing) • Step 7 is optional in this example. The step is need only in implanting a well or doping polysilicon • Planarization step is applied at least once in a cycle of photolithography CMOS Process Technology 24

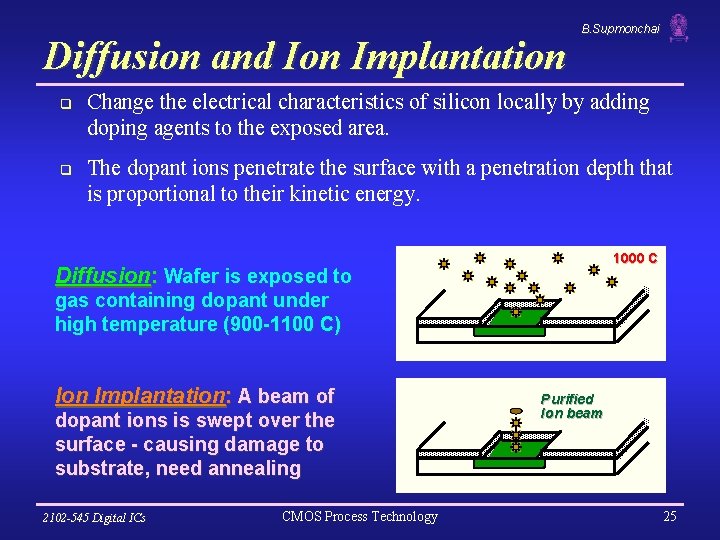

Diffusion and Ion Implantation q q B. Supmonchai Change the electrical characteristics of silicon locally by adding doping agents to the exposed area. The dopant ions penetrate the surface with a penetration depth that is proportional to their kinetic energy. 1000 C Diffusion: Wafer is exposed to gas containing dopant under high temperature (900 -1100 C) Ion Implantation: A beam of dopant ions is swept over the surface - causing damage to substrate, need annealing 2102 -545 Digital ICs CMOS Process Technology Purified Ion beam 25

B. Supmonchai Outlines q Chip-Making Process q Photolithography q CMOS IC Fabrication Processes § Simple Process § Modern Process q Packaging Technology 2102 -545 Digital ICs CMOS Process Technology 27

Photolithography Masks q q q B. Supmonchai Each photolithography step during fabrication must be defined by a separate photolithography mask. Each mask layer must be drawn (either manually or using a design automation tool) according to the layout design rules The combination (superposition) of all necessary mask layers completely defines the circuit to be fabricated. 2102 -545 Digital ICs CMOS Process Technology 28

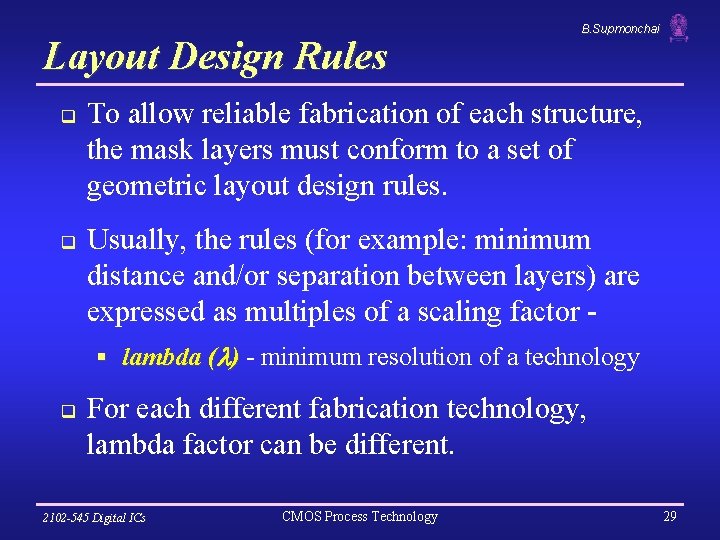

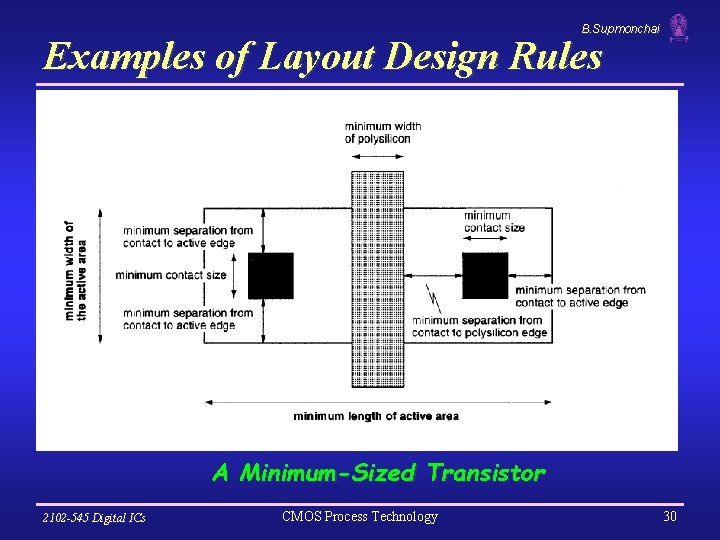

Layout Design Rules q q B. Supmonchai To allow reliable fabrication of each structure, the mask layers must conform to a set of geometric layout design rules. Usually, the rules (for example: minimum distance and/or separation between layers) are expressed as multiples of a scaling factor § lambda ( ) - minimum resolution of a technology q For each different fabrication technology, lambda factor can be different. 2102 -545 Digital ICs CMOS Process Technology 29

B. Supmonchai Examples of Layout Design Rules A Minimum-Sized Transistor 2102 -545 Digital ICs CMOS Process Technology 30

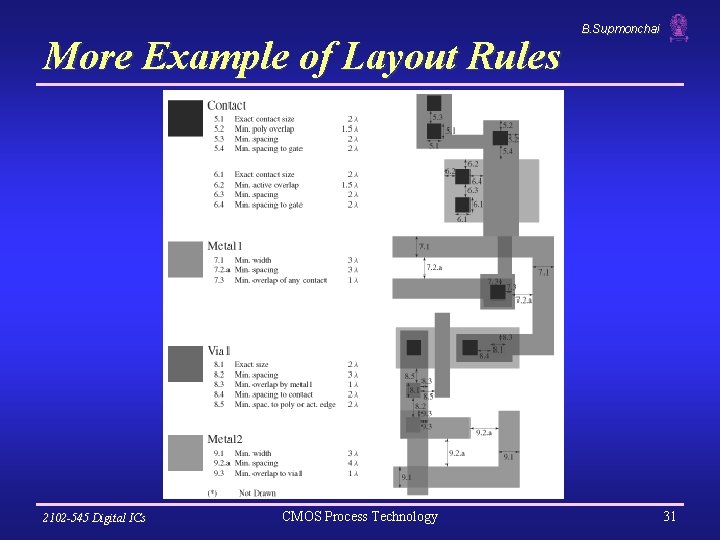

More Example of Layout Rules 2102 -545 Digital ICs CMOS Process Technology B. Supmonchai 31

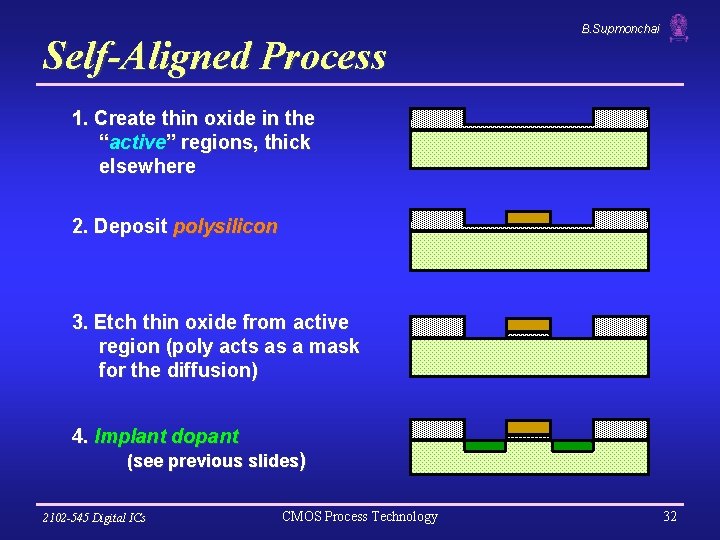

Self-Aligned Process B. Supmonchai 1. Create thin oxide in the “active” regions, thick elsewhere 2. Deposit polysilicon 3. Etch thin oxide from active region (poly acts as a mask for the diffusion) 4. Implant dopant (see previous slides) 2102 -545 Digital ICs CMOS Process Technology 32

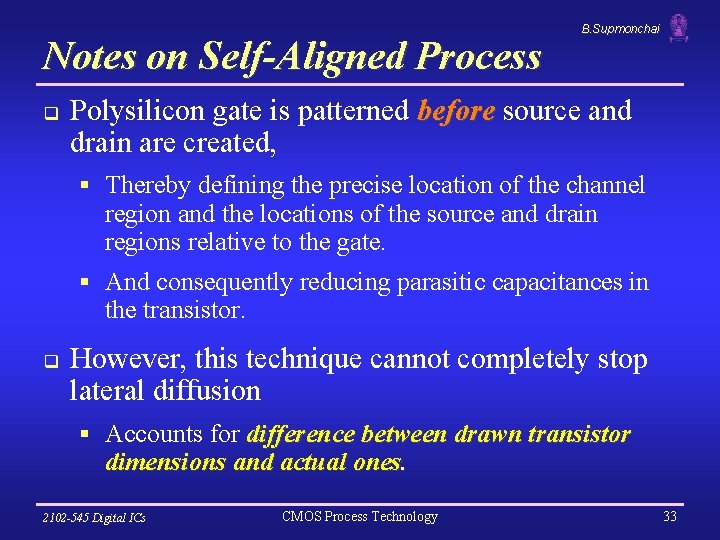

Notes on Self-Aligned Process q B. Supmonchai Polysilicon gate is patterned before source and drain are created, § Thereby defining the precise location of the channel region and the locations of the source and drain regions relative to the gate. § And consequently reducing parasitic capacitances in the transistor. q However, this technique cannot completely stop lateral diffusion § Accounts for difference between drawn transistor dimensions and actual ones. 2102 -545 Digital ICs CMOS Process Technology 33

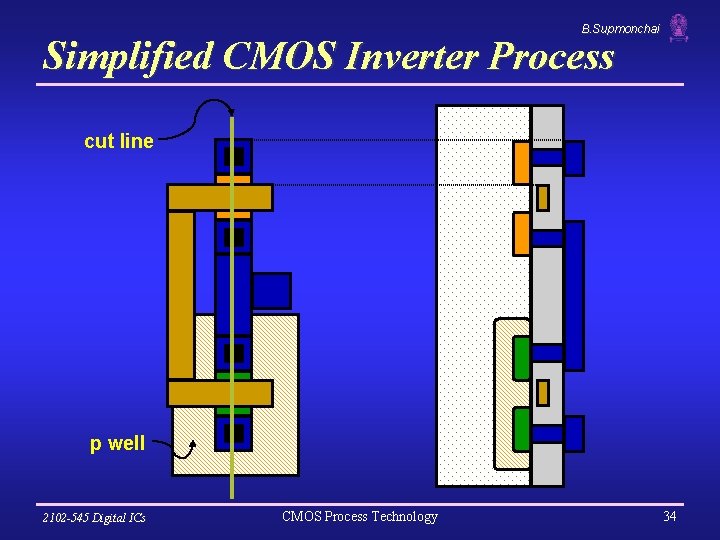

B. Supmonchai Simplified CMOS Inverter Process cut line p well 2102 -545 Digital ICs CMOS Process Technology 34

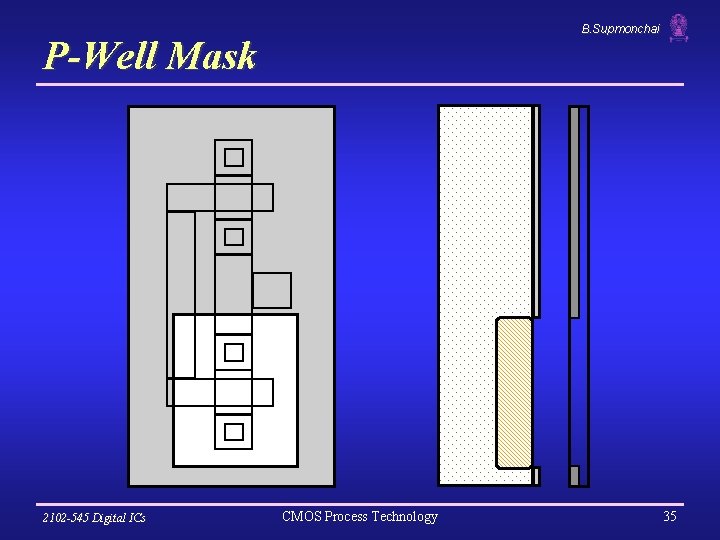

B. Supmonchai P-Well Mask 2102 -545 Digital ICs CMOS Process Technology 35

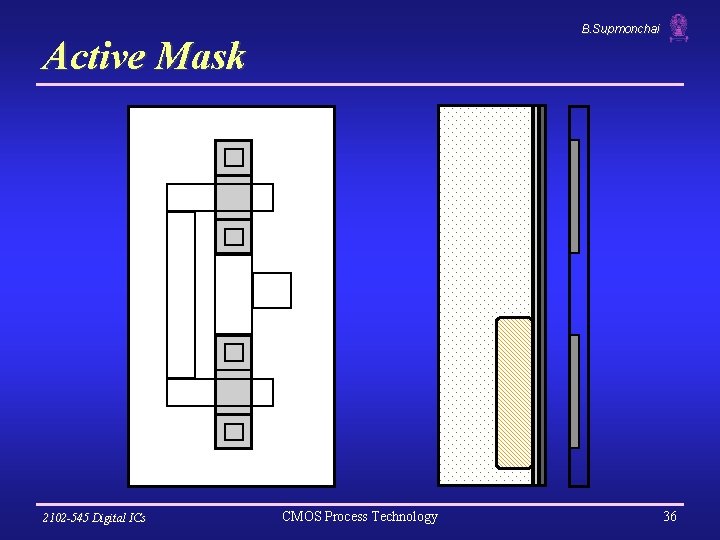

B. Supmonchai Active Mask 2102 -545 Digital ICs CMOS Process Technology 36

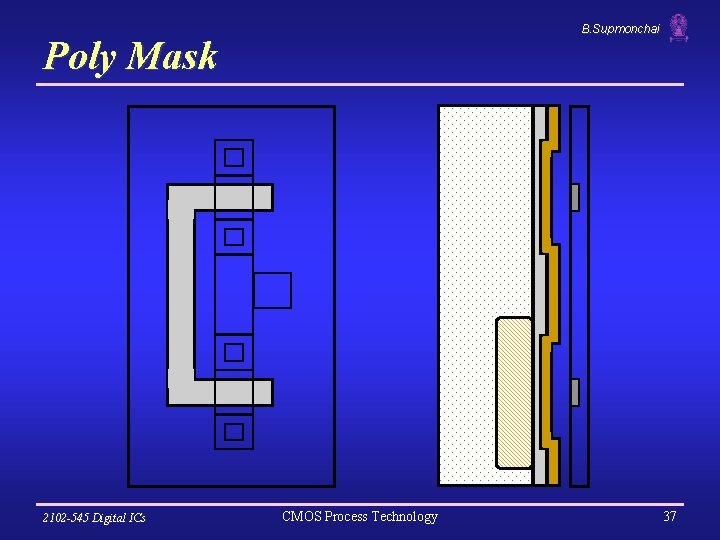

B. Supmonchai Poly Mask 2102 -545 Digital ICs CMOS Process Technology 37

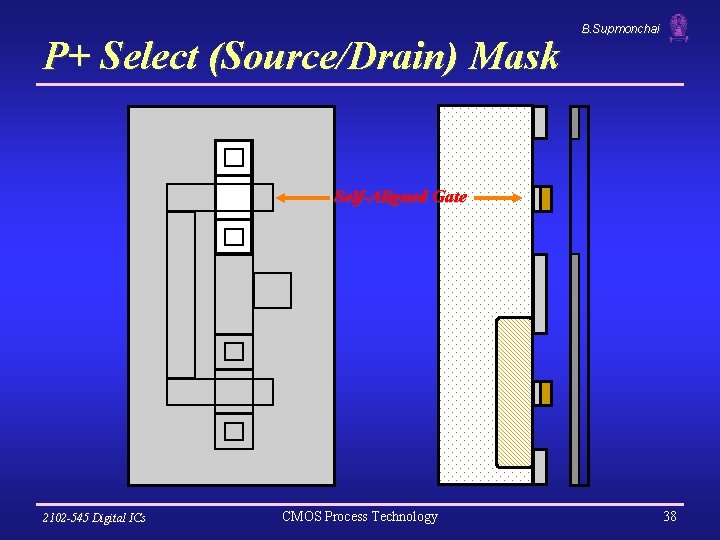

P+ Select (Source/Drain) Mask B. Supmonchai Self-Aligned Gate 2102 -545 Digital ICs CMOS Process Technology 38

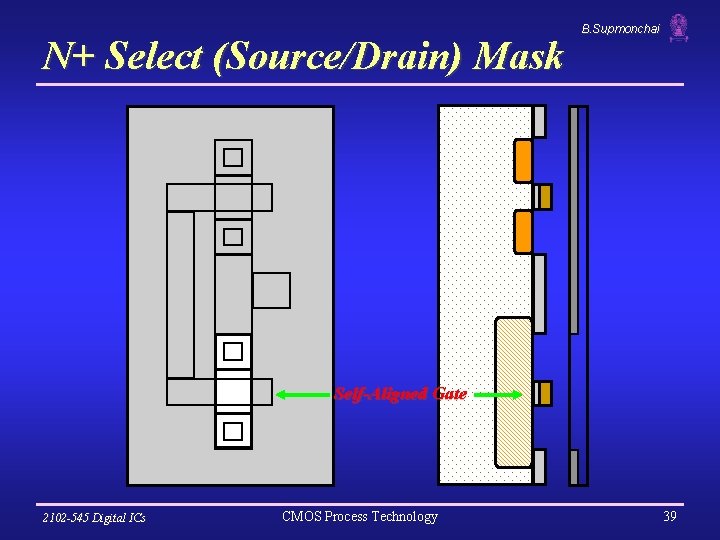

N+ Select (Source/Drain) Mask B. Supmonchai Self-Aligned Gate 2102 -545 Digital ICs CMOS Process Technology 39

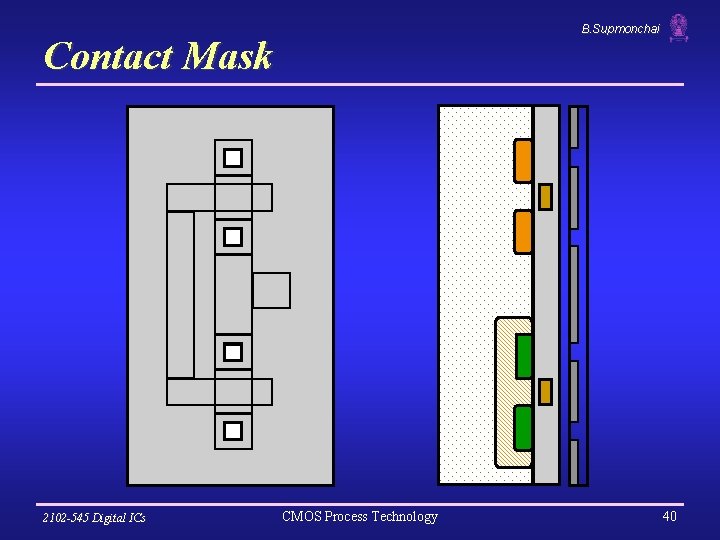

B. Supmonchai Contact Mask 2102 -545 Digital ICs CMOS Process Technology 40

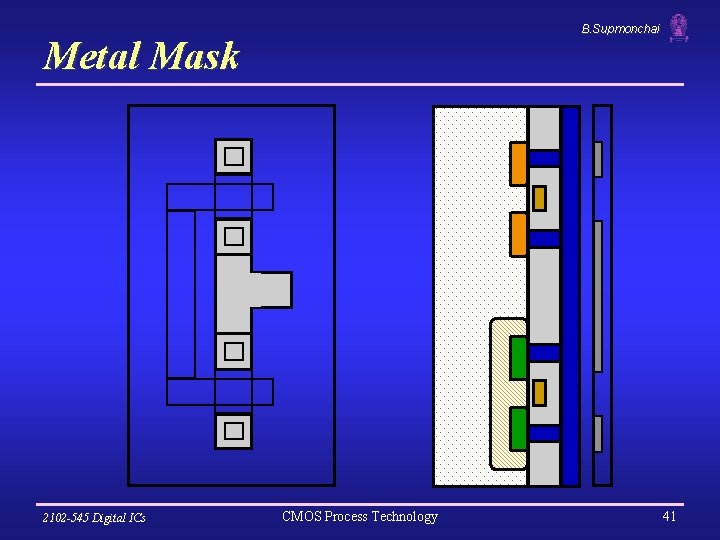

B. Supmonchai Metal Mask 2102 -545 Digital ICs CMOS Process Technology 41

B. Supmonchai Outlines q Chip-Making Process q Photolithography q CMOS IC Fabrication Processes § Simple Process § Modern Process q Packaging Technology 2102 -545 Digital ICs CMOS Process Technology 42

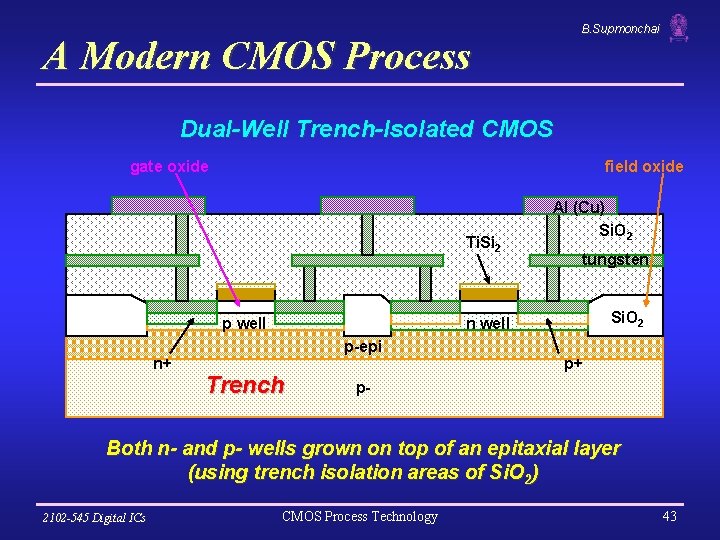

B. Supmonchai A Modern CMOS Process Dual-Well Trench-Isolated CMOS gate oxide field oxide Ti. Si 2 p well n+ Al (Cu) Si. O 2 tungsten Si. O 2 n well p-epi Trench p+ p- Both n- and p- wells grown on top of an epitaxial layer (using trench isolation areas of Si. O 2) 2102 -545 Digital ICs CMOS Process Technology 43

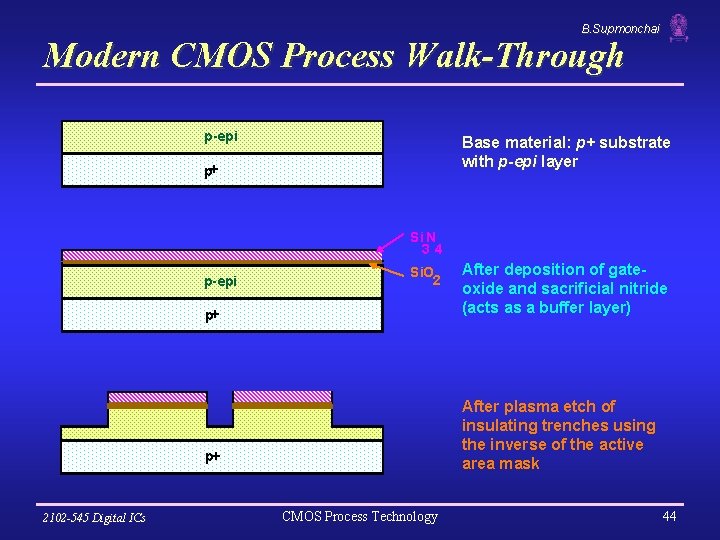

B. Supmonchai Modern CMOS Process Walk-Through p-epi Base material: p+ substrate with p-epi layer p+ Si N 3 4 p-epi Si. O 2 p+ After plasma etch of insulating trenches using the inverse of the active area mask p+ 2102 -545 Digital ICs After deposition of gateoxide and sacrificial nitride (acts as a buffer layer) CMOS Process Technology 44

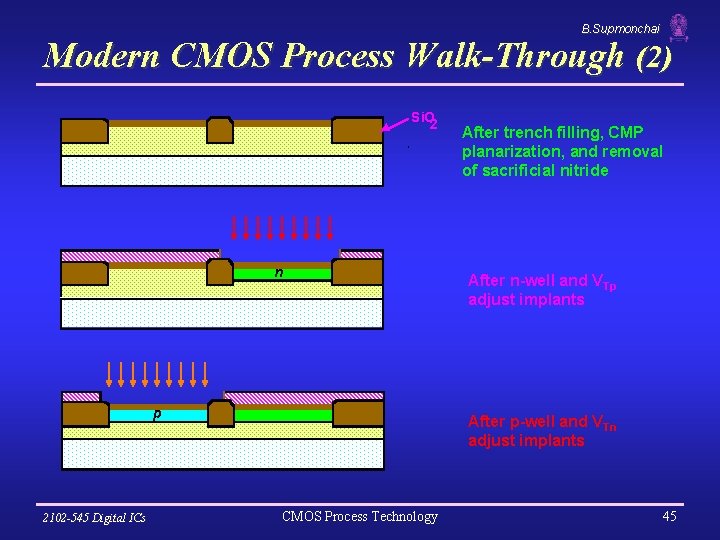

B. Supmonchai Modern CMOS Process Walk-Through (2) Si. O 2 n p 2102 -545 Digital ICs After trench filling, CMP planarization, and removal of sacrificial nitride After n-well and VTp adjust implants After p-well and VTn adjust implants CMOS Process Technology 45

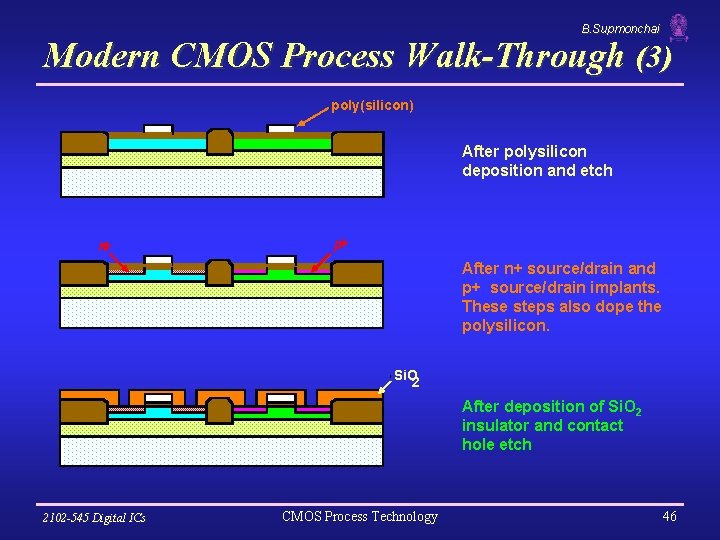

B. Supmonchai Modern CMOS Process Walk-Through (3) poly(silicon) After polysilicon deposition and etch n+ p+ After n+ source/drain and p+ source/drain implants. These steps also dope the polysilicon. Si. O 2 After deposition of Si. O 2 insulator and contact hole etch 2102 -545 Digital ICs CMOS Process Technology 46

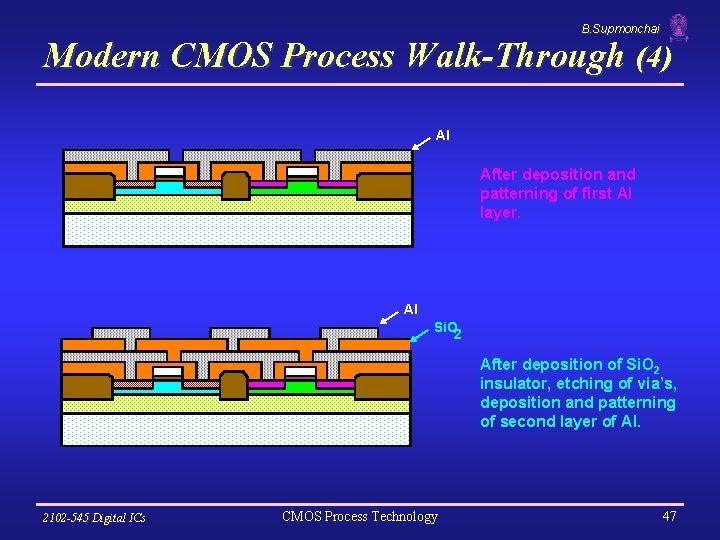

B. Supmonchai Modern CMOS Process Walk-Through (4) Al After deposition and patterning of first Al layer. Al Si. O 2 After deposition of Si. O 2 insulator, etching of via’s, deposition and patterning of second layer of Al. 2102 -545 Digital ICs CMOS Process Technology 47

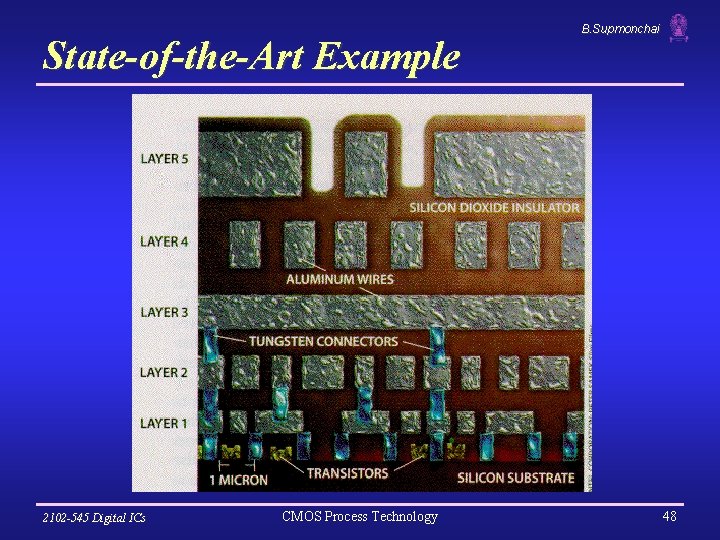

State-of-the-Art Example 2102 -545 Digital ICs CMOS Process Technology B. Supmonchai 48

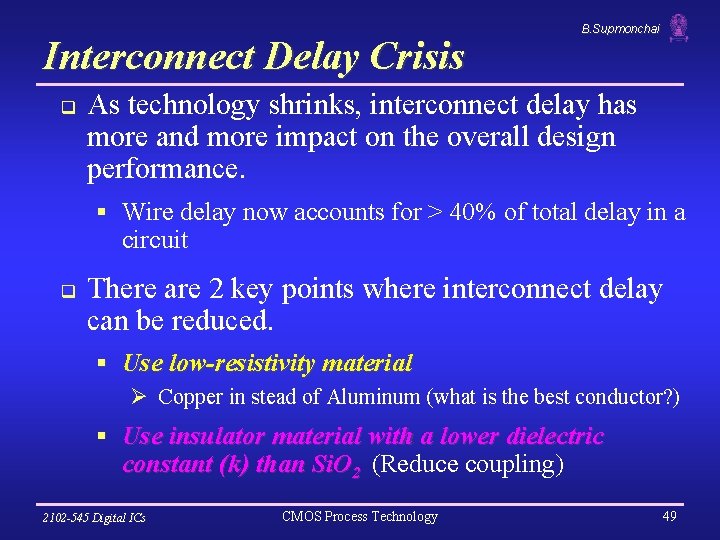

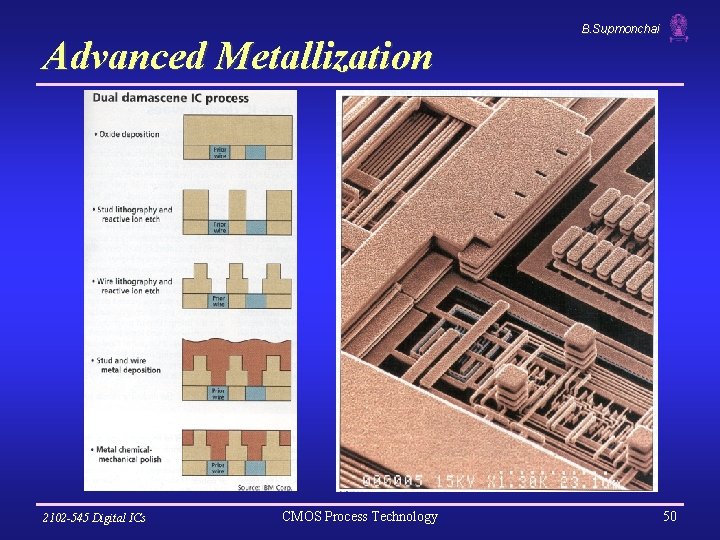

Interconnect Delay Crisis q B. Supmonchai As technology shrinks, interconnect delay has more and more impact on the overall design performance. § Wire delay now accounts for > 40% of total delay in a circuit q There are 2 key points where interconnect delay can be reduced. § Use low-resistivity material Ø Copper in stead of Aluminum (what is the best conductor? ) § Use insulator material with a lower dielectric constant (k) than Si. O 2 (Reduce coupling) 2102 -545 Digital ICs CMOS Process Technology 49

Advanced Metallization 2102 -545 Digital ICs CMOS Process Technology B. Supmonchai 50

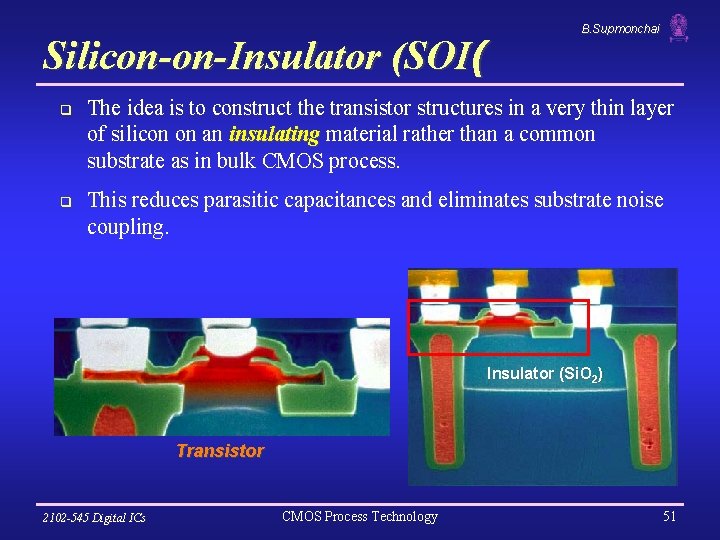

Silicon-on-Insulator (SOI( q q B. Supmonchai The idea is to construct the transistor structures in a very thin layer of silicon on an insulating material rather than a common substrate as in bulk CMOS process. This reduces parasitic capacitances and eliminates substrate noise coupling. Insulator (Si. O 2) Transistor 2102 -545 Digital ICs CMOS Process Technology 51

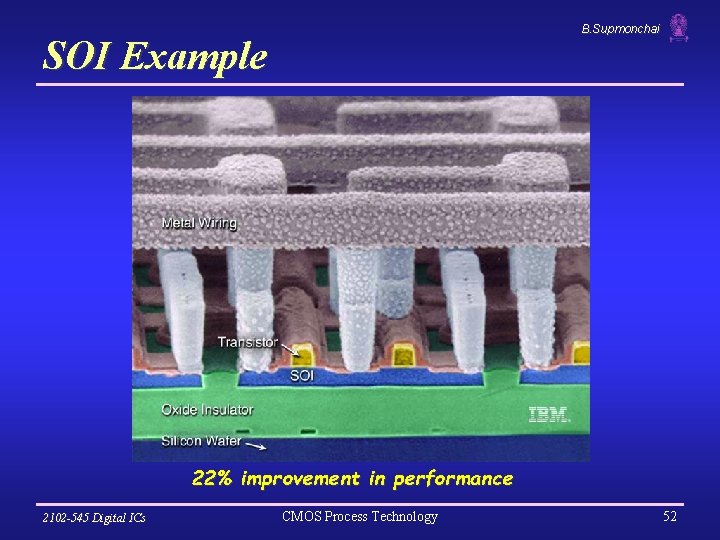

B. Supmonchai SOI Example 22% improvement in performance 2102 -545 Digital ICs CMOS Process Technology 52

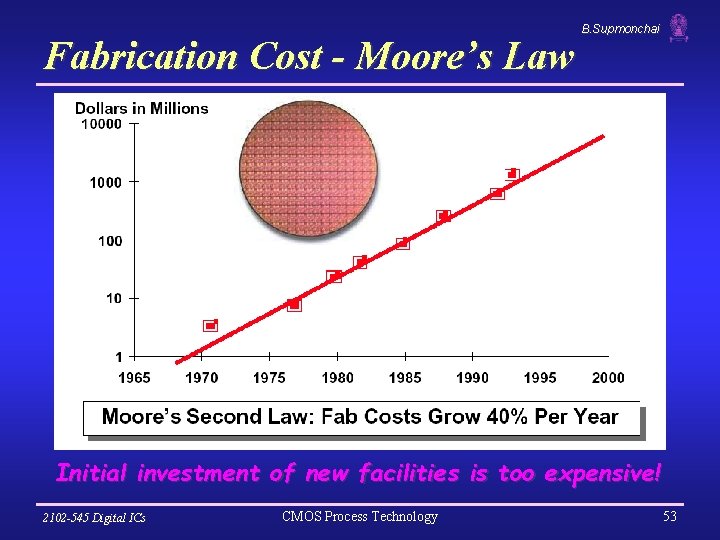

Fabrication Cost - Moore’s Law B. Supmonchai Initial investment of new facilities is too expensive! 2102 -545 Digital ICs CMOS Process Technology 53

B. Supmonchai Outlines q Chip-Making Process q Photolithography q CMOS IC Fabrication Processes § Simple Process § Modern Process q Packaging Technology 2102 -545 Digital ICs CMOS Process Technology 54

Packaging Technology q B. Supmonchai Many high-performance chips failed stringent test specifications after packaging because the designer (usually novice!) have not included various effects of packaging constraints and parasitics into their designs. § Ground planes, power planes, and bonding pads greatly affect the behavior of on-chip power and ground bus. § Length of bonding wire and lead length in a package generate a voltage drop in the output circuit. § Inappropriate type of package body can cause thermal runaway and hence damage the ICs. 2102 -545 Digital ICs CMOS Process Technology 55

Packaging Requirements q B. Supmonchai Electrical: Electrical Low parasitics § Low capacitance and Inductance q Mechanical: Mechanical Reliable and robust § Moisture-proof § High pin density q Thermal: Thermal Efficient heat removal § High thermal conductivity § Low thermal expansion coefficient q Economical: Economical Cheap 2102 -545 Digital ICs CMOS Process Technology 56

Bonding Techniques B. Supmonchai Wire Bonding High and unpredictable value of parasitics 2102 -545 Digital ICs CMOS Process Technology 57

B. Supmonchai Tape-Automated Bonding (TAB( Die Attachment using Soldier bumps Polymer Tape with imprinted Wiring pattern 2102 -545 Digital ICs Highly Automated, Eliminate long bonding wires CMOS Process Technology 58

Flip-Chip Bonding B. Supmonchai Alleviate power- and clock-distribution problem 2102 -545 Digital ICs CMOS Process Technology 59

Package-to-Board Interconnect Through-Hole Mounting Surface Mounting Difficult to mount Mechanical weaker structure Higher packaging density 2102 -545 Digital ICs B. Supmonchai Sturdy, Mechanically reliably, Lower packaging density CMOS Process Technology 60

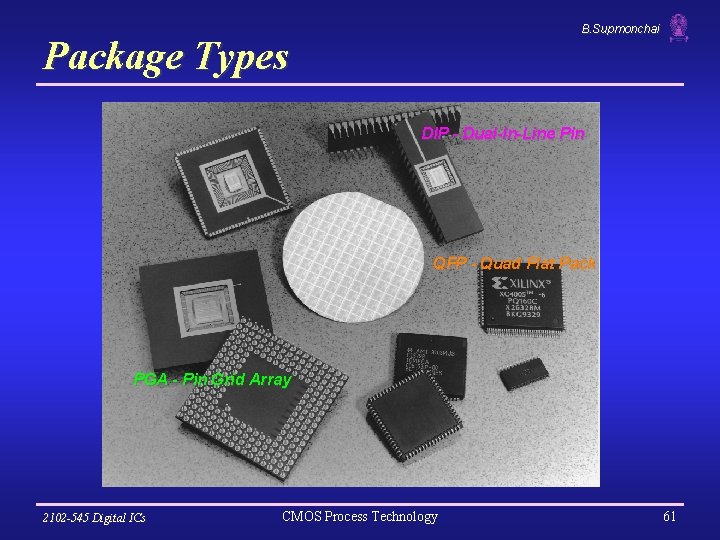

B. Supmonchai Package Types DIP - Dual-In-Line Pin QFP - Quad Flat Pack PGA - Pin Grid Array 2102 -545 Digital ICs CMOS Process Technology 61

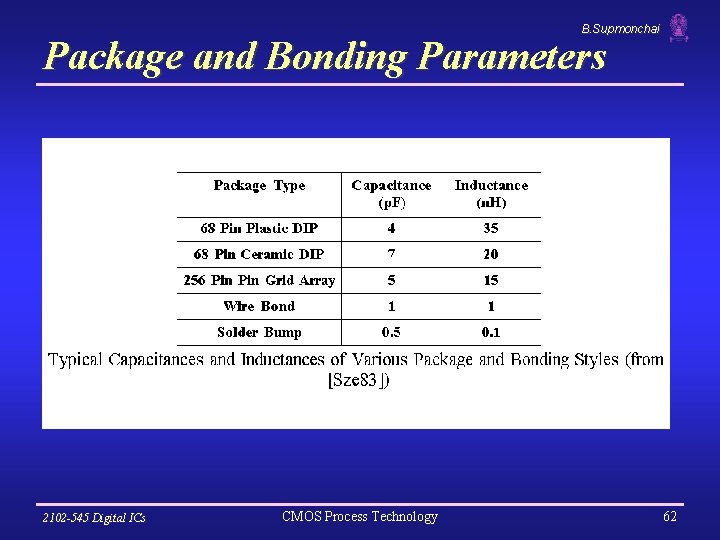

B. Supmonchai Package and Bonding Parameters 2102 -545 Digital ICs CMOS Process Technology 62

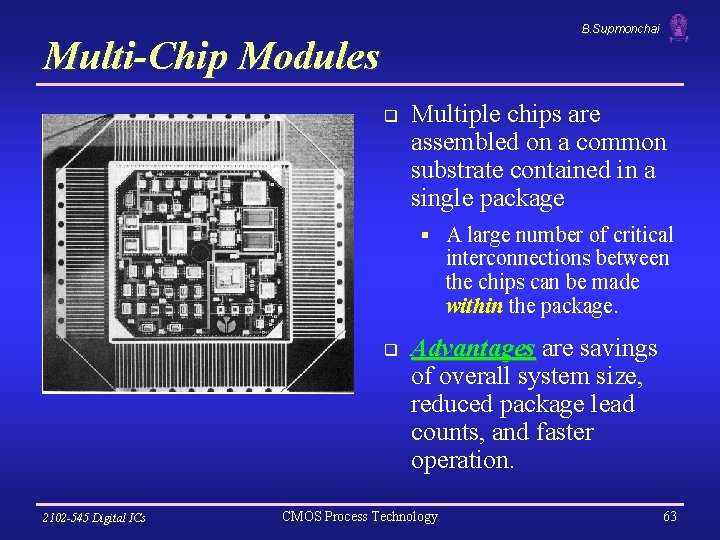

B. Supmonchai Multi-Chip Modules q Multiple chips are assembled on a common substrate contained in a single package § A large number of critical interconnections between the chips can be made within the package. q 2102 -545 Digital ICs Advantages are savings of overall system size, reduced package lead counts, and faster operation. CMOS Process Technology 63

- Slides: 62