DISEO MICROELECTRNICO I Captulo 3 El Inversor CMOS

- Slides: 60

DISEÑO MICROELECTRÓNICO I Capítulo 3 El Inversor CMOS Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Índice 3. - EL INVERSOR CMOS 3. 1. - Características de funcionamiento estático 3. 2. - Análisis del régimen dinámico 3. 2. a. - Estimación de capacidades 3. 2. b. - Retardo de propagación 3. 2. c. - Consumo de potencia 3. 3. - Perspectivas de futuro: efectos del escalado Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

PUERTAS LÓGICAS Parámetros Fundamentales COMPORTAMIENTO ESTÁTICO Funcionalidad, Fiabilidad, Robustez l ÁREA l COMPORTAMIENTO DINÁMICO: Prestaciones l » Velocidad (retardo) » Consumo de Potencia » Energía Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Ruido en Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Operación en Continua: Característica de Transferencia de Voltaje “ 1” : VOH “ 0” : VOL = f (VM) Circuitos Integrados Digitales El Inversor CMOS VOH = f (VOL) VOL = f (VOH) Diseño Microelectrónico

Señales analógicas vs. señales digitales VOH = f (VOL) VOL = f (VOH) Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Definición de Margen de Ruido Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

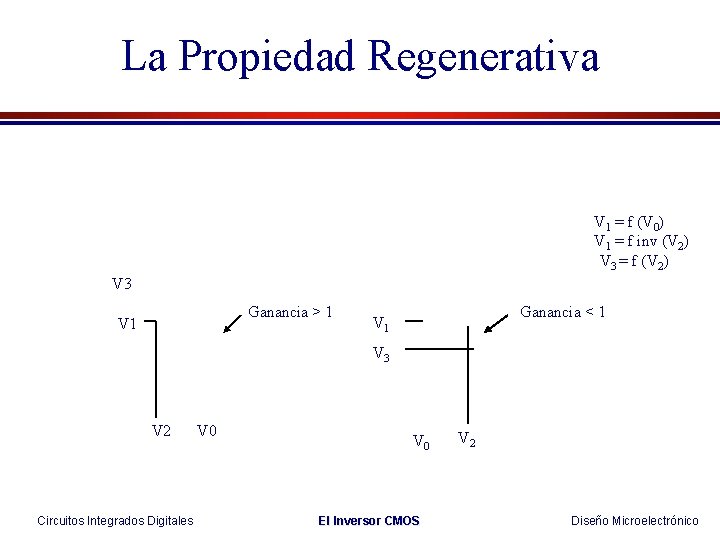

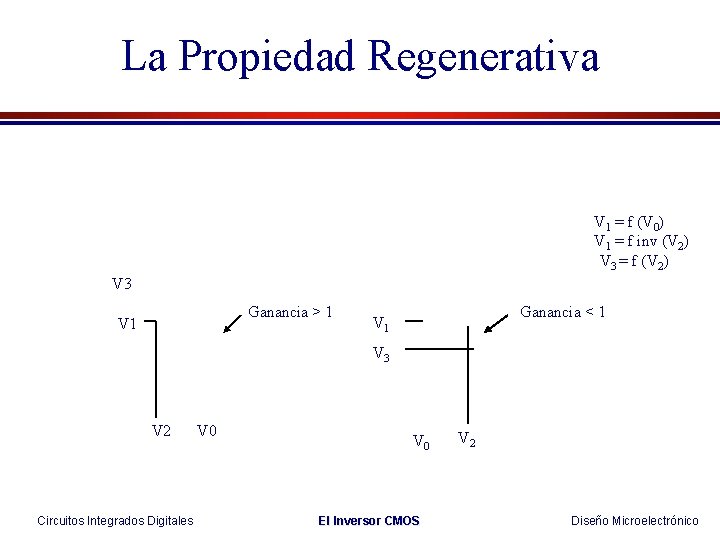

La Propiedad Regenerativa V 1 = f (V 0) V 1 = f inv (V 2) V 3 = f (V 2) V 3 Ganancia > 1 V 1 Ganancia < 1 V 3 V 2 Circuitos Integrados Digitales V 0 El Inversor CMOS V 2 Diseño Microelectrónico

Fan-in y Fan-out Ro ↓↓ Ri ↑↑ Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

El Inversor Ideal Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

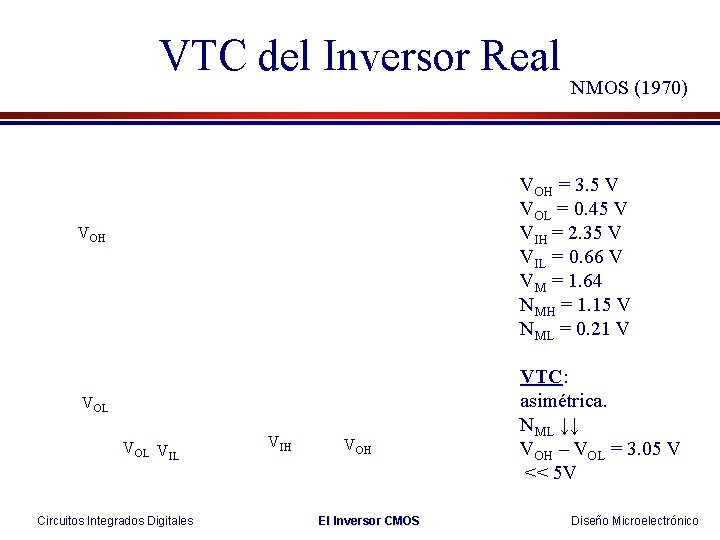

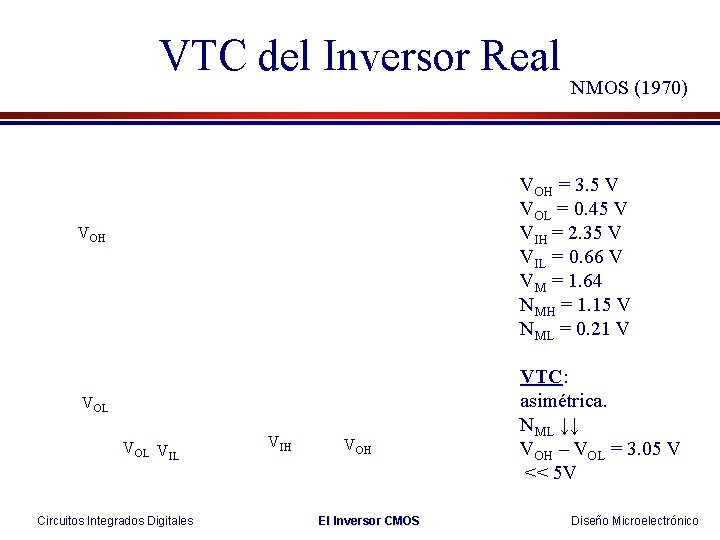

VTC del Inversor Real NMOS (1970) VOH = 3. 5 V VOL = 0. 45 V VIH = 2. 35 V VIL = 0. 66 V VM = 1. 64 NMH = 1. 15 V NML = 0. 21 V VOH VOL VIL Circuitos Integrados Digitales VIH VOH El Inversor CMOS VTC: asimétrica. NML ↓↓ VOH – VOL = 3. 05 V << 5 V Diseño Microelectrónico

COMPORTAMIENTO DINÁMICO: Definición del Retardo Influencia del fan-in y del fan-out Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

El Oscilador de Anillo fan-in = fan-out = 1 >> tf + tr Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

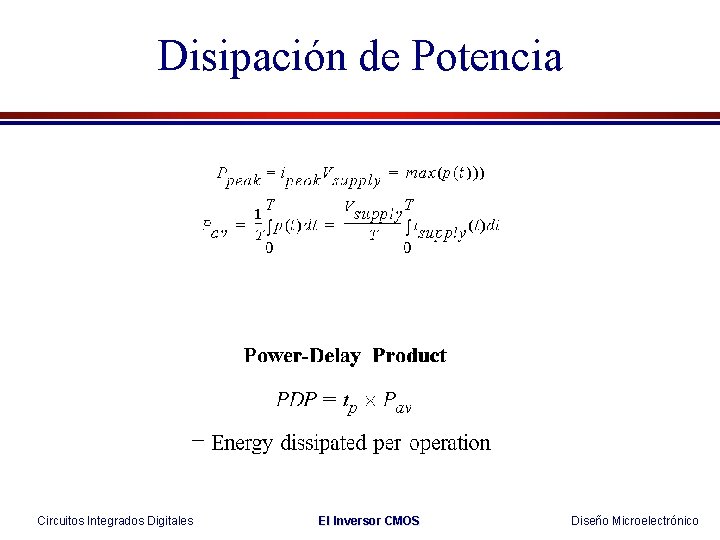

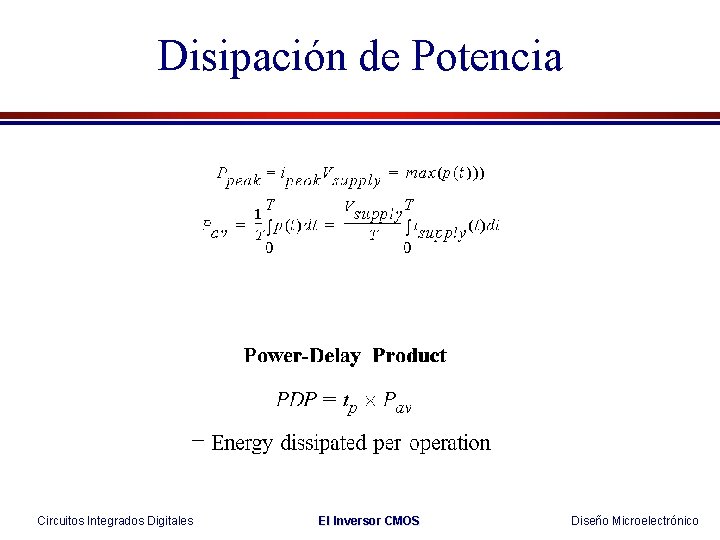

Disipación de Potencia Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

EL INVERSOR CMOS Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

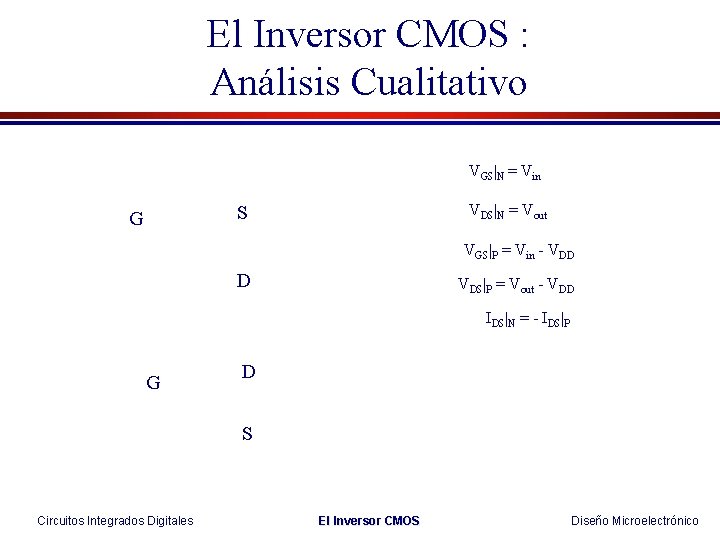

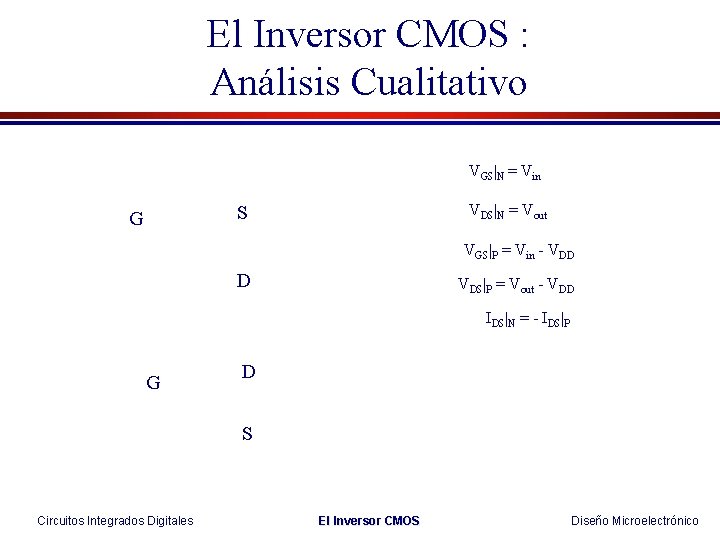

El Inversor CMOS : Análisis Cualitativo VGS|N = Vin VDS|N = Vout S G VGS|P = Vin - VDD D VDS|P = Vout - VDD IDS|N = - IDS|P G D S Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

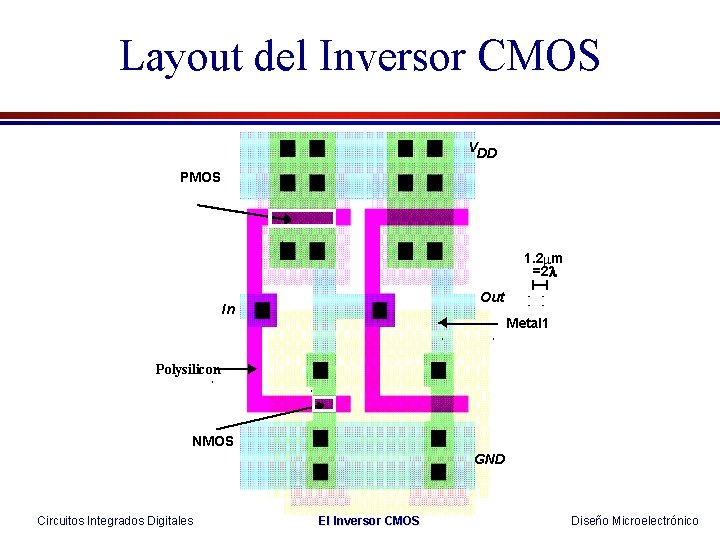

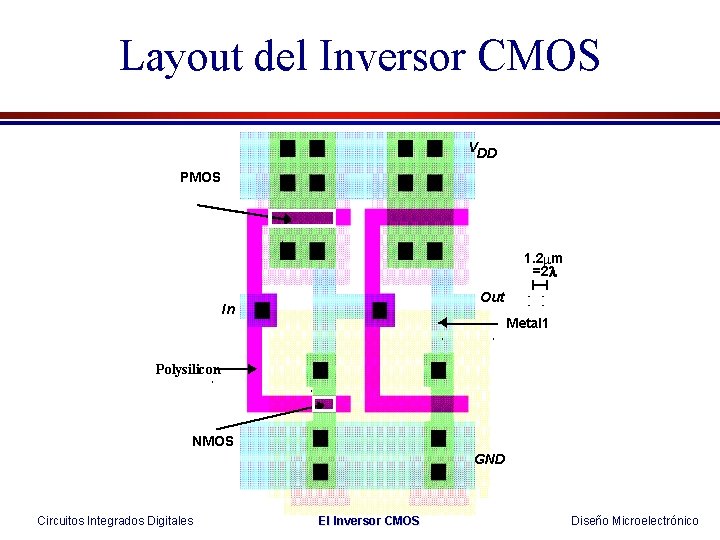

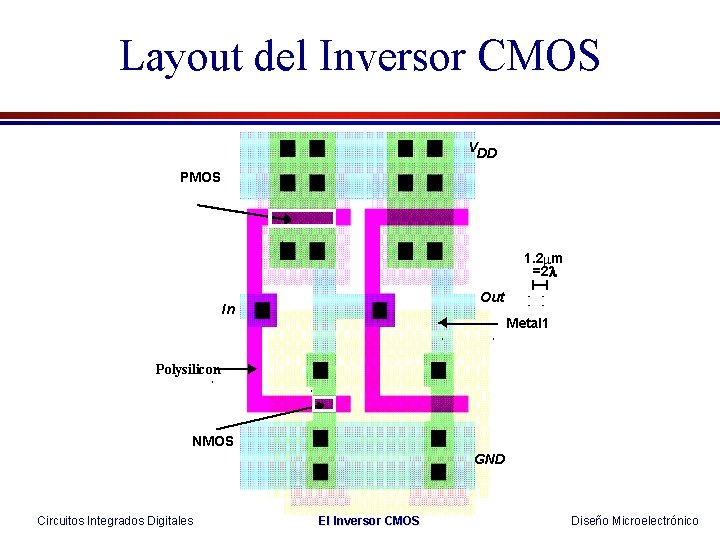

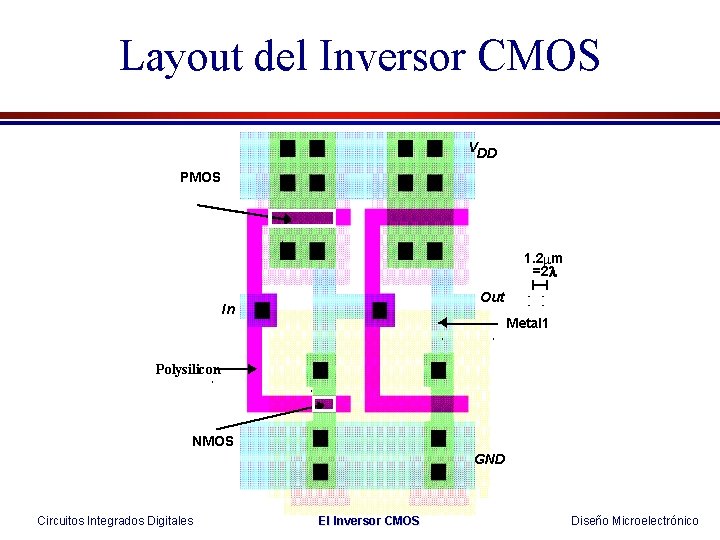

Layout del Inversor CMOS VDD PMOS 1. 2 mm =2 l Out In Metal 1 Polysilicon NMOS GND Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Proceso CMOS de doble pozo con aislamiento por muro de óxido Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

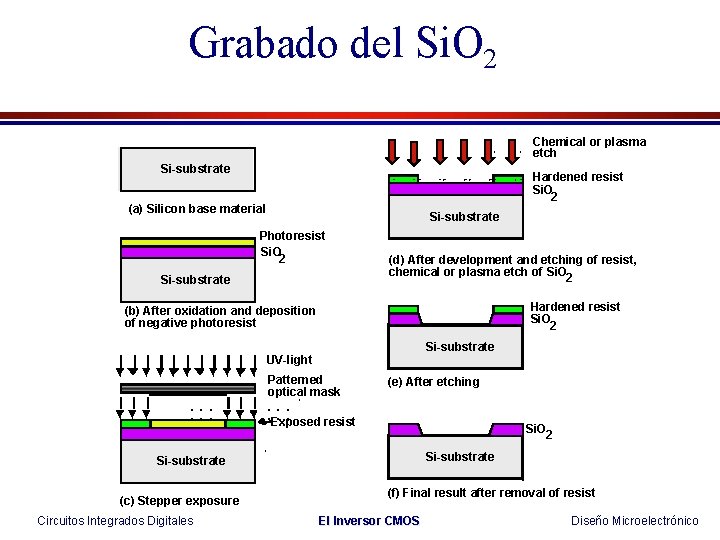

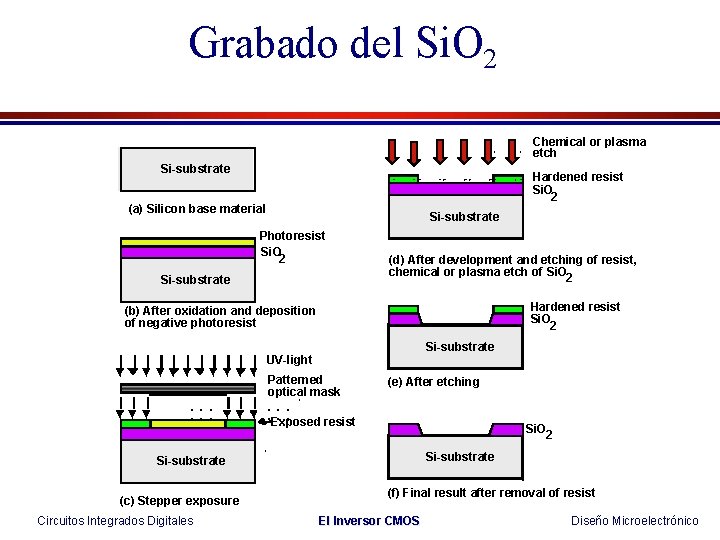

Grabado del Si. O 2 Chemical or plasma etch Si-substrate Hardened resist Si. O 2 (a) Silicon base material Si-substrate Photoresist Si. O 2 Si-substrate (d) After development and etching of resist, chemical or plasma etch of Si. O 2 Hardened resist Si. O 2 (b) After oxidation and deposition of negative photoresist Si-substrate UV-light Patterned optical mask (e) After etching Exposed resist Si. O 2 Si-substrate (c) Stepper exposure Circuitos Integrados Digitales (f) Final result after removal of resist El Inversor CMOS Diseño Microelectrónico

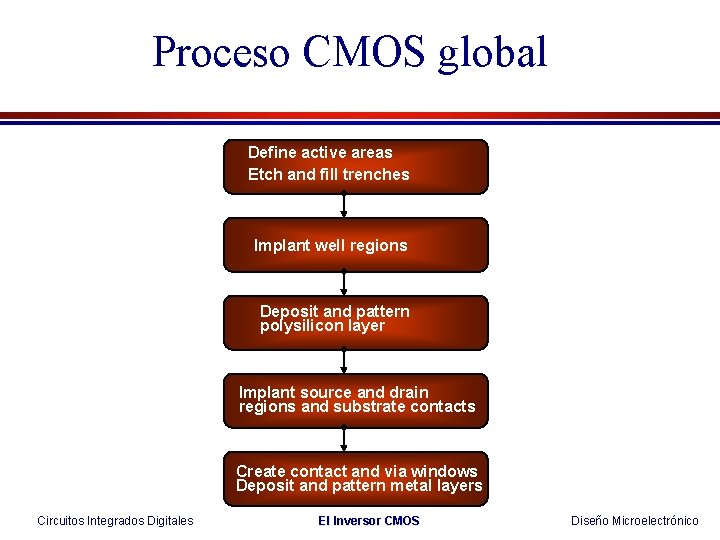

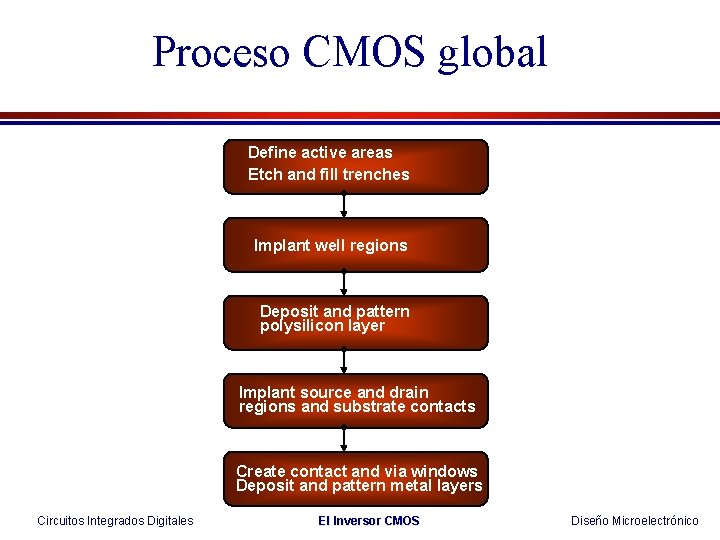

Proceso CMOS global Define active areas Etch and fill trenches Implant well regions Deposit and pattern polysilicon layer Implant source and drain regions and substrate contacts Create contact and via windows Deposit and pattern metal layers Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

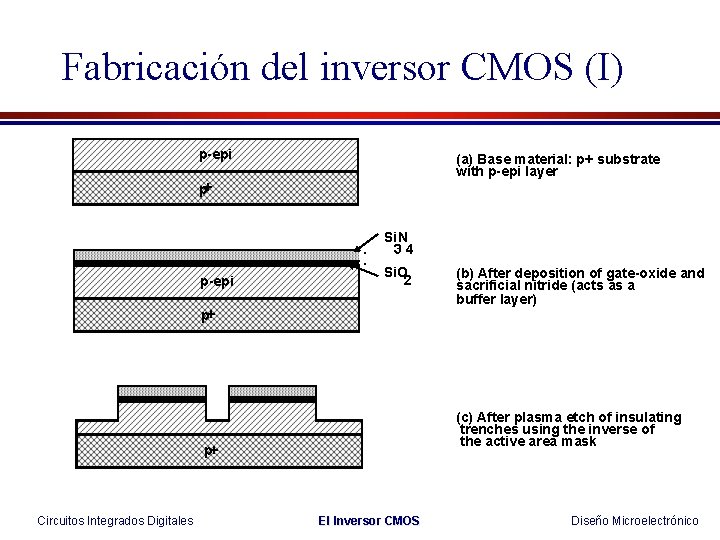

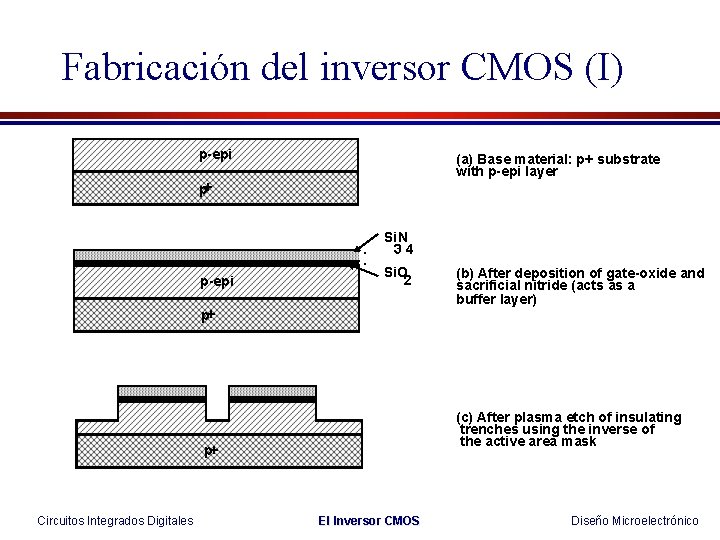

Fabricación del inversor CMOS (I) p-epi (a) Base material: p+ substrate with p-epi layer p+ Si. N 34 p-epi Si. O 2 p+ (c) After plasma etch of insulating trenches using the inverse of the active area mask p+ Circuitos Integrados Digitales (b) After deposition of gate-oxide and sacrificial nitride (acts as a buffer layer) El Inversor CMOS Diseño Microelectrónico

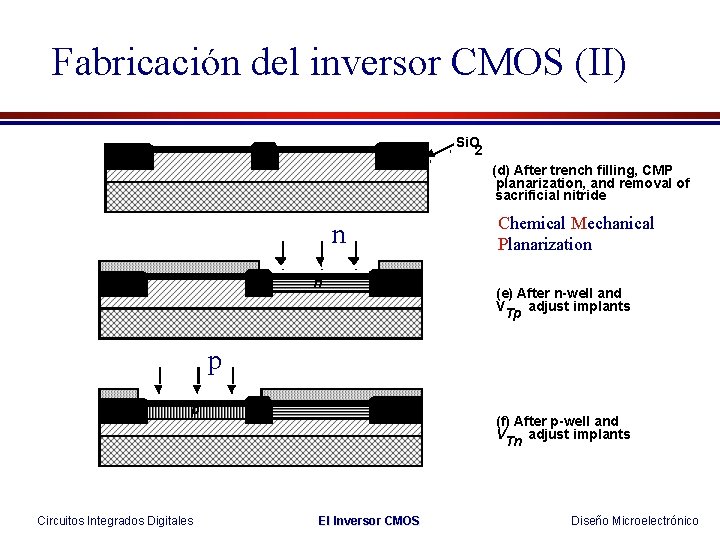

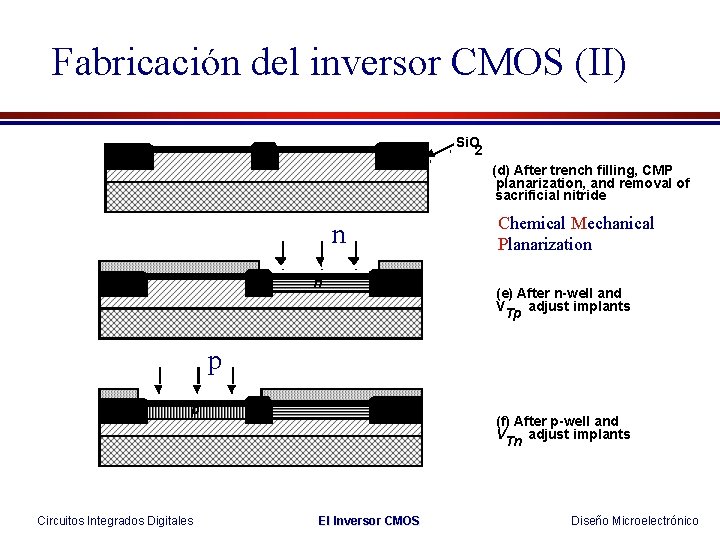

Fabricación del inversor CMOS (II) Si. O 2 (d) After trench filling, CMP planarization, and removal of sacrificial nitride n n Chemical Mechanical Planarization (e) After n-well and V adjust implants Tp p p Circuitos Integrados Digitales (f) After p-well and V adjust implants Tn El Inversor CMOS Diseño Microelectrónico

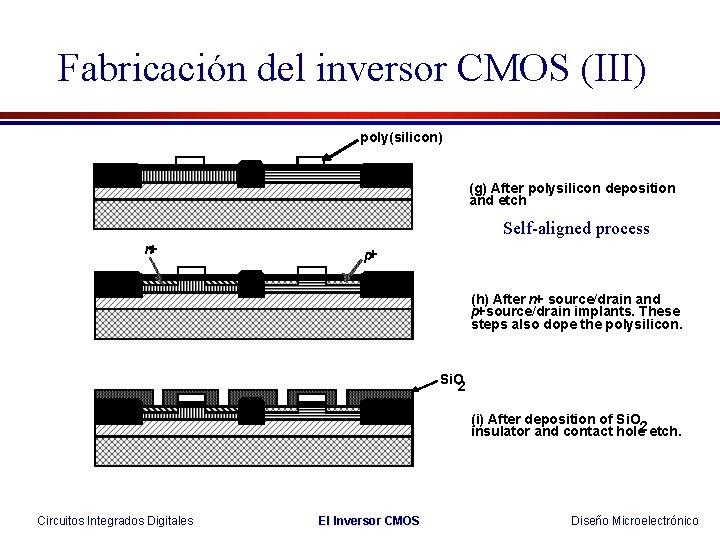

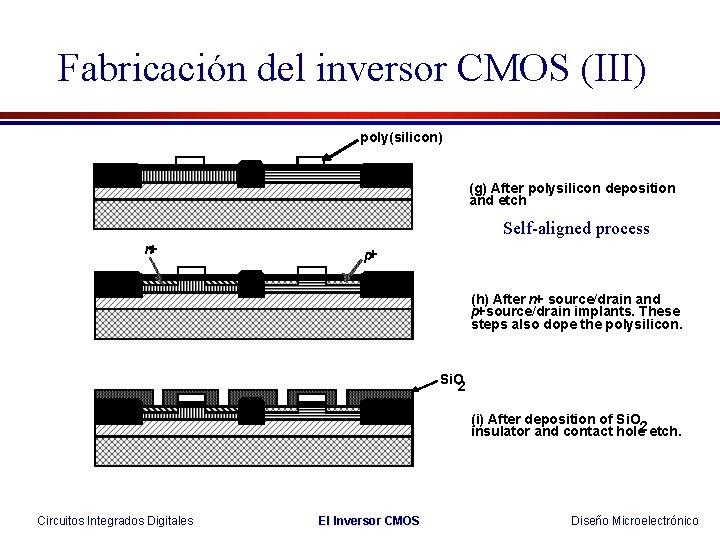

Fabricación del inversor CMOS (III) poly(silicon) (g) After polysilicon deposition and etch Self-aligned process n+ p+ (h) After n+ source/drain and p+ source/drain implants. These steps also dope the polysilicon. Si. O 2 (i) After deposition of Si. O insulator and contact hole 2 etch. Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

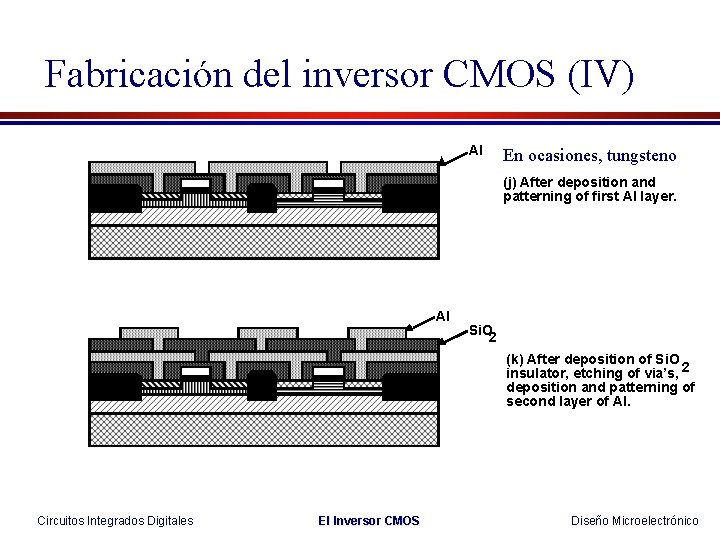

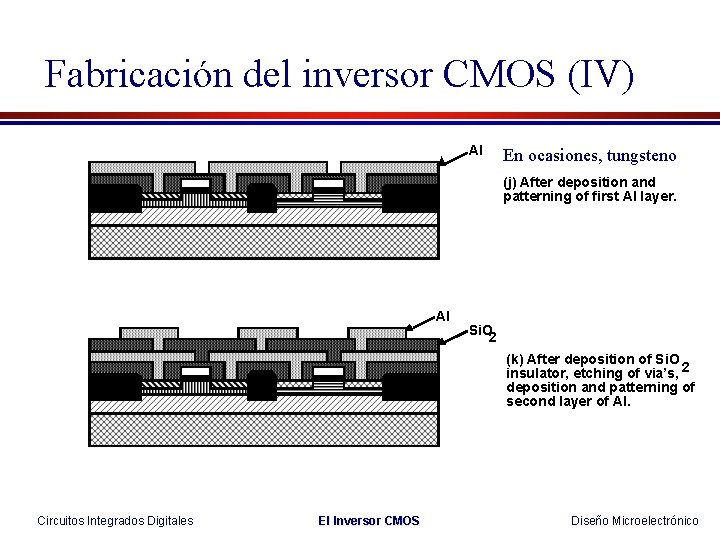

Fabricación del inversor CMOS (IV) Al En ocasiones, tungsteno (j) After deposition and patterning of first Al layer. Al Si. O 2 (k) After deposition of Si. O insulator, etching of via’s, 2 deposition and patterning of second layer of Al. Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Metalización avanzada (I) Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

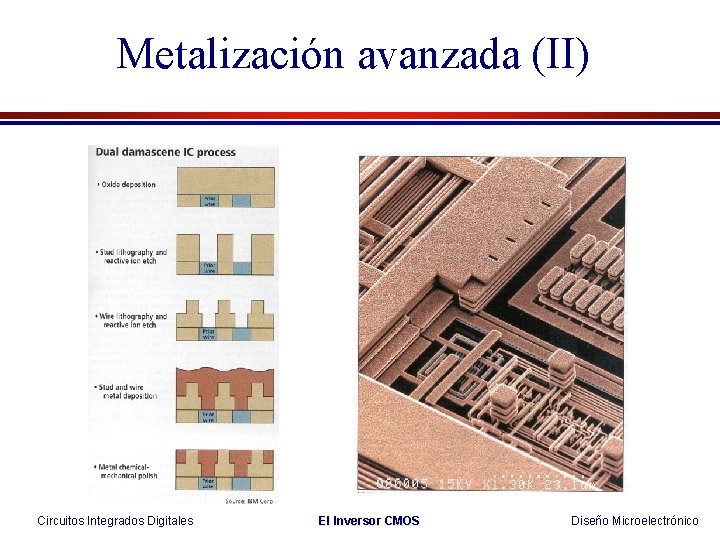

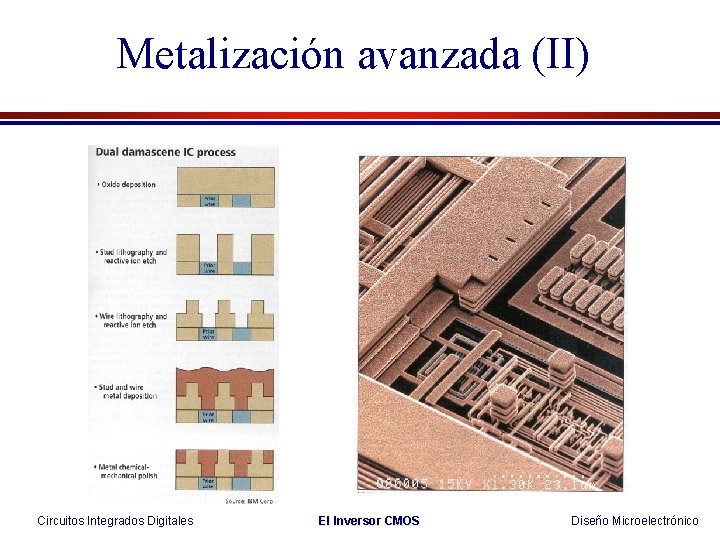

Metalización avanzada (II) Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

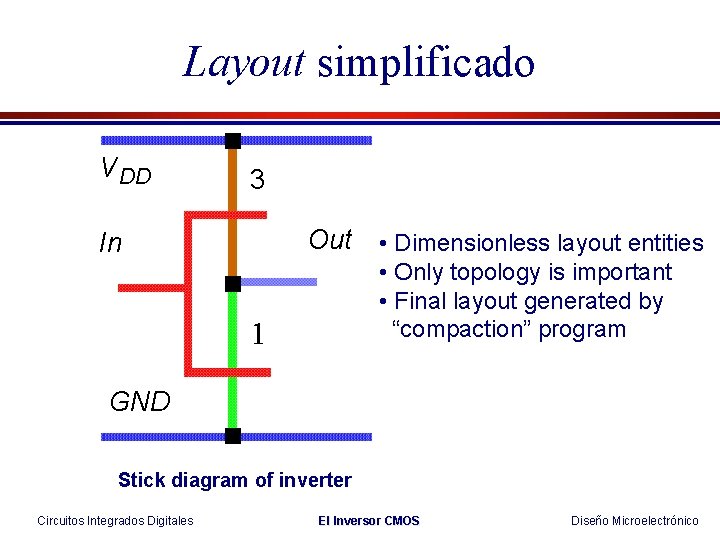

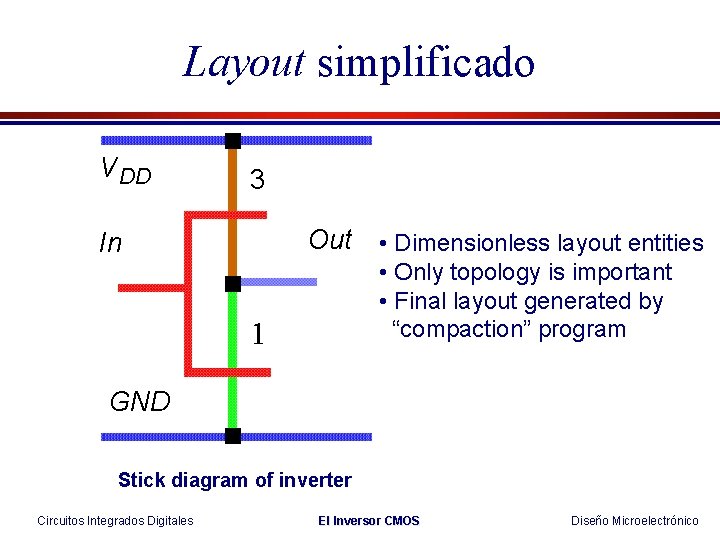

Layout simplificado V DD 3 Out In 1 • Dimensionless layout entities • Only topology is important • Final layout generated by “compaction” program GND Stick diagram of inverter Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

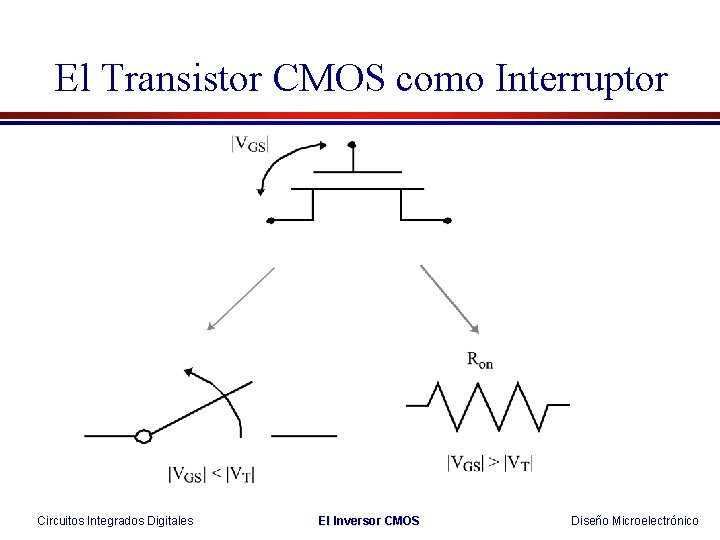

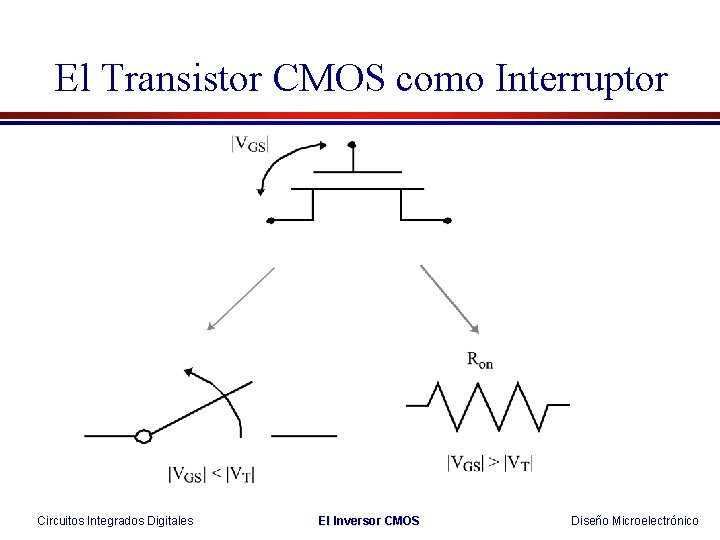

El Transistor CMOS como Interruptor Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

El Inversor CMOS : Comportamiento Estacionario Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

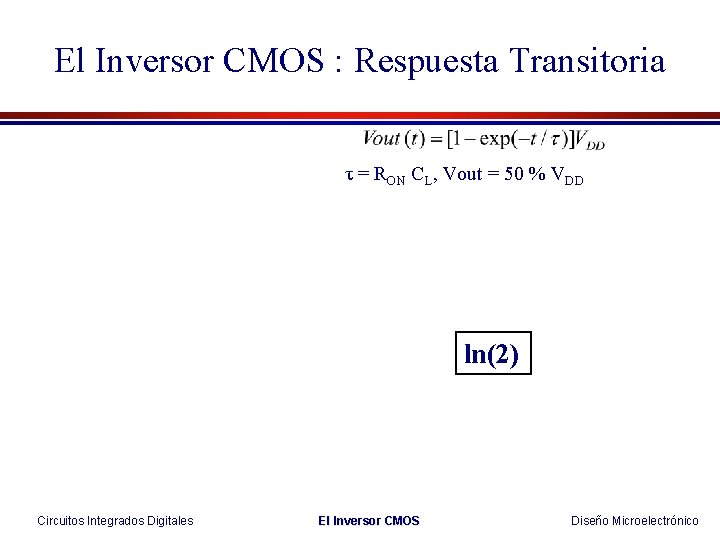

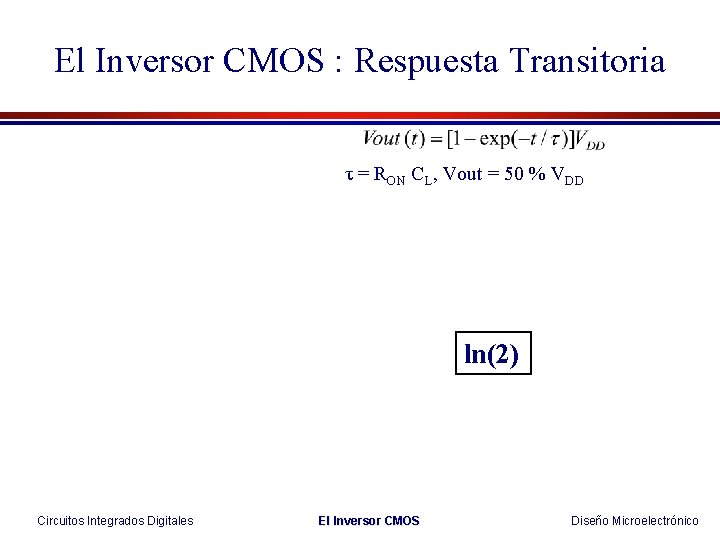

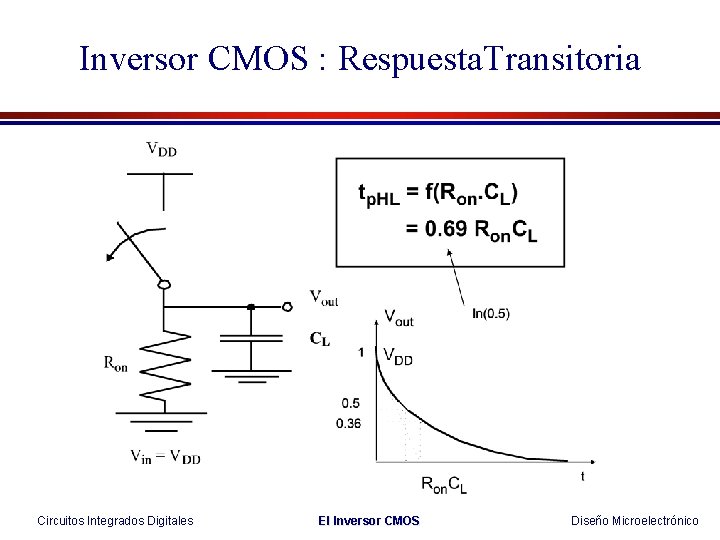

El Inversor CMOS : Respuesta Transitoria τ = RON CL, Vout = 50 % VDD ln(2) Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

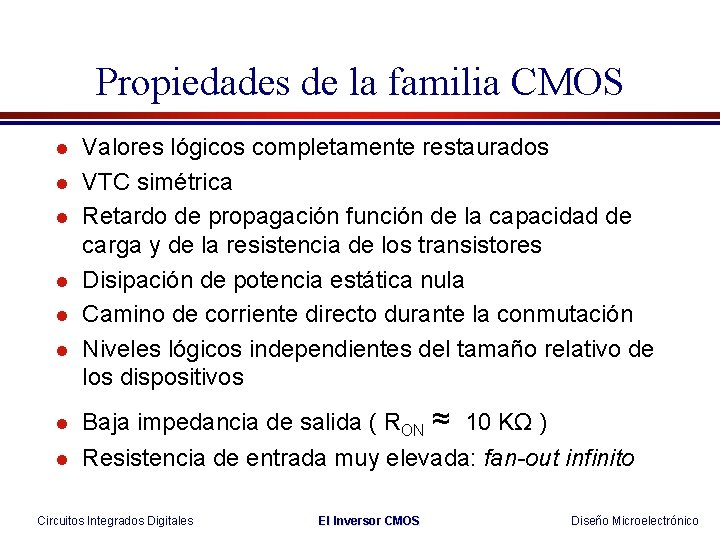

Propiedades de la familia CMOS l l l Valores lógicos completamente restaurados VTC simétrica Retardo de propagación función de la capacidad de carga y de la resistencia de los transistores Disipación de potencia estática nula Camino de corriente directo durante la conmutación Niveles lógicos independientes del tamaño relativo de los dispositivos l Baja impedancia de salida ( RON ≈ 10 KΩ ) l Resistencia de entrada muy elevada: fan-out infinito Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

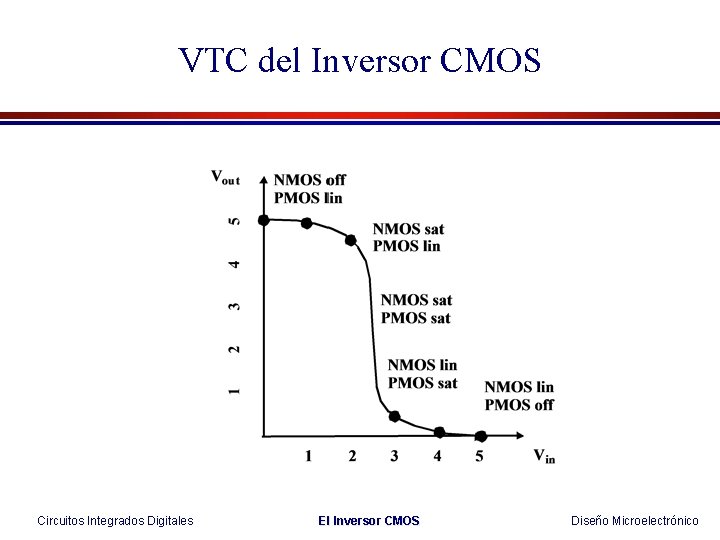

Característica de Transferencia de Voltaje (VTC) Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

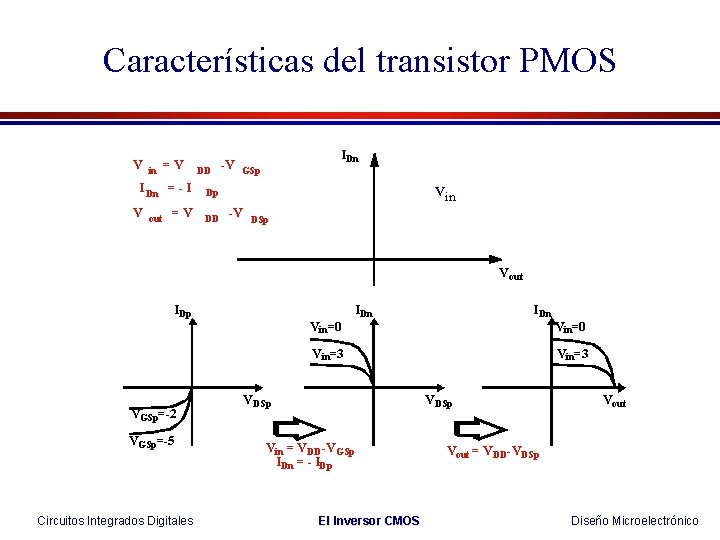

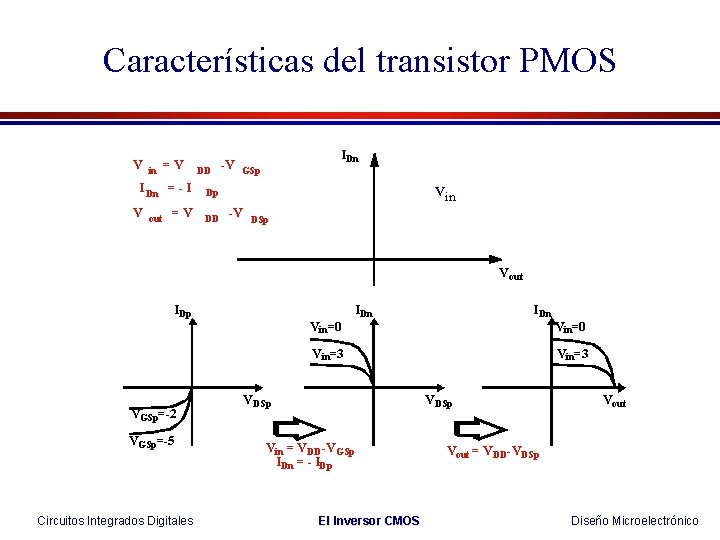

Características del transistor PMOS V in =V I Dn = - I V out =V DD -V IDn GSp vin Dp DD -V DSp Vout IDp Vin=0 IDn Vin=3 VGSp=-2 VGSp=-5 Circuitos Integrados Digitales V DSp Vin=3 VDSp Vin = VDD-VGSp IDn = - IDp El Inversor CMOS Vin=0 Vout = V DD-VDSp Diseño Microelectrónico

Respuesta del Inversor CMOS vout Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

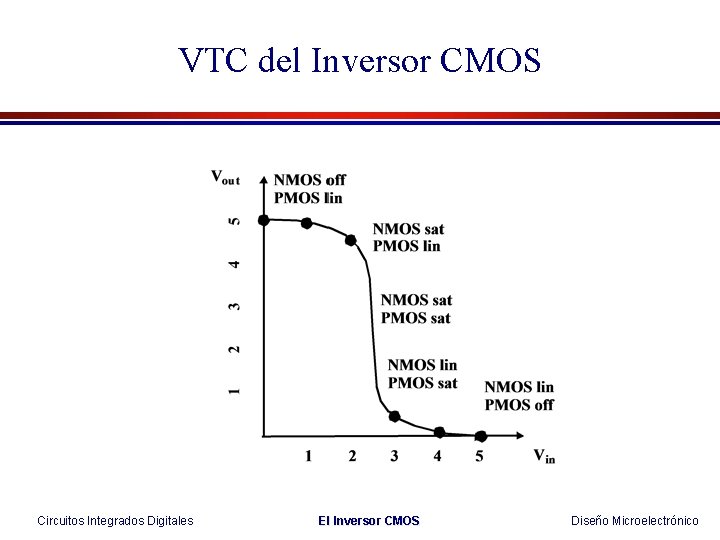

VTC del Inversor CMOS Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

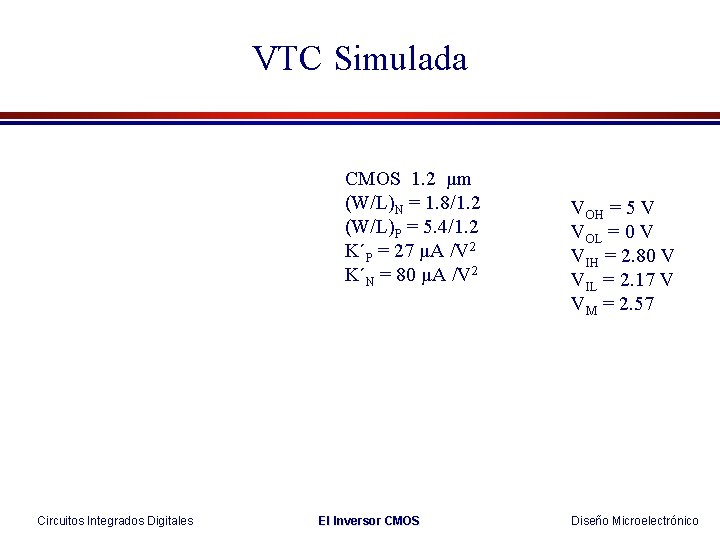

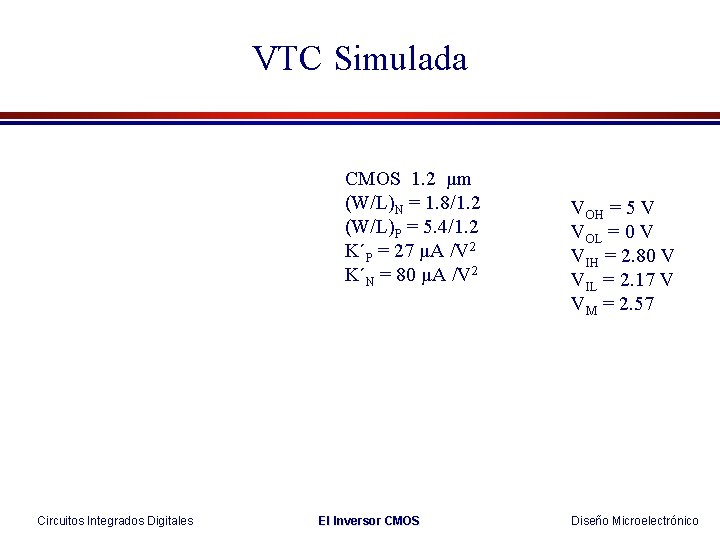

VTC Simulada CMOS 1. 2 μm (W/L)N = 1. 8/1. 2 (W/L)P = 5. 4/1. 2 K´P = 27 μA /V 2 K´N = 80 μA /V 2 Circuitos Integrados Digitales El Inversor CMOS VOH = 5 V VOL = 0 V VIH = 2. 80 V VIL = 2. 17 V VM = 2. 57 Diseño Microelectrónico

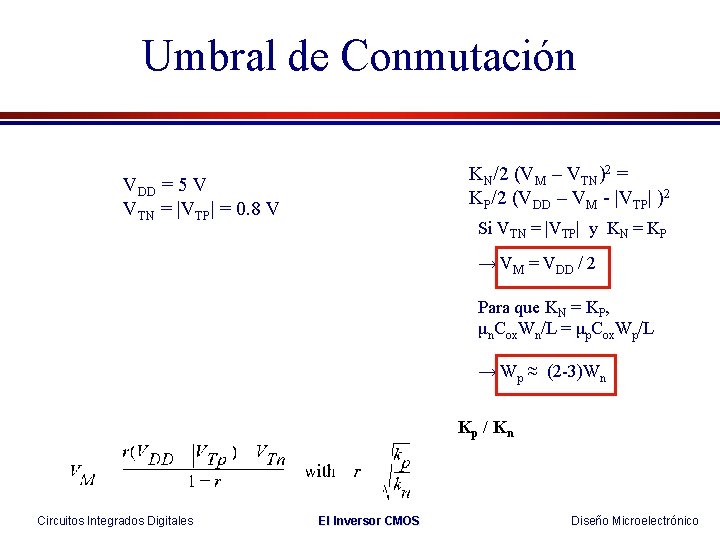

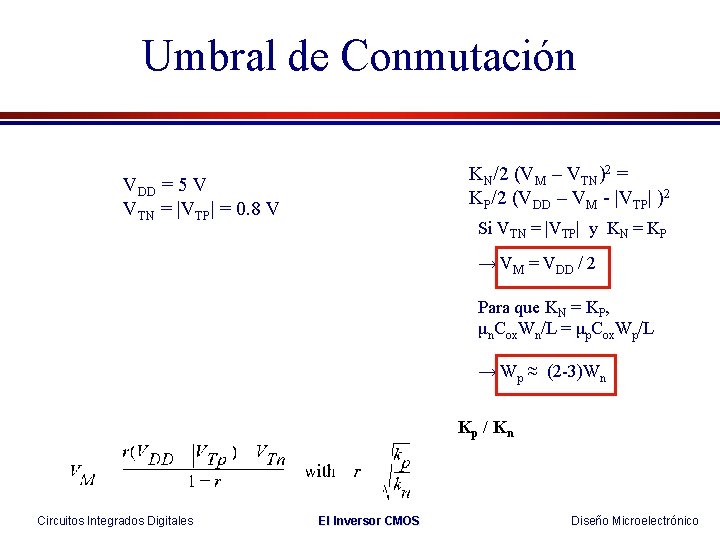

Umbral de Conmutación KN/2 (VM – VTN)2 = KP/2 (VDD – VM - |VTP| )2 VDD = 5 V VTN = |VTP| = 0. 8 V Si VTN = |VTP| y KN = KP → VM = VDD / 2 Para que KN = KP, μn. Cox. Wn/L = μp. Cox. Wp/L → Wp ≈ (2 -3)Wn Kp / Kn Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

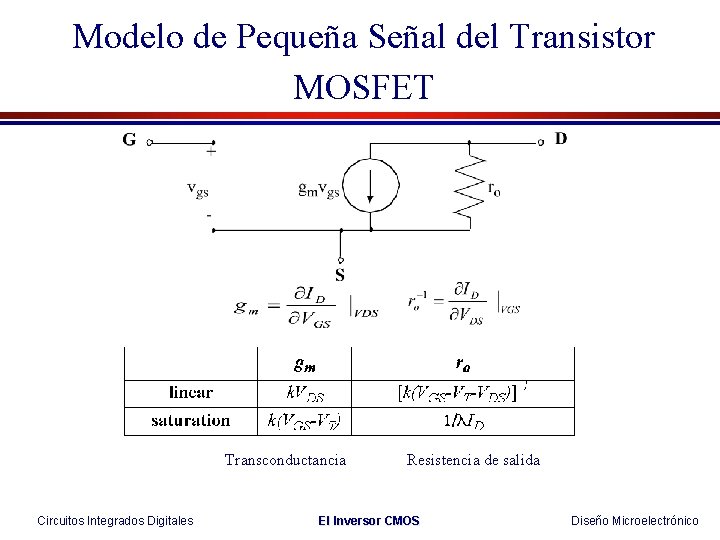

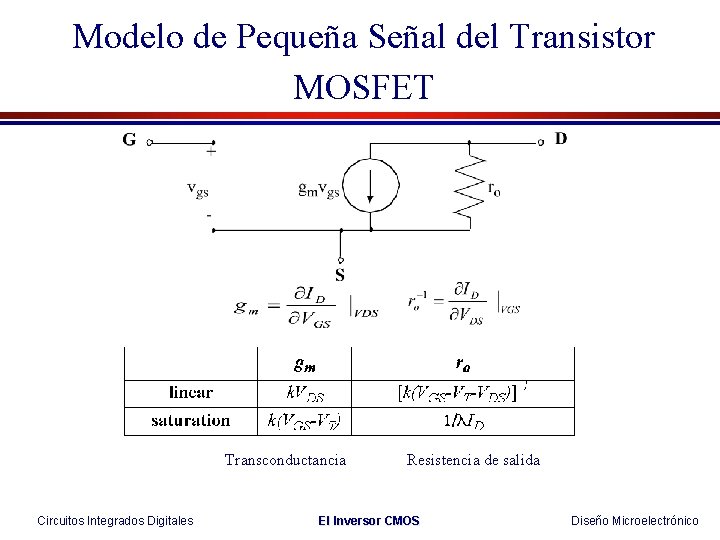

Modelo de Pequeña Señal del Transistor MOSFET Transconductancia Circuitos Integrados Digitales Resistencia de salida El Inversor CMOS Diseño Microelectrónico

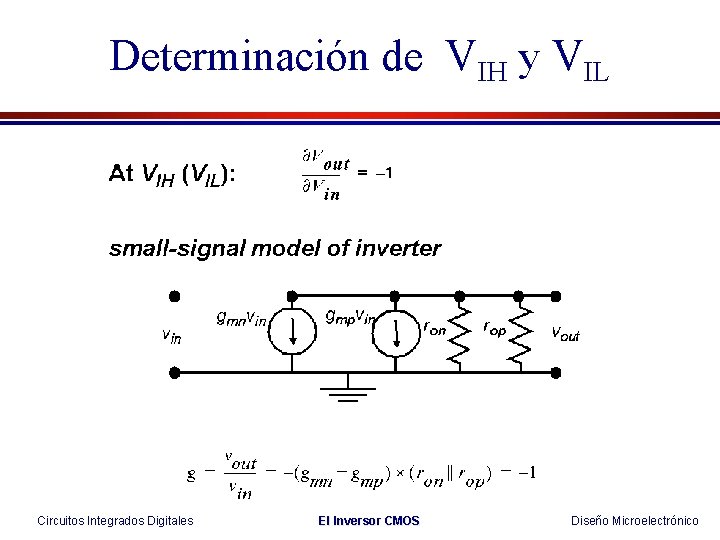

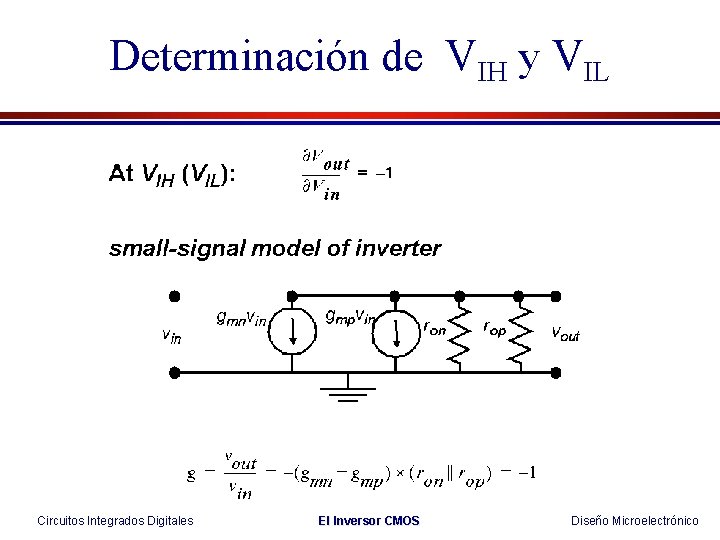

Determinación de VIH y VIL Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Retardo de Propagación Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

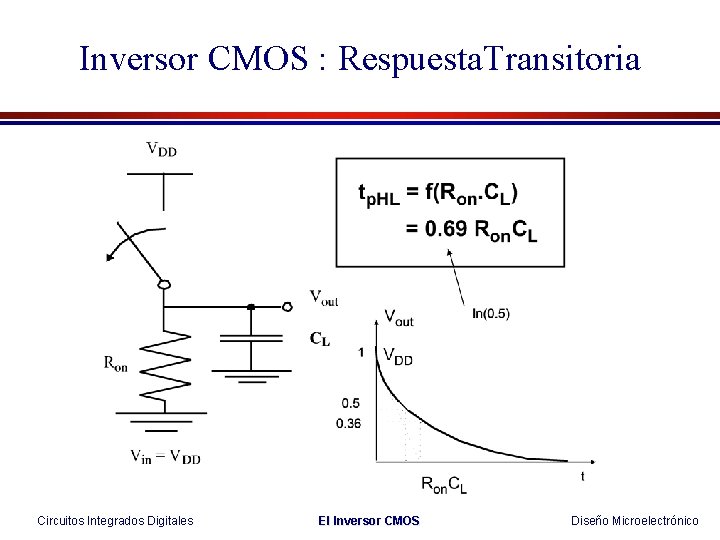

Inversor CMOS : Respuesta. Transitoria Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

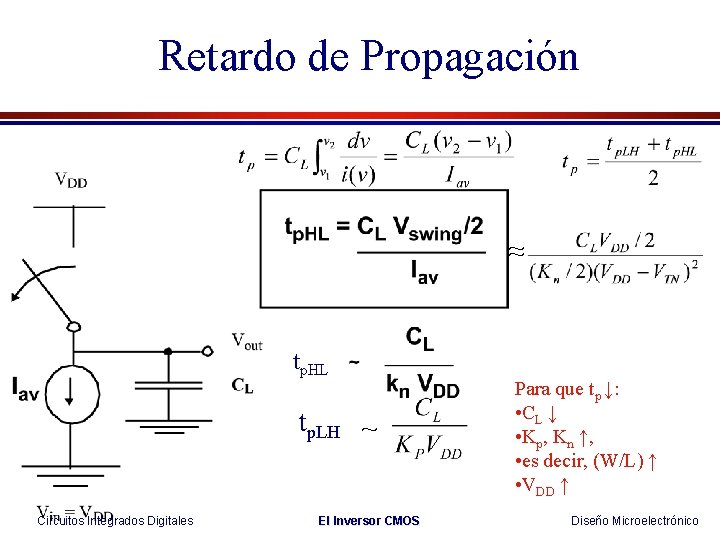

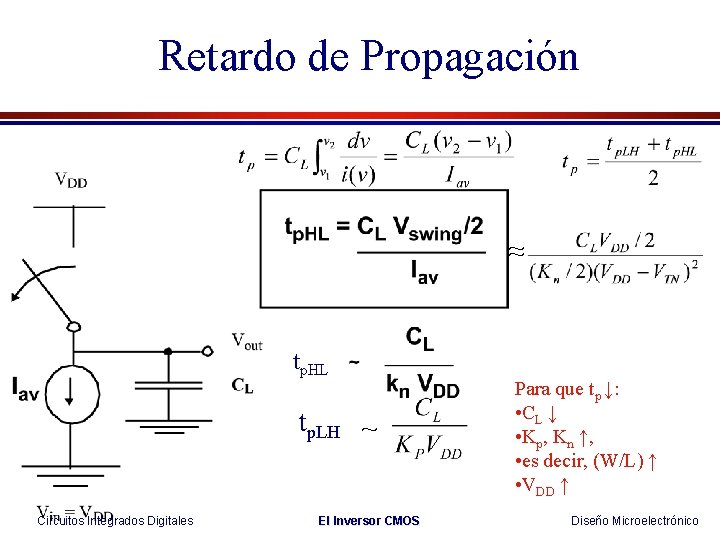

Retardo de Propagación ≈ tp. HL tp. LH ~ Circuitos Integrados Digitales El Inversor CMOS Para que tp ↓: • C L ↓ • Kp, Kn ↑, • es decir, (W/L) ↑ • VDD ↑ Diseño Microelectrónico

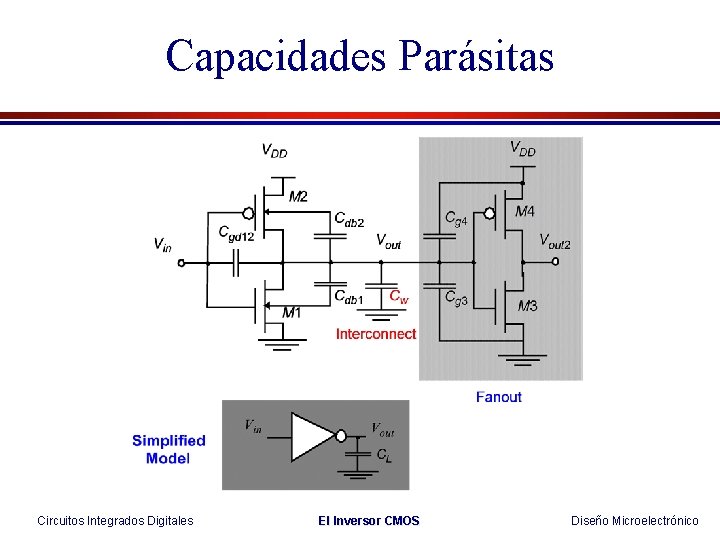

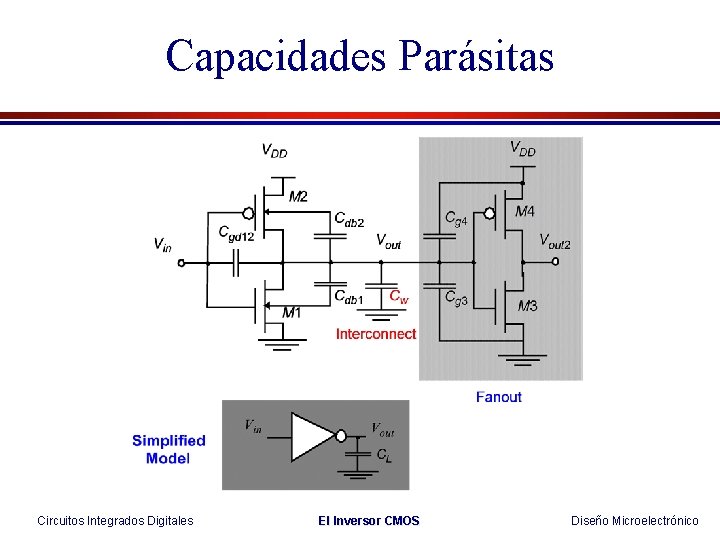

Capacidades Parásitas Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

El Efecto Miller Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Layout del Inversor CMOS VDD PMOS 1. 2 mm =2 l Out In Metal 1 Polysilicon NMOS GND Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

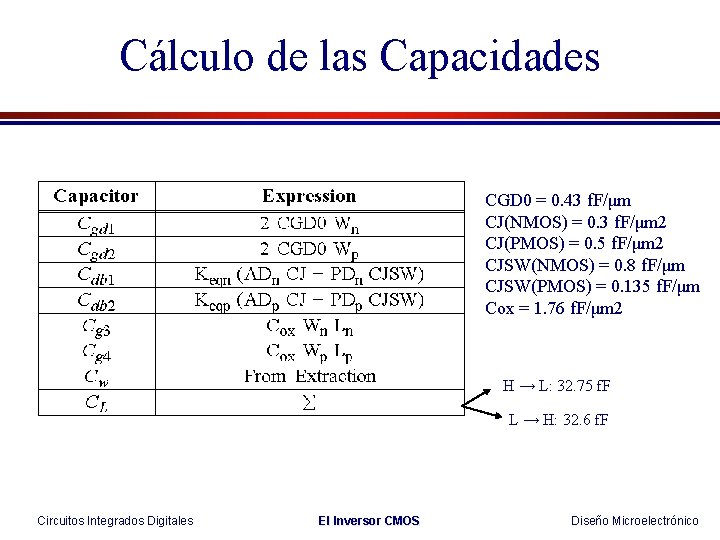

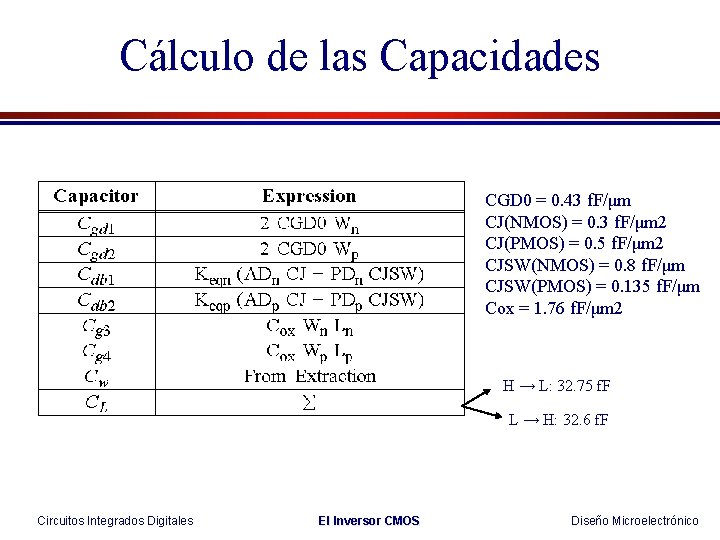

Cálculo de las Capacidades CGD 0 = 0. 43 f. F/μm CJ(NMOS) = 0. 3 f. F/μm 2 CJ(PMOS) = 0. 5 f. F/μm 2 CJSW(NMOS) = 0. 8 f. F/μm CJSW(PMOS) = 0. 135 f. F/μm Cox = 1. 76 f. F/μm 2 H → L: 32. 75 f. F L → H: 32. 6 f. F Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

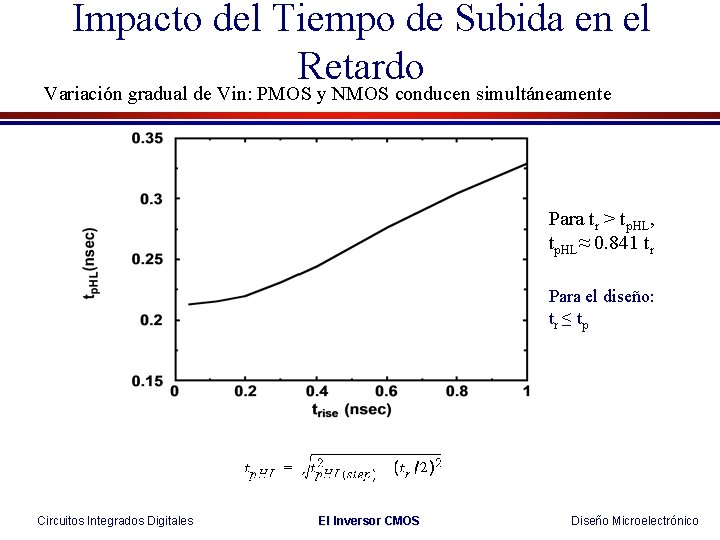

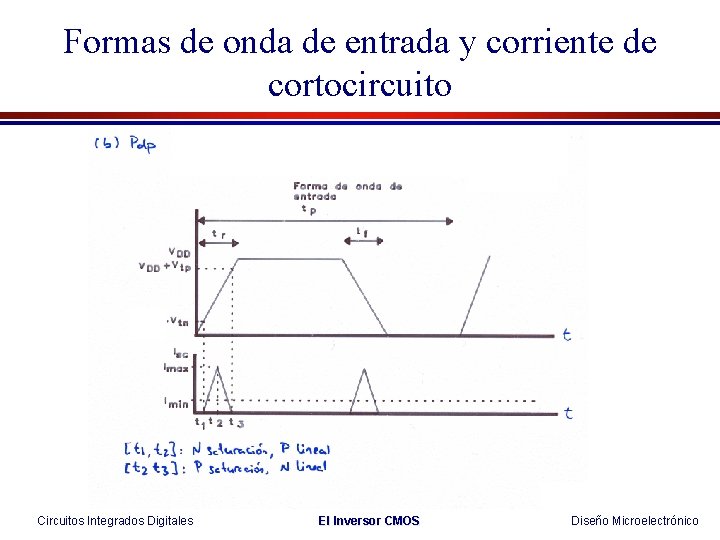

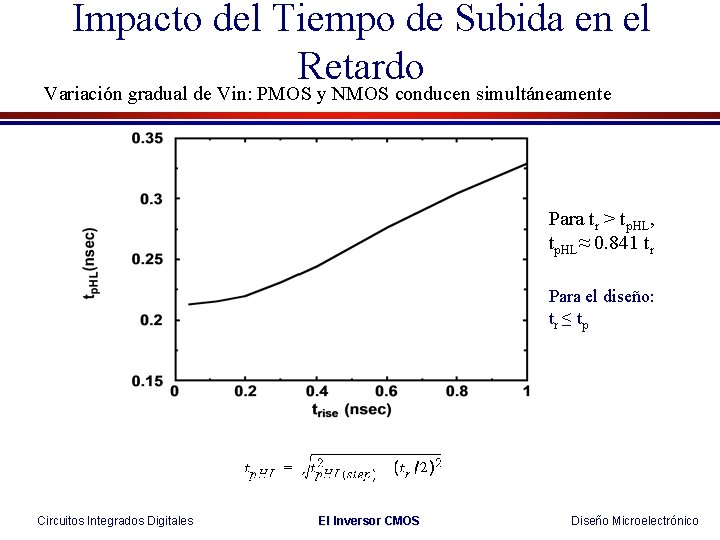

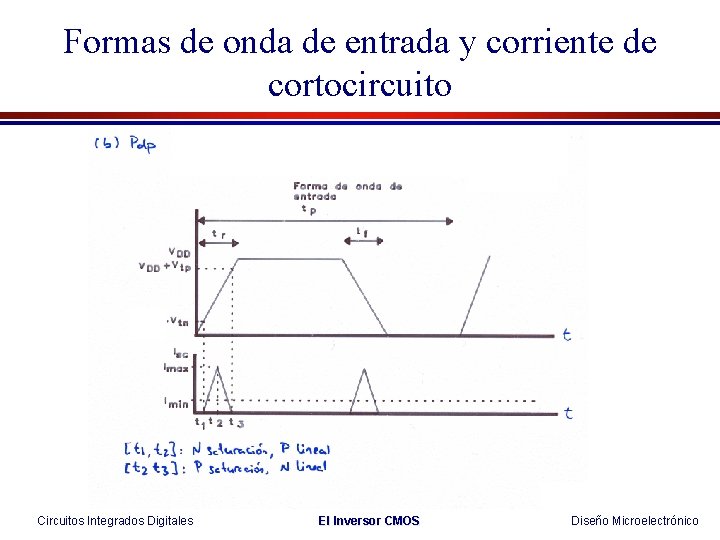

Impacto del Tiempo de Subida en el Retardo Variación gradual de Vin: PMOS y NMOS conducen simultáneamente Para tr > tp. HL, tp. HL≈ 0. 841 tr Para el diseño: tr ≤ tp Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

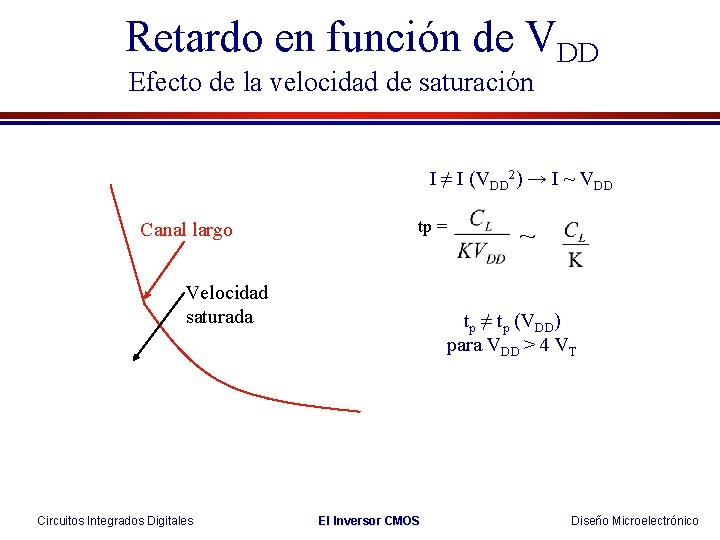

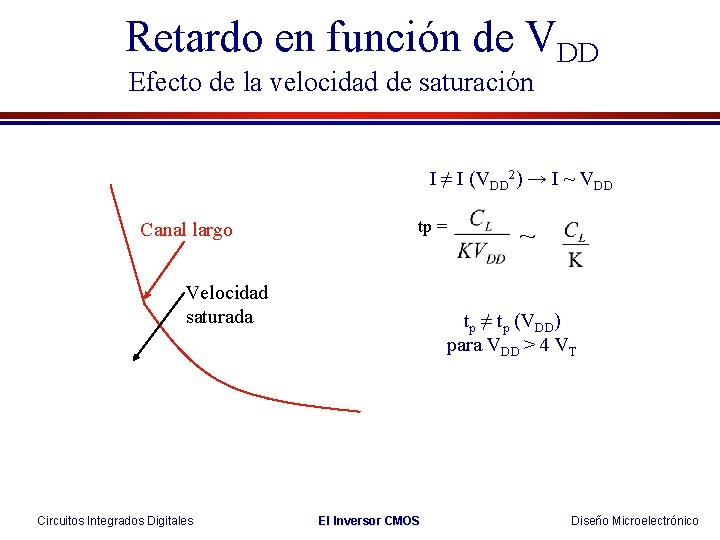

Retardo en función de VDD Efecto de la velocidad de saturación I ≠ I (VDD 2) → I ~ VDD Canal largo tp = Velocidad saturada Circuitos Integrados Digitales ~ tp ≠ tp (VDD) para VDD > 4 VT El Inversor CMOS Diseño Microelectrónico

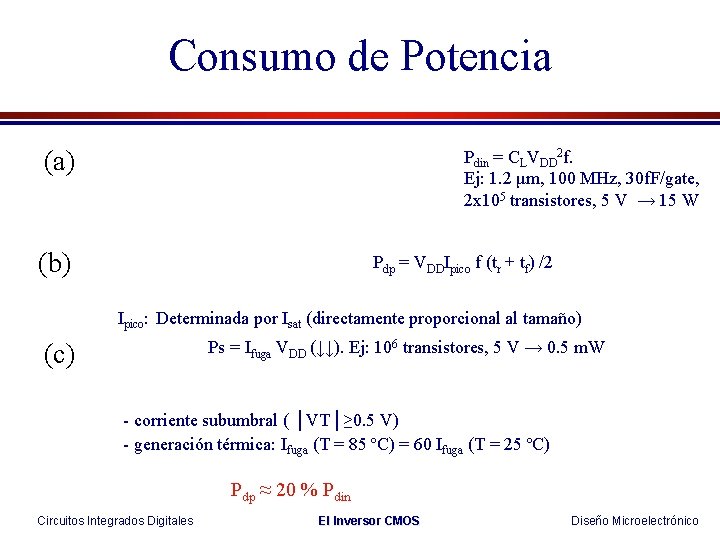

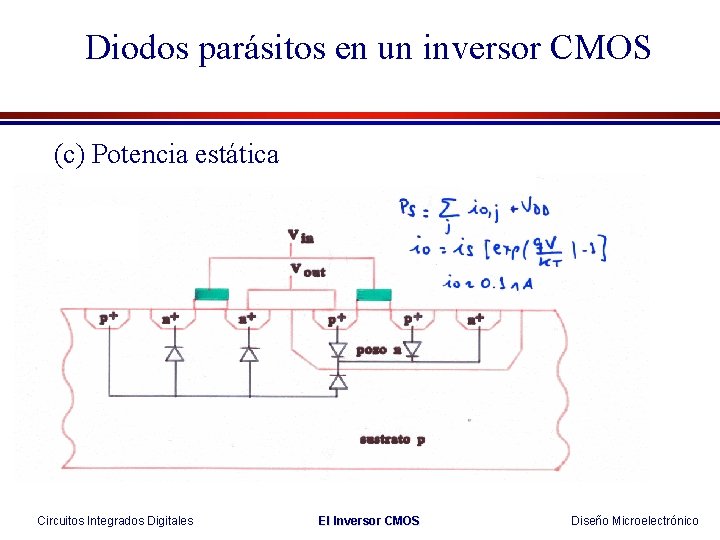

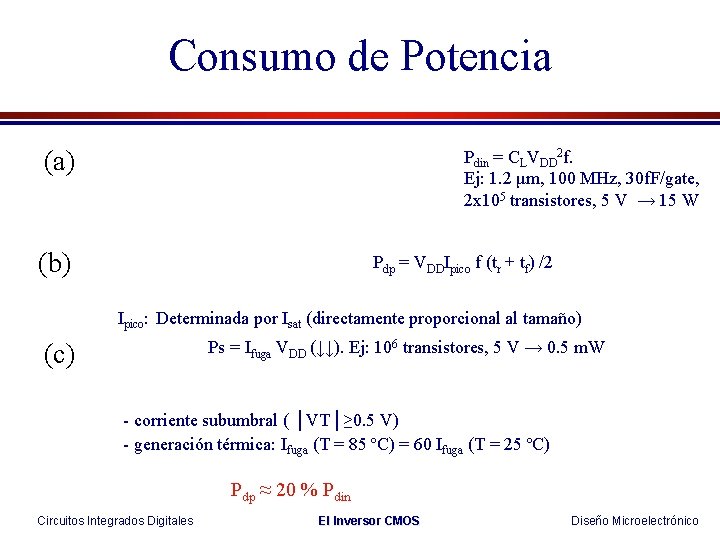

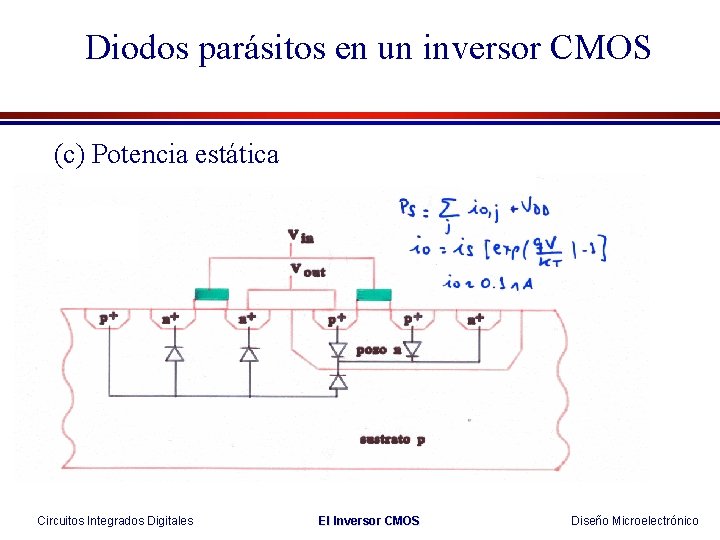

Consumo de Potencia (a) Pdin = CLVDD 2 f. Ej: 1. 2 μm, 100 MHz, 30 f. F/gate, 2 x 105 transistores, 5 V → 15 W (b) Pdp = VDDIpico f (tr + tf) /2 Ipico: Determinada por Isat (directamente proporcional al tamaño) Ps = Ifuga VDD (↓↓). Ej: 106 transistores, 5 V → 0. 5 m. W (c) - corriente subumbral ( │VT│≥ 0. 5 V) - generación térmica: Ifuga (T = 85 ºC) = 60 Ifuga (T = 25 ºC) Pdp ≈ 20 % Pdin Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

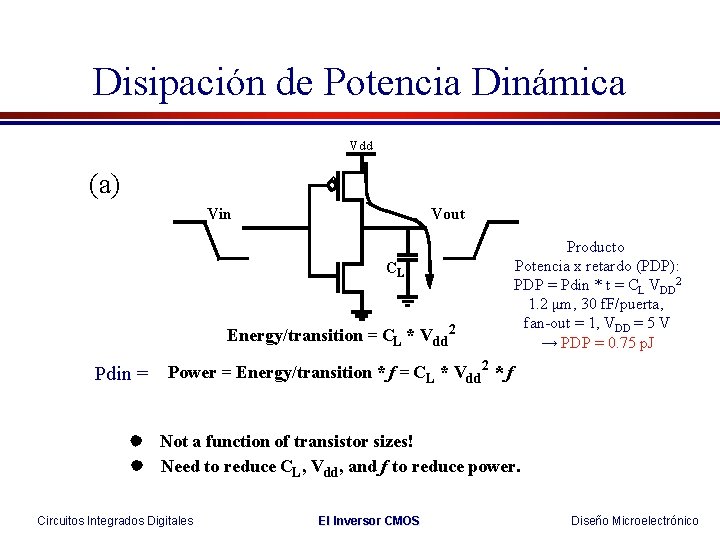

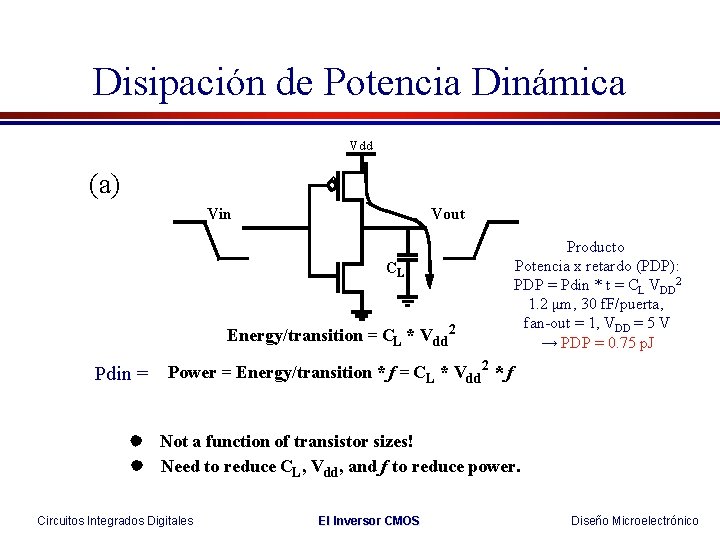

Disipación de Potencia Dinámica Vdd (a) Vin Vout CL Energy/transition = CL * Vdd 2 Pdin = Producto Potencia x retardo (PDP): PDP = Pdin * t = CL VDD 2 1. 2 μm, 30 f. F/puerta, fan-out = 1, VDD = 5 V → PDP = 0. 75 p. J Power = Energy/transition * f = CL * Vdd 2 * f Not a function of transistor sizes! Need to reduce CL, Vdd, and f to reduce power. Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Diodos parásitos en un inversor CMOS (c) Potencia estática Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Formas de onda de entrada y corriente de cortocircuito Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Impacto del Escalado de la Tecnología Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

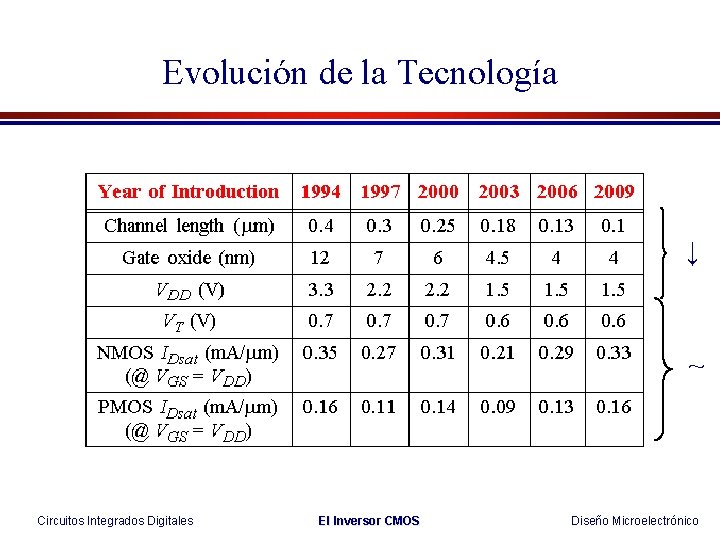

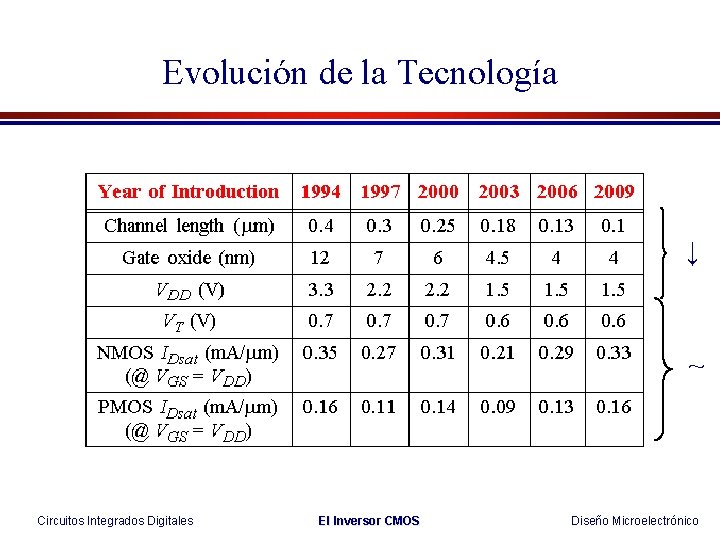

Evolución de la Tecnología ↓ ~ Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

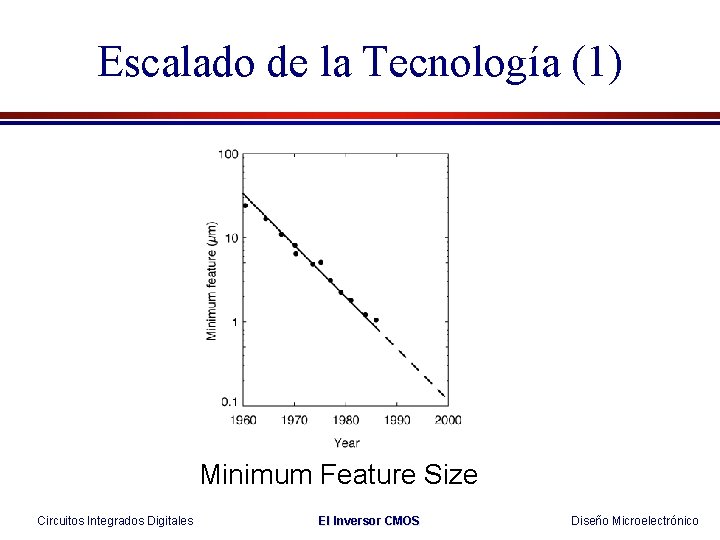

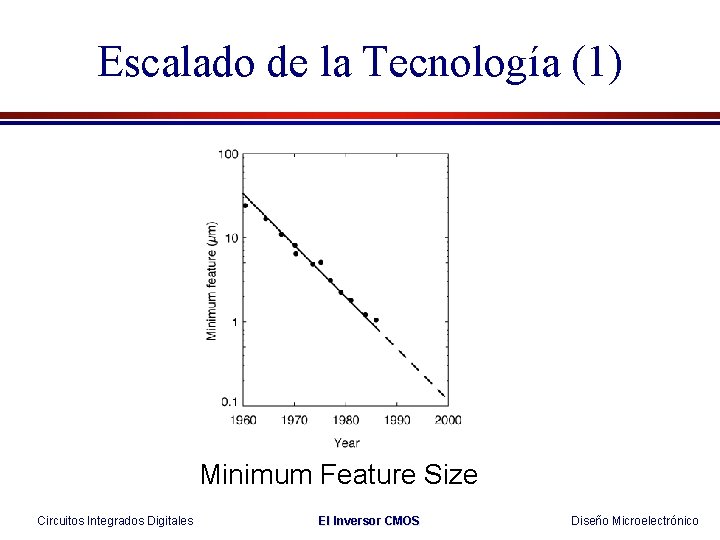

Escalado de la Tecnología (1) Minimum Feature Size Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

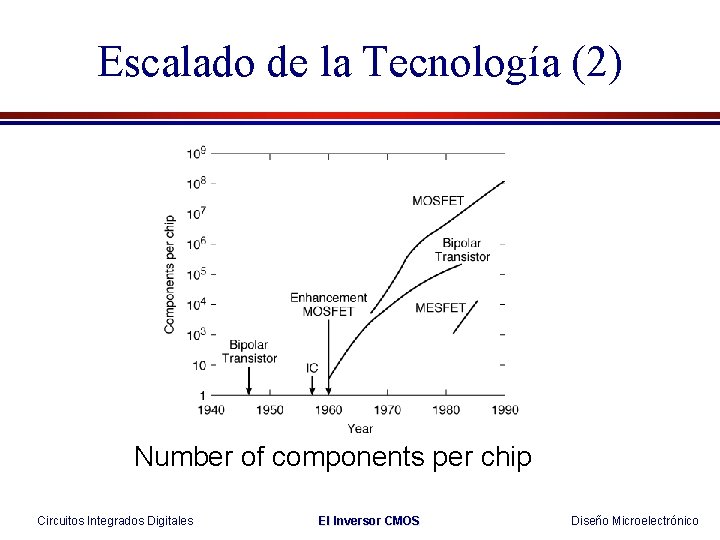

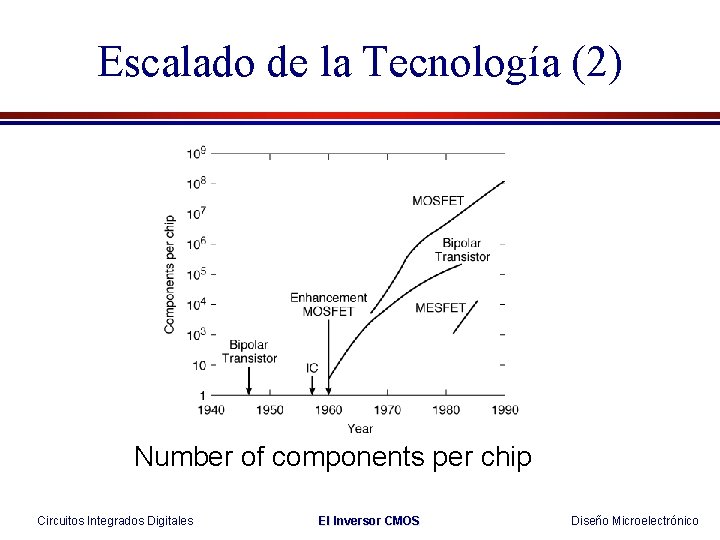

Escalado de la Tecnología (2) Number of components per chip Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

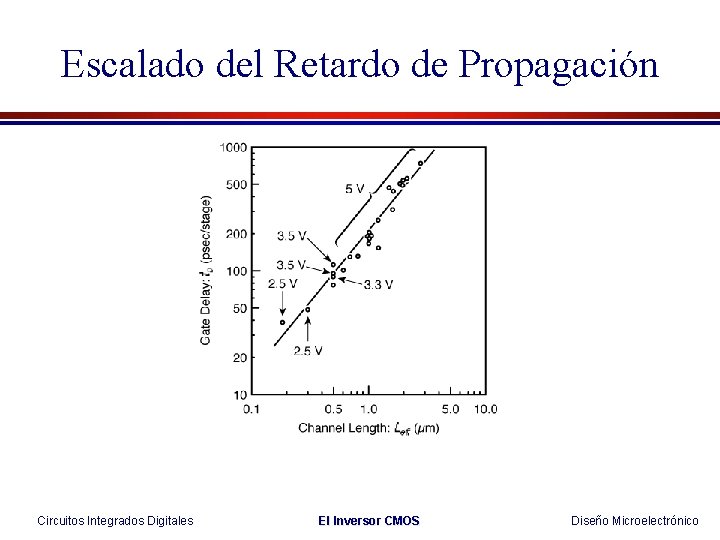

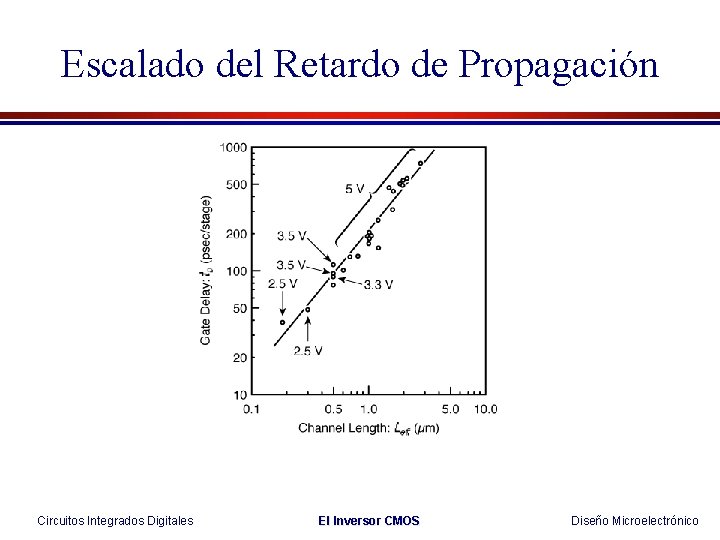

Escalado del Retardo de Propagación Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

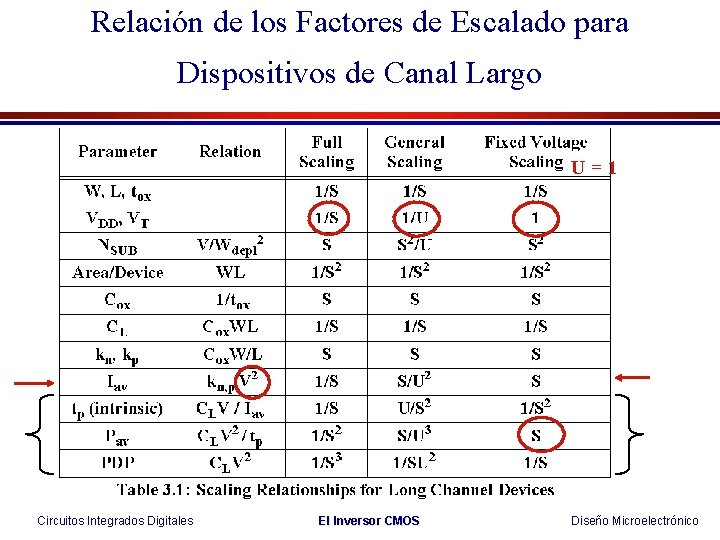

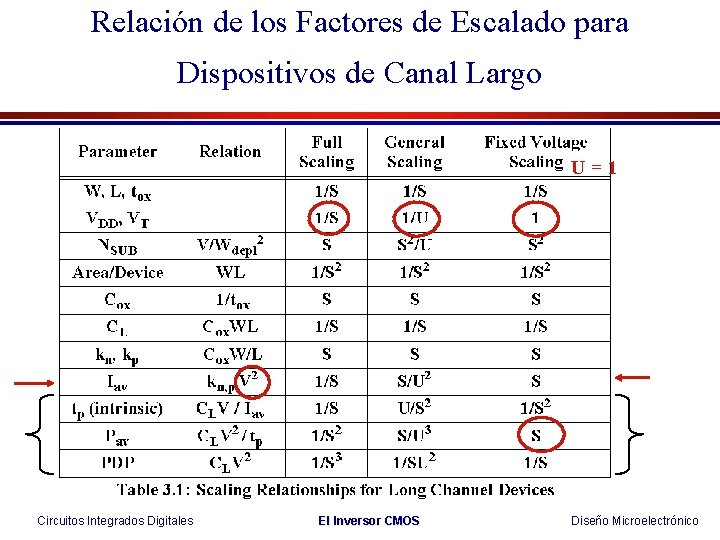

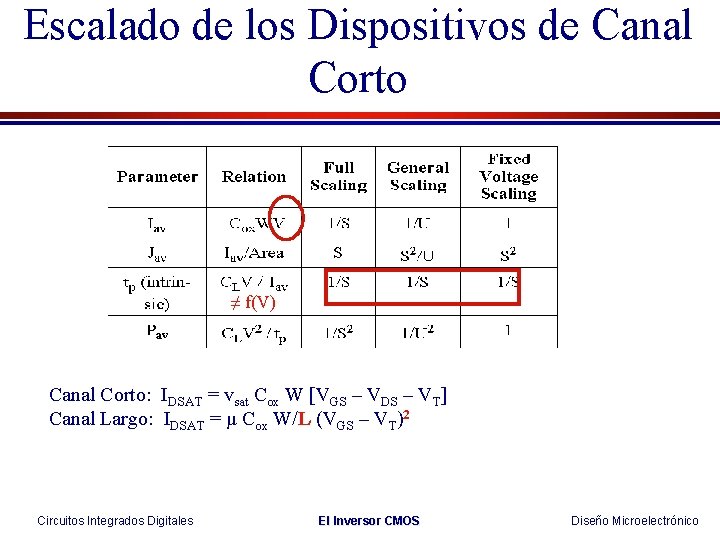

Modelos de Escalado de la Tecnología. Escalado completo (Campo eléctrico constante) Modelo ideal: las tensiones y las dimensiones geométricas Se reducen un mismo factor S. Escalado a tensión constante: Las dimensiones geométricas se reducen un factor S, las tensiones permanecen constantes. Escalado general: Las dimensiones geométricas se reducen un factor S, y las tensiones lo hacen un factor U Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

Relación de los Factores de Escalado para Dispositivos de Canal Largo U=1 Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico

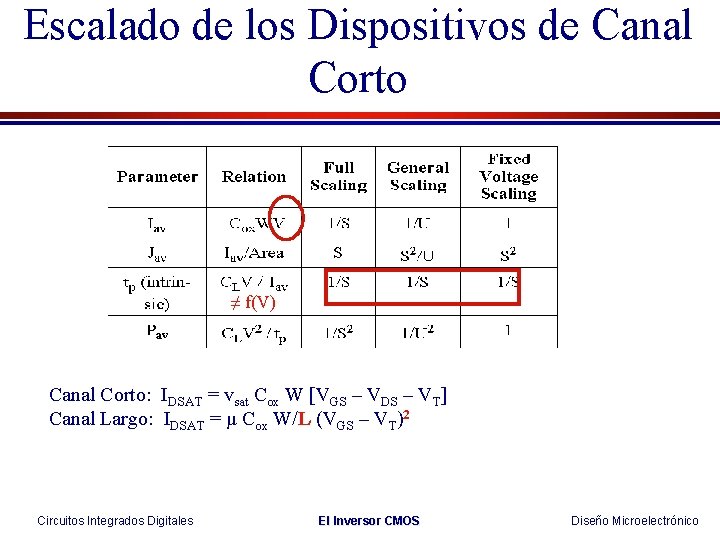

Escalado de los Dispositivos de Canal Corto ≠ f(V) Canal Corto: IDSAT = vsat Cox W [VGS – VDS – VT] Canal Largo: IDSAT = μ Cox W/L (VGS – VT)2 Circuitos Integrados Digitales El Inversor CMOS Diseño Microelectrónico