A 2030 Gbps CMOS Backplane Driver with Digital

A 20/30 Gbps CMOS Backplane Driver with Digital Pre-emphasis • Paul Westergaard, Timothy Dickson, and Sorin Voinigescu • University of Toronto • Canada

Outline • • • Motivation Design Goals Circuit Description and Design Experimental Results Summary and Conclusion

Motivation Application • Serial inter-chip communications over backplanes at 20 -Gb/s. Unfulfilled Needs • CMOS implementation over 10 -Gbps • > 30 d. B dynamic range, low-power • Programmable width and height preemphasis to increase receiver simplicity Prior Art • Previous CMOS backplane drivers have only achieved 10 Gb/s data rate.

Design Goals • 30 -Gb/s main path operation without pre-emphasis • 20 -Gb/s fully featured operation with – ‘digital’ pre-emphasis – eye-crossing – output swing control • High Sensitivity (<10 m. Vpp per side) • Large output swing (>350 m. Vpp per side) • 50 -Ohm input/output matching • 1. 5 V supply • 130 nm CMOS implementation

Circuit Design and Description

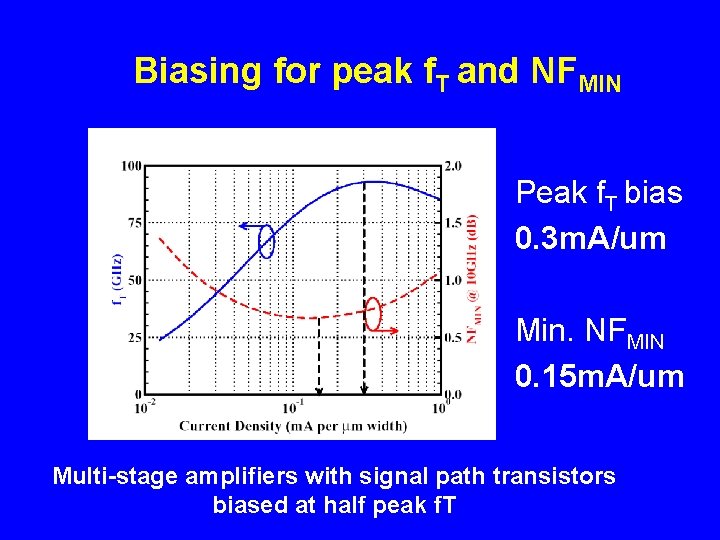

Biasing for peak f. T and NFMIN Peak f. T bias 0. 3 m. A/um Min. NFMIN 0. 15 m. A/um Multi-stage amplifiers with signal path transistors biased at half peak f. T

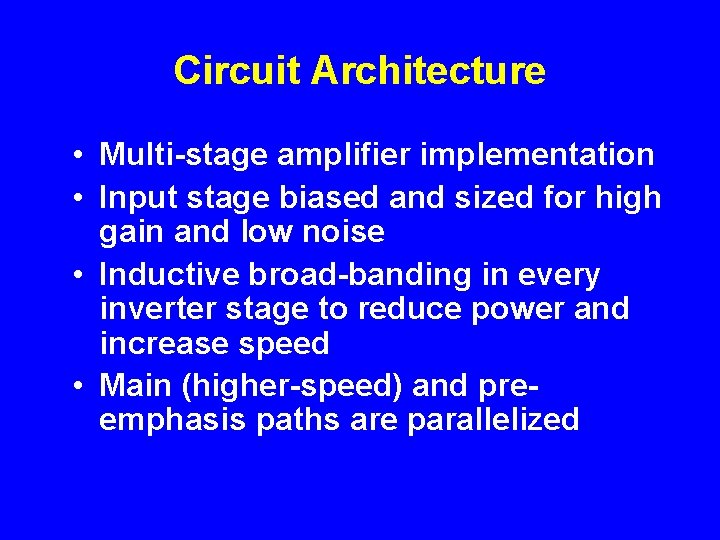

Circuit Architecture • Multi-stage amplifier implementation • Input stage biased and sized for high gain and low noise • Inductive broad-banding in every inverter stage to reduce power and increase speed • Main (higher-speed) and preemphasis paths are parallelized

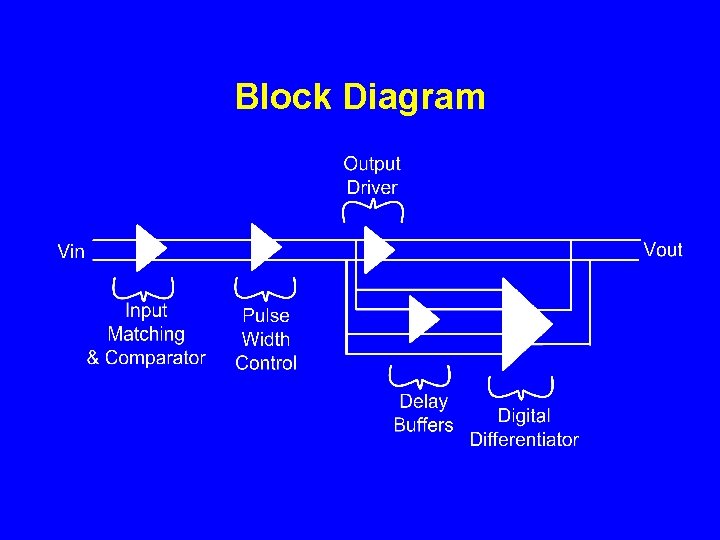

Block Diagram

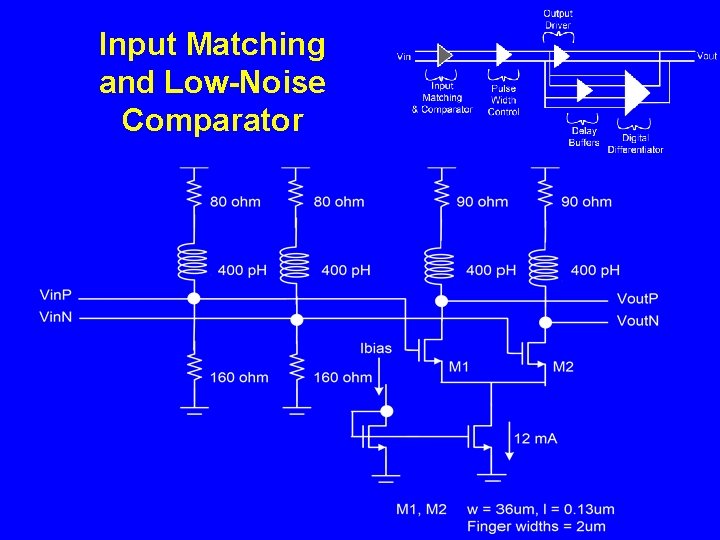

Input Matching and Low-Noise Comparator

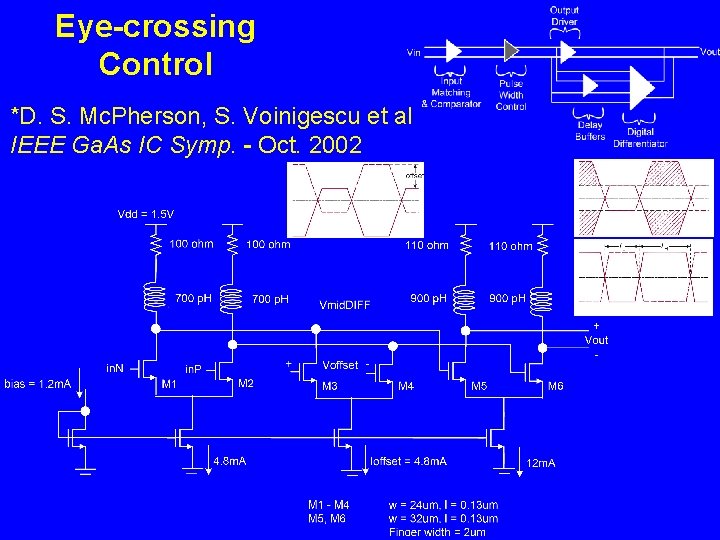

Eye-crossing Control *D. S. Mc. Pherson, S. Voinigescu et al IEEE Ga. As IC Symp. - Oct. 2002

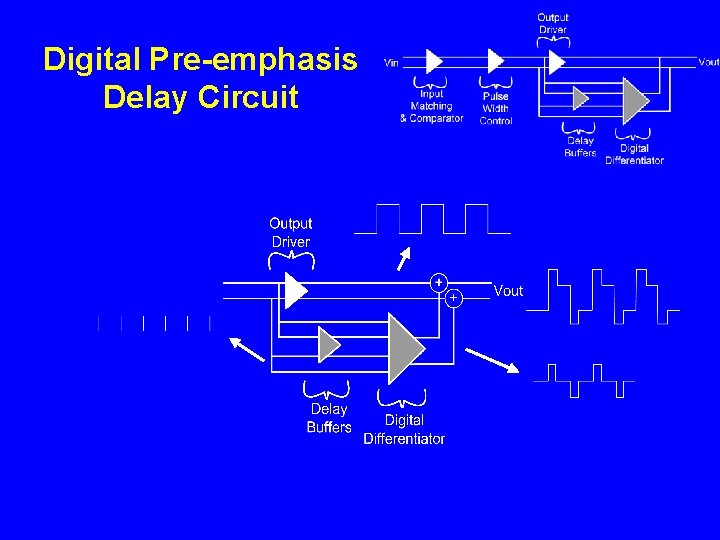

Digital Pre-emphasis Delay Circuit

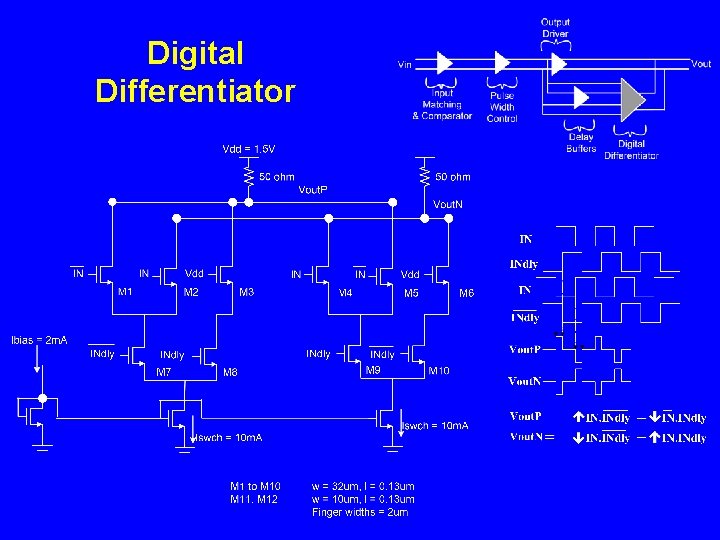

Digital Differentiator

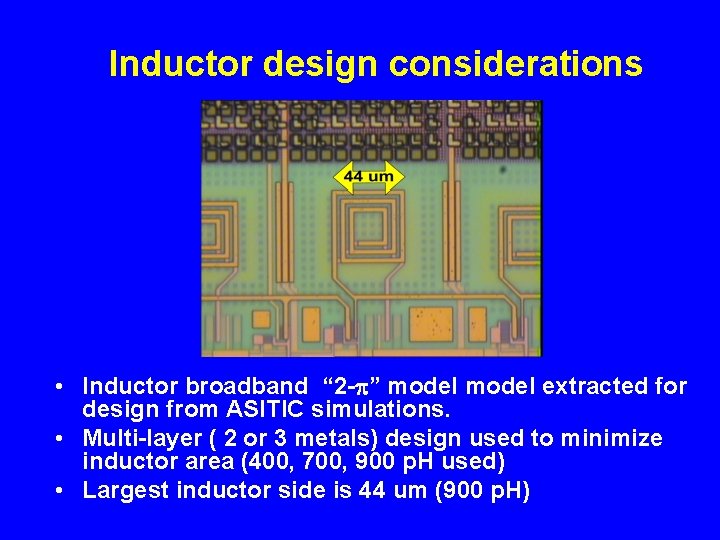

Inductor design considerations • Inductor broadband “ 2 -p” model extracted for design from ASITIC simulations. • Multi-layer ( 2 or 3 metals) design used to minimize inductor area (400, 700, 900 p. H used) • Largest inductor side is 44 um (900 p. H)

Experimental Results

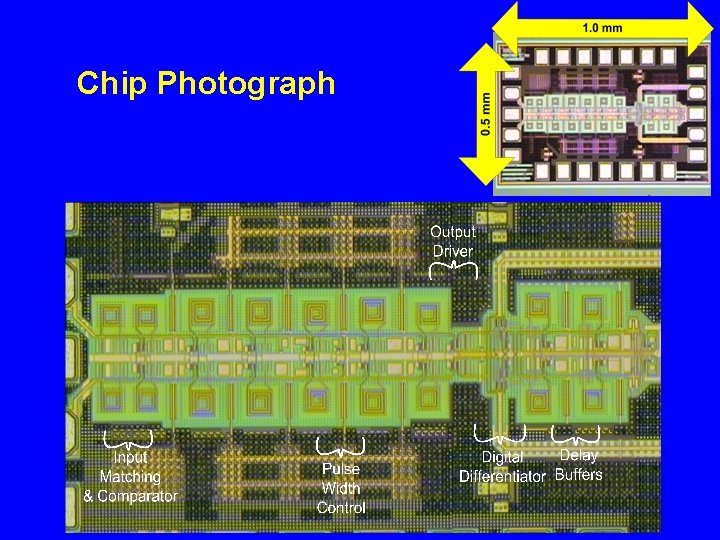

Chip Photograph

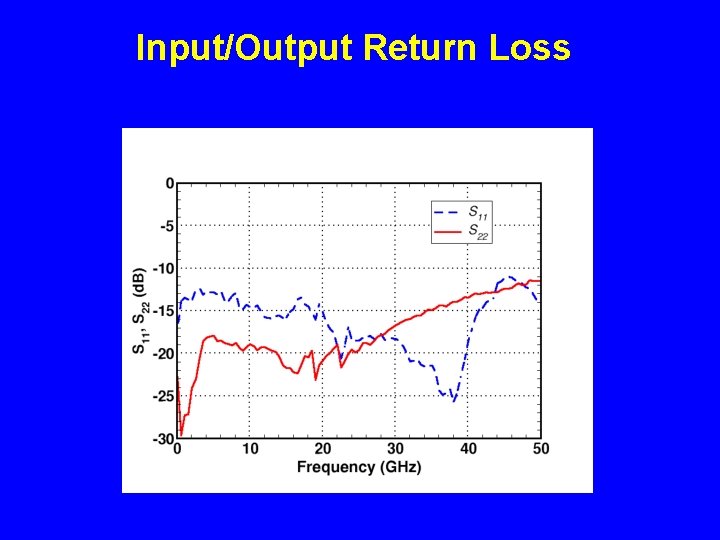

Input/Output Return Loss

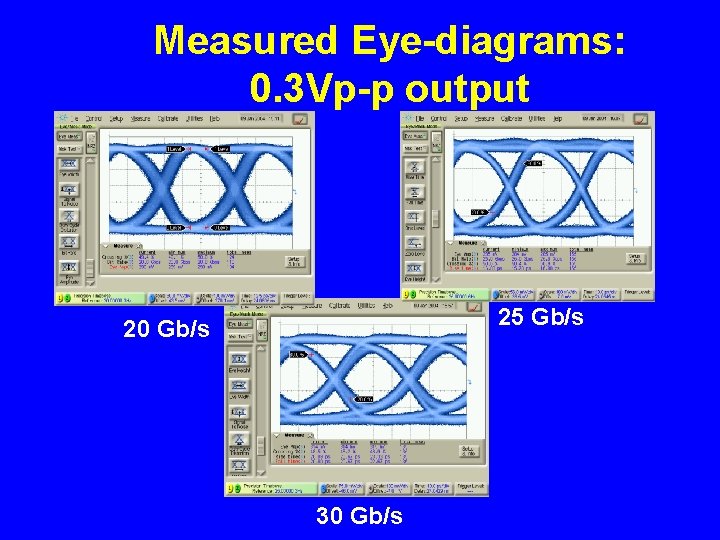

Measured Eye-diagrams: 0. 3 Vp-p output 25 Gb/s 20 Gb/s 30 Gb/s

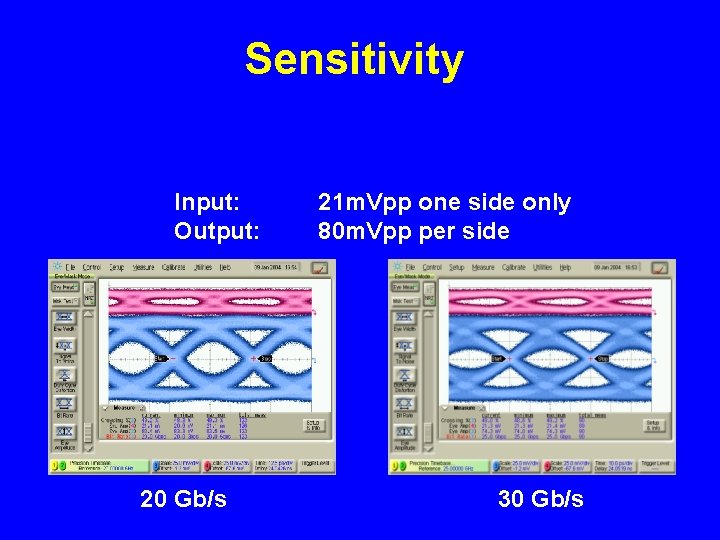

Sensitivity Input: Output: 20 Gb/s 21 m. Vpp one side only 80 m. Vpp per side 30 Gb/s

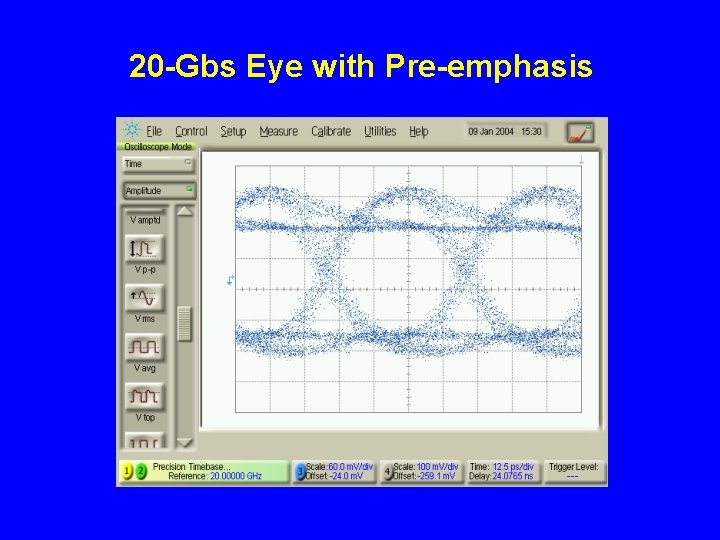

20 -Gbs Eye with Pre-emphasis

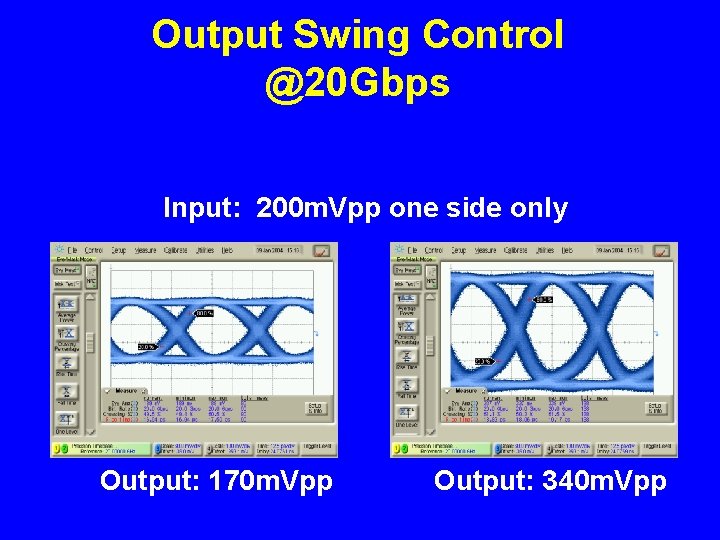

Output Swing Control @20 Gbps Input: 200 m. Vpp one side only Output: 170 m. Vpp Output: 340 m. Vpp

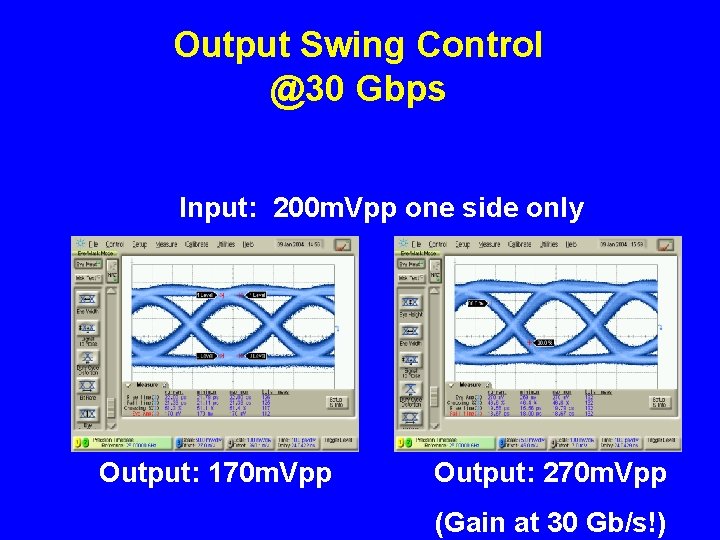

Output Swing Control @30 Gbps Input: 200 m. Vpp one side only Output: 170 m. Vpp Output: 270 m. Vpp (Gain at 30 Gb/s!)

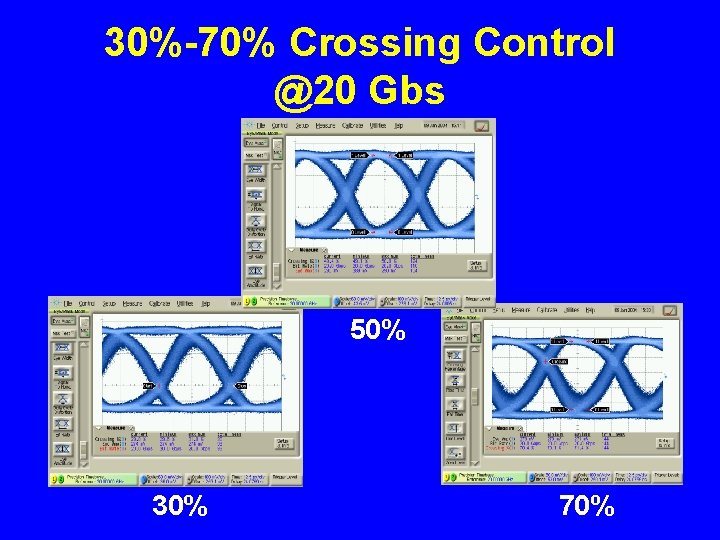

30%-70% Crossing Control @20 Gbs 50% 30% 70%

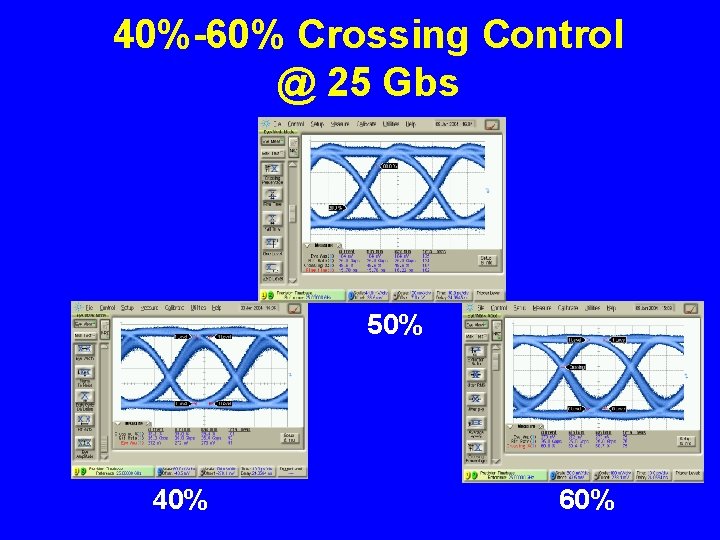

40%-60% Crossing Control @ 25 Gbs 50% 40% 60%

Summary and Conclusion

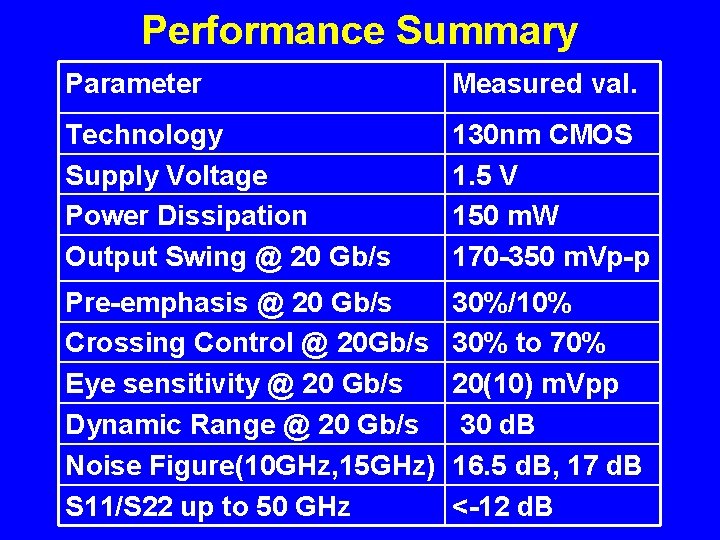

Performance Summary Parameter Measured val. Technology Supply Voltage Power Dissipation Output Swing @ 20 Gb/s 130 nm CMOS 1. 5 V 150 m. W 170 -350 m. Vp-p Pre-emphasis @ 20 Gb/s Crossing Control @ 20 Gb/s Eye sensitivity @ 20 Gb/s Dynamic Range @ 20 Gb/s Noise Figure(10 GHz, 15 GHz) S 11/S 22 up to 50 GHz 30%/10% 30% to 70% 20(10) m. Vpp 30 d. B 16. 5 d. B, 17 d. B <-12 d. B

Conclusion • • • First CMOS driver above 20 Gb/s Novel digital pre-emphasis High sensitivity, dynamic range Large output swing Eye-crossing control Communications between chips and backplanes is feasible at 20 Gb/s in 130 -nm CMOS technology

Acknowledgements • Rudy Beerkens and Boris Prokes of STMicroelectronics Ottawa • STMicroelectronics for fabrication • Micronet and Gennum Corporation for financial support • Quake Technologies for access to 40 Gb/s BERT

- Slides: 27