EE 365 CMOS gates Electrical characteristics and timing

- Slides: 42

EE 365 CMOS gates Electrical characteristics and timing TTL gates

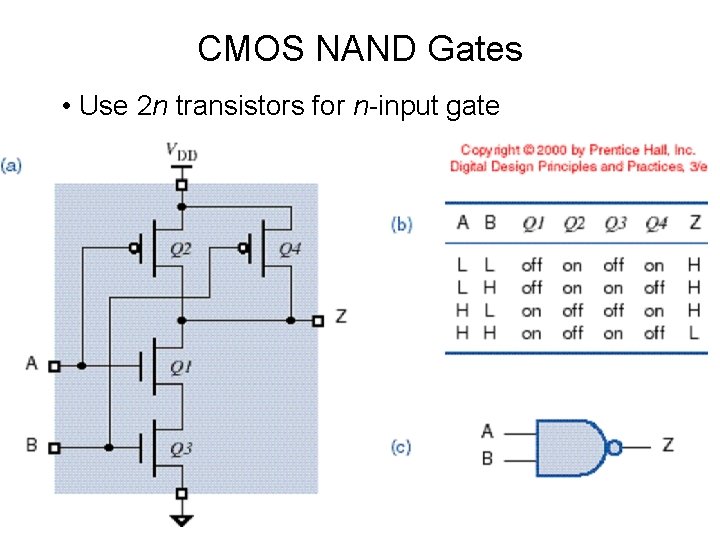

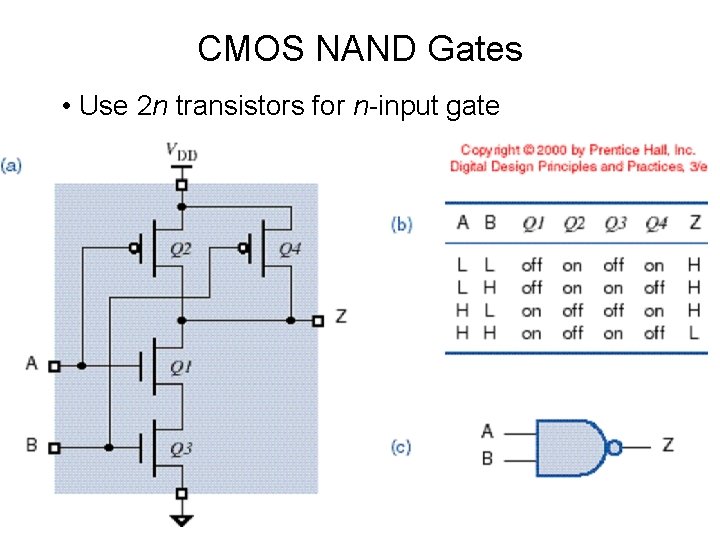

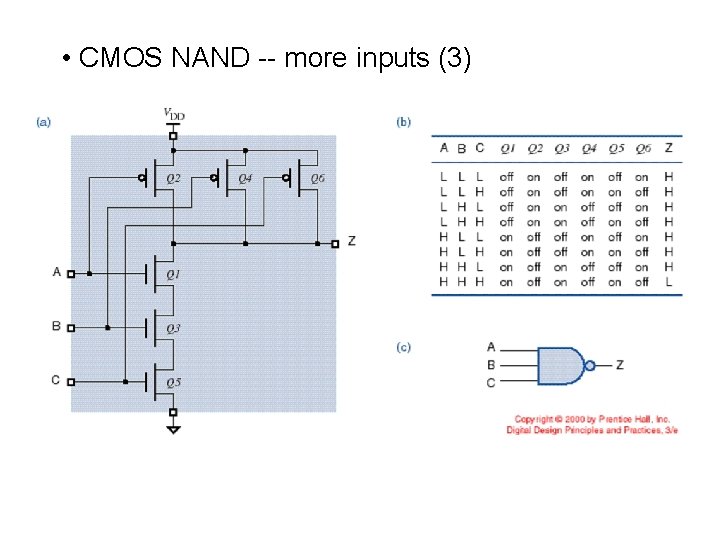

CMOS NAND Gates • Use 2 n transistors for n-input gate

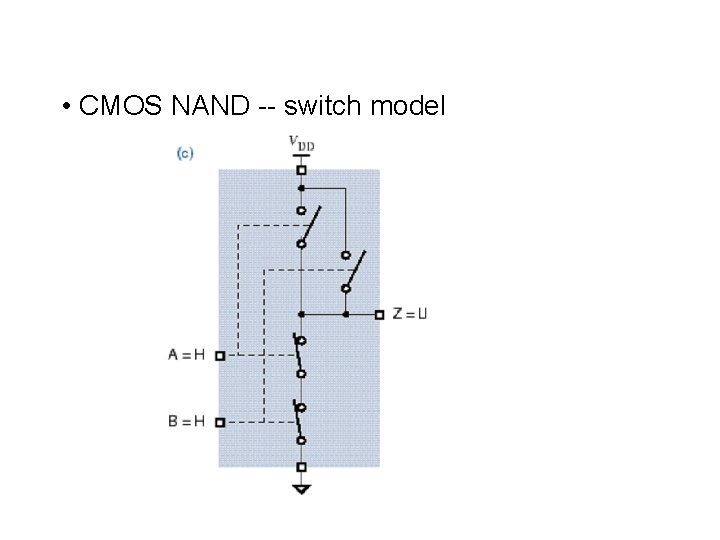

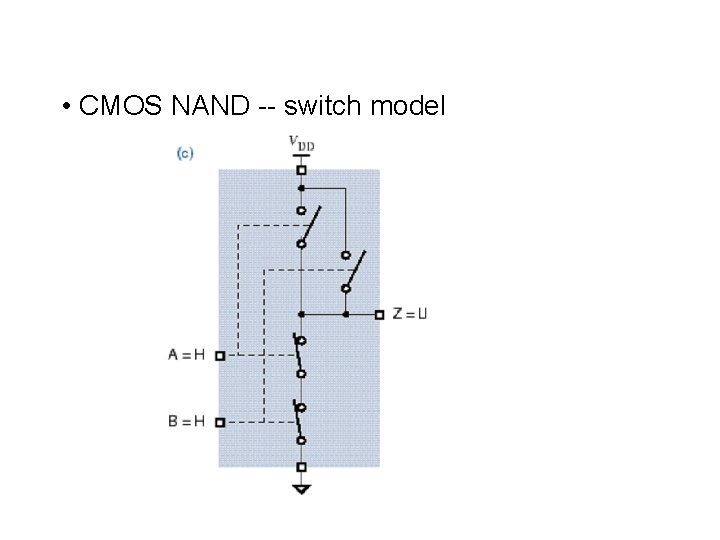

• CMOS NAND -- switch model

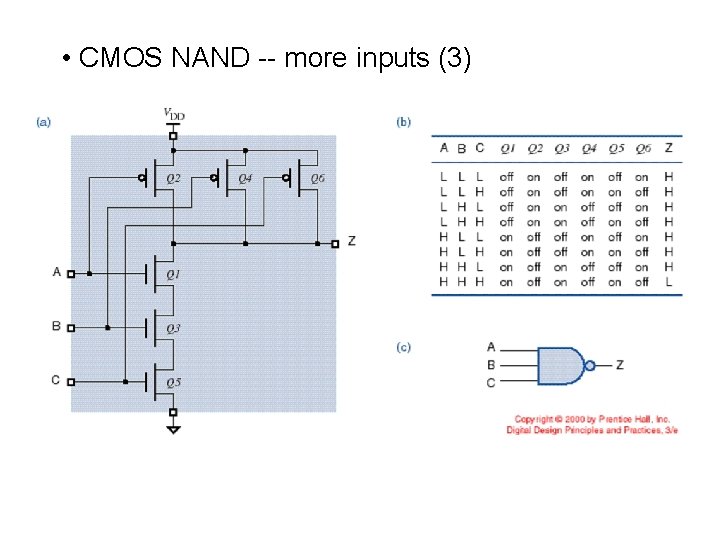

• CMOS NAND -- more inputs (3)

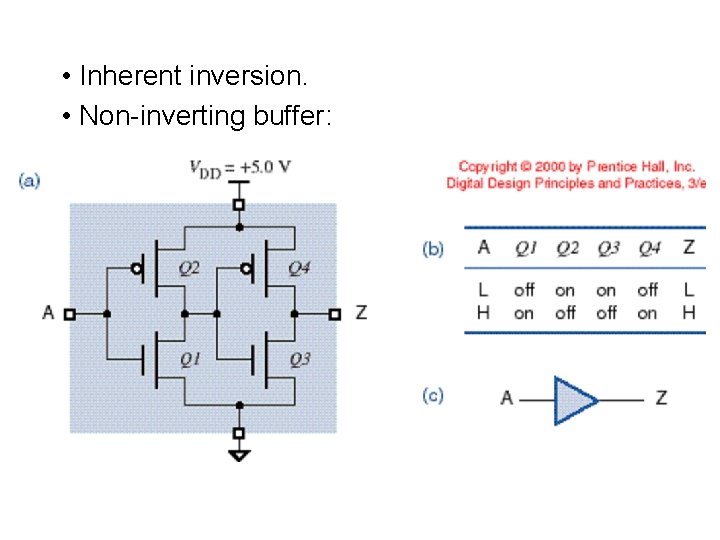

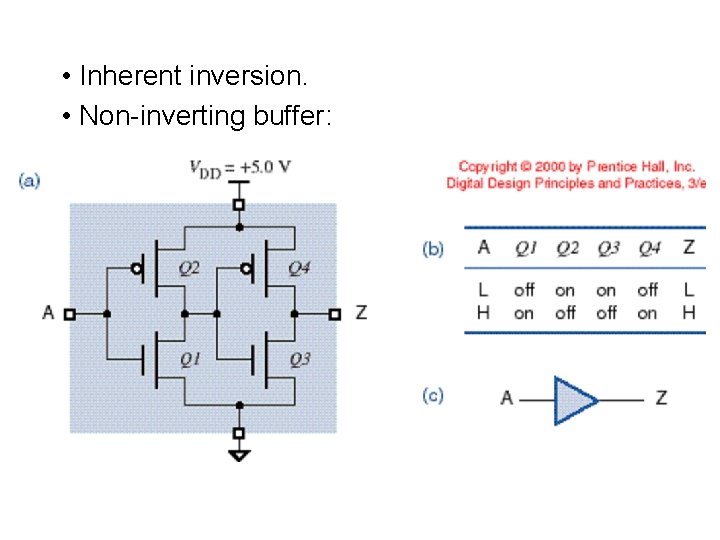

• Inherent inversion. • Non-inverting buffer:

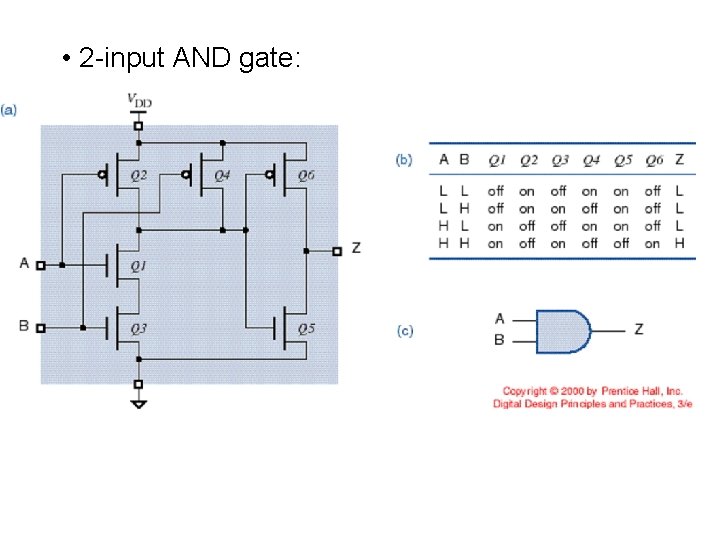

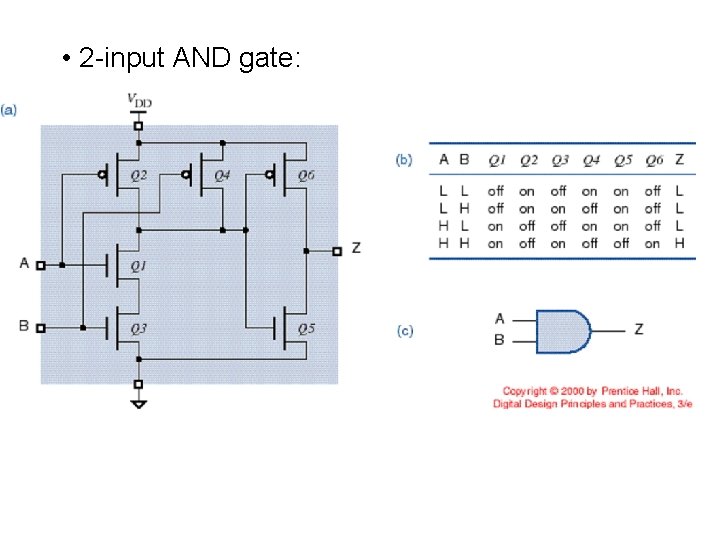

• 2 -input AND gate:

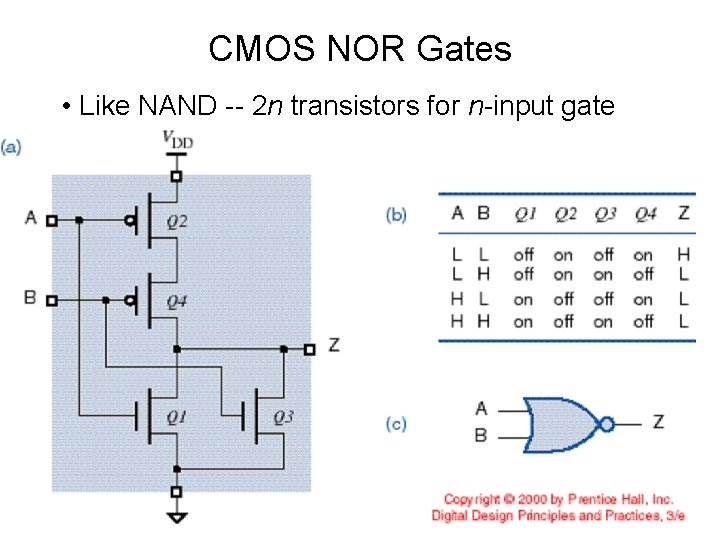

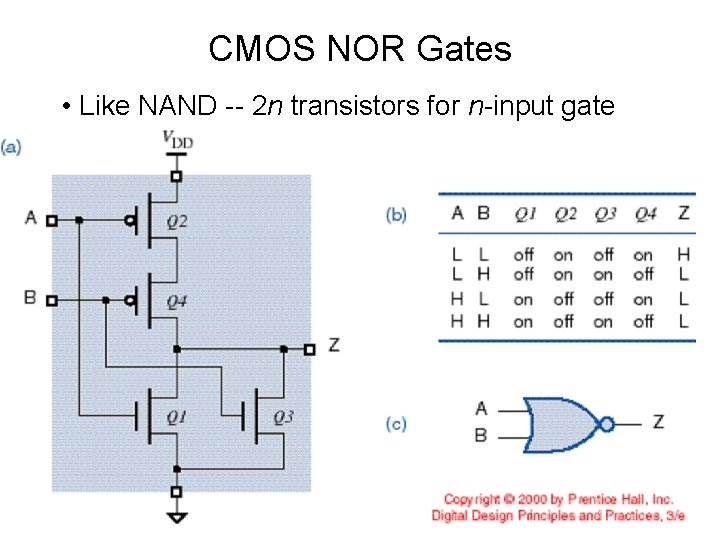

CMOS NOR Gates • Like NAND -- 2 n transistors for n-input gate

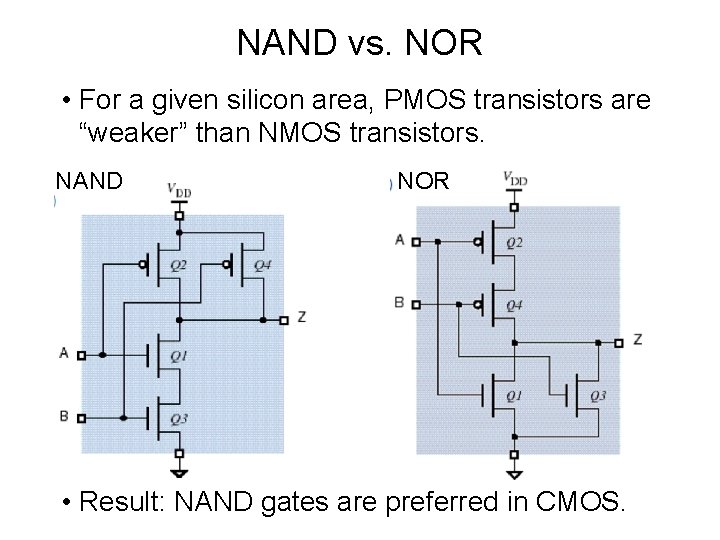

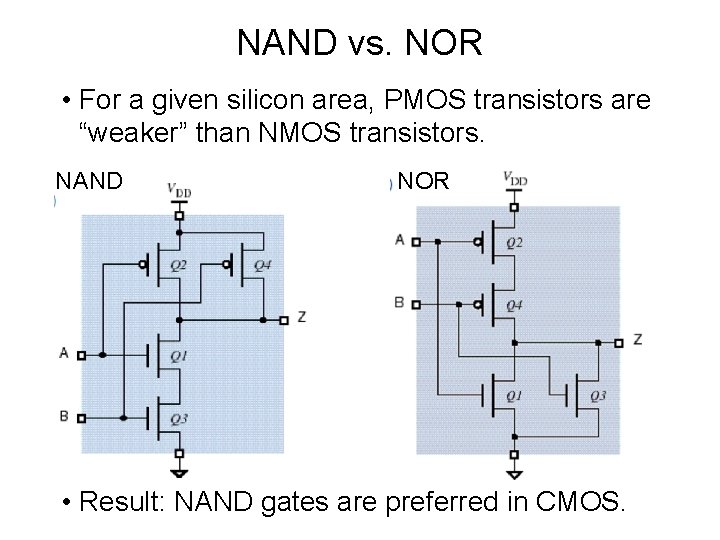

NAND vs. NOR • For a given silicon area, PMOS transistors are “weaker” than NMOS transistors. NAND NOR • Result: NAND gates are preferred in CMOS.

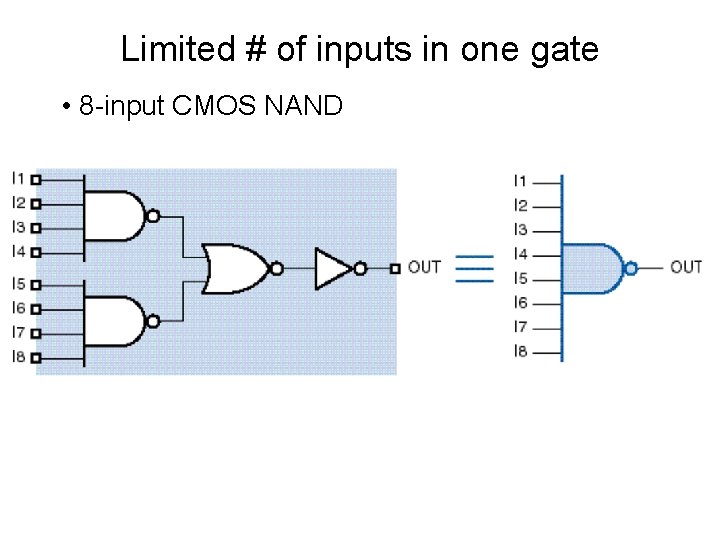

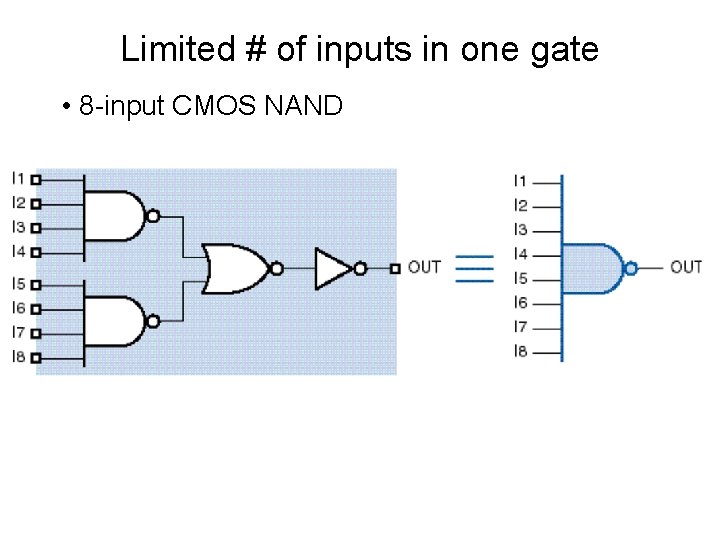

Limited # of inputs in one gate • 8 -input CMOS NAND

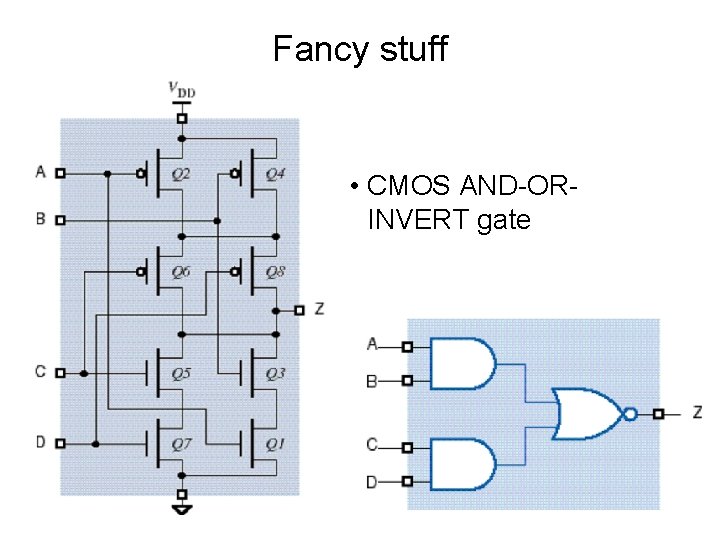

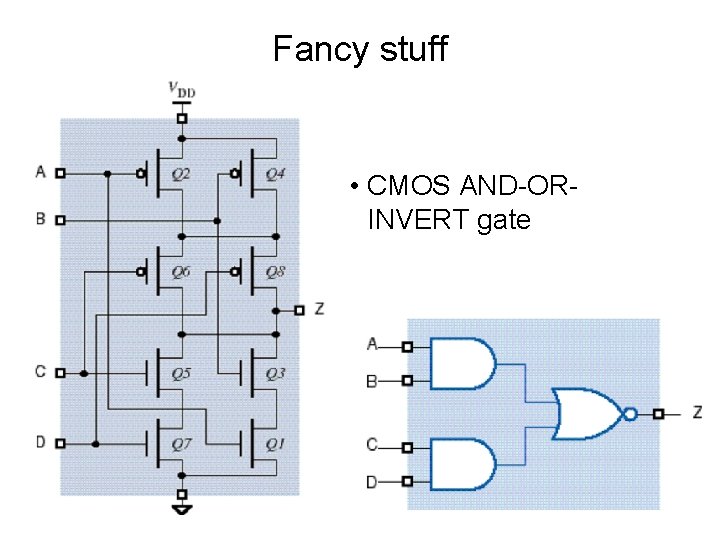

Fancy stuff • CMOS AND-ORINVERT gate

CMOS Electrical Characteristics • Digital analysis works only if circuits are operated in spec: – Power supply voltage – Temperature – Input-signal quality – Output loading • Must do some “analog” analysis to prove that circuits are operated in spec. – Fanout specs – Timing analysis (setup and hold times)

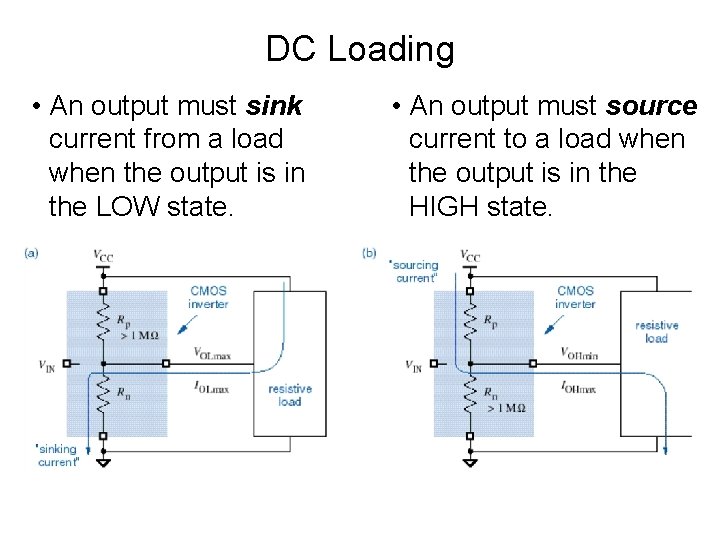

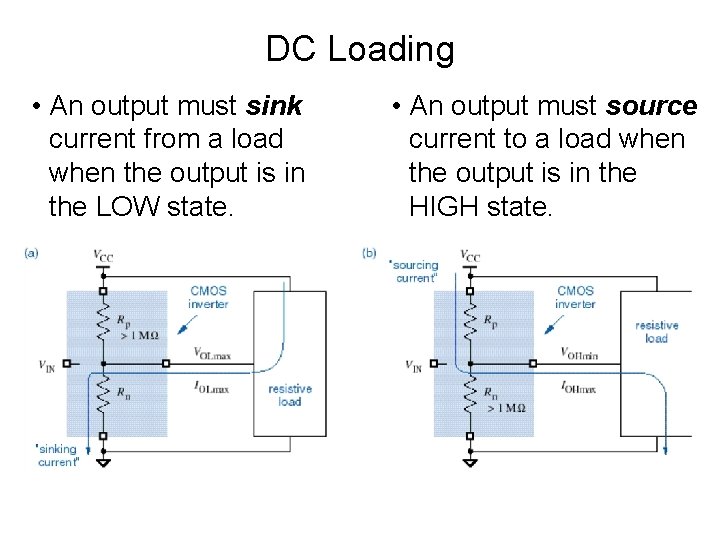

DC Loading • An output must sink current from a load when the output is in the LOW state. • An output must source current to a load when the output is in the HIGH state.

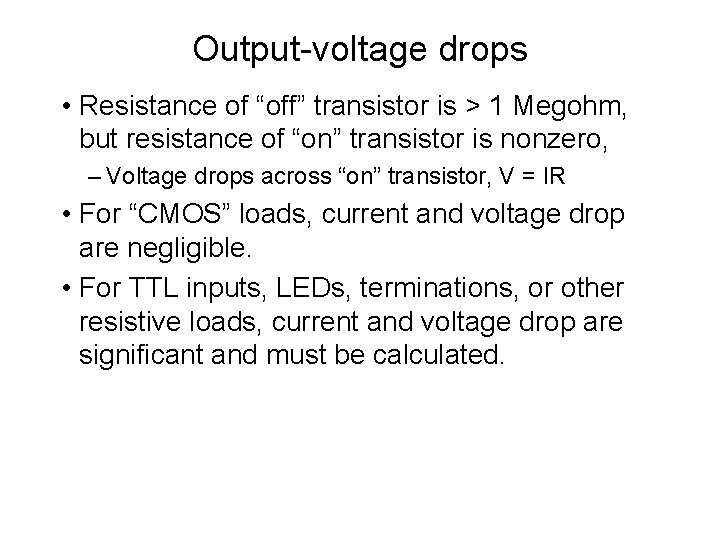

Output-voltage drops • Resistance of “off” transistor is > 1 Megohm, but resistance of “on” transistor is nonzero, – Voltage drops across “on” transistor, V = IR • For “CMOS” loads, current and voltage drop are negligible. • For TTL inputs, LEDs, terminations, or other resistive loads, current and voltage drop are significant and must be calculated.

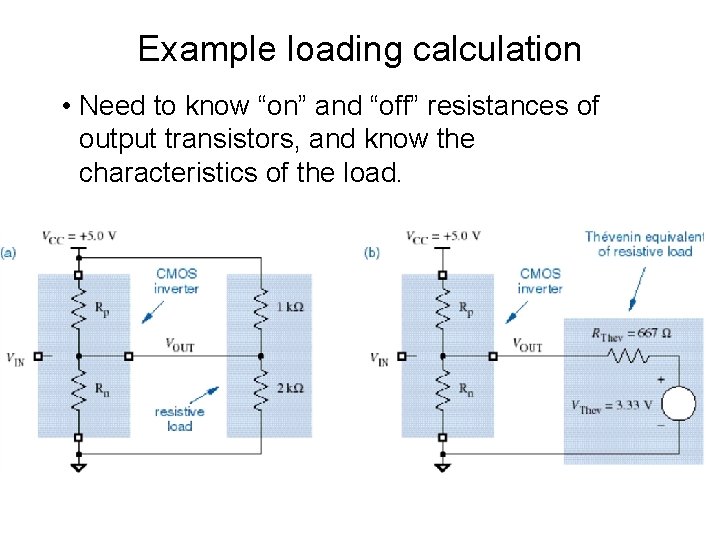

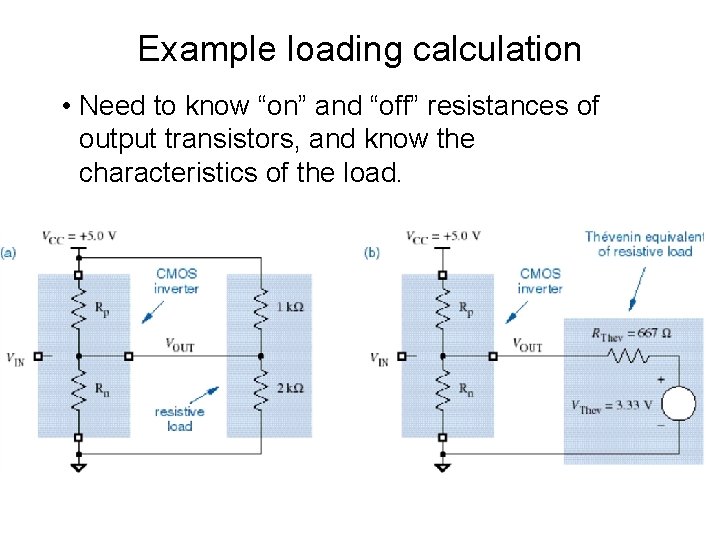

Example loading calculation • Need to know “on” and “off” resistances of output transistors, and know the characteristics of the load.

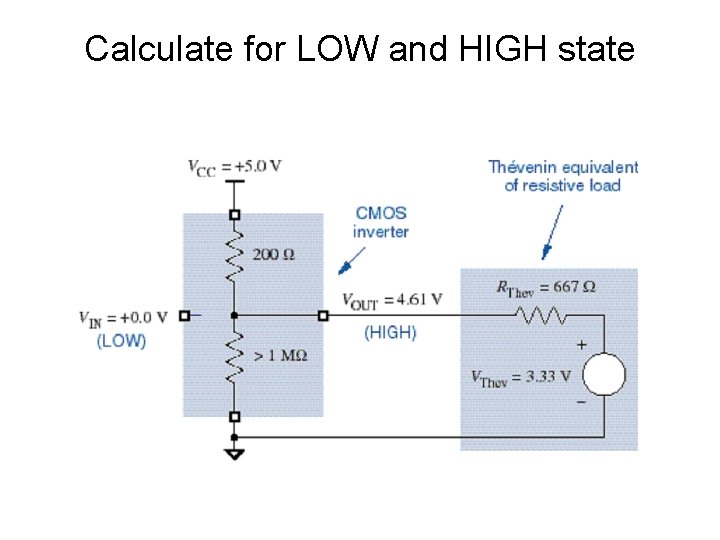

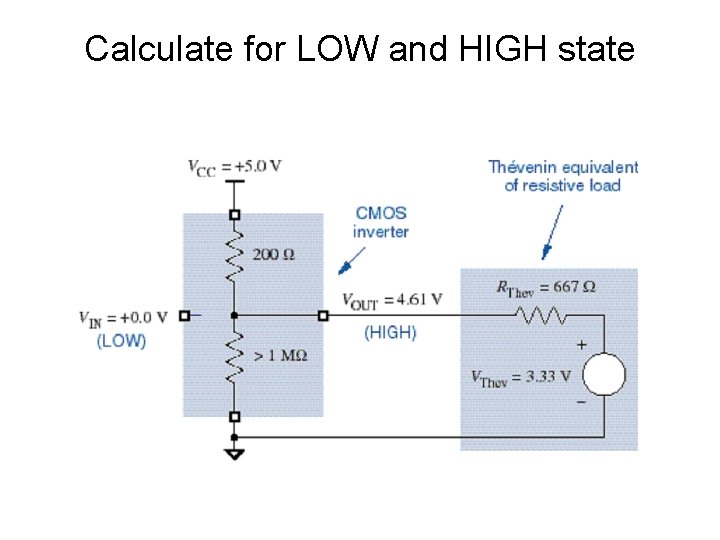

Calculate for LOW and HIGH state

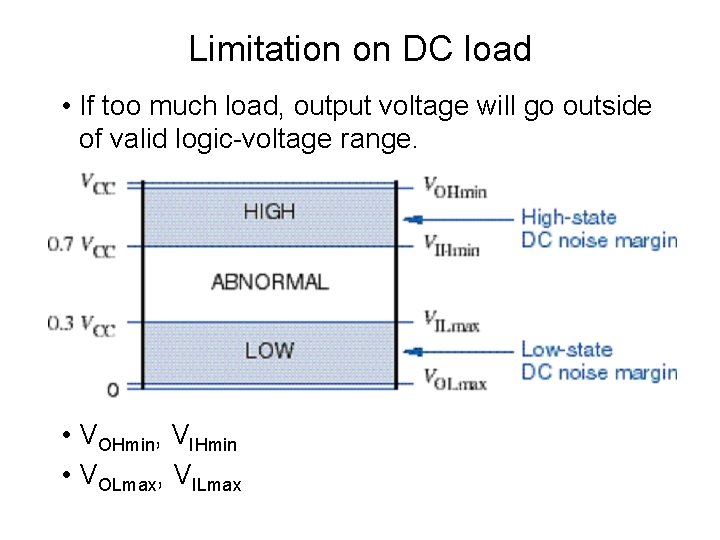

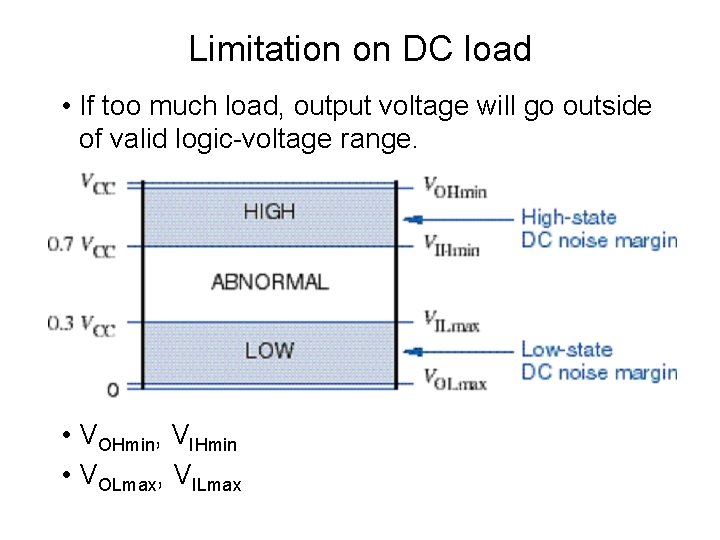

Limitation on DC load • If too much load, output voltage will go outside of valid logic-voltage range. • VOHmin, VIHmin • VOLmax, VILmax

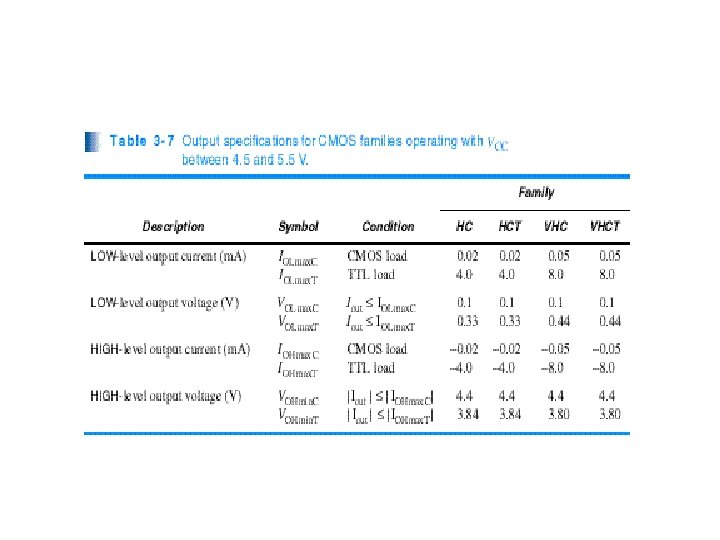

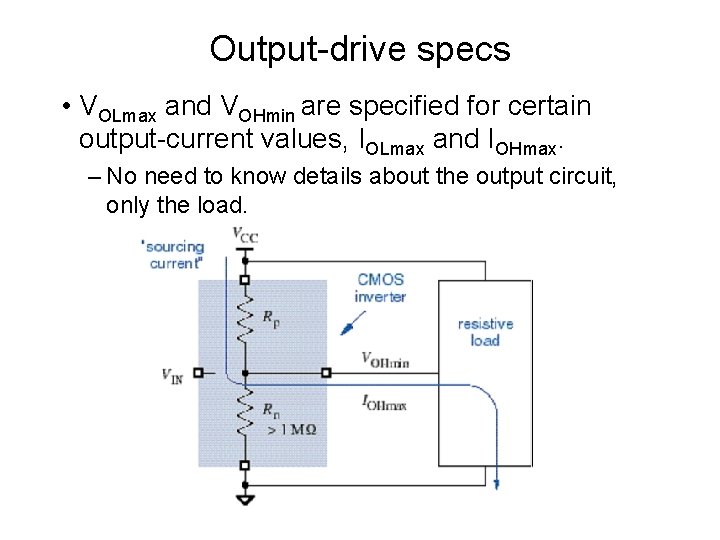

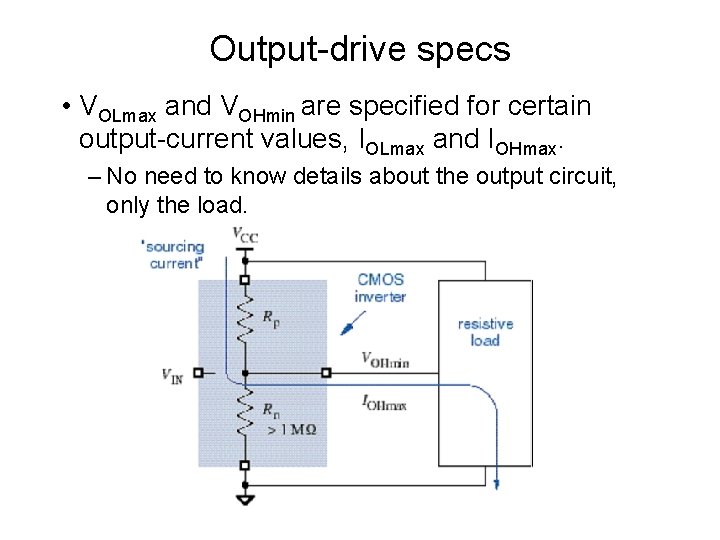

Output-drive specs • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load.

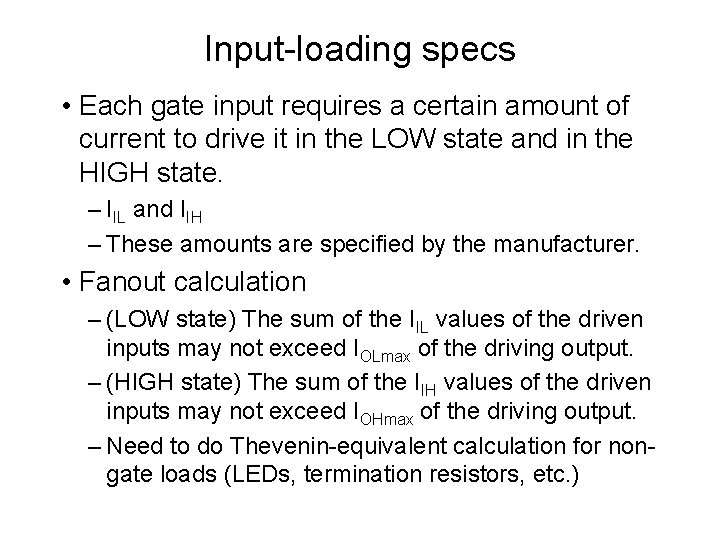

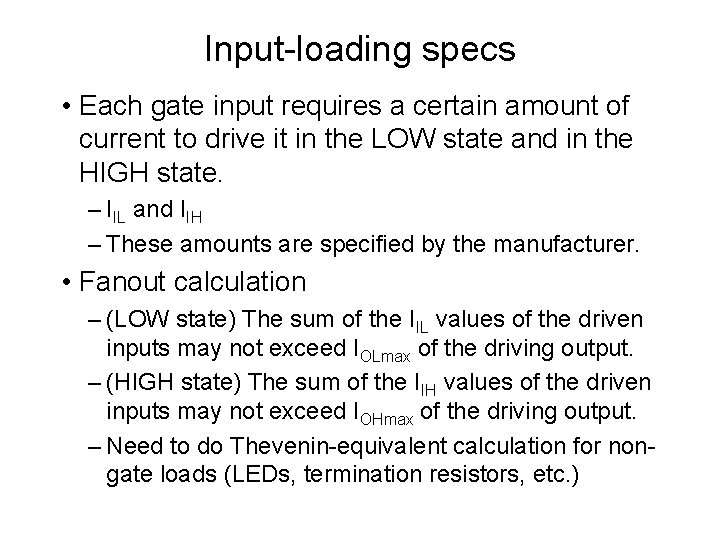

Input-loading specs • Each gate input requires a certain amount of current to drive it in the LOW state and in the HIGH state. – IIL and IIH – These amounts are specified by the manufacturer. • Fanout calculation – (LOW state) The sum of the IIL values of the driven inputs may not exceed IOLmax of the driving output. – (HIGH state) The sum of the IIH values of the driven inputs may not exceed IOHmax of the driving output. – Need to do Thevenin-equivalent calculation for nongate loads (LEDs, termination resistors, etc. )

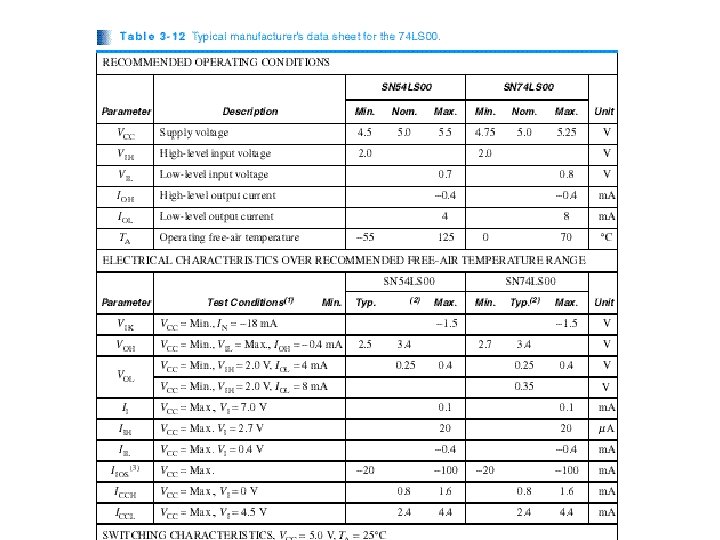

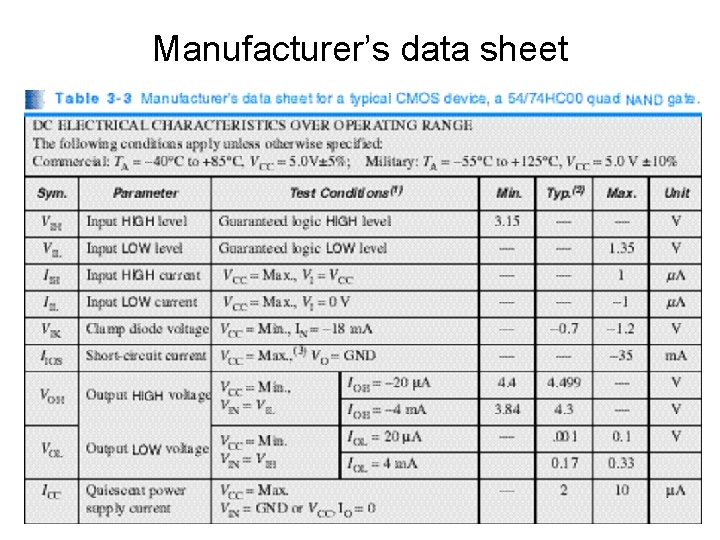

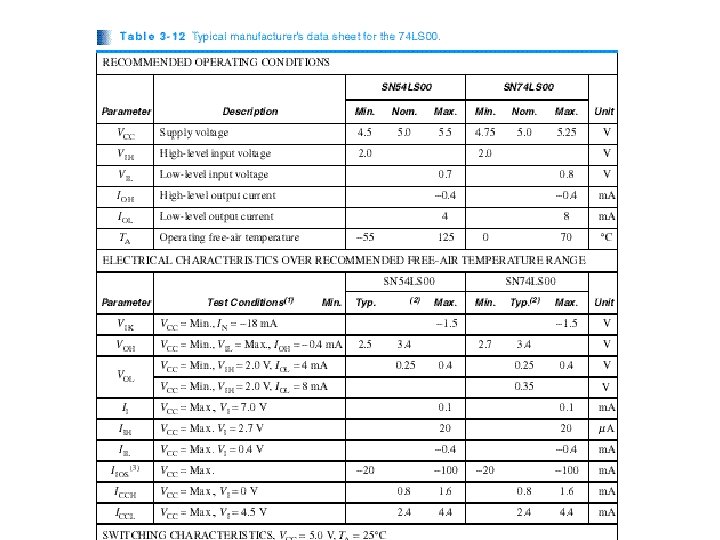

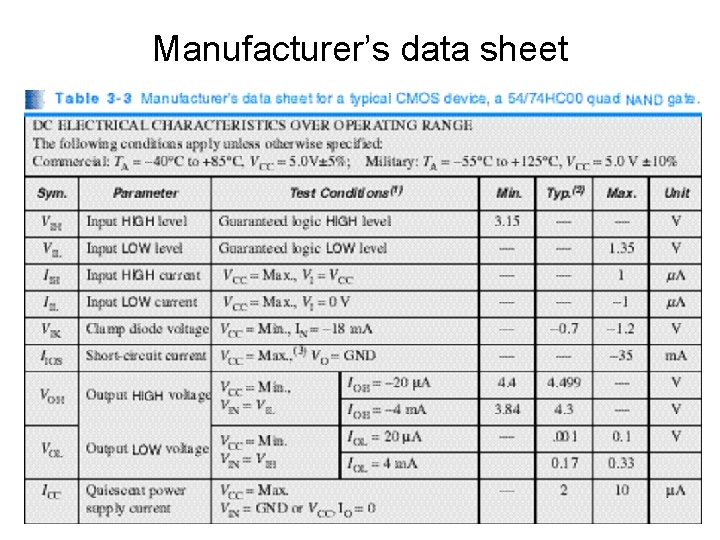

Manufacturer’s data sheet

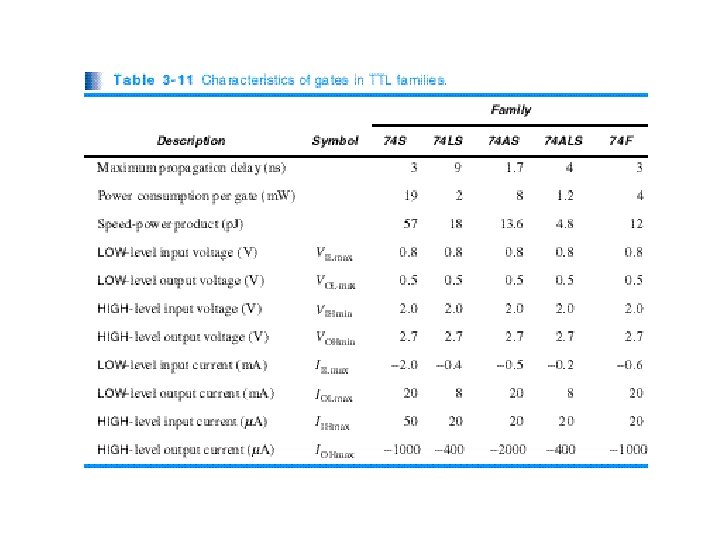

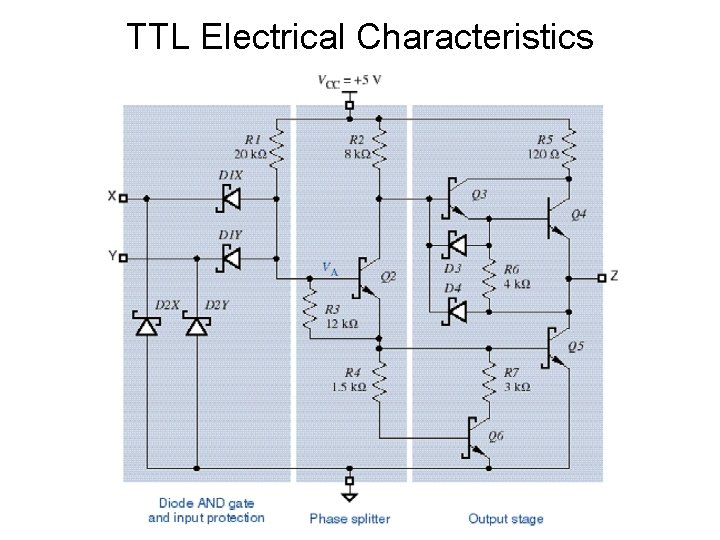

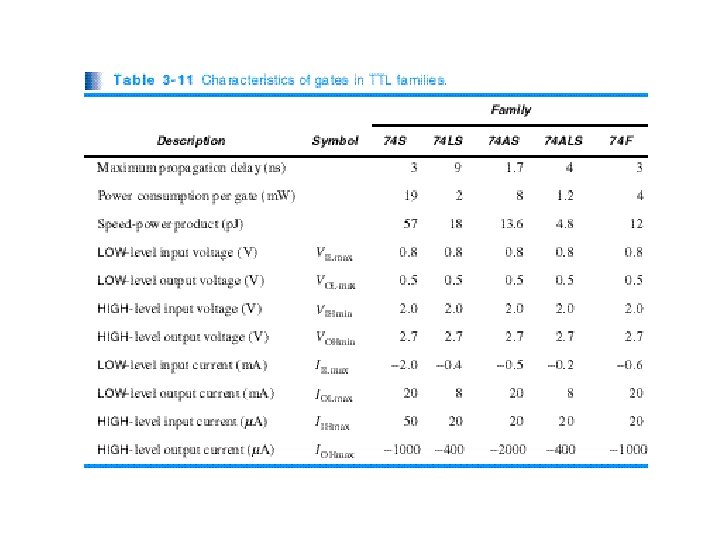

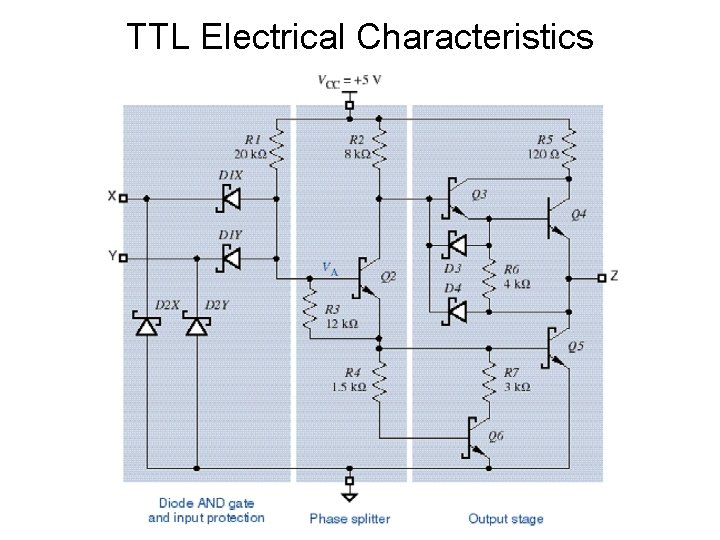

TTL Electrical Characteristics

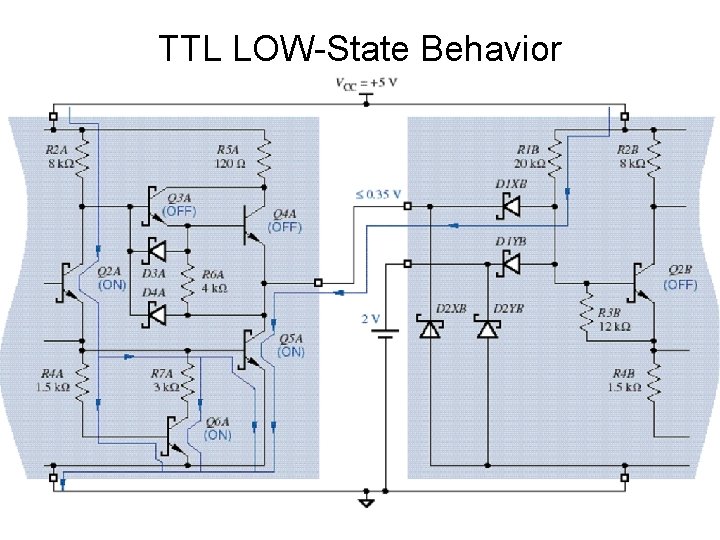

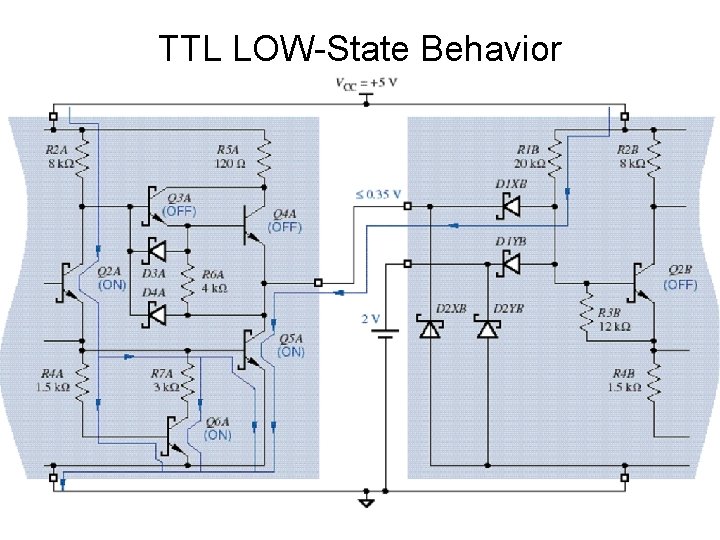

TTL LOW-State Behavior

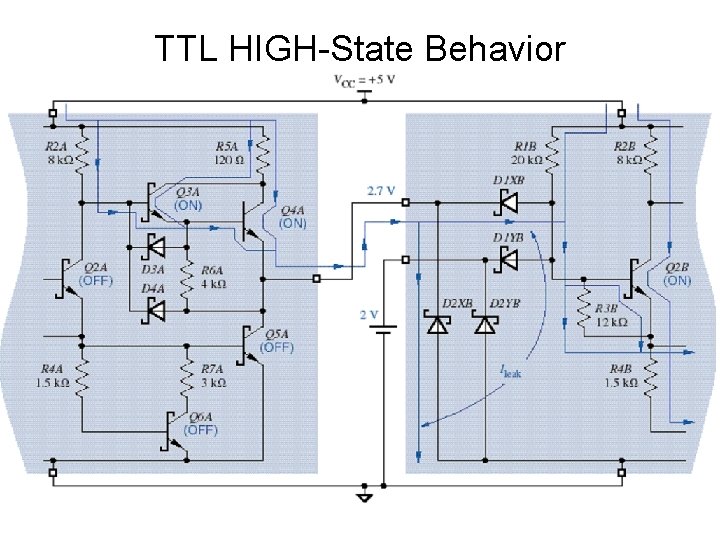

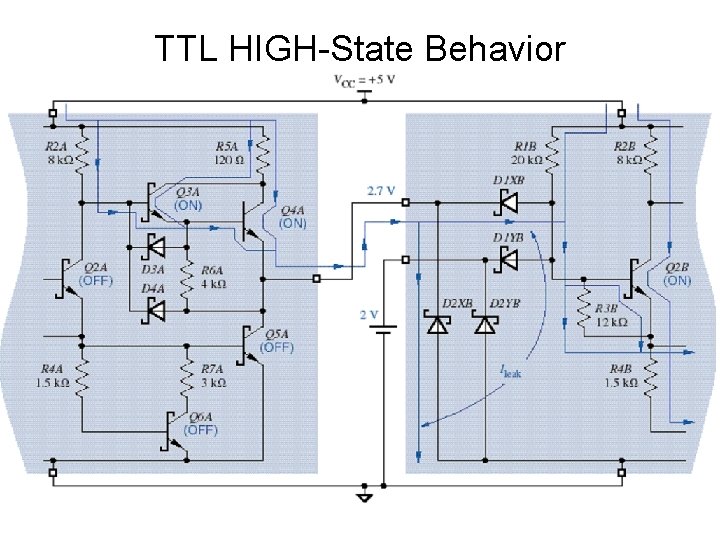

TTL HIGH-State Behavior

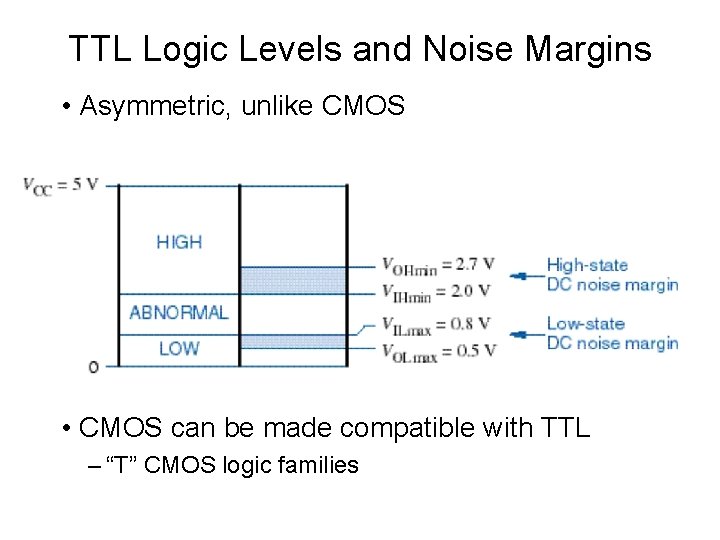

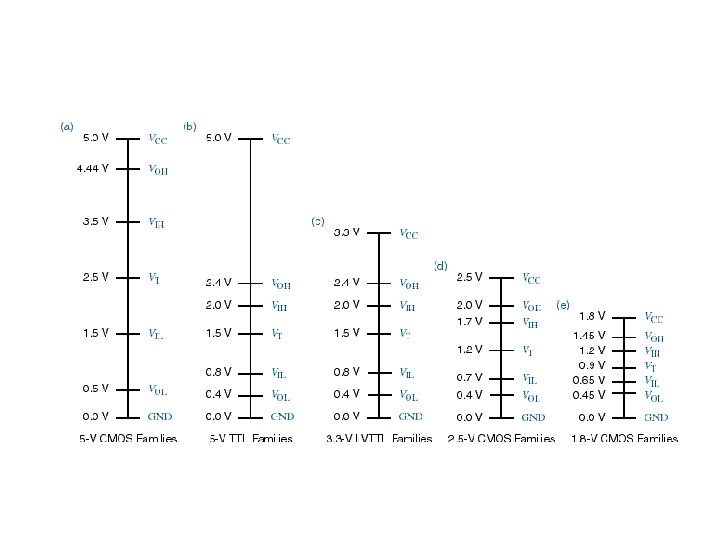

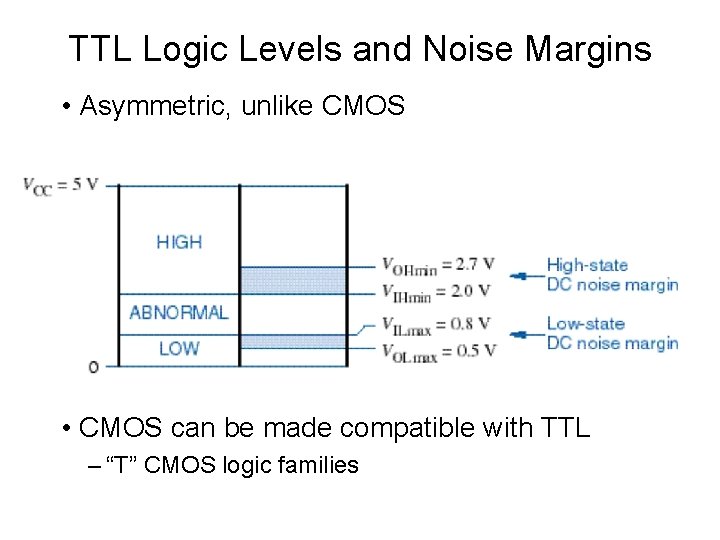

TTL Logic Levels and Noise Margins • Asymmetric, unlike CMOS • CMOS can be made compatible with TTL – “T” CMOS logic families

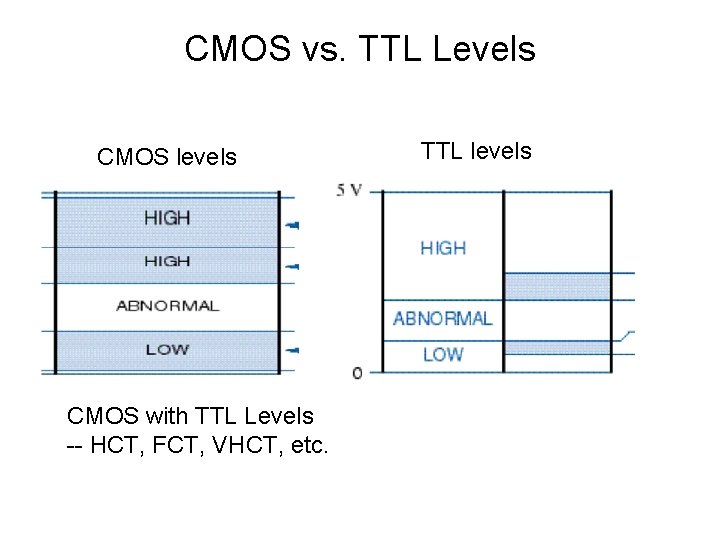

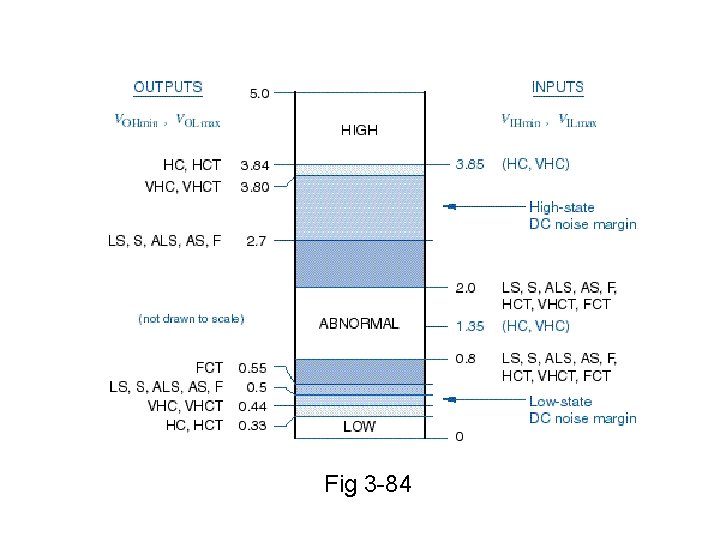

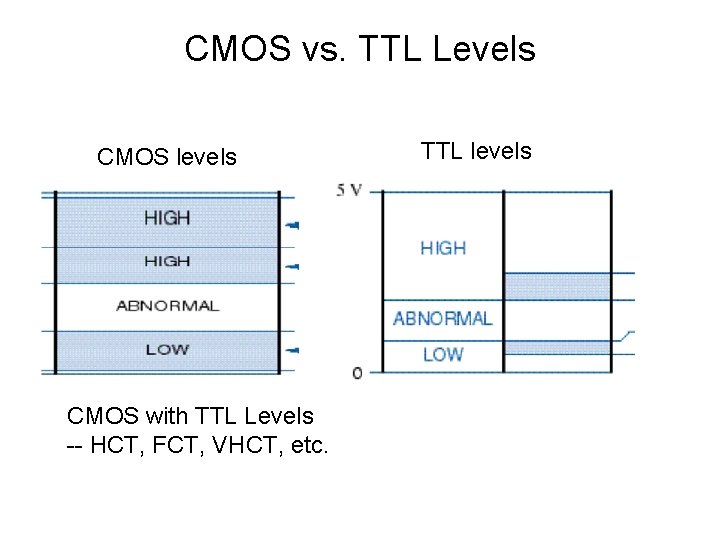

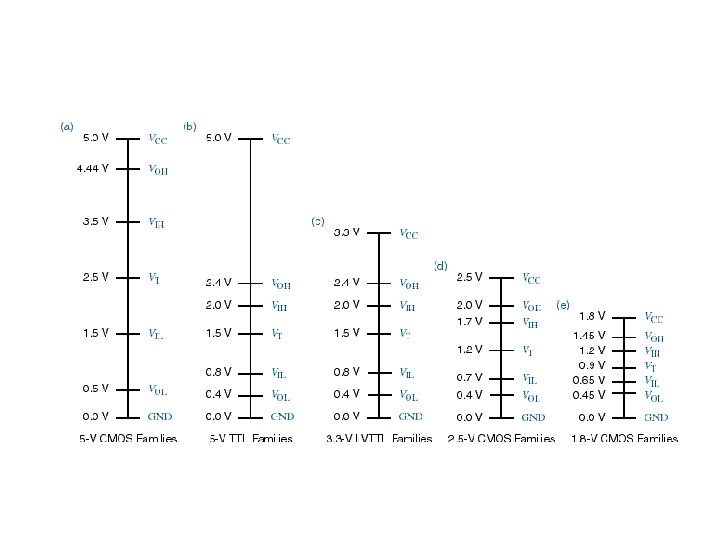

CMOS vs. TTL Levels CMOS levels CMOS with TTL Levels -- HCT, FCT, VHCT, etc. TTL levels

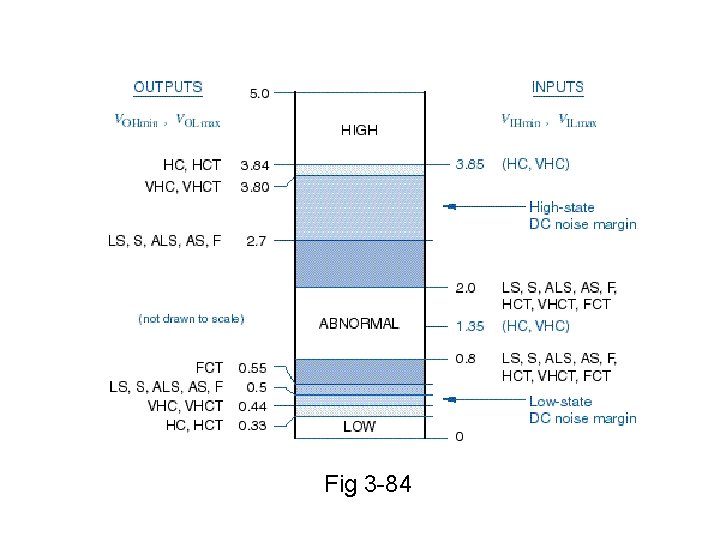

Fig 3 -84

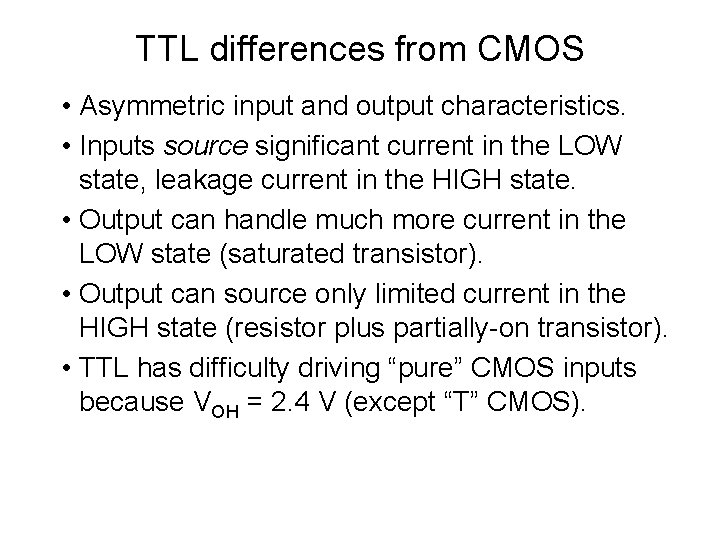

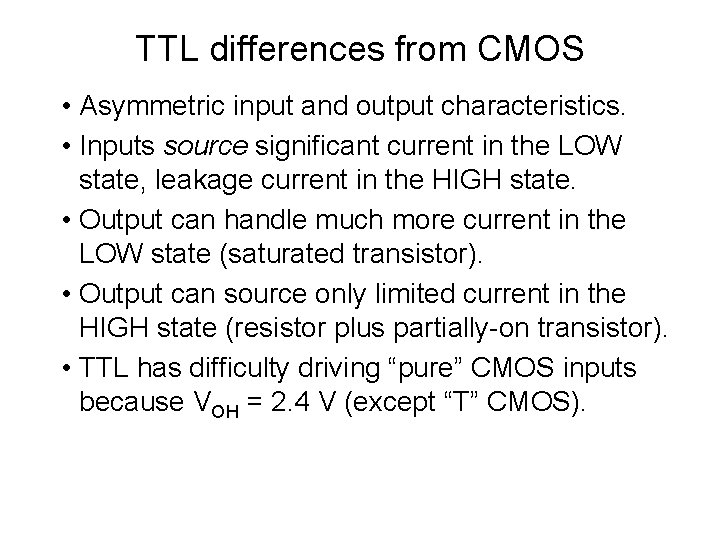

TTL differences from CMOS • Asymmetric input and output characteristics. • Inputs source significant current in the LOW state, leakage current in the HIGH state. • Output can handle much more current in the LOW state (saturated transistor). • Output can source only limited current in the HIGH state (resistor plus partially-on transistor). • TTL has difficulty driving “pure” CMOS inputs because VOH = 2. 4 V (except “T” CMOS).

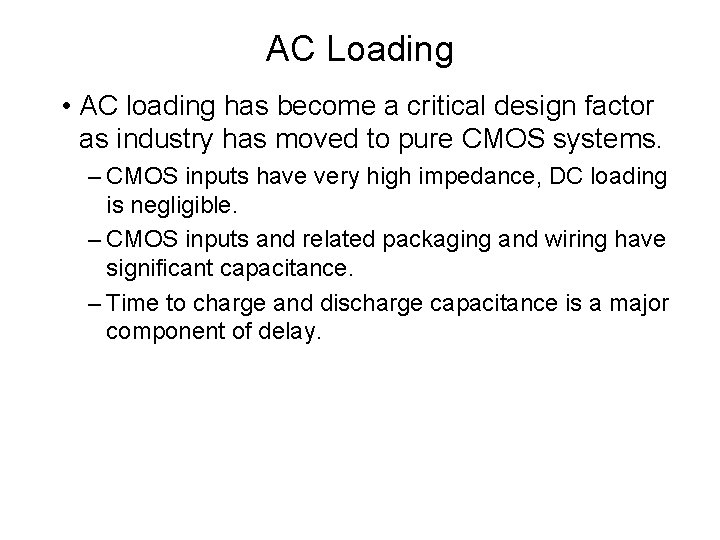

AC Loading • AC loading has become a critical design factor as industry has moved to pure CMOS systems. – CMOS inputs have very high impedance, DC loading is negligible. – CMOS inputs and related packaging and wiring have significant capacitance. – Time to charge and discharge capacitance is a major component of delay.

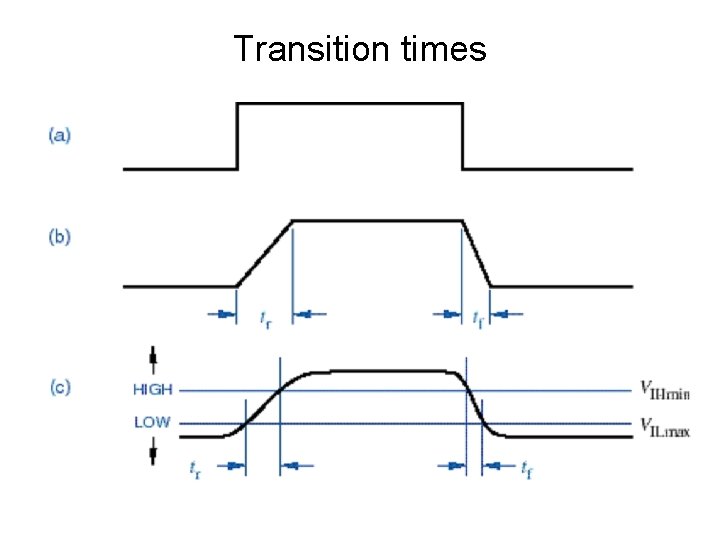

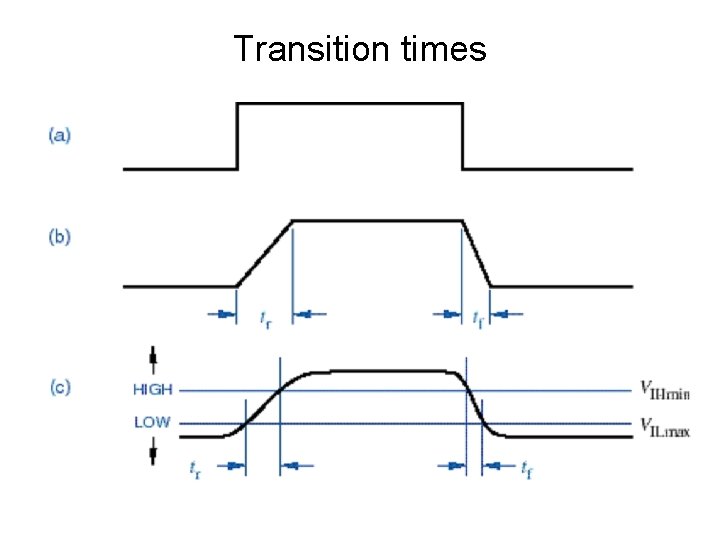

Transition times

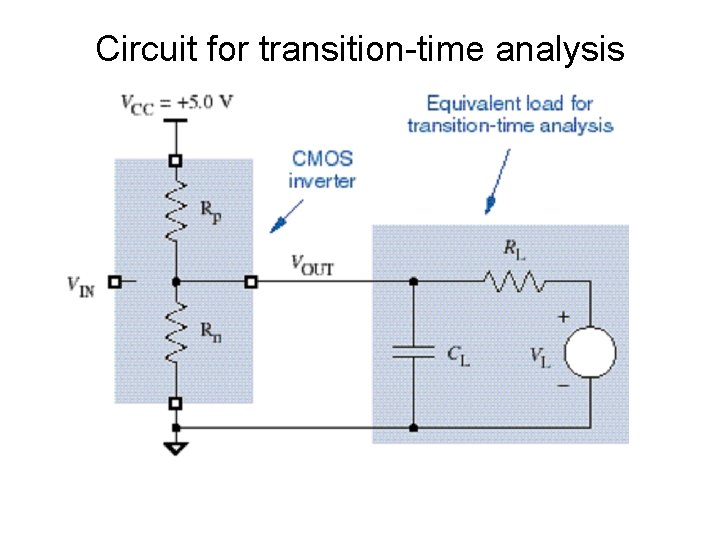

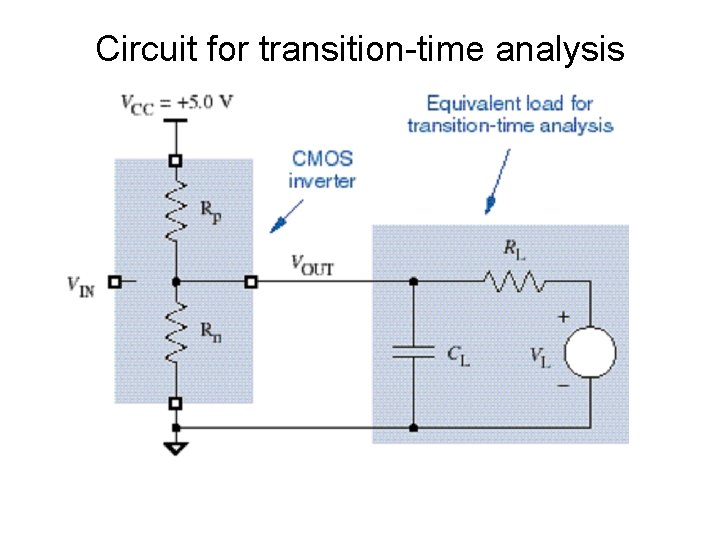

Circuit for transition-time analysis

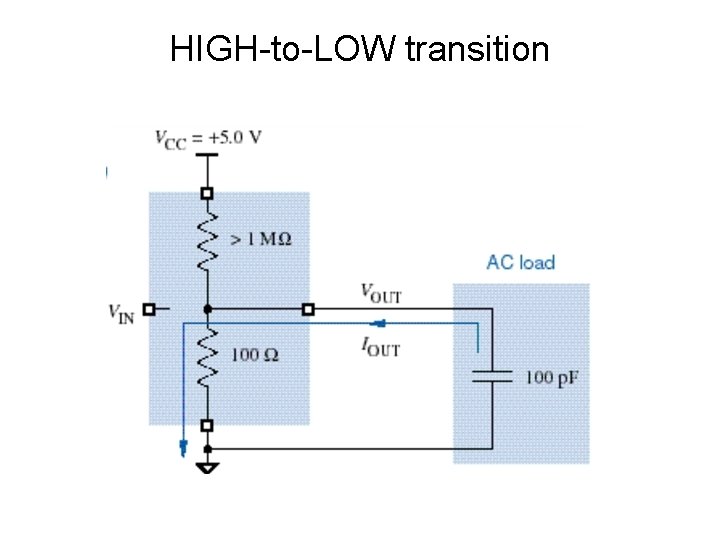

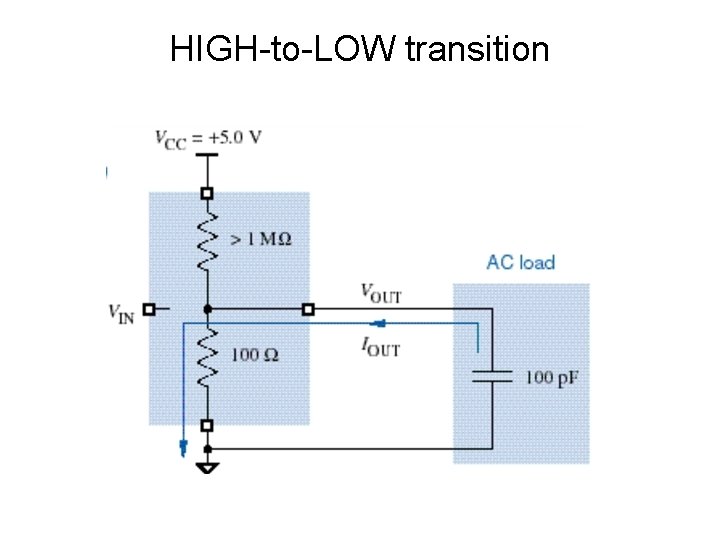

HIGH-to-LOW transition

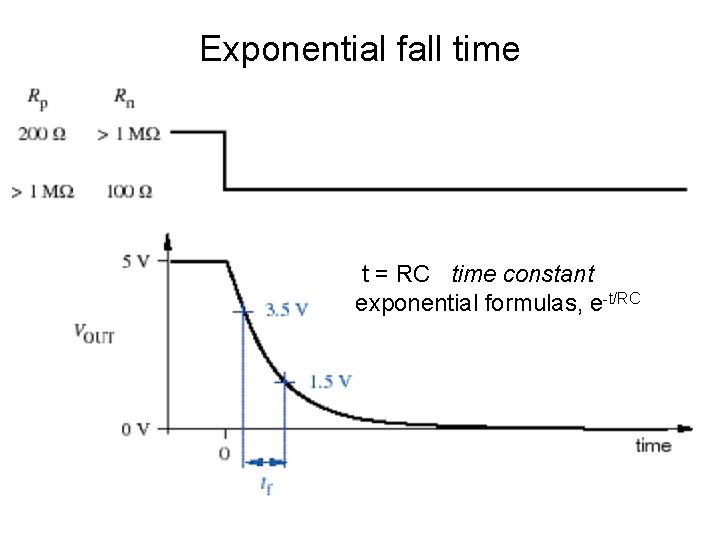

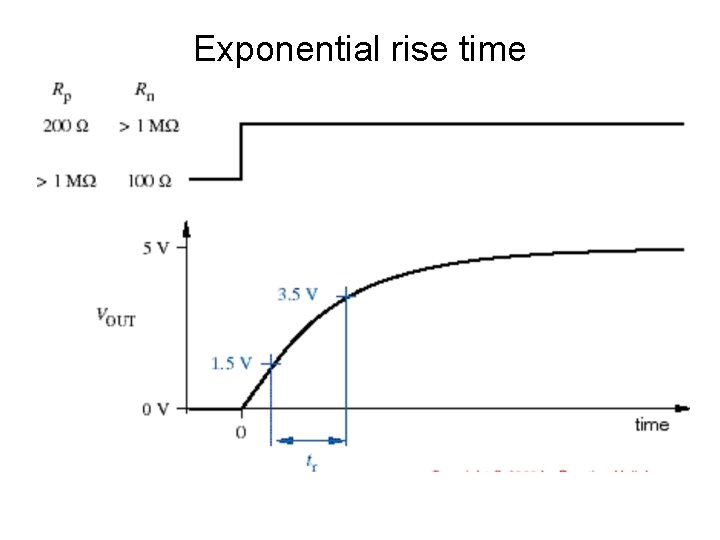

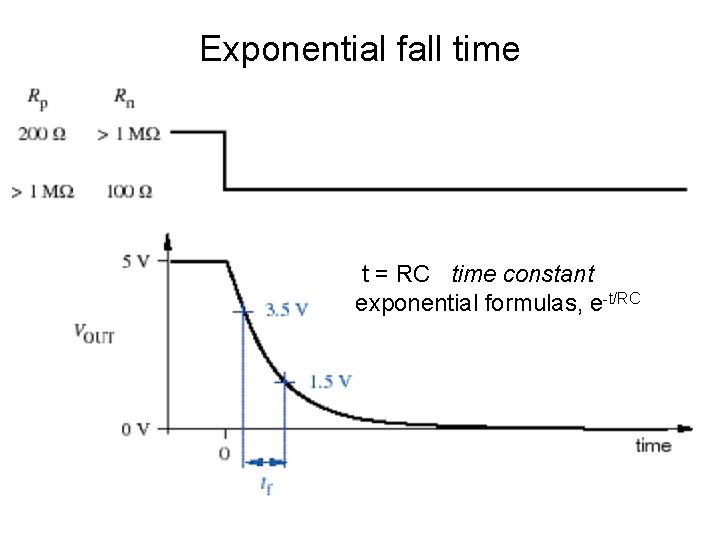

Exponential fall time t = RC time constant exponential formulas, e-t/RC

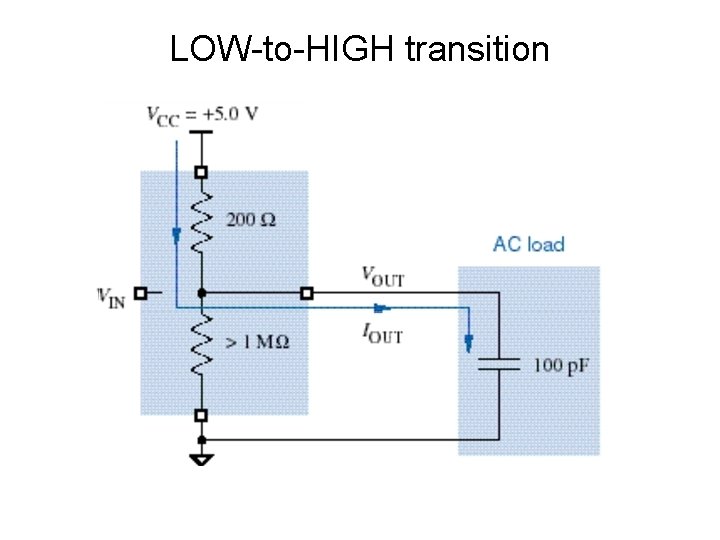

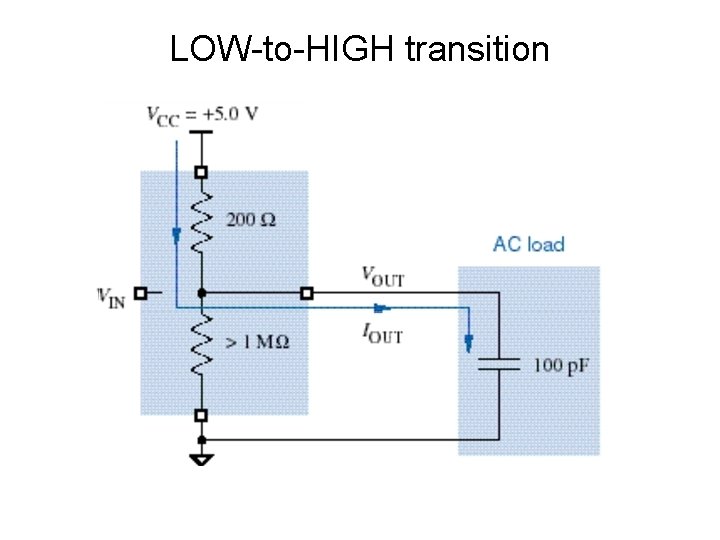

LOW-to-HIGH transition

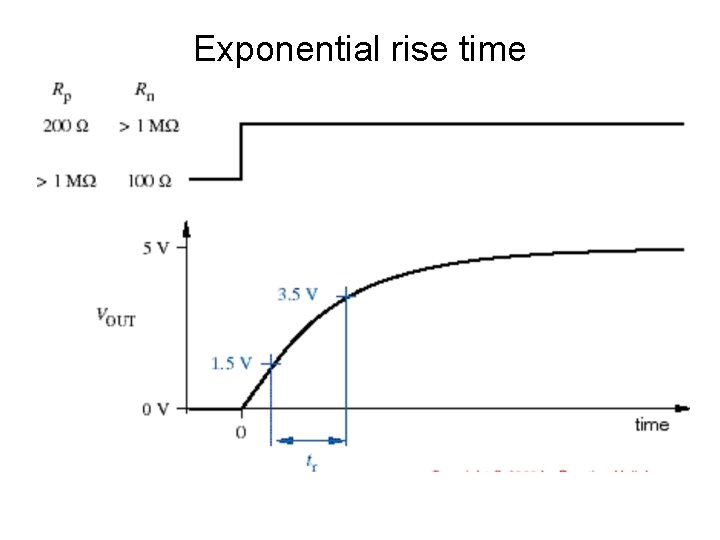

Exponential rise time

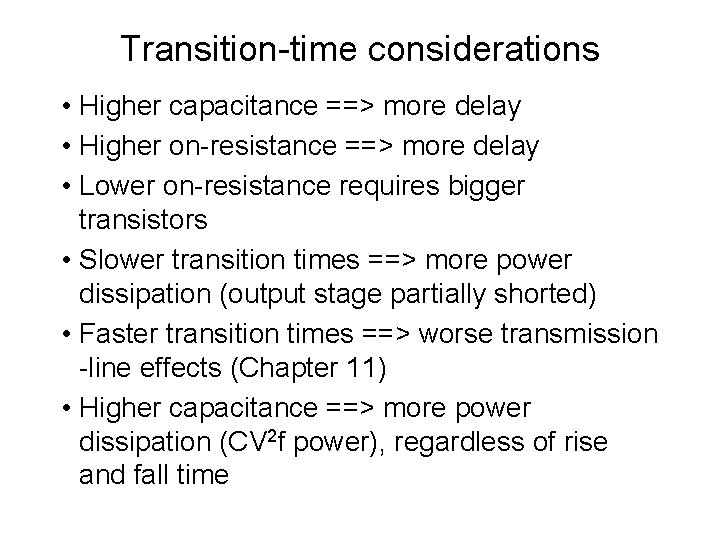

Transition-time considerations • Higher capacitance ==> more delay • Higher on-resistance ==> more delay • Lower on-resistance requires bigger transistors • Slower transition times ==> more power dissipation (output stage partially shorted) • Faster transition times ==> worse transmission -line effects (Chapter 11) • Higher capacitance ==> more power dissipation (CV 2 f power), regardless of rise and fall time

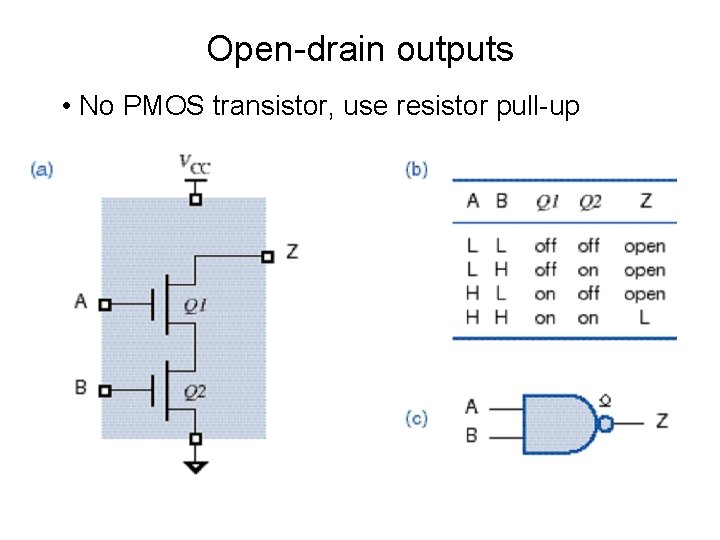

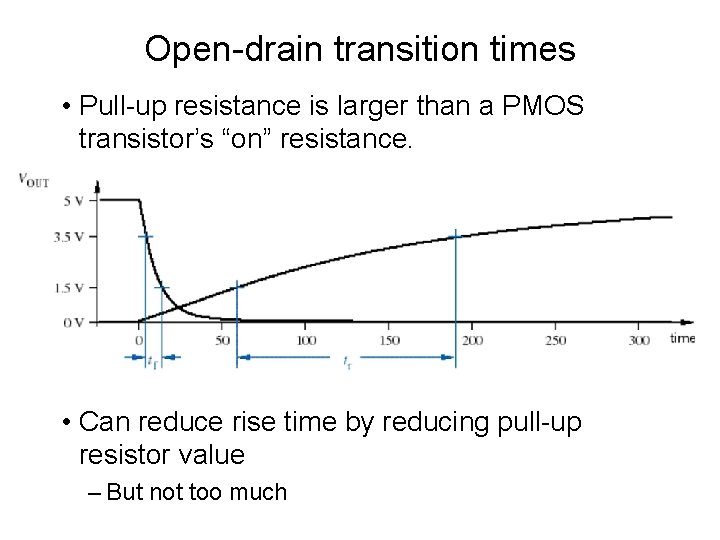

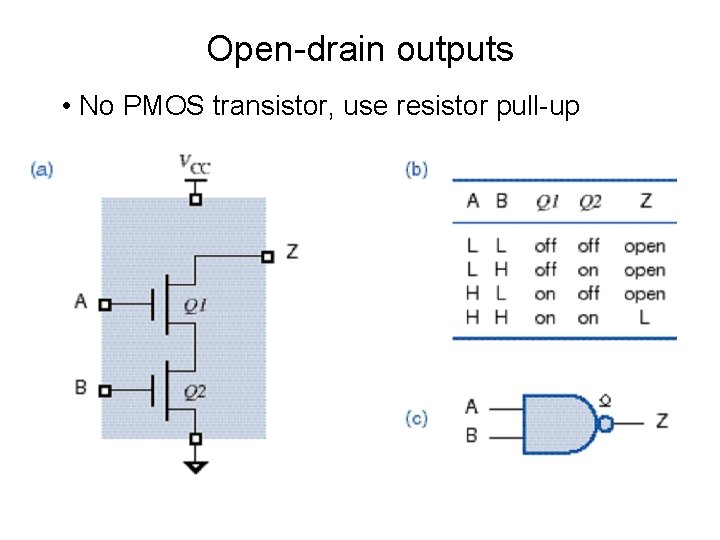

Open-drain outputs • No PMOS transistor, use resistor pull-up

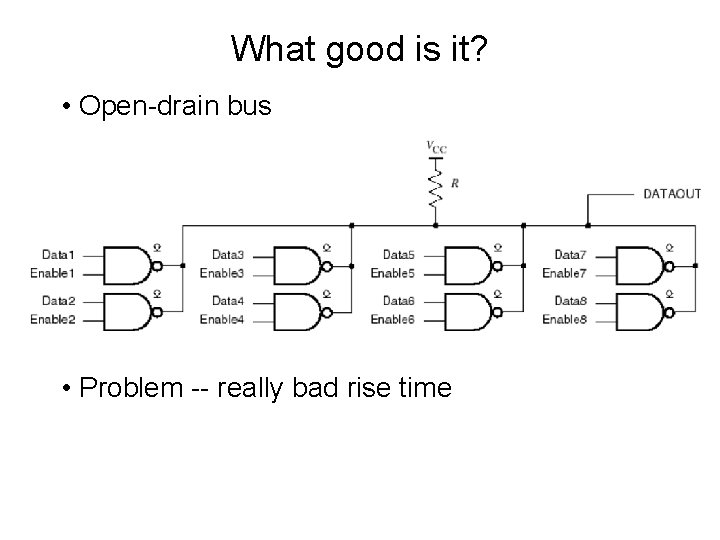

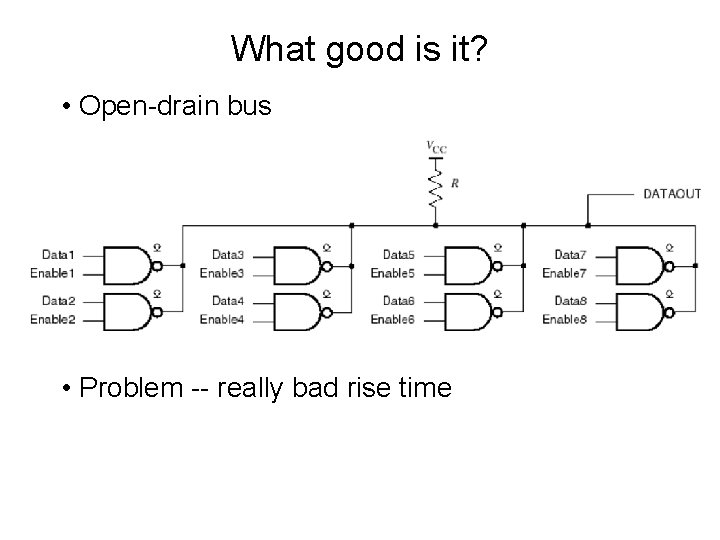

What good is it? • Open-drain bus • Problem -- really bad rise time

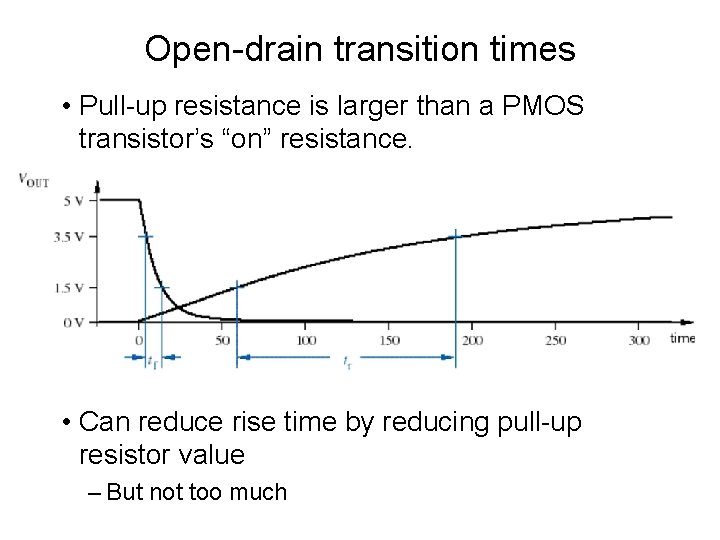

Open-drain transition times • Pull-up resistance is larger than a PMOS transistor’s “on” resistance. • Can reduce rise time by reducing pull-up resistor value – But not too much

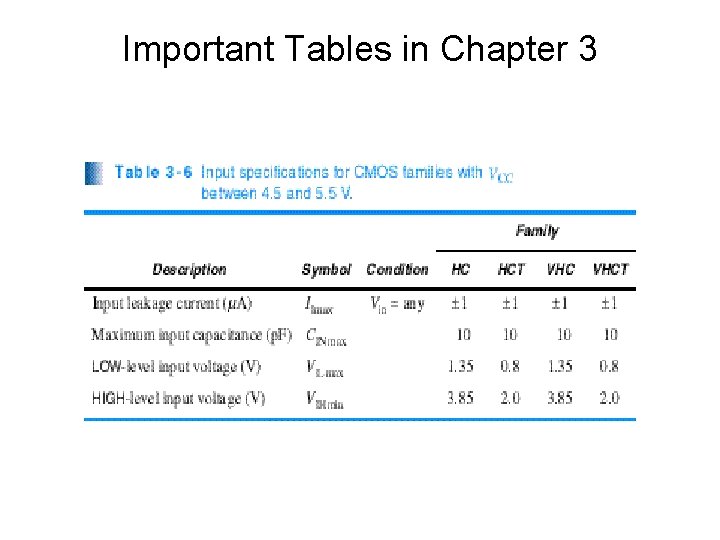

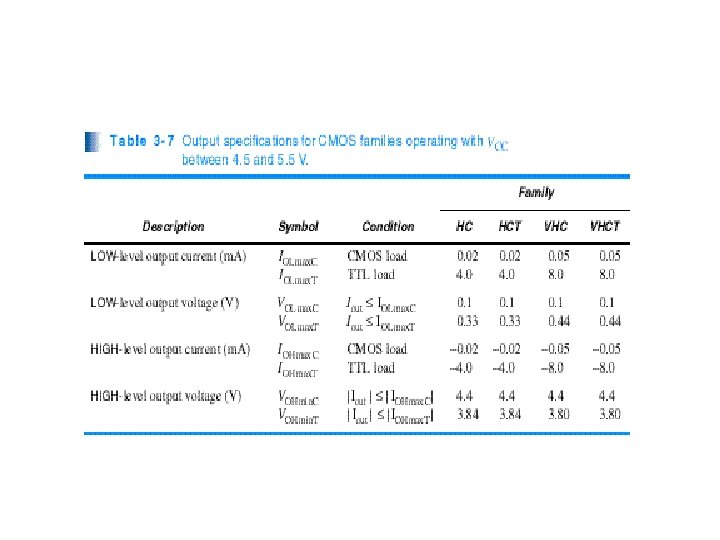

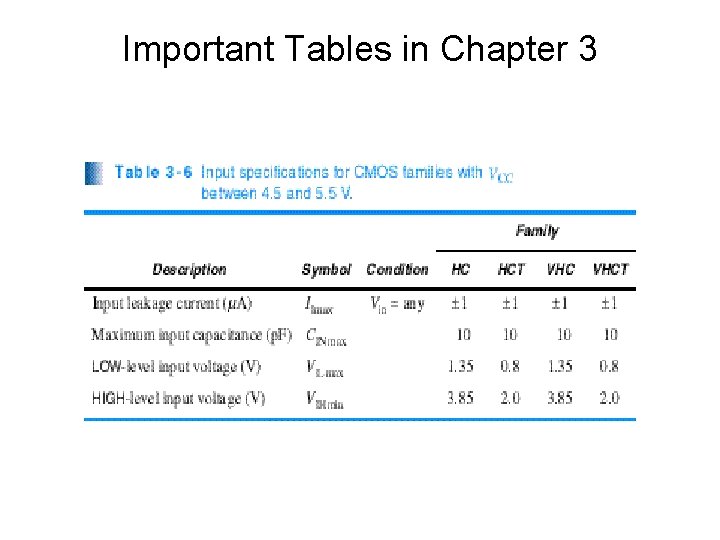

Important Tables in Chapter 3