SLK Capstone Design 1 CMOS Inverter 2 SONOS

![Reference Parameters Geometric parameters Value Process parameters Value The other parameters Value Ltotal [μm] Reference Parameters Geometric parameters Value Process parameters Value The other parameters Value Ltotal [μm]](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-7.jpg)

![Parameter Variables Nsub Reference Data #1 Data #2 [cm-3] Npg [cm-3] Xj, SD [nm] Parameter Variables Nsub Reference Data #1 Data #2 [cm-3] Npg [cm-3] Xj, SD [nm]](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-8.jpg)

![CMOS Inverter Example #1. Nsub, Lg variation 1. [Table #1]에 주어진 공정변수 변화(Nsub, Lg)에 CMOS Inverter Example #1. Nsub, Lg variation 1. [Table #1]에 주어진 공정변수 변화(Nsub, Lg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-37.jpg)

![CMOS Inverter Example #2. Npg variation [Table #2] 1. [Table #2]에 주어진 공정변수 변화(Npg)에 CMOS Inverter Example #2. Npg variation [Table #2] 1. [Table #2]에 주어진 공정변수 변화(Npg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-39.jpg)

![CMOS Inverter Example #3. Xj, SD, Lg variation 1. [Table #3]에 주어진 공정변수 변화(Xj, CMOS Inverter Example #3. Xj, SD, Lg variation 1. [Table #3]에 주어진 공정변수 변화(Xj,](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-40.jpg)

![CMOS Inverter Example #4. Nhalo, Lg variation 1. [Table #4]에 주어진 공정변수 변화(Nhalo, Lg)에 CMOS Inverter Example #4. Nhalo, Lg variation 1. [Table #4]에 주어진 공정변수 변화(Nhalo, Lg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-41.jpg)

![CMOS Inverter Example #5. Tox, Lg variation 1. [Table #5]에 주어진 공정변수 변화(Tox, Lg)에 CMOS Inverter Example #5. Tox, Lg variation 1. [Table #5]에 주어진 공정변수 변화(Tox, Lg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-42.jpg)

![CMOS Inverter Example #6. Wn : Wp variation 1. [Table #6]에 주어진 공정변수 변화(Wn CMOS Inverter Example #6. Wn : Wp variation 1. [Table #6]에 주어진 공정변수 변화(Wn](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-43.jpg)

![CMOS Inverter Example #7. Cload variation [Table #7] Process variations 1. [Table #7]에 주어진 CMOS Inverter Example #7. Cload variation [Table #7] Process variations 1. [Table #7]에 주어진](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-44.jpg)

![CMOS Inverter Example #8. εox variation [Table #8] 1. [Table #8]에 주어진 공정변수 변화(εox)에 CMOS Inverter Example #8. εox variation [Table #8] 1. [Table #8]에 주어진 공정변수 변화(εox)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-45.jpg)

![CMOS Inverter Example #9. qφm variation [Table #9] 1. [Table #9]에 주어진 공정변수 변화(qφm)에 CMOS Inverter Example #9. qφm variation [Table #9] 1. [Table #9]에 주어진 공정변수 변화(qφm)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-46.jpg)

- Slides: 46

S!LK Capstone Design Ⅰ 1. CMOS Inverter 2. SONOS Memory silk. kookmin. ac. kr 2014. 3. 13 Dae Hwan Kim Jungmin Lee Seungguk Kim <1>

CMOS Inverter Basic Theory <2>

Basic Theory CMOS inverter: • Most basic element of digital static CMOS circuit • Combination of an N-MOSFET and P-MOSFET • One of the transistors is “ON” in the steady state, there is no static current or static power consumption. • Power dissipation occurs only during switching transient when a charging or discharging current is flowing through the circuit. VDD + PMOS S B D Vin + Vout D - • Drain terminal of n. MOS and p. MOS are common and connected to the output terminal. • Source terminal of n. MOS is connected to the ground. • Source terminal of p. MOS is connected to the VDD. - NMOS B S <3>

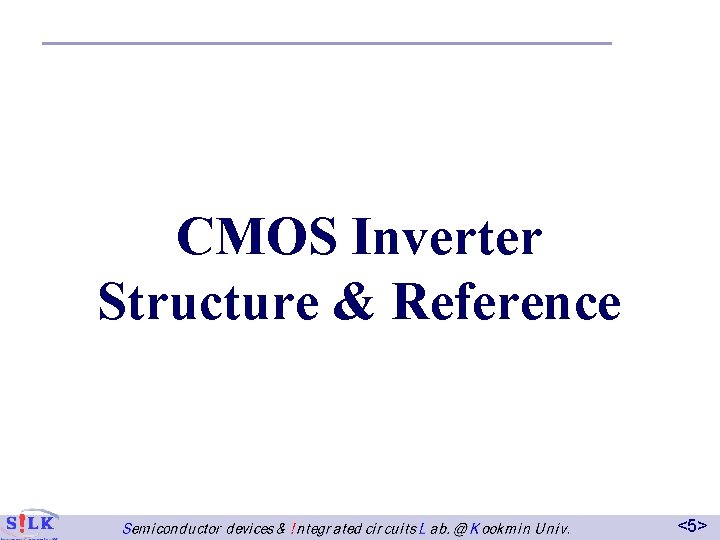

Basic Theory CMOS inverter I-V Characteristics: Case 1) Vin= 0 Vgsn= 0 → n. MOS “OFF” Vgsp= -VDD → p. MOS “ON” ⇒Vout= VDD by current path through p. MOS as a pull-up transistor Case 2) Vin= Vdd Vgsn= VDD → n. MOS “ON” Vgsp= 0 → p. MOS “OFF” ⇒Vout= 0 by current path through n. MOS as a pull-down transistor One transistor is “ON”, there is no direct current from VDD to the GND ⇒ No static power consumption <4>

CMOS Inverter Structure & Reference <5>

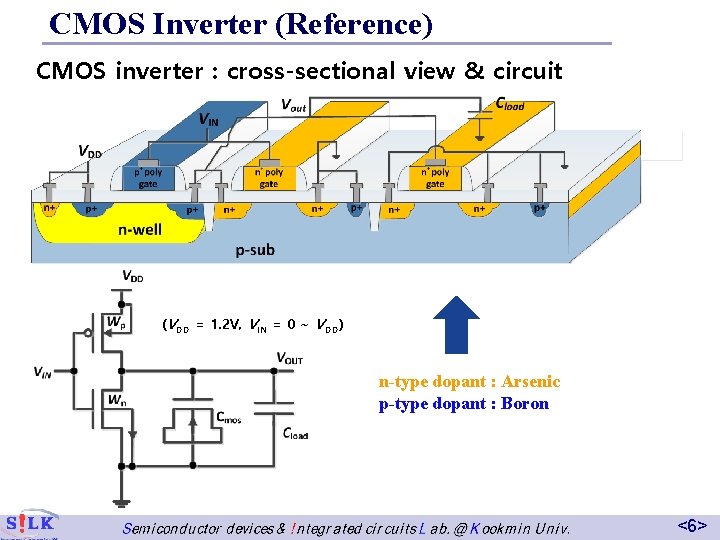

CMOS Inverter (Reference) CMOS inverter : cross-sectional view & circuit (VDD = 1. 2 V, VIN = 0 ~ VDD) n-type dopant : Arsenic p-type dopant : Boron <6>

![Reference Parameters Geometric parameters Value Process parameters Value The other parameters Value Ltotal μm Reference Parameters Geometric parameters Value Process parameters Value The other parameters Value Ltotal [μm]](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-7.jpg)

Reference Parameters Geometric parameters Value Process parameters Value The other parameters Value Ltotal [μm] 1. 1 Nsub [cm-3] 7 x 1017 VDD [V] 1. 2 Lg [nm] 65 Npg [cm-3] 1 x 1020 Cload [f. F] 2. 1 Lsp [μm] 0. 1 NS or ND [cm-3] 1 x 1020 Cmos [f. F] 2. 1 Tox [nm] 1. 5 Nhalo [cm-3] 3 x 1017 Hsub [μm] 1 Hpg [μm] 0. 2 n. MOS (p. MOS) gate type n+ (p+) polysilicon Xj, SD [μm] 0. 12 n. MOS (p. MOS) source/drain type n+ (p+) polysilicon Wn or. Wp 1 n. MOS (p. MOS) substrate type p (n) silicon [μm] <n. MOSFET structure> 3. 9 (Si. O 2) *n. MOSFET/p. MOSFET/MOS-cap : Type을 제외한 모든 parameters 값은 같음 MOS-cap은 n. MOSFET type <7>

![Parameter Variables Nsub Reference Data 1 Data 2 cm3 Npg cm3 Xj SD nm Parameter Variables Nsub Reference Data #1 Data #2 [cm-3] Npg [cm-3] Xj, SD [nm]](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-8.jpg)

Parameter Variables Nsub Reference Data #1 Data #2 [cm-3] Npg [cm-3] Xj, SD [nm] Nhalo 120 60 180 [cm- 3] Tox [nm] 1. 5 3 6 Lg [nm] 65 40 200 Wn : Wp 1 : 2. 5 1: 1 1: 4 Cload 1 × CMOS 0. 1 × CMOS 10 × CMOS εox Si. O 2 (3. 9) Hf. O 2 (22) Si 3 N 4 (7. 5) Variables Reference Data #1 Data #2 Wn : Wp 1 : 2. 5 1: 1 1: 4 Cload 1 × CMOS 0. 1 × CMOS 10 × CMOS εox Si. O 2 Hf. O 2 Si 3 N 4 Gate material (qφm) (n. MOS : 4. 05 p. MOS : 5. 16) Polysilicon n. MOS : Molybdenum (4. 53) p. MOS : Copper (4. 7) (CMOS = 2. 1 f. F) <8>

Electrical Parameters <9>

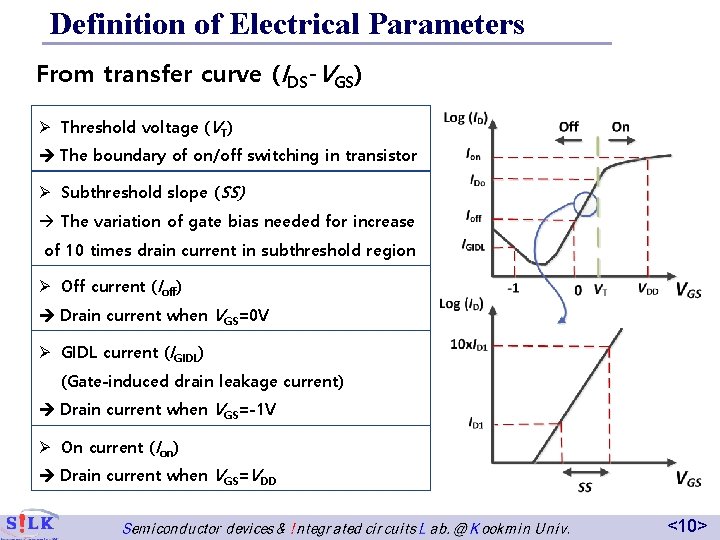

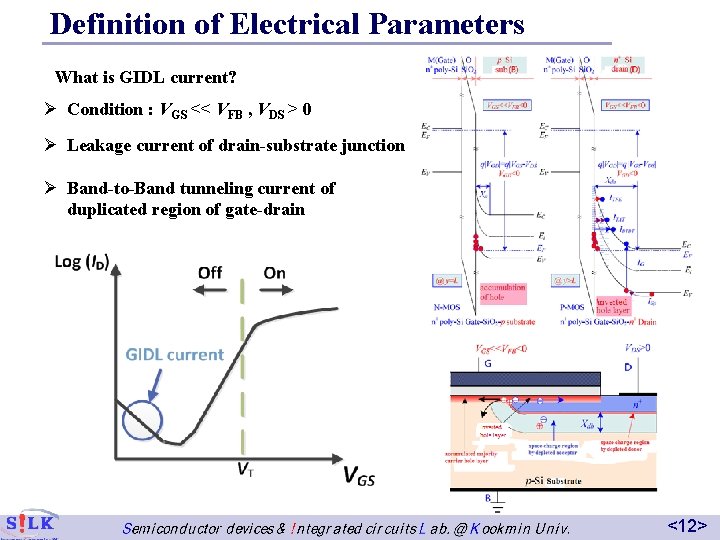

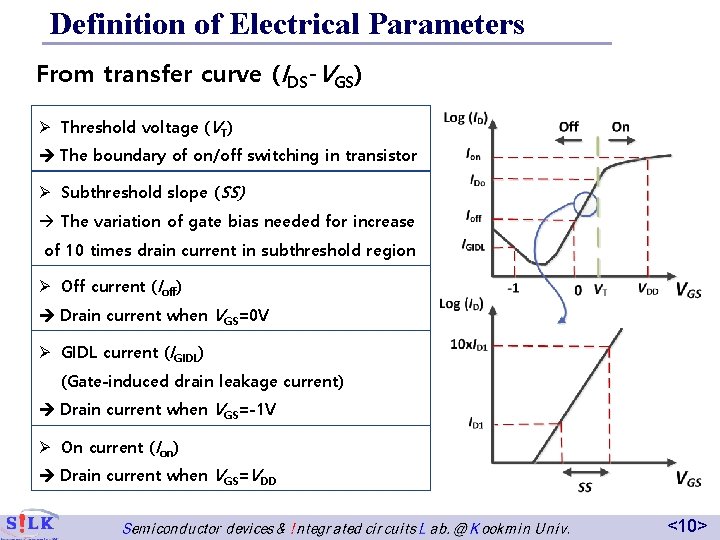

Definition of Electrical Parameters From transfer curve (IDS-VGS) Ø Threshold voltage (VT) The boundary of on/off switching in transistor Ø Subthreshold slope (SS) à The variation of gate bias needed for increase of 10 times drain current in subthreshold region Ø Off current (Ioff) Drain current when VGS=0 V Ø GIDL current (IGIDL) (Gate-induced drain leakage current) Drain current when VGS=-1 V Ø On current (Ion) Drain current when VGS=VDD <10>

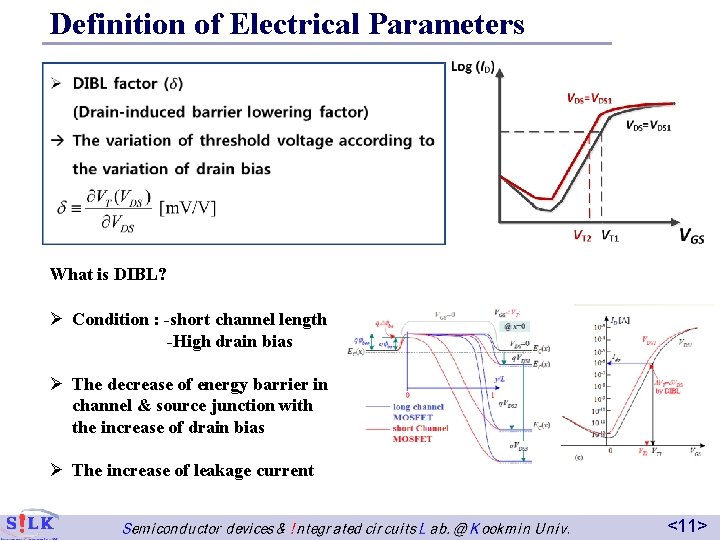

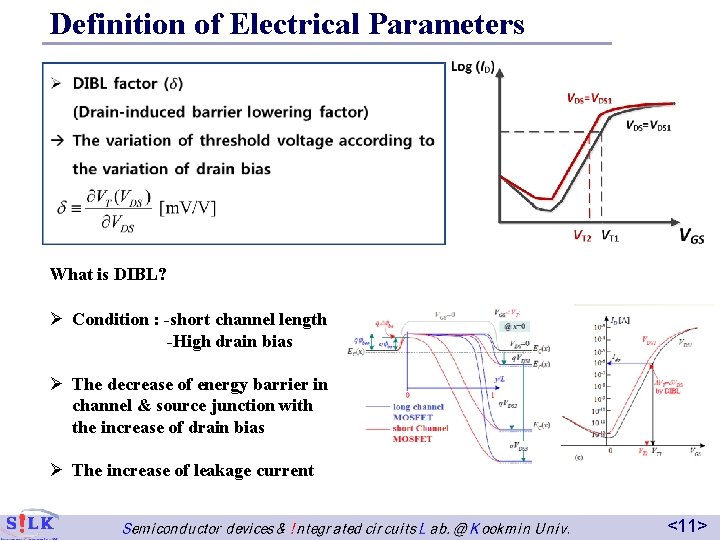

Definition of Electrical Parameters What is DIBL? Ø Condition : -short channel length -High drain bias Ø The decrease of energy barrier in channel & source junction with the increase of drain bias Ø The increase of leakage current <11>

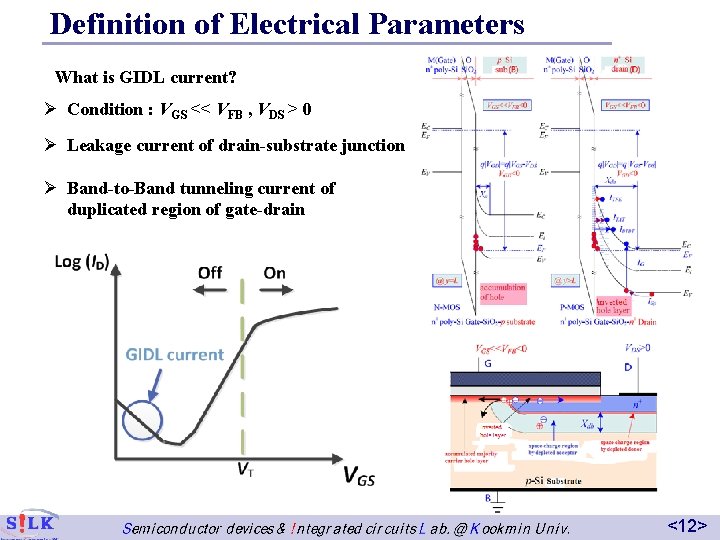

Definition of Electrical Parameters What is GIDL current? Ø Condition : VGS << VFB , VDS > 0 Ø Leakage current of drain-substrate junction Ø Band-to-Band tunneling current of duplicated region of gate-drain <12>

Circuit Performance Index (1) Voltage Transfer Characteristics <13>

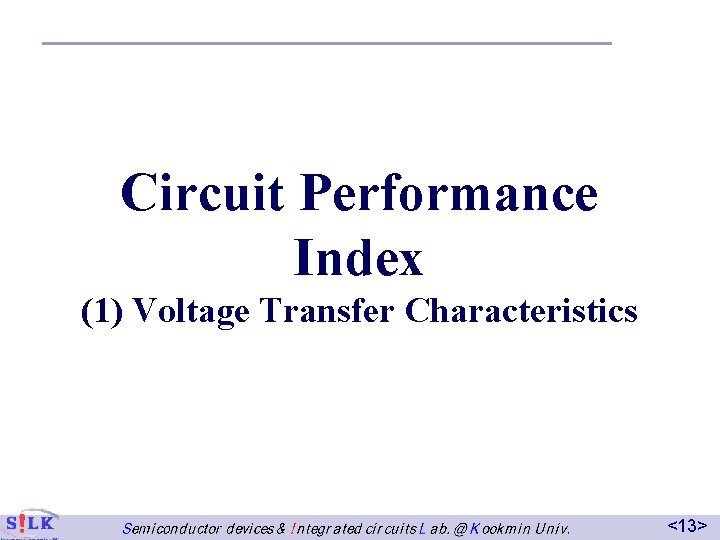

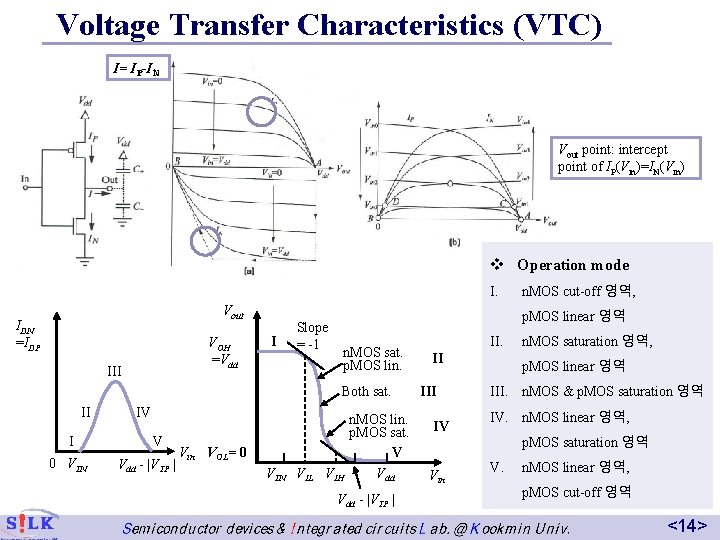

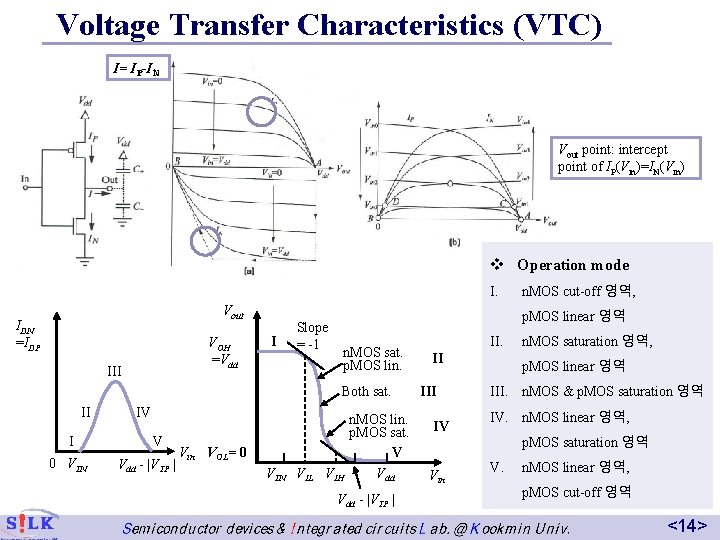

Voltage Transfer Characteristics (VTC) I= IP-IN IDS NMOS Vin=VDD Vout point: intercept point of IP(Vin)=IN(Vin) III IV PMOS Vin=0 II NMOS PMOS Vin=0 Vin=VDD V I Vout VDD 0 v Operation mode I. Vout IDN =IDP VOH =Vdd III I Slope = -1 p. MOS linear 영역 n. MOS sat. p. MOS lin. Both sat. II I 0 VTN IV V Vdd - |VTP | n. MOS cut-off 영역, n. MOS lin. p. MOS sat. V Vin VOL= 0 VTN VIL VIH Vdd - |VTP | II. II IV n. MOS saturation 영역, p. MOS linear 영역 III. n. MOS & p. MOS saturation 영역 IV. n. MOS linear 영역, p. MOS saturation 영역 Vin V. n. MOS linear 영역, p. MOS cut-off 영역 <14>

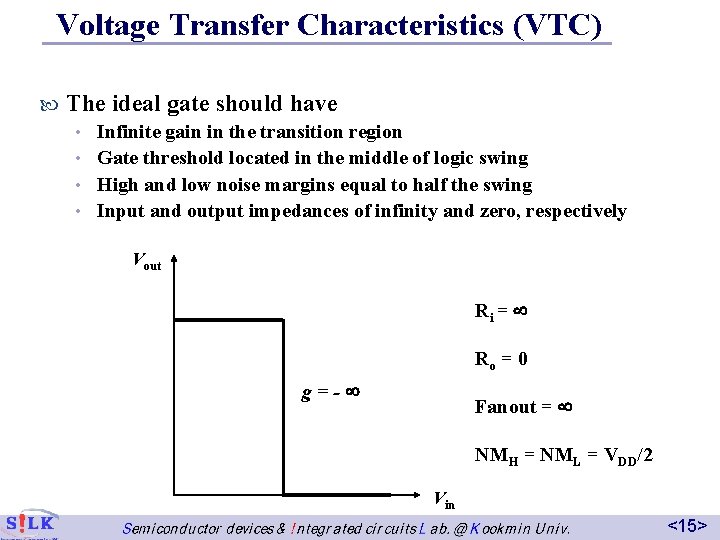

Voltage Transfer Characteristics (VTC) The ideal gate should have Infinite gain in the transition region • Gate threshold located in the middle of logic swing • High and low noise margins equal to half the swing • Input and output impedances of infinity and zero, respectively • Vout Ri = Ro = 0 g=- Fanout = NMH = NML = VDD/2 Vin <15>

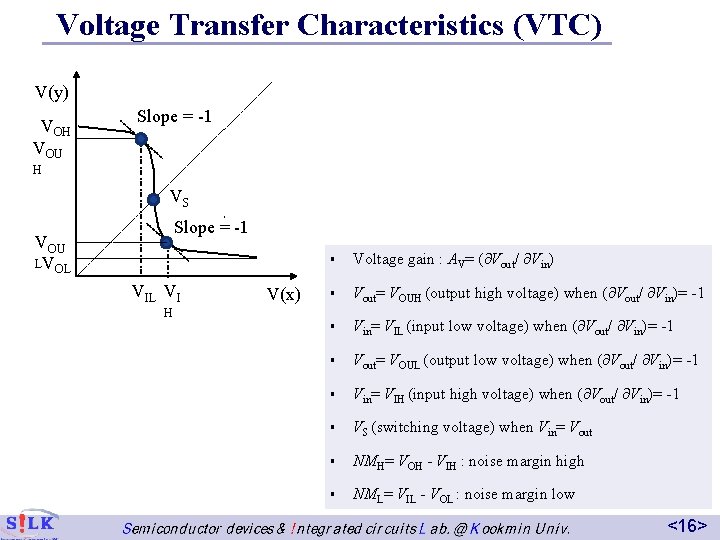

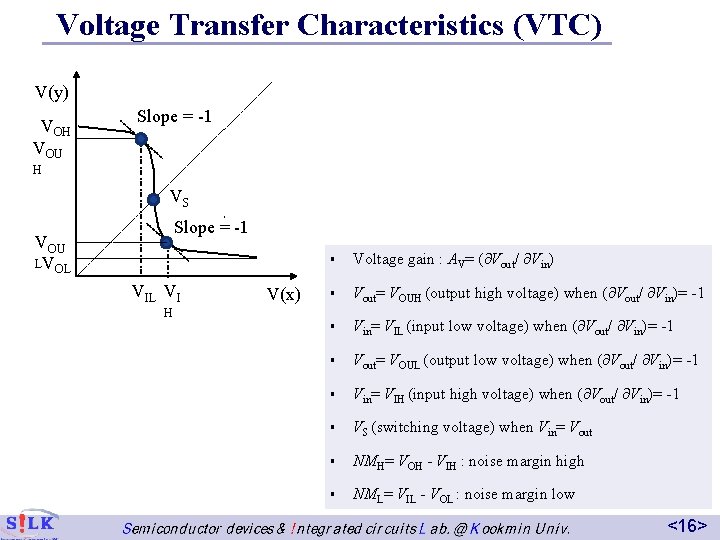

Voltage Transfer Characteristics (VTC) V(y) VOH VOU Slope = -1 H VS Slope = -1 VOU LVOL VI V(x) § Voltage gain : AV= (∂Vout/ ∂Vin) § Vout= VOUH (output high voltage) when (∂Vout/ ∂Vin)= -1 § Vin= VIL (input low voltage) when (∂Vout/ ∂Vin)= -1 § Vout= VOUL (output low voltage) when (∂Vout/ ∂Vin)= -1 § Vin= VIH (input high voltage) when (∂Vout/ ∂Vin)= -1 § VS (switching voltage) when Vin= Vout § NMH= VOH - VIH : noise margin high § NML= VIL - VOL : noise margin low H <16>

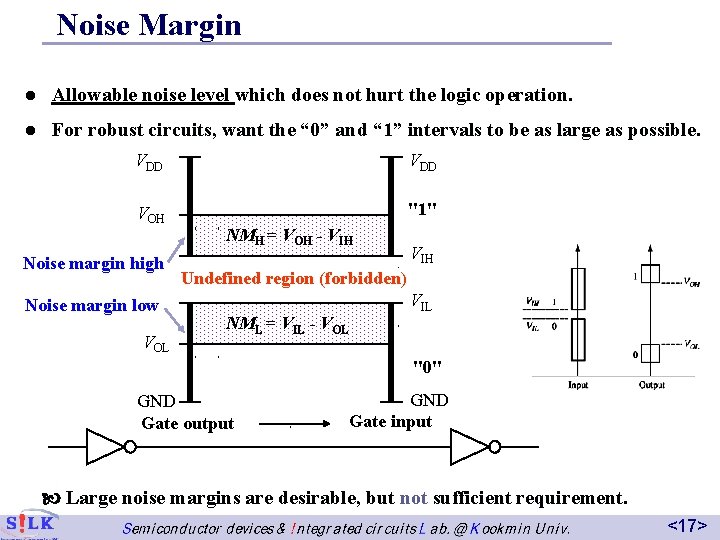

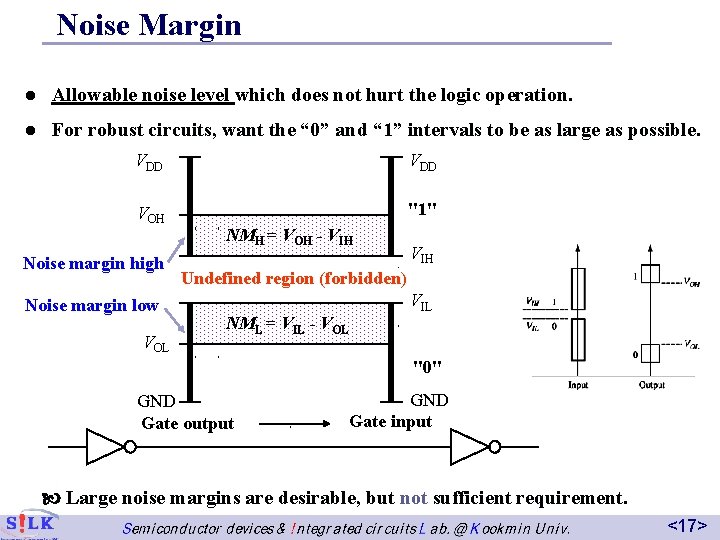

Noise Margin l Allowable noise level which does not hurt the logic operation. l For robust circuits, want the “ 0” and “ 1” intervals to be as large as possible. VDD VOH "1" Noise margin high Noise margin low VOL NMH = VOH - VIH Undefined region (forbidden) NML = VIL - VOL VIL "0" GND Gate output GND Gate input Large noise margins are desirable, but not sufficient requirement. <17>

Circuit Performance Index (2) Delay Calculation <18>

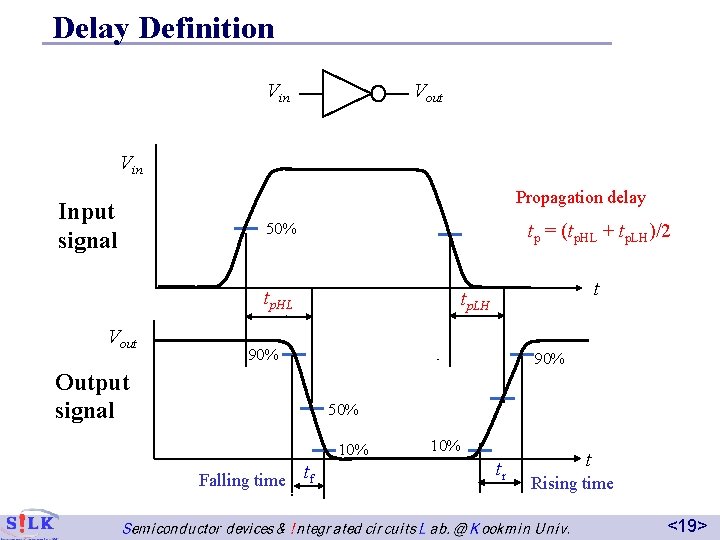

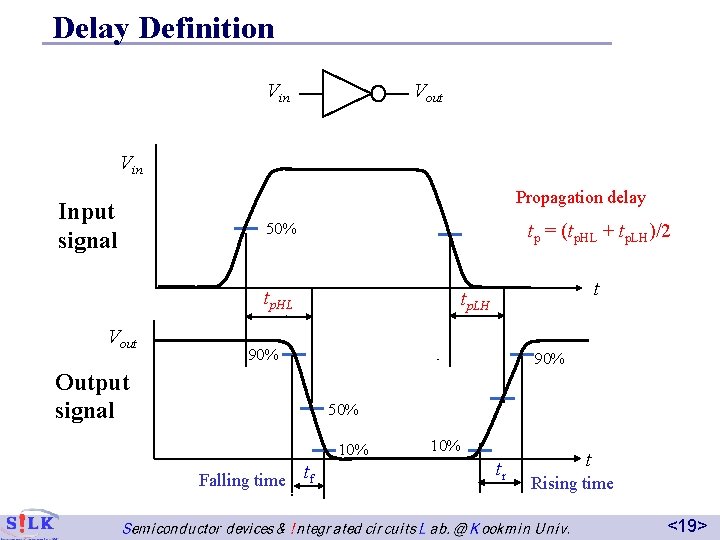

Delay Definition Vin Vout Vin Input signal Propagation delay 50% tp = (tp. HL + tp. LH)/2 tp. HL Vout t tp. LH 90% Output signal 90% 50% 10% Falling time tf 10% tr t Rising time <19>

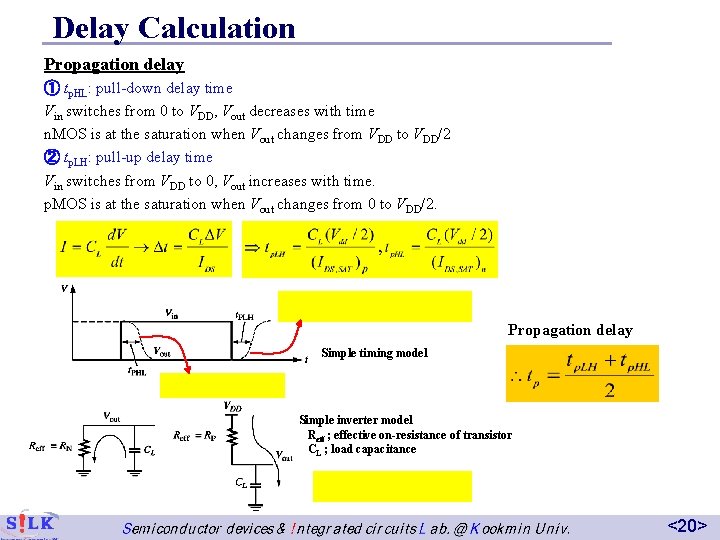

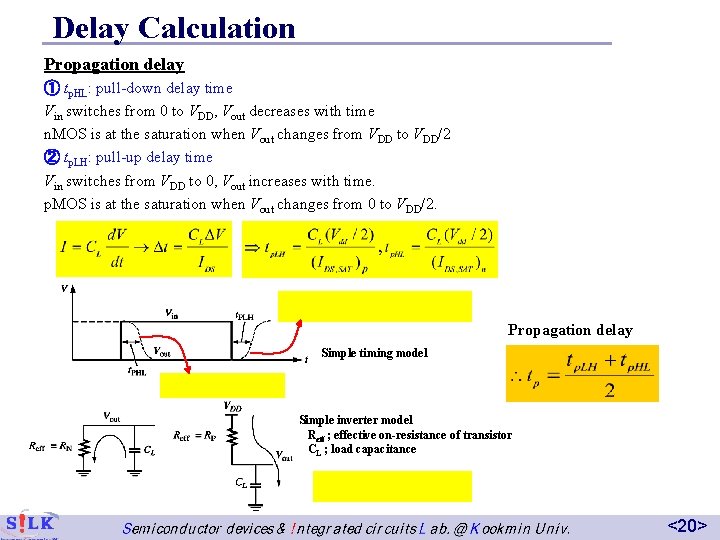

Delay Calculation Propagation delay ① tp. HL: pull-down delay time Vin switches from 0 to VDD, Vout decreases with time n. MOS is at the saturation when Vout changes from VDD to VDD/2 ② tp. LH: pull-up delay time Vin switches from VDD to 0, Vout increases with time. p. MOS is at the saturation when Vout changes from 0 to VDD/2. Propagation delay Simple timing model Simple inverter model Reff ; effective on-resistance of transistor CL ; load capacitance <20>

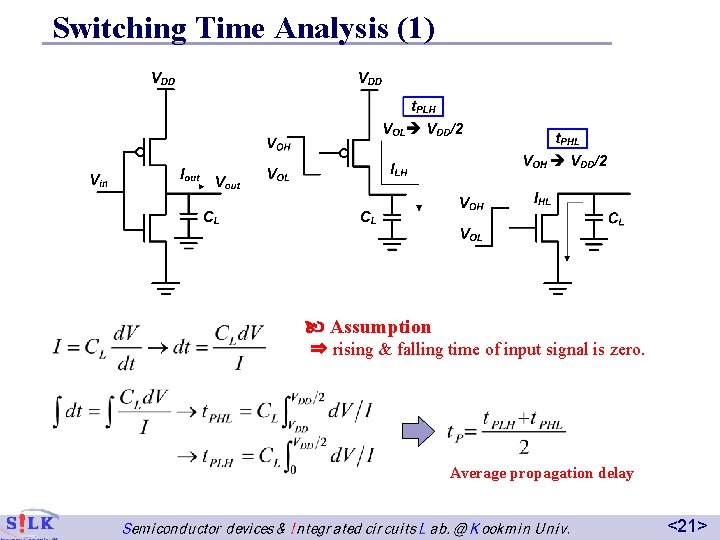

Switching Time Analysis (1) Assumption ⇒ rising & falling time of input signal is zero. Average propagation delay <21>

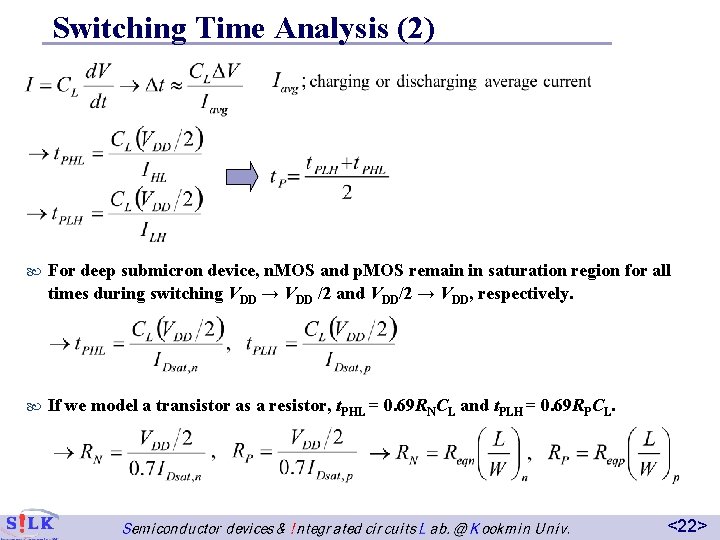

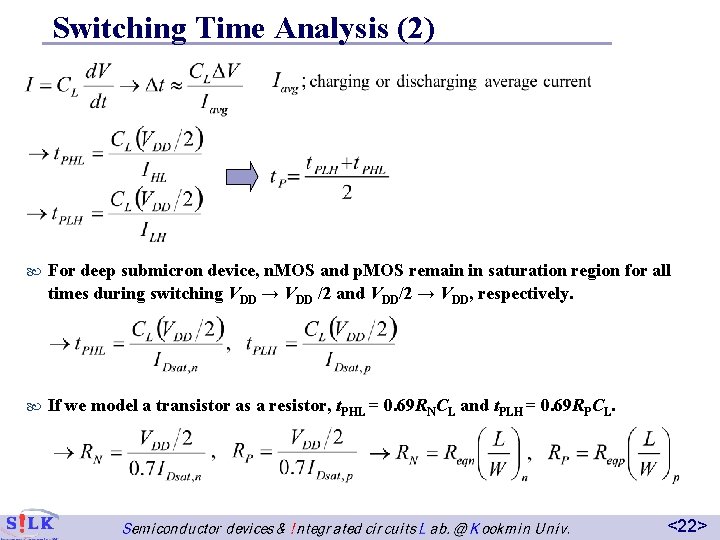

Switching Time Analysis (2) For deep submicron device, n. MOS and p. MOS remain in saturation region for all times during switching VDD → VDD /2 and VDD/2 → VDD, respectively. If we model a transistor as a resistor, t. PHL = 0. 69 RNCL and t. PLH = 0. 69 RPCL. <22>

Circuit Performance Index (3) Power Consumption <23>

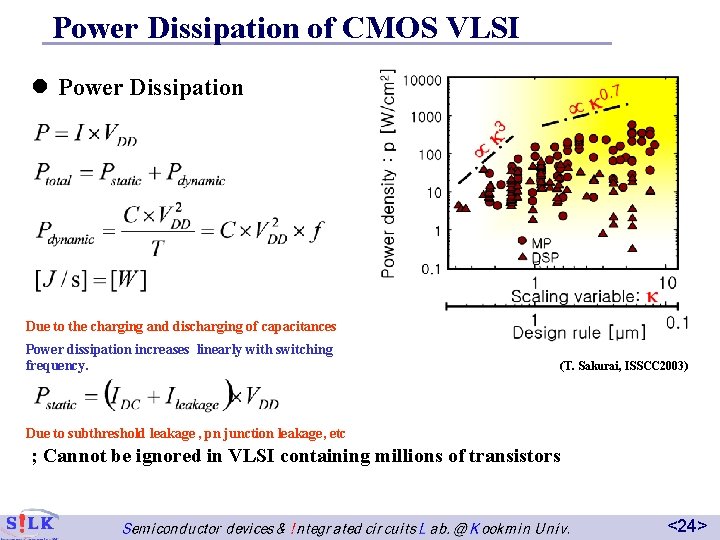

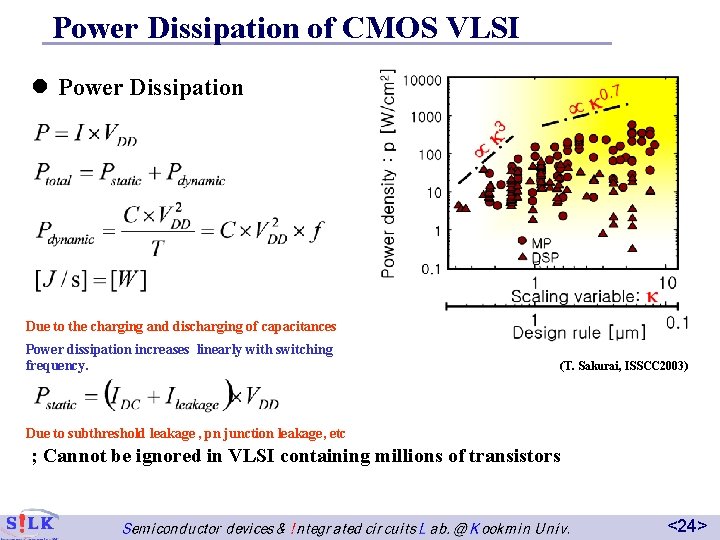

Power Dissipation of CMOS VLSI l Power Dissipation Due to the charging and discharging of capacitances Power dissipation increases linearly with switching frequency. (T. Sakurai, ISSCC 2003) Due to subthreshold leakage , pn junction leakage, etc ; Cannot be ignored in VLSI containing millions of transistors <24>

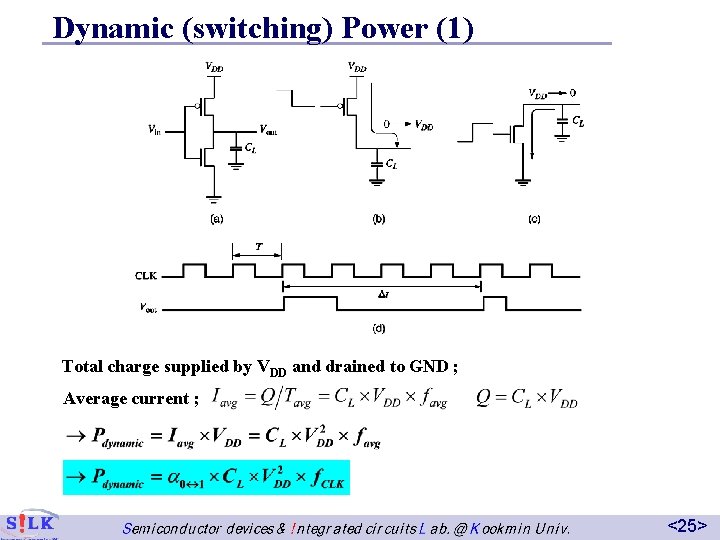

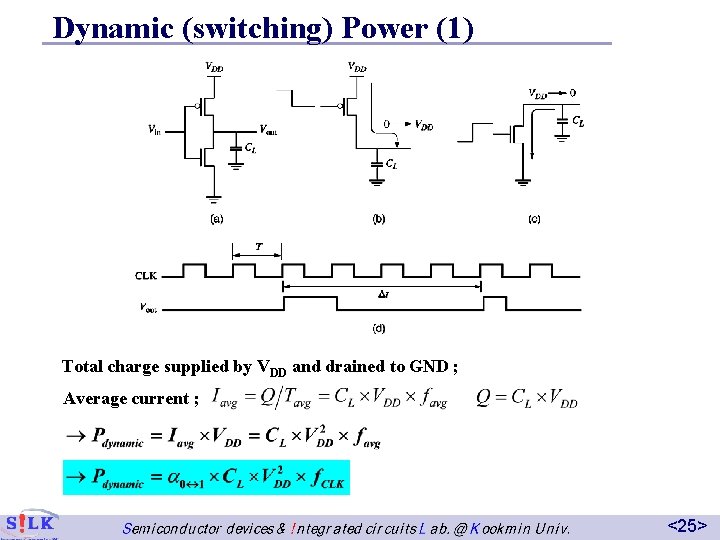

Dynamic (switching) Power (1) Total charge supplied by VDD and drained to GND ; Average current ; <25>

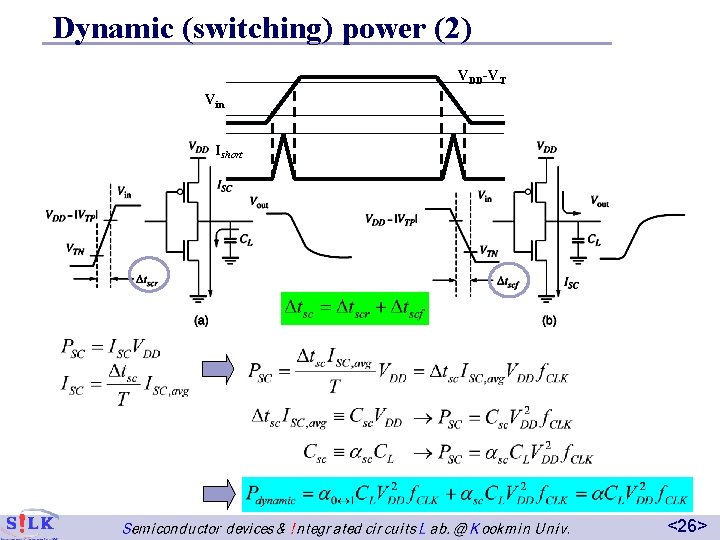

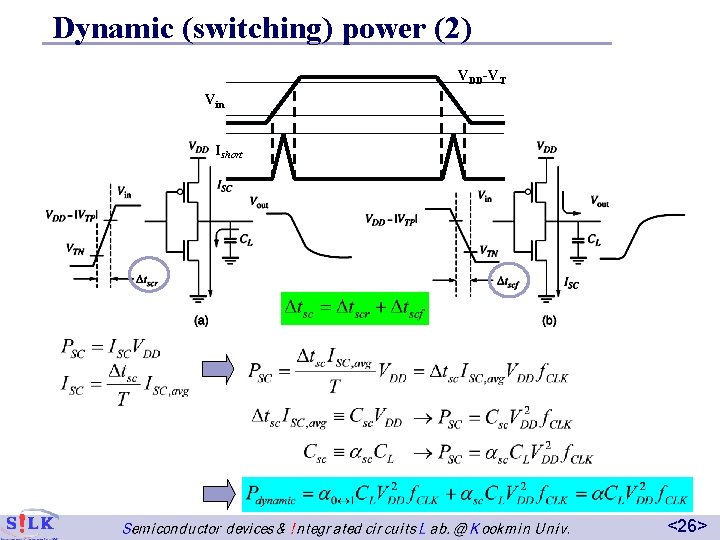

Dynamic (switching) power (2) VDD-VT Vin Ishort n Practical dynamic power is larger than n Due to the short circuit power dissipation <26>

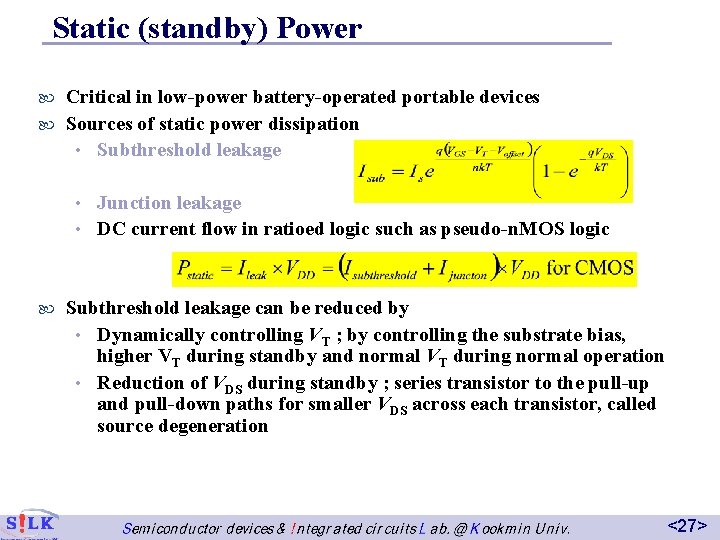

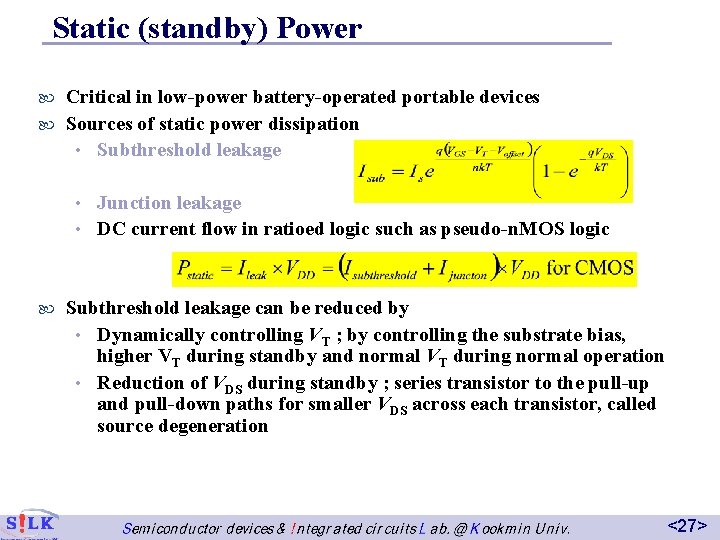

Static (standby) Power Critical in low-power battery-operated portable devices Sources of static power dissipation • Subthreshold leakage Junction leakage • DC current flow in ratioed logic such as pseudo-n. MOS logic • Subthreshold leakage can be reduced by • Dynamically controlling VT ; by controlling the substrate bias, higher VT during standby and normal VT during normal operation • Reduction of VDS during standby ; series transistor to the pull-up and pull-down paths for smaller VDS across each transistor, called source degeneration <27>

TCAD simulation <28>

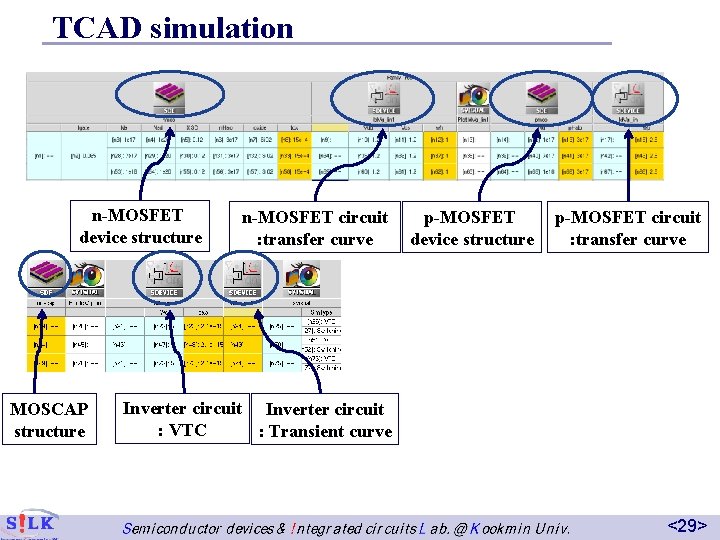

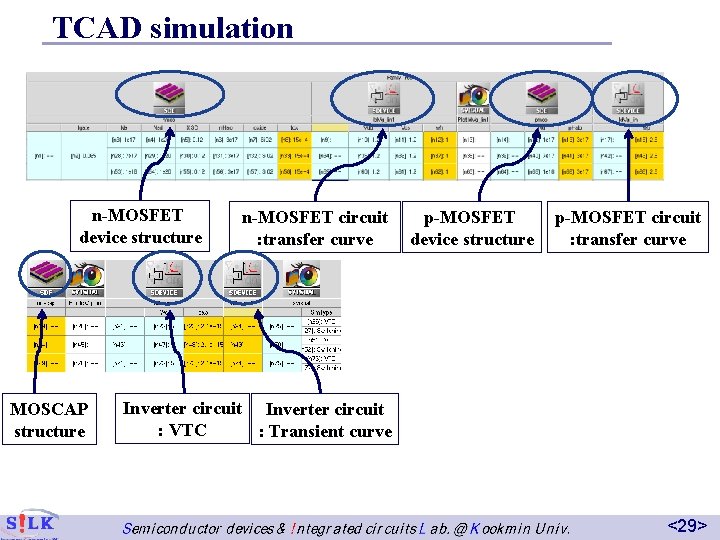

TCAD simulation n-MOSFET device structure MOSCAP structure n-MOSFET circuit : transfer curve p-MOSFET device structure p-MOSFET circuit : transfer curve Inverter circuit : VTC : Transient curve <29>

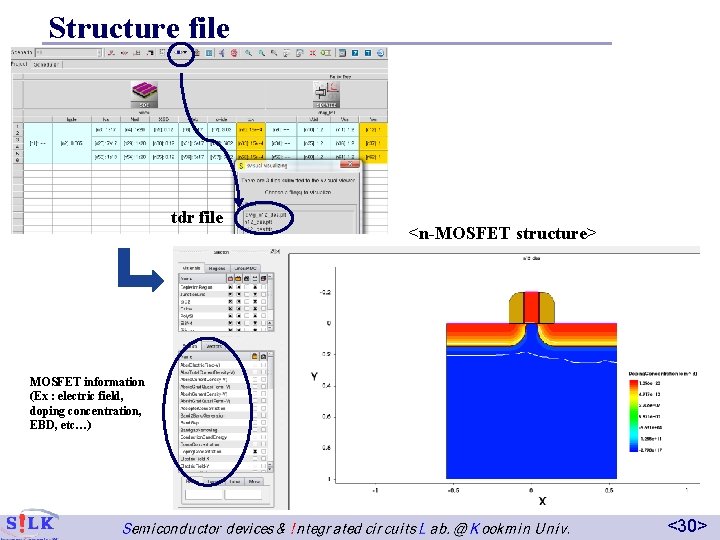

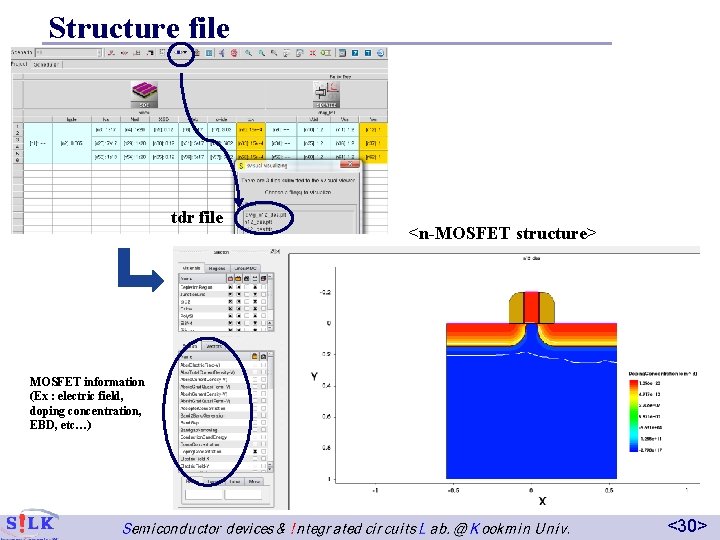

Structure file tdr file <n-MOSFET structure> MOSFET information (Ex : electric field, doping concentration, EBD, etc…) <30>

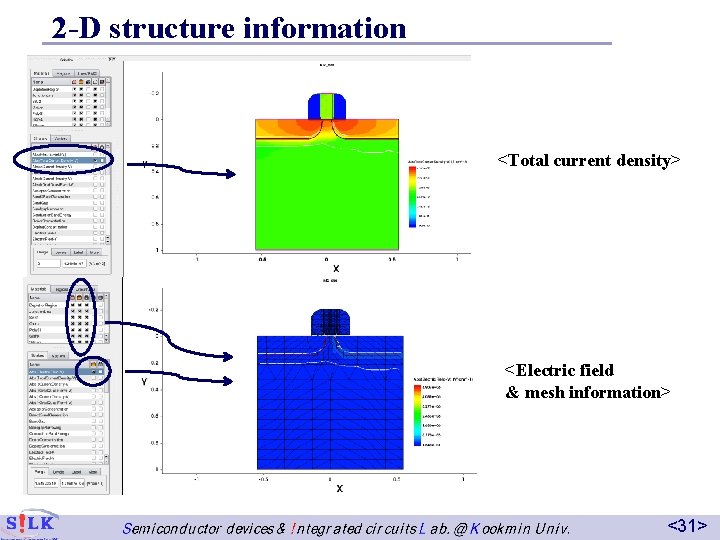

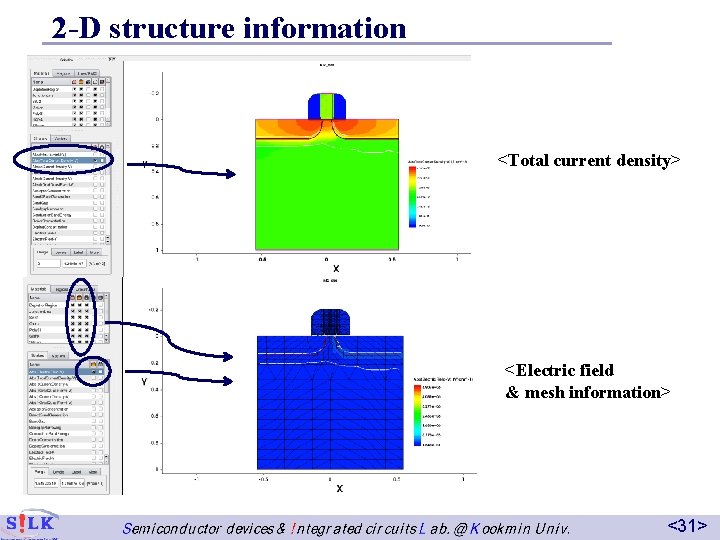

2 -D structure information <Total current density> <Electric field & mesh information> <31>

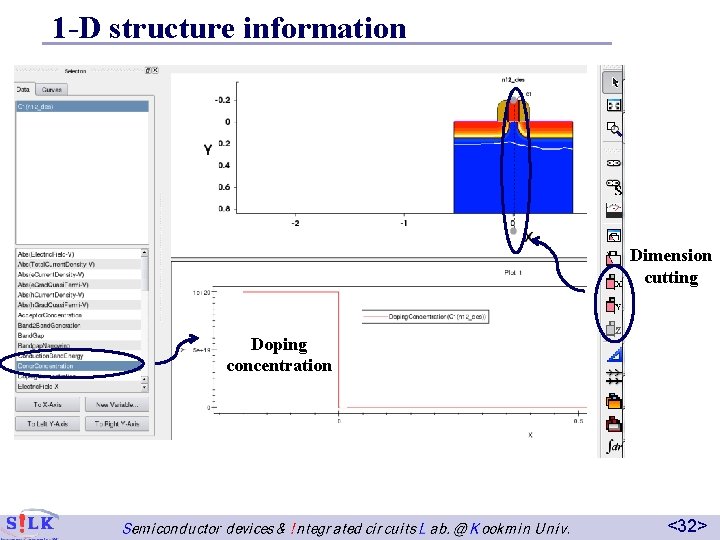

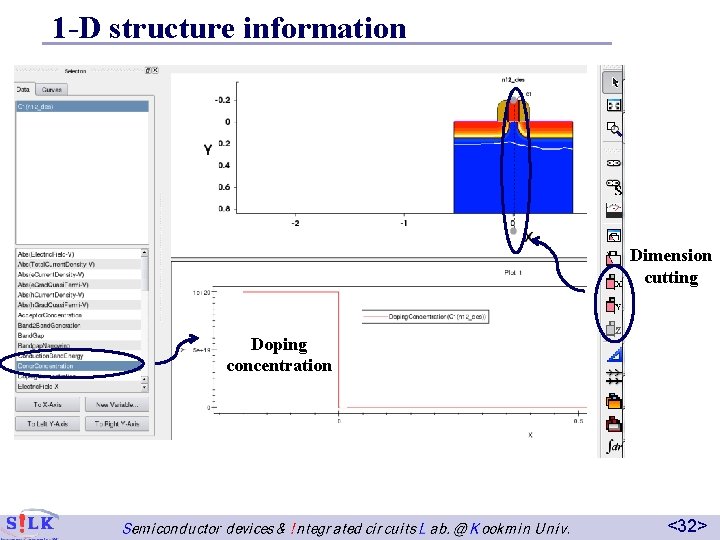

1 -D structure information Dimension cutting Doping concentration <32>

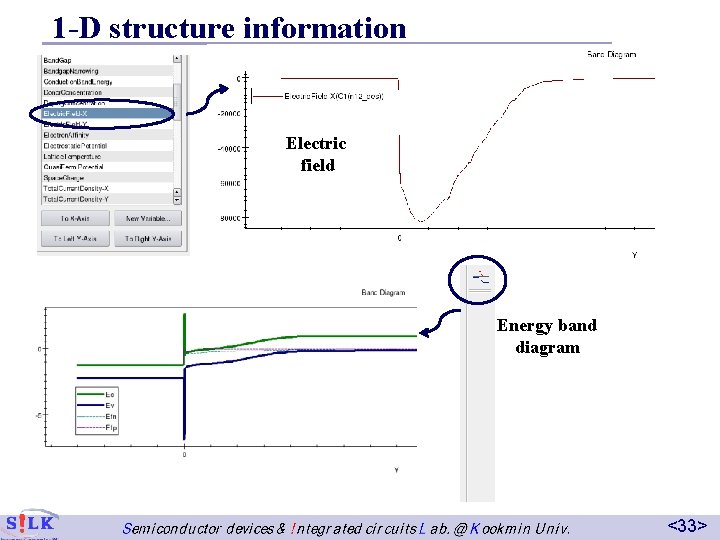

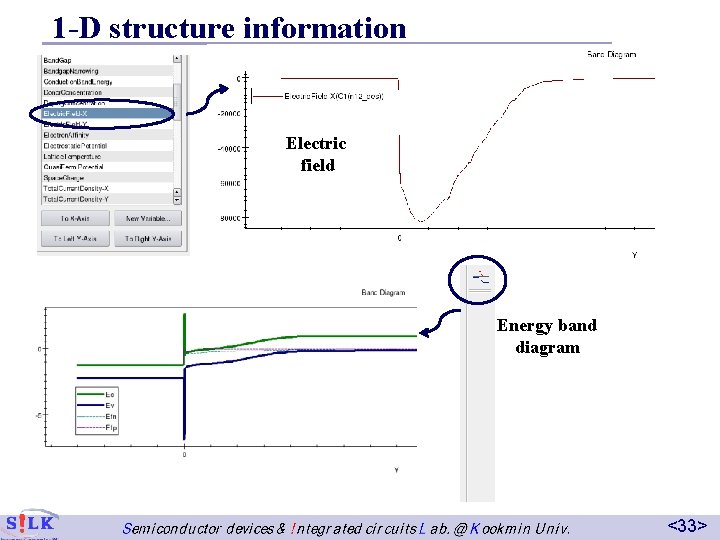

1 -D structure information Electric field Energy band diagram <33>

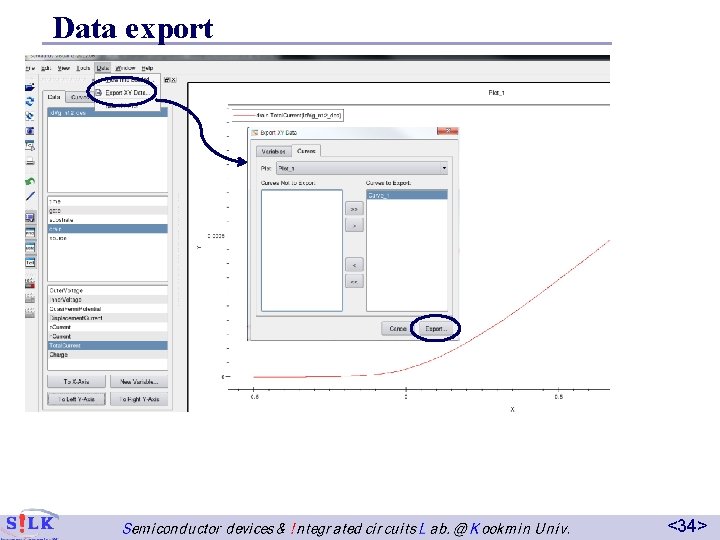

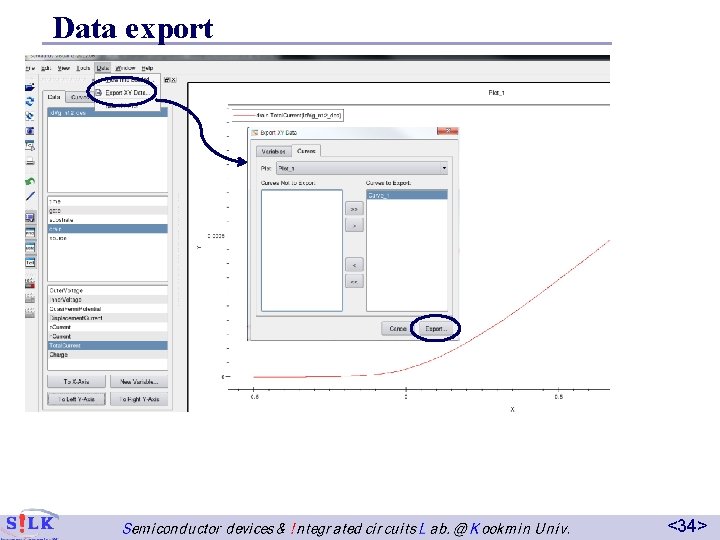

Data export <34>

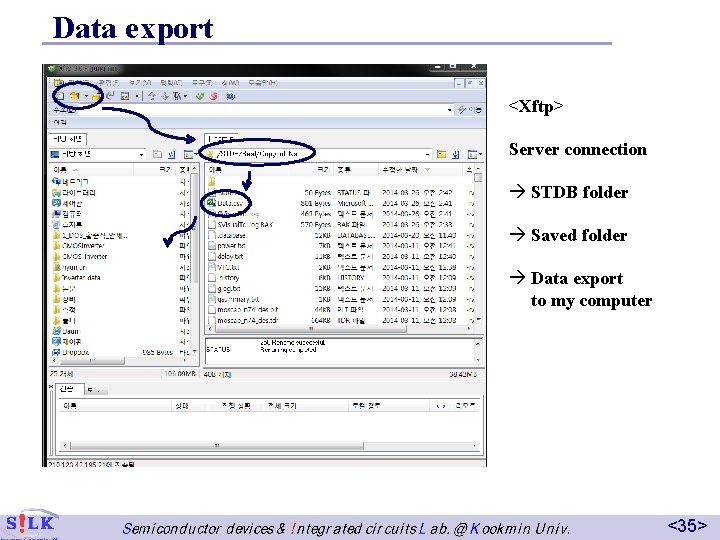

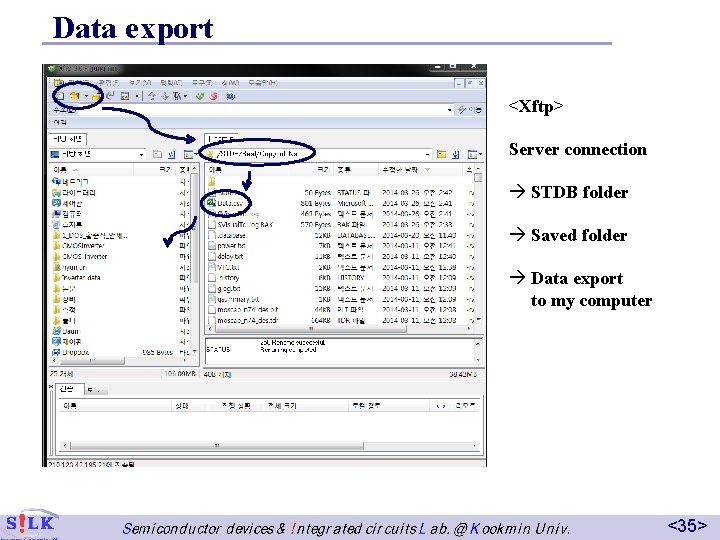

Data export <Xftp> Server connection à STDB folder à Saved folder à Data export to my computer <35>

Homework <36>

![CMOS Inverter Example 1 Nsub Lg variation 1 Table 1에 주어진 공정변수 변화Nsub Lg에 CMOS Inverter Example #1. Nsub, Lg variation 1. [Table #1]에 주어진 공정변수 변화(Nsub, Lg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-37.jpg)

CMOS Inverter Example #1. Nsub, Lg variation 1. [Table #1]에 주어진 공정변수 변화(Nsub, Lg)에 따라 아래의 소자변수를 비교하고 이유에 대해 논하시오. (Lg variation : short channel effect 관점) [Table #1] Process variations Nsub [cm-3] Reference Data #1 Data #2 Process variations Lg [nm] Reference Data #1 Data #2 <37>

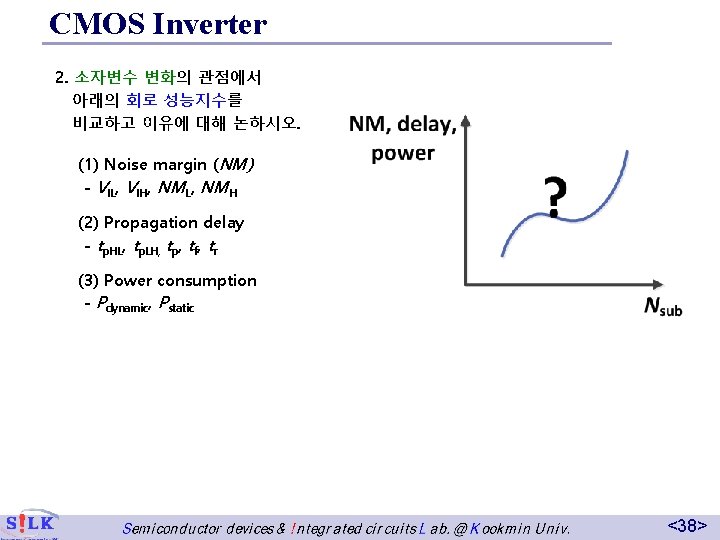

CMOS Inverter 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교하고 이유에 대해 논하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <38>

![CMOS Inverter Example 2 Npg variation Table 2 1 Table 2에 주어진 공정변수 변화Npg에 CMOS Inverter Example #2. Npg variation [Table #2] 1. [Table #2]에 주어진 공정변수 변화(Npg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-39.jpg)

CMOS Inverter Example #2. Npg variation [Table #2] 1. [Table #2]에 주어진 공정변수 변화(Npg)에 따라 아래의 소자변수를 비교하고 이유에 대해 논하시오. (1) Threshold voltage (VT) (2) Subthreshold slope (SS) (3) On current (Ion) (4) Off current (Ioff) (5) GIDL current (IGIDL) Process variations Npg [cm-3] Reference Data #1 Data #2 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교, 설명하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <39>

![CMOS Inverter Example 3 Xj SD Lg variation 1 Table 3에 주어진 공정변수 변화Xj CMOS Inverter Example #3. Xj, SD, Lg variation 1. [Table #3]에 주어진 공정변수 변화(Xj,](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-40.jpg)

CMOS Inverter Example #3. Xj, SD, Lg variation 1. [Table #3]에 주어진 공정변수 변화(Xj, SD, Lg)에 따라 아래의 소자변수를 비교하고 이유에 대해 논하시오. (Lg variation : short channel effect 관점) [Table #3] Process variations Xj, SD [nm] Reference Data #1 60 Data #2 180 Process variations Lg [nm] Reference Data #1 Data #2 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교하고 이유에 대해 논하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <40>

![CMOS Inverter Example 4 Nhalo Lg variation 1 Table 4에 주어진 공정변수 변화Nhalo Lg에 CMOS Inverter Example #4. Nhalo, Lg variation 1. [Table #4]에 주어진 공정변수 변화(Nhalo, Lg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-41.jpg)

CMOS Inverter Example #4. Nhalo, Lg variation 1. [Table #4]에 주어진 공정변수 변화(Nhalo, Lg)에 따라 아래의 소자변수를 비교하고 이유에 대해 논하시오. (Lg variation : short channel effect 관점) [Table #4] Process variations Nhalo [cm-3] Reference Data #1 0 (No halo) Data #2 Process variations Lg [nm] Reference Data #1 Data #2 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교하고 이유에 대해 논하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <41>

![CMOS Inverter Example 5 Tox Lg variation 1 Table 5에 주어진 공정변수 변화Tox Lg에 CMOS Inverter Example #5. Tox, Lg variation 1. [Table #5]에 주어진 공정변수 변화(Tox, Lg)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-42.jpg)

CMOS Inverter Example #5. Tox, Lg variation 1. [Table #5]에 주어진 공정변수 변화(Tox, Lg)에 따라 아래의 소자변수를 비교하고 이유에 대해 논하시오. (Lg variation : short channel effect 관점) [Table #5] Process variations Tox [nm] Reference Data #1 3 Data #2 Process variations 6 Lg [nm] Reference Data #1 Data #2 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교하고 이유에 대해 논하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <42>

![CMOS Inverter Example 6 Wn Wp variation 1 Table 6에 주어진 공정변수 변화Wn CMOS Inverter Example #6. Wn : Wp variation 1. [Table #6]에 주어진 공정변수 변화(Wn](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-43.jpg)

CMOS Inverter Example #6. Wn : Wp variation 1. [Table #6]에 주어진 공정변수 변화(Wn : Wp)에 따라 아래의 소자변수를 비교, 설명하시오. (1) Threshold voltage (VT) (2) Subthreshold slope (SS) (3) On current (Ion) (4) Off current (Ioff) (5) GIDL current(IGIDL) [Table #6] Process variations Wn : Wp Reference Data #1 1: 1 Data #2 1: 4 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교, 설명하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <43>

![CMOS Inverter Example 7 Cload variation Table 7 Process variations 1 Table 7에 주어진 CMOS Inverter Example #7. Cload variation [Table #7] Process variations 1. [Table #7]에 주어진](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-44.jpg)

CMOS Inverter Example #7. Cload variation [Table #7] Process variations 1. [Table #7]에 주어진 공정변수 변화(Cload)에 따라 아래의 소자변수를 비교, 설명하시오. Reference Data #1 0. 1 × CMOS Data #2 10 × CMOS (CMOS = 2. 1 f. F) (1) Threshold voltage (VT) (2) Subthreshold slope (SS) (3) On current (Ion) (4) Off current (Ioff) (5) GIDL current(IGIDL) Cload 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교, 설명하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <44>

![CMOS Inverter Example 8 εox variation Table 8 1 Table 8에 주어진 공정변수 변화εox에 CMOS Inverter Example #8. εox variation [Table #8] 1. [Table #8]에 주어진 공정변수 변화(εox)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-45.jpg)

CMOS Inverter Example #8. εox variation [Table #8] 1. [Table #8]에 주어진 공정변수 변화(εox)에 따라 아래의 소자변수를 비교, 설명하시오. (1) Threshold voltage (VT) (2) Subthreshold slope (SS) (3) On current (Ion) (4) Off current (Ioff) (5) GIDL current(IGIDL) Process variations Oxide material (εox) Reference Si. O 2 (3. 9) Data #1 Hf. O 2 (22) Data #2 Si 3 N 4 (7. 5) 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교, 설명하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <45>

![CMOS Inverter Example 9 qφm variation Table 9 1 Table 9에 주어진 공정변수 변화qφm에 CMOS Inverter Example #9. qφm variation [Table #9] 1. [Table #9]에 주어진 공정변수 변화(qφm)에](https://slidetodoc.com/presentation_image_h/740308fb2abdd919a88ac9498cff6253/image-46.jpg)

CMOS Inverter Example #9. qφm variation [Table #9] 1. [Table #9]에 주어진 공정변수 변화(qφm)에 따라 아래의 소자변수를 비교, 설명하시오. Process variations Reference Data (1) Threshold voltage (VT) (2) Subthreshold slope (SS) (3) On current (Ion) (4) Off current (Ioff) (5) GIDL current(IGIDL) qφm n. MOS : Polysilicon (4. 05) p. MOS : Polysilicon (5. 16) n. MOS : Molybdenum (4. 53) p. MOS : Copper (4. 7) 2. 소자변수 변화의 관점에서 아래의 회로 성능지수를 비교, 설명하시오. (1) Noise margin (NM) - VIL, VIH, NML, NMH (2) Propagation delay - tp. HL, tp. LH, tp, tf, tr (3) Power consumption - Pdynamic, Pstatic <46>