CMOS VLSI Design Digital Design CMOS VLSI 1

- Slides: 71

CMOS VLSI Design Digital Design CMOS VLSI 1

Overview q q q Physical principles Combinational logic Sequential logic Datapath Memories Trends Digital Design CMOS VLSI 2

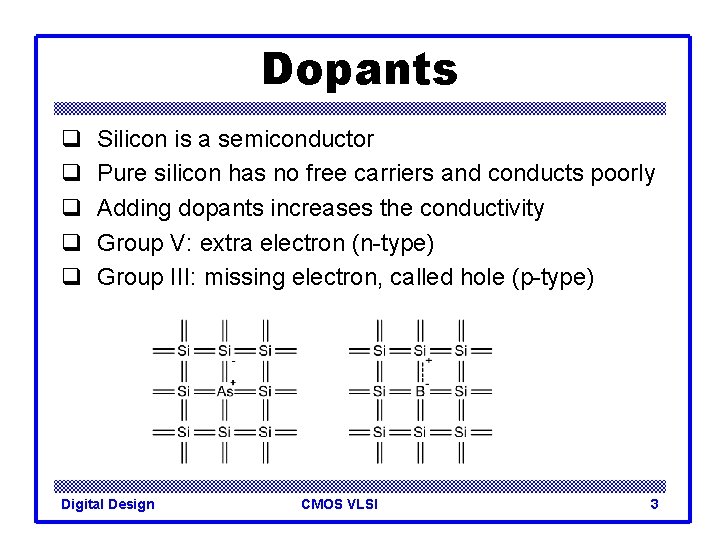

Dopants q q q Silicon is a semiconductor Pure silicon has no free carriers and conducts poorly Adding dopants increases the conductivity Group V: extra electron (n-type) Group III: missing electron, called hole (p-type) Digital Design CMOS VLSI 3

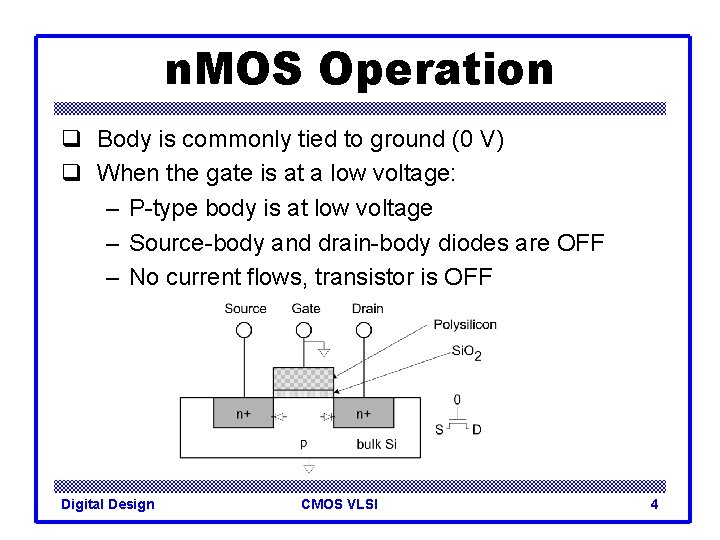

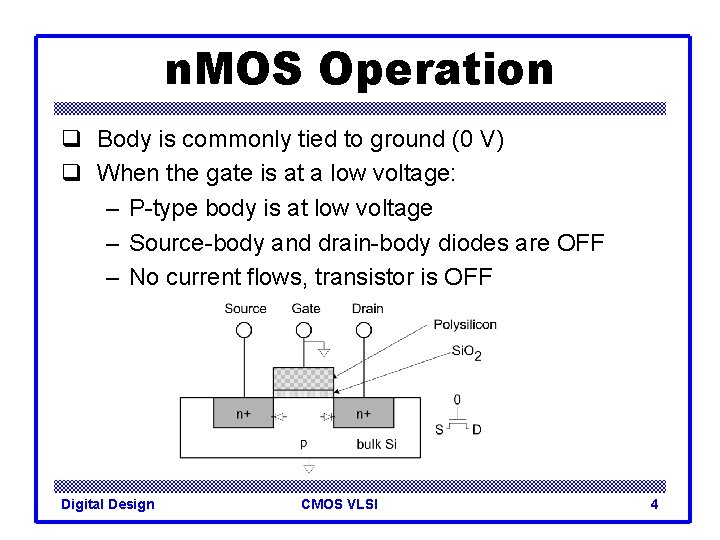

n. MOS Operation q Body is commonly tied to ground (0 V) q When the gate is at a low voltage: – P-type body is at low voltage – Source-body and drain-body diodes are OFF – No current flows, transistor is OFF Digital Design CMOS VLSI 4

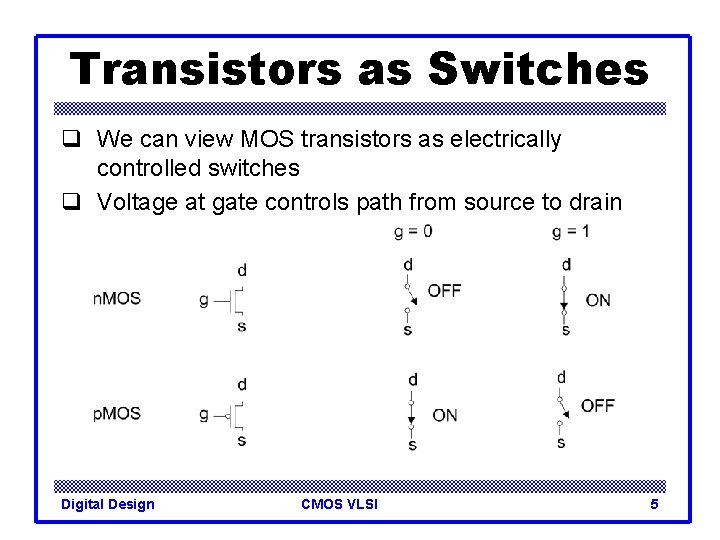

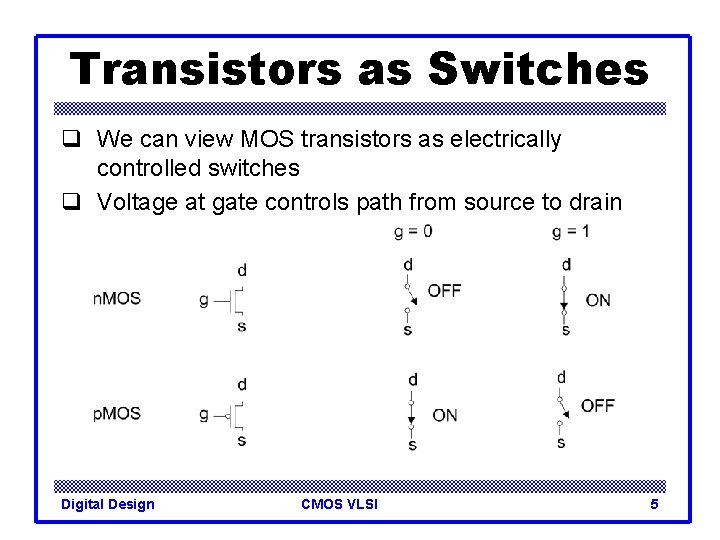

Transistors as Switches q We can view MOS transistors as electrically controlled switches q Voltage at gate controls path from source to drain Digital Design CMOS VLSI 5

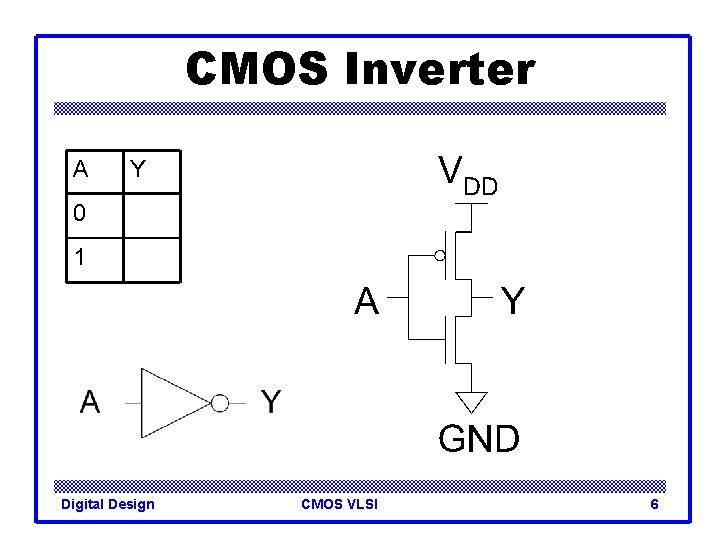

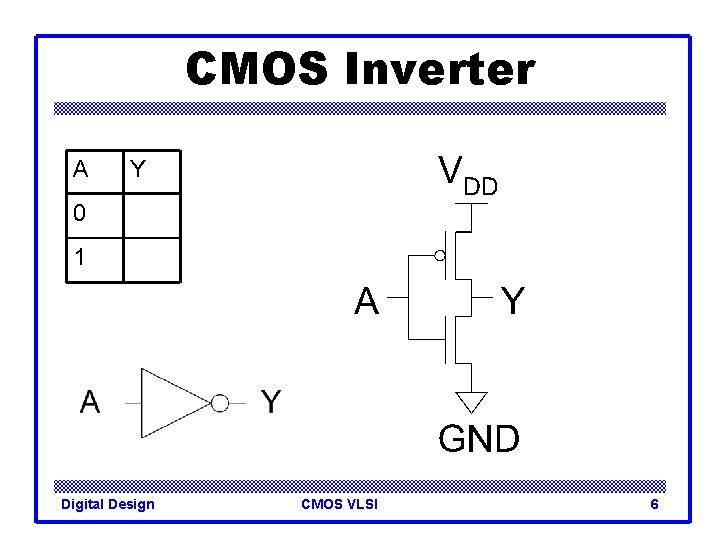

CMOS Inverter A Y 0 1 Digital Design CMOS VLSI 6

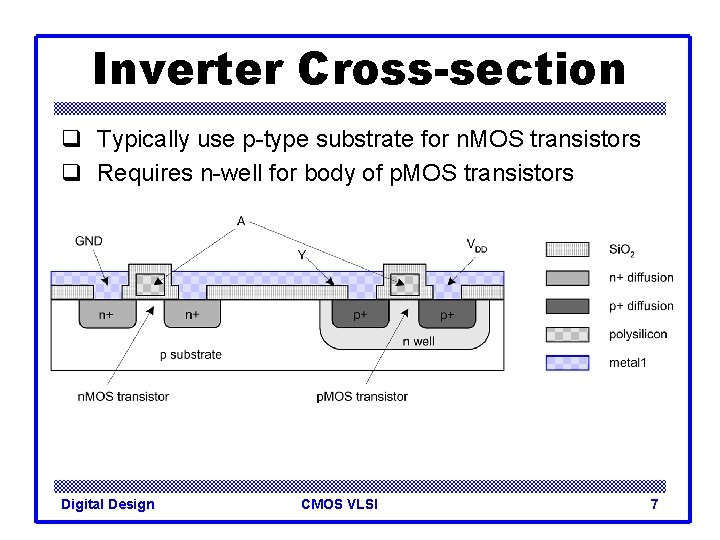

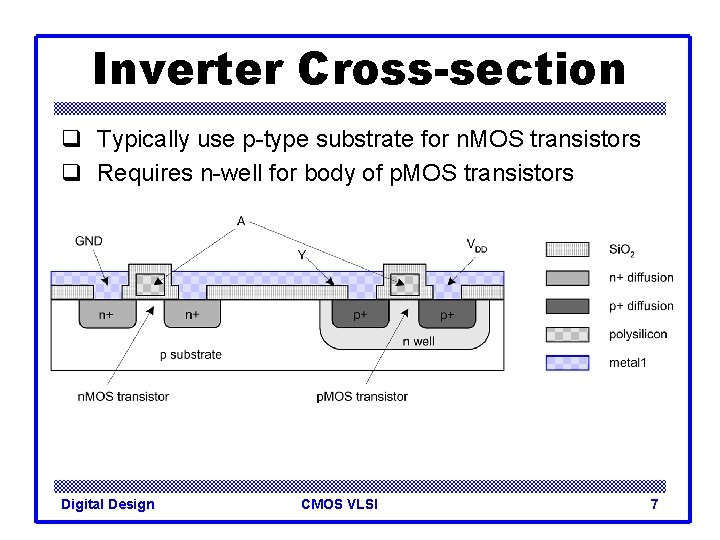

Inverter Cross-section q Typically use p-type substrate for n. MOS transistors q Requires n-well for body of p. MOS transistors Digital Design CMOS VLSI 7

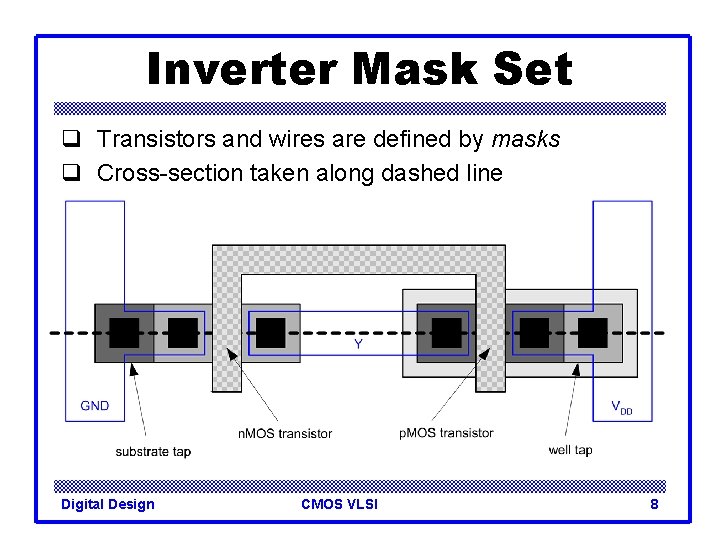

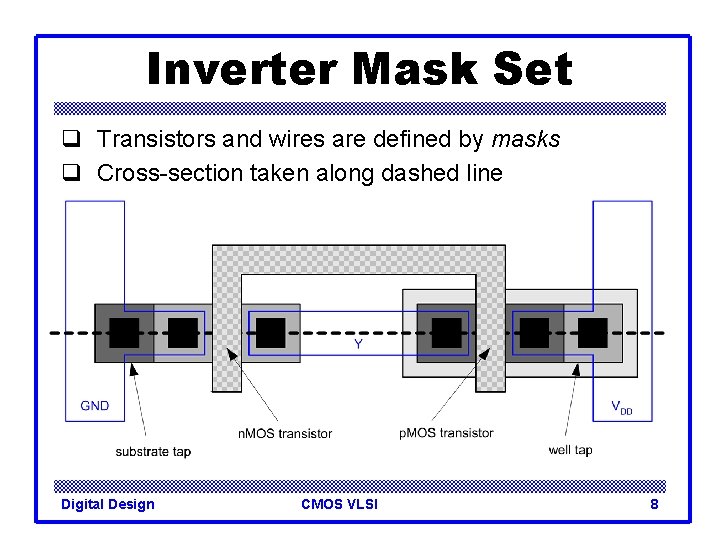

Inverter Mask Set q Transistors and wires are defined by masks q Cross-section taken along dashed line Digital Design CMOS VLSI 8

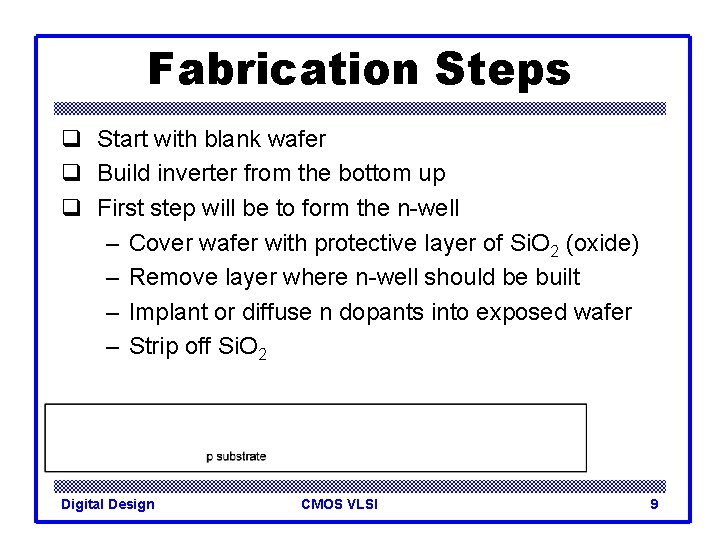

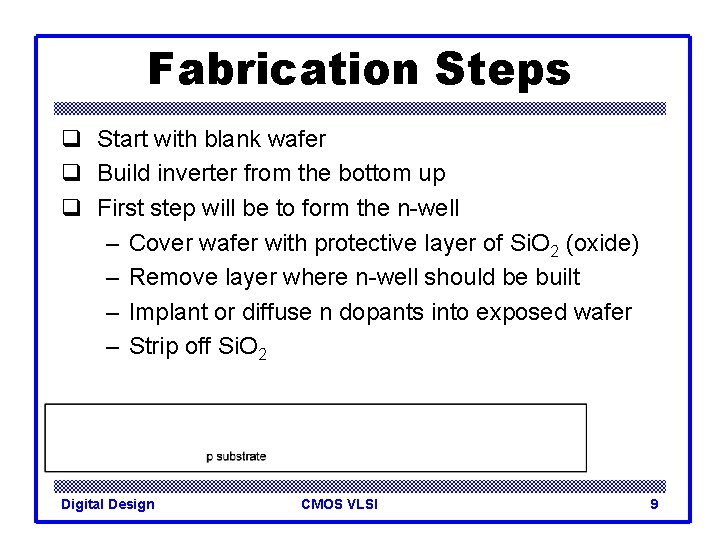

Fabrication Steps q Start with blank wafer q Build inverter from the bottom up q First step will be to form the n-well – Cover wafer with protective layer of Si. O 2 (oxide) – Remove layer where n-well should be built – Implant or diffuse n dopants into exposed wafer – Strip off Si. O 2 Digital Design CMOS VLSI 9

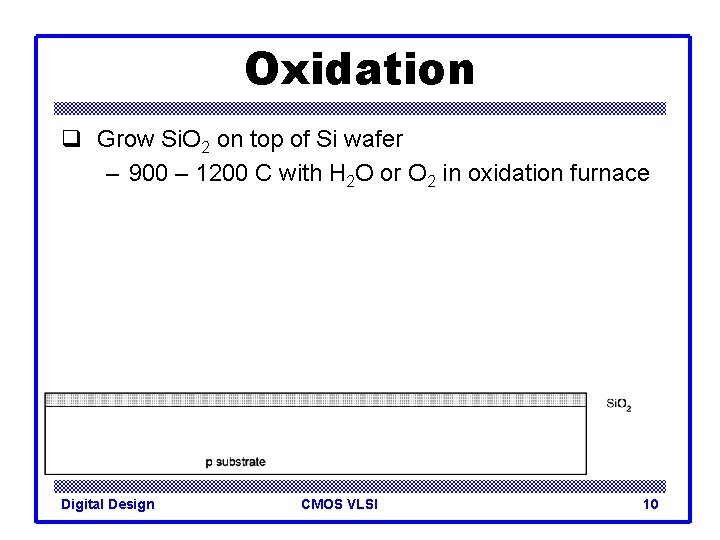

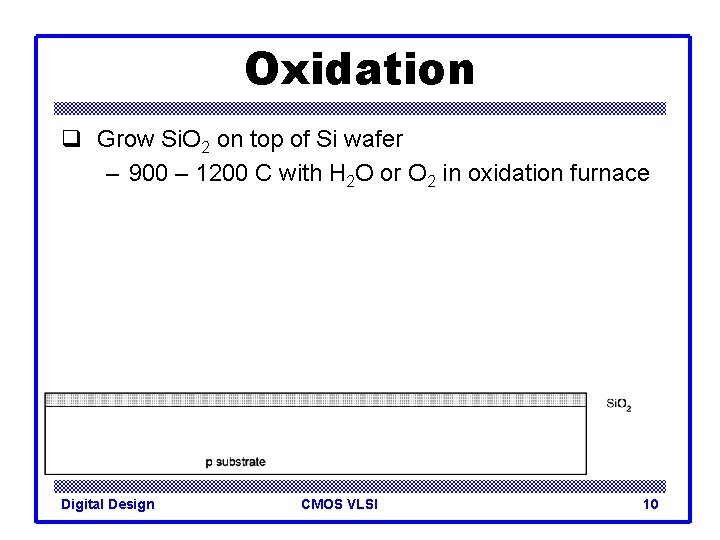

Oxidation q Grow Si. O 2 on top of Si wafer – 900 – 1200 C with H 2 O or O 2 in oxidation furnace Digital Design CMOS VLSI 10

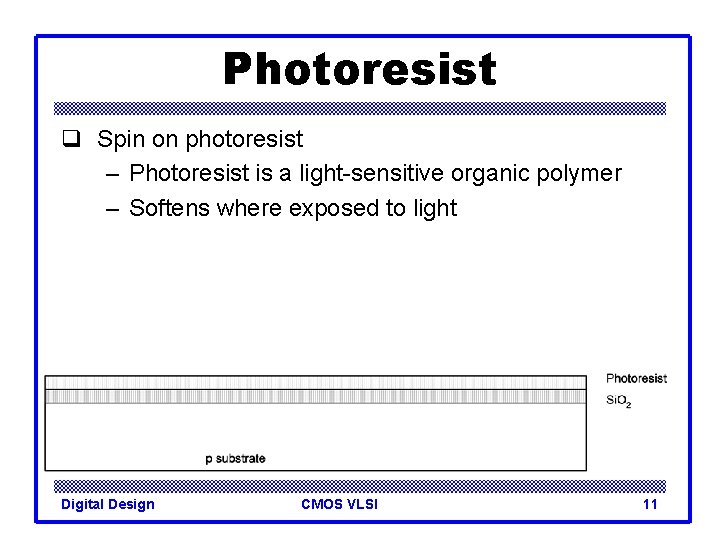

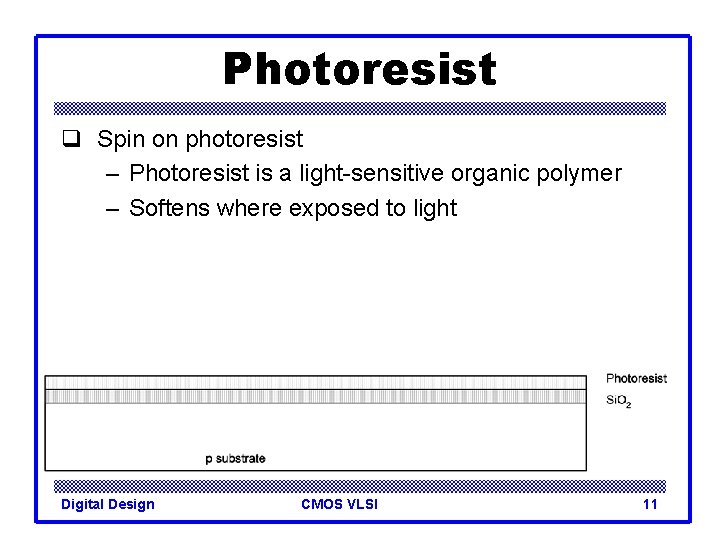

Photoresist q Spin on photoresist – Photoresist is a light-sensitive organic polymer – Softens where exposed to light Digital Design CMOS VLSI 11

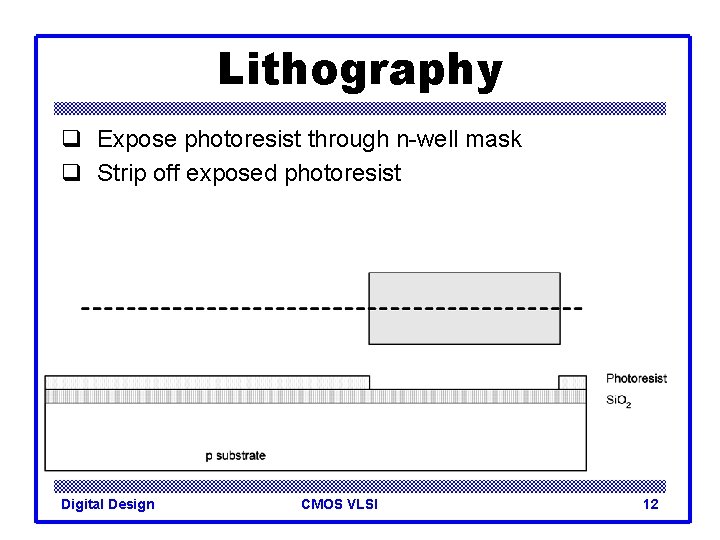

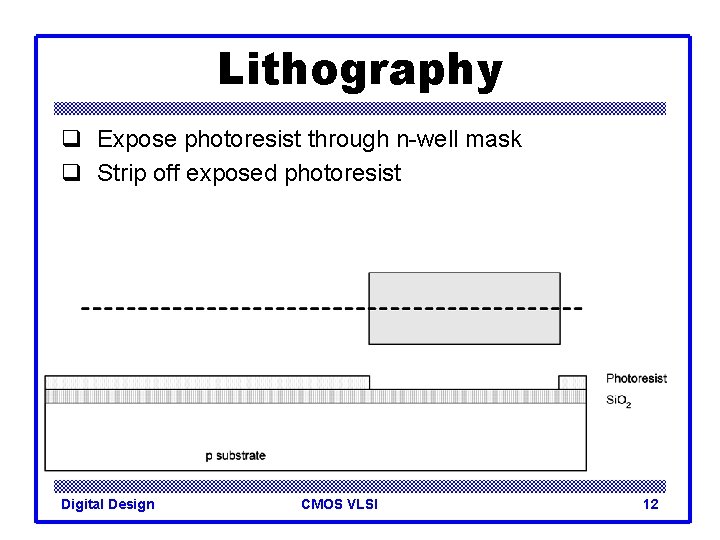

Lithography q Expose photoresist through n-well mask q Strip off exposed photoresist Digital Design CMOS VLSI 12

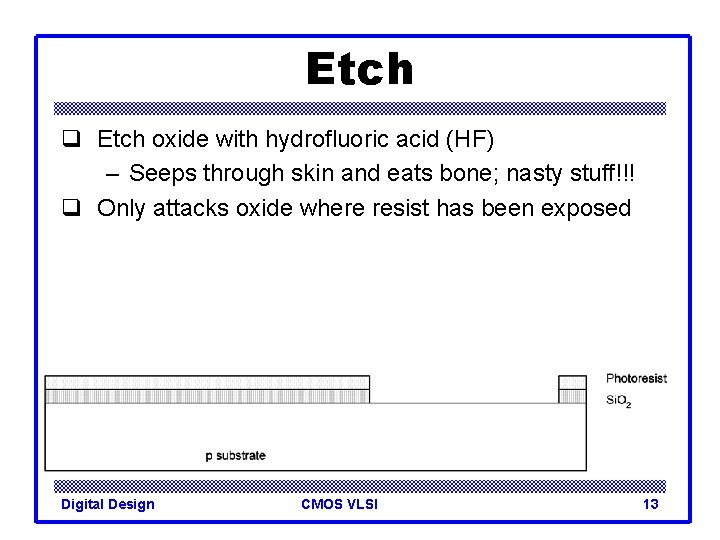

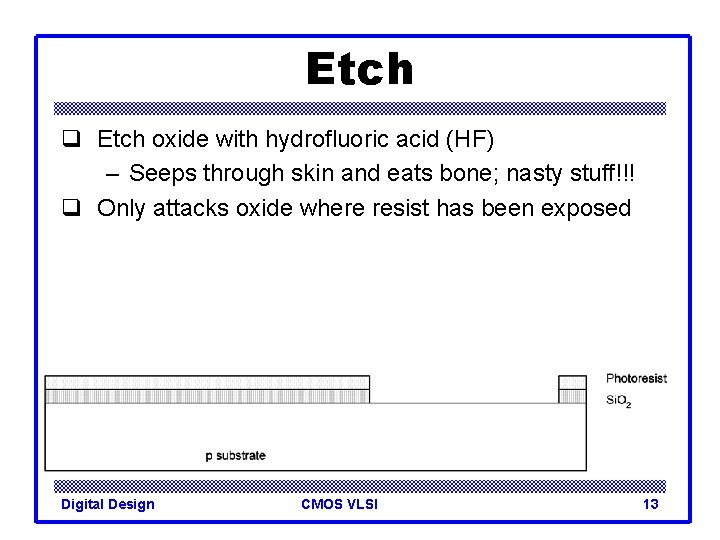

Etch q Etch oxide with hydrofluoric acid (HF) – Seeps through skin and eats bone; nasty stuff!!! q Only attacks oxide where resist has been exposed Digital Design CMOS VLSI 13

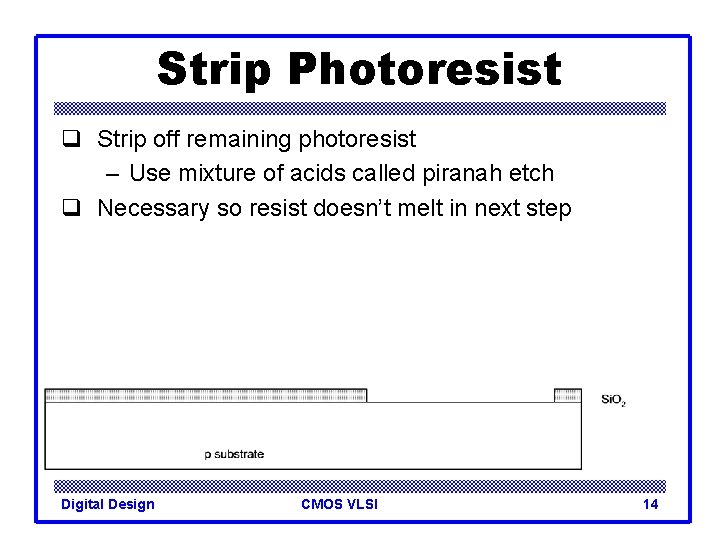

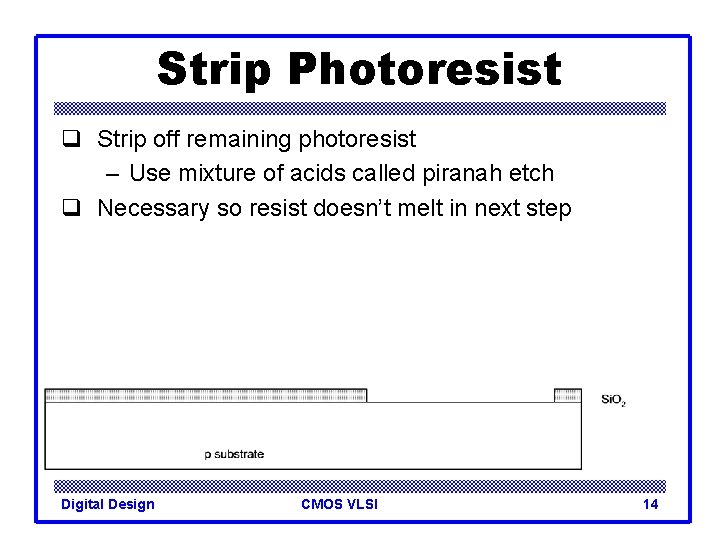

Strip Photoresist q Strip off remaining photoresist – Use mixture of acids called piranah etch q Necessary so resist doesn’t melt in next step Digital Design CMOS VLSI 14

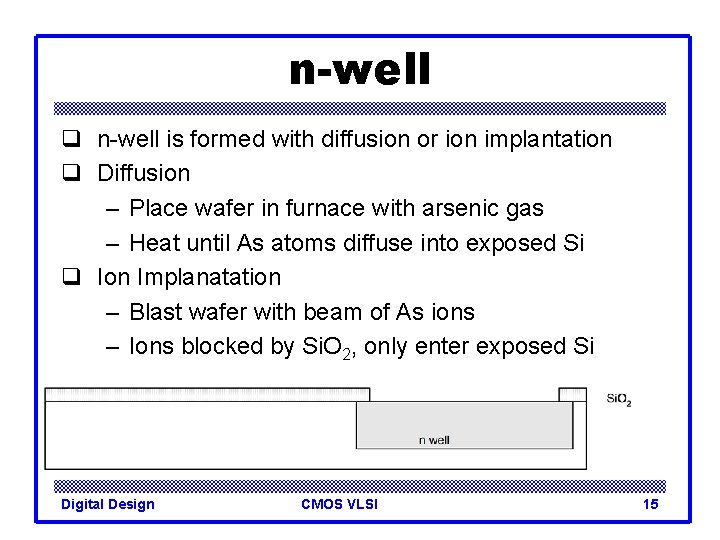

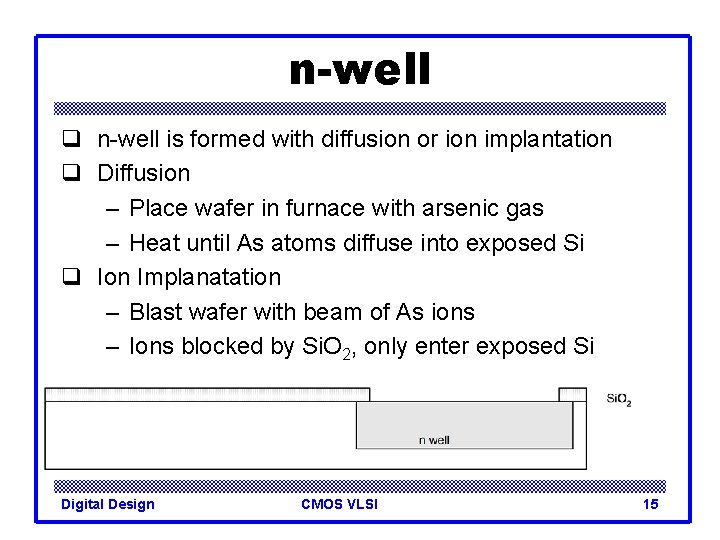

n-well q n-well is formed with diffusion or ion implantation q Diffusion – Place wafer in furnace with arsenic gas – Heat until As atoms diffuse into exposed Si q Ion Implanatation – Blast wafer with beam of As ions – Ions blocked by Si. O 2, only enter exposed Si Digital Design CMOS VLSI 15

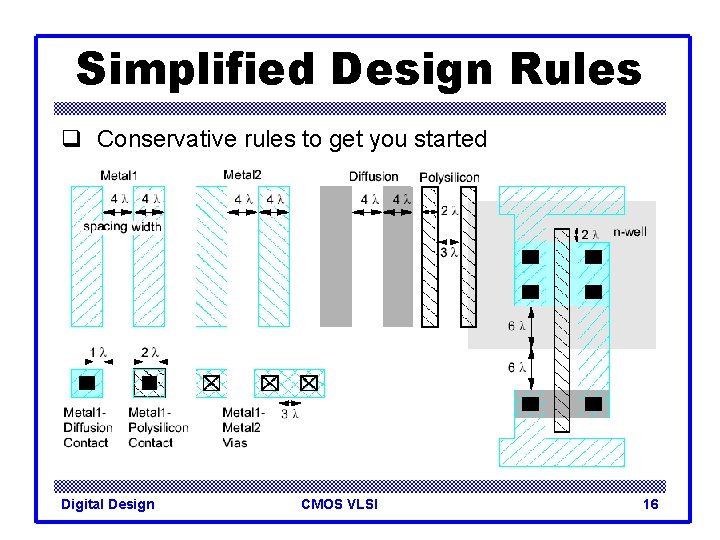

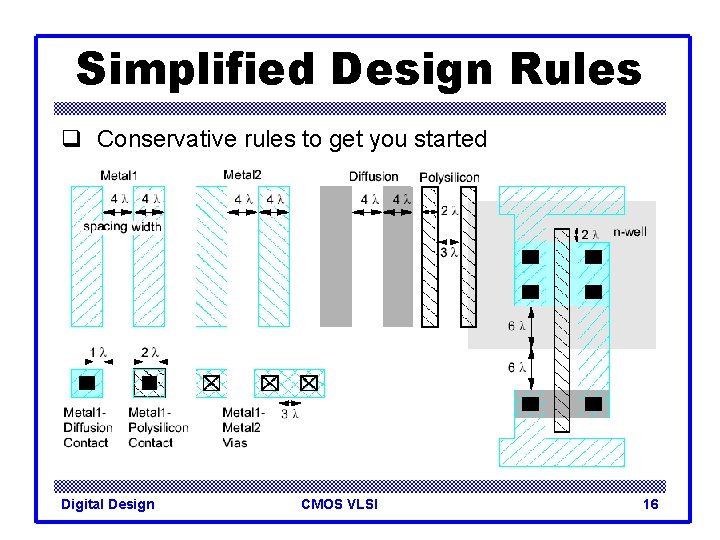

Simplified Design Rules q Conservative rules to get you started Digital Design CMOS VLSI 16

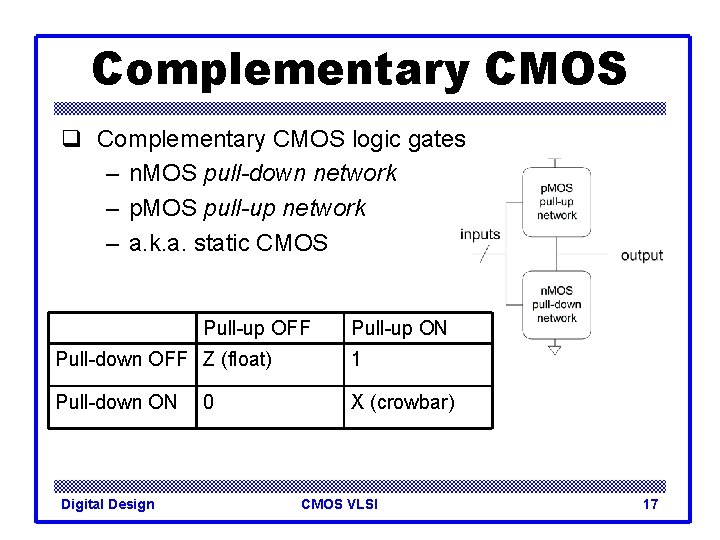

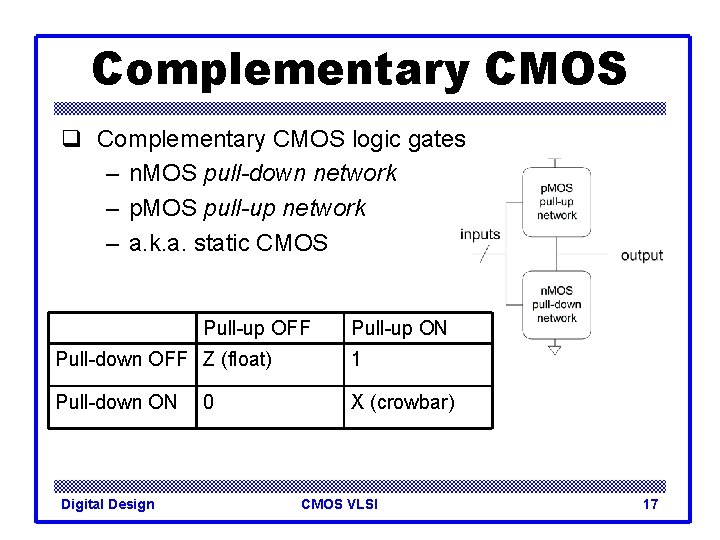

Complementary CMOS q Complementary CMOS logic gates – n. MOS pull-down network – p. MOS pull-up network – a. k. a. static CMOS Pull-up OFF Pull-up ON Pull-down OFF Z (float) 1 Pull-down ON X (crowbar) Digital Design 0 CMOS VLSI 17

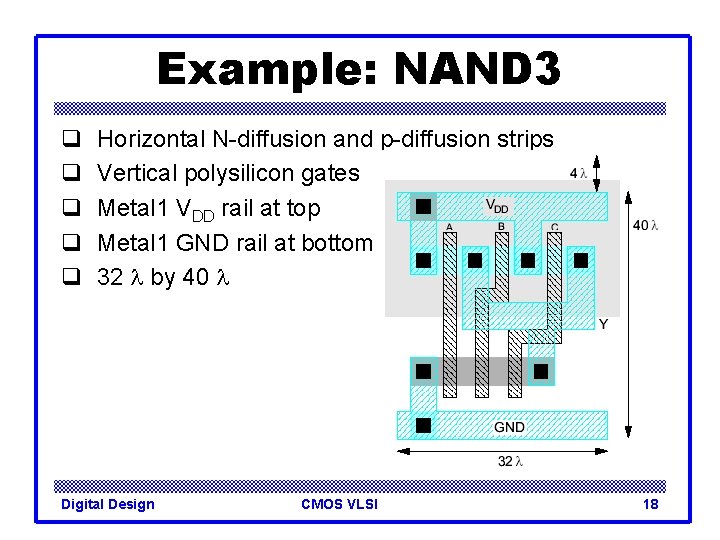

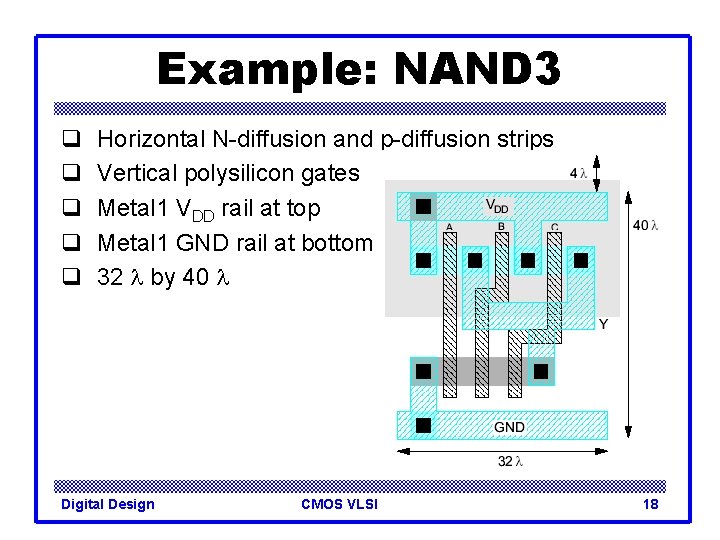

Example: NAND 3 q q q Horizontal N-diffusion and p-diffusion strips Vertical polysilicon gates Metal 1 VDD rail at top Metal 1 GND rail at bottom 32 l by 40 l Digital Design CMOS VLSI 18

I-V Characteristics q In Linear region, Ids depends on – How much charge is in the channel? – How fast is the charge moving? Digital Design CMOS VLSI 19

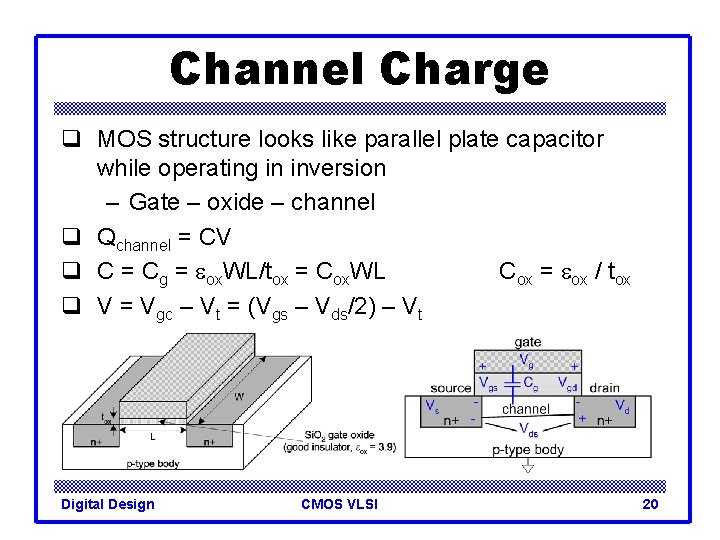

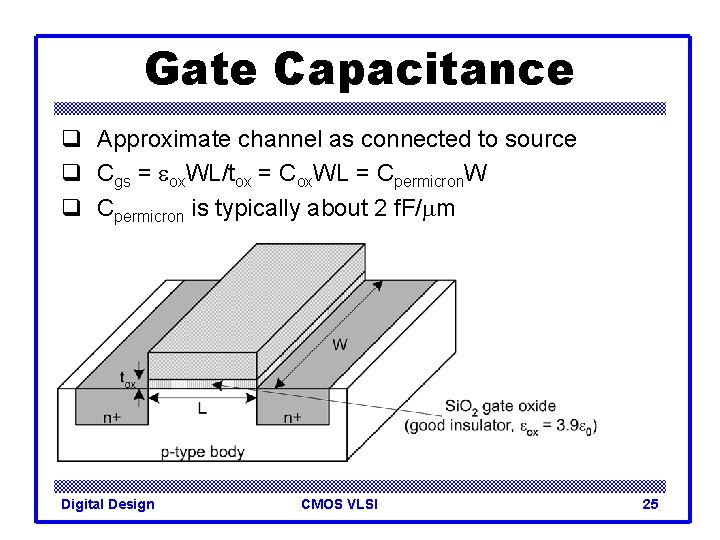

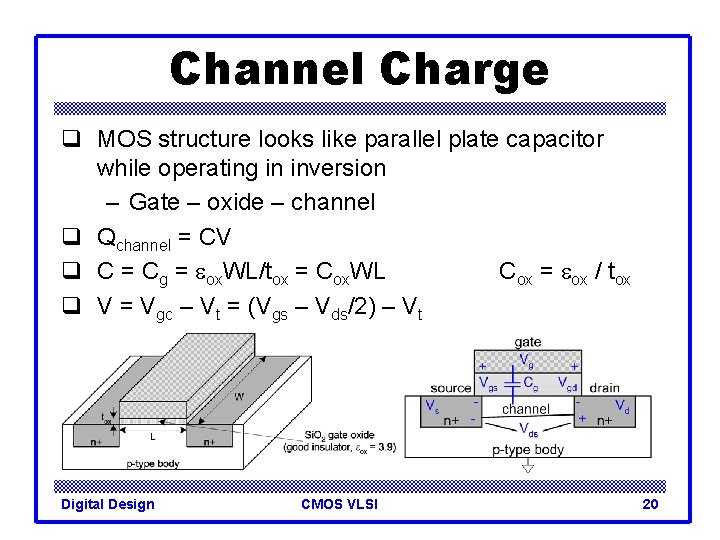

Channel Charge q MOS structure looks like parallel plate capacitor while operating in inversion – Gate – oxide – channel q Qchannel = CV Cox = eox / tox q C = Cg = eox. WL/tox = Cox. WL q V = Vgc – Vt = (Vgs – Vds/2) – Vt Digital Design CMOS VLSI 20

Carrier velocity q Charge is carried by eq Carrier velocity v proportional to lateral E-field between source and drain q v = m. E m called mobility q E = Vds/L q Time for carrier to cross channel: – t=L/v Digital Design CMOS VLSI 21

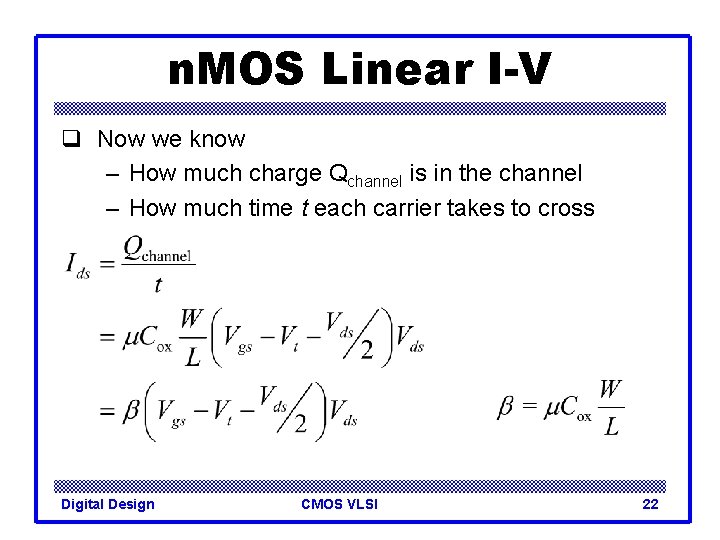

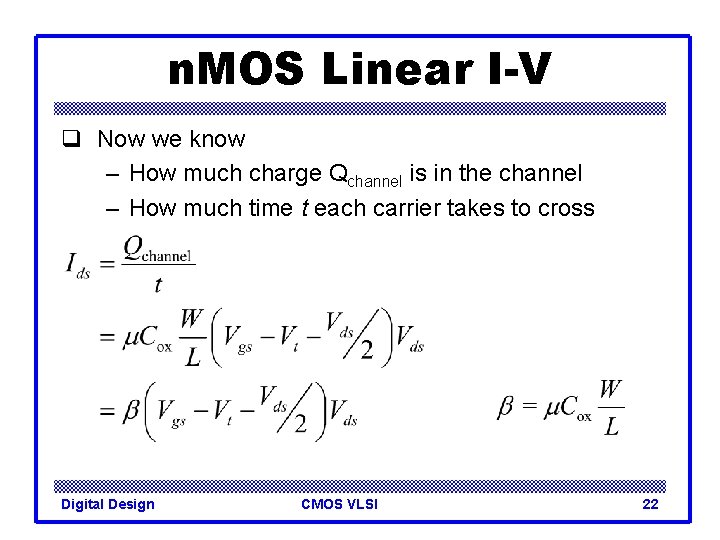

n. MOS Linear I-V q Now we know – How much charge Qchannel is in the channel – How much time t each carrier takes to cross Digital Design CMOS VLSI 22

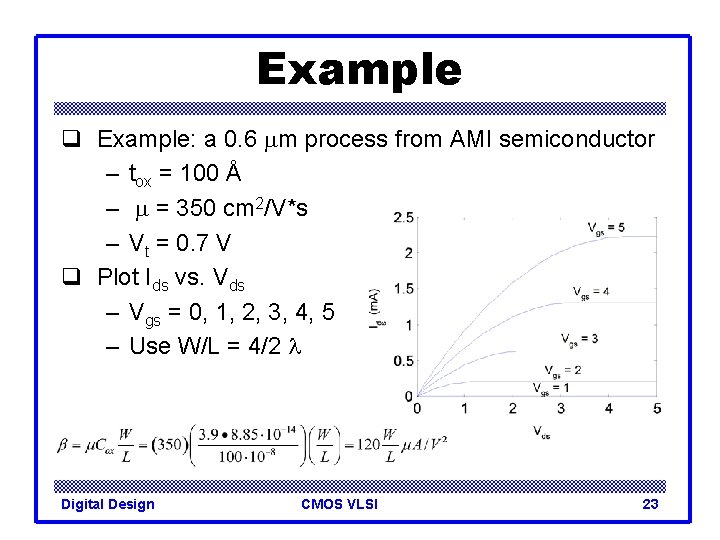

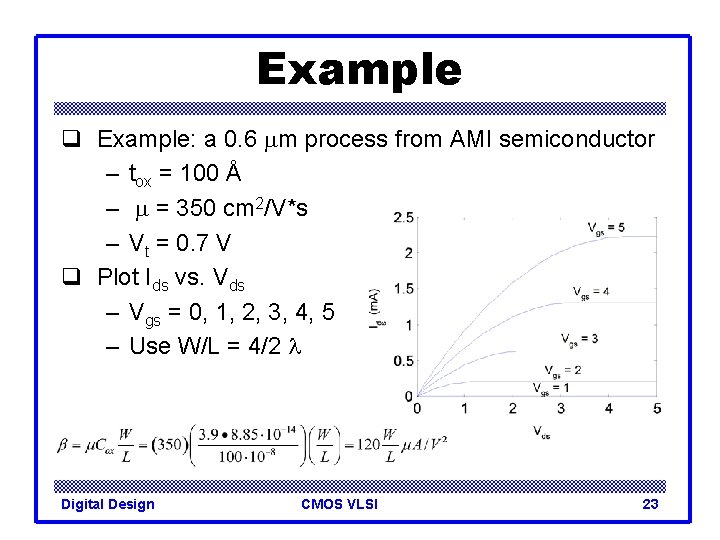

Example q Example: a 0. 6 mm process from AMI semiconductor – tox = 100 Å – m = 350 cm 2/V*s – Vt = 0. 7 V q Plot Ids vs. Vds – Vgs = 0, 1, 2, 3, 4, 5 – Use W/L = 4/2 l Digital Design CMOS VLSI 23

Capacitance q Any two conductors separated by an insulator have capacitance q Gate to channel capacitor is very important – Creates channel charge necessary for operation q Source and drain have capacitance to body – Across reverse-biased diodes – Called diffusion capacitance because it is associated with source/drain diffusion Digital Design CMOS VLSI 24

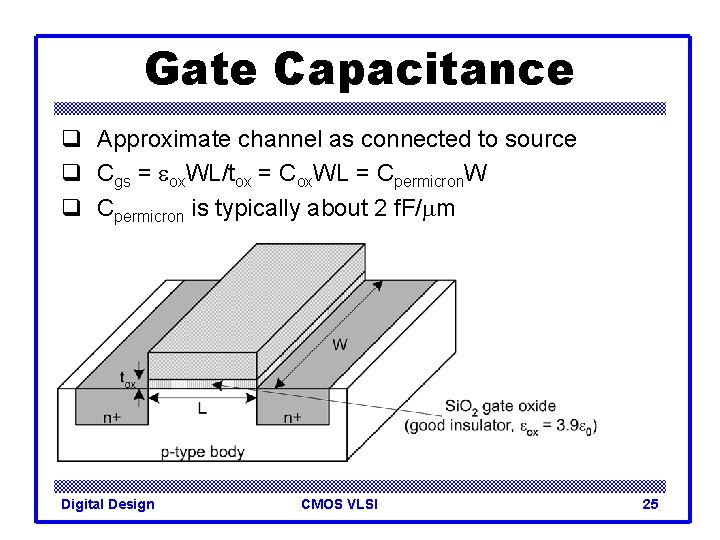

Gate Capacitance q Approximate channel as connected to source q Cgs = eox. WL/tox = Cox. WL = Cpermicron. W q Cpermicron is typically about 2 f. F/mm Digital Design CMOS VLSI 25

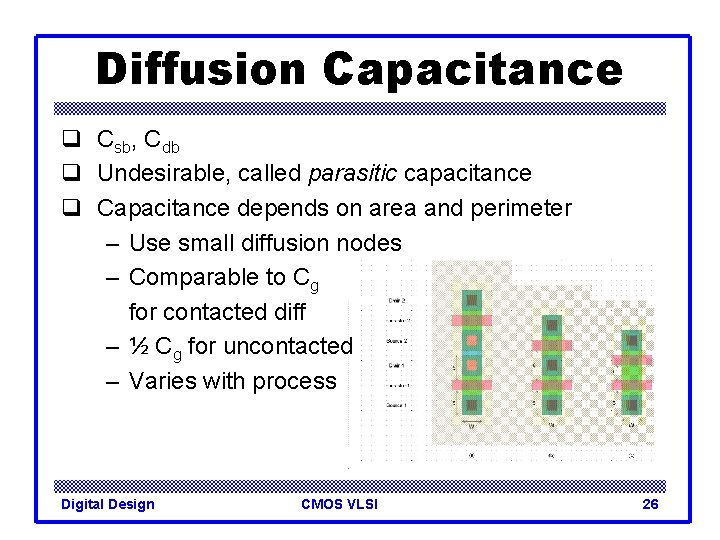

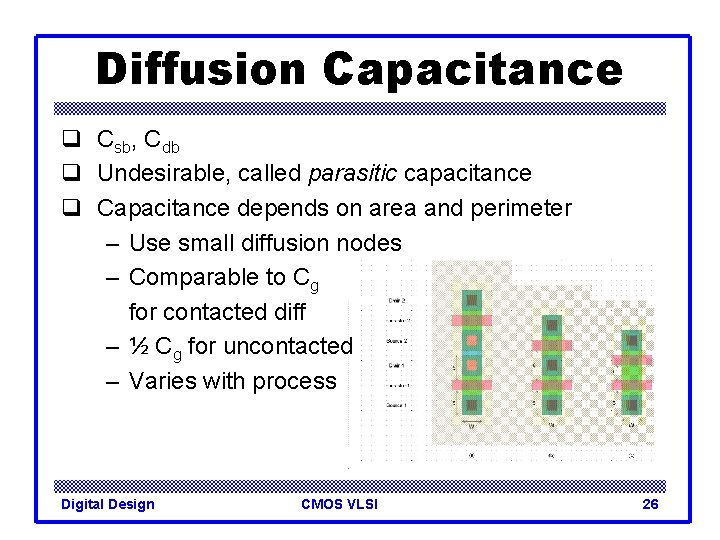

Diffusion Capacitance q Csb, Cdb q Undesirable, called parasitic capacitance q Capacitance depends on area and perimeter – Use small diffusion nodes – Comparable to Cg for contacted diff – ½ Cg for uncontacted – Varies with process Digital Design CMOS VLSI 26

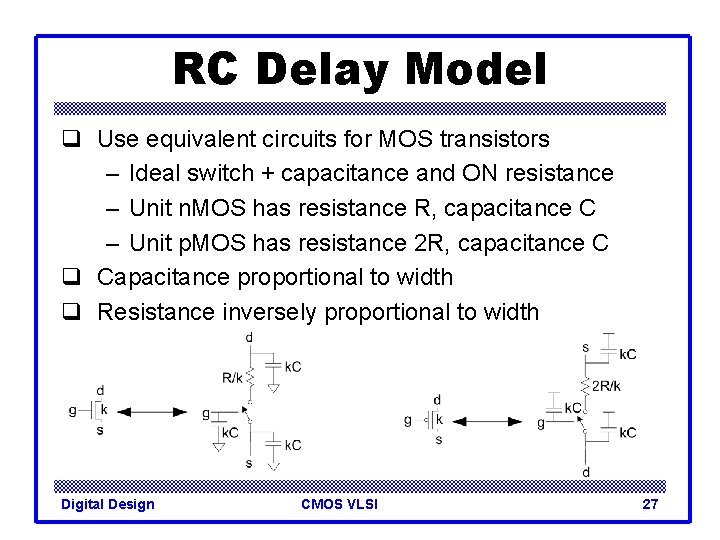

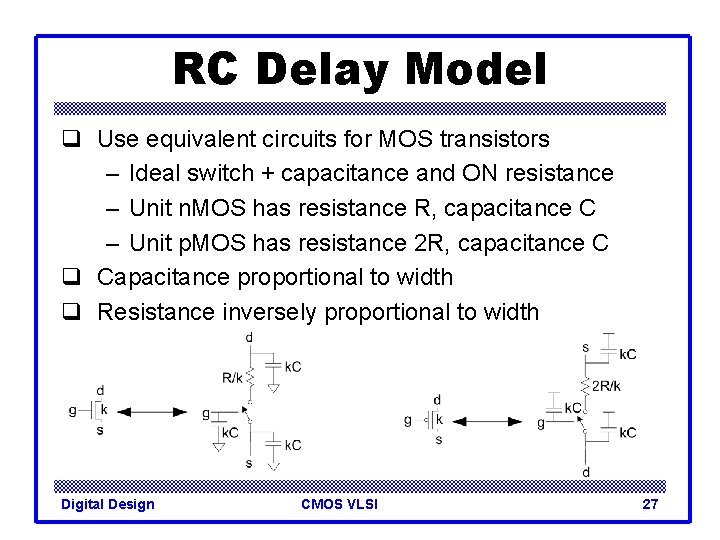

RC Delay Model q Use equivalent circuits for MOS transistors – Ideal switch + capacitance and ON resistance – Unit n. MOS has resistance R, capacitance C – Unit p. MOS has resistance 2 R, capacitance C q Capacitance proportional to width q Resistance inversely proportional to width Digital Design CMOS VLSI 27

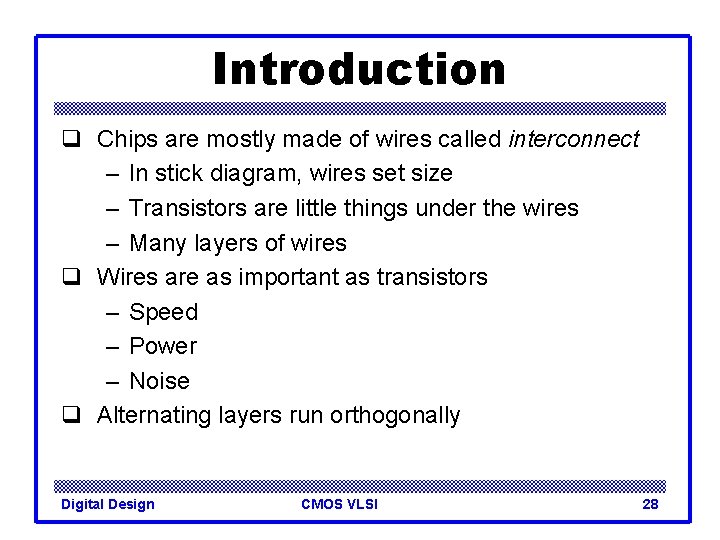

Introduction q Chips are mostly made of wires called interconnect – In stick diagram, wires set size – Transistors are little things under the wires – Many layers of wires q Wires are as important as transistors – Speed – Power – Noise q Alternating layers run orthogonally Digital Design CMOS VLSI 28

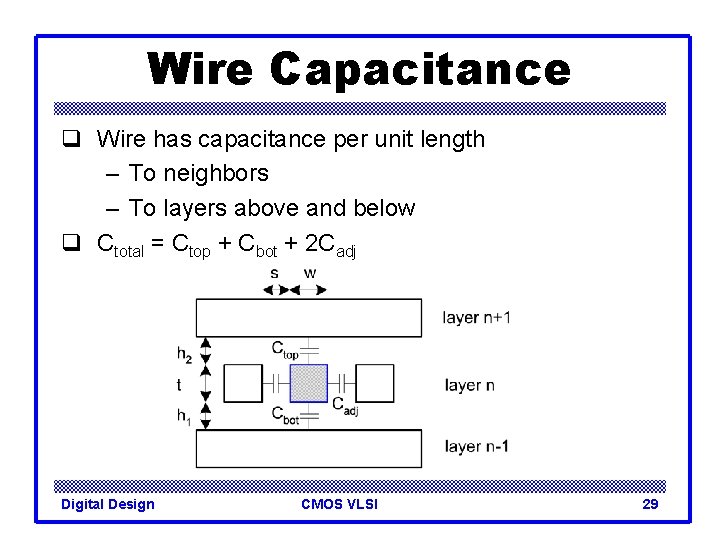

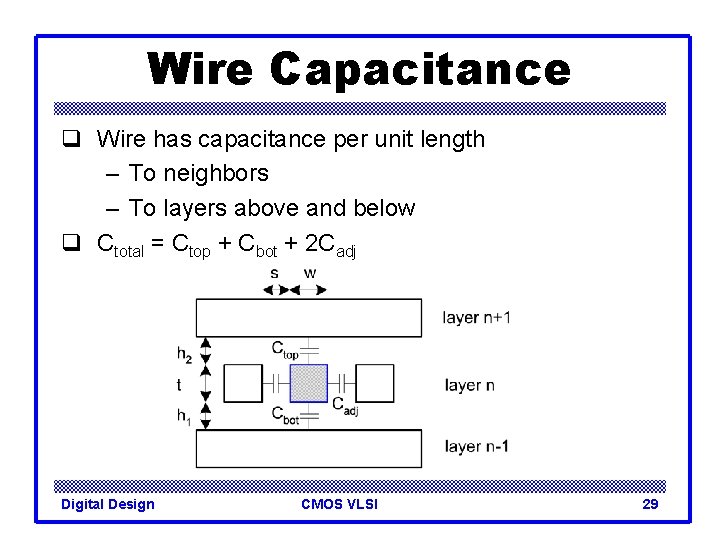

Wire Capacitance q Wire has capacitance per unit length – To neighbors – To layers above and below q Ctotal = Ctop + Cbot + 2 Cadj Digital Design CMOS VLSI 29

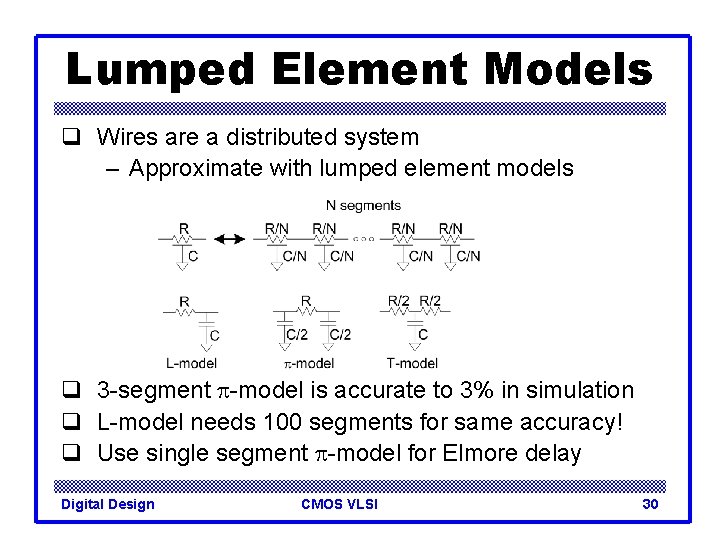

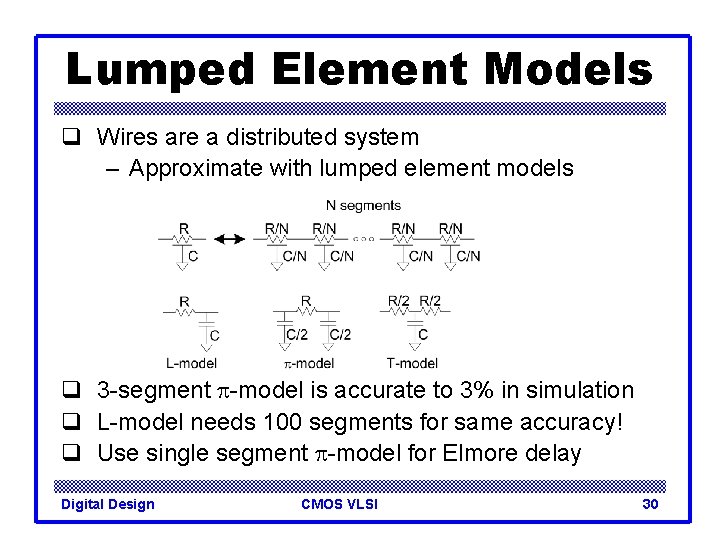

Lumped Element Models q Wires are a distributed system – Approximate with lumped element models q 3 -segment p-model is accurate to 3% in simulation q L-model needs 100 segments for same accuracy! q Use single segment p-model for Elmore delay Digital Design CMOS VLSI 30

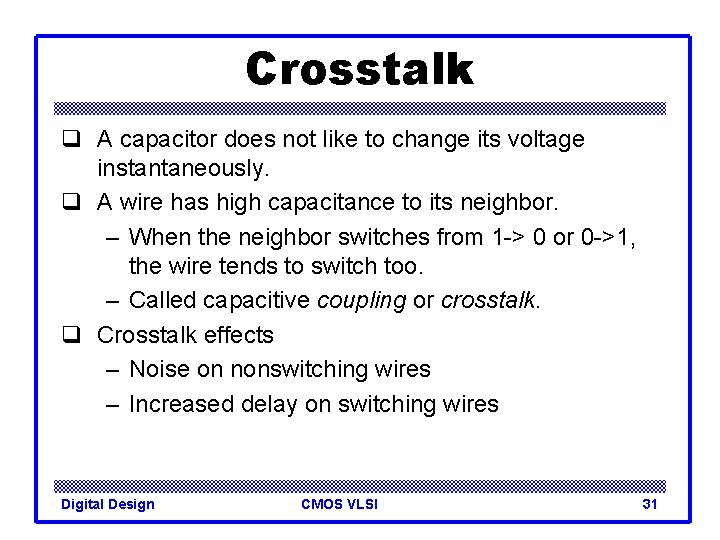

Crosstalk q A capacitor does not like to change its voltage instantaneously. q A wire has high capacitance to its neighbor. – When the neighbor switches from 1 -> 0 or 0 ->1, the wire tends to switch too. – Called capacitive coupling or crosstalk. q Crosstalk effects – Noise on nonswitching wires – Increased delay on switching wires Digital Design CMOS VLSI 31

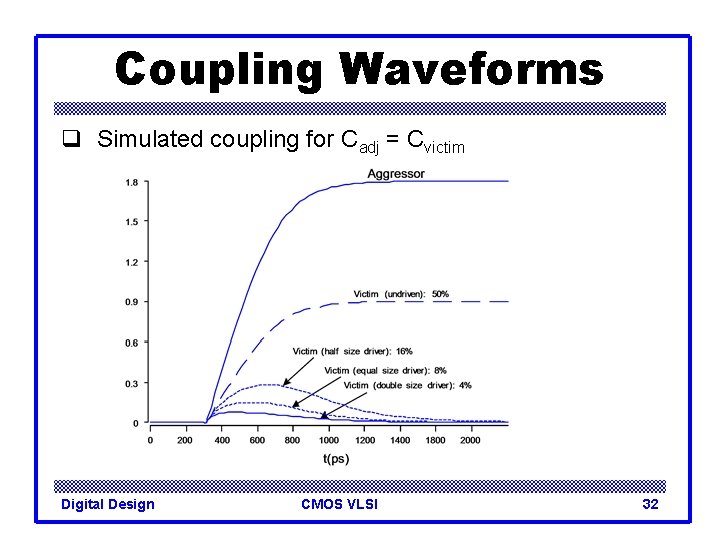

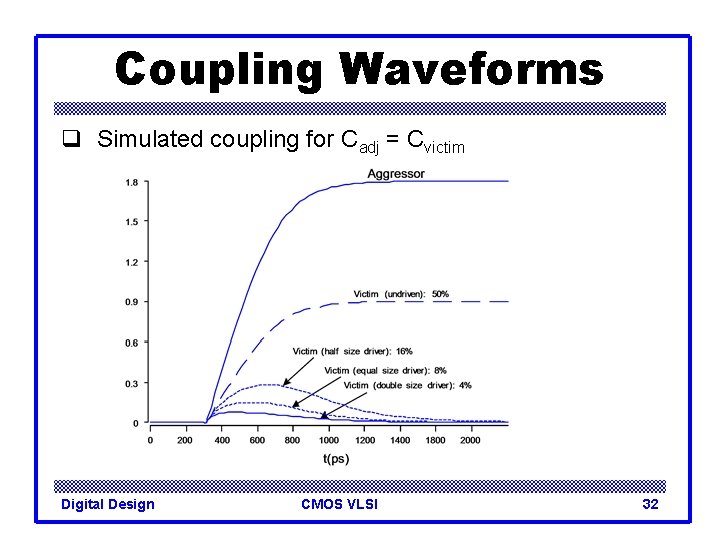

Coupling Waveforms q Simulated coupling for Cadj = Cvictim Digital Design CMOS VLSI 32

Introduction q What makes a circuit fast? – I = C d. V/dt -> tpd (C/I) DV – low capacitance – high current – small swing q Logical effort is proportional to C/I q p. MOS are the enemy! – High capacitance for a given current q Can we take the p. MOS capacitance off the input? q Various circuit families try to do this… Digital Design CMOS VLSI 33

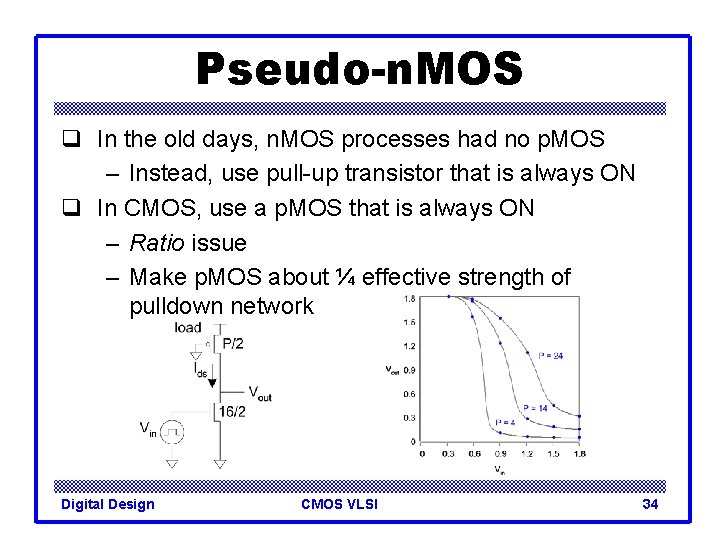

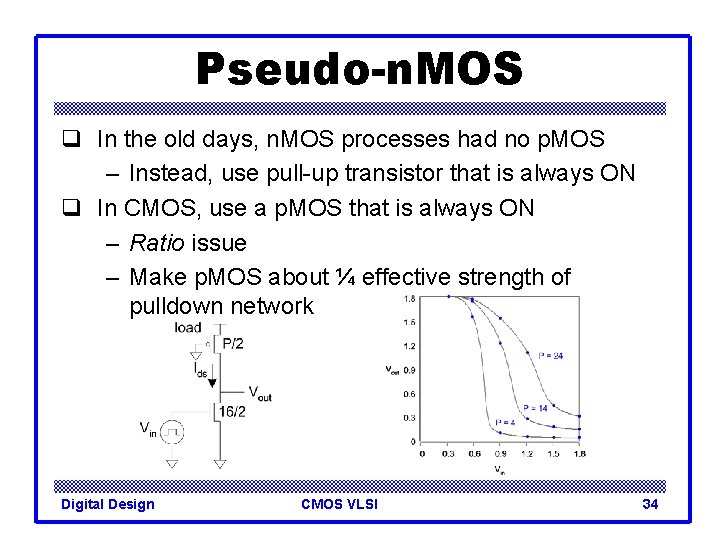

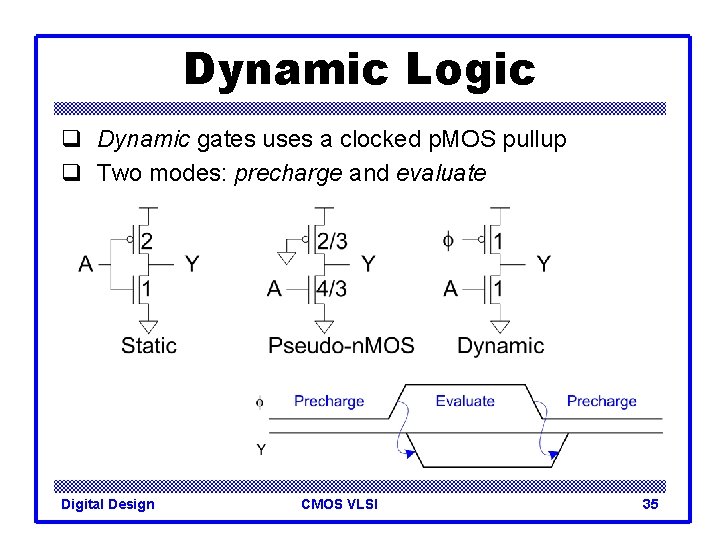

Pseudo-n. MOS q In the old days, n. MOS processes had no p. MOS – Instead, use pull-up transistor that is always ON q In CMOS, use a p. MOS that is always ON – Ratio issue – Make p. MOS about ¼ effective strength of pulldown network Digital Design CMOS VLSI 34

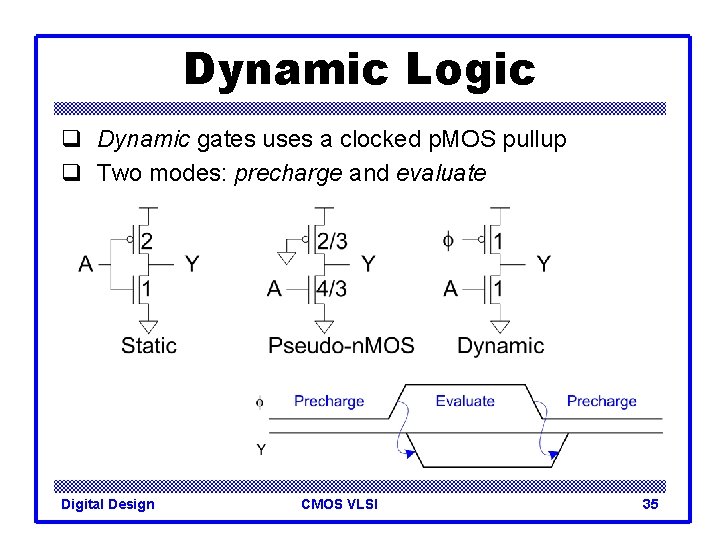

Dynamic Logic q Dynamic gates uses a clocked p. MOS pullup q Two modes: precharge and evaluate Digital Design CMOS VLSI 35

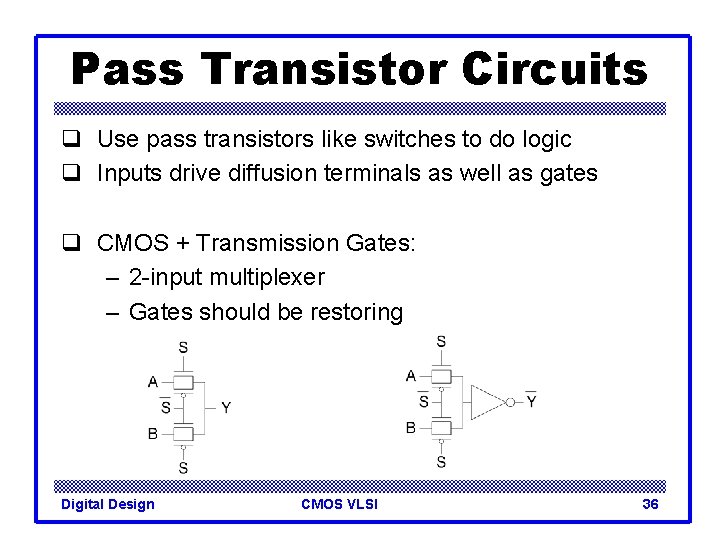

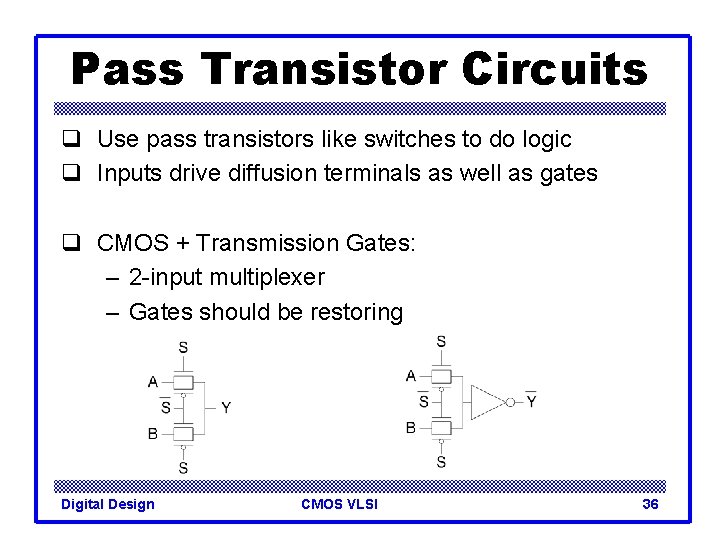

Pass Transistor Circuits q Use pass transistors like switches to do logic q Inputs drive diffusion terminals as well as gates q CMOS + Transmission Gates: – 2 -input multiplexer – Gates should be restoring Digital Design CMOS VLSI 36

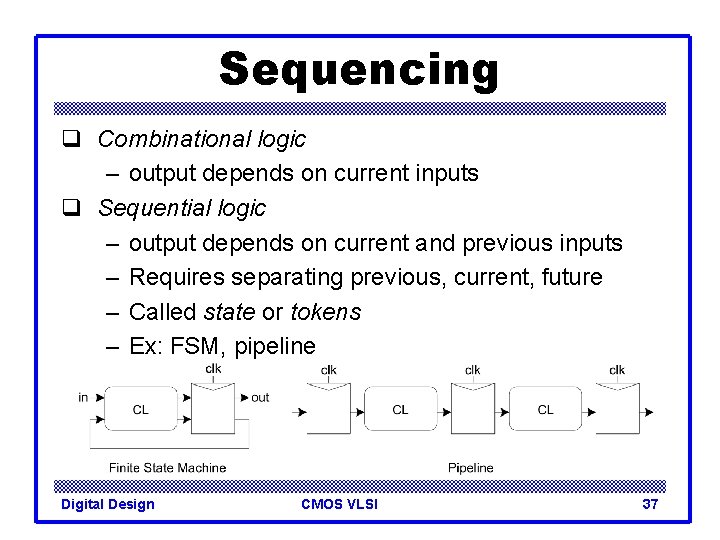

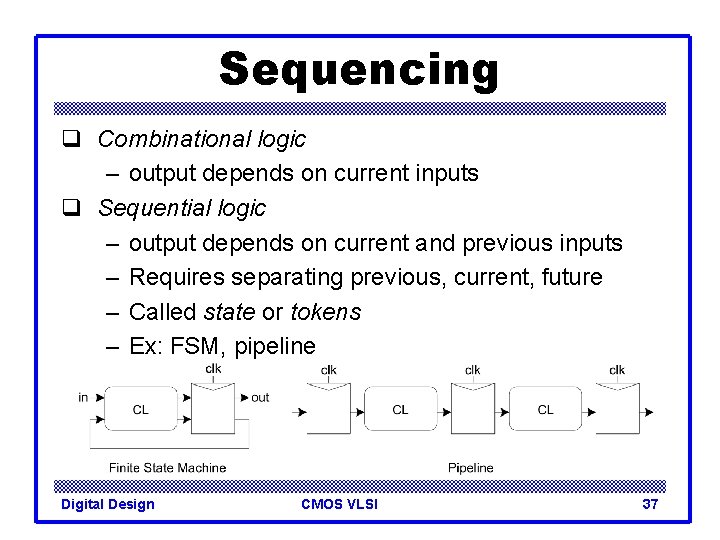

Sequencing q Combinational logic – output depends on current inputs q Sequential logic – output depends on current and previous inputs – Requires separating previous, current, future – Called state or tokens – Ex: FSM, pipeline Digital Design CMOS VLSI 37

Sequencing Overhead q Use flip-flops to delay fast tokens so they move through exactly one stage each cycle. q Inevitably adds some delay to the slow tokens q Makes circuit slower than just the logic delay – Called sequencing overhead q Some people call this clocking overhead – But it applies to asynchronous circuits too – Inevitable side effect of maintaining sequence Digital Design CMOS VLSI 38

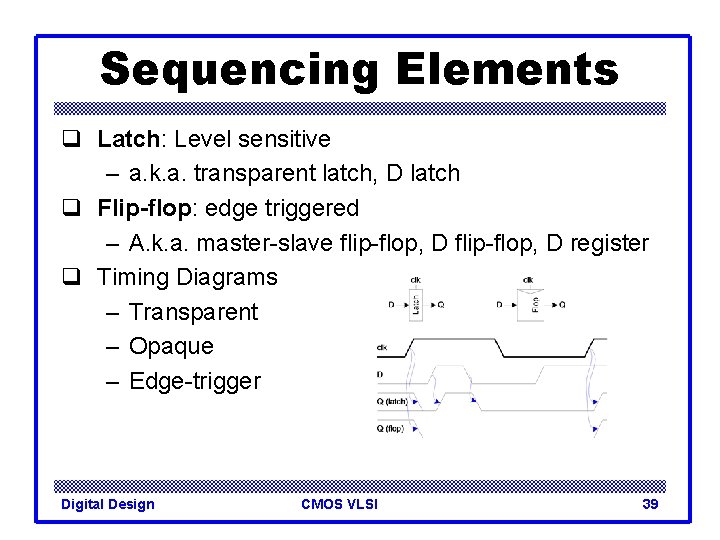

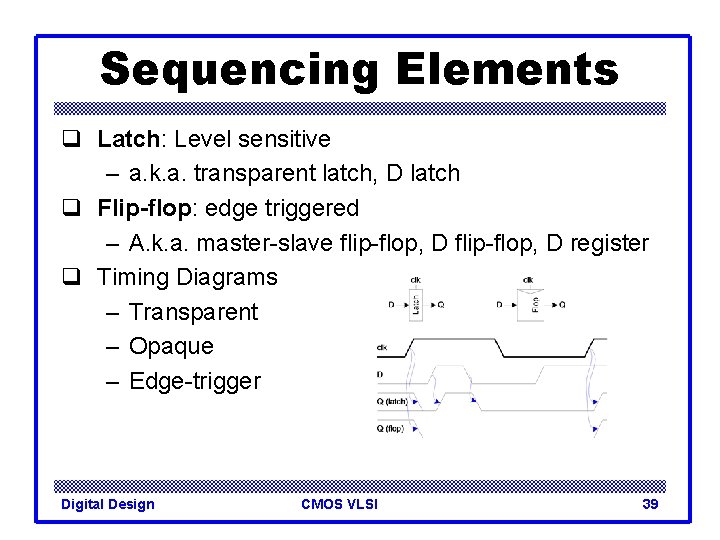

Sequencing Elements q Latch: Level sensitive – a. k. a. transparent latch, D latch q Flip-flop: edge triggered – A. k. a. master-slave flip-flop, D register q Timing Diagrams – Transparent – Opaque – Edge-trigger Digital Design CMOS VLSI 39

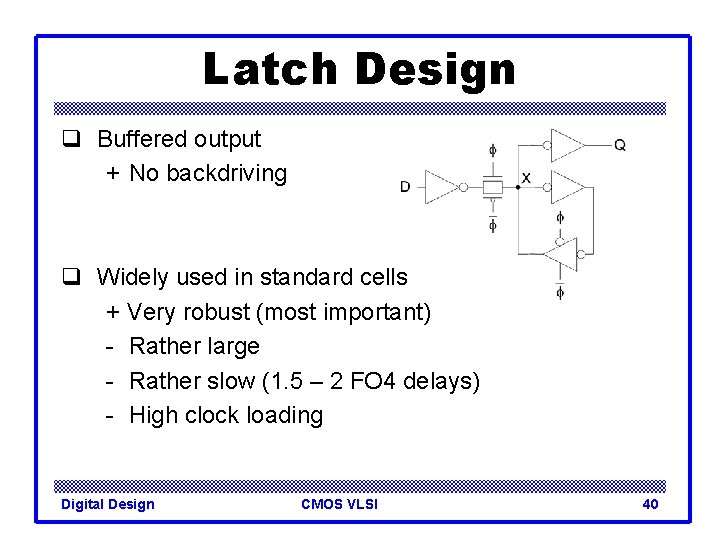

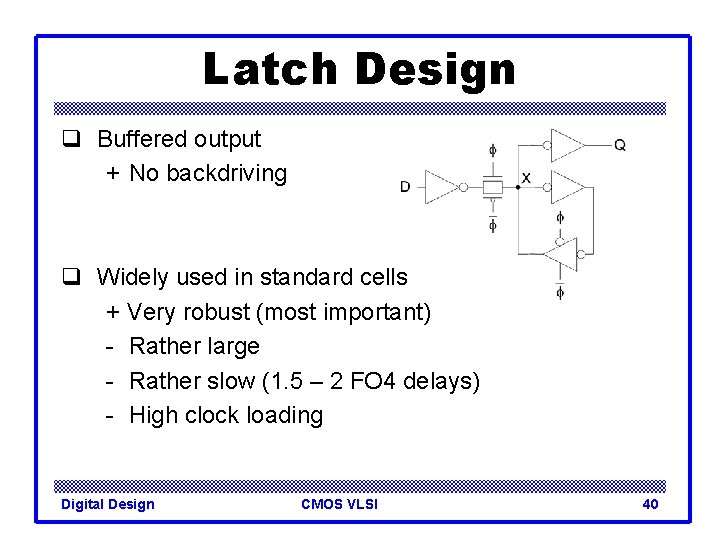

Latch Design q Buffered output + No backdriving q Widely used in standard cells + Very robust (most important) - Rather large - Rather slow (1. 5 – 2 FO 4 delays) - High clock loading Digital Design CMOS VLSI 40

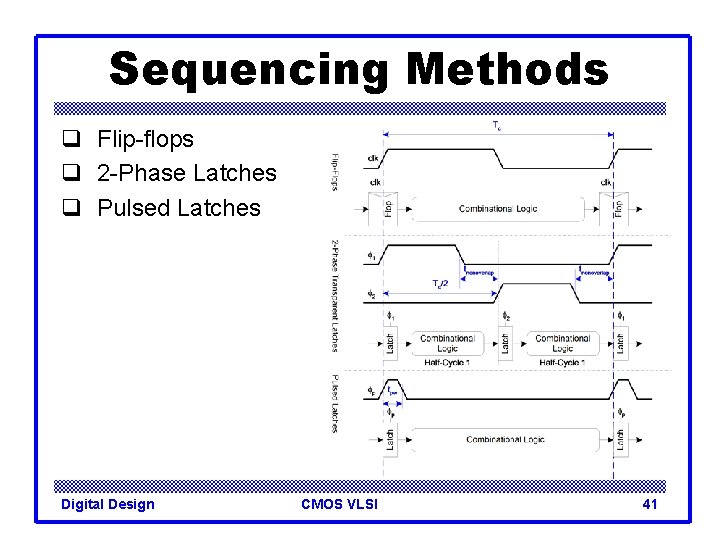

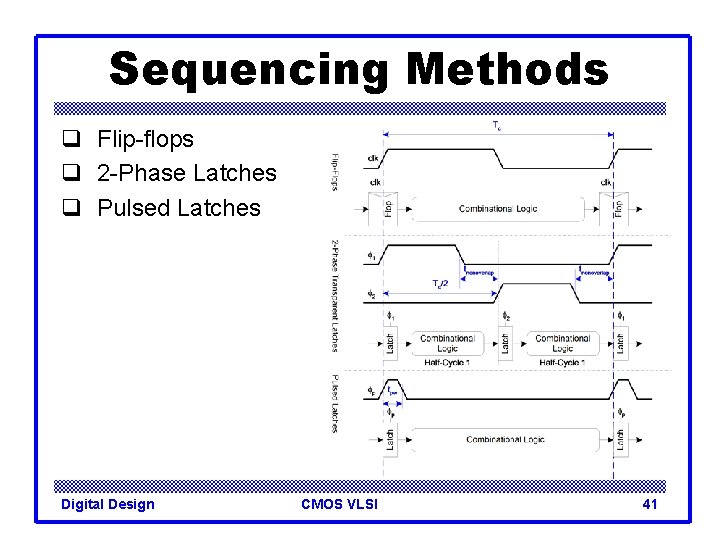

Sequencing Methods q Flip-flops q 2 -Phase Latches q Pulsed Latches Digital Design CMOS VLSI 41

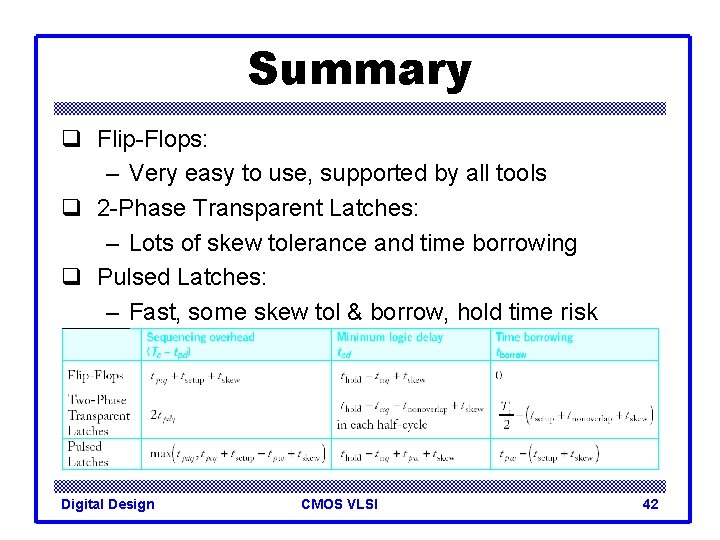

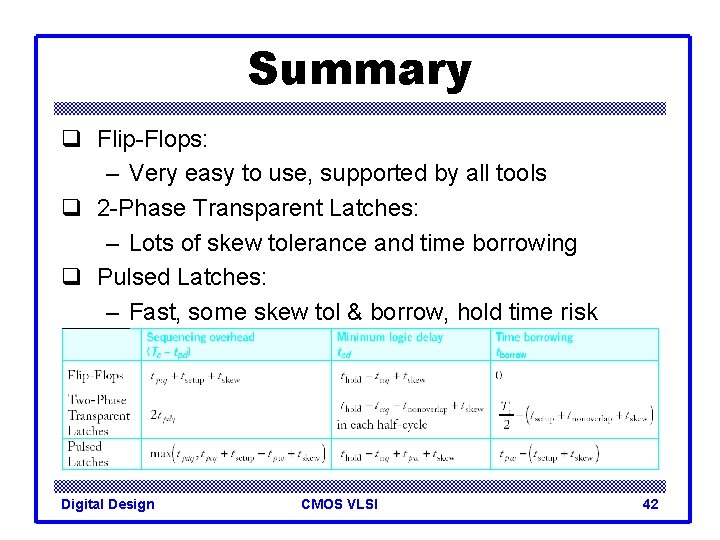

Summary q Flip-Flops: – Very easy to use, supported by all tools q 2 -Phase Transparent Latches: – Lots of skew tolerance and time borrowing q Pulsed Latches: – Fast, some skew tol & borrow, hold time risk Digital Design CMOS VLSI 42

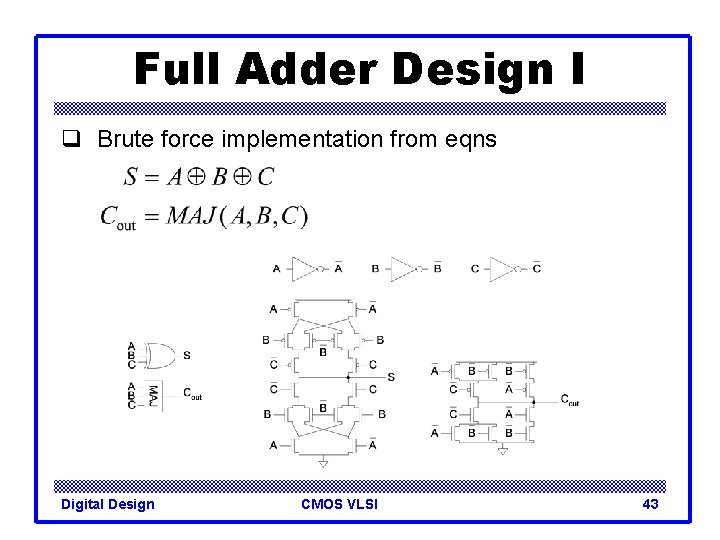

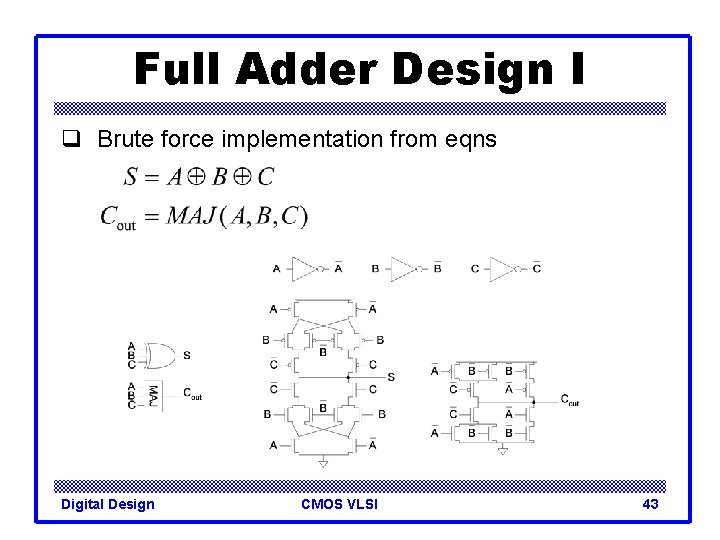

Full Adder Design I q Brute force implementation from eqns Digital Design CMOS VLSI 43

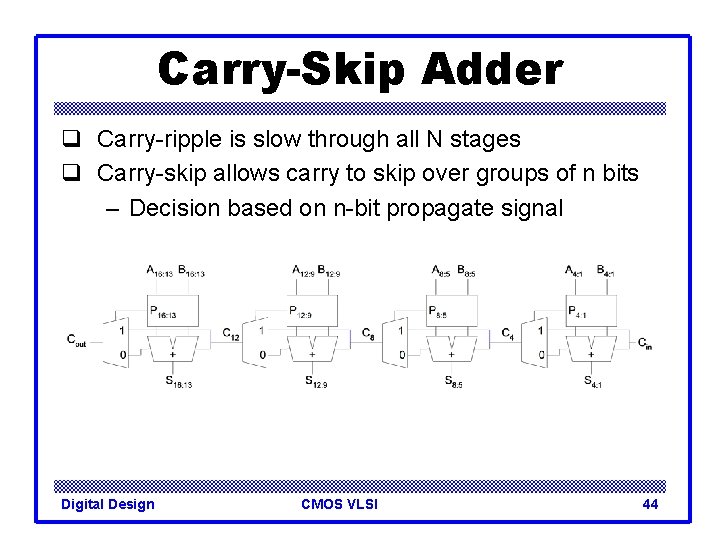

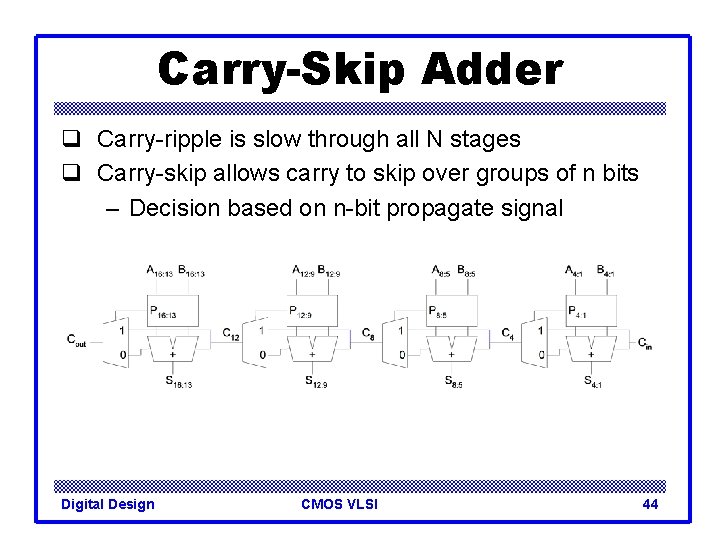

Carry-Skip Adder q Carry-ripple is slow through all N stages q Carry-skip allows carry to skip over groups of n bits – Decision based on n-bit propagate signal Digital Design CMOS VLSI 44

Tree Adder q If lookahead is good, lookahead across lookahead! – Recursive lookahead gives O(log N) delay q Many variations on tree adders Digital Design CMOS VLSI 45

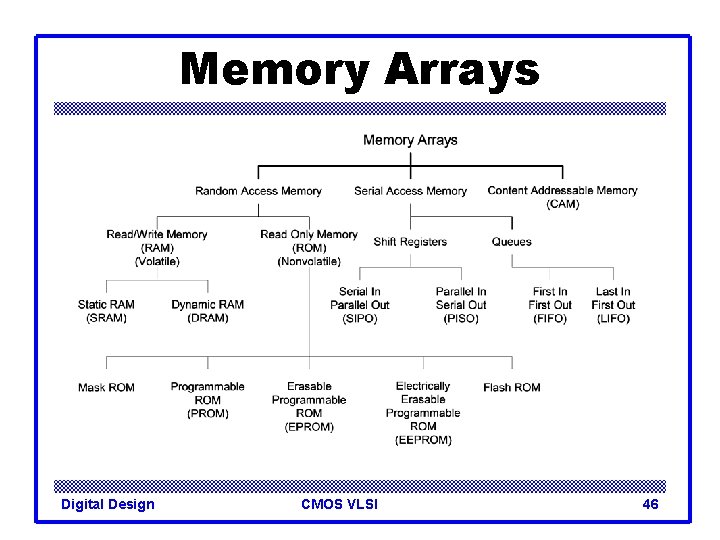

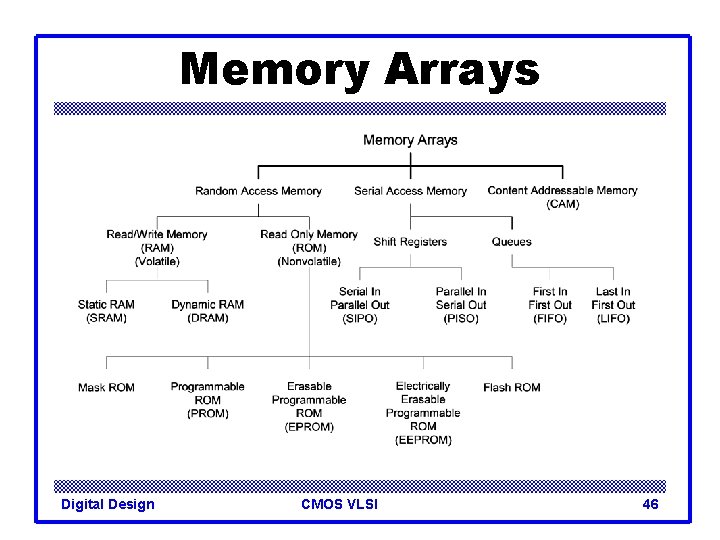

Memory Arrays Digital Design CMOS VLSI 46

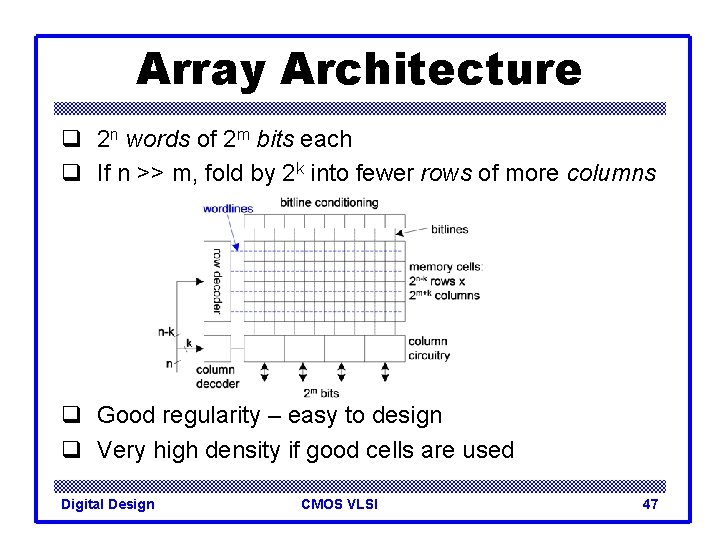

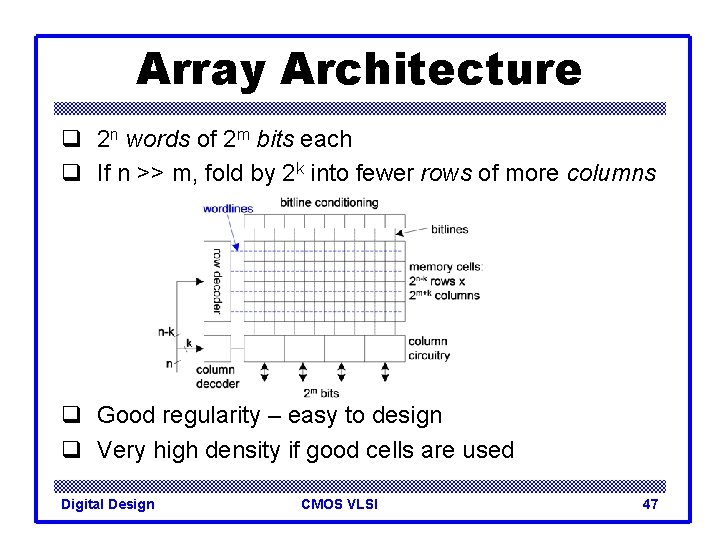

Array Architecture q 2 n words of 2 m bits each q If n >> m, fold by 2 k into fewer rows of more columns q Good regularity – easy to design q Very high density if good cells are used Digital Design CMOS VLSI 47

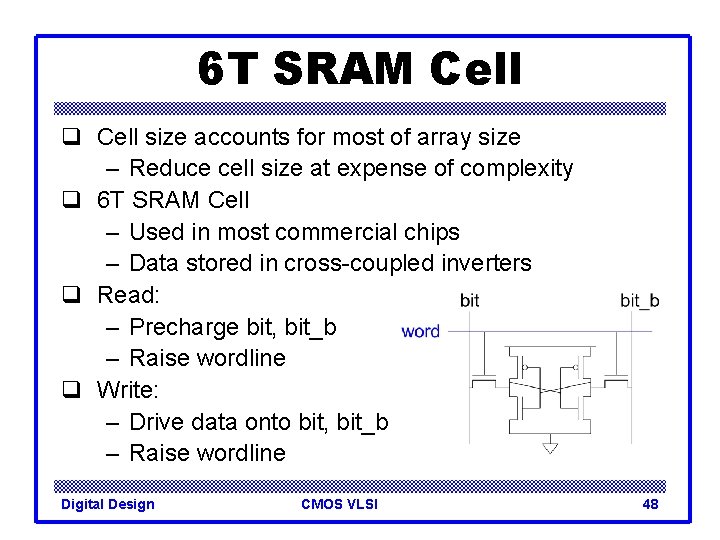

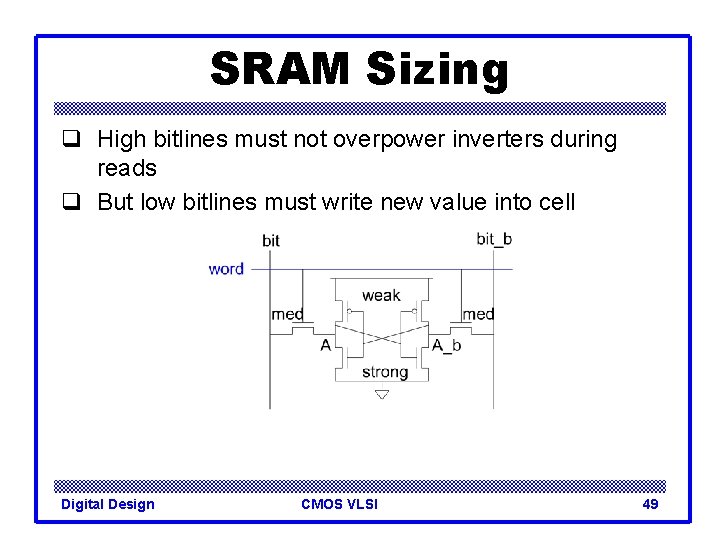

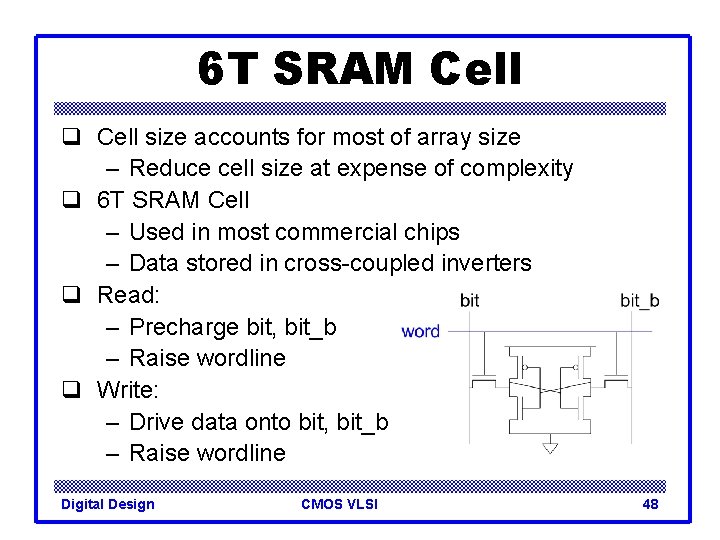

6 T SRAM Cell q Cell size accounts for most of array size – Reduce cell size at expense of complexity q 6 T SRAM Cell – Used in most commercial chips – Data stored in cross-coupled inverters q Read: – Precharge bit, bit_b – Raise wordline q Write: – Drive data onto bit, bit_b – Raise wordline Digital Design CMOS VLSI 48

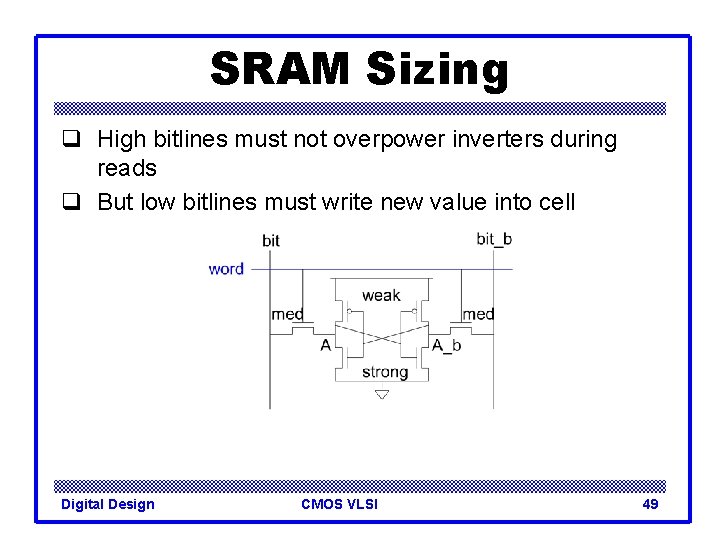

SRAM Sizing q High bitlines must not overpower inverters during reads q But low bitlines must write new value into cell Digital Design CMOS VLSI 49

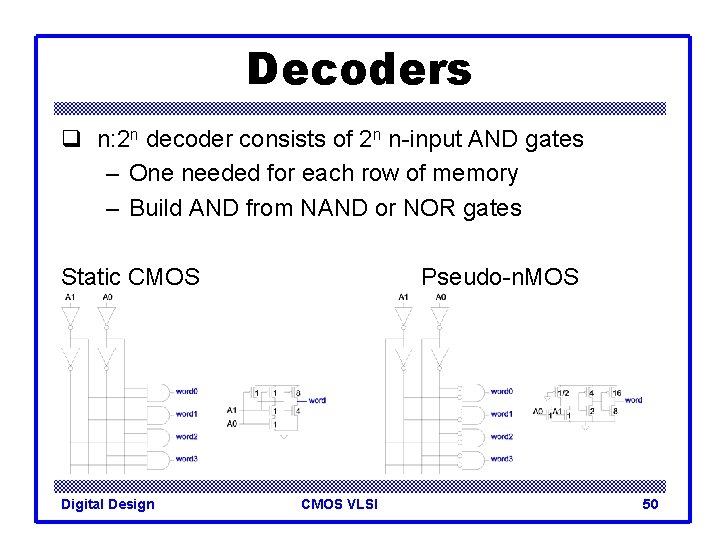

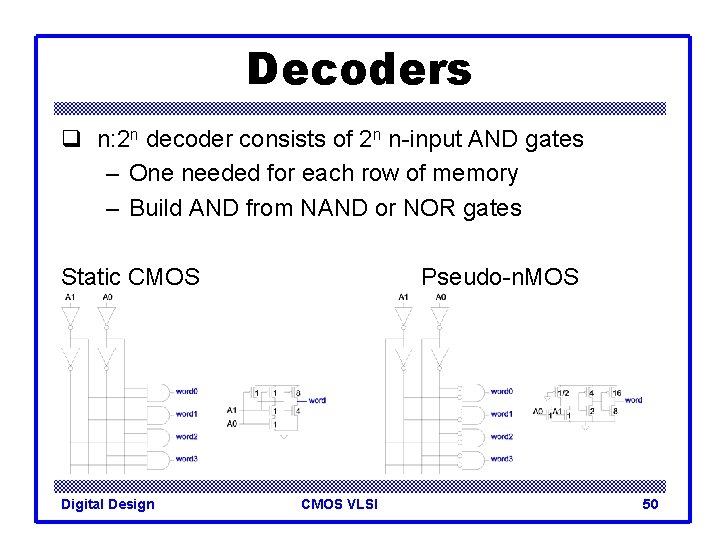

Decoders q n: 2 n decoder consists of 2 n n-input AND gates – One needed for each row of memory – Build AND from NAND or NOR gates Static CMOS Digital Design Pseudo-n. MOS CMOS VLSI 50

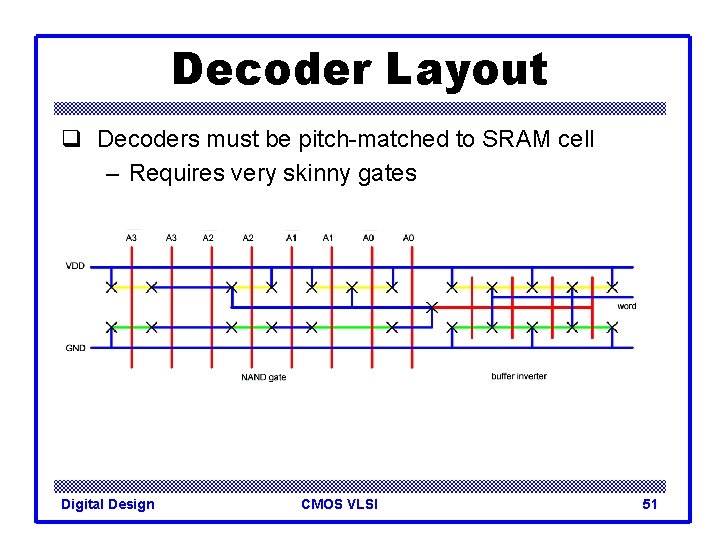

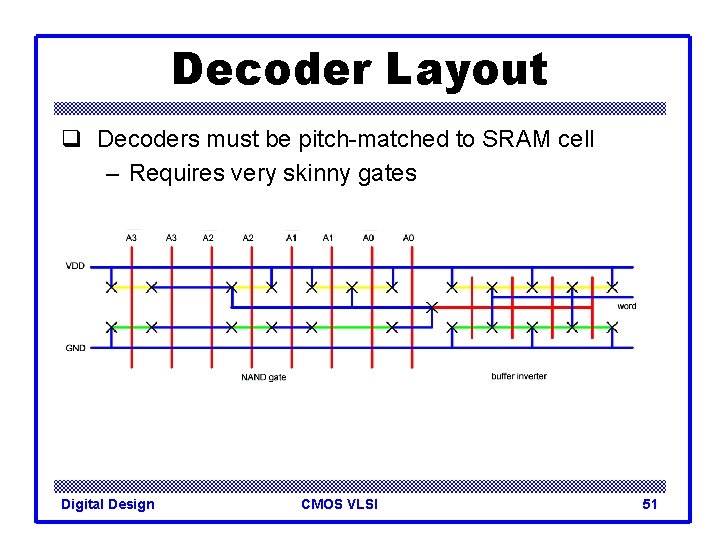

Decoder Layout q Decoders must be pitch-matched to SRAM cell – Requires very skinny gates Digital Design CMOS VLSI 51

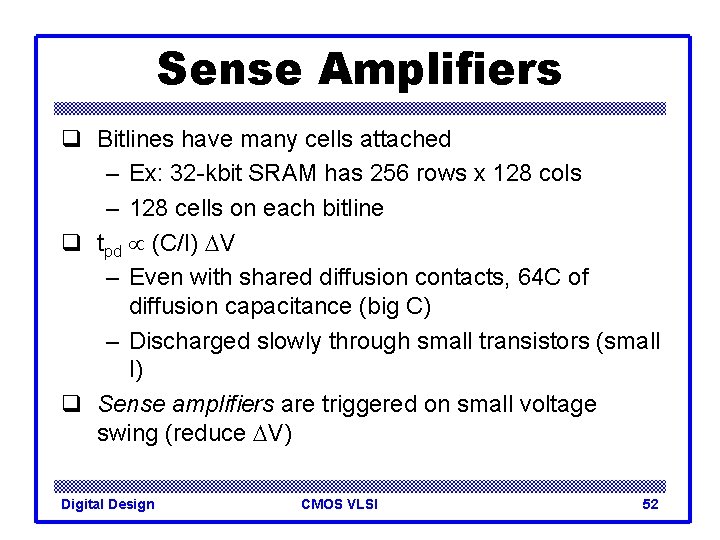

Sense Amplifiers q Bitlines have many cells attached – Ex: 32 -kbit SRAM has 256 rows x 128 cols – 128 cells on each bitline q tpd (C/I) DV – Even with shared diffusion contacts, 64 C of diffusion capacitance (big C) – Discharged slowly through small transistors (small I) q Sense amplifiers are triggered on small voltage swing (reduce DV) Digital Design CMOS VLSI 52

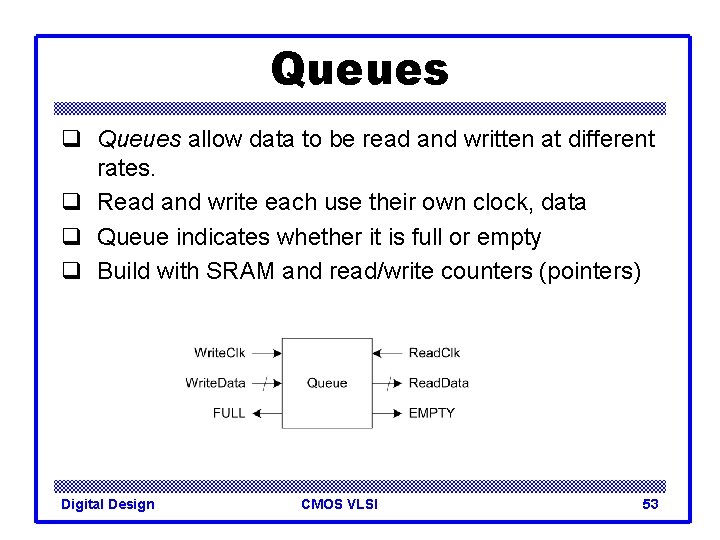

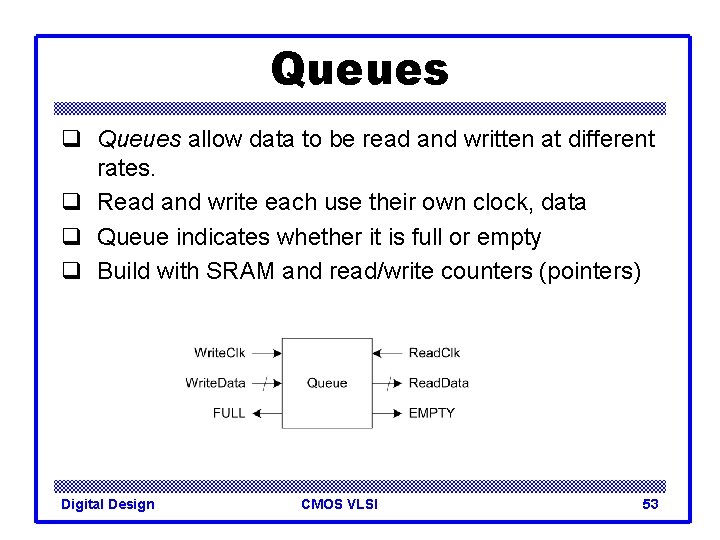

Queues q Queues allow data to be read and written at different rates. q Read and write each use their own clock, data q Queue indicates whether it is full or empty q Build with SRAM and read/write counters (pointers) Digital Design CMOS VLSI 53

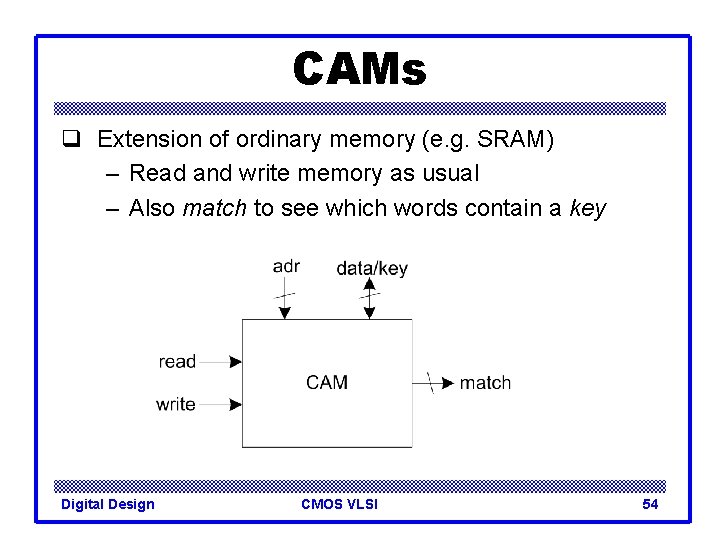

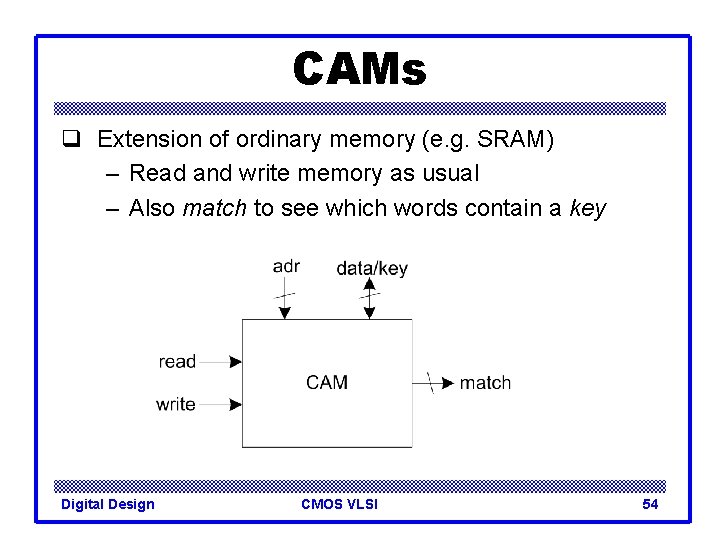

CAMs q Extension of ordinary memory (e. g. SRAM) – Read and write memory as usual – Also match to see which words contain a key Digital Design CMOS VLSI 54

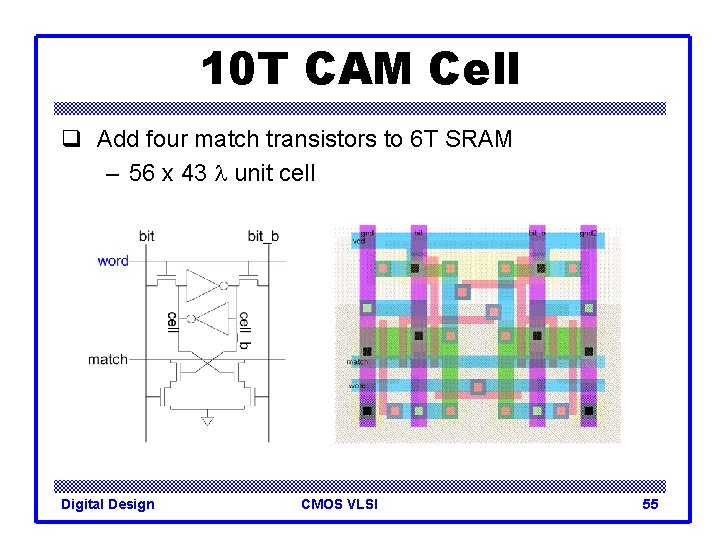

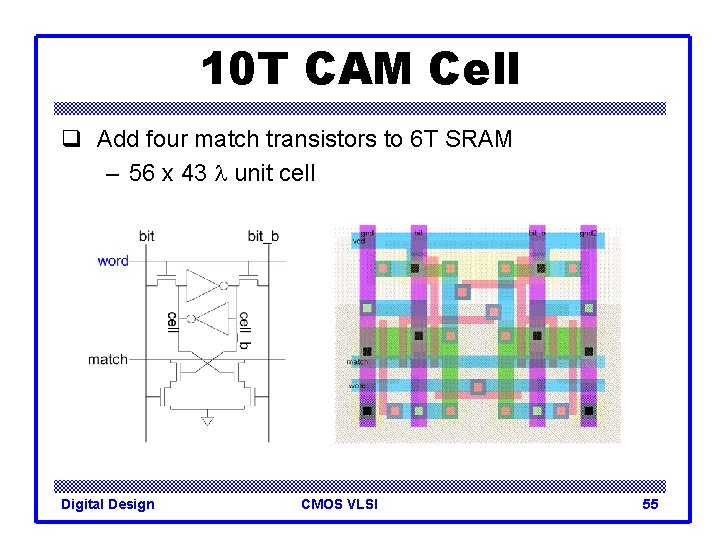

10 T CAM Cell q Add four match transistors to 6 T SRAM – 56 x 43 l unit cell Digital Design CMOS VLSI 55

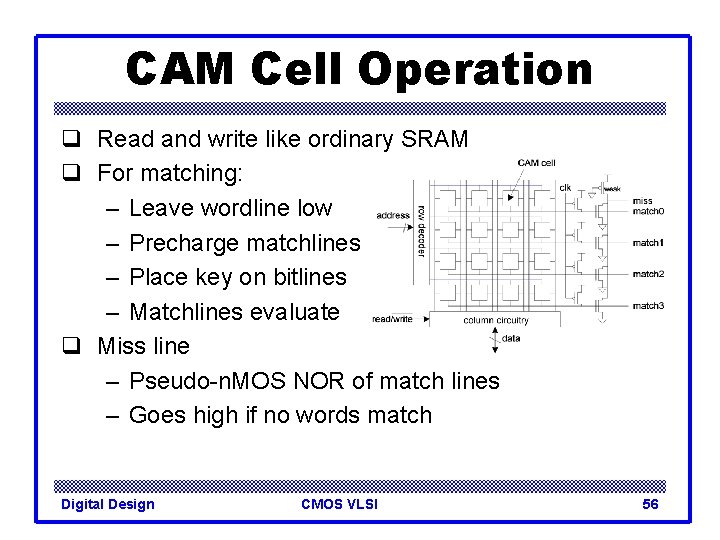

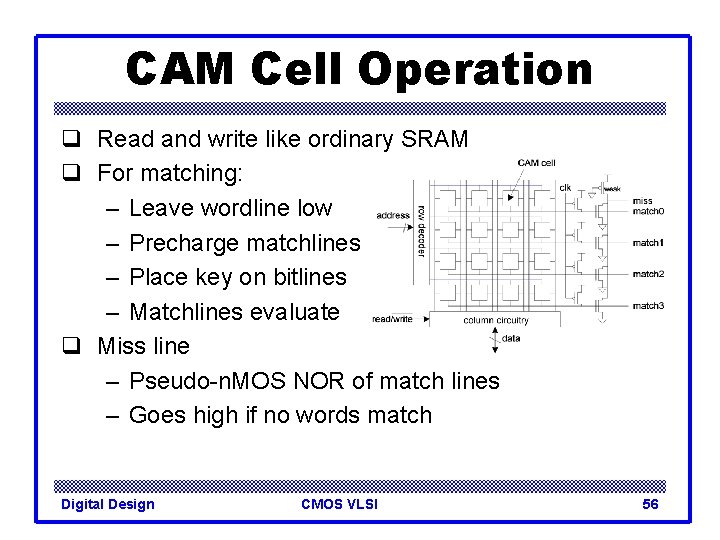

CAM Cell Operation q Read and write like ordinary SRAM q For matching: – Leave wordline low – Precharge matchlines – Place key on bitlines – Matchlines evaluate q Miss line – Pseudo-n. MOS NOR of match lines – Goes high if no words match Digital Design CMOS VLSI 56

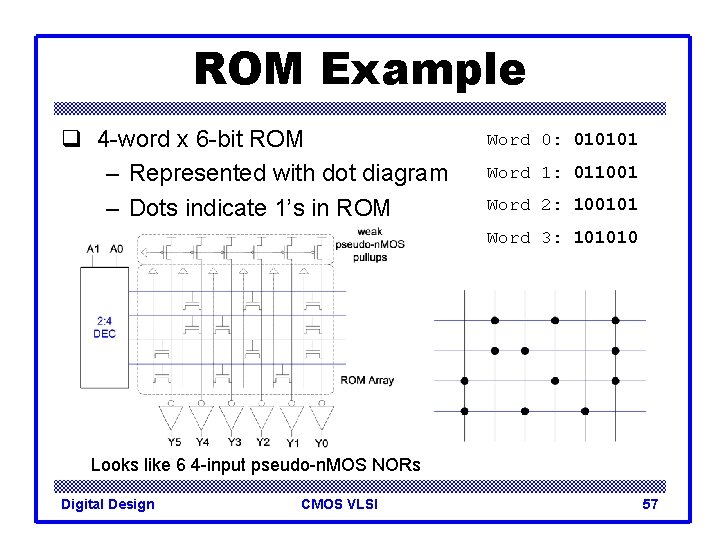

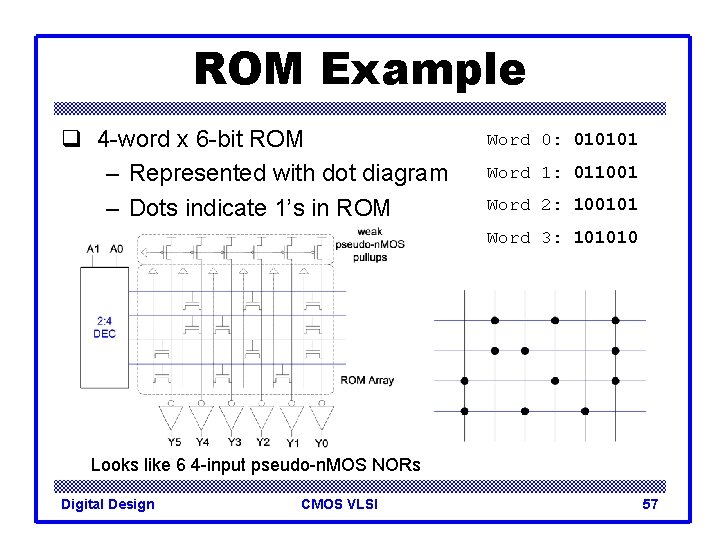

ROM Example q 4 -word x 6 -bit ROM – Represented with dot diagram – Dots indicate 1’s in ROM Word 0: 010101 Word 1: 011001 Word 2: 100101 Word 3: 101010 Looks like 6 4 -input pseudo-n. MOS NORs Digital Design CMOS VLSI 57

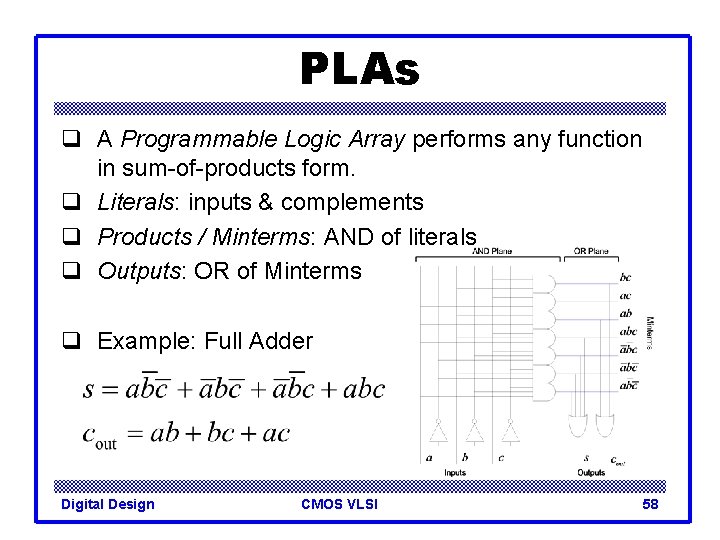

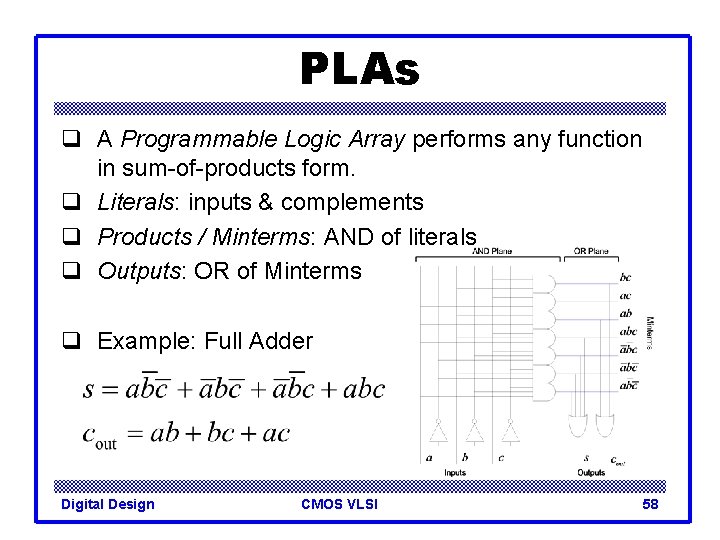

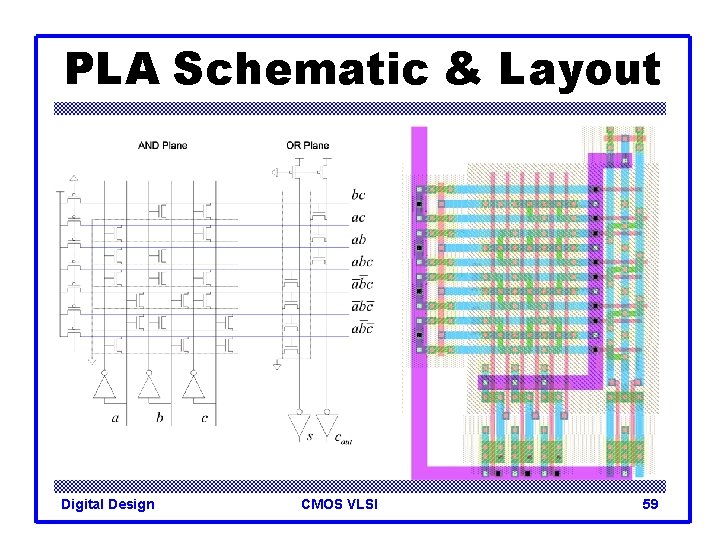

PLAs q A Programmable Logic Array performs any function in sum-of-products form. q Literals: inputs & complements q Products / Minterms: AND of literals q Outputs: OR of Minterms q Example: Full Adder Digital Design CMOS VLSI 58

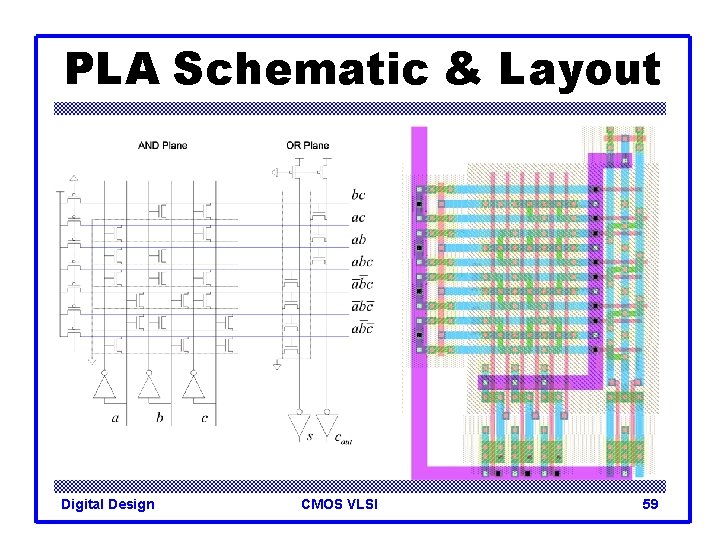

PLA Schematic & Layout Digital Design CMOS VLSI 59

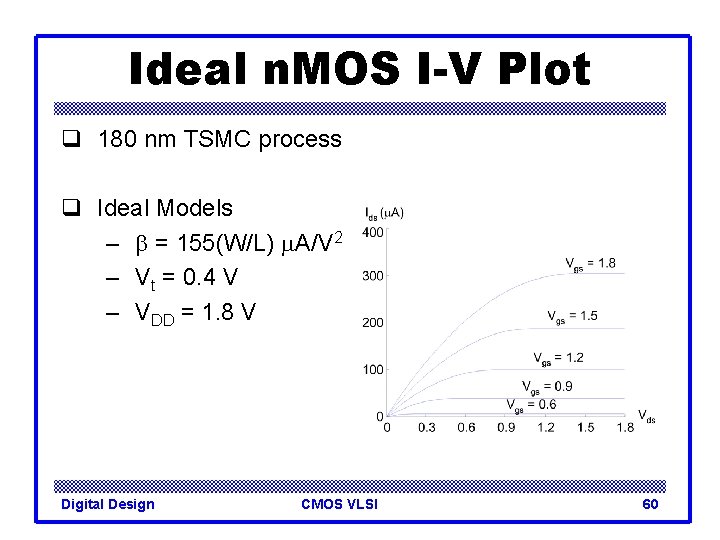

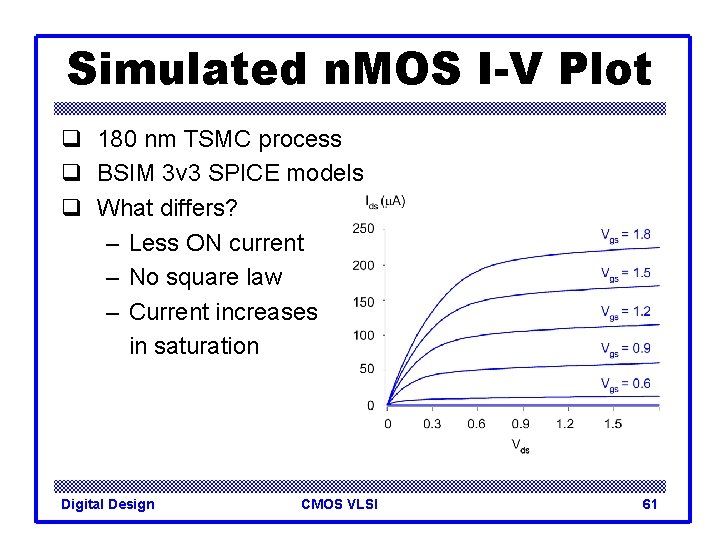

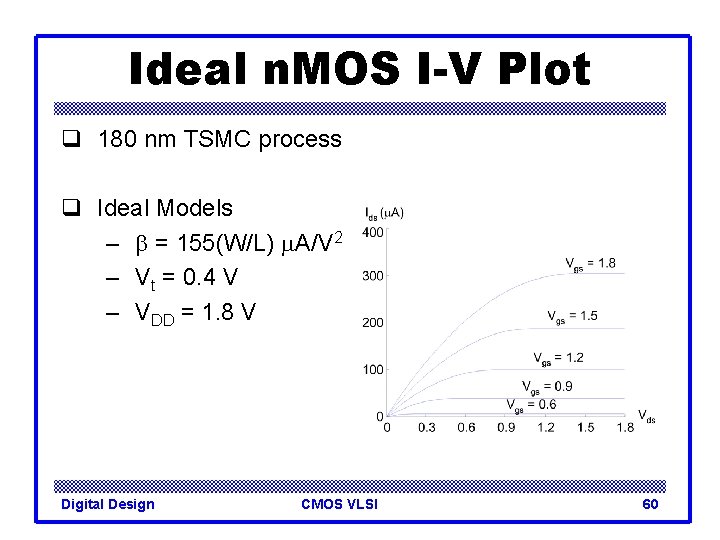

Ideal n. MOS I-V Plot q 180 nm TSMC process q Ideal Models – b = 155(W/L) m. A/V 2 – Vt = 0. 4 V – VDD = 1. 8 V Digital Design CMOS VLSI 60

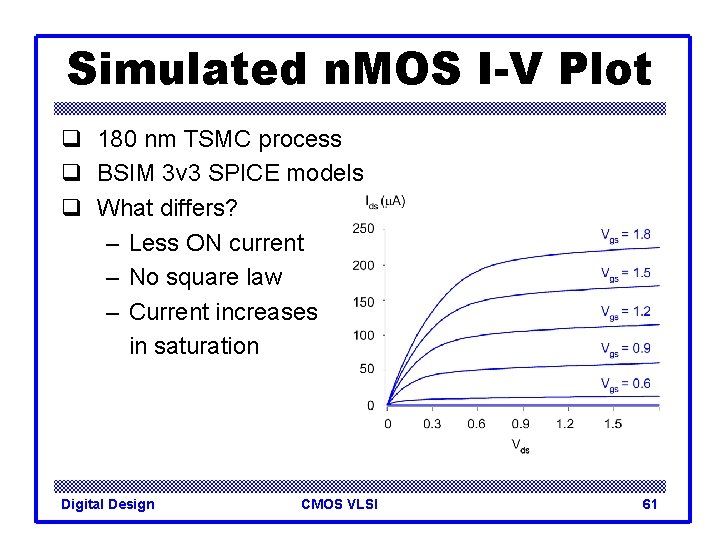

Simulated n. MOS I-V Plot q 180 nm TSMC process q BSIM 3 v 3 SPICE models q What differs? – Less ON current – No square law – Current increases in saturation Digital Design CMOS VLSI 61

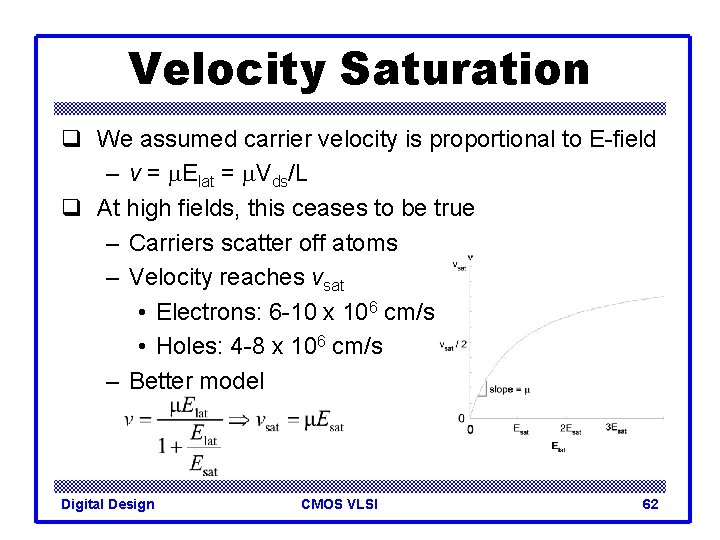

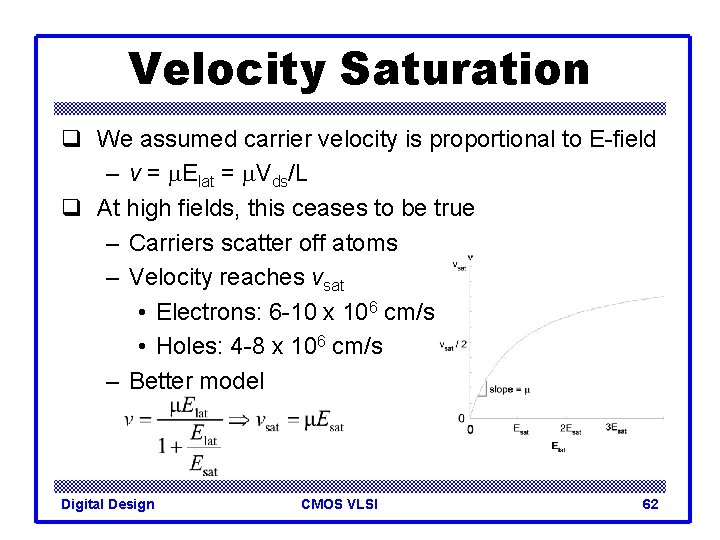

Velocity Saturation q We assumed carrier velocity is proportional to E-field – v = m. Elat = m. Vds/L q At high fields, this ceases to be true – Carriers scatter off atoms – Velocity reaches vsat • Electrons: 6 -10 x 106 cm/s • Holes: 4 -8 x 106 cm/s – Better model Digital Design CMOS VLSI 62

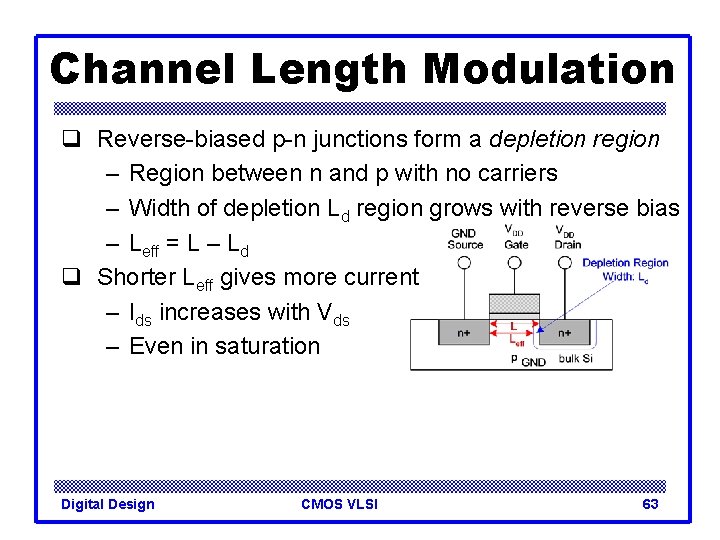

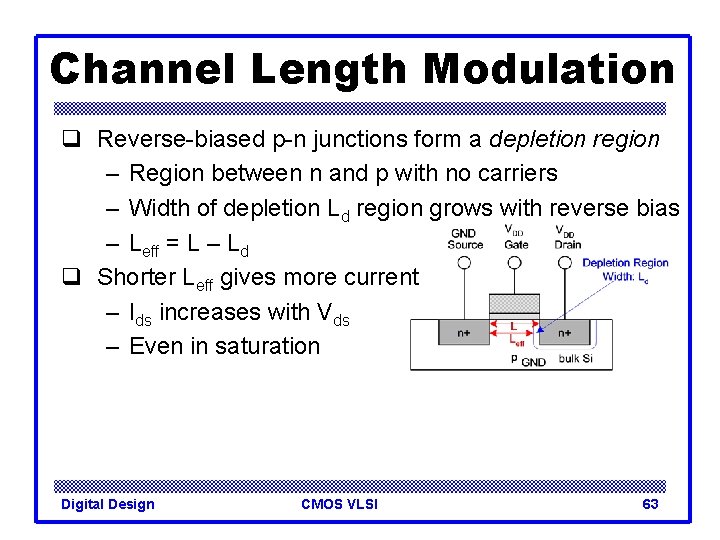

Channel Length Modulation q Reverse-biased p-n junctions form a depletion region – Region between n and p with no carriers – Width of depletion Ld region grows with reverse bias – Leff = L – Ld q Shorter Leff gives more current – Ids increases with Vds – Even in saturation Digital Design CMOS VLSI 63

Body Effect q Vt: gate voltage necessary to invert channel q Increases if source voltage increases because source is connected to the channel q Increase in Vt with Vs is called the body effect Digital Design CMOS VLSI 64

OFF Transistor Behavior q What about current in cutoff? q Simulated results q What differs? – Current doesn’t go to 0 in cutoff Digital Design CMOS VLSI 65

Leakage Sources q Subthreshold conduction – Transistors can’t abruptly turn ON or OFF q Junction leakage – Reverse-biased PN junction diode current q Gate leakage – Tunneling through ultrathin gate dielectric q Subthreshold leakage is the biggest source in modern transistors Digital Design CMOS VLSI 66

Low Power Design q Reduce dynamic power – a: clock gating, sleep mode – C: small transistors (esp. on clock), short wires – VDD: lowest suitable voltage – f: lowest suitable frequency q Reduce static power – Selectively use ratioed circuits – Selectively use low Vt devices – Leakage reduction: stacked devices, body bias, low temperature Digital Design CMOS VLSI 67

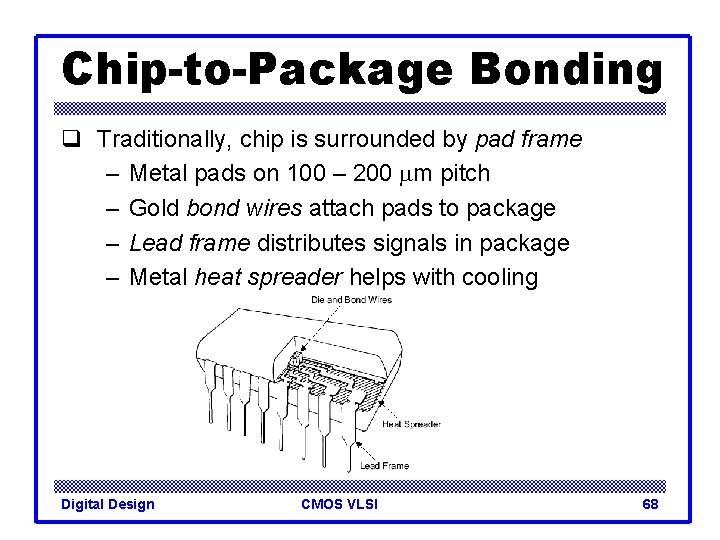

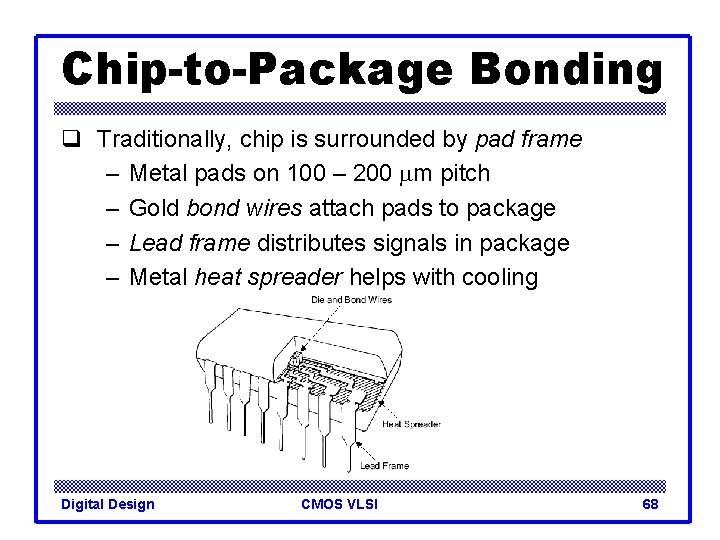

Chip-to-Package Bonding q Traditionally, chip is surrounded by pad frame – Metal pads on 100 – 200 mm pitch – Gold bond wires attach pads to package – Lead frame distributes signals in package – Metal heat spreader helps with cooling Digital Design CMOS VLSI 68

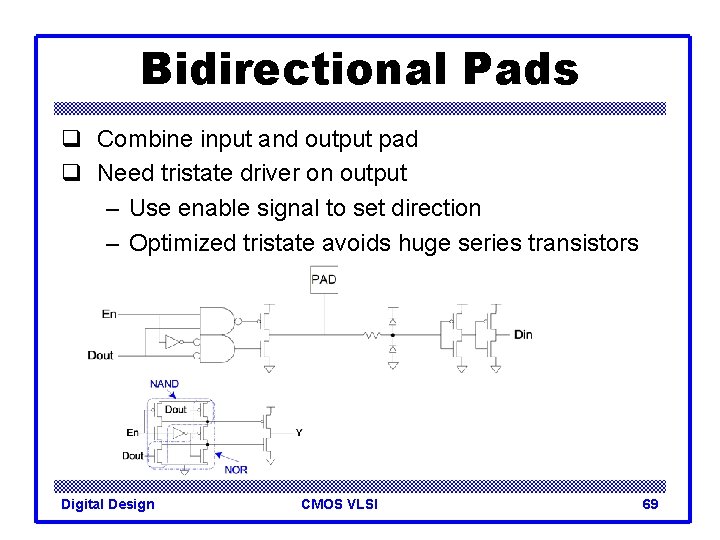

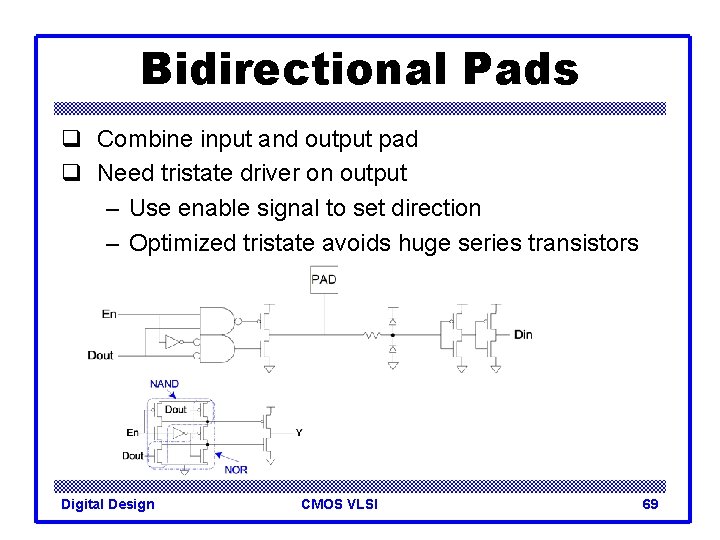

Bidirectional Pads q Combine input and output pad q Need tristate driver on output – Use enable signal to set direction – Optimized tristate avoids huge series transistors Digital Design CMOS VLSI 69

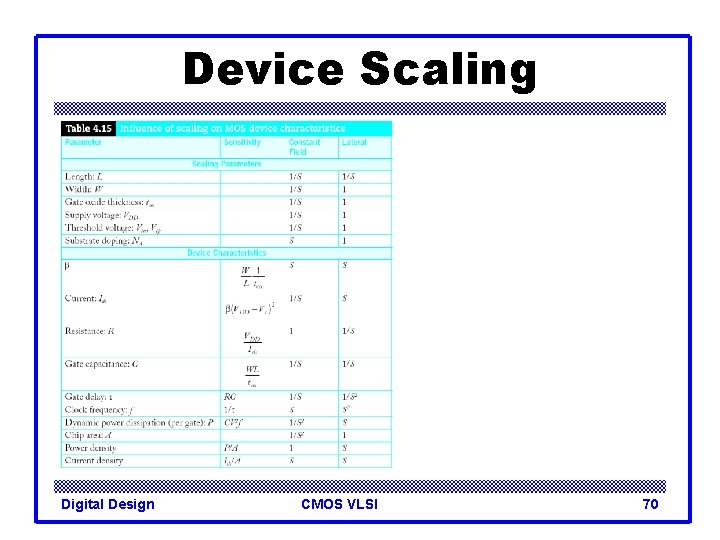

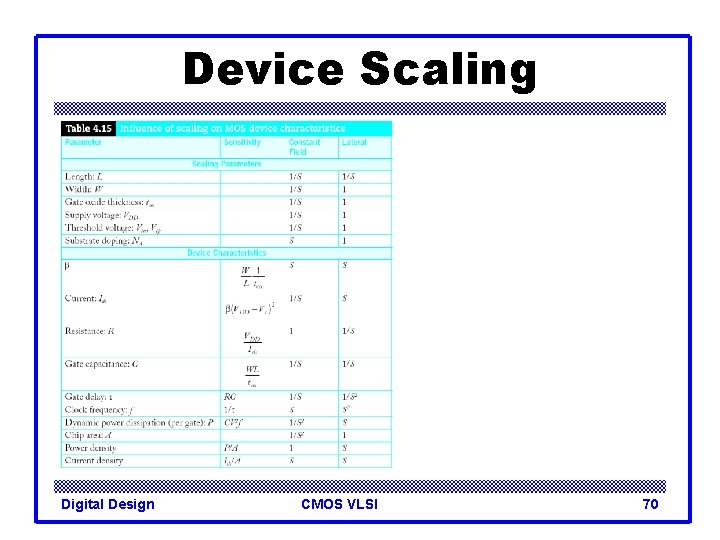

Device Scaling Digital Design CMOS VLSI 70

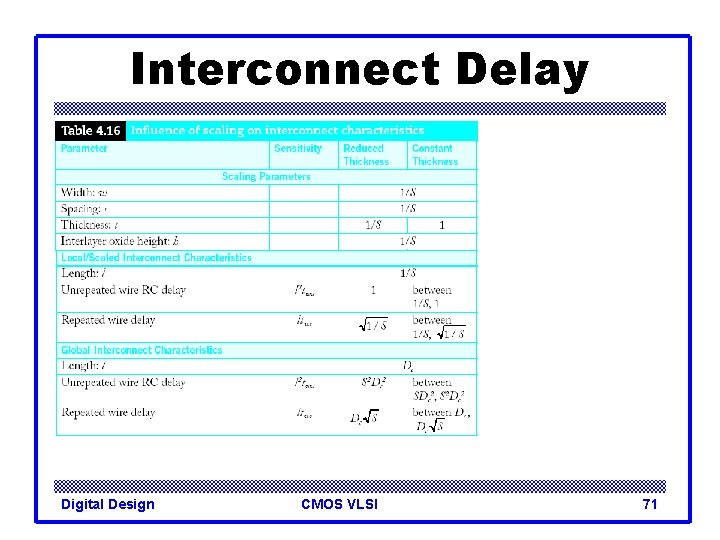

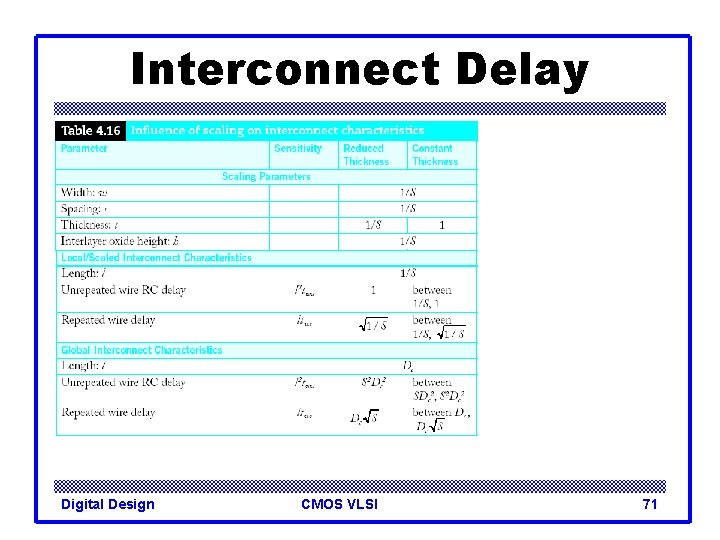

Interconnect Delay Digital Design CMOS VLSI 71