Chapter 5 CMOS Inverter Boonchuay Supmonchai Integrated Design

Chapter 5 CMOS Inverter Boonchuay Supmonchai Integrated Design Application Research (IDAR) Laboratory July 5, 2004; Revised - June 25, 2005 2102 -545 Digital ICs

B. Supmonchai Goals of This Chapter q Quantification of Design Metrics of an inverter § Static (or Steady-State) Behavior § Dynamic (or Transient Response) Behavior § Energy Efficiency q q Optimization of an inverter design Technology Scaling and its impact on the inverter metrics 2102 -545 Digital ICs CMOS Inverter 2

B. Supmonchai Digital Gate Design Metrics: Recap q Cost § Complexity and Area q Reliability and Robustness Static Behavior § Noise Margin, Regenerative Property q Performance Dynamic Behavior § Speed (Delay) q Energy Efficiency § Energy and Power Consumption, Energy-Delay 2102 -545 Digital ICs CMOS Inverter 3

B. Supmonchai Why CMOS Inverter? q CMOS because it is the dominating technology of the era. § High Packing Density § Relatively Easy Process q Inverter because it is the nucleus of all digital designs. § Behavior of more intricate structures (logic gates, adders, etc. ) can be almost completely derived by extrapolating the results obtained from the inverters. 2102 -545 Digital ICs CMOS Inverter 4

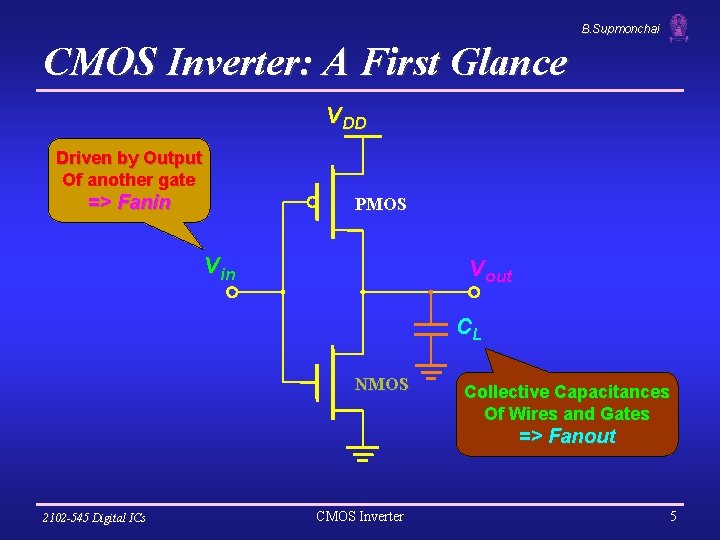

B. Supmonchai CMOS Inverter: A First Glance V DD Driven by Output Of another gate => Fanin PMOS V in V out CL NMOS Collective Capacitances Of Wires and Gates => Fanout 2102 -545 Digital ICs CMOS Inverter 5

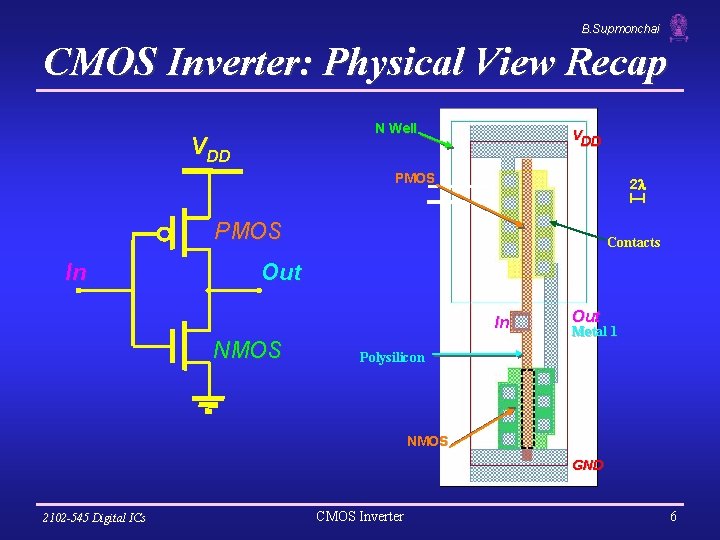

B. Supmonchai CMOS Inverter: Physical View Recap N Well VDD PMOS 2 PMOS In Contacts Out In NMOS Out Metal 1 Polysilicon NMOS GND 2102 -545 Digital ICs CMOS Inverter 6

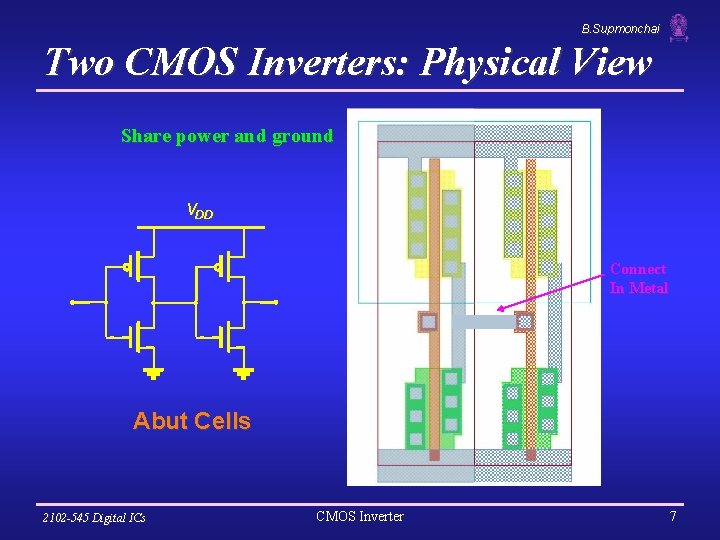

B. Supmonchai Two CMOS Inverters: Physical View Share power and ground VDD Connect In Metal Abut Cells 2102 -545 Digital ICs CMOS Inverter 7

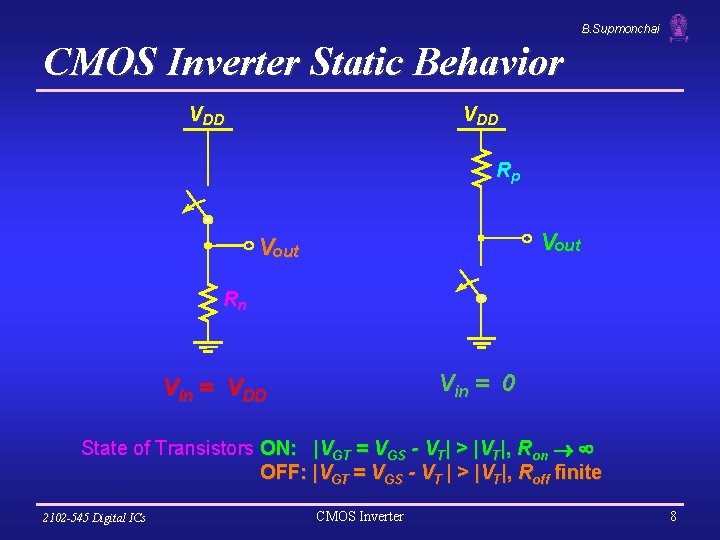

B. Supmonchai CMOS Inverter Static Behavior V DD Rp Vout Rn Vin = 0 Vin = VDD State of Transistors ON: |VGT = VGS - VT| > |VT|, Ron OFF: |VGT = VGS - VT | > |VT|, Roff finite 2102 -545 Digital ICs CMOS Inverter 8

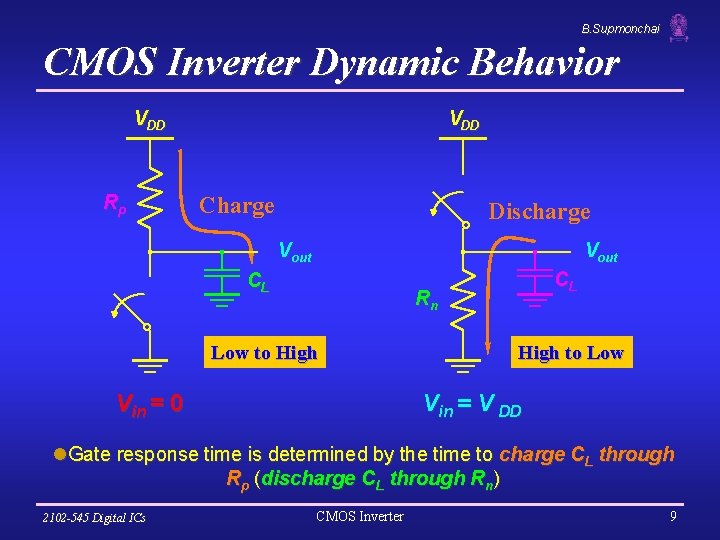

B. Supmonchai CMOS Inverter Dynamic Behavior VDD Rp VDD Charge Discharge Vout CL CL Rn Low to High Vin = 0 High to Low Vin = V DD l. Gate response time is determined by the time to charge CL through Rp (discharge CL through Rn) 2102 -545 Digital ICs CMOS Inverter 9

B. Supmonchai CMOS Properties q Full rail-to-rail swing § High noise margins § Logic levels not dependent upon the relative device sizes => Ratioless Ø Transistors can be minimum size Ø Regenerative Property q Low output impedance § Large Fan-out (albeit with degraded performance) § Typical output resistance in k range. 2102 -545 Digital ICs CMOS Inverter 10

B. Supmonchai CMOS Properties (2( q Extremely high input resistance (MOS transistor is near perfect insulator) § nearly zero steady-state input current q No direct path between power and ground under steady-state (but there always exists a path with finite resistance between the output and either VDD or GND) § no static power dissipation q Propagation delay a function of load capacitance and resistance of transistors 2102 -545 Digital ICs CMOS Inverter 11

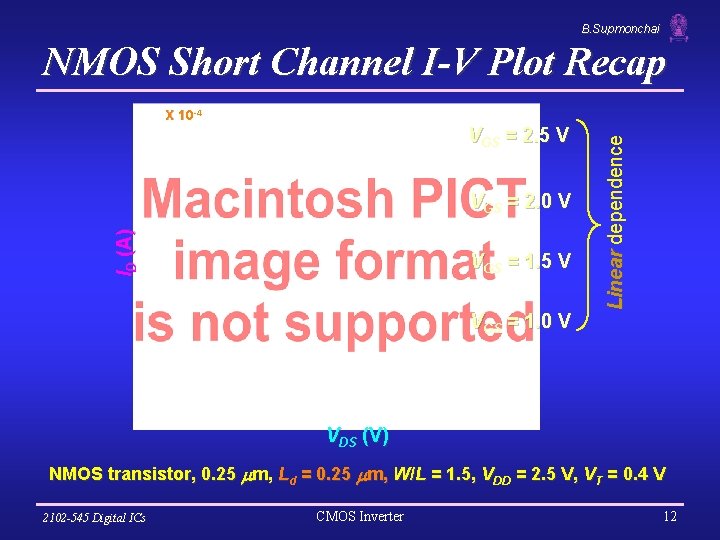

B. Supmonchai NMOS Short Channel I-V Plot Recap VGS = 2. 5 V ID (A) VGS = 2. 0 V VGS = 1. 5 V VGS = 1. 0 V Linear dependence X 10 -4 VDS (V) NMOS transistor, 0. 25 m, Ld = 0. 25 m, W/L = 1. 5, VDD = 2. 5 V, VT = 0. 4 V 2102 -545 Digital ICs CMOS Inverter 12

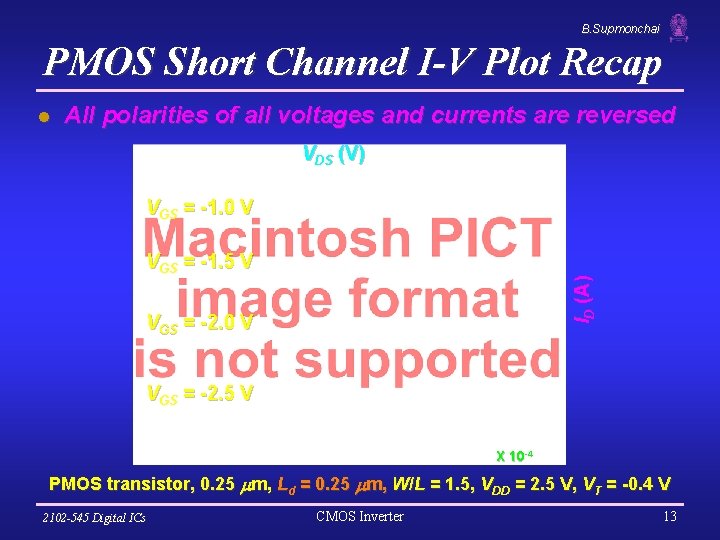

B. Supmonchai PMOS Short Channel I-V Plot Recap l All polarities of all voltages and currents are reversed VDS (V) VGS = -1. 0 V ID (A) VGS = -1. 5 V VGS = -2. 0 V VGS = -2. 5 V X 10 -4 PMOS transistor, 0. 25 m, Ld = 0. 25 m, W/L = 1. 5, VDD = 2. 5 V, VT = -0. 4 V 2102 -545 Digital ICs CMOS Inverter 13

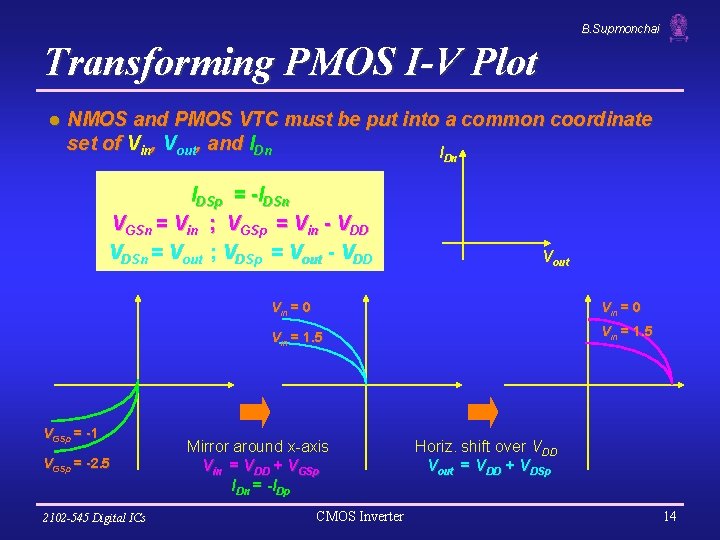

B. Supmonchai Transforming PMOS I-V Plot l NMOS and PMOS VTC must be put into a common coordinate set of Vin, Vout, and IDn IDSp = -IDSn VGSn = Vin ; VGSp = Vin - VDD VDSn = Vout ; VDSp = Vout - VDD VGSp = -1 VGSp = -2. 5 2102 -545 Digital ICs Vout Vin = 0 Vin = 1. 5 Mirror around x-axis Vin = VDD + VGSp IDn = -IDp CMOS Inverter Horiz. shift over VDD Vout = VDD + VDSp 14

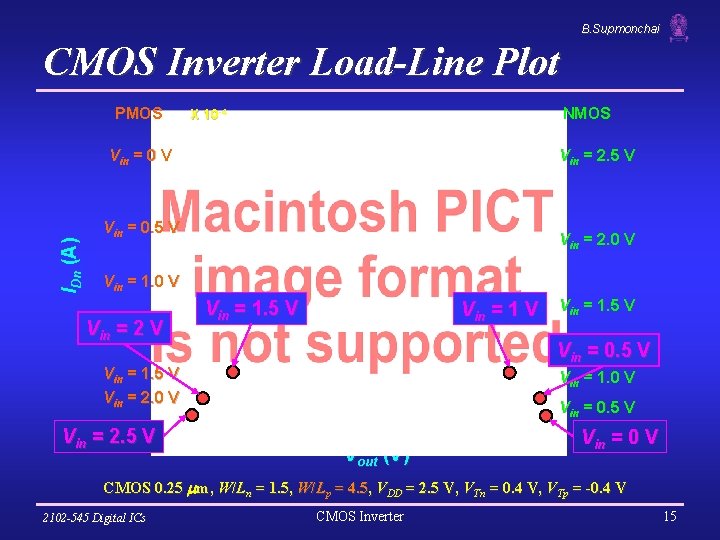

B. Supmonchai CMOS Inverter Load-Line Plot PMOS NMOS X 10 -4 IDn (A) Vin = 0 V Vin = 2. 5 V Vin = 0. 5 V Vin = 2. 0 V Vin = 1. 0 V Vin = 2 V Vin = 1. 5 V Vin = 1 V Vin = 0. 5 V Vin = 1. 5 V Vin = 2. 0 V Vin = 2. 5 V Vin = 1. 0 V Vin = 0. 5 V Vout (V) Vin = 0 V CMOS 0. 25 m, W/Ln = 1. 5, W/Lp = 4. 5, VDD = 2. 5 V, VTn = 0. 4 V, VTp = -0. 4 V 2102 -545 Digital ICs CMOS Inverter 15

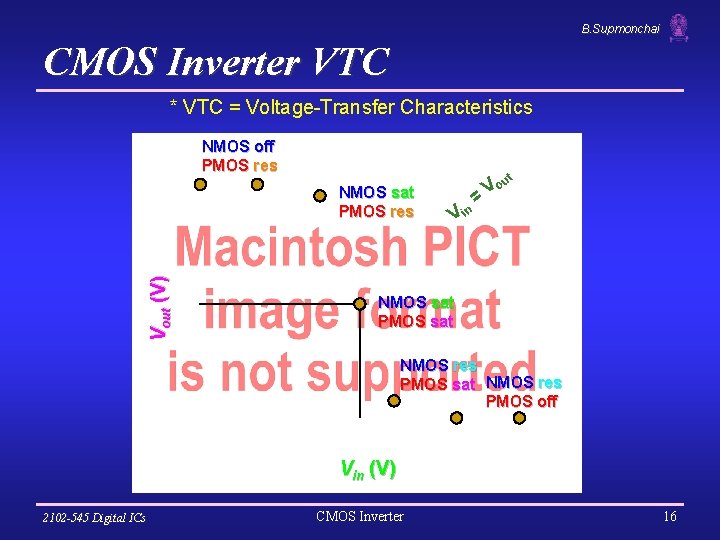

B. Supmonchai CMOS Inverter VTC * VTC = Voltage-Transfer Characteristics NMOS off PMOS res Vout (V) NMOS sat PMOS res t V in = V ou NMOS sat PMOS sat NMOS res PMOS off Vin (V) 2102 -545 Digital ICs CMOS Inverter 16

B. Supmonchai Robustness of CMOS Inverter q Precise Values of Switching Threshold, VM § VM is defined as the point where Vin = Vout q Noise Margins § Piece-Wise Linear Approximation § Maximization q Process Variations § Device Variations § Technology Scaling 2102 -545 Digital ICs CMOS Inverter 17

B. Supmonchai Switching Threshold q At VM where Vin = Vout, both PMOS and NMOS transistors are in saturation (since VDS = VGS) VM r. VDD/(1 + r) where r = kp. VDSATp/kn. VDSATn q q Switching threshold set by the ratio r, which compares the relative driving strengths of the PMOS and NMOS transistors Goal: To set VM = VDD/2 (to maximize noise margins), so r 1 2102 -545 Digital ICs CMOS Inverter 18

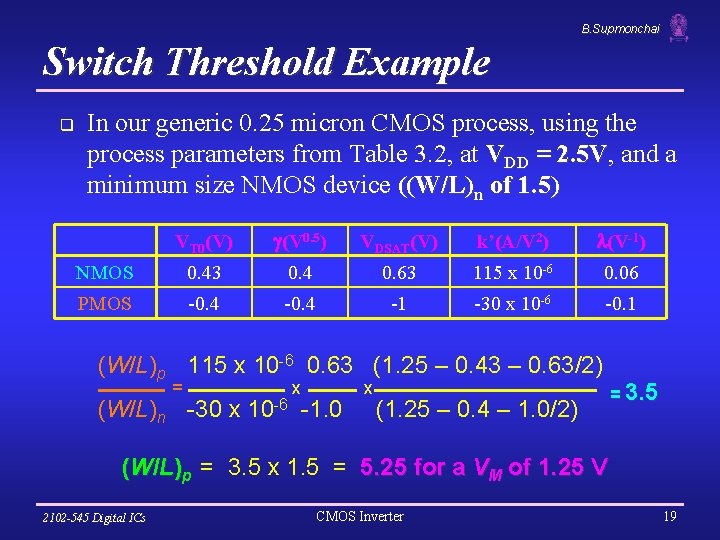

B. Supmonchai Switch Threshold Example q In our generic 0. 25 micron CMOS process, using the process parameters from Table 3. 2, at VDD = 2. 5 V, 2. 5 V and a minimum size NMOS device ((W/L)n of 1. 5) VT 0(V) (V 0. 5) VDSAT(V) k’(A/V 2) (V-1) NMOS 0. 43 0. 4 0. 63 115 x 10 -6 0. 06 PMOS -0. 4 -1 -30 x 10 -6 -0. 1 (W/L)p 115 x 10 -6 0. 63 (1. 25 – 0. 43 – 0. 63/2) = (W/L)n -30 x 10 -6 x -1. 0 x (1. 25 – 0. 4 – 1. 0/2) = 3. 5 (W/L)p = 3. 5 x 1. 5 = 5. 25 for a VM of 1. 25 V 2102 -545 Digital ICs CMOS Inverter 19

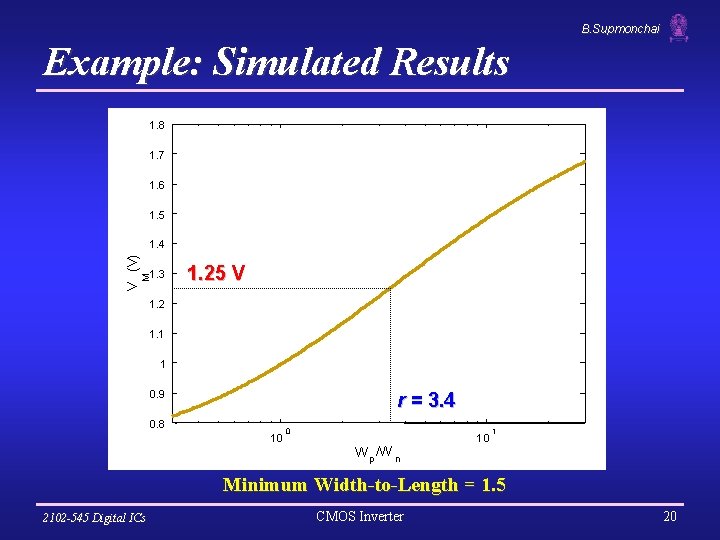

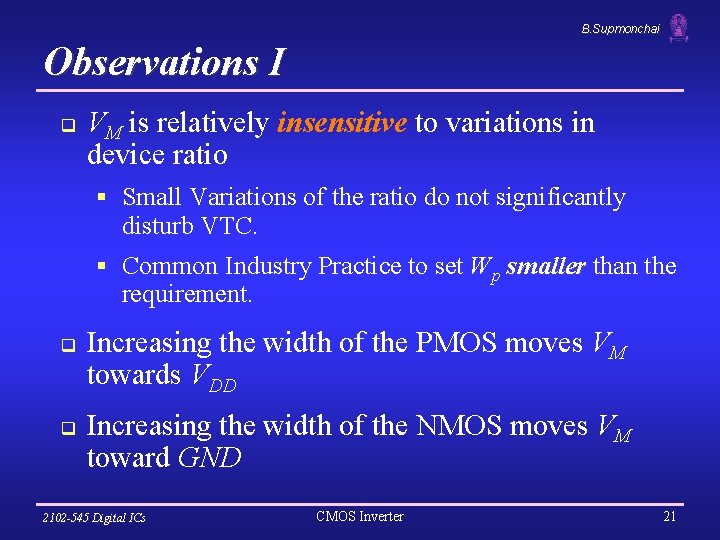

B. Supmonchai Example: Simulated Results 1. 8 1. 7 1. 6 1. 5 1. 3 M V (V) 1. 4 1. 25 V 1. 2 1. 1 1 0. 9 r = 3. 4 0. 8 10 0 10 1 W p /W n Minimum Width-to-Length = 1. 5 2102 -545 Digital ICs CMOS Inverter 20

B. Supmonchai Observations I q VM is relatively insensitive to variations in device ratio § Small Variations of the ratio do not significantly disturb VTC. § Common Industry Practice to set Wp smaller than the requirement. q q Increasing the width of the PMOS moves VM towards VDD Increasing the width of the NMOS moves VM toward GND 2102 -545 Digital ICs CMOS Inverter 21

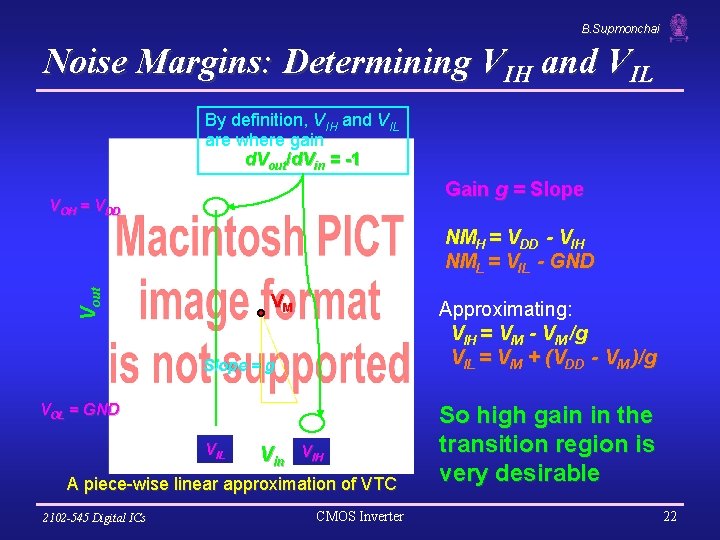

B. Supmonchai Noise Margins: Determining VIH and VIL By definition, VIH and VIL are where gain d. Vout/d. Vin = -1 Gain g = Slope VOH = VDD Vout NMH = VDD - VIH NML = VIL - GND VM Approximating: VIH = VM - VM /g VIL = VM + (VDD - VM )/g Slope = g VOL = GND VIL Vin VIH A piece-wise linear approximation of VTC 2102 -545 Digital ICs CMOS Inverter So high gain in the transition region is very desirable 22

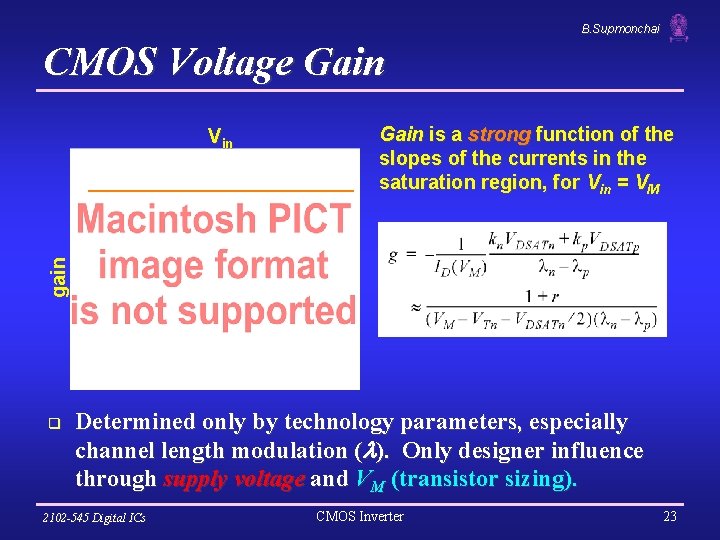

B. Supmonchai CMOS Voltage Gain is a strong function of the slopes of the currents in the saturation region, for Vin = VM gain Vin q Determined only by technology parameters, especially channel length modulation ( ). Only designer influence through supply voltage and VM (transistor sizing). 2102 -545 Digital ICs CMOS Inverter 23

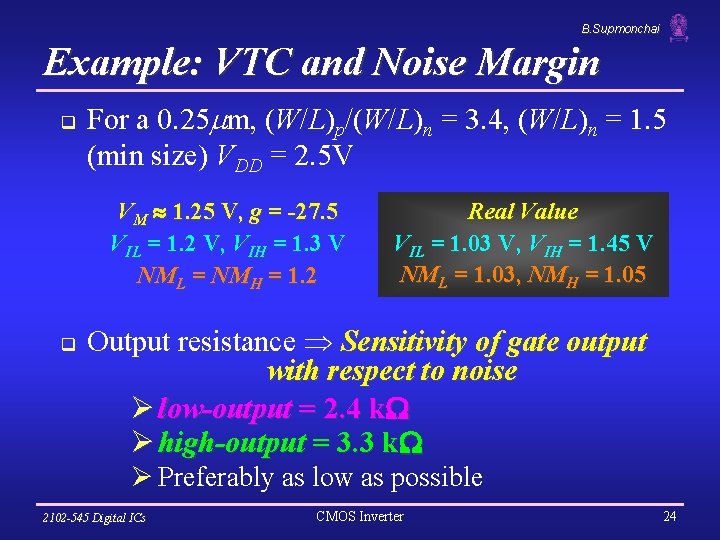

B. Supmonchai Example: VTC and Noise Margin q For a 0. 25 m, (W/L)p/(W/L)n = 3. 4, (W/L)n = 1. 5 (min size) VDD = 2. 5 V VM 1. 25 V, g = -27. 5 VIL = 1. 2 V, VIH = 1. 3 V NML = NMH = 1. 2 q Real Value VIL = 1. 03 V, VIH = 1. 45 V NML = 1. 03, NMH = 1. 05 Output resistance Sensitivity of gate output with respect to noise Ø low-output = 2. 4 k Ø high-output = 3. 3 k Ø Preferably as low as possible 2102 -545 Digital ICs CMOS Inverter 24

B. Supmonchai Observations II q First-Order Analysis overestimates the gain § Max. gain only 17 at VM VIL = 1. 17 V, VIH = 1. 33 V q Piecewise Linear Approximation is too overly optimistic § Major contributor to deviation from the true gain q CMOS inverter is a poor analog amplifier! § One of the major differences between analog and digital designs is that digital circuits operate in the regions of extreme nonlinearity Ø Well-defined and well-separated high and low signals 2102 -545 Digital ICs CMOS Inverter 25

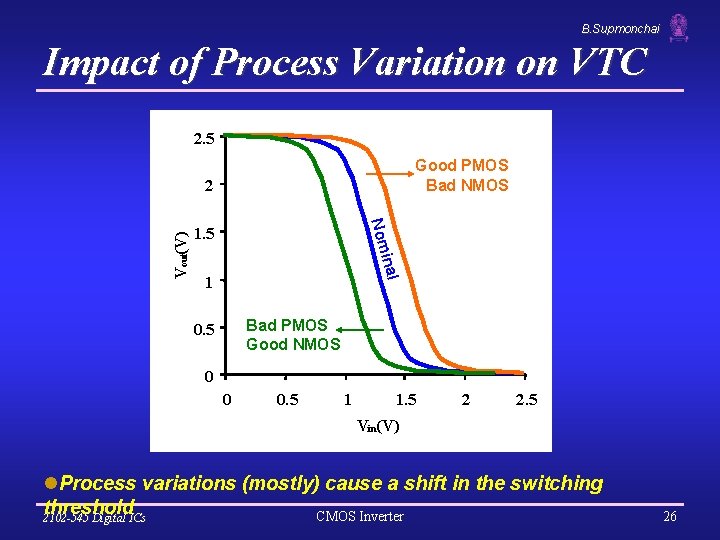

B. Supmonchai Impact of Process Variation on VTC 2. 5 Good PMOS Bad NMOS Nom 1. 5 inal Vout(V) 2 1 Bad PMOS Good NMOS 0. 5 0 0 0. 5 1 1. 5 2 2. 5 Vin(V) l. Process variations (mostly) cause a shift in the switching threshold CMOS Inverter 2102 -545 Digital ICs 26

B. Supmonchai Scaling the Supply Voltage Gain=-1 Reducing VDD improves Gain… But it deteriorates for very low VDD Practical Lower Bound: VDDmin > 2 to 4 kt /q 2102 -545 Digital ICs CMOS Inverter 27

B. Supmonchai Observations III q Reducing the supply voltage has a positive impact on the energy dissipation … § But is also detrimental to the delay of the gate q q DC Characteristic becomes increasingly sensitive to device variations once supply and intrinsic voltages become comparable Scaling the supply voltage = reducing the swing § Reduce internal noise (e. g. , crosstalk) § More susceptible to external noise that do not scale 2102 -545 Digital ICs CMOS Inverter 28

B. Supmonchai CMOS Inverter Dynamic Behavior q Transient behavior of the gate is determined by the time it takes to charge and discharge the load capacitance, CL, through on-transistors § Delay is a function of load capacitances and transistor on-resistances q Getting CL as small as possible is crucial to the realization of high-performance CMOS circuits § Transistor Capacitances § Wire Capacitances § Fanout q Wire Resistances also become more important. 2102 -545 Digital ICs CMOS Inverter 29

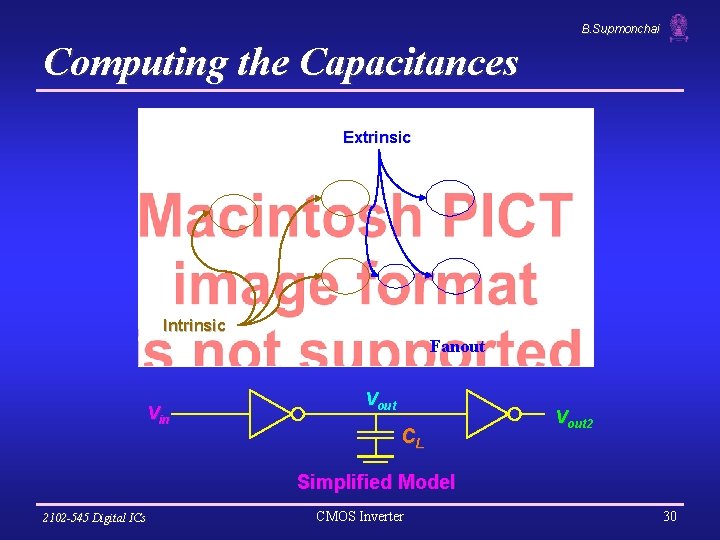

B. Supmonchai Computing the Capacitances Extrinsic Intrinsic Fanout Vin Vout CL Vout 2 Simplified Model 2102 -545 Digital ICs CMOS Inverter 30

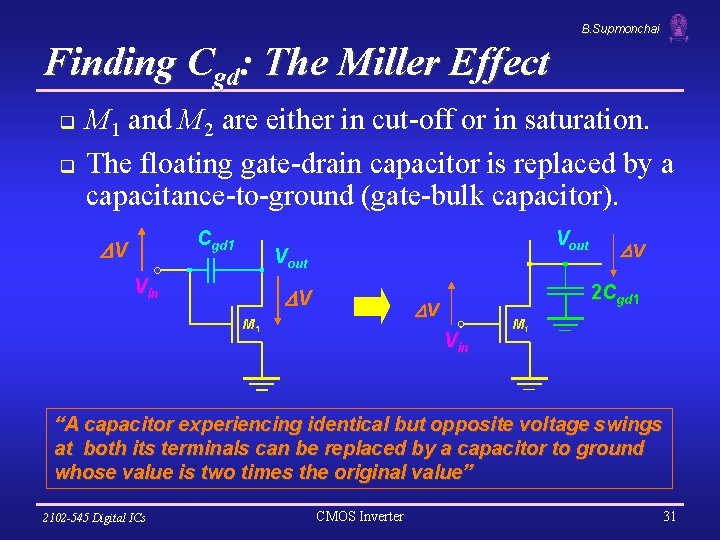

B. Supmonchai Finding Cgd: The Miller Effect q q M 1 and M 2 are either in cut-off or in saturation. The floating gate-drain capacitor is replaced by a capacitance-to-ground (gate-bulk capacitor). Cgd 1 V Vout Vin V 2 Cgd 1 V M 1 V Vin M 1 “A capacitor experiencing identical but opposite voltage swings at both its terminals can be replaced by a capacitor to ground whose value is two times the original value” 2102 -545 Digital ICs CMOS Inverter 31

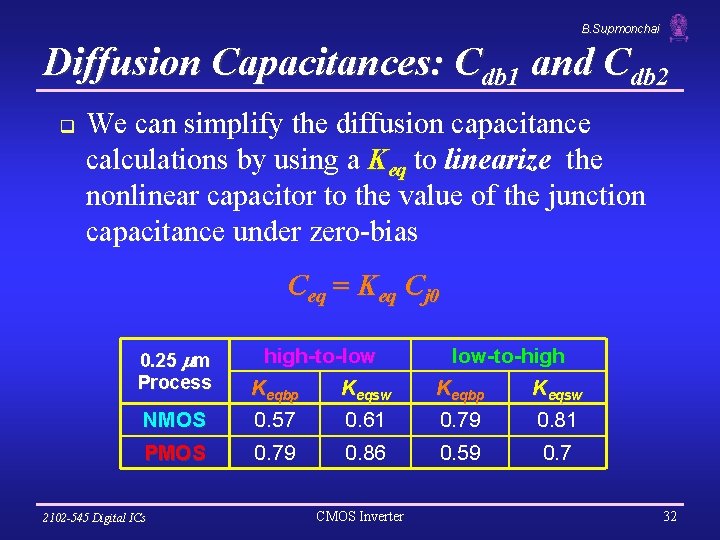

B. Supmonchai Diffusion Capacitances: Cdb 1 and Cdb 2 q We can simplify the diffusion capacitance calculations by using a Keq to linearize the nonlinear capacitor to the value of the junction capacitance under zero-bias Ceq = Keq Cj 0 0. 25 m Process high-to-low low-to-high Keqbp Keqsw NMOS 0. 57 0. 61 0. 79 0. 81 PMOS 0. 79 0. 86 0. 59 0. 7 2102 -545 Digital ICs CMOS Inverter 32

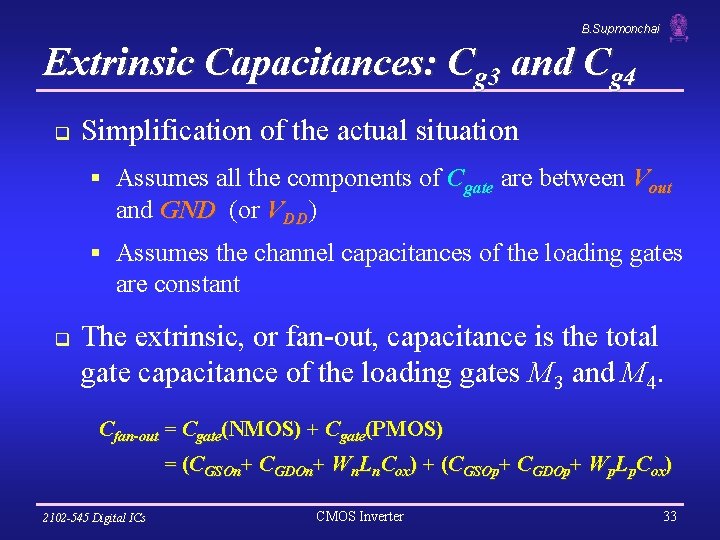

B. Supmonchai Extrinsic Capacitances: Cg 3 and Cg 4 q Simplification of the actual situation § Assumes all the components of Cgate are between Vout and GND (or VDD) § Assumes the channel capacitances of the loading gates are constant q The extrinsic, or fan-out, capacitance is the total gate capacitance of the loading gates M 3 and M 4. Cfan-out = Cgate(NMOS) + Cgate(PMOS) = (CGSOn+ CGDOn+ Wn. Ln. Cox) + (CGSOp+ CGDOp+ Wp. Lp. Cox) 2102 -545 Digital ICs CMOS Inverter 33

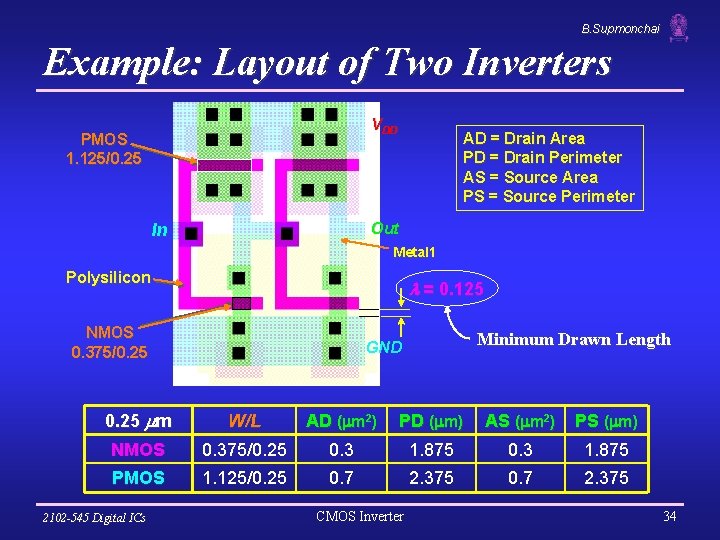

B. Supmonchai Example: Layout of Two Inverters VDD PMOS 1. 125/0. 25 AD = Drain Area PD = Drain Perimeter AS = Source Area PS = Source Perimeter Out In Metal 1 Polysilicon = 0. 125 NMOS 0. 375/0. 25 Minimum Drawn Length GND 0. 25 m W/L AD ( m 2) PD ( m) AS ( m 2) PS ( m) NMOS 0. 375/0. 25 0. 3 1. 875 PMOS 1. 125/0. 25 0. 7 2. 375 2102 -545 Digital ICs CMOS Inverter 34

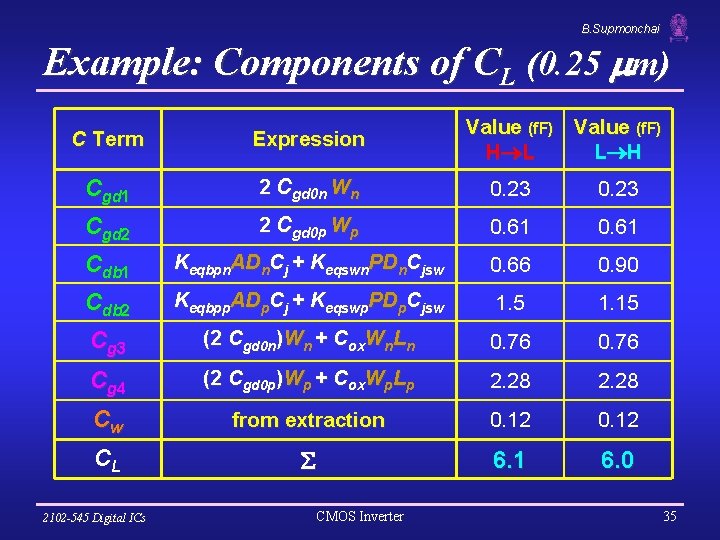

B. Supmonchai Example: Components of CL (0. 25 m) Value (f. F) H L L H C Term Expression Cgd 1 2 Cgd 0 n Wn 0. 23 Cgd 2 2 Cgd 0 p Wp 0. 61 Cdb 1 Keqbpn. ADn. Cj + Keqswn. PDn. Cjsw 0. 66 0. 90 Cdb 2 Keqbpp. ADp. Cj + Keqswp. PDp. Cjsw 1. 5 1. 15 Cg 3 (2 Cgd 0 n)Wn + Cox. Wn. Ln 0. 76 Cg 4 (2 Cgd 0 p)Wp + Cox. Wp. Lp 2. 28 Cw from extraction 0. 12 CL 6. 1 6. 0 2102 -545 Digital ICs CMOS Inverter 35

B. Supmonchai Wiring Capacitance q q The wiring capacitance depends upon the length and width of the connecting wires and is a function of the fan-out from the driving gate and the number of fan-out gates. Wiring capacitance is growing in importance with the scaling of technology. 2102 -545 Digital ICs CMOS Inverter 36

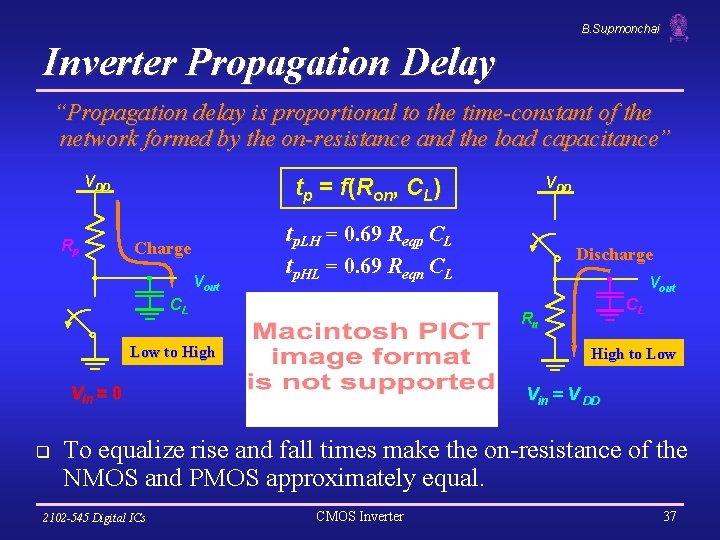

B. Supmonchai Inverter Propagation Delay “Propagation delay is proportional to the time-constant of the network formed by the on-resistance and the load capacitance” VDD Rp tp = f(Ron, CL) Charge Vout tp. LH = 0. 69 Reqp CL tp. HL = 0. 69 Reqn CL CL Discharge Vout CL Rn Low to High to Low Vin = 0 q VDD Vin = V DD To equalize rise and fall times make the on-resistance of the NMOS and PMOS approximately equal. 2102 -545 Digital ICs CMOS Inverter 37

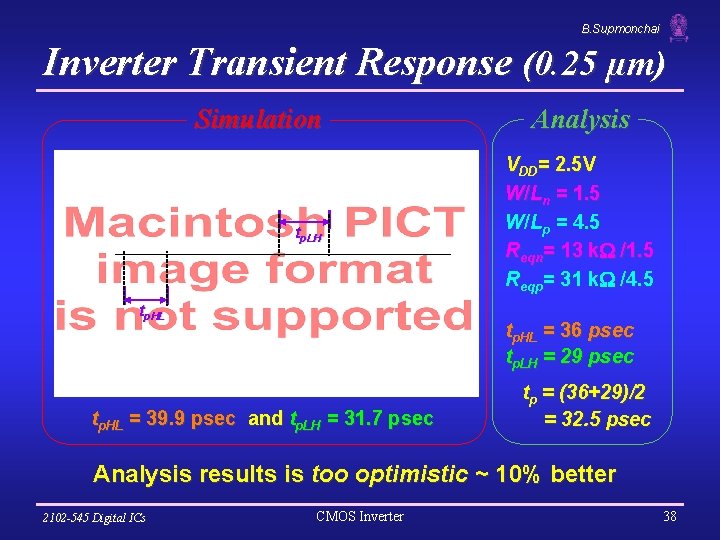

B. Supmonchai Inverter Transient Response (0. 25 µm) Simulation tp. LH tp. HL Analysis VDD= 2. 5 V W/Ln = 1. 5 W/Lp = 4. 5 Reqn= 13 k /1. 5 Reqp= 31 k /4. 5 tp. HL = 36 psec tp. LH = 29 psec tp. HL = 39. 9 psec and tp. LH = 31. 7 psec tp = (36+29)/2 = 32. 5 psec Analysis results is too optimistic ~ 10% better 2102 -545 Digital ICs CMOS Inverter 38

B. Supmonchai Inverter Propagation Delay, Revisited q To see how a designer can optimize the delay of a gate, we have to expand Req in the delay equation. tp. HL = 0. 69 Reqn CL = 0. 69(3 CVDD)/(4 IDSATn) 2102 -545 Digital ICs CMOS Inverter 39

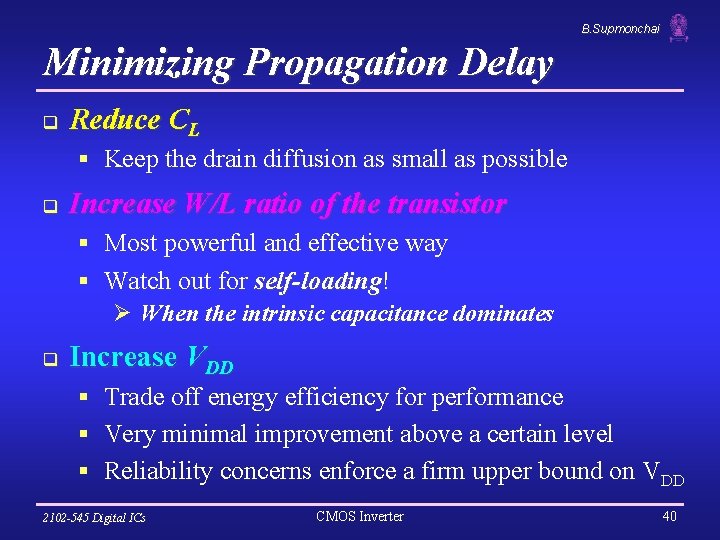

B. Supmonchai Minimizing Propagation Delay q Reduce CL § Keep the drain diffusion as small as possible q Increase W/L ratio of the transistor § Most powerful and effective way § Watch out for self-loading! self-loading Ø When the intrinsic capacitance dominates q Increase VDD § Trade off energy efficiency for performance § Very minimal improvement above a certain level § Reliability concerns enforce a firm upper bound on VDD 2102 -545 Digital ICs CMOS Inverter 40

B. Supmonchai PMOS-to-NMOS Ratio q So far PMOS and NMOS have been sized such that their Req’s match (ratio of 3 to 3. 5) § symmetrical VTC § equal high-to-low and low-to-high propagation delays q If speed is the only concern, reduce the width of the PMOS device! § widening the PMOS degrades the tp. HL due to larger parasitic capacitance = (W/L)p/(W/L)n r = Reqp/Reqn resistance ratio of identically-sized PMOS and NMOS 2102 -545 Digital ICs CMOS Inverter 41

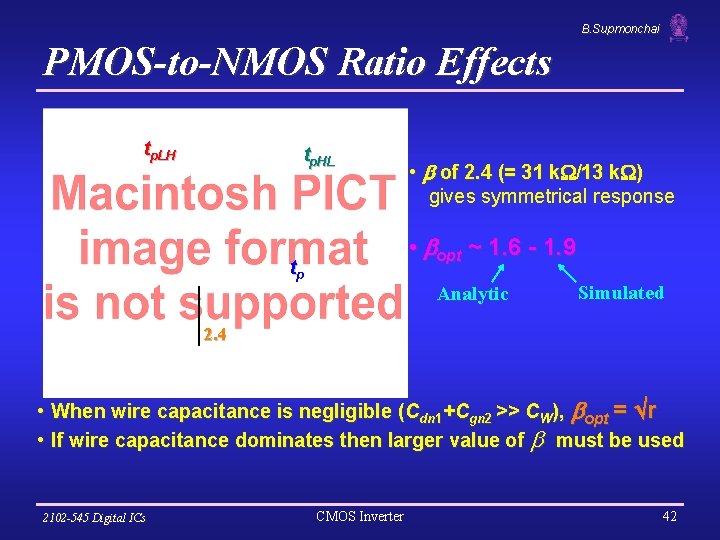

B. Supmonchai PMOS-to-NMOS Ratio Effects tp. LH tp. HL • of 2. 4 (= 31 k /13 k ) gives symmetrical response • opt ~ 1. 6 - 1. 9 tp Analytic Simulated 2. 4 • When wire capacitance is negligible (Cdn 1+Cgn 2 >> CW), opt = r • If wire capacitance dominates then larger value of must be used 2102 -545 Digital ICs CMOS Inverter 42

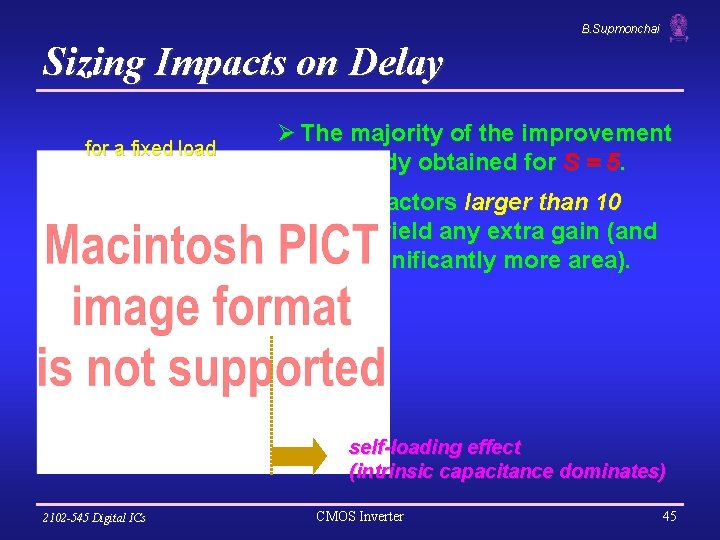

B. Supmonchai Device Sizing for Performance q Divide capacitive load, CL, into § Cint : intrinsic - diffusion and Miller effect § Cext : extrinsic - wiring and fanout tp = 0. 69 Req Cint (1 + Cext/Cint) = tp 0 (1 + Cext/Cint) Ø where tp 0 = 0. 69 Req Cint is the intrinsic (unloaded) delay of the gate q Widening both PMOS and NMOS by a factor S reduces Req by an identical factor (Req = Rref/S), /S but raises the intrinsic capacitance by the same factor (Cint = SCiref) tp = 0. 69 Rref Ciref (1 + Cext/(SCiref)) = tp 0(1 + Cext/(SCiref)) 2102 -545 Digital ICs CMOS Inverter 43

B. Supmonchai Observation IV q Intrinsic Delay of the inverter tp 0 is independent of the sizing of the gate; • tp 0 can be determined purely by technology and inverter layout • With no load the increased drive strength of the gate is totally offset by the increased capacitance q Any S sufficiently larger than (Cext/Cint) would yield a much better performance gain with a substantial area increase 2102 -545 Digital ICs CMOS Inverter 44

B. Supmonchai Sizing Impacts on Delay for a fixed load Ø The majority of the improvement is already obtained for S = 5. Ø Sizing factors larger than 10 barely yield any extra gain (and cost significantly more area). self-loading effect (intrinsic capacitance dominates) 2102 -545 Digital ICs CMOS Inverter 45

B. Supmonchai Impact of Fanout on Delay q Extrinsic capacitance, Cext, is a function of the fanout of the gate § the larger the fanout, the larger the external load. q First determine the input loading effect of the inverter. Both Cg and Cint are proportional to the gate sizing, so Cint = Cg is independent of gate sizing and tp = tp 0 (1 + Cext/ Cg) = tp 0 (1 + f / ) q The delay of an inverter is a function of the ratio between its external load capacitance and its input gate capacitance: the effective fan-out f f = Cext/Cg 2102 -545 Digital ICs CMOS Inverter 46

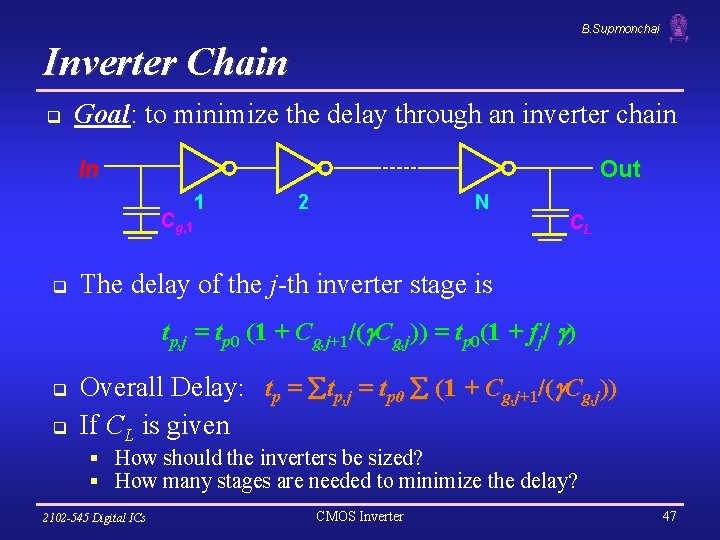

B. Supmonchai Inverter Chain q Goal: to minimize the delay through an inverter chain In Out Cg, 1 q 1 2 N CL The delay of the j-th inverter stage is tp, j = tp 0 (1 + Cg, j+1/( Cg, j)) = tp 0(1 + fj/ ) q q Overall Delay: tp = tp, j = tp 0 (1 + Cg, j+1/( Cg, j)) If CL is given § How should the inverters be sized? § How many stages are needed to minimize the delay? 2102 -545 Digital ICs CMOS Inverter 47

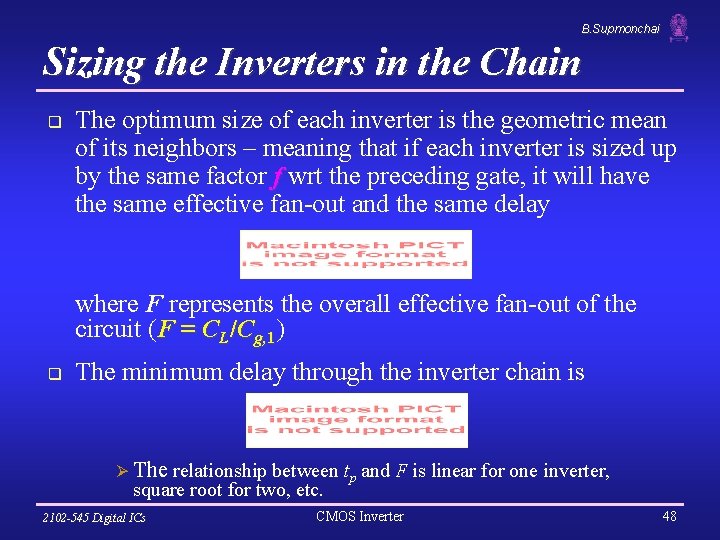

B. Supmonchai Sizing the Inverters in the Chain q The optimum size of each inverter is the geometric mean of its neighbors – meaning that if each inverter is sized up by the same factor f wrt the preceding gate, it will have the same effective fan-out and the same delay where F represents the overall effective fan-out of the circuit (F = CL/Cg, 1) q The minimum delay through the inverter chain is Ø The relationship between tp and F is linear for one inverter, square root for two, etc. 2102 -545 Digital ICs CMOS Inverter 48

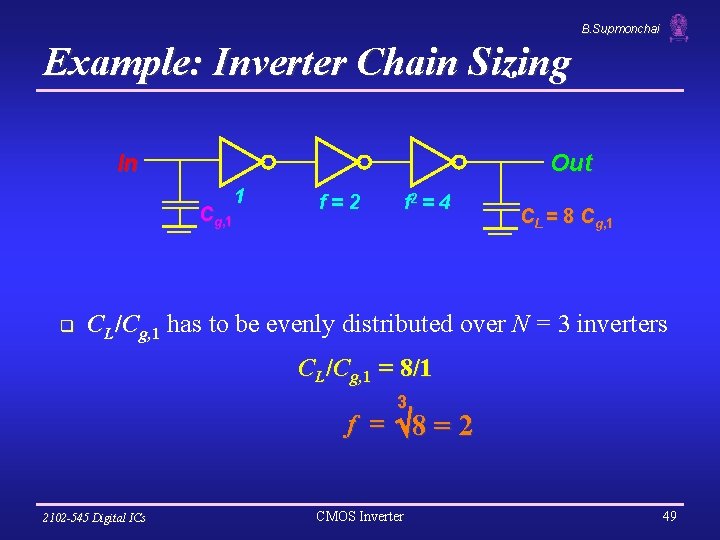

B. Supmonchai Example: Inverter Chain Sizing In Out Cg, 1 q 1 f=2 f 2 = 4 CL = 8 Cg, 1 CL/Cg, 1 has to be evenly distributed over N = 3 inverters CL/Cg, 1 = 8/1 3 f = 8 = 2 2102 -545 Digital ICs CMOS Inverter 49

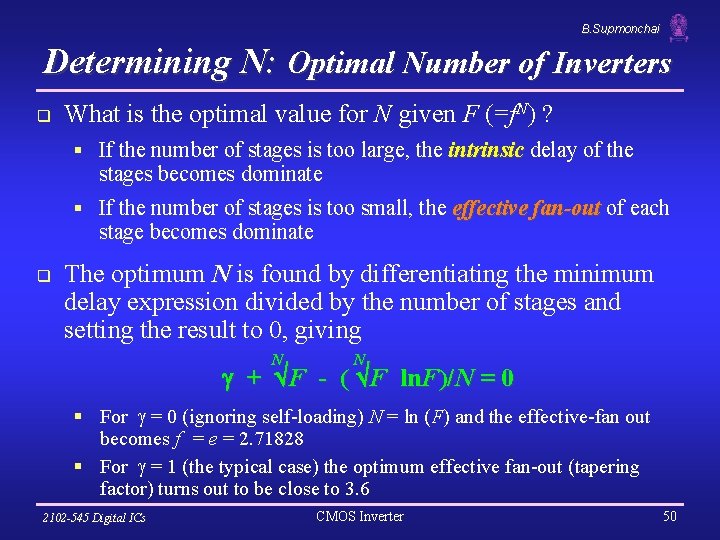

B. Supmonchai Determining N: Optimal Number of Inverters q What is the optimal value for N given F (=f. N) ? § If the number of stages is too large, the intrinsic delay of the stages becomes dominate § If the number of stages is too small, the effective fan-out of each stage becomes dominate q The optimum N is found by differentiating the minimum delay expression divided by the number of stages and setting the result to 0, giving N N + F - ( F ln. F)/N = 0 § For = 0 (ignoring self-loading) N = ln (F) and the effective-fan out becomes f = e = 2. 71828 § For = 1 (the typical case) the optimum effective fan-out (tapering factor) turns out to be close to 3. 6 2102 -545 Digital ICs CMOS Inverter 50

B. Supmonchai Optimum Effective Fan-Out q Choosing f larger than optimum has little effect on delay and reduces the number of stages (and area). § Common practice to use f = 4 (for = 1) § But too many stages has a substantial negative impact on delay 2102 -545 Digital ICs CMOS Inverter 51

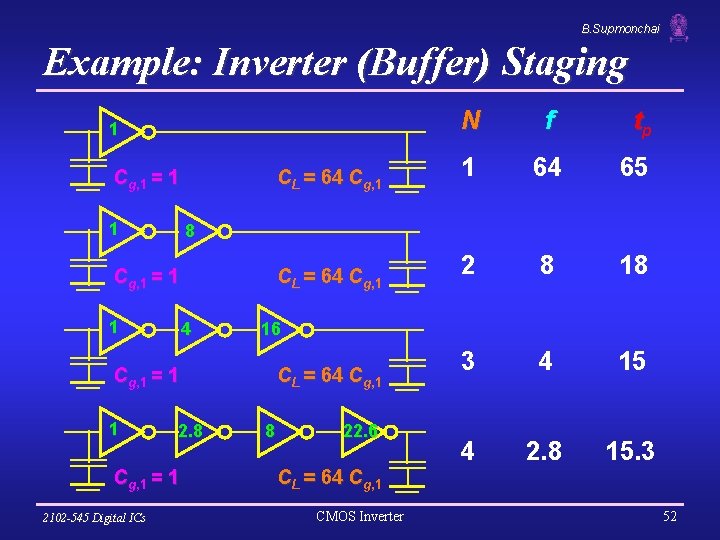

B. Supmonchai Example: Inverter (Buffer) Staging 1 Cg, 1 = 1 1 CL = 64 Cg, 1 4 tp 1 64 65 2 8 18 3 4 15 4 2. 8 15. 3 16 Cg, 1 = 1 2. 8 Cg, 1 = 1 2102 -545 Digital ICs f 8 Cg, 1 = 1 1 N CL = 64 Cg, 1 8 22. 6 CL = 64 Cg, 1 CMOS Inverter 52

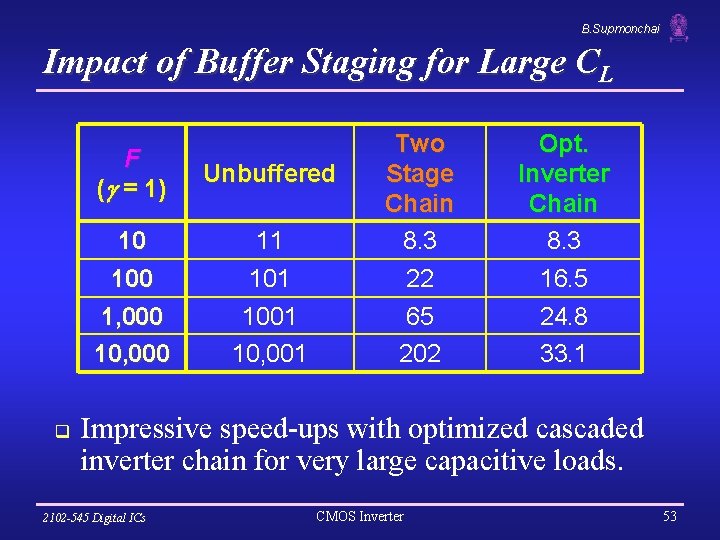

B. Supmonchai Impact of Buffer Staging for Large CL F ( = 1) 10 100 1, 000 10, 000 q 11 Two Stage Chain 8. 3 Opt. Inverter Chain 8. 3 101 22 16. 5 1001 65 24. 8 10, 001 202 33. 1 Unbuffered Impressive speed-ups with optimized cascaded inverter chain for very large capacitive loads. 2102 -545 Digital ICs CMOS Inverter 53

B. Supmonchai Input Signal Rise/Fall Time q In reality, the input signal changes gradually (and both PMOS and NMOS conduct for a brief time). This affects the current available for charging/discharging CL and impacts propagation delay. t = input signal slope ts = input signal slope ð tp increases linearly with increasing input slope, ts, once ts > tp ð ts is due to the limited driving capability of the preceding gate for a minimum-size inverter with a fan-out of a single gate 2102 -545 Digital ICs CMOS Inverter 54

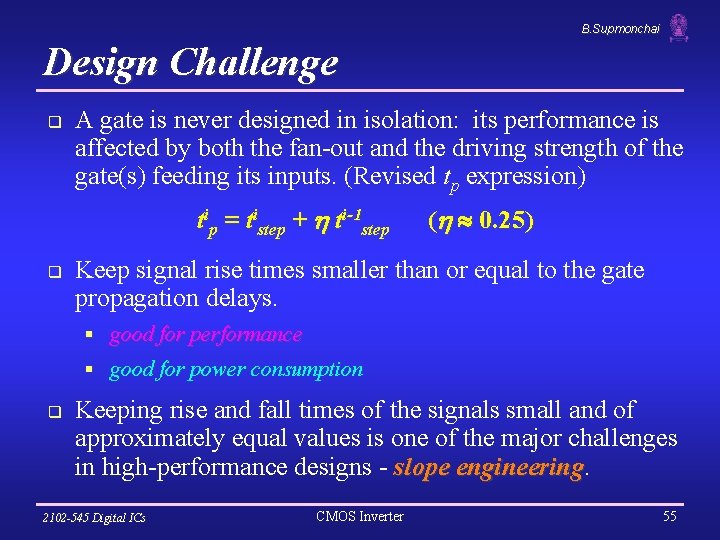

B. Supmonchai Design Challenge q A gate is never designed in isolation: its performance is affected by both the fan-out and the driving strength of the gate(s) feeding its inputs. (Revised tp expression) tip = tistep + ti-1 step q ( 0. 25) Keep signal rise times smaller than or equal to the gate propagation delays. § good for performance § good for power consumption q Keeping rise and fall times of the signals small and of approximately equal values is one of the major challenges in high-performance designs - slope engineering 2102 -545 Digital ICs CMOS Inverter 55

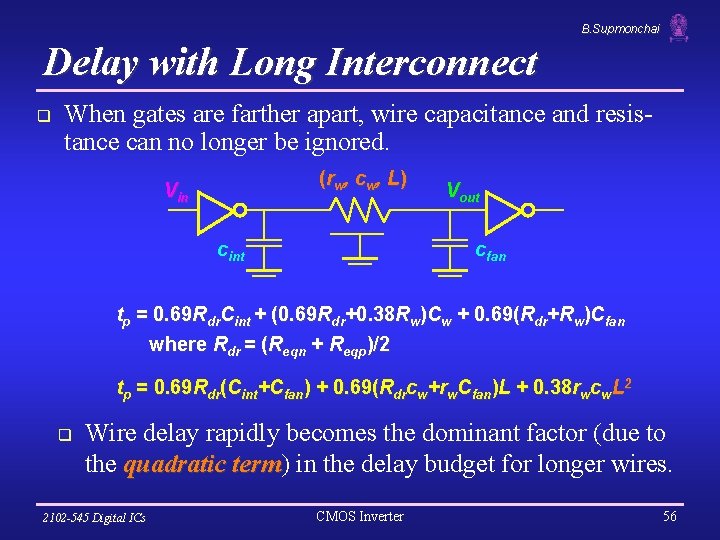

B. Supmonchai Delay with Long Interconnect q When gates are farther apart, wire capacitance and resistance can no longer be ignored. (rw, cw, L) Vin cint Vout cfan tp = 0. 69 Rdr. Cint + (0. 69 Rdr+0. 38 Rw)Cw + 0. 69(Rdr+Rw)Cfan where Rdr = (Reqn + Reqp)/2 tp = 0. 69 Rdr(Cint+Cfan) + 0. 69(Rdrcw+rw. Cfan)L + 0. 38 rwcw. L 2 q Wire delay rapidly becomes the dominant factor (due to the quadratic term) term in the delay budget for longer wires. 2102 -545 Digital ICs CMOS Inverter 56

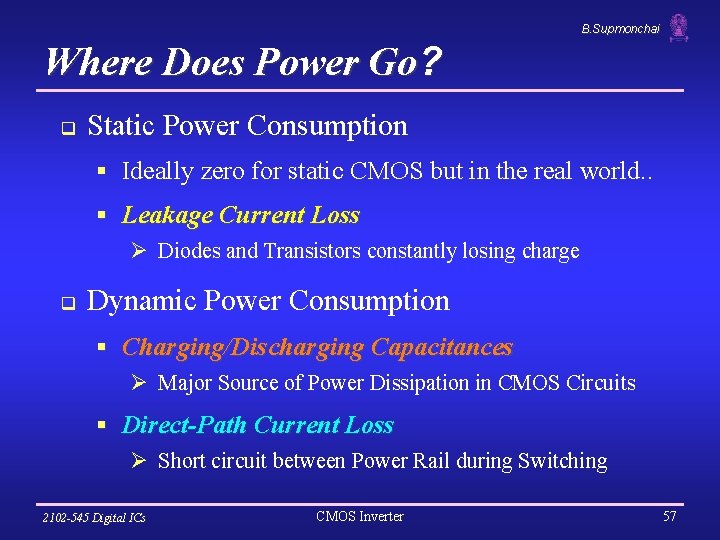

B. Supmonchai Where Does Power Go? q Static Power Consumption § Ideally zero for static CMOS but in the real world. . § Leakage Current Loss Ø Diodes and Transistors constantly losing charge q Dynamic Power Consumption § Charging/Discharging Capacitances Ø Major Source of Power Dissipation in CMOS Circuits § Direct-Path Current Loss Ø Short circuit between Power Rail during Switching 2102 -545 Digital ICs CMOS Inverter 57

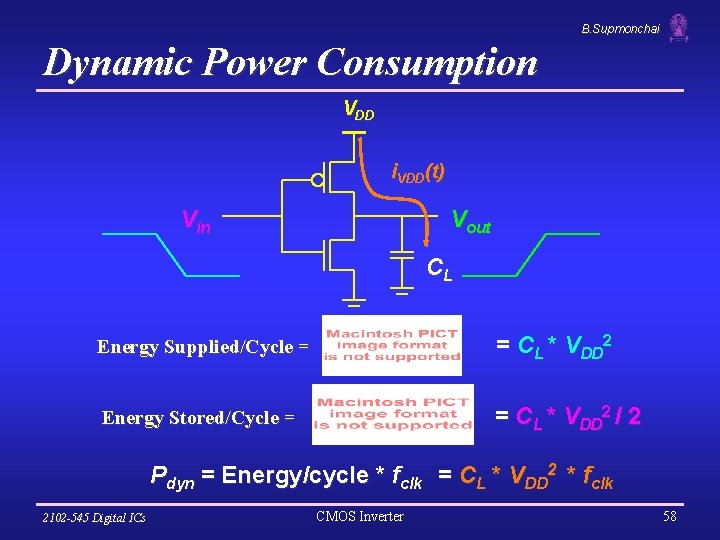

B. Supmonchai Dynamic Power Consumption VDD i. VDD(t) Vin Vout CL Energy Supplied/Cycle = = CL * VDD 2 Energy Stored/Cycle = = CL * VDD 2 / 2 Pdyn = Energy/cycle * fclk = CL * VDD 2 * fclk 2102 -545 Digital ICs CMOS Inverter 58

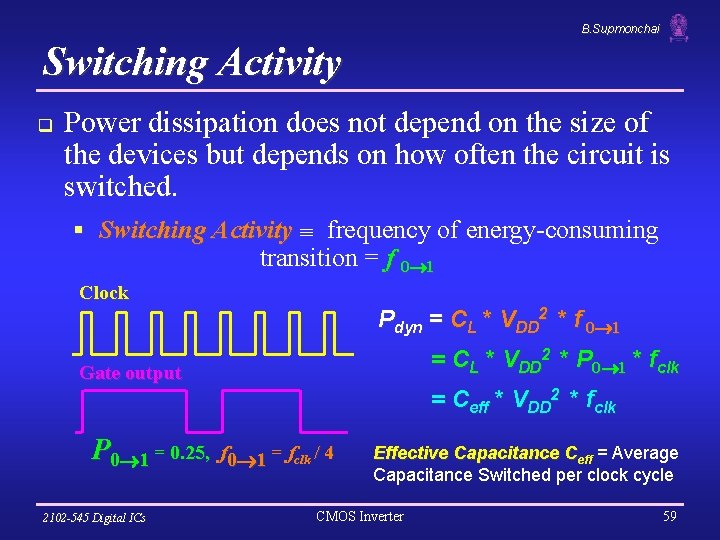

B. Supmonchai Switching Activity q Power dissipation does not depend on the size of the devices but depends on how often the circuit is switched. § Switching Activity frequency of energy-consuming transition = f 0 1 Clock Pdyn = CL * VDD 2 * f 0 1 = CL * VDD 2 * P 0 1 * fclk Gate output = Ceff * VDD 2 * fclk P 0 1 = 0. 25, 2102 -545 Digital ICs f 0 1 = fclk / 4 Effective Capacitance Ceff = Average Capacitance Switched per clock cycle CMOS Inverter 59

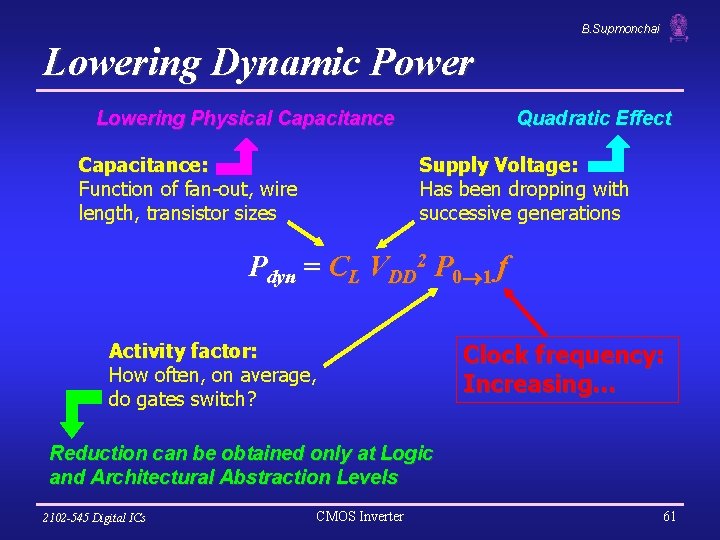

B. Supmonchai Lowering Dynamic Power Lowering Physical Capacitance: Function of fan-out, wire length, transistor sizes Quadratic Effect Supply Voltage: Has been dropping with successive generations Pdyn = CL VDD 2 P 0 1 f Activity factor: How often, on average, do gates switch? Clock frequency: Increasing… Reduction can be obtained only at Logic and Architectural Abstraction Levels 2102 -545 Digital ICs CMOS Inverter 61

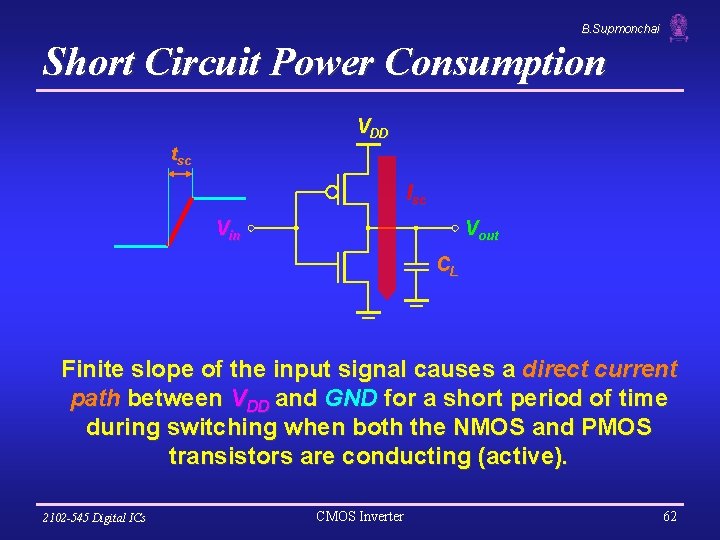

B. Supmonchai Short Circuit Power Consumption VDD tsc Isc Vin Vout CL Finite slope of the input signal causes a direct current path between VDD and GND for a short period of time during switching when both the NMOS and PMOS transistors are conducting (active). 2102 -545 Digital ICs CMOS Inverter 62

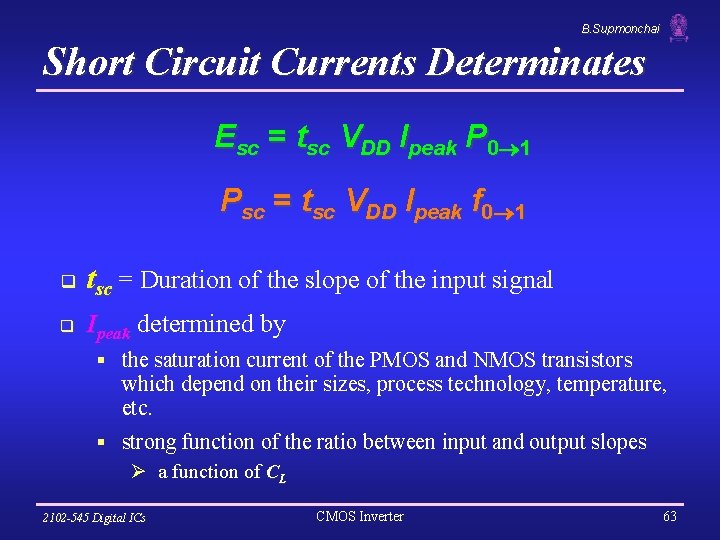

B. Supmonchai Short Circuit Currents Determinates Esc = tsc VDD Ipeak P 0 1 Psc = tsc VDD Ipeak f 0 1 t = Duration of the slope of the input signal q sc q Ipeak determined by § the saturation current of the PMOS and NMOS transistors which depend on their sizes, process technology, temperature, etc. § strong function of the ratio between input and output slopes Ø a function of CL 2102 -545 Digital ICs CMOS Inverter 63

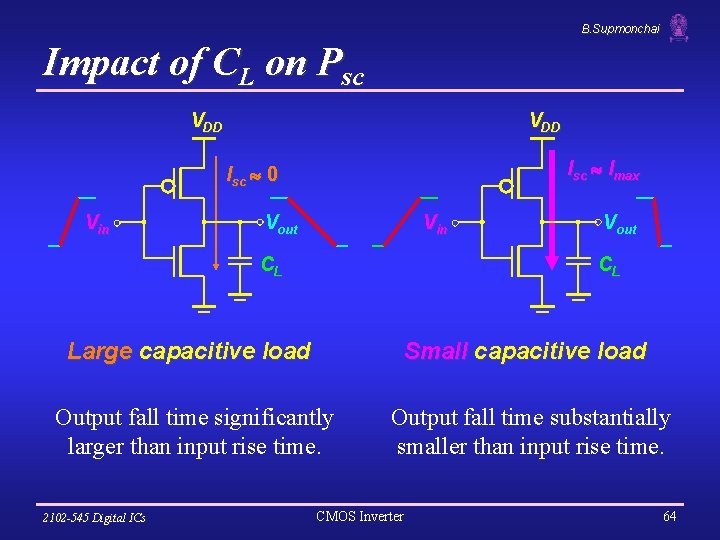

B. Supmonchai Impact of CL on Psc VDD Isc Imax Isc 0 Vin Vout Vin CL Vout CL Large capacitive load Small capacitive load Output fall time significantly larger than input rise time. Output fall time substantially smaller than input rise time. 2102 -545 Digital ICs CMOS Inverter 64

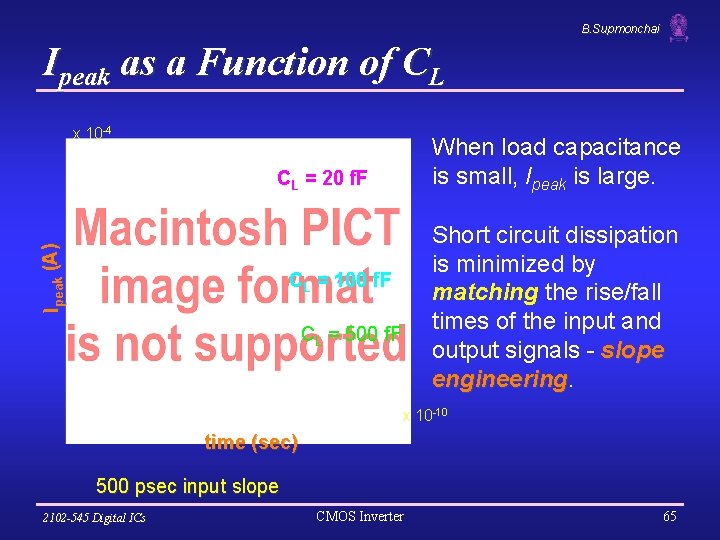

B. Supmonchai Ipeak as a Function of CL x 10 -4 When load capacitance is small, Ipeak is large. Ipeak (A) CL = 20 f. F Short circuit dissipation is minimized by matching the rise/fall times of the input and output signals - slope engineering CL = 100 f. F CL = 500 f. F x 10 -10 time (sec) 500 psec input slope 2102 -545 Digital ICs CMOS Inverter 65

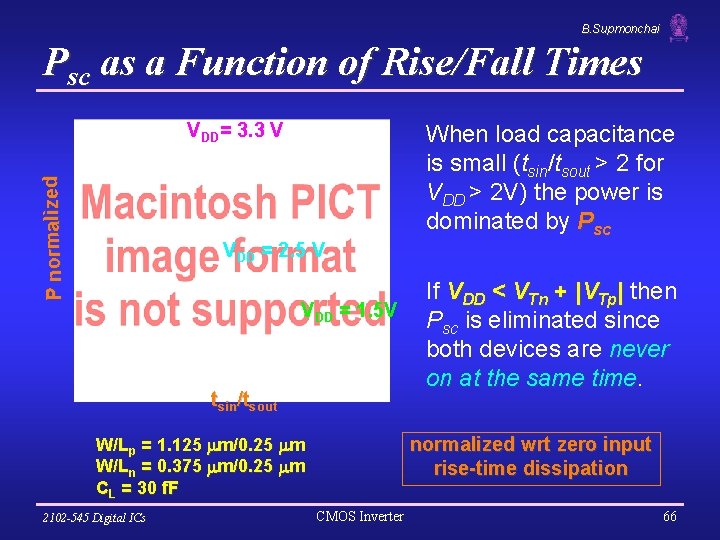

B. Supmonchai Psc as a Function of Rise/Fall Times P normalized VDD= 3. 3 V When load capacitance is small (tsin/tsout > 2 for VDD > 2 V) the power is dominated by Psc VDD = 2. 5 V VDD = 1. 5 V tsin/tsout W/Lp = 1. 125 m/0. 25 m W/Ln = 0. 375 m/0. 25 m CL = 30 f. F 2102 -545 Digital ICs If VDD < VTn + |VTp| then Psc is eliminated since both devices are never on at the same time normalized wrt zero input rise-time dissipation CMOS Inverter 66

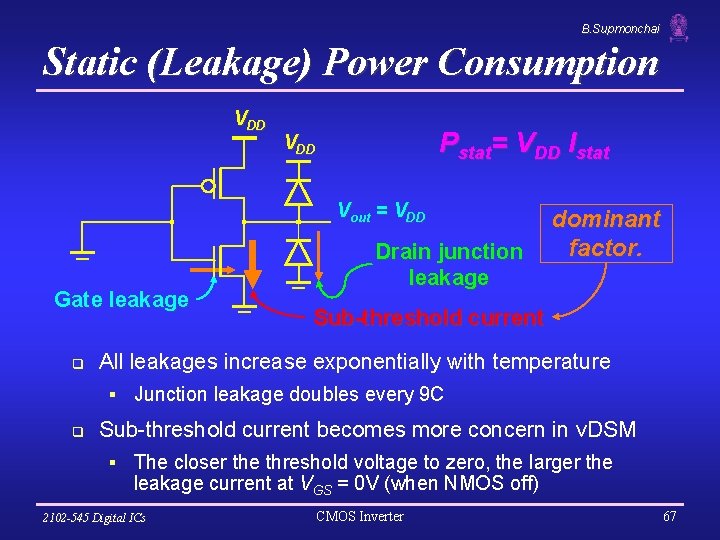

B. Supmonchai Static (Leakage) Power Consumption VDD Pstat= VDD Istat VDD Vout = VDD Gate leakage q Drain junction leakage dominant factor. Sub-threshold current All leakages increase exponentially with temperature § Junction leakage doubles every 9 C q Sub-threshold current becomes more concern in v. DSM § The closer the threshold voltage to zero, the larger the leakage current at VGS = 0 V (when NMOS off) 2102 -545 Digital ICs CMOS Inverter 67

B. Supmonchai Leakage as a Function of VT q Continued scaling of supply voltage and the subsequent scaling of threshold voltage will make sub-threshold conduction a dominant component of power dissipation. q An 90 m. V/decade VT roll-off - so each 255 m. V increase in VT gives 3 orders of magnitude reduction in leakage (but adversely affects performance) 2102 -545 Digital ICs CMOS Inverter 68

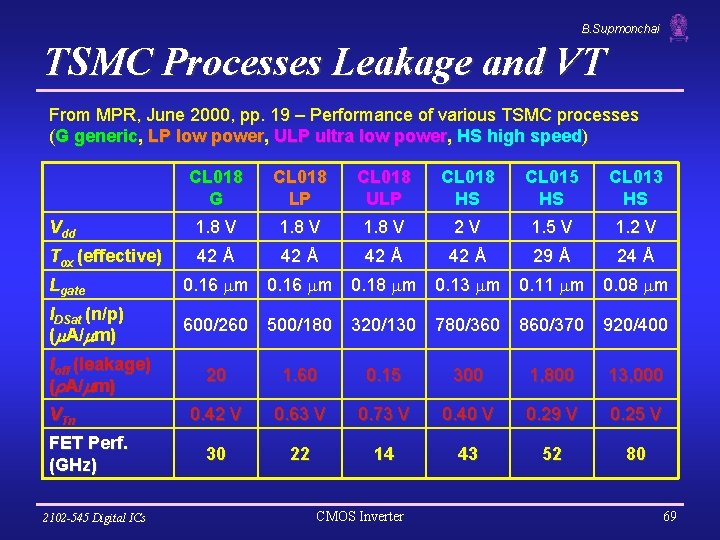

B. Supmonchai TSMC Processes Leakage and VT From MPR, June 2000, pp. 19 – Performance of various TSMC processes (G generic, LP low power, ULP ultra low power, HS high speed) CL 018 G CL 018 LP CL 018 ULP CL 018 HS CL 015 HS CL 013 HS Vdd 1. 8 V 2 V 1. 5 V 1. 2 V Tox (effective) 42 Å 29 Å 24 Å Lgate 0. 16 m 0. 18 m 0. 13 m 0. 11 m 0. 08 m IDSat (n/p) ( A/ m) 600/260 500/180 320/130 780/360 860/370 920/400 20 1. 60 0. 15 300 1, 800 13, 000 0. 42 V 0. 63 V 0. 73 V 0. 40 V 0. 29 V 0. 25 V 30 22 14 43 52 80 Ioff (leakage) ( A/ m) VTn FET Perf. (GHz) 2102 -545 Digital ICs CMOS Inverter 69

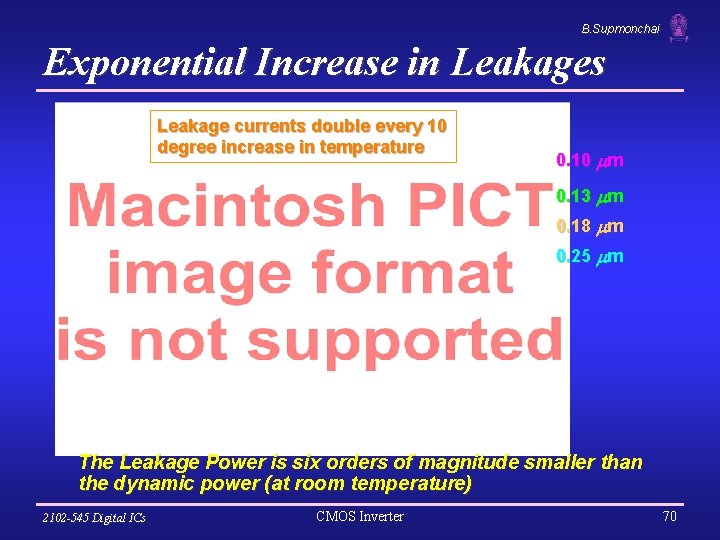

B. Supmonchai Exponential Increase in Leakages Leakage currents double every 10 degree increase in temperature 0. 10 m 0. 13 m 0. 18 m 0. 25 m The Leakage Power is six orders of magnitude smaller than the dynamic power (at room temperature) 2102 -545 Digital ICs CMOS Inverter 70

B. Supmonchai Energy and Power Equations E = CL VDD 2 P 0 1 + tsc VDD Ipeak P 0 1 + VDD Ileakage. Tclock f 0 1 = P 0 1 * fclock P = CL VDD 2 f 0 1 + tsc VDD Ipeak f 0 1 + VDD Ileakage Dynamic power (~90% today and decreasing relatively) 2102 -545 Digital ICs Short-circuit power (~8% today and decreasing absolutely) CMOS Inverter Leakage power (~2% today and increasing) 71

B. Supmonchai Sizing for Minimum Energy q Goal: Minimize Energy of the whole circuit § Design parameters: f and VDD § tp tpref of circuit with f = 1 and VDD = Vref Overall Effective Fan-out F = Cext/Cg 1 2102 -545 Digital ICs Intrinsic Delay of the inverter tp 0 ~ VDDt/(VDDt - VTE) CMOS Inverter 72

B. Supmonchai Sizing for Minimum Energy II q Performance Constraint ( =1) q Energy for single Transition 2102 -545 Digital ICs CMOS Inverter 73

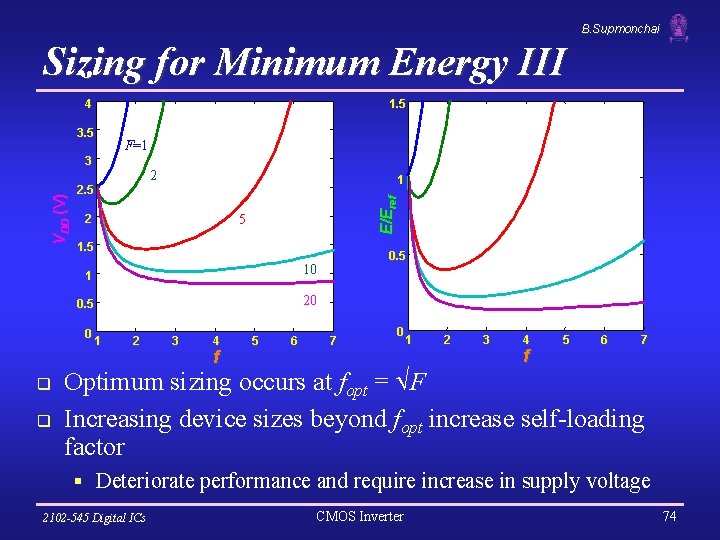

B. Supmonchai Sizing for Minimum Energy III 1. 5 4 3. 5 F=1 2 1 2. 5 E/Eref VDD (V) 3 5 2 1. 5 1 20 0. 5 0 q q 0. 5 10 1 2 3 4 f 5 6 7 Optimum sizing occurs at fopt = F Increasing device sizes beyond fopt increase self-loading factor § Deteriorate performance and require increase in supply voltage 2102 -545 Digital ICs CMOS Inverter 74

B. Supmonchai Observation V q Device sizing, combined with supply voltage reduction, is very effective in reducing the energy consumption § For F = 1, minimum size device is the most effective § For network with large effective fan-out (F >> 1), a large reduction factor of almost 10 can be obtained. q Oversizing transistors beyond the optimal value results in a hefty increase of energy § Unfortunately, a common approach in many today’s design q Optimal sizing factor for energy is smaller than the one for performance (delay), especially for large F § For a fan-out of 20, fopt(energy) = 3. 53, fopt(delay) = 4. 47 2102 -545 Digital ICs CMOS Inverter 75

B. Supmonchai Power-Delay and Energy-Delay Product q Power-delay product (PDP) = Pav * tp = (CLVDD 2)/2 § PDP is the average energy consumed per switching event (Watts * sec = Joule) § Lower power design could simply be a slower design q Energy-delay product (EDP) = PDP * tp = Pav * tp 2 § EDP is the average energy consumed multiplied by the computation time required § Takes into account that one can trade increased delay for lower energy/operation (e. g. , via supply voltage scaling that increases delay, but decreases energy consumption) 2102 -545 Digital ICs CMOS Inverter 76

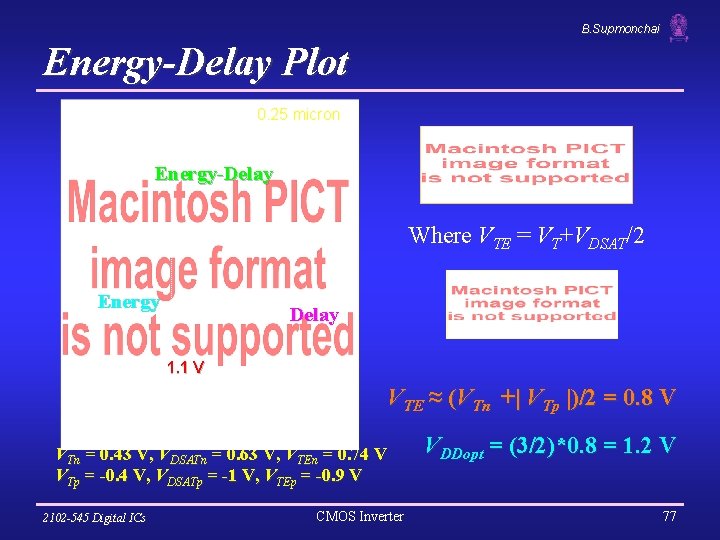

B. Supmonchai Energy-Delay Plot 0. 25 micron Energy-Delay Where VTE = VT+VDSAT/2 Energy Delay 1. 1 V VTE ≈ (VTn +| VTp |)/2 = 0. 8 V VTn = 0. 43 V, VDSATn = 0. 63 V, VTEn = 0. 74 V VTp = -0. 4 V, VDSATp = -1 V, VTEp = -0. 9 V 2102 -545 Digital ICs CMOS Inverter VDDopt = (3/2)*0. 8 = 1. 2 V 77

B. Supmonchai Observation VI q Voltage Dependence of the EDP § Higher Supply Voltages reduce delay, but harm the energy. § Vice Versa for low voltages q VDDopt simultaneously optimizes performance (delay) and energy § For submicron technologies with VT in the range of 0. 5 V, VDDopt ~ 1 V. q VDDopt does not necessarily represent the optimum voltage for a given design problem § Goal of the design (speed or power) determinates the supply voltage 2102 -545 Digital ICs CMOS Inverter 78

B. Supmonchai Goals of Technology Scaling q Make things cheaper: § Want to sell more functions (transistors) per chip for the same money § Build same products cheaper, sell the same part for less money § Price per transistor has to be reduced q But also want to be faster, smaller, lower power 2102 -545 Digital ICs CMOS Inverter 79

B. Supmonchai Technology Scaling q Goals of scaling the dimensions by 30%: § Reduce gate delay by 30% (increase operating frequency by 43%) § Double transistor density § Reduce energy per transition by 65% (50% power savings @ 43% increase in frequency q Die size used to increase by 14% per generation q Technology generation spans 2 -3 years 2102 -545 Digital ICs CMOS Inverter 80

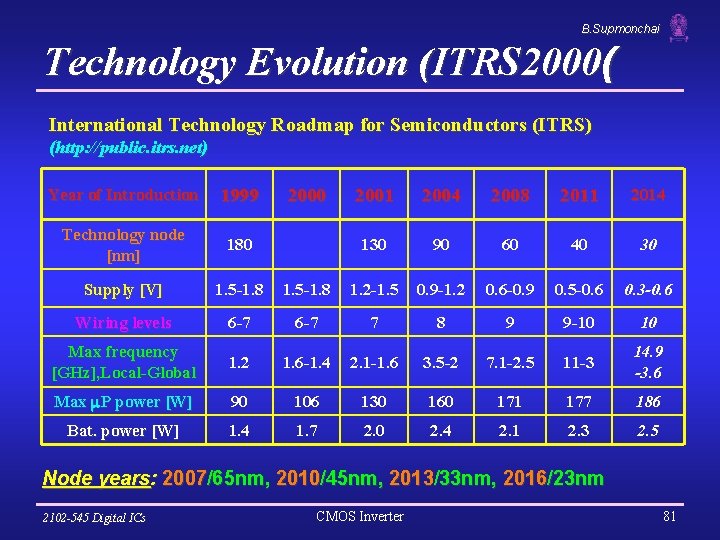

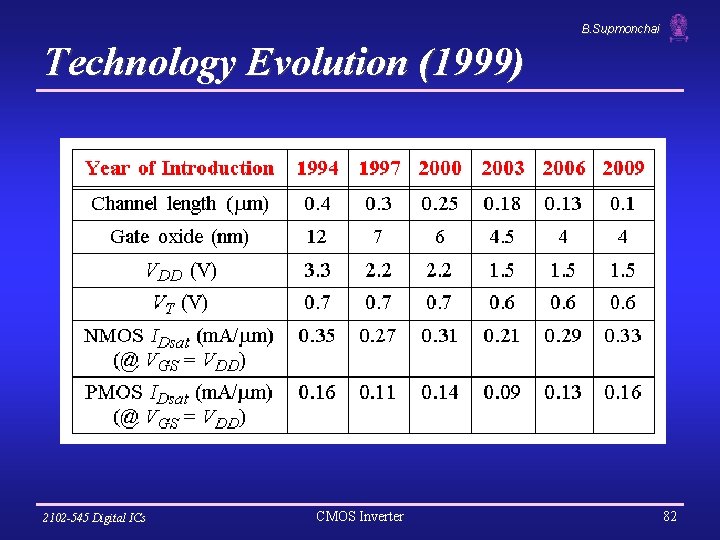

B. Supmonchai Technology Evolution (ITRS 2000( International Technology Roadmap for Semiconductors (ITRS) (http: //public. itrs. net) Year of Introduction 1999 Technology node [nm] 180 Supply [V] 1. 5 -1. 8 Wiring levels 2000 2001 2004 2008 2011 2014 130 90 60 40 30 1. 5 -1. 8 1. 2 -1. 5 0. 9 -1. 2 0. 6 -0. 9 0. 5 -0. 6 0. 3 -0. 6 6 -7 7 8 9 9 -10 10 Max frequency [GHz], Local-Global 1. 2 1. 6 -1. 4 2. 1 -1. 6 3. 5 -2 7. 1 -2. 5 11 -3 14. 9 -3. 6 Max P power [W] 90 106 130 160 171 177 186 Bat. power [W] 1. 4 1. 7 2. 0 2. 4 2. 1 2. 3 2. 5 Node years: 2007/65 nm, 2010/45 nm, 2013/33 nm, 2016/23 nm 2102 -545 Digital ICs CMOS Inverter 81

B. Supmonchai Technology Evolution (1999) 2102 -545 Digital ICs CMOS Inverter 82

B. Supmonchai Technology Scaling Models q Full Scaling (Constant Electrical Field) § Ideal model - dimensions and voltage scale together by the same factor S q Fixed Voltage Scaling § Most common until recently § Only dimensions scale, voltages remain constant q General Scaling § Most realistic for todays situation § Voltages and dimensions scale with different factors 2102 -545 Digital ICs CMOS Inverter 83

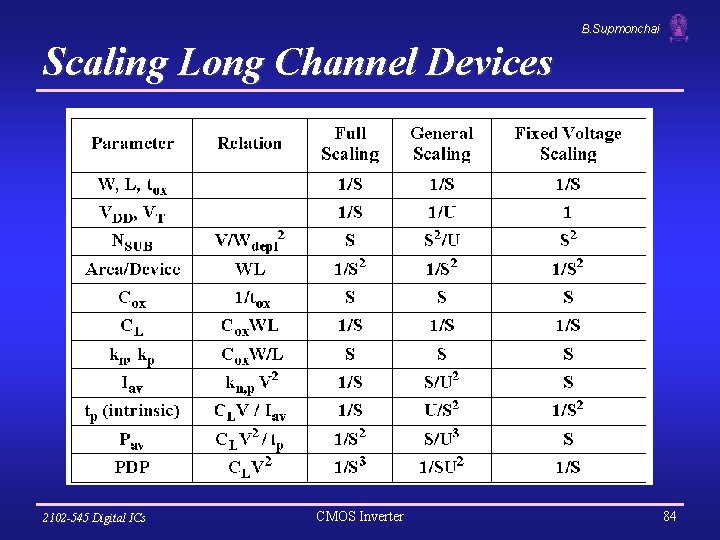

B. Supmonchai Scaling Long Channel Devices 2102 -545 Digital ICs CMOS Inverter 84

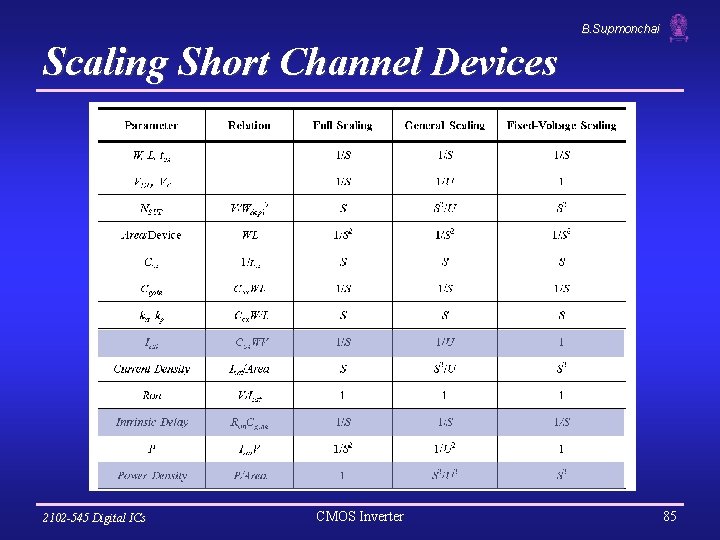

B. Supmonchai Scaling Short Channel Devices 2102 -545 Digital ICs CMOS Inverter 85

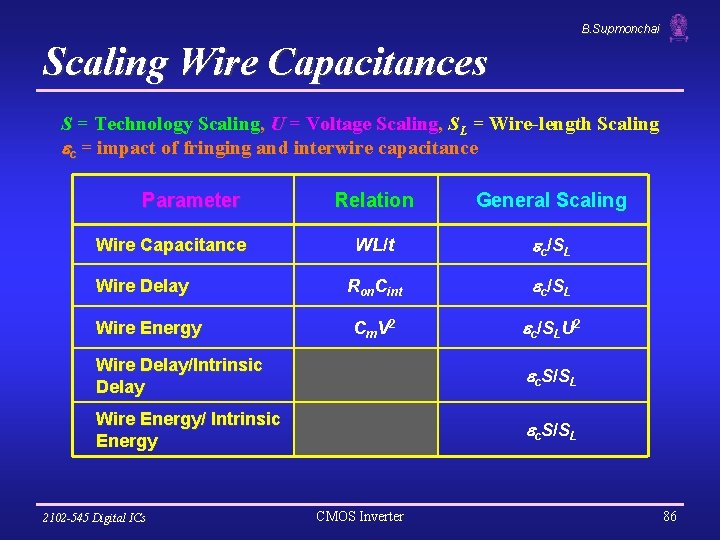

B. Supmonchai Scaling Wire Capacitances S = Technology Scaling, U = Voltage Scaling, SL = Wire-length Scaling c = impact of fringing and interwire capacitance Parameter Wire Capacitance Wire Delay Wire Energy Relation General Scaling WL/t c/SL Ron. Cint c/SL Cm V 2 c/SLU 2 Wire Delay/Intrinsic Delay c. S/SL Wire Energy/ Intrinsic Energy c. S/SL 2102 -545 Digital ICs CMOS Inverter 86

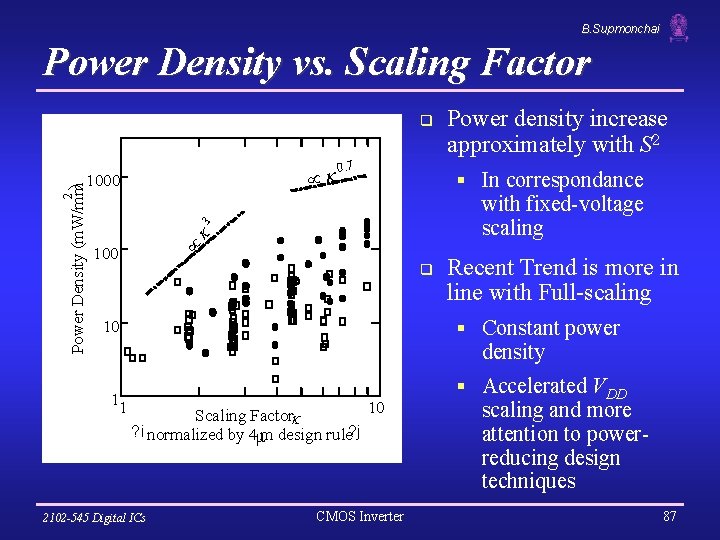

B. Supmonchai Power Density vs. Scaling Factor q µk § In correspondance with fixed-voltage scaling 2 Power Density (m. W/mm) 1000 0. 7 k 3 µ 100 Power density increase approximately with S 2 q Recent Trend is more in line with Full-scaling § Constant power 10 density 11 10 Scaling Factork ? i normalized by 4 m design rule? j 2102 -545 Digital ICs CMOS Inverter § Accelerated VDD scaling and more attention to powerreducing design techniques 87

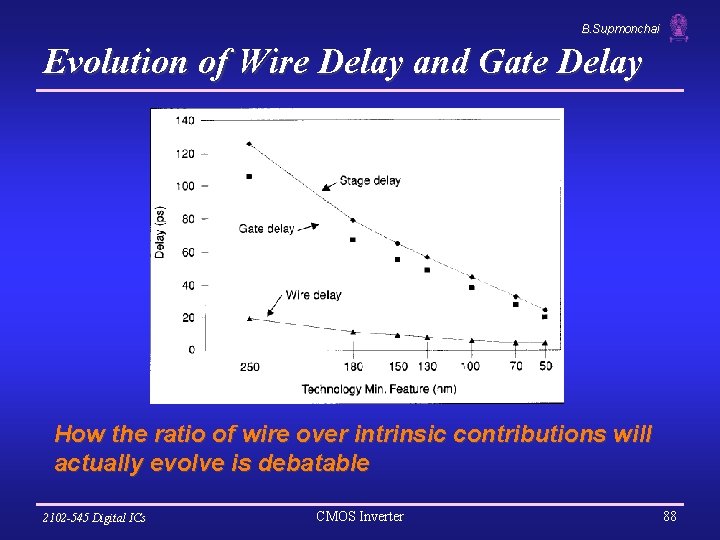

B. Supmonchai Evolution of Wire Delay and Gate Delay How the ratio of wire over intrinsic contributions will actually evolve is debatable 2102 -545 Digital ICs CMOS Inverter 88

B. Supmonchai Looking into the Future… (Year 2010) q Performance 2 X/16 months § 1 TIP (terra instructions/s) § 30 GHz clock q Size § No of transistors: 2 Billion § Die: 40*40 mm q Power § 10 k. W!! § Leakage: 1/3 active Power 2102 -545 Digital ICs CMOS Inverter 89

B. Supmonchai Some Interesting Questions q What will cause this model to break? q When will it break? q Will the model gradually slow down? § Power and power density § Leakage § Process Variation 2102 -545 Digital ICs CMOS Inverter 90

- Slides: 89