Chapter 4 Post Layout Simulation IC CAD Analog

![Cadence Layout editor Example> Inverter layout & post layout simulation [ICCAD@train##]/user 1/train##/ > mkdir Cadence Layout editor Example> Inverter layout & post layout simulation [ICCAD@train##]/user 1/train##/ > mkdir](https://slidetodoc.com/presentation_image_h2/e783871f95dbfd753f0fa8433a3da6d1/image-7.jpg)

- Slides: 20

Chapter 4. Post Layout Simulation IC CAD 실험 Analog part

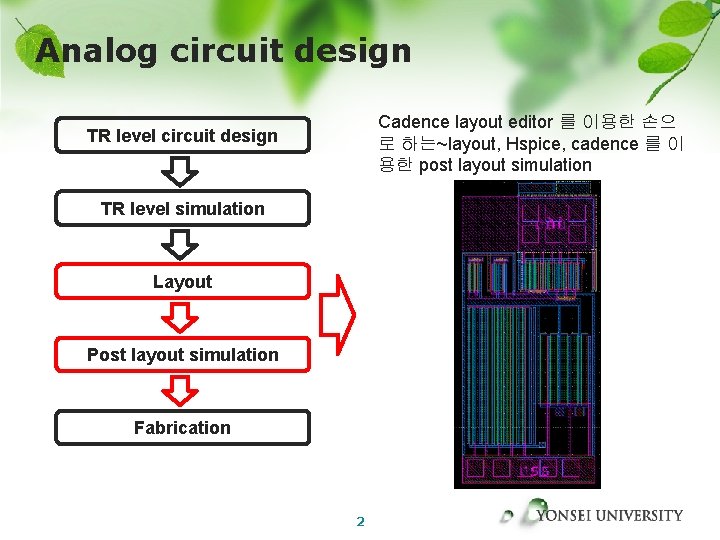

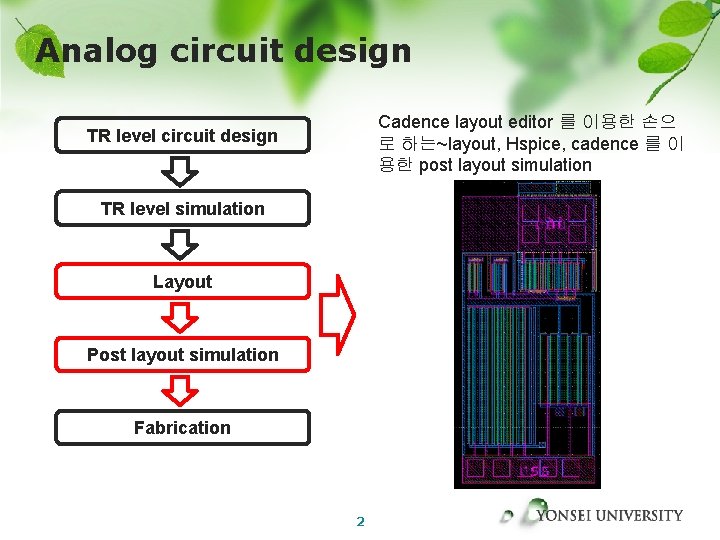

Analog circuit design Cadence layout editor 를 이용한 손으 로 하는~layout, Hspice, cadence 를 이 용한 post layout simulation TR level circuit design TR level simulation Layout Post layout simulation Fabrication 2

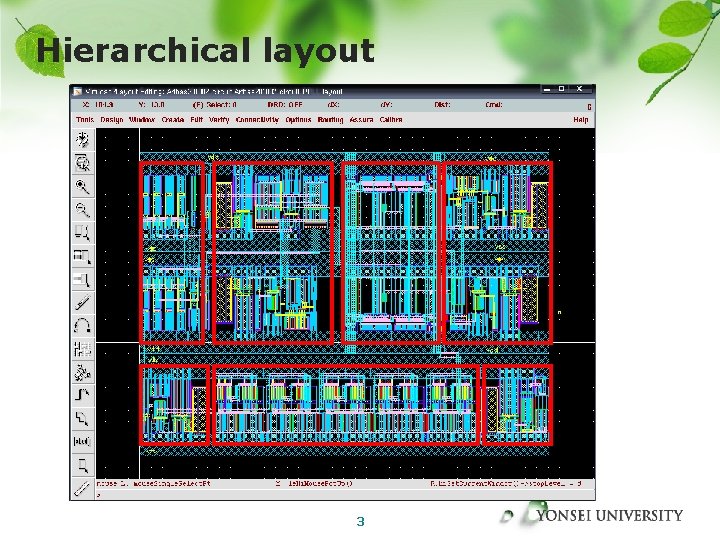

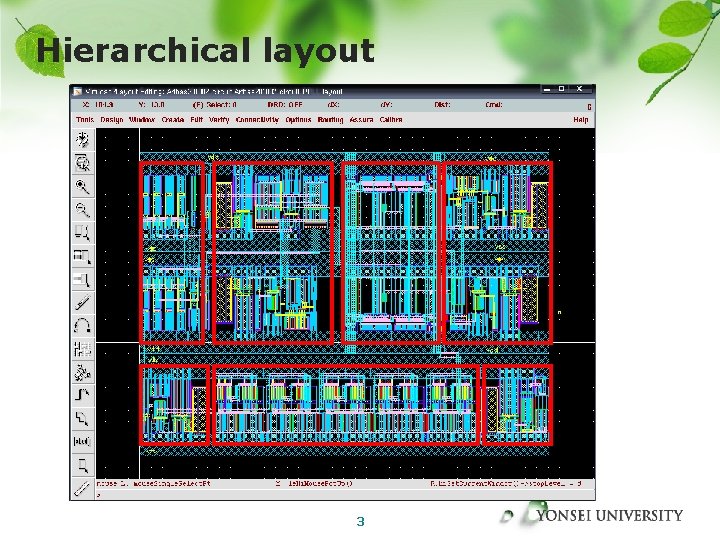

Hierarchical layout 3

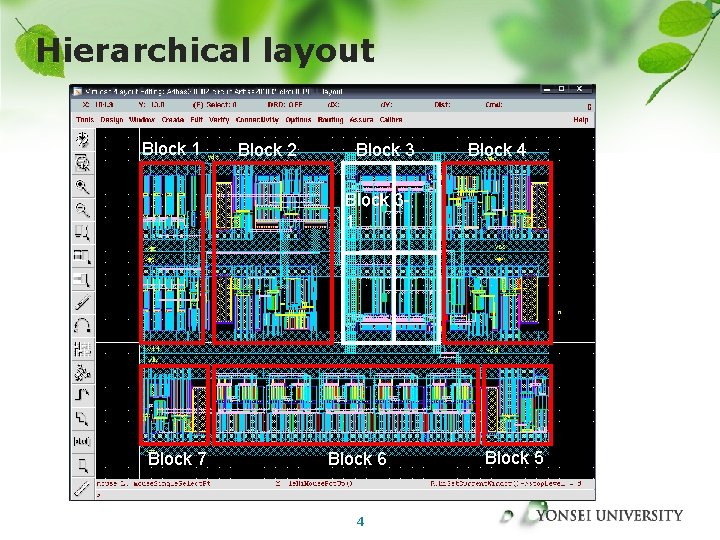

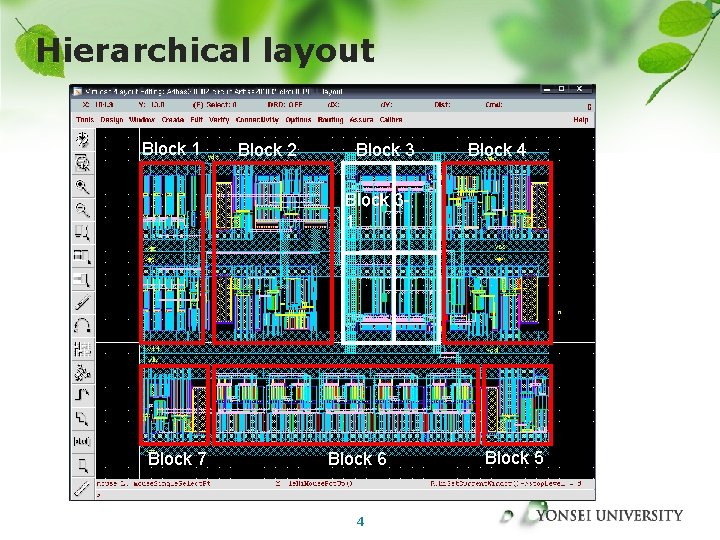

Hierarchical layout Block 1 Block 2 Block 3 Block 4 Block 31 Block 7 Block 6 4 Block 5

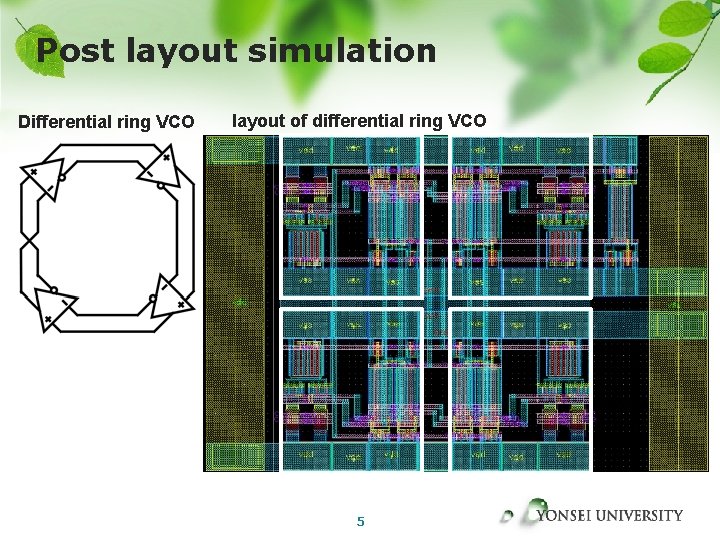

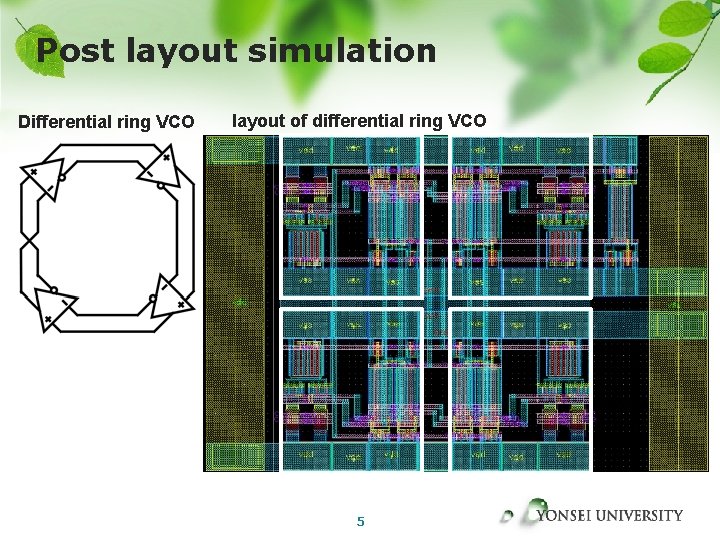

Post layout simulation Differential ring VCO layout of differential ring VCO 5

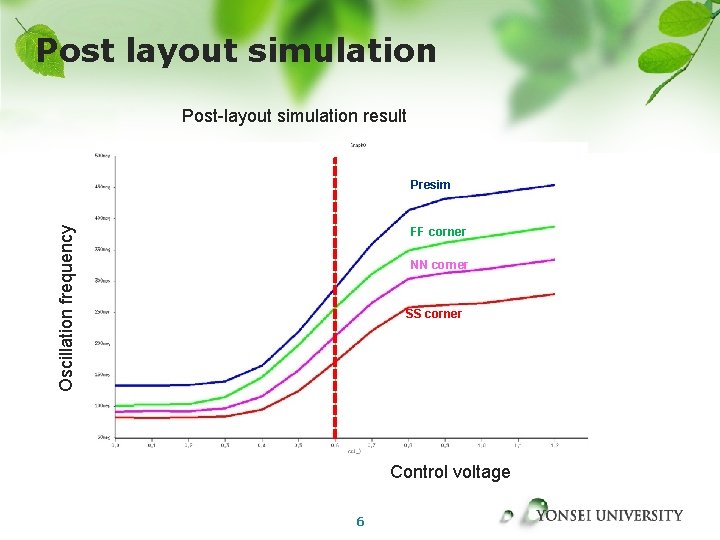

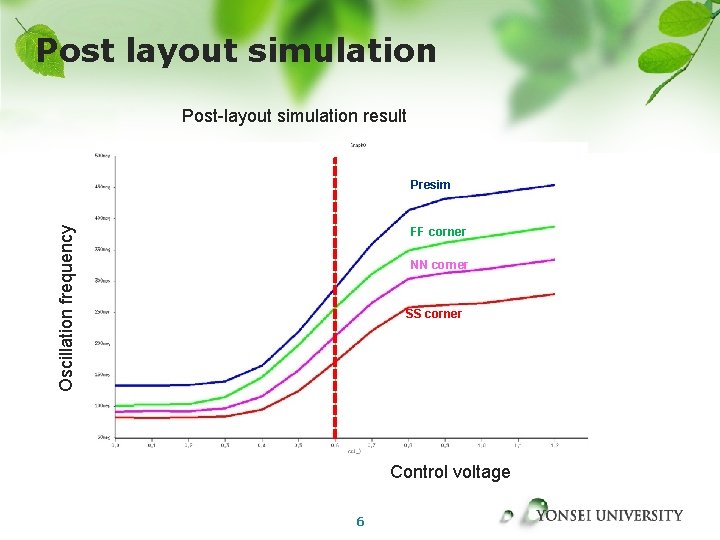

Post layout simulation Post-layout simulation result Oscillation frequency Presim FF corner NN corner SS corner Control voltage 6

![Cadence Layout editor Example Inverter layout post layout simulation ICCADtrainuser 1train mkdir Cadence Layout editor Example> Inverter layout & post layout simulation [ICCAD@train##]/user 1/train##/ > mkdir](https://slidetodoc.com/presentation_image_h2/e783871f95dbfd753f0fa8433a3da6d1/image-7.jpg)

Cadence Layout editor Example> Inverter layout & post layout simulation [ICCAD@train##]/user 1/train##/ > mkdir cadence [ICCAD@train##]/user 1/train##/ > cd cadence [ICCAD@train##]/user 1/train##/ cadence> sourceic [ICCAD@train##]/user 1/train##/ cadence> icfb & 7

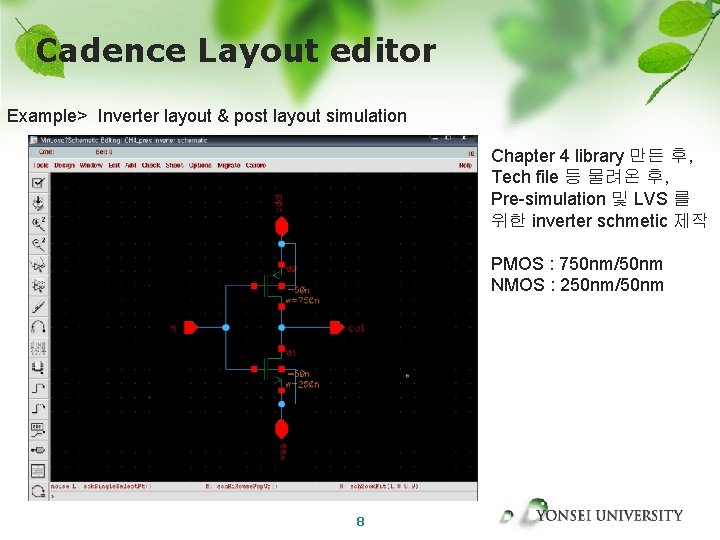

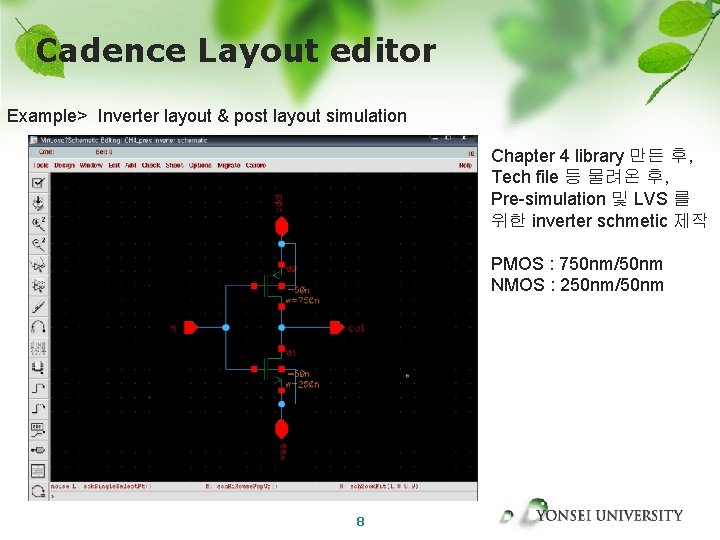

Cadence Layout editor Example> Inverter layout & post layout simulation Chapter 4 library 만든 후, Tech file 등 물려온 후, Pre-simulation 및 LVS 를 위한 inverter schmetic 제작 PMOS : 750 nm/50 nm NMOS : 250 nm/50 nm 8

Cadence Layout editor Example> Inverter layout & post layout simulation Inverter layout 을 위한 layout editor 실행 9

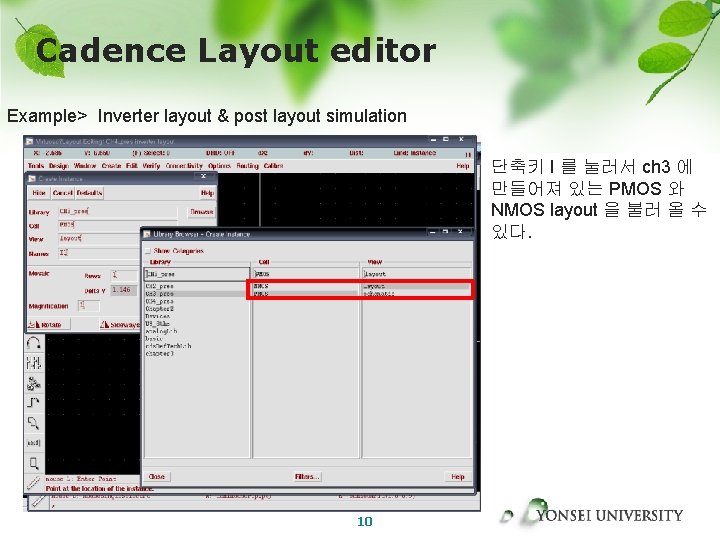

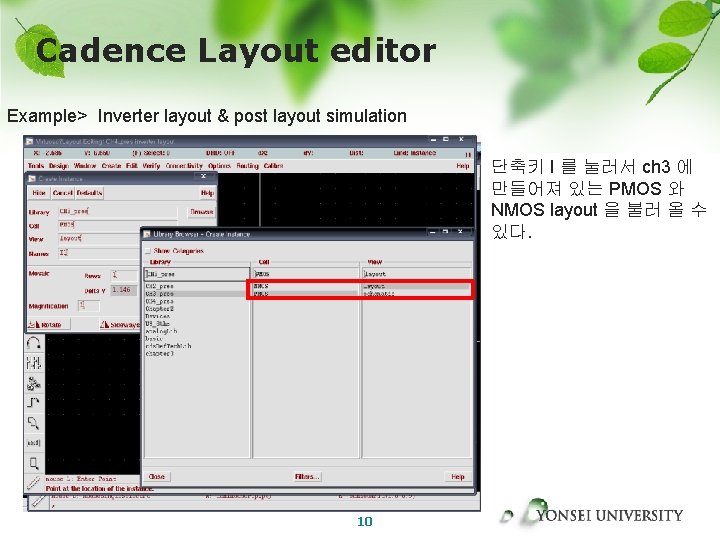

Cadence Layout editor Example> Inverter layout & post layout simulation 단축키 I 를 눌러서 ch 3 에 만들어져 있는 PMOS 와 NMOS layout 을 불러 올 수 있다. 10

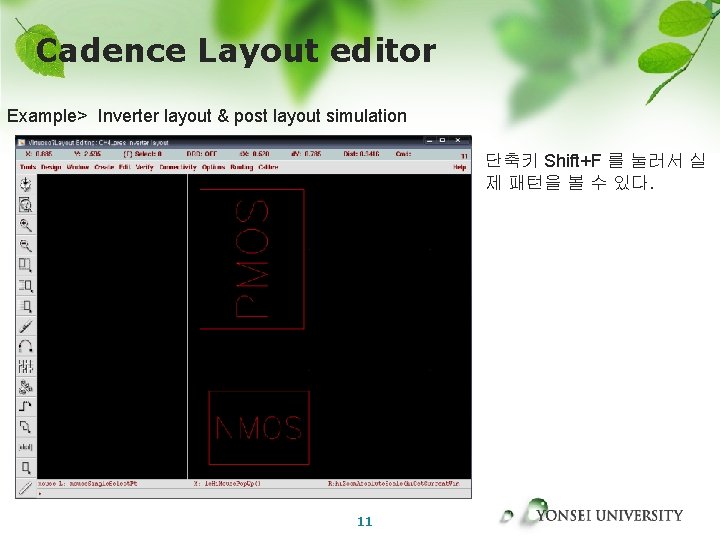

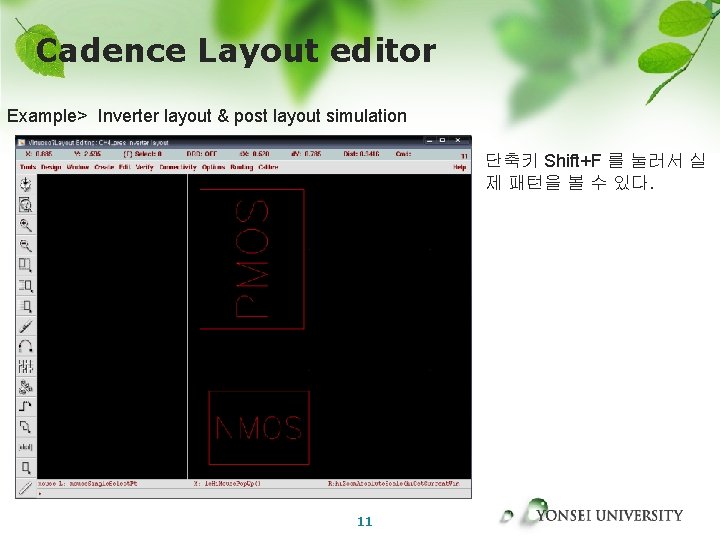

Cadence Layout editor Example> Inverter layout & post layout simulation 단축키 Shift+F 를 눌러서 실 제 패턴을 볼 수 있다. 11

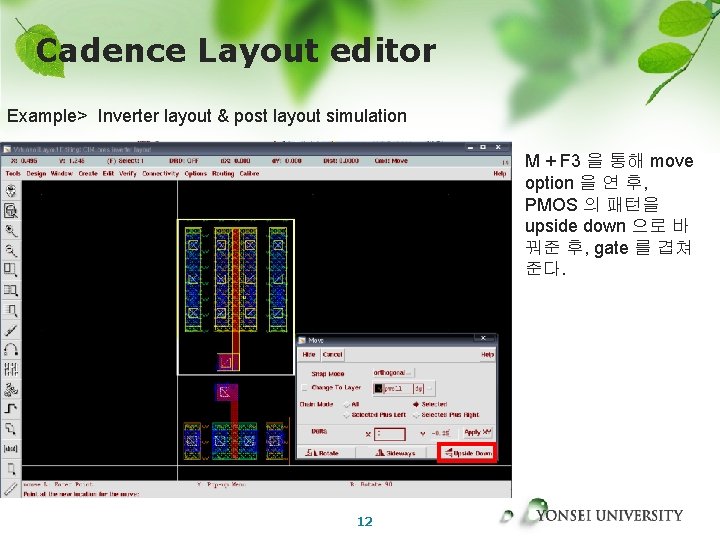

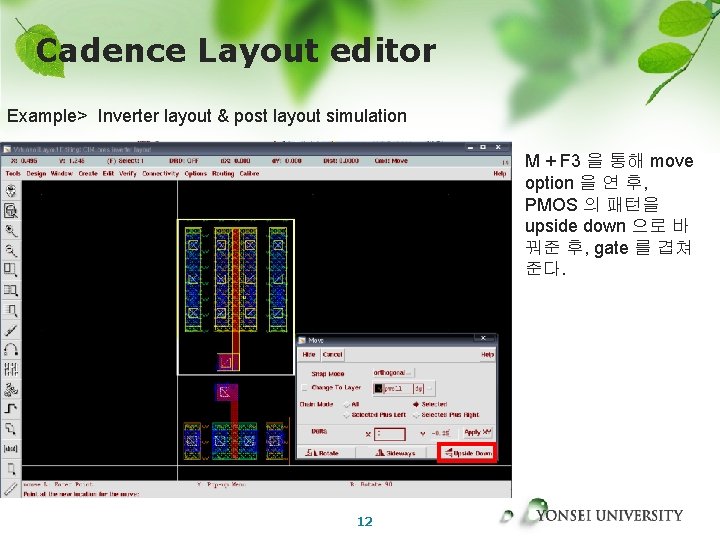

Cadence Layout editor Example> Inverter layout & post layout simulation M + F 3 을 통해 move option 을 연 후, PMOS 의 패턴을 upside down 으로 바 꿔준 후, gate 를 겹쳐 준다. 12

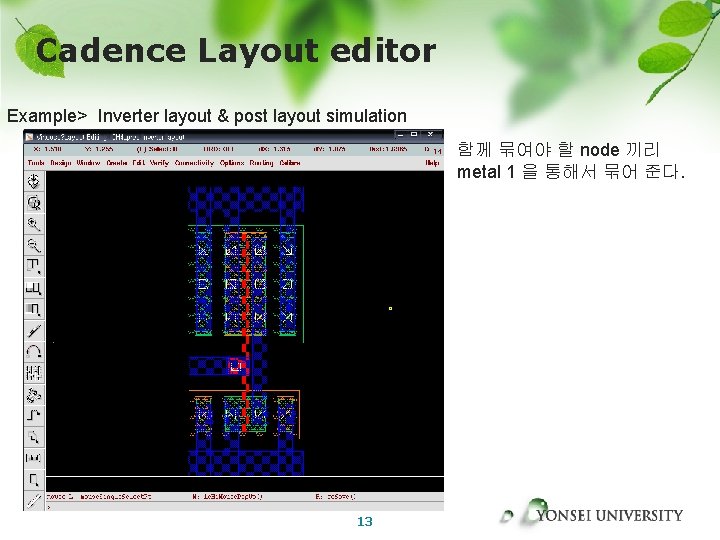

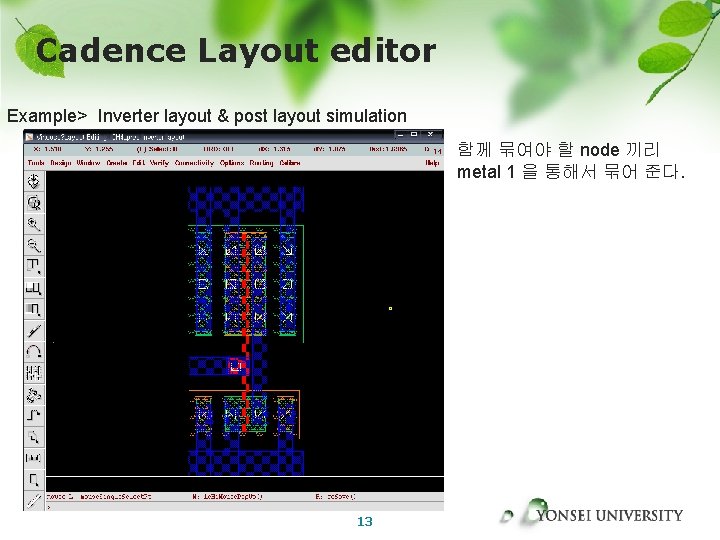

Cadence Layout editor Example> Inverter layout & post layout simulation 함께 묶여야 할 node 끼리 metal 1 을 통해서 묶어 준다. 13

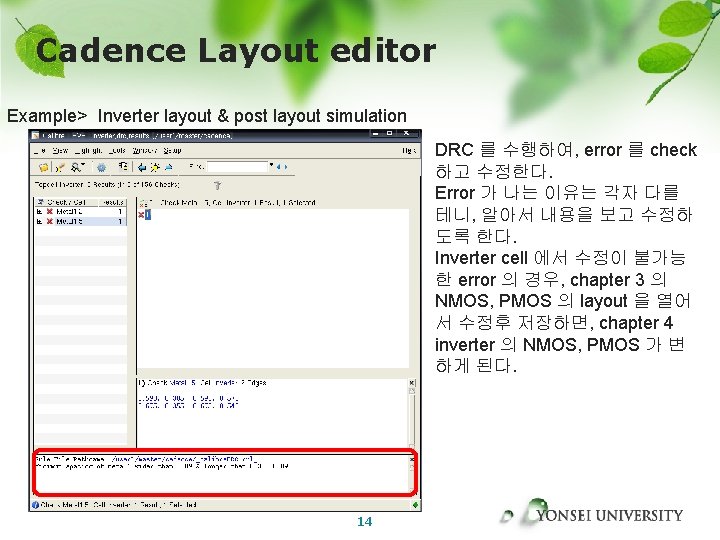

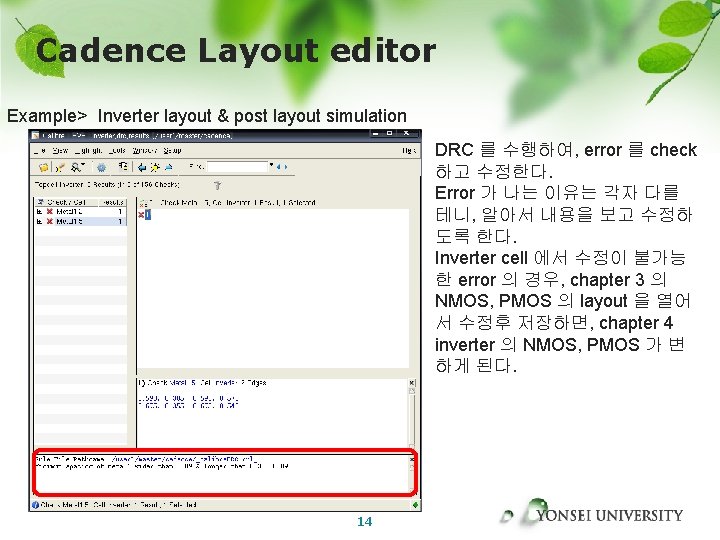

Cadence Layout editor Example> Inverter layout & post layout simulation DRC 를 수행하여, error 를 check 하고 수정한다. Error 가 나는 이유는 각자 다를 테니, 알아서 내용을 보고 수정하 도록 한다. Inverter cell 에서 수정이 불가능 한 error 의 경우, chapter 3 의 NMOS, PMOS 의 layout 을 열어 서 수정후 저장하면, chapter 4 inverter 의 NMOS, PMOS 가 변 하게 된다. 14

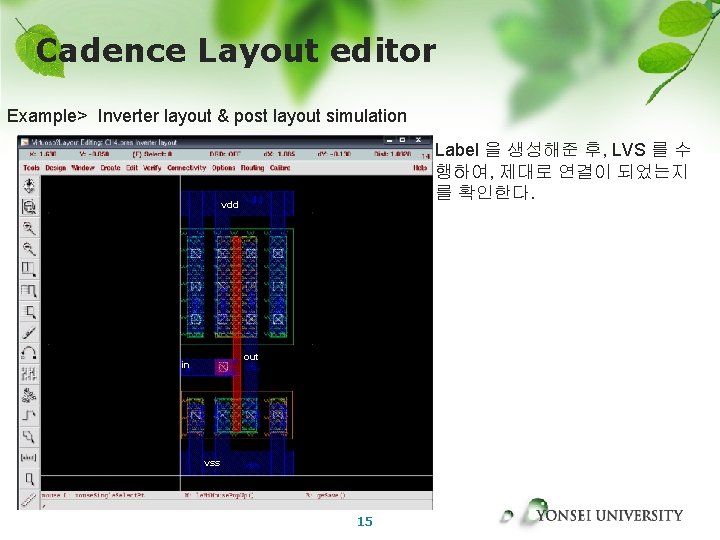

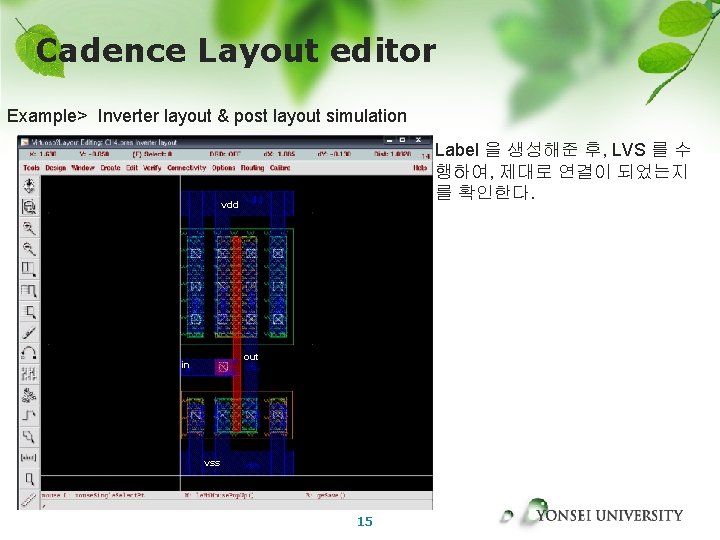

Cadence Layout editor Example> Inverter layout & post layout simulation Label 을 생성해준 후, LVS 를 수 행하여, 제대로 연결이 되었는지 를 확인한다. vdd out in vss 15

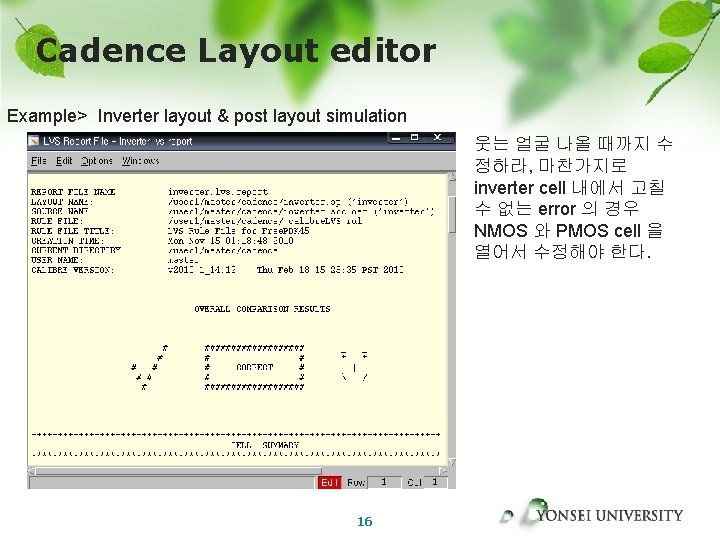

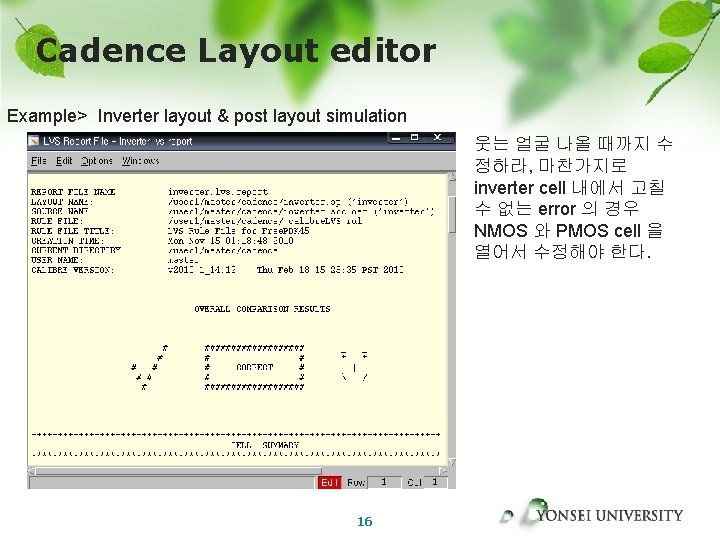

Cadence Layout editor Example> Inverter layout & post layout simulation 웃는 얼굴 나올 때까지 수 정하라, 마찬가지로 inverter cell 내에서 고칠 수 없는 error 의 경우 NMOS 와 PMOS cell 을 열어서 수정해야 한다. 16

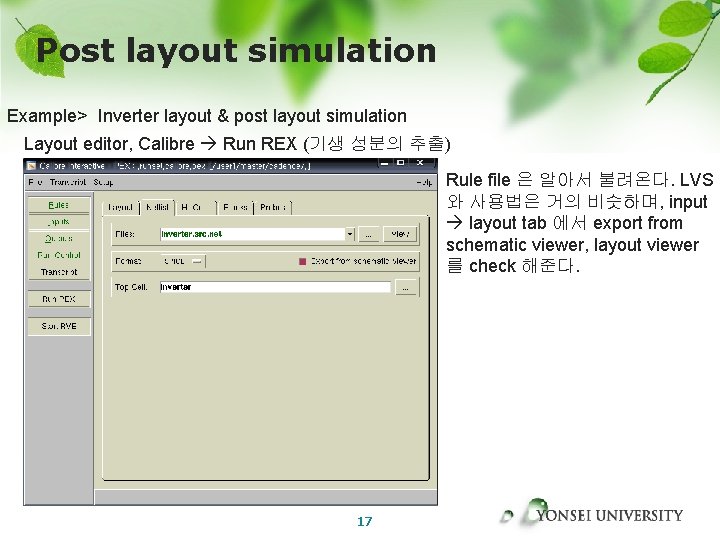

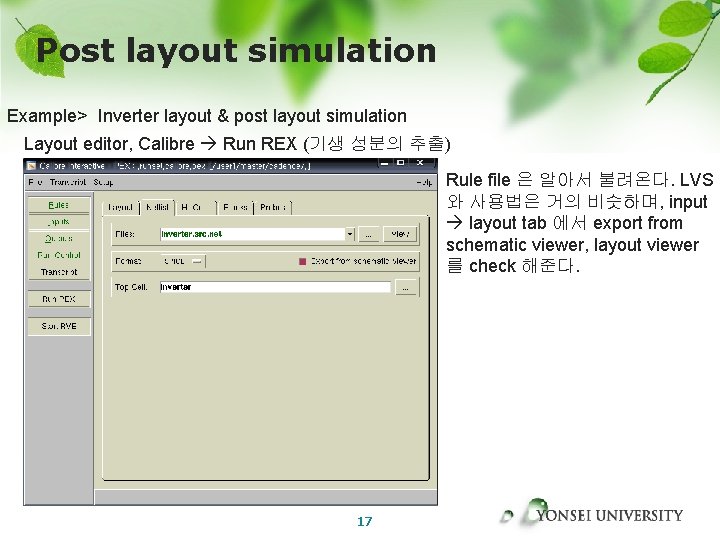

Post layout simulation Example> Inverter layout & post layout simulation Layout editor, Calibre Run REX (기생 성분의 추출) Rule file 은 알아서 불려온다. LVS 와 사용법은 거의 비슷하며, input layout tab 에서 export from schematic viewer, layout viewer 를 check 해준다. 17

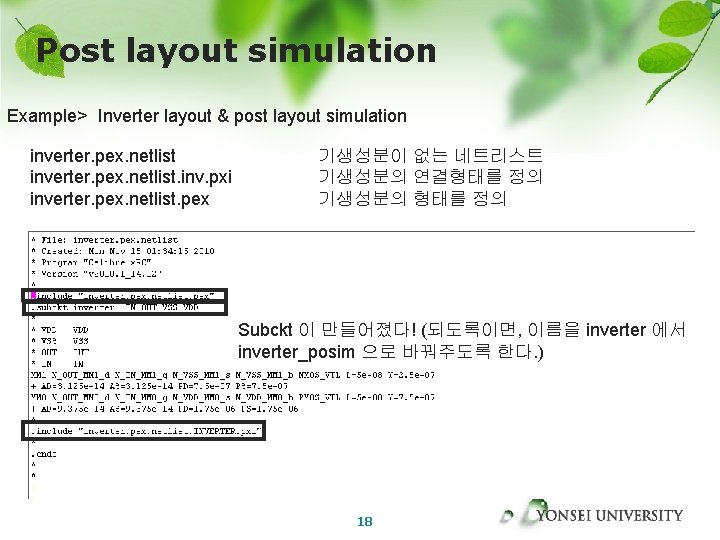

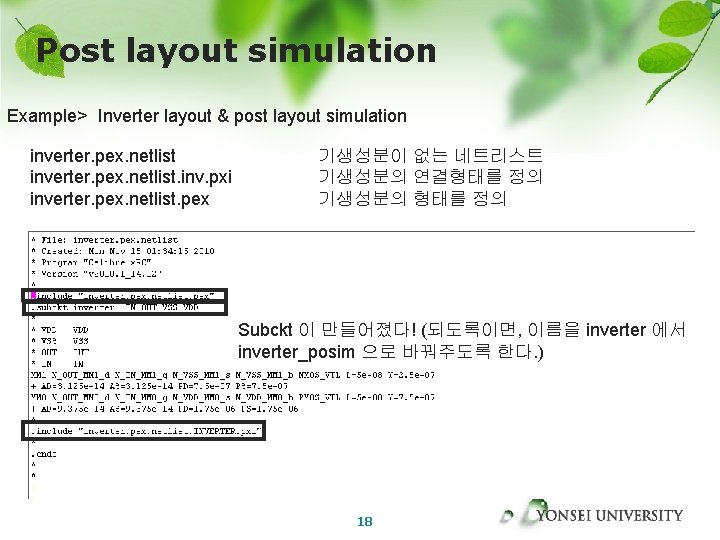

Post layout simulation Example> Inverter layout & post layout simulation inverter. pex. netlist. inv. pxi inverter. pex. netlist. pex 기생성분이 없는 네트리스트 기생성분의 연결형태를 정의 기생성분의 형태를 정의 Subckt 이 만들어졌다! (되도록이면, 이름을 inverter 에서 inverter_posim 으로 바꿔주도록 한다. ) 18

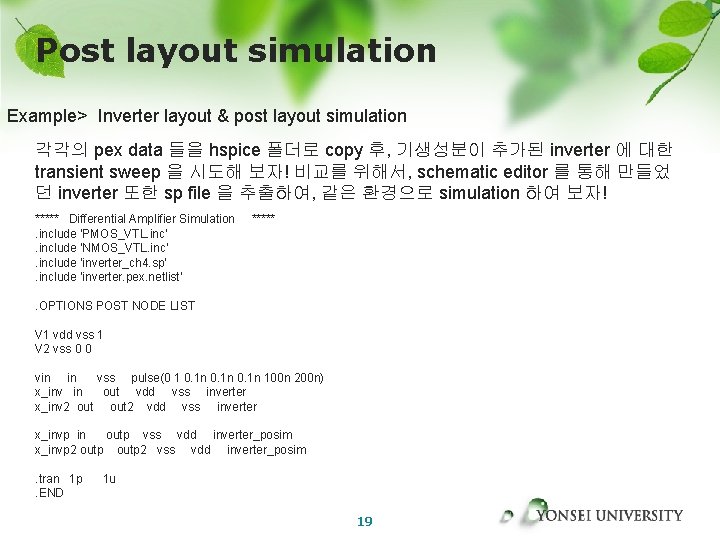

Post layout simulation Example> Inverter layout & post layout simulation 각각의 pex data 들을 hspice 폴더로 copy 후, 기생성분이 추가된 inverter 에 대한 transient sweep 을 시도해 보자! 비교를 위해서, schematic editor 를 통해 만들었 던 inverter 또한 sp file 을 추출하여, 같은 환경으로 simulation 하여 보자! ***** Differential Amplifier Simulation. include 'PMOS_VTL. inc'. include 'NMOS_VTL. inc'. include 'inverter_ch 4. sp'. include 'inverter. pex. netlist' ***** . OPTIONS POST NODE LIST V 1 vdd vss 1 V 2 vss 0 0 vin in vss pulse(0 1 0. 1 n 100 n 200 n) x_inv in out vdd vss inverter x_inv 2 out 2 vdd vss inverter x_invp in outp vss vdd inverter_posim x_invp 2 outp 2 vss vdd inverter_posim. tran 1 p. END 1 u 19

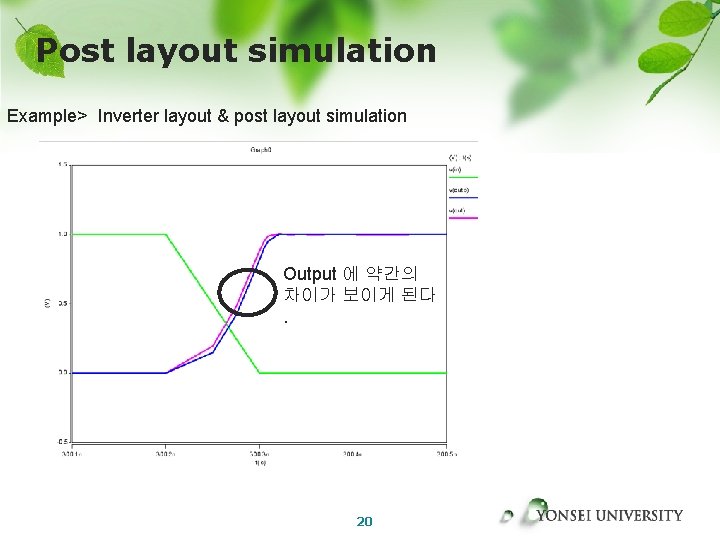

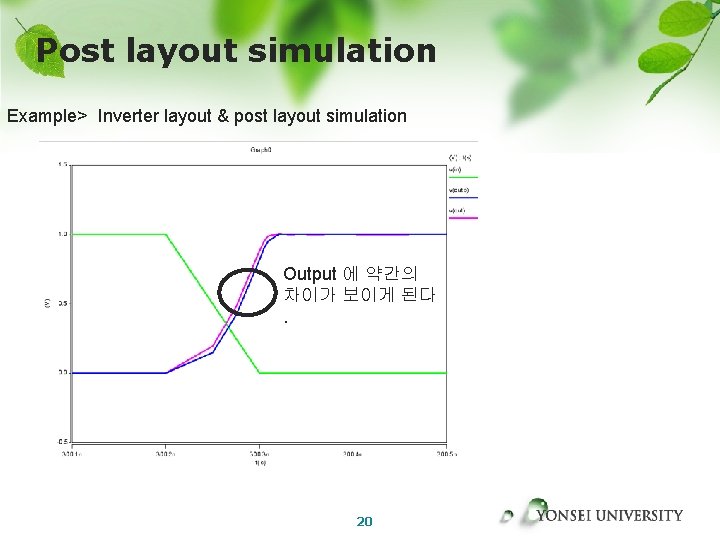

Post layout simulation Example> Inverter layout & post layout simulation Output 에 약간의 차이가 보이게 된다. 20