KARAKTERISTIKE CMOS KOLA Komplementarna MOS CMOS kola predstavljaju

- Slides: 7

KARAKTERISTIKE CMOS KOLA Komplementarna MOS (CMOS) kola predstavljaju najrasprostranjeniju familiju modernih logičkih kola zbog toga što se jedina koriste u svim stepenima integracije od SSI do VLSI. U CMOS tehnologiji mogu se napraviti sva digitalna kola, od invertora pa do izuzetno složenih memorijskih sistema imikroprocesora. CMOS tehnologija ima ogroman značaj za savremenu elektroniku. Napredak u bipolarnim i CMOS tehnologijama integrisanih kola, koji je postignut u poslednjih 25 godina, u osnovi se odnosi na smanjivanje dimenzija aktivnih komponenata čime je značajno povećana maksimalna frekvencija rada savremenih integrisanih kola na silicijumu. Na primer, u kombinovanoj nanometarskoj bipolarnoj-CMOS (Bi. CMOS) tehnologiji realizovani su tranzistori sa kritičnim dužinama(širina baze i/ili dužina kanala) reda 100 nm, kod kojih granična frekvencija prelazi 100 GHz. Zbog mogućnosti rada na ovako visokim frekvencijama i relativno niske cene proizvodnje, Bi. CMOS tehnologija je postala glavni kandidat za projektovanje i proizvodnju integrisanih kola namenjenih za tržište bežičnih telekomunikacija. Pored samog smanjivanja dimenzija, ogromno povećanje brzine rada integrisanih kola postignuto je korišćenjem novih tehnoloških struktura MOS i bipolarnih tranzistora izrađenih tehnologijom vakuumskog narastanja ultra-tankih slojeva silicijuma (Si), germanijuma (Ge) ili legura Si 1 -x. Gex sa debljinama reda 5 -50 nm. U radu ovakvih tranzistora dolazi do čitavog niza novih fizičkih pojava, koje neće biti predmet ove lekcije.

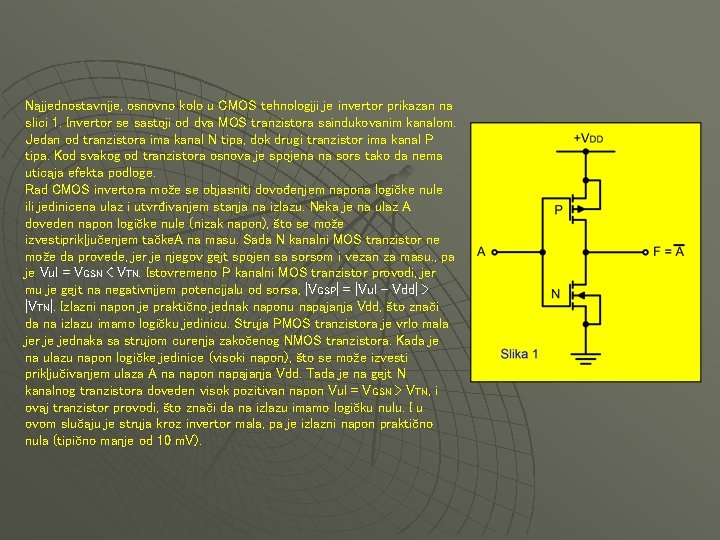

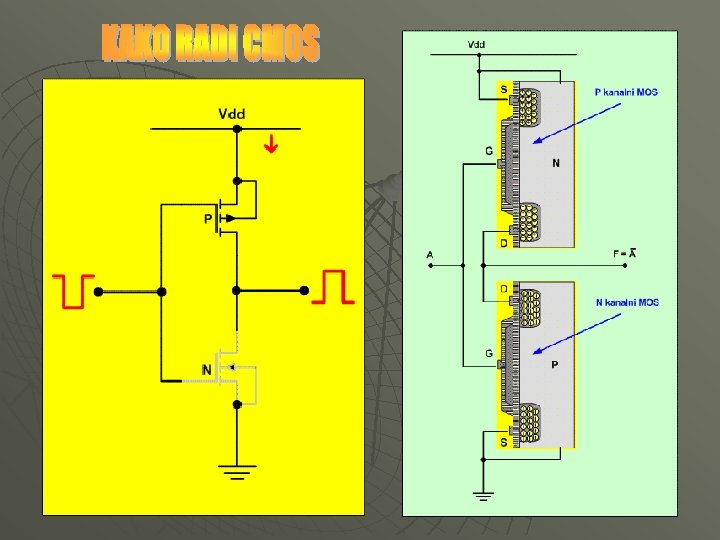

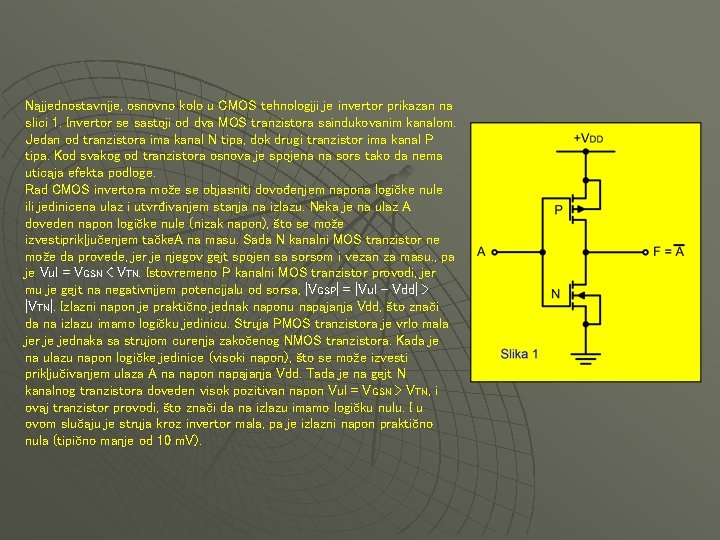

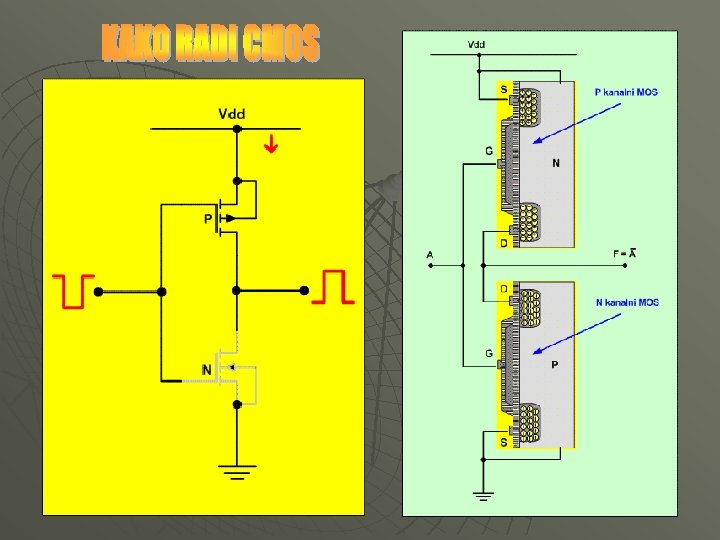

Najjednostavnije, osnovno kolo u CMOS tehnologiji je invertor prikazan na slici 1. Invertor se sastoji od dva MOS tranzistora saindukovanim kanalom. Jedan od tranzistora ima kanal N tipa, dok drugi tranzistor ima kanal P tipa. Kod svakog od tranzistora osnova je spojena na sors tako da nema uticaja efekta podloge. Rad CMOS invertora može se objasniti dovođenjem napona logičke nule ili jedinicena ulaz i utvrđivanjem stanja na izlazu. Neka je na ulaz A doveden napon logičke nule (nizak napon), što se može izvestipriključenjem tačke. A na masu. Sada N kanalni MOS tranzistor ne može da provede, jer je njegov gejt spojen sa sorsom i vezan za masu. , pa je Vul = VGSN < VTN. Istovremeno P kanalni MOS tranzistor provodi, jer mu je gejt na negativnijem potencijalu od sorsa, |VGSP| = |Vul - Vdd| > |VTN|. Izlazni napon je praktično jednak naponu napajanja Vdd, što znači da na izlazu imamo logičku jedinicu. Struja PMOS tranzistora je vrlo mala jer je jednaka sa strujom curenja zakočenog NMOS tranzistora. Kada je na ulazu napon logičke jedinice (visoki napon), što se može izvesti priključivanjem ulaza A na napon napajanja Vdd. Tada je na gejt N kanalnog tranzistora doveden visok pozitivan napon Vul = V GSN > VTN, i ovaj tranzistor provodi, što znači da na izlazu imamo logičku nulu. I u ovom slučaju je struja kroz invertor mala, pa je izlazni napon praktično nula (tipično manje od 10 m. V).

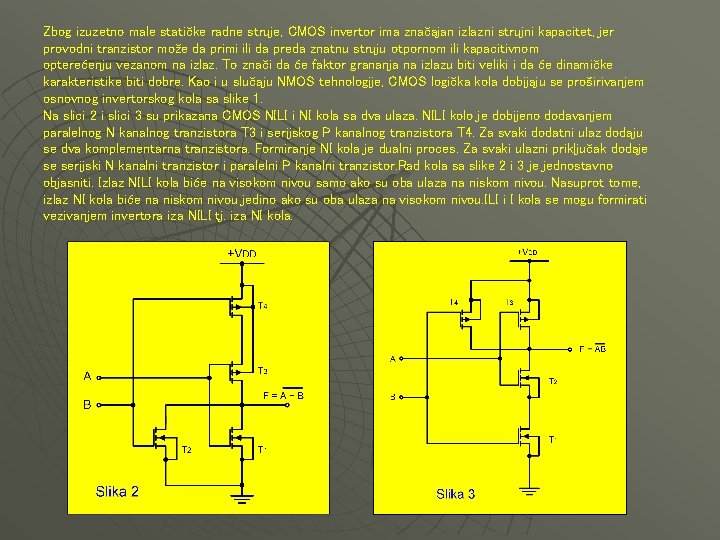

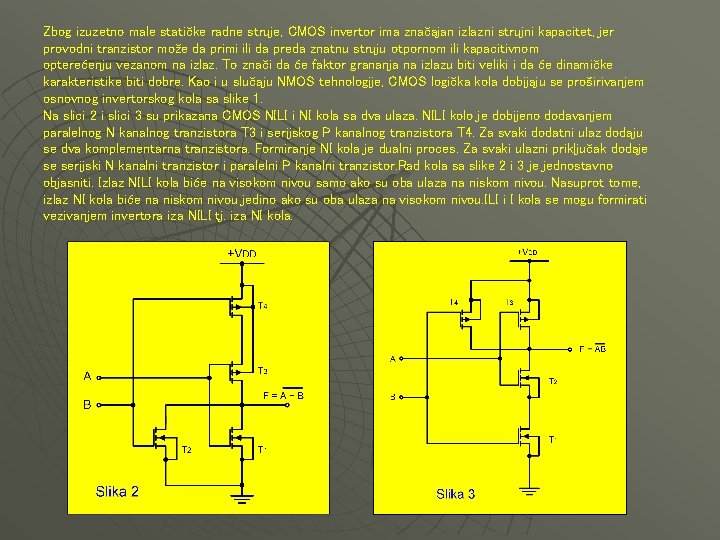

Zbog izuzetno male statičke radne struje, CMOS invertor ima značajan izlazni strujni kapacitet, jer provodni tranzistor može da primi ili da preda znatnu struju otpornom ili kapacitivnom opterećenju vezanom na izlaz. To znači da će faktor grananja na izlazu biti veliki i da će dinamičke karakteristike biti dobre. Kao i u slučaju NMOS tehnologije, CMOS logička kola dobijaju se proširivanjem osnovnog invertorskog kola sa slike 1. Na slici 2 i slici 3 su prikazana CMOS NILI i NI kola sa dva ulaza. NILI kolo je dobijeno dodavanjem paralelnog N kanalnog tranzistora T 3 i serijskog P kanalnog tranzistora T 4. Za svaki dodatni ulaz dodaju se dva komplementarna tranzistora. Formiranje NI kola je dualni proces. Za svaki ulazni priključak dodaje se serijski N kanalni tranzistor i paralelni P kanalni tranzistor. Rad kola sa slike 2 i 3 je jednostavno objasniti. Izlaz NILI kola biće na visokom nivou samo ako su oba ulaza na niskom nivou. Nasuprot tome, izlaz NI kola biće na niskom nivou jedino ako su oba ulaza na visokom nivou. ILI i I kola se mogu formirati vezivanjem invertora iza NILI tj. iza NI kola.

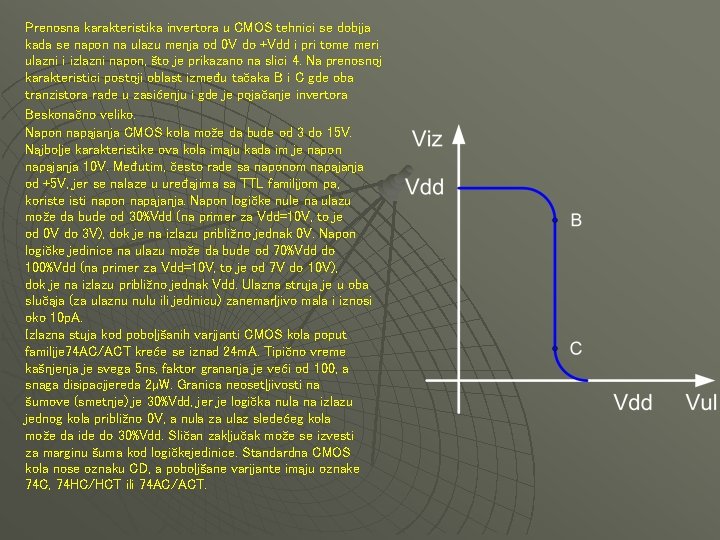

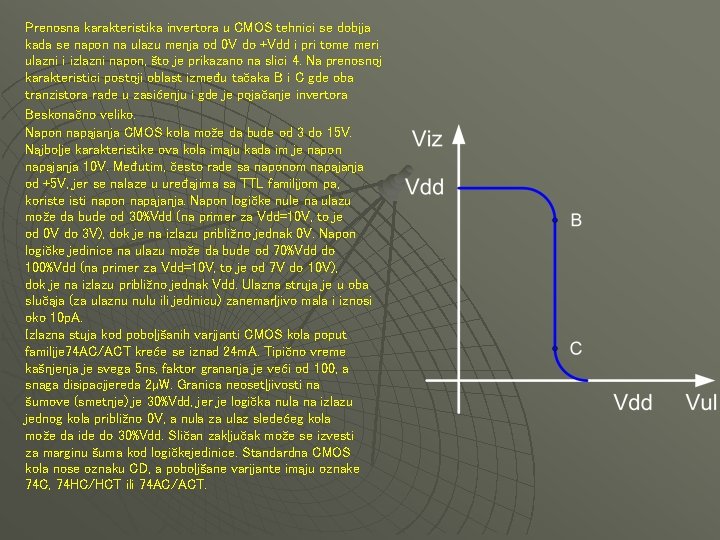

Prenosna karakteristika invertora u CMOS tehnici se dobija kada se napon na ulazu menja od 0 V do +Vdd i pri tome meri ulazni i izlazni napon, što je prikazano na slici 4. Na prenosnoj karakteristici postoji oblast između tačaka B i C gde oba tranzistora rade u zasićenju i gde je pojačanje invertora Beskonačno veliko. Napon napajanja CMOS kola može da bude od 3 do 15 V. Najbolje karakteristike ova kola imaju kada im je napon napajanja 10 V. Međutim, često rade sa naponom napajanja od +5 V, jer se nalaze u uređajima sa TTL familijom pa, koriste isti napon napajanja. Napon logičke nule na ulazu može da bude od 30%Vdd (na primer za Vdd=10 V, to je od 0 V do 3 V), dok je na izlazu približno jednak 0 V. Napon logičke jedinice na ulazu može da bude od 70%Vdd do 100%Vdd (na primer za Vdd=10 V, to je od 7 V do 10 V), dok je na izlazu približno jednak Vdd. Ulazna struja je u oba slučaja (za ulaznu nulu ili jedinicu) zanemarljivo mala i iznosi oko 10 p. A. Izlazna stuja kod poboljšanih varijanti CMOS kola poput familije 74 AC/ACT kreće se iznad 24 m. A. Tipično vreme kašnjenja je svega 5 ns, faktor grananja je veći od 100, a snaga disipacijereda 2µW. Granica neosetljivosti na šumove (smetnje) je 30%Vdd, jer je logička nula na izlazu jednog kola približno 0 V, a nula za ulaz sledećeg kola može da ide do 30%Vdd. Sličan zaključak može se izvesti za marginu šuma kod logičkejedinice. Standardna CMOS kola nose oznaku CD, a poboljšane varijante imaju oznake 74 C, 74 HC/HCT ili 74 AC/ACT.

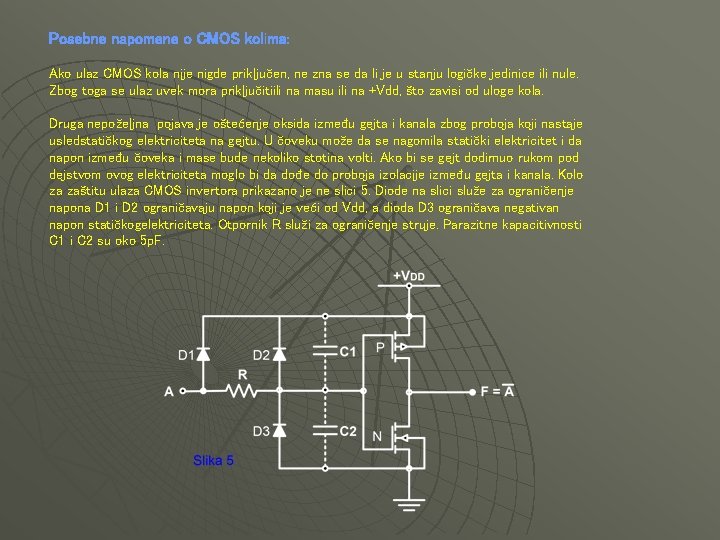

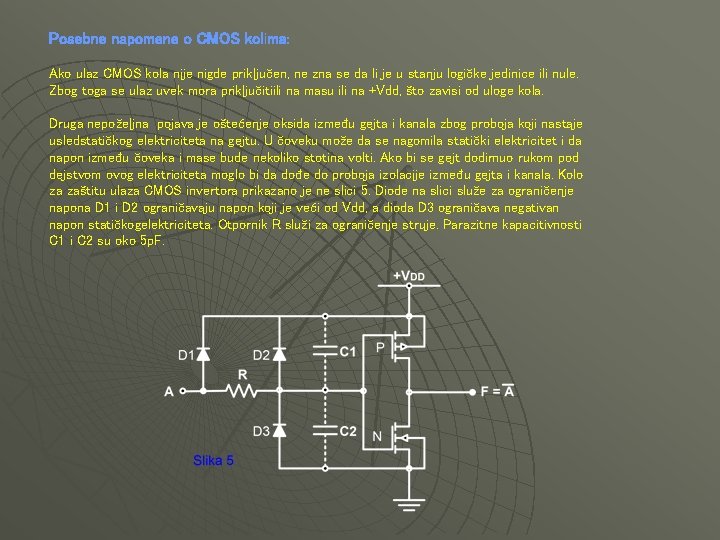

Posebne napomene o CMOS kolima: Ako ulaz CMOS kola nije nigde priključen, ne zna se da li je u stanju logičke jedinice ili nule. Zbog toga se ulaz uvek mora priključitiili na masu ili na +Vdd, što zavisi od uloge kola. Druga nepoželjna pojava je oštećenje oksida između gejta i kanala zbog proboja koji nastaje usledstatičkog elektriciteta na gejtu. U čoveku može da se nagomila statički elektricitet i da napon između čoveka i mase bude nekoliko stotina volti. Ako bi se gejt dodirnuo rukom pod dejstvom ovog elektriciteta moglo bi da dođe do proboja izolacije između gejta i kanala. Kolo za zaštitu ulaza CMOS invertora prikazano je ne slici 5. Diode na slici služe za ograničenje napona D 1 i D 2 ograničavaju napon koji je veći od Vdd, a dioda D 3 ograničava negativan napon statičkogelektriciteta. Otpornik R služi za ograničenje struje. Parazitne kapacitivnosti C 1 i C 2 su oko 5 p. F.