Modlisation du dlai dune porte CMOS SOI en

- Slides: 21

Modélisation du délai d’une porte CMOS SOI en faible inversion Alexandre VALENTIAN * Olivier THOMAS * Andrei VLADIMIRESCU *, ** Amara AMARA * FTFC 15/05/2003 * ISEP, ** Berkeley Wireless Research Center, UCB, FTFC Mai 2003 Paris 1

Plan Ø Présentation du modèle sous-seuil Ø Dérivation du délai Øtransition rapide en entrée Øtransition lente en entrée Ø Application à un oscillateur en anneaux Ø Conclusion FTFC Mai 2003 Paris 2

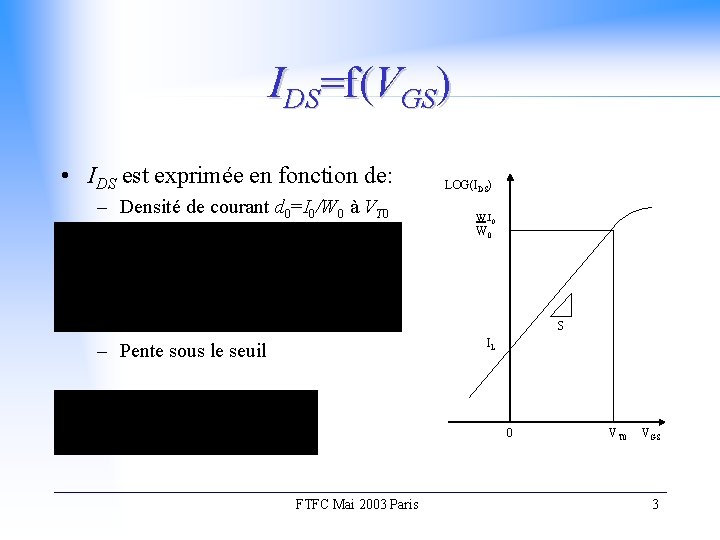

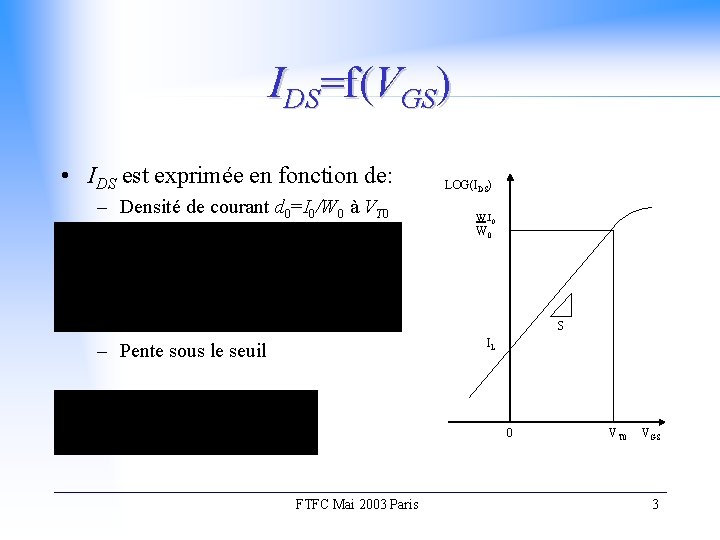

IDS=f(VGS) • IDS est exprimée en fonction de: – Densité de courant d 0=I 0/W 0 à VT 0 LOG(IDS) W. I 0 W 0 S IL – Pente sous le seuil 0 VT 0 VGS FTFC Mai 2003 Paris 3

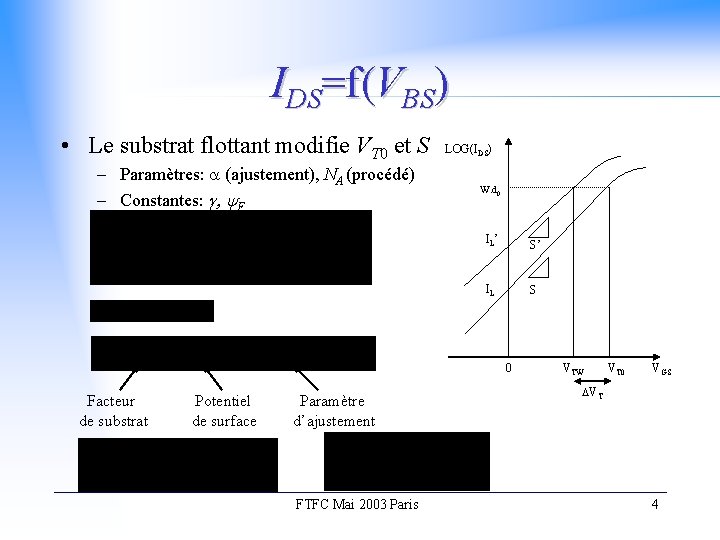

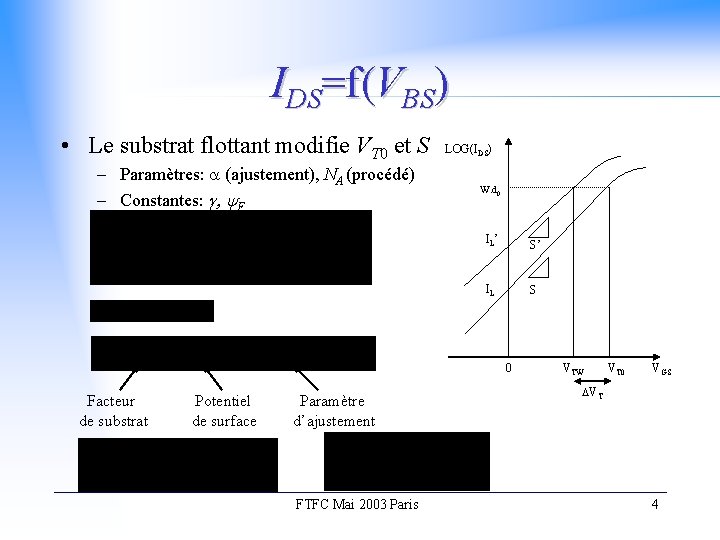

IDS=f(VBS) • Le substrat flottant modifie VT 0 et S – Paramètres: (ajustement), NA (procédé) – Constantes: g, y. F LOG(IDS) W. d 0 IL ’ S’ IL S 0 VTW VT 0 VGS Facteur Potentiel Paramètre de substrat de surface d’ajustement FTFC Mai 2003 Paris VT 4

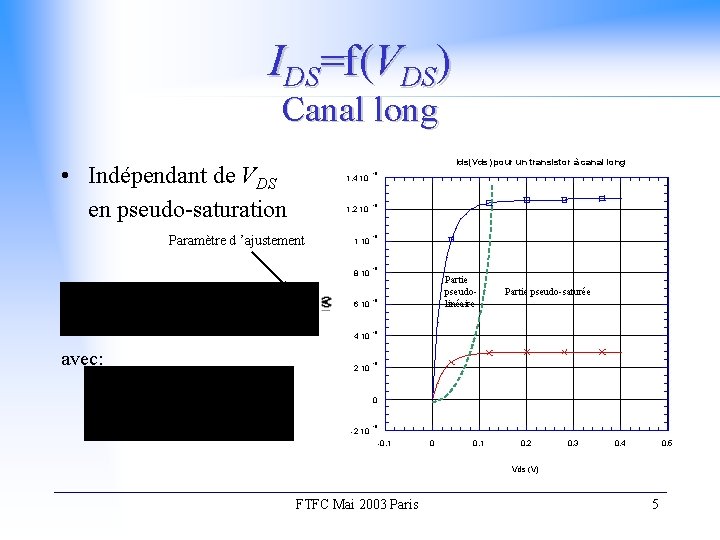

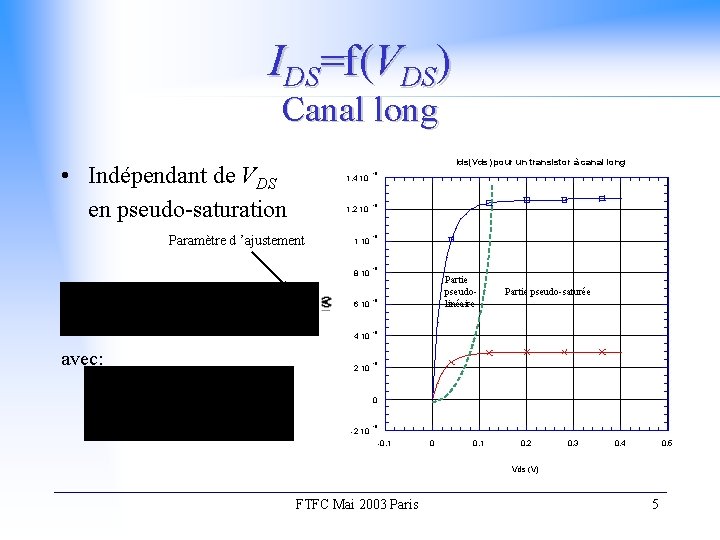

IDS=f(VDS) Canal long Ids(Vds) pour un transistor à canal long • Indépendant de VDS en pseudo-saturation 1. 4 10 1. 2 10 Paramètre d ’ajustement 1 10 8 10 6 10 4 10 avec: 2 10 -8 -8 -8 -9 Partie pseudolinéaire -9 Partie pseudo-saturée -9 -9 0 -2 10 -9 -0. 1 0. 2 0. 3 0. 4 0. 5 Vds (V) FTFC Mai 2003 Paris 5

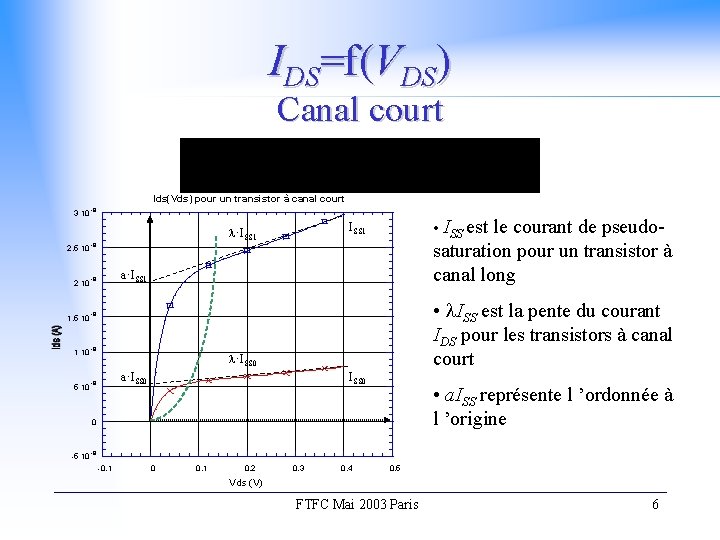

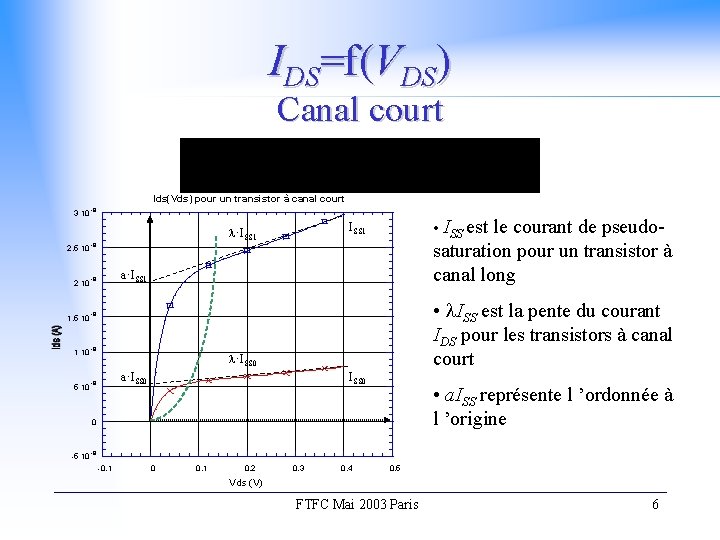

IDS=f(VDS) Canal court Ids(Vds) pour un transistor à canal court 3 10 -8 2. 5 10 -8 2 10 -8 1. 5 10 -8 1 10 -8 5 10 -9 • ISS est le courant de pseudo- ISS 1 ·ISS 1 saturation pour un transistor à canal long a·ISS 1 • ISS est la pente du courant IDS pour les transistors à canal court ·ISS 0 a·ISS 0 • a. ISS représente l ’ordonnée à l ’origine 0 -5 10 -9 -0. 1 0. 2 0. 3 0. 4 0. 5 Vds (V) FTFC Mai 2003 Paris 6

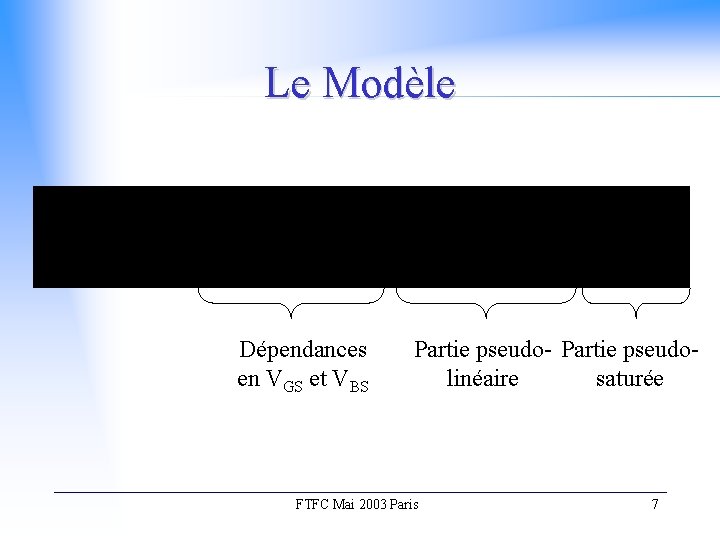

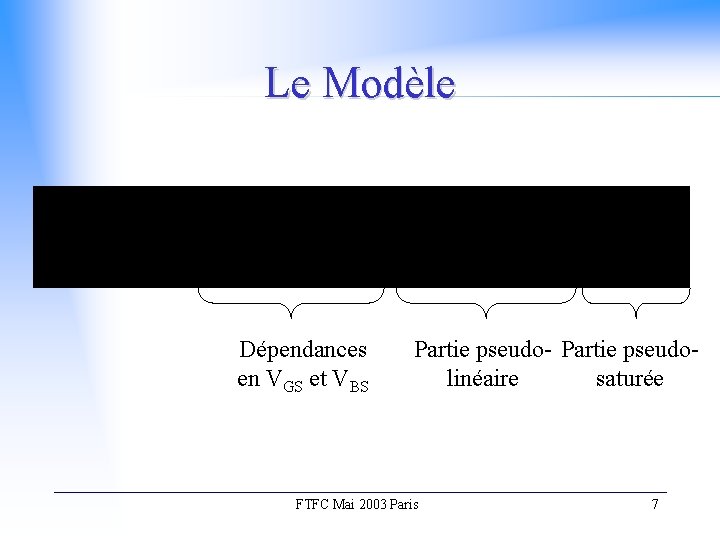

Le Modèle Dépendances en VGS et VBS Partie pseudo- linéaire saturée FTFC Mai 2003 Paris 7

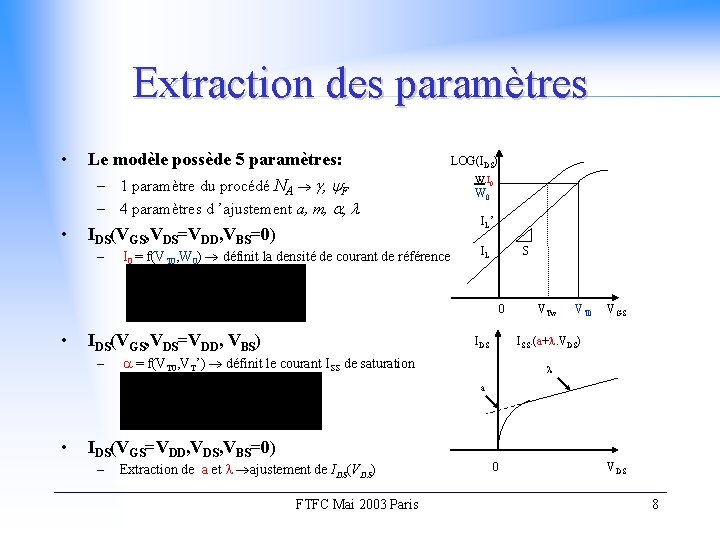

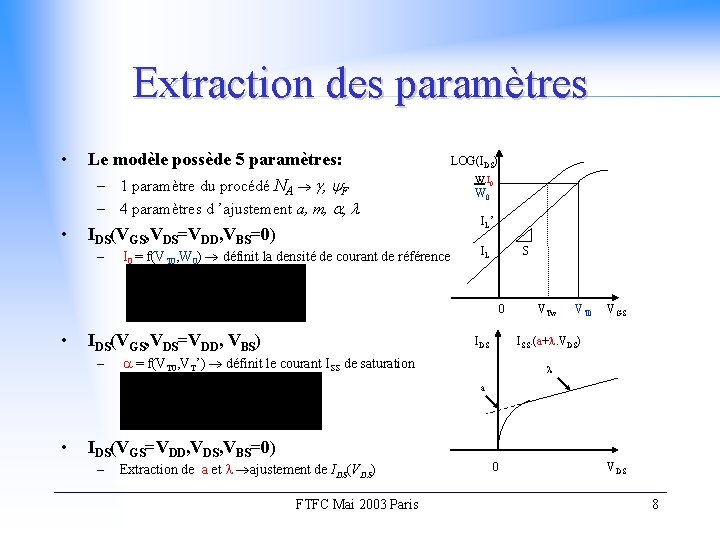

Extraction des paramètres • Le modèle possède 5 paramètres: – 1 paramètre du procédé NA g, y. F – 4 paramètres d ’ajustement a, m, a, l • IDS(VGS, VDS=VDD, VBS=0) – I 0 = f(VT 0, W 0) définit la densité de courant de référence LOG(IDS) W. I 0 W 0 IL’ IL S 0 VTw VT 0 VGS • IDS(VGS, VDS=VDD, VBS) – IDS = f(VT 0, VT’) définit le courant ISS de saturation ISS. (a+. VDS) a • IDS(VGS=VDD, VDS, VBS=0) – Extraction de a et ajustement de IDS(VDS) FTFC Mai 2003 Paris 0 VDS 8

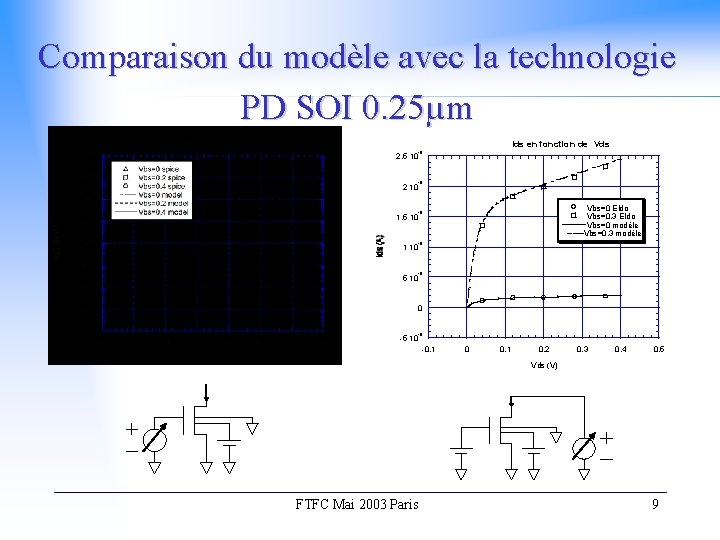

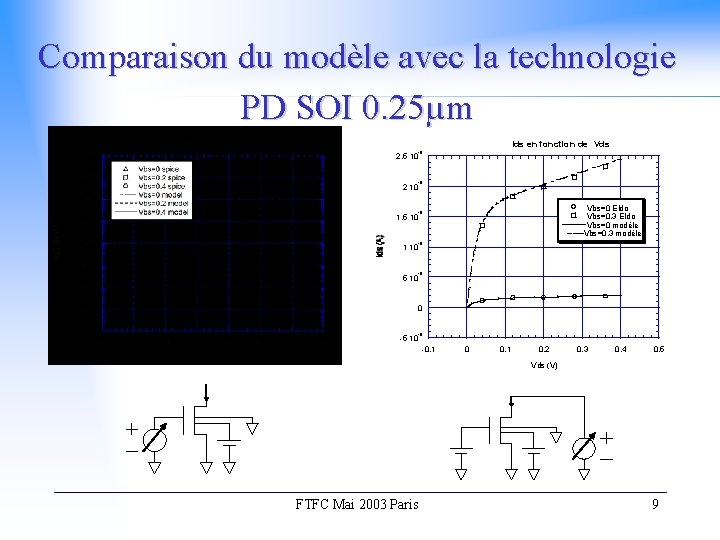

Comparaison du modèle avec la technologie PD SOI 0. 25µm Ids en fonction de Vds -8 2. 5 10 -8 2 10 Vbs=0 Eldo Vbs=0. 3 Eldo Vbs=0 modèle Vbs=0. 3 modèle -8 1. 5 10 -8 1 10 -9 5 10 0 -9 -5 10 -0. 1 0. 2 0. 3 0. 4 0. 5 Vds (V) FTFC Mai 2003 Paris 9

Plan Ø Présentation du modèle sous-seuil Ø Dérivation du délai Øtransition rapide en entrée Øtransition lente en entrée Ø Application à un oscillateur en anneaux Ø Conclusion FTFC Mai 2003 Paris 10

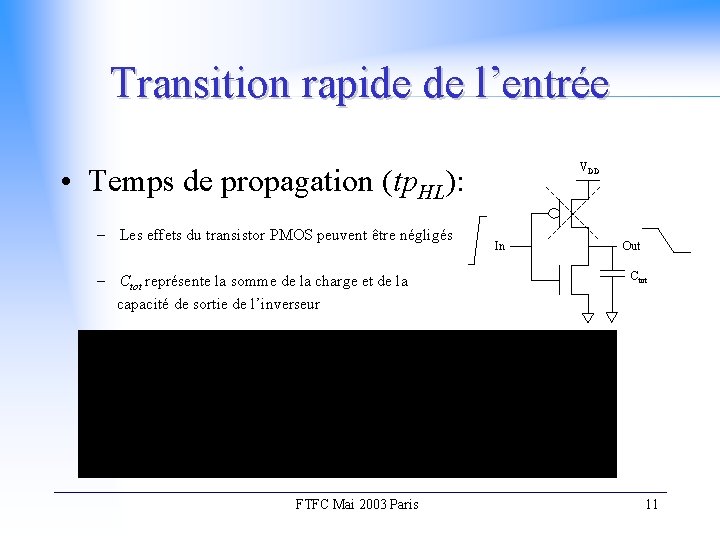

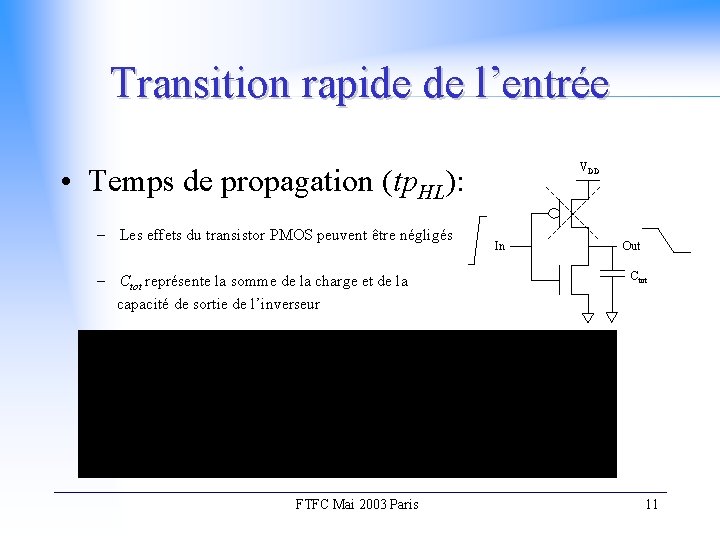

Transition rapide de l’entrée VDD • Temps de propagation (tp. HL): – Les effets du transistor PMOS peuvent être négligés – Ctot représente la somme de la charge et de la capacité de sortie de l’inverseur FTFC Mai 2003 Paris In Out Ctot 11

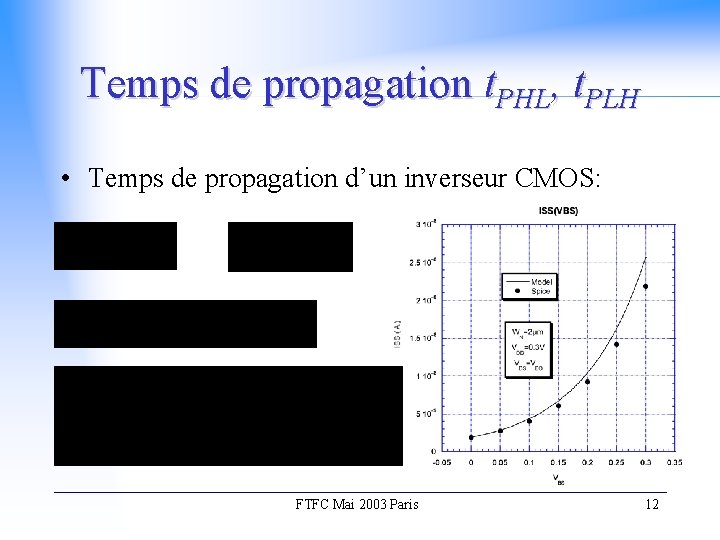

Temps de propagation t. PHL, t. PLH • Temps de propagation d’un inverseur CMOS: FTFC Mai 2003 Paris 12

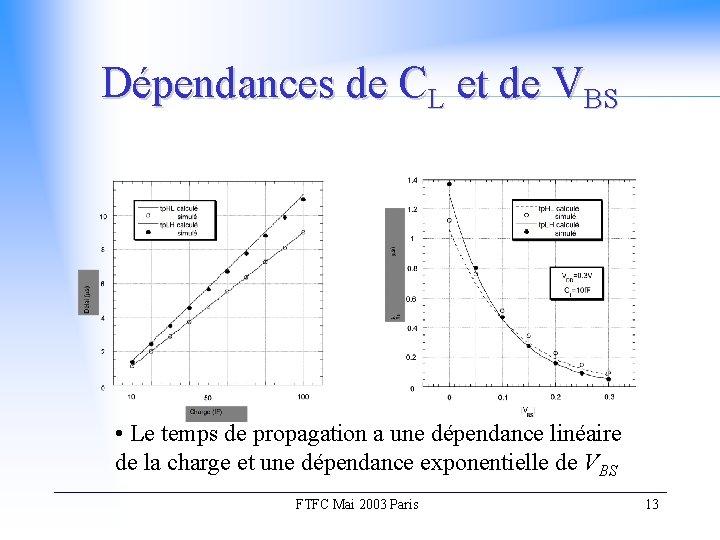

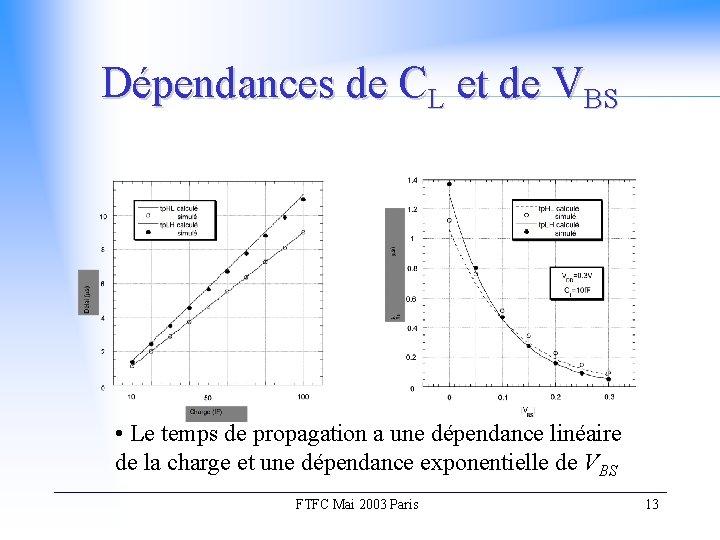

Dépendances de CL et de VBS • Le temps de propagation a une dépendance linéaire de la charge et une dépendance exponentielle de VBS FTFC Mai 2003 Paris 13

Plan Ø Présentation du modèle sous-seuil Ø Dérivation du délai Øtransition rapide en entrée Øtransition lente en entrée Ø Application à un oscillateur en anneaux Ø Conclusion FTFC Mai 2003 Paris 14

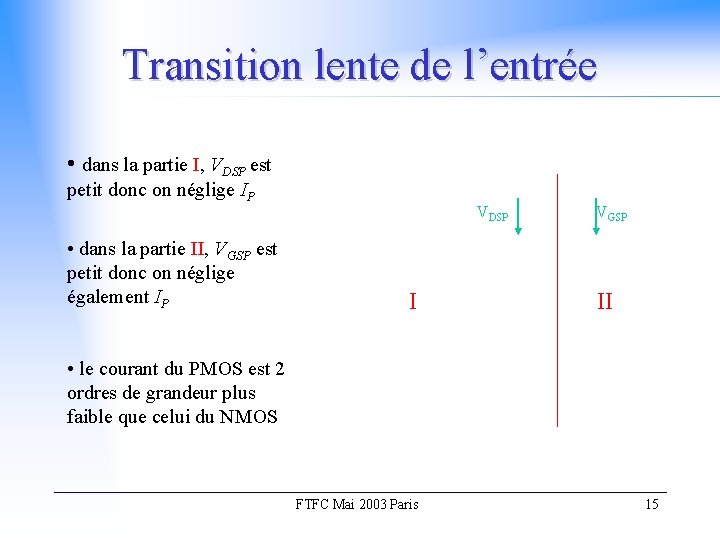

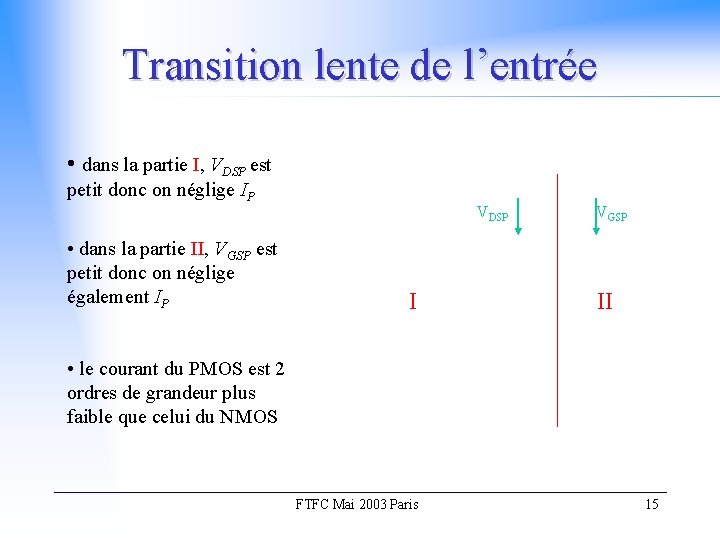

Transition lente de l’entrée • dans la partie I, VDSP est petit donc on néglige IP • dans la partie II, VGSP est petit donc on néglige également IP VDSP I VGSP II • le courant du PMOS est 2 ordres de grandeur plus faible que celui du NMOS FTFC Mai 2003 Paris 15

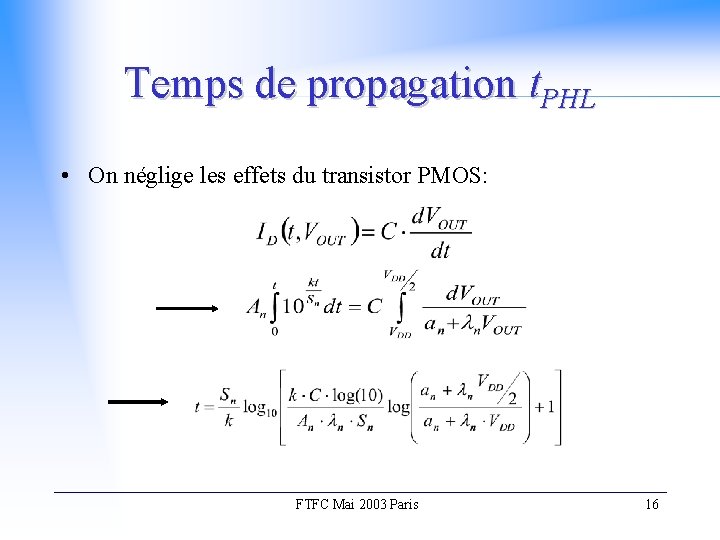

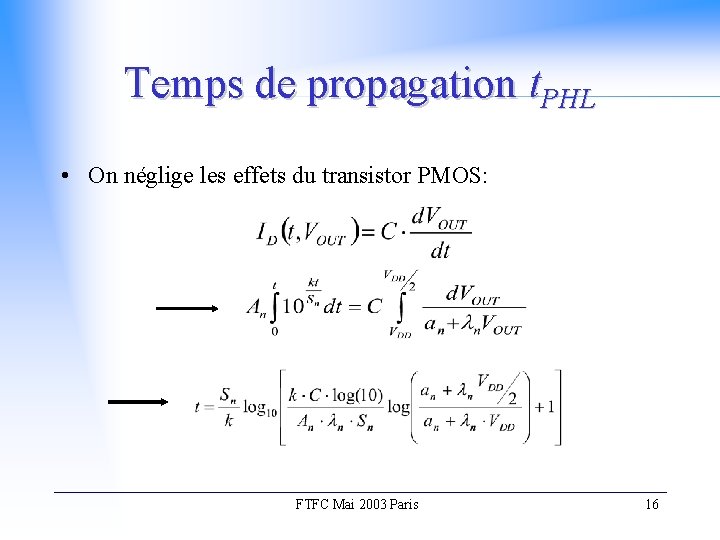

Temps de propagation t. PHL • On néglige les effets du transistor PMOS: FTFC Mai 2003 Paris 16

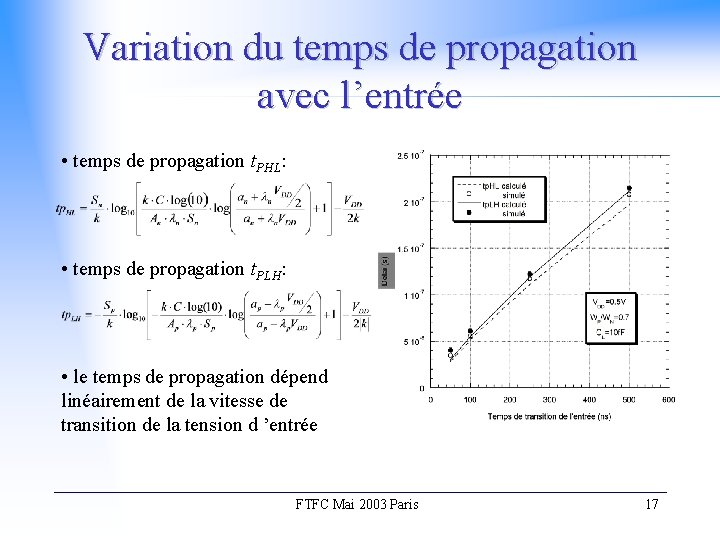

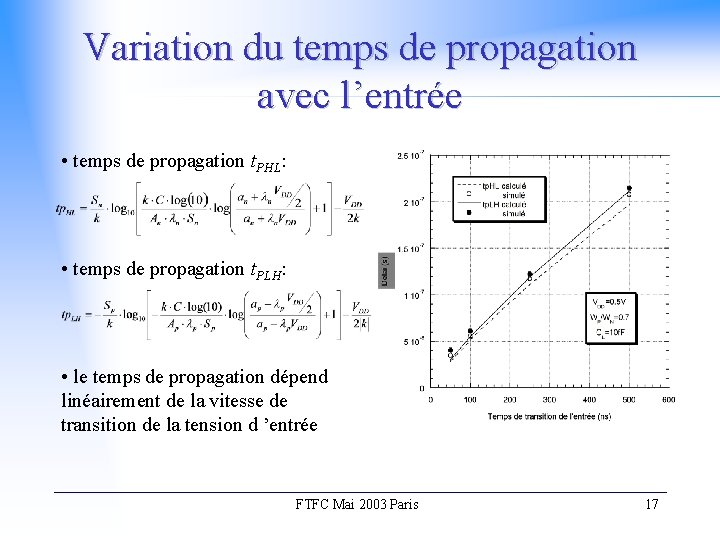

Variation du temps de propagation avec l’entrée • temps de propagation t. PHL: • temps de propagation t. PLH: • le temps de propagation dépend linéairement de la vitesse de transition de la tension d ’entrée FTFC Mai 2003 Paris 17

Plan Ø Présentation du modèle sous-seuil Ø Dérivation du délai Øtransition rapide en entrée Øtransition lente en entrée Ø Application à un oscillateur en anneaux Ø Conclusion FTFC Mai 2003 Paris 18

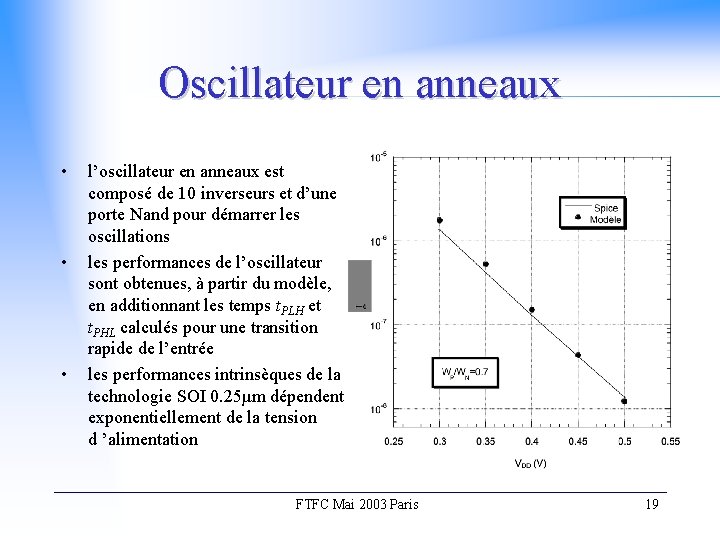

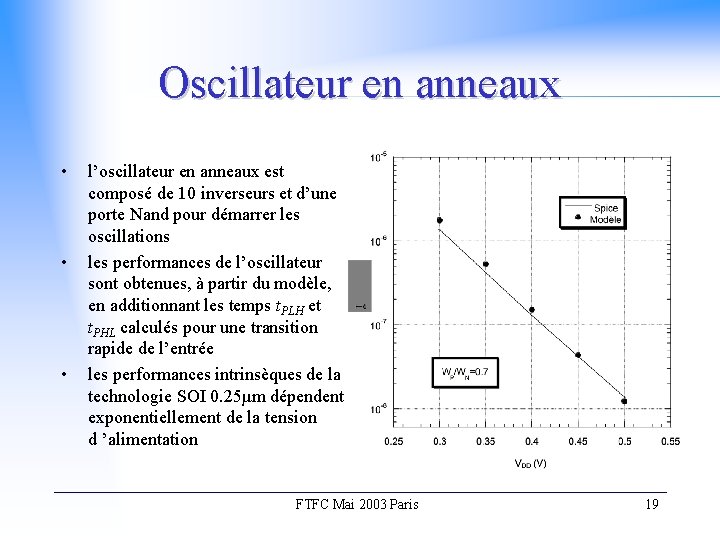

Oscillateur en anneaux • • • l’oscillateur en anneaux est composé de 10 inverseurs et d’une porte Nand pour démarrer les oscillations les performances de l’oscillateur sont obtenues, à partir du modèle, en additionnant les temps t. PLH et t. PHL calculés pour une transition rapide de l’entrée les performances intrinsèques de la technologie SOI 0. 25µm dépendent exponentiellement de la tension d ’alimentation FTFC Mai 2003 Paris 19

Plan Ø Présentation du modèle sous-seuil Ø Dérivation du délai Øtransition rapide en entrée Øtransition lente en entrée Ø Application à un oscillateur en anneaux Ø Conclusion FTFC Mai 2003 Paris 20

Conclusion • A partir d’un modèle sous-seuil simple incluant les dépendances en VGS, VBS et VDS, les équations du délai d’un inverseur ont été dérivées. • Le temps de propagation obtenu prend en compte l’influence de la vitesse de transition de la tension d’entrée. • Les résultats montrent une variation linéaire du délai avec la charge en sortie et la pente en entrée et une variation exponentielle avec la tension VBS. • Appliqués à une structure d’oscillateur en anneaux, on note que les performances intrinsèques de la technologie SOI 0. 25µm varient exponentiellement avec la tension d’alimentation. • Les résultats obtenus sont en bonne concordance avec les simulations. FTFC Mai 2003 Paris 21