Organizacija sistema zasnovana na mikropocesoru 80 x 86

![[BX] Addressing Mode [BX] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-43.jpg)

![[BP] Addressing Mode [BP] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-44.jpg)

![[BX+disp] Addressing Mode [BX+disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-45.jpg)

![[BP+disp] Addressing Mode [BP+disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-46.jpg)

![[BX+SI] Addressing Mode [BX+SI] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-47.jpg)

![[BP+SI] Addressing Mode [BP+SI] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-48.jpg)

![[BX + SI + disp] Addressing Mode [BX + SI + disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-49.jpg)

![[BP + SI + disp] Addressing Mode [BP + SI + disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-50.jpg)

- Slides: 125

Organizacija sistema zasnovana na mikropocesoru 80 x 86

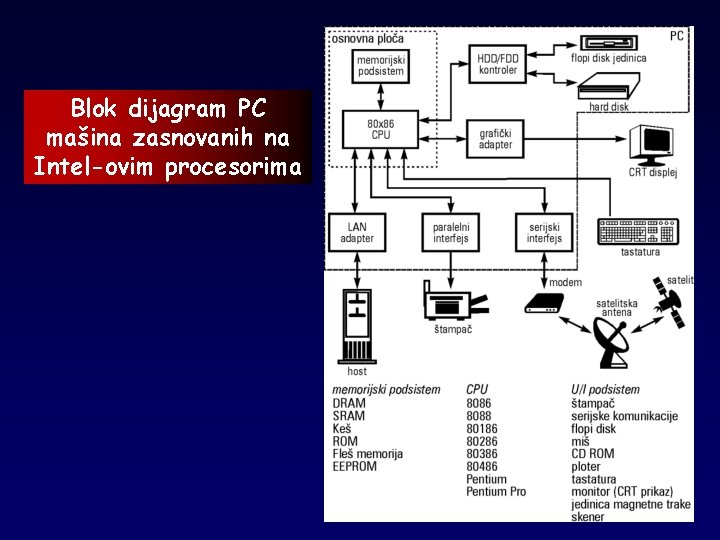

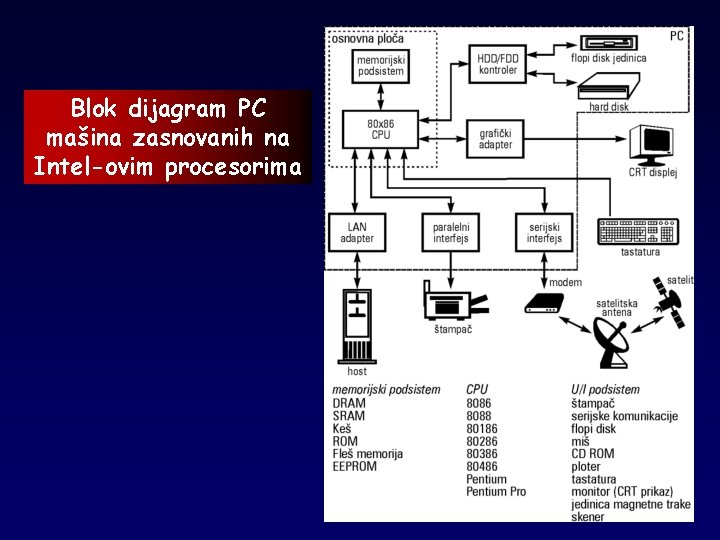

Blok dijagram PC mašina zasnovanih na Intel-ovim procesorima

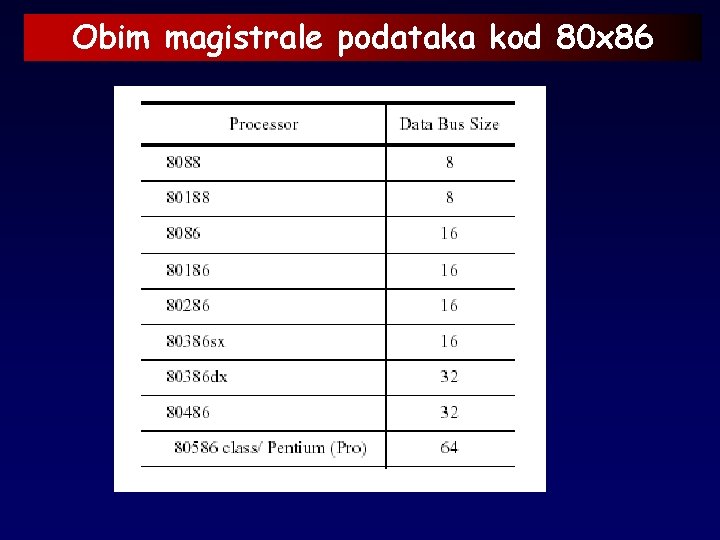

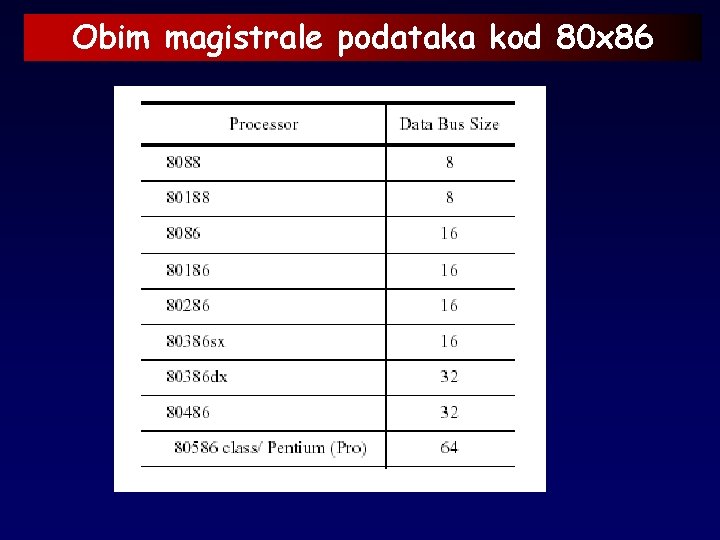

Obim magistrale podataka kod 80 x 86

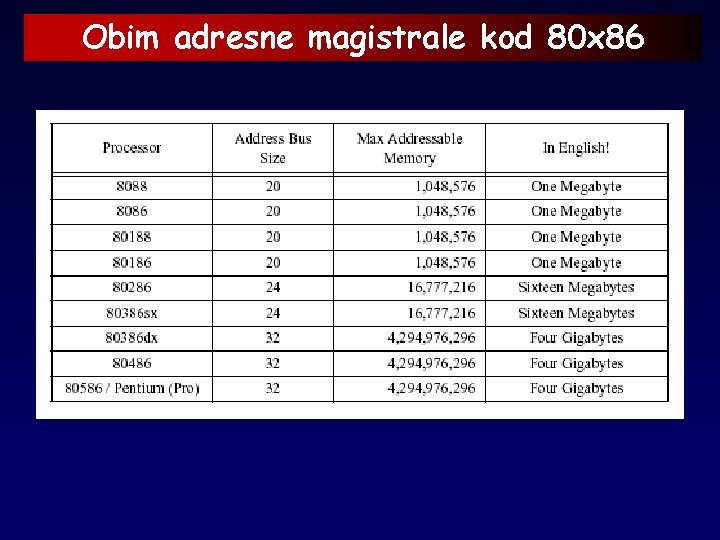

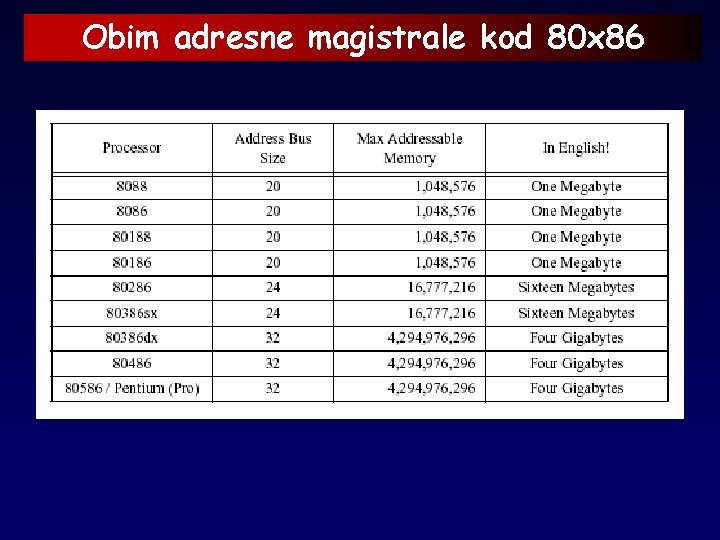

Obim adresne magistrale kod 80 x 86

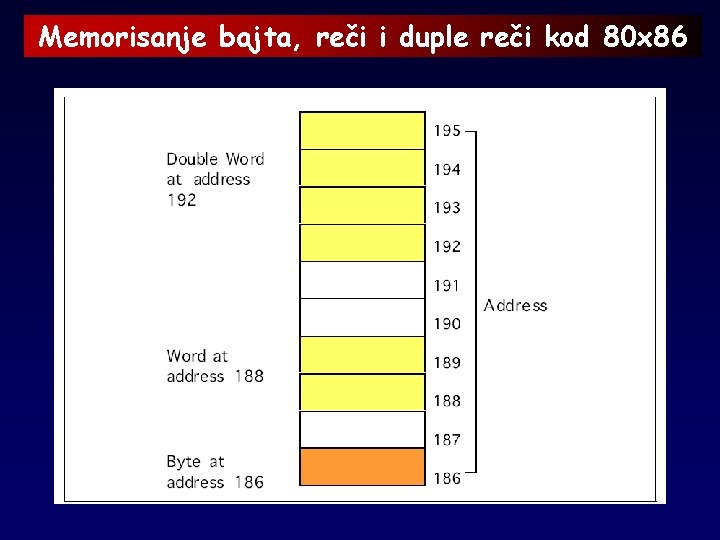

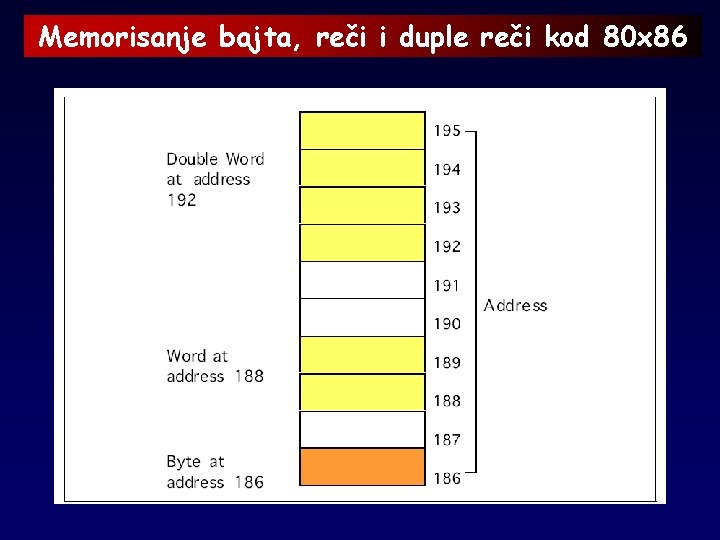

Memorisanje bajta, reči i duple reči kod 80 x 86

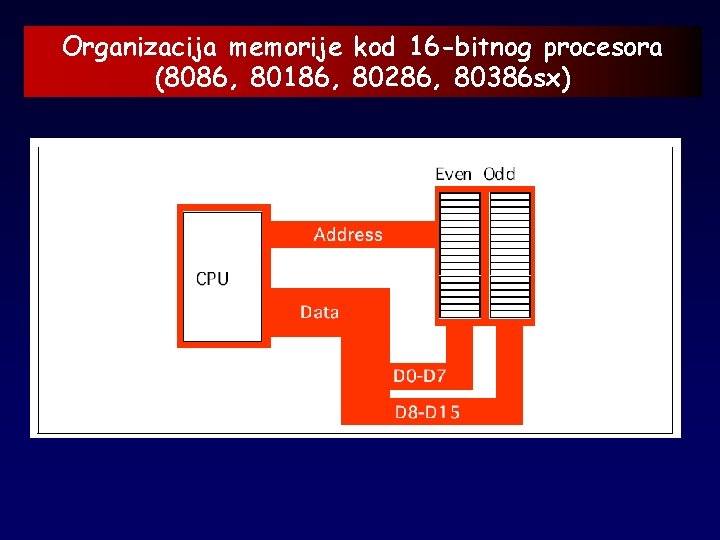

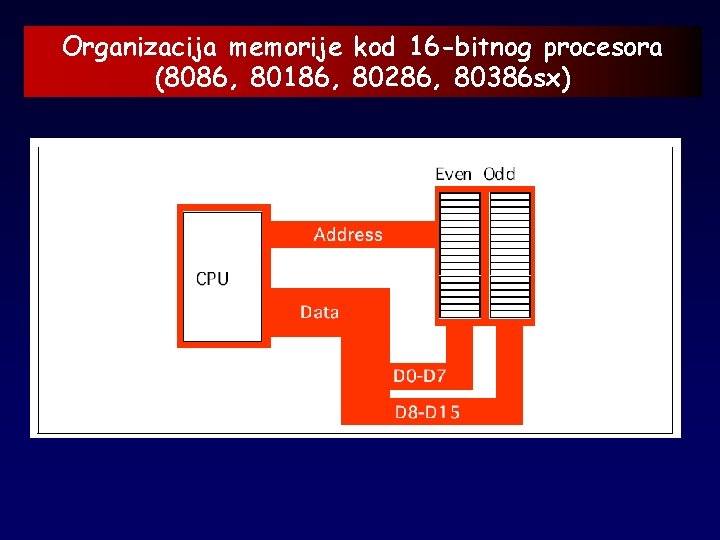

Organizacija memorije kod 16 -bitnog procesora (8086, 80186, 80286, 80386 sx)

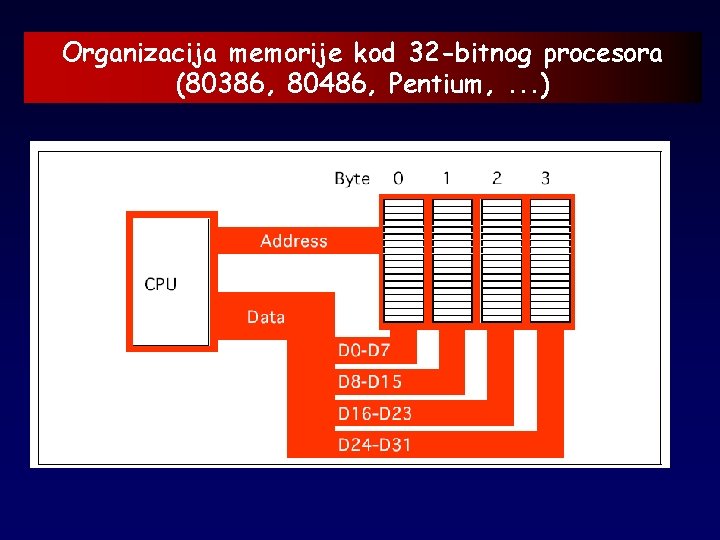

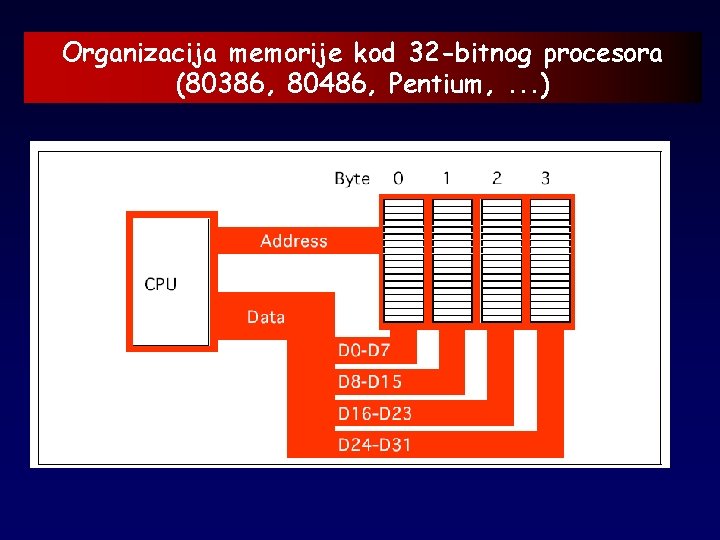

Organizacija memorije kod 32 -bitnog procesora (80386, 80486, Pentium, . . . )

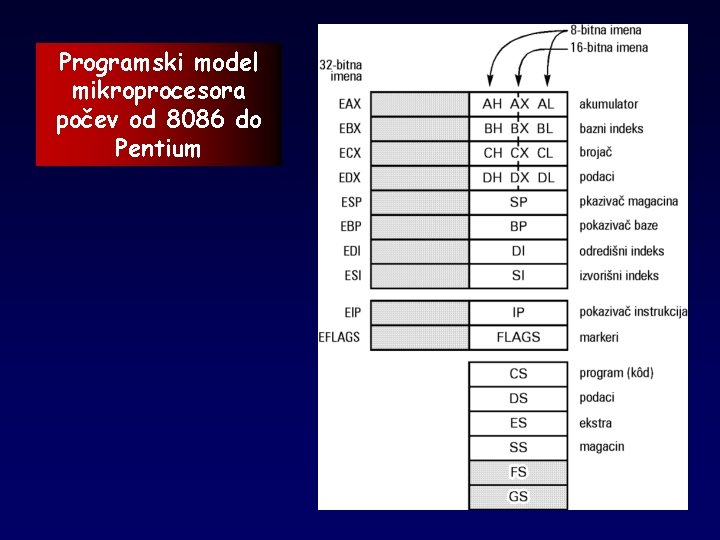

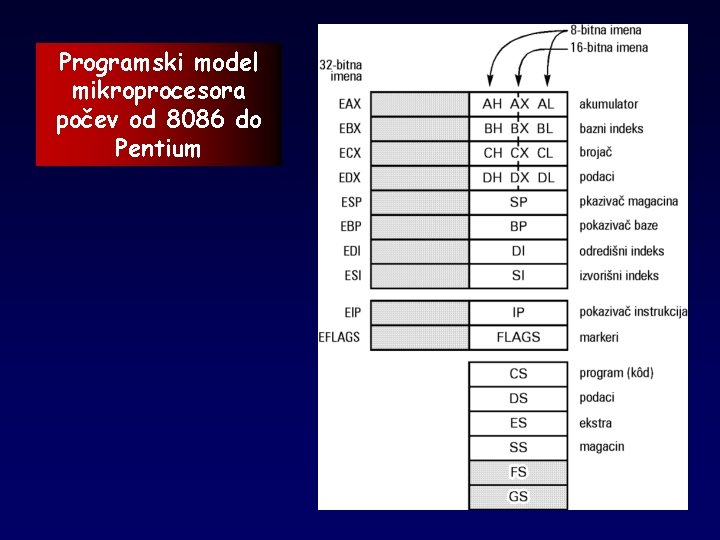

Programski model mikroprocesora počev od 8086 do Pentium

8086 register set

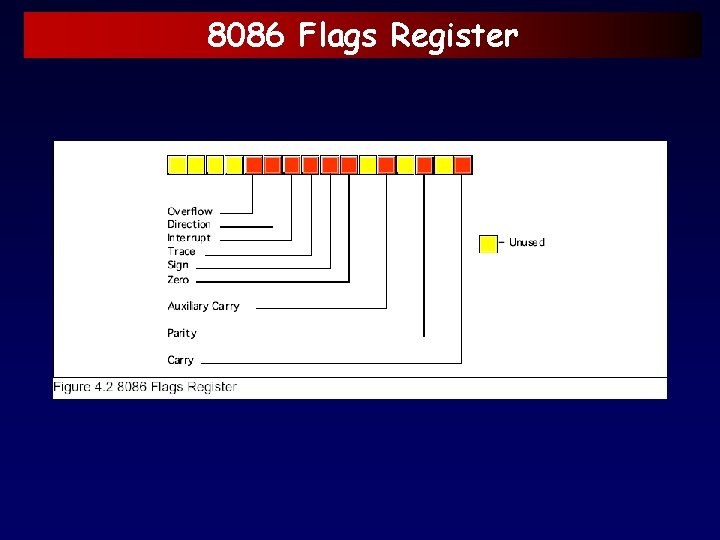

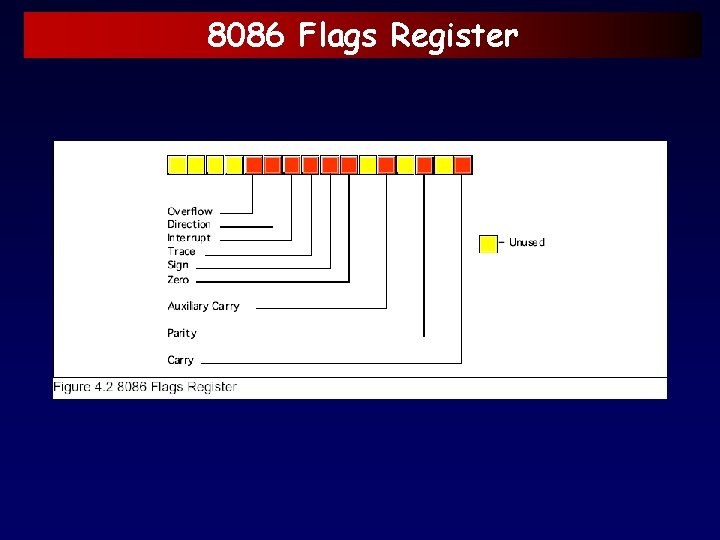

8086 Flags Register

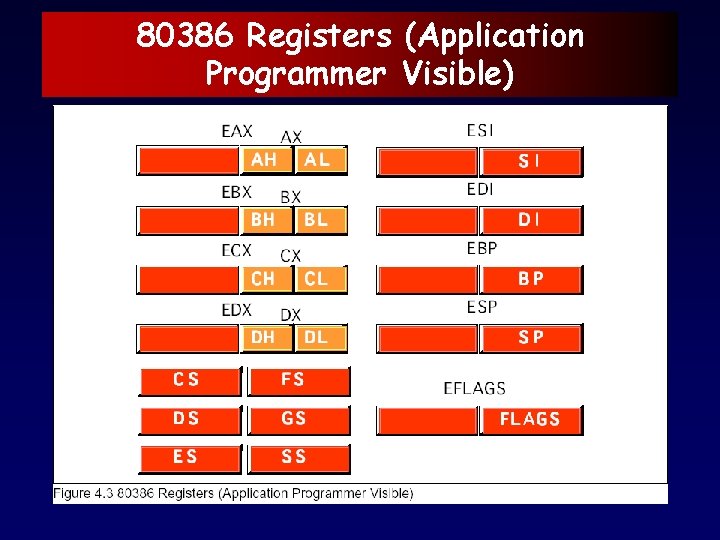

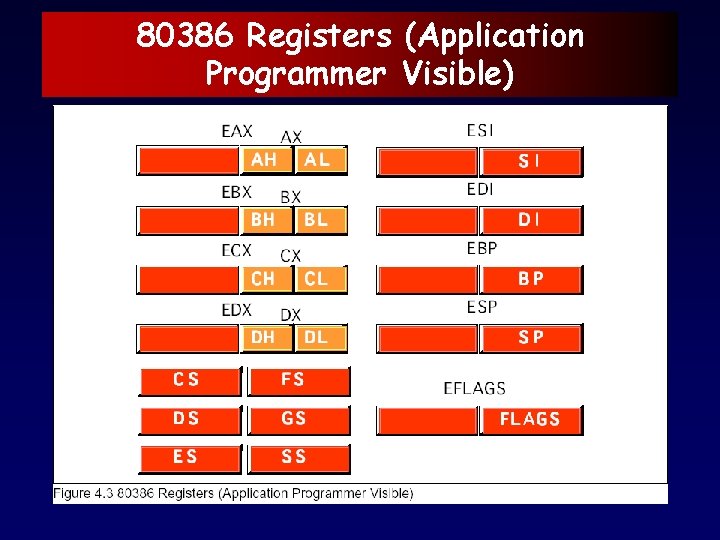

80386 Registers (Application Programmer Visible)

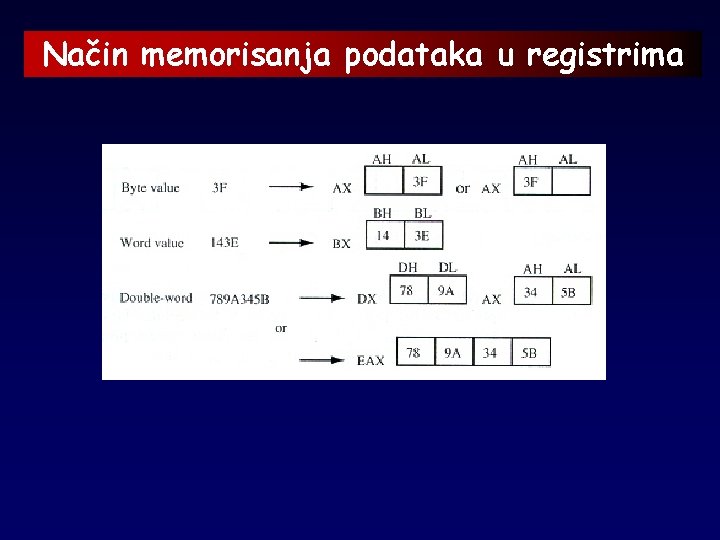

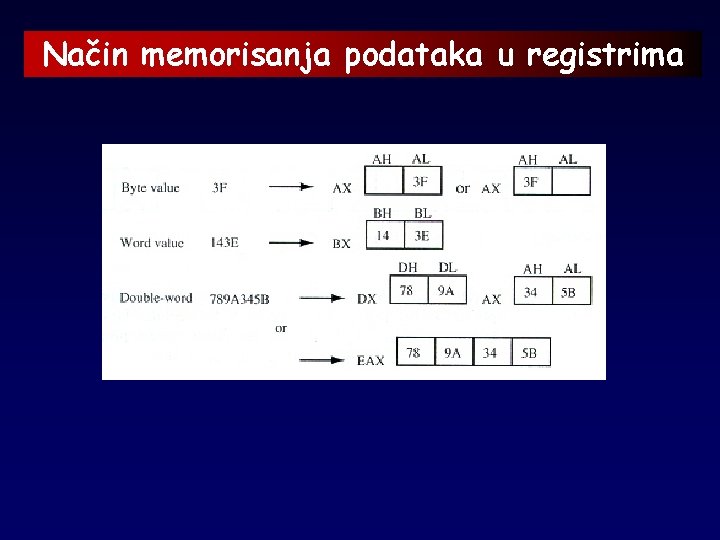

Način memorisanja podataka u registrima

Registri FLAG i EFLAGS za familiju mikroprocesora 80 x 86 i Pentium

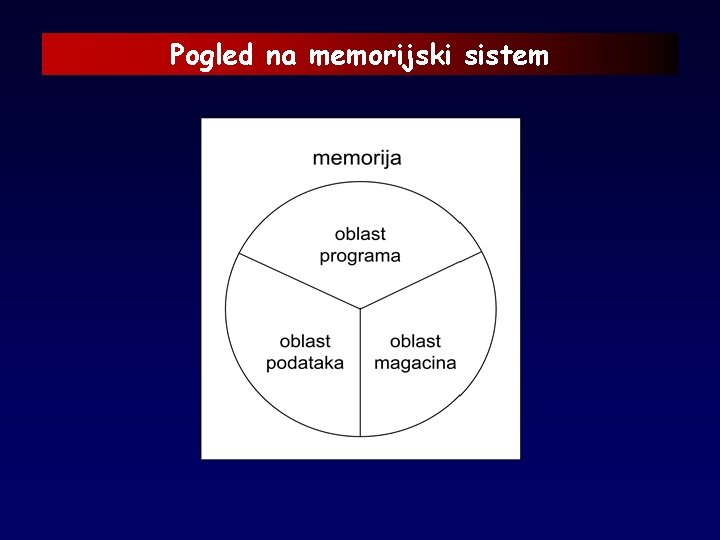

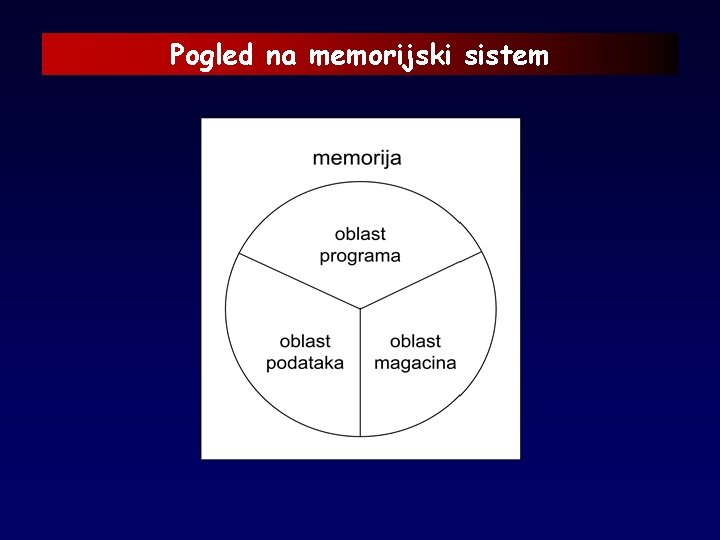

Pogled na memorijski sistem

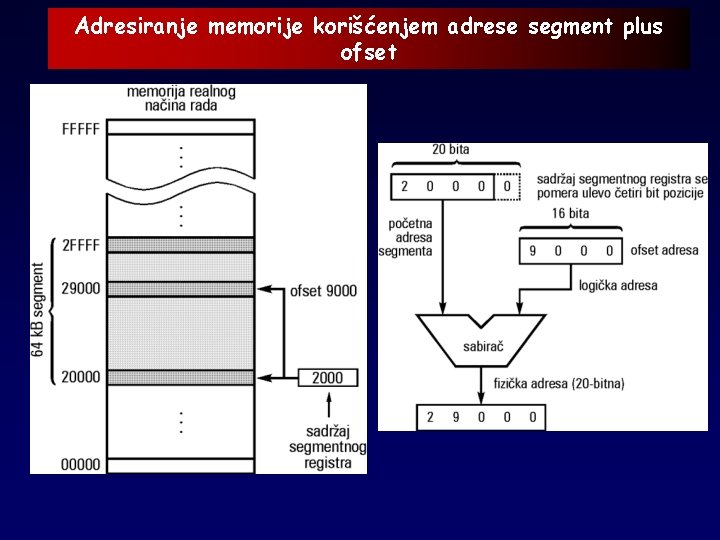

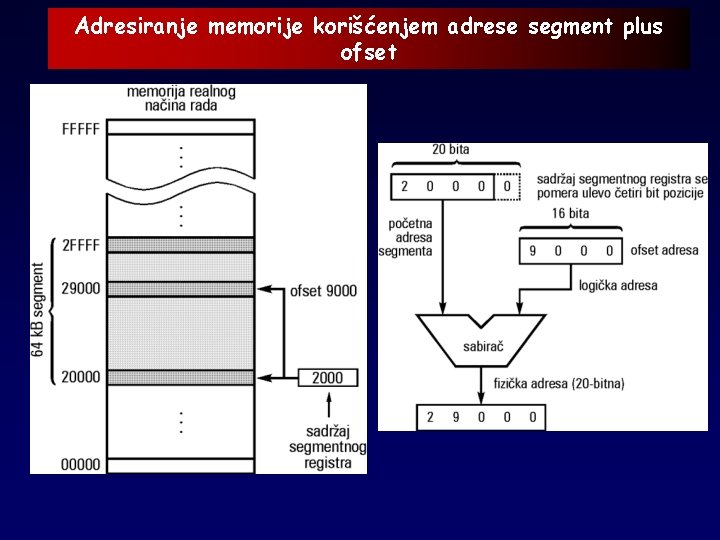

Adresiranje memorije korišćenjem adrese segment plus ofset

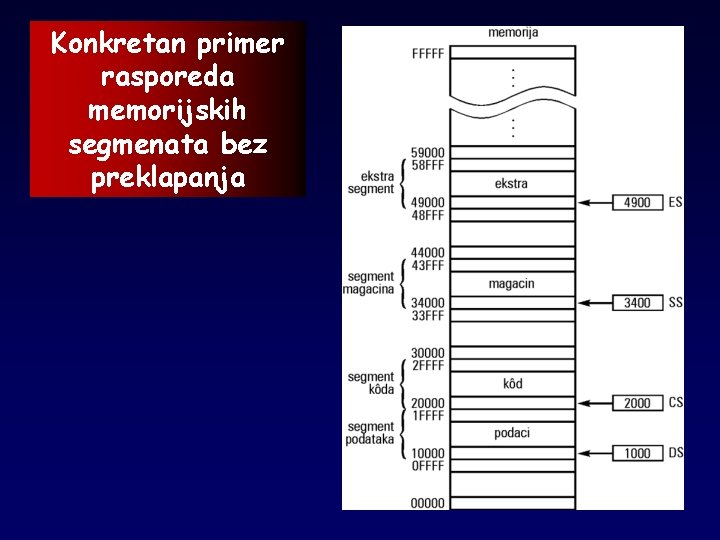

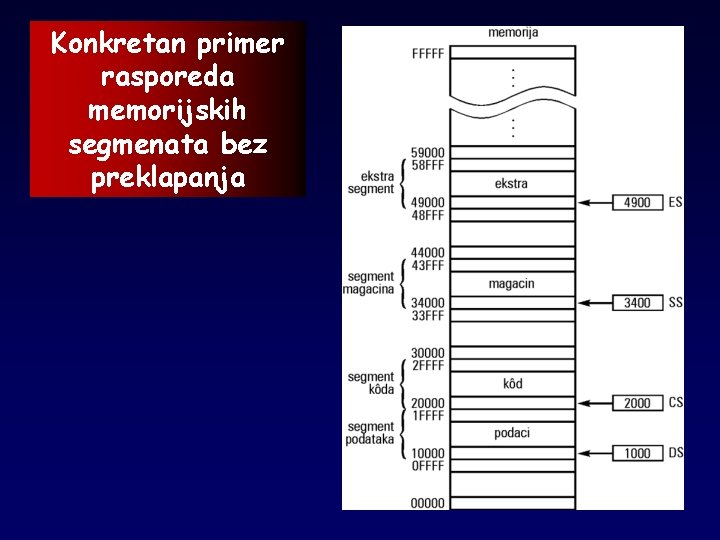

Konkretan primer rasporeda memorijskih segmenata bez preklapanja

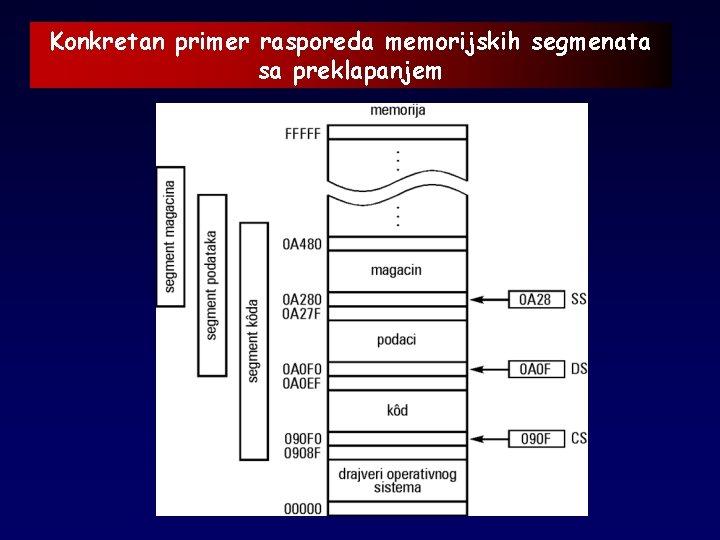

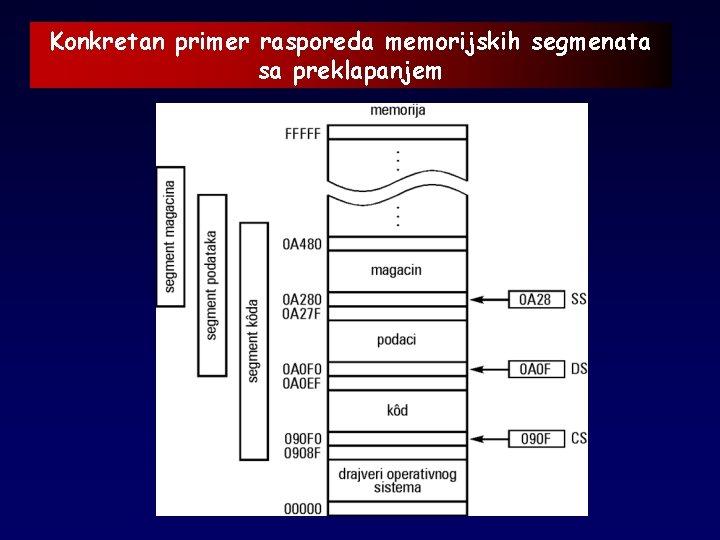

Konkretan primer rasporeda memorijskih segmenata sa preklapanjem

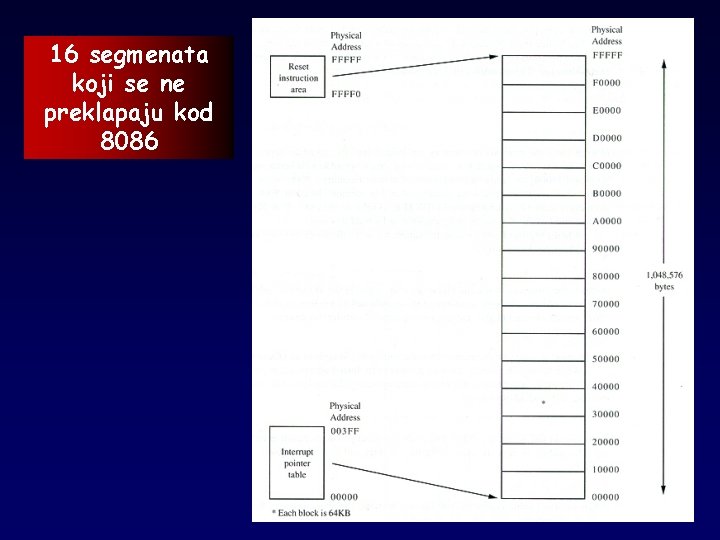

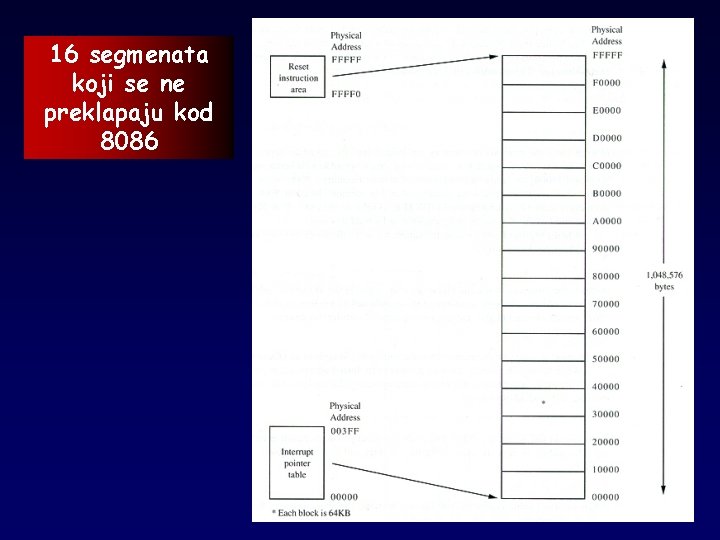

16 segmenata koji se ne preklapaju kod 8086

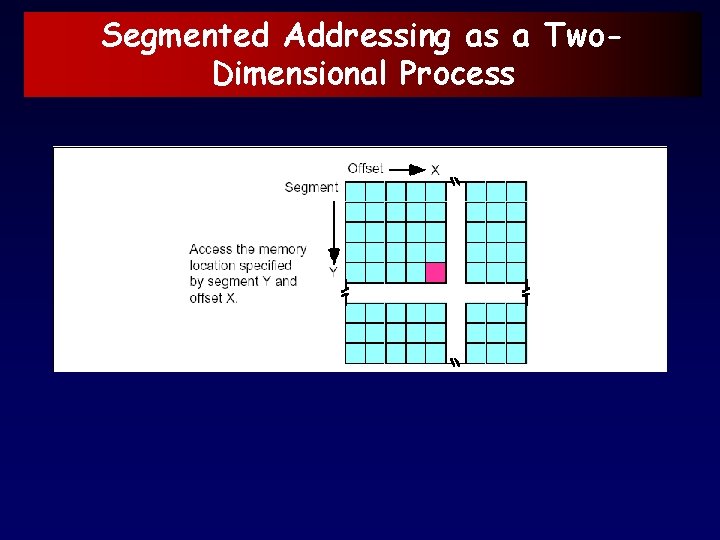

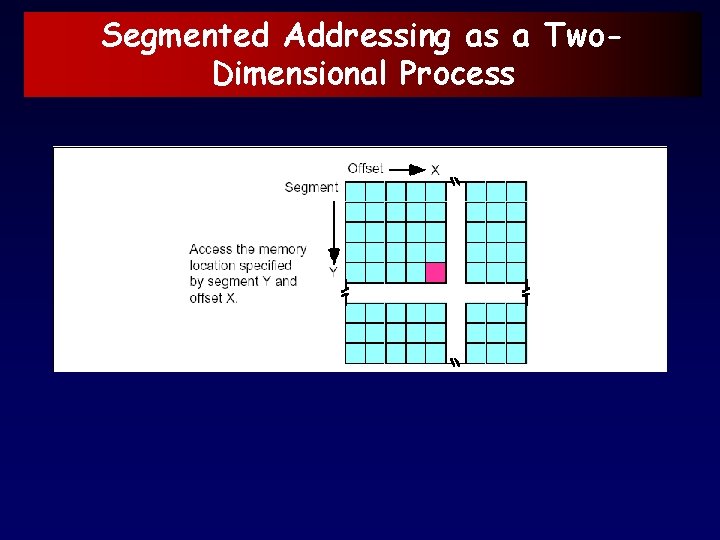

Segmented Addressing as a Two. Dimensional Process

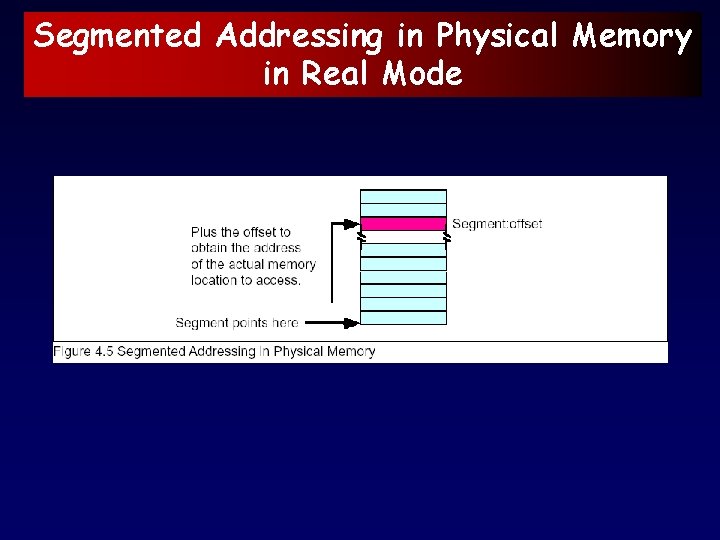

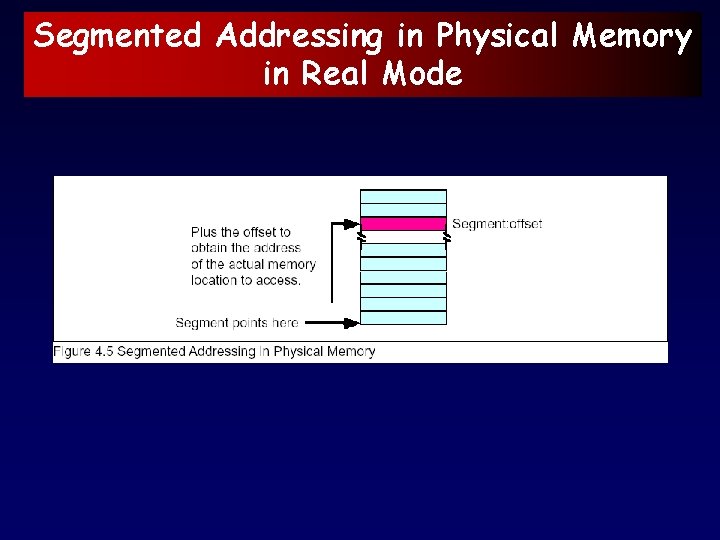

Segmented Addressing in Physical Memory in Real Mode

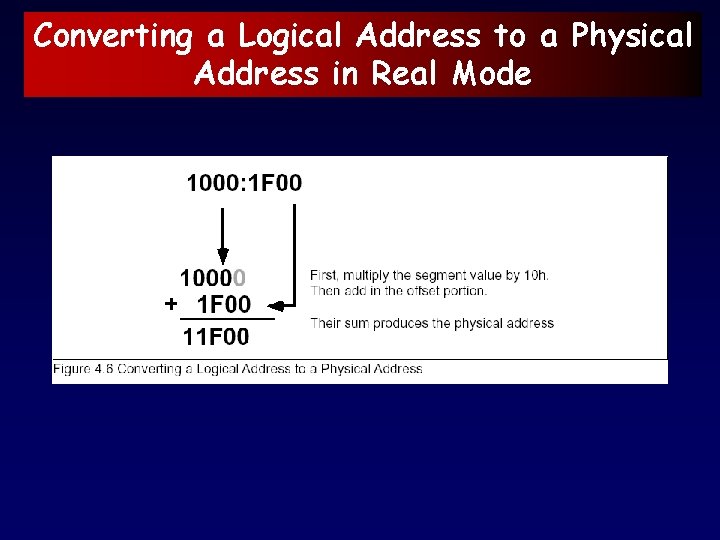

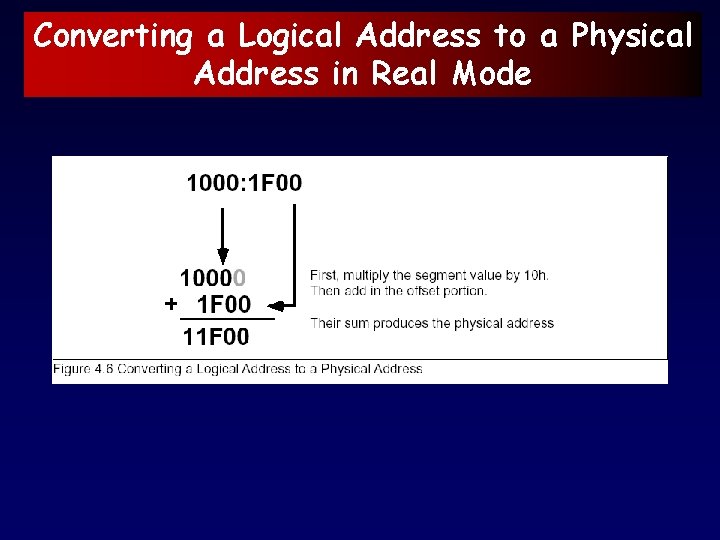

Converting a Logical Address to a Physical Address in Real Mode

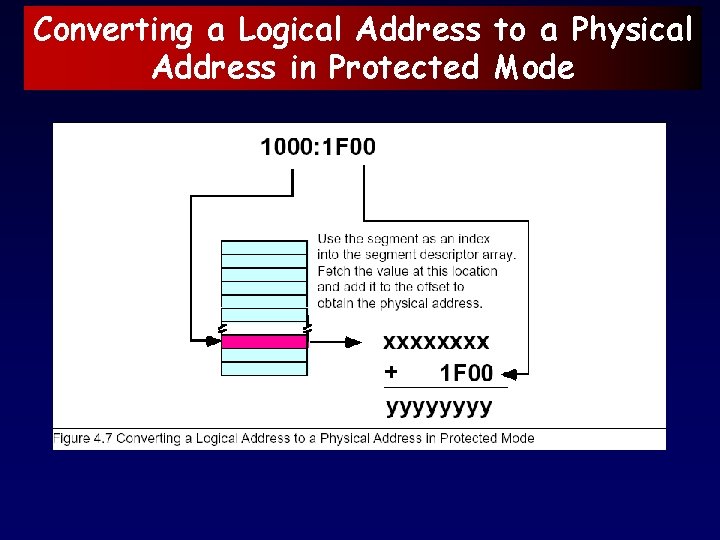

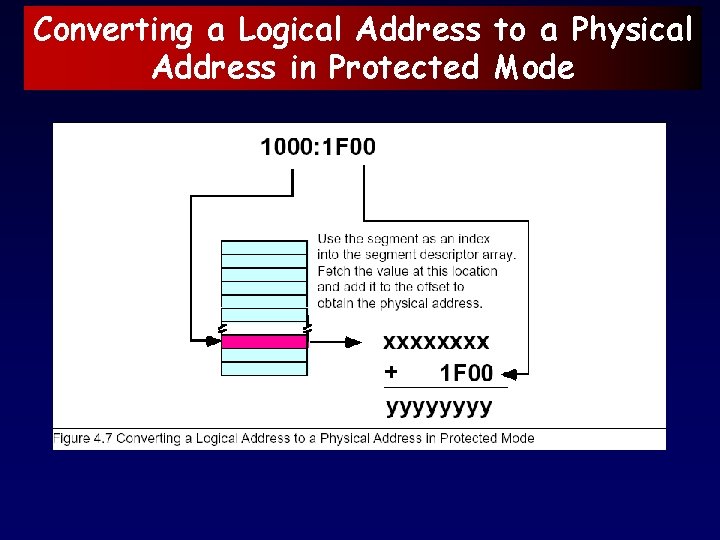

Converting a Logical Address to a Physical Address in Protected Mode

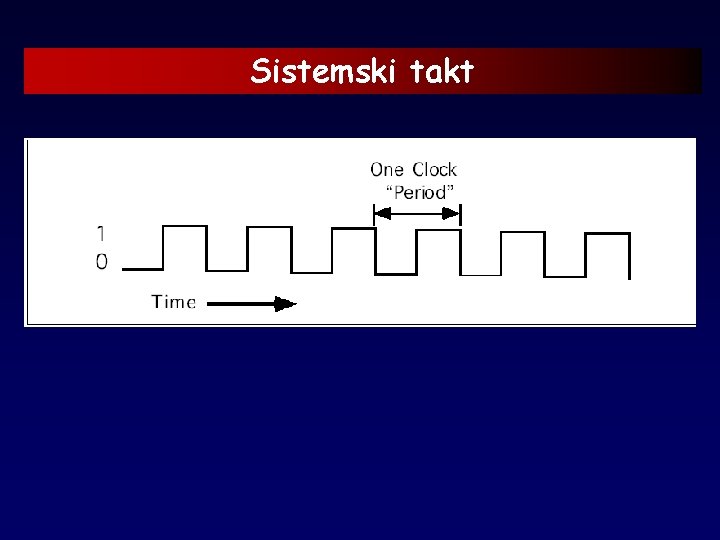

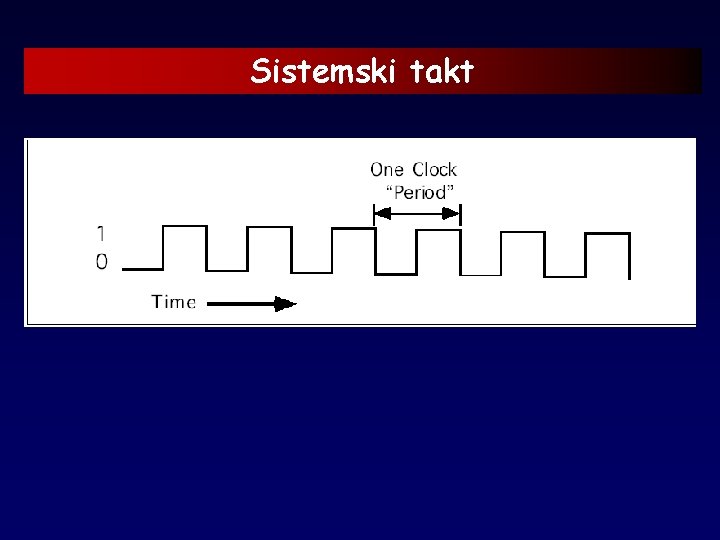

Sistemski takt

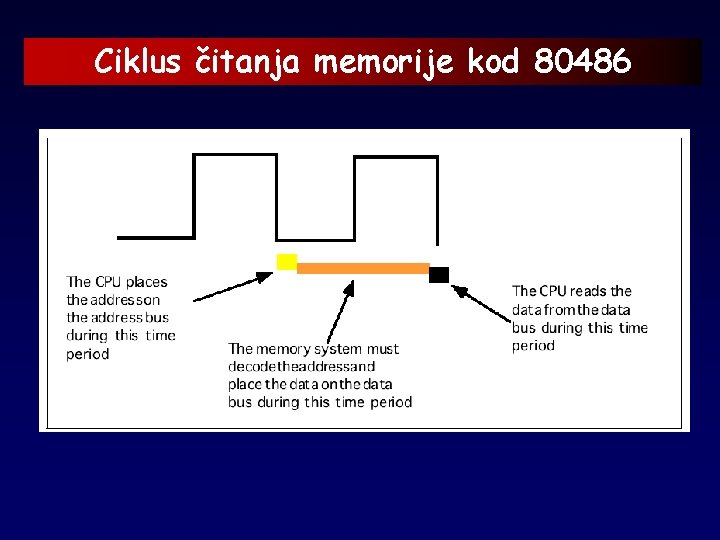

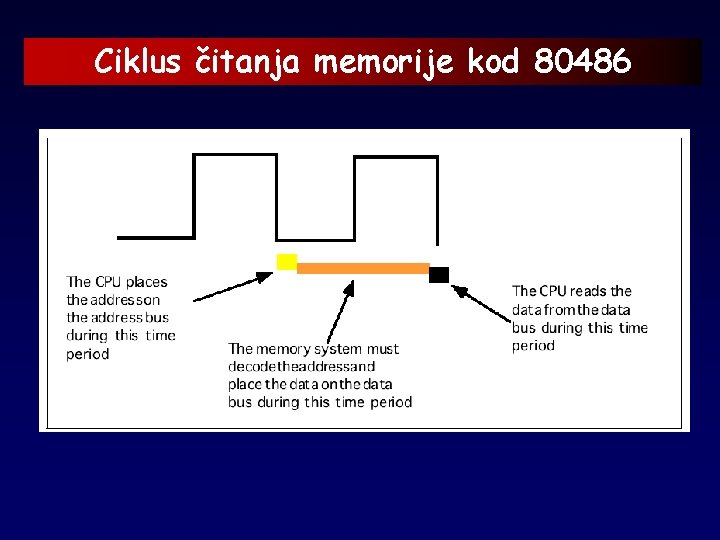

Ciklus čitanja memorije kod 80486

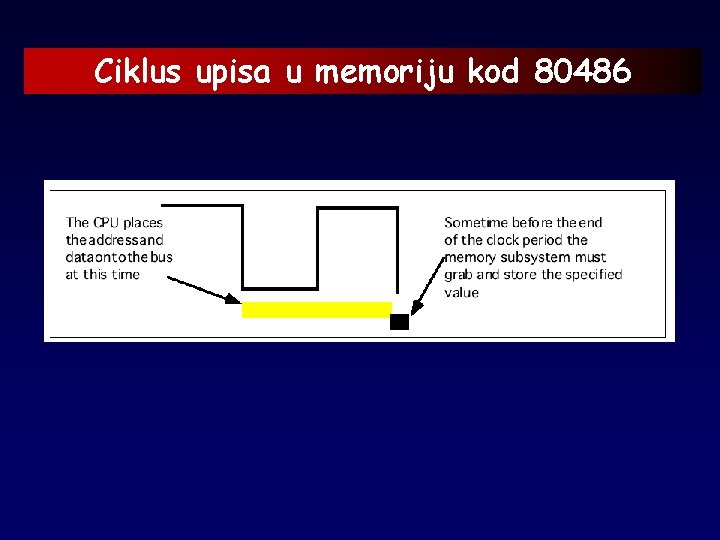

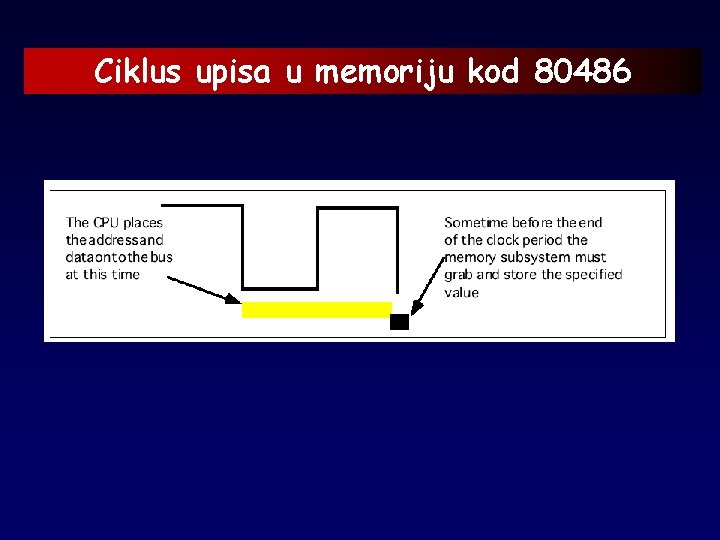

Ciklus upisa u memoriju kod 80486

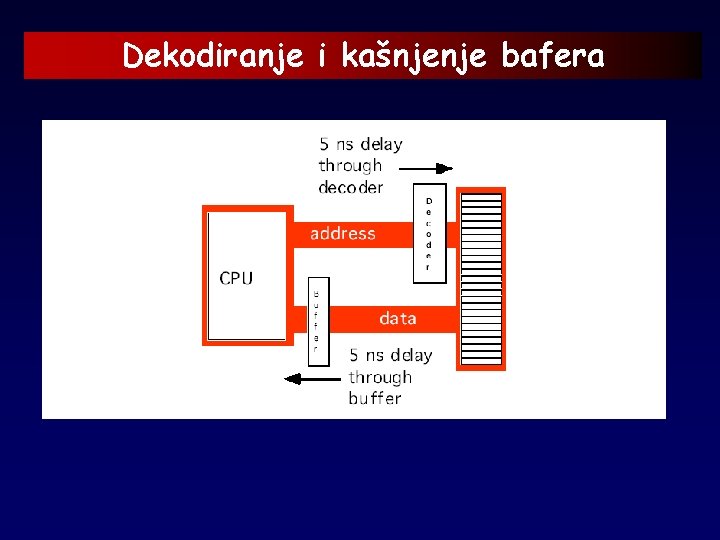

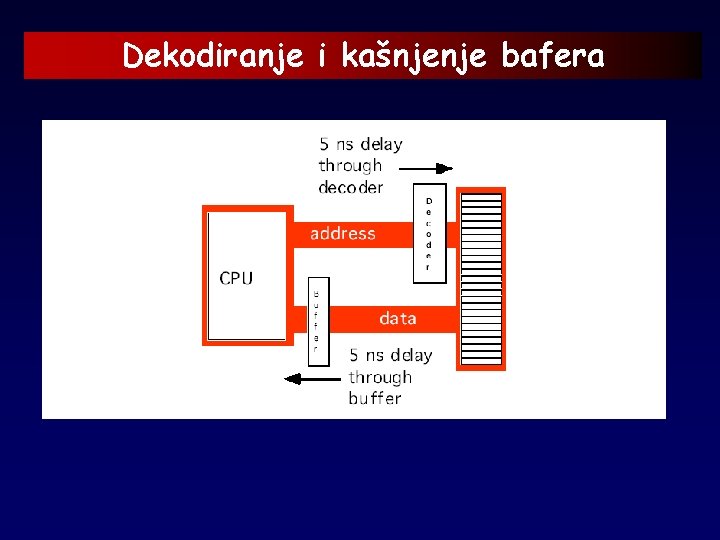

Dekodiranje i kašnjenje bafera

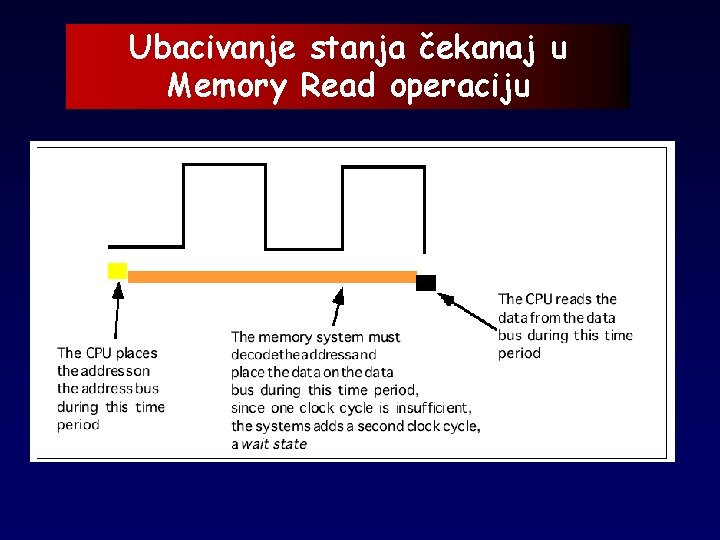

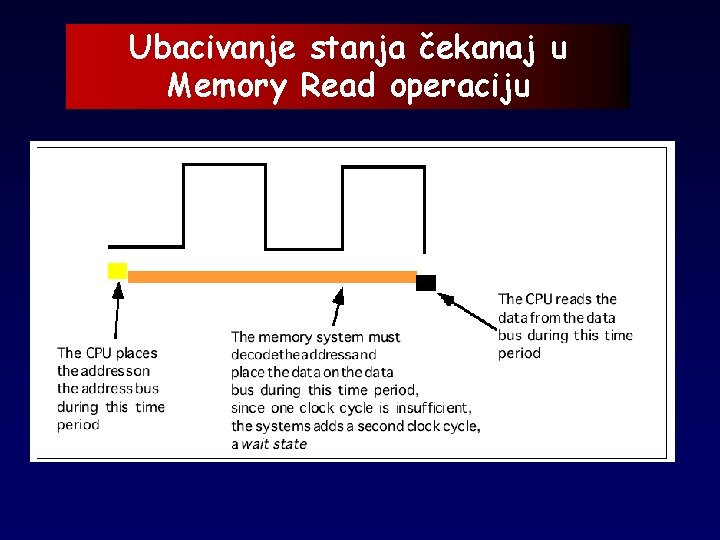

Ubacivanje stanja čekanaj u Memory Read operaciju

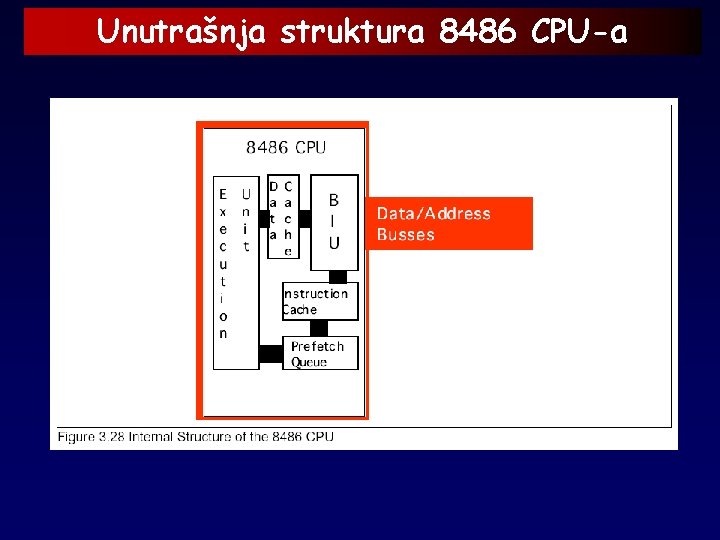

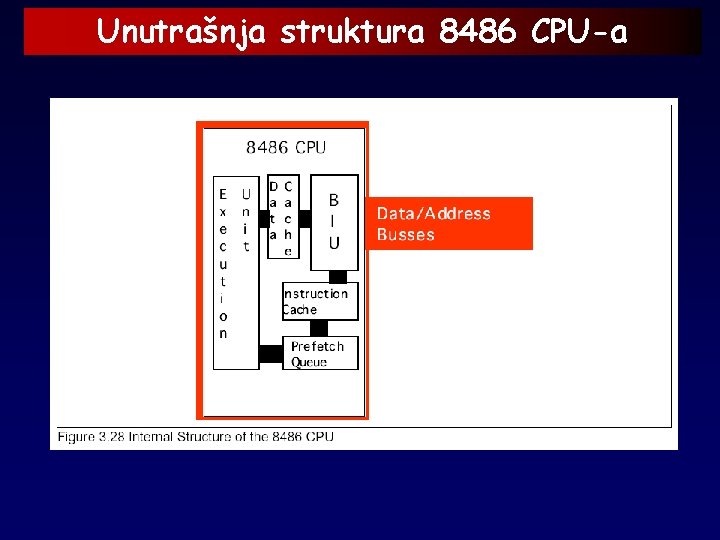

Unutrašnja struktura 8486 CPU-a

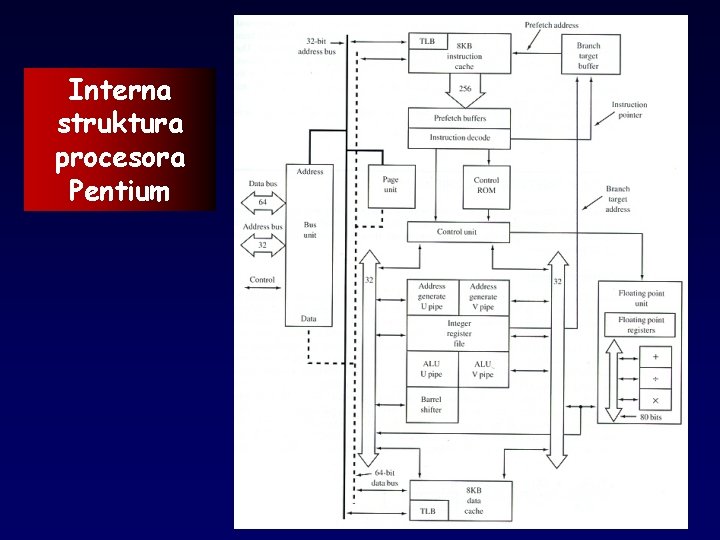

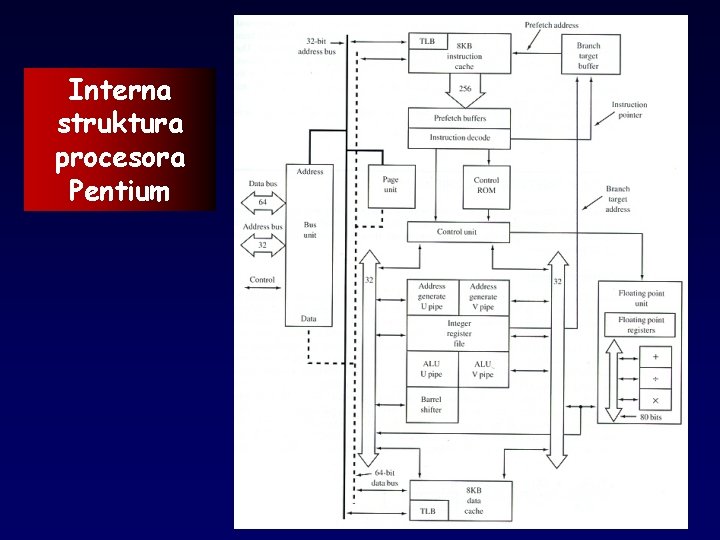

Interna struktura procesora Pentium

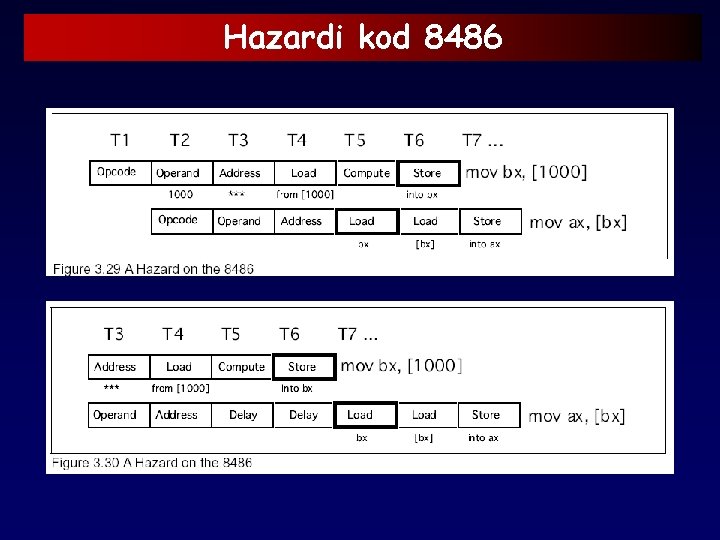

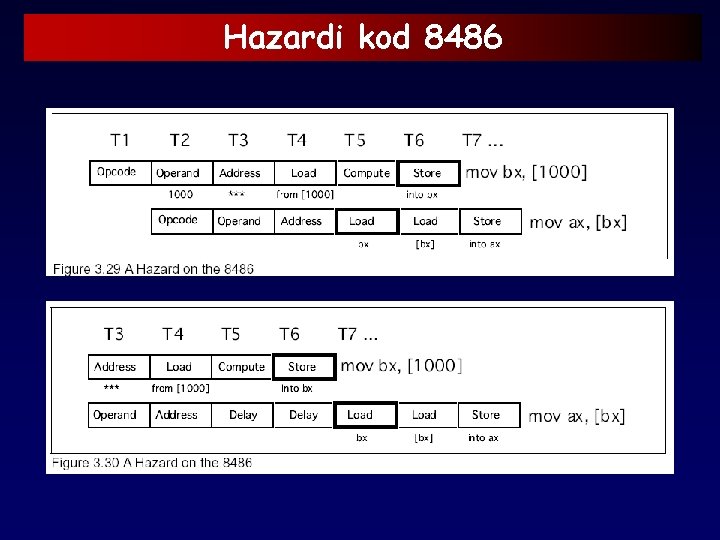

Hazardi kod 8486

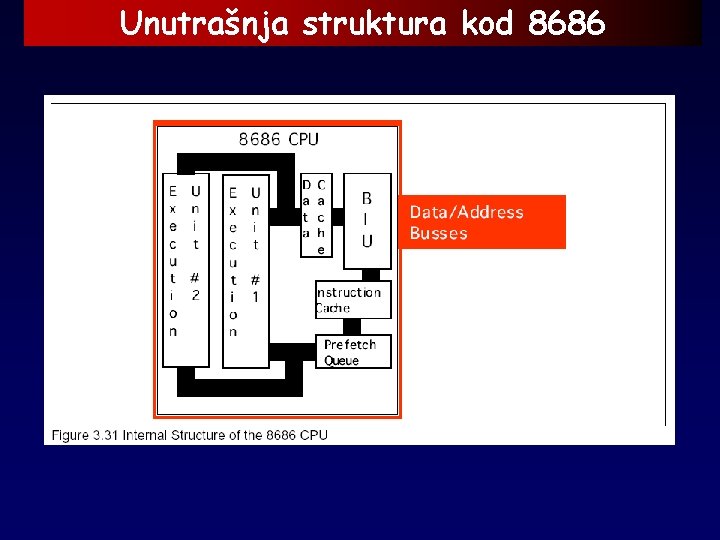

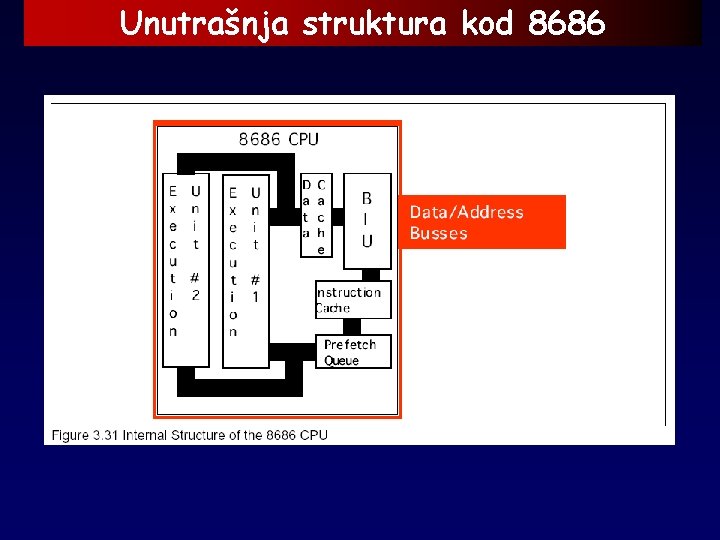

Unutrašnja struktura kod 8686

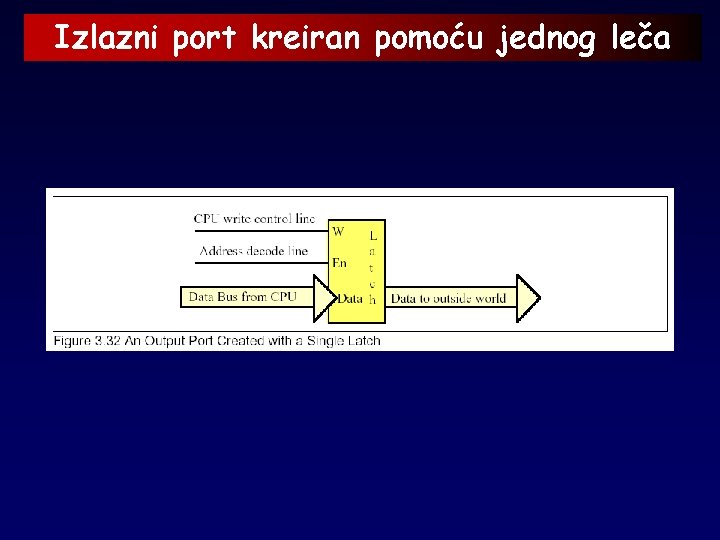

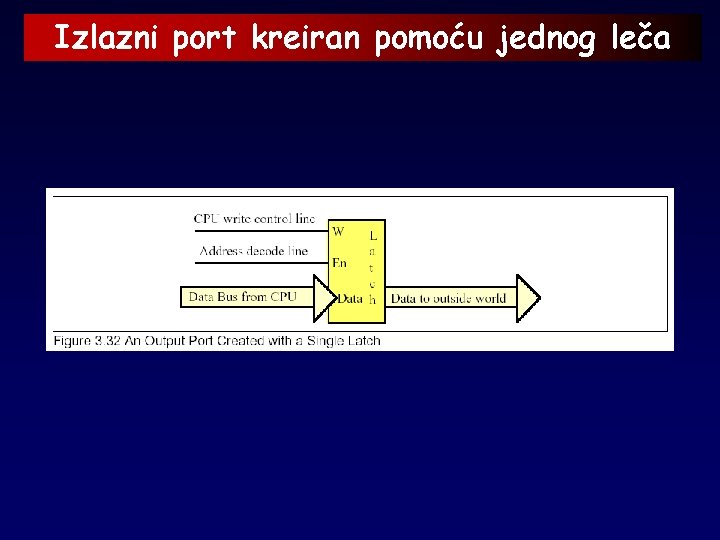

Izlazni port kreiran pomoću jednog leča

Ulazno/izlazni port zahteva dva leča

Inputing Data Vector Number

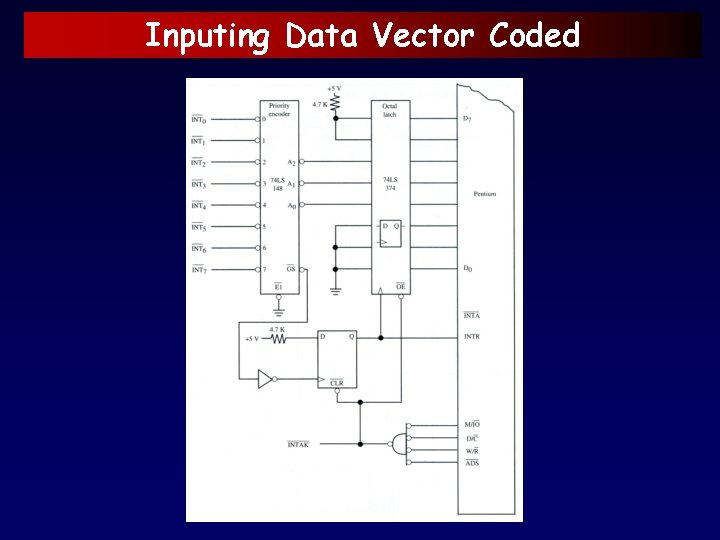

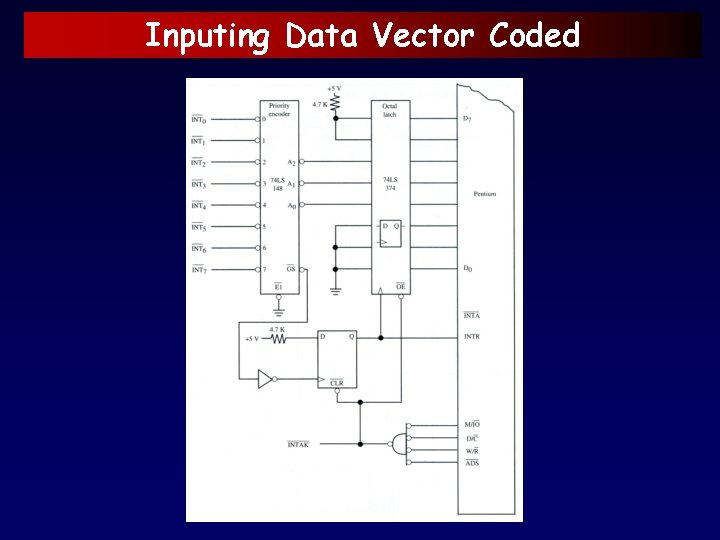

Inputing Data Vector Coded

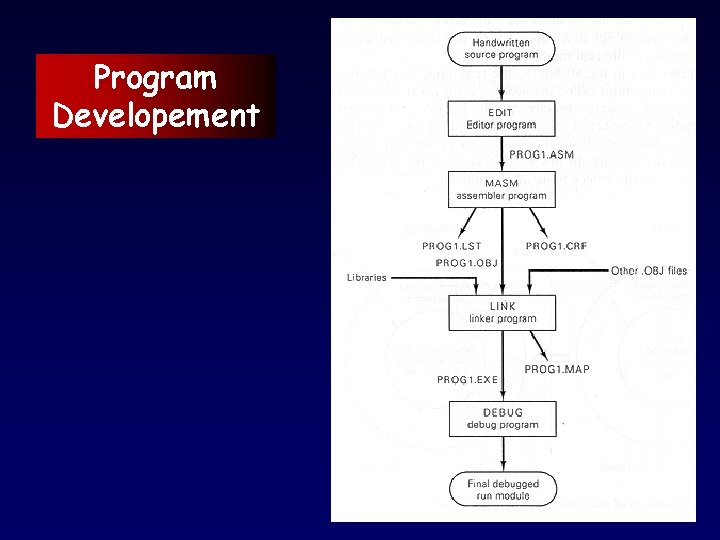

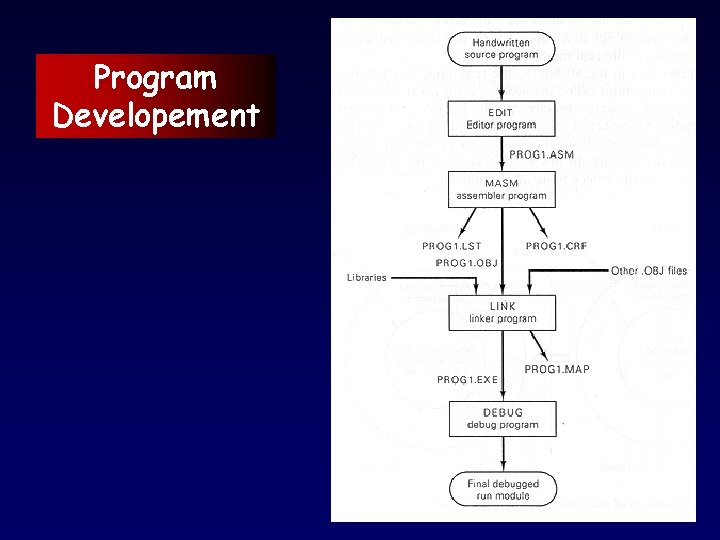

Program Developement

Adresni načini rada kod 8086

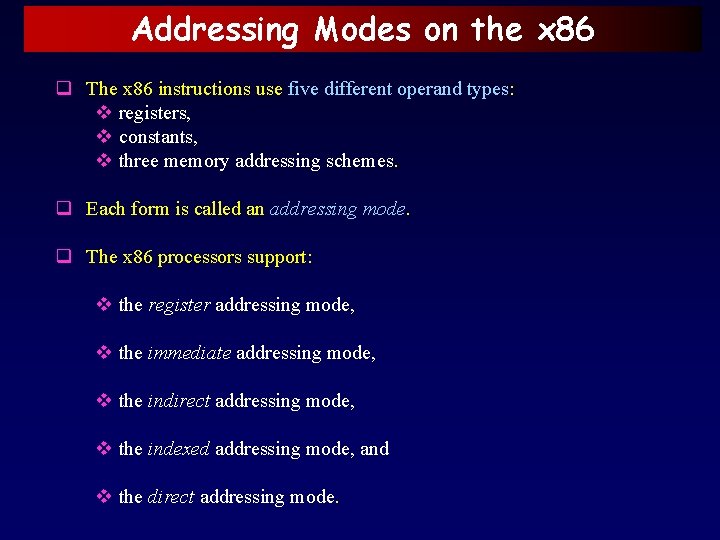

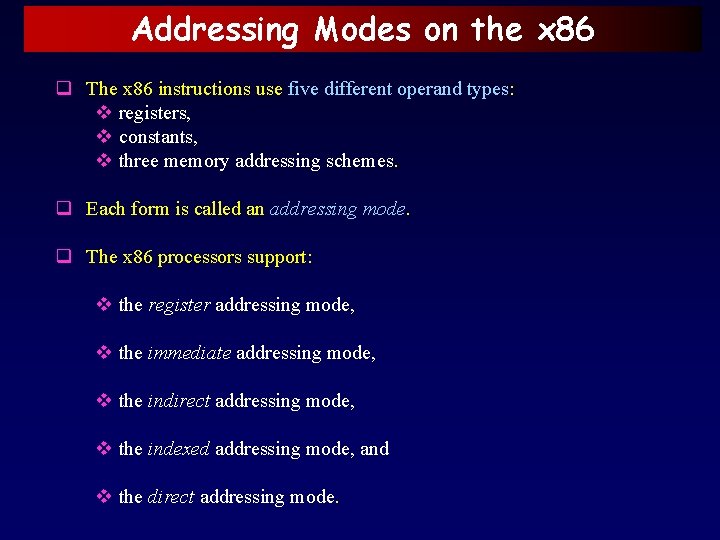

Addressing Modes on the x 86 q The x 86 instructions use five different operand types: v registers, v constants, v three memory addressing schemes. q Each form is called an addressing mode. q The x 86 processors support: v the register addressing mode, v the immediate addressing mode, v the indirect addressing mode, v the indexed addressing mode, and v the direct addressing mode.

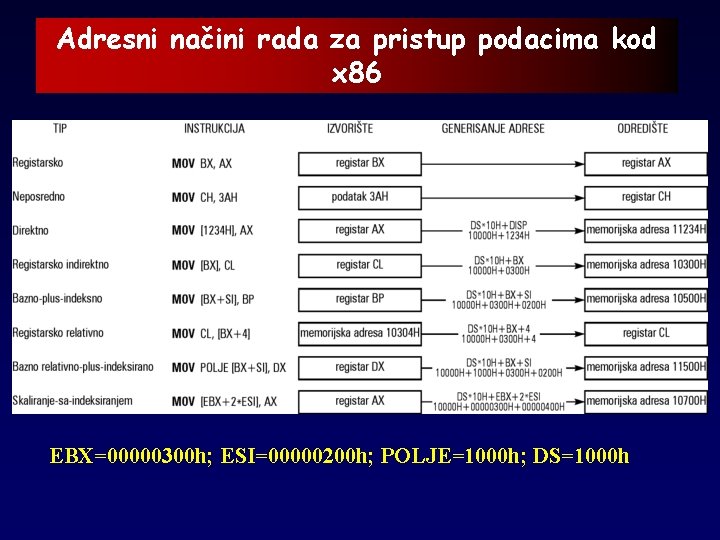

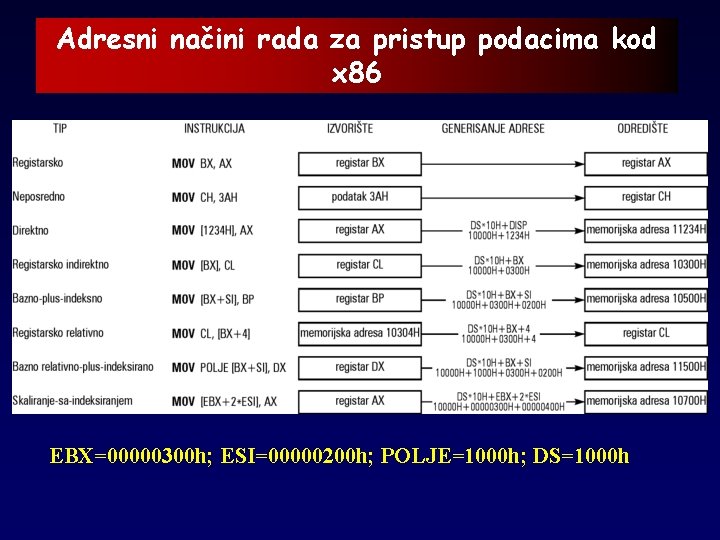

Adresni načini rada za pristup podacima kod x 86 EBX=00000300 h; ESI=00000200 h; POLJE=1000 h; DS=1000 h

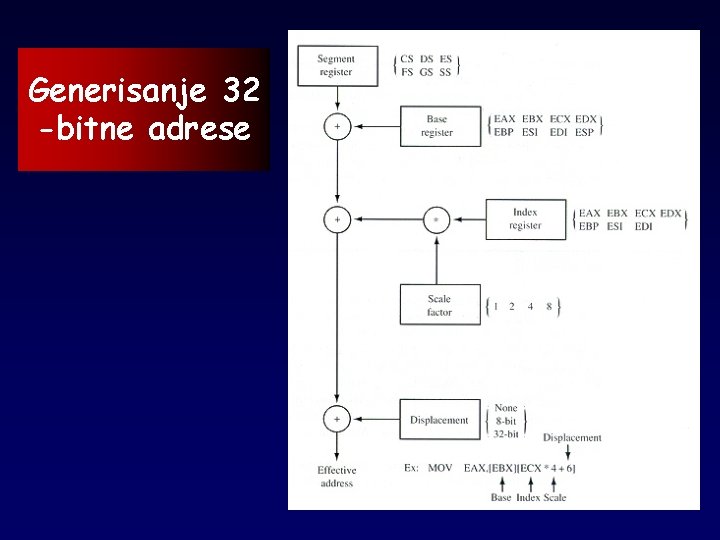

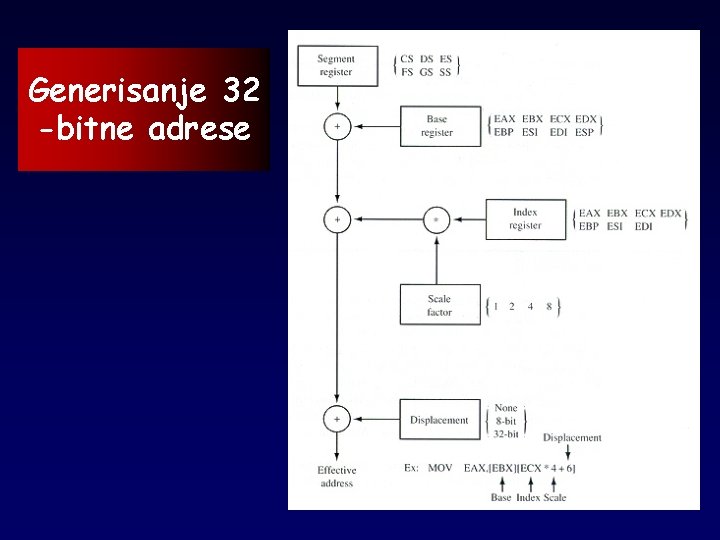

Generisanje 32 -bitne adrese

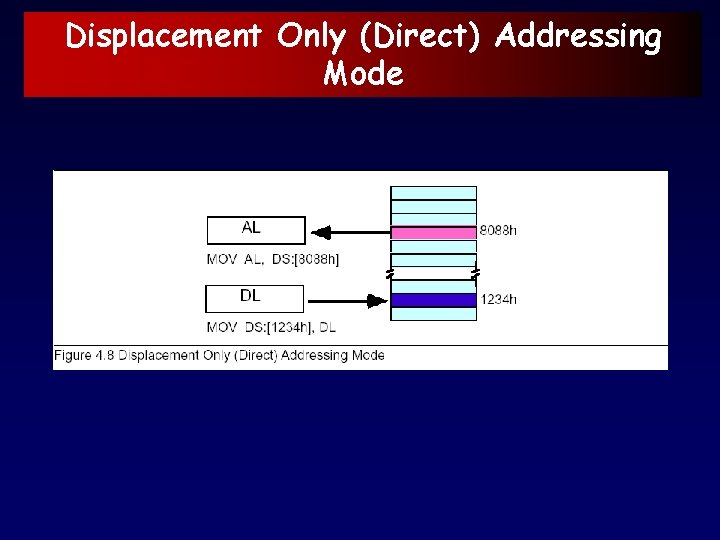

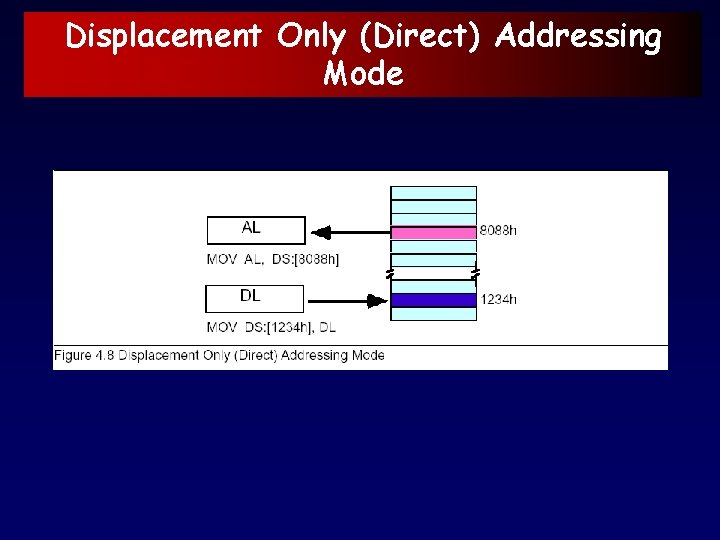

Displacement Only (Direct) Addressing Mode

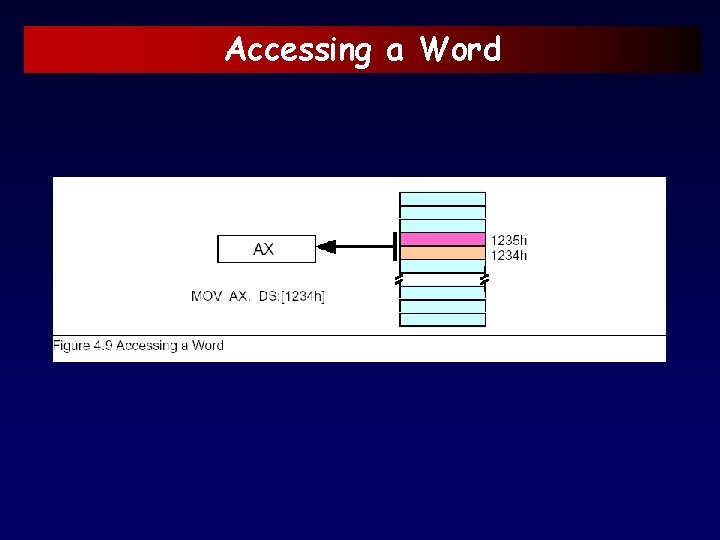

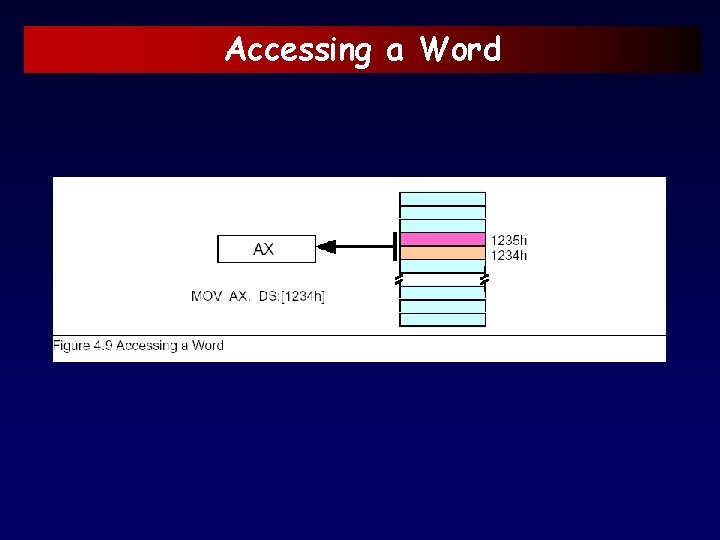

Accessing a Word

![BX Addressing Mode [BX] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-43.jpg)

[BX] Addressing Mode

![BP Addressing Mode [BP] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-44.jpg)

[BP] Addressing Mode

![BXdisp Addressing Mode [BX+disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-45.jpg)

[BX+disp] Addressing Mode

![BPdisp Addressing Mode [BP+disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-46.jpg)

[BP+disp] Addressing Mode

![BXSI Addressing Mode [BX+SI] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-47.jpg)

[BX+SI] Addressing Mode

![BPSI Addressing Mode [BP+SI] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-48.jpg)

[BP+SI] Addressing Mode

![BX SI disp Addressing Mode [BX + SI + disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-49.jpg)

[BX + SI + disp] Addressing Mode

![BP SI disp Addressing Mode [BP + SI + disp] Addressing Mode](https://slidetodoc.com/presentation_image_h2/527d66b2ae8194e3ffed0e5d5539cb83/image-50.jpg)

[BP + SI + disp] Addressing Mode

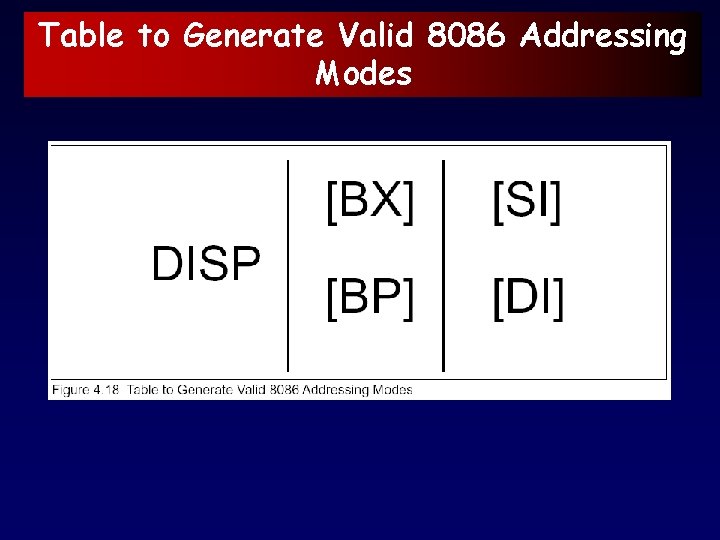

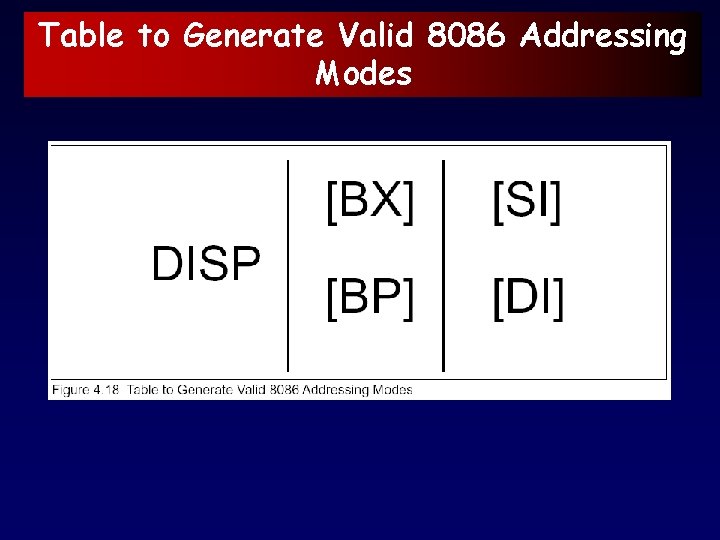

Table to Generate Valid 8086 Addressing Modes

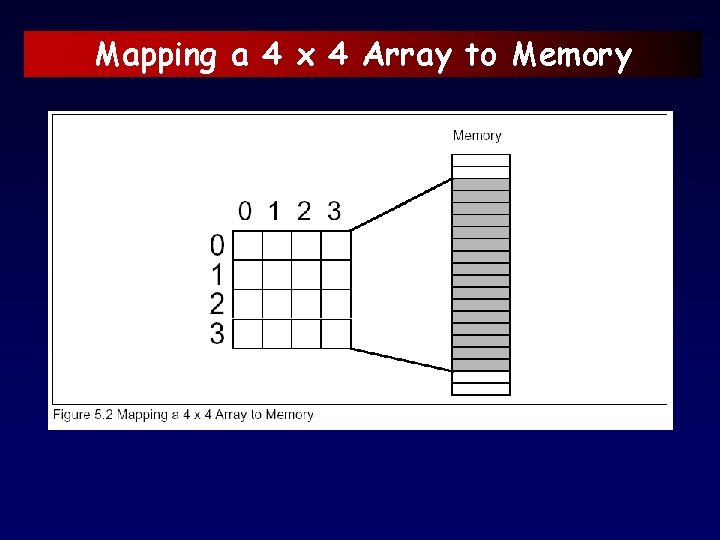

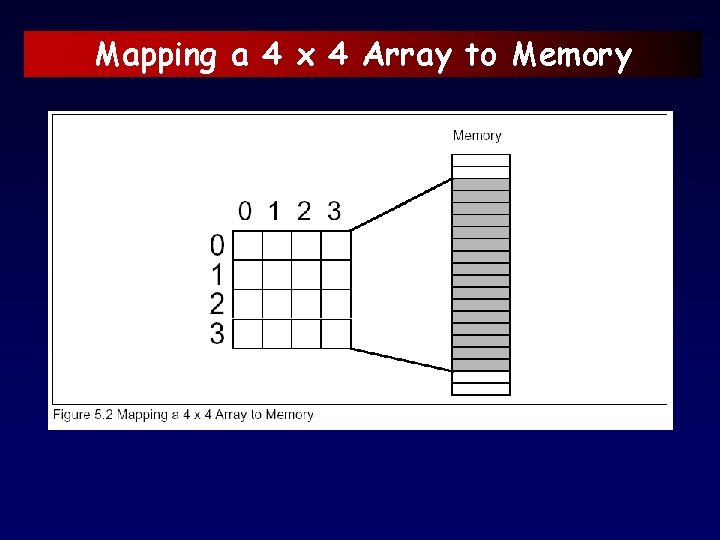

Mapping a 4 x 4 Array to Memory

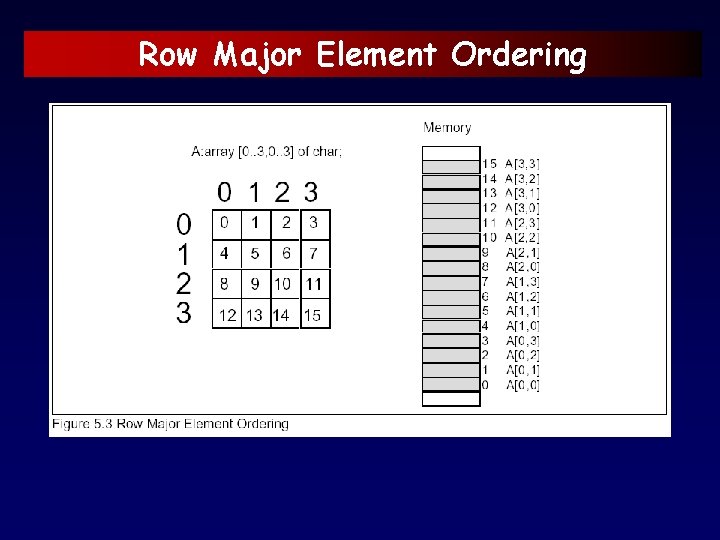

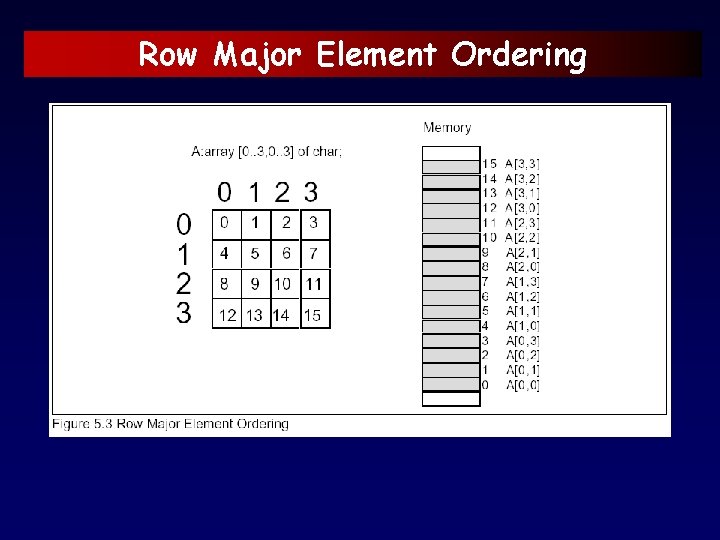

Row Major Element Ordering

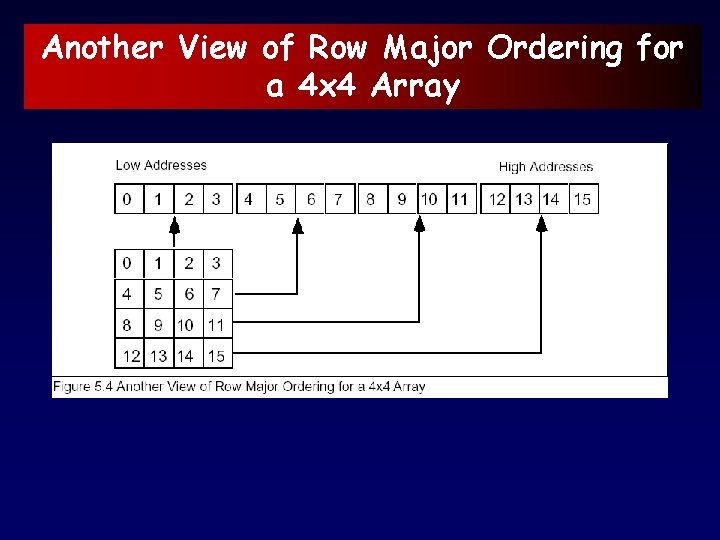

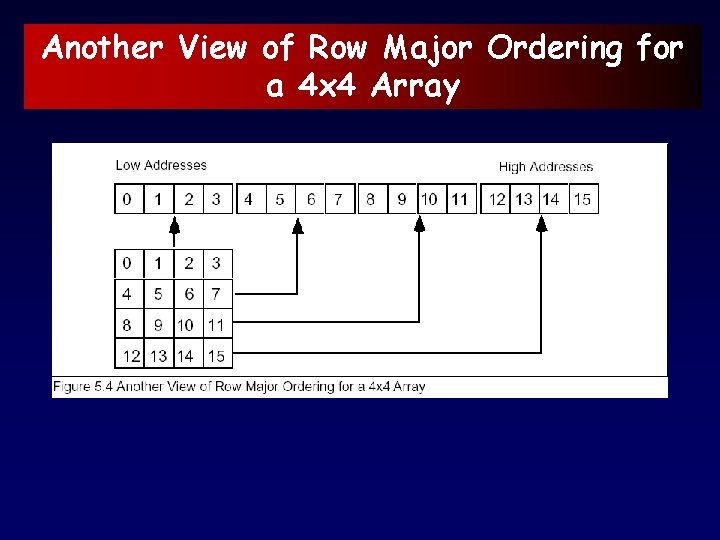

Another View of Row Major Ordering for a 4 x 4 Array

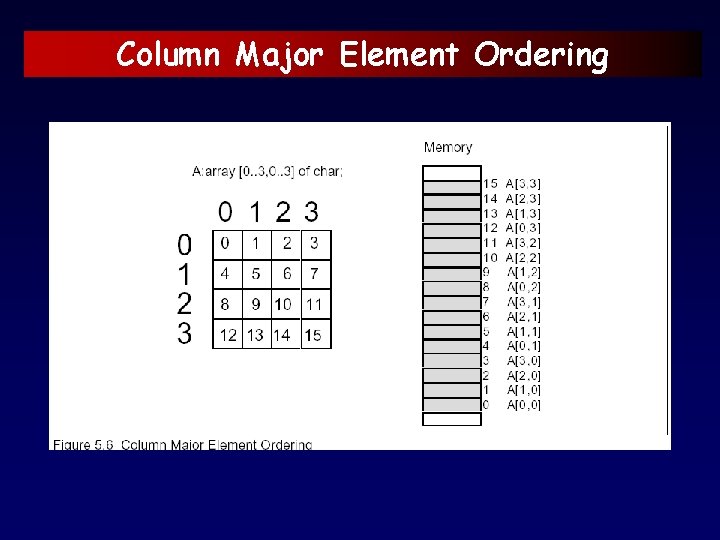

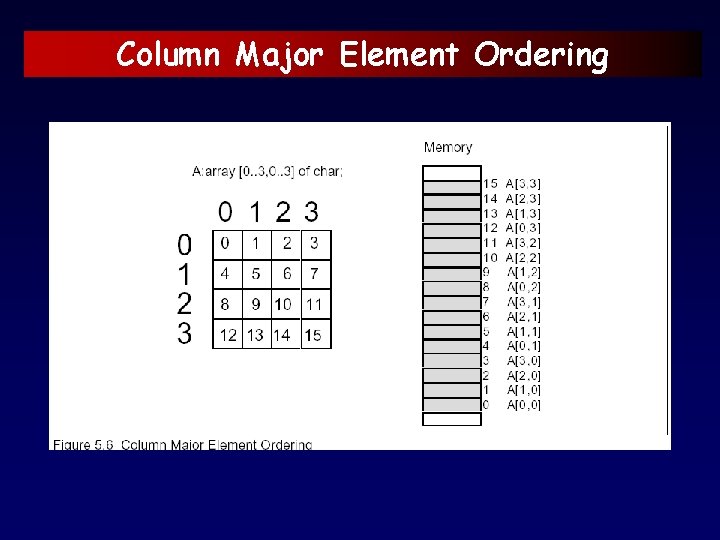

Column Major Element Ordering

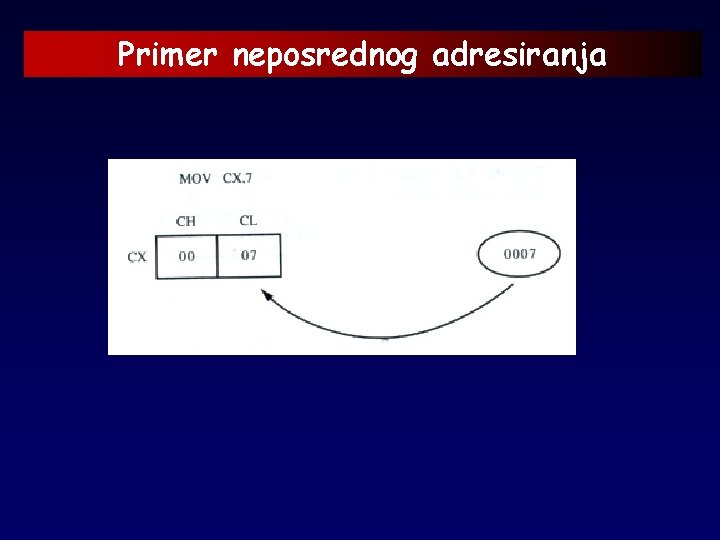

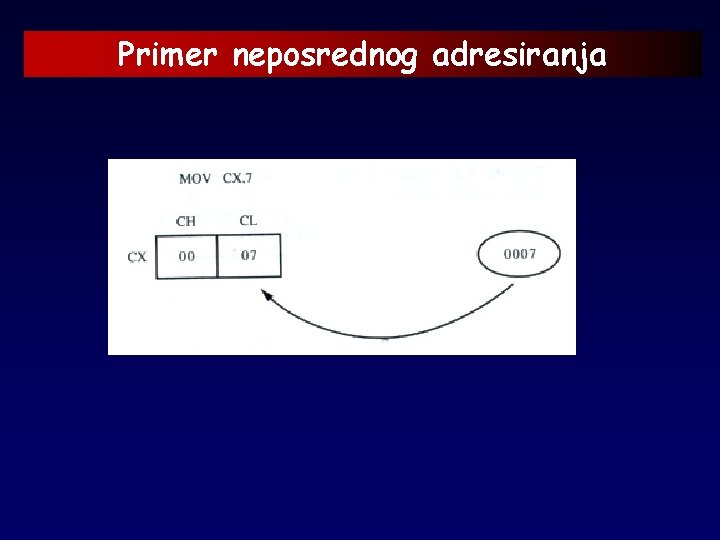

Primer neposrednog adresiranja

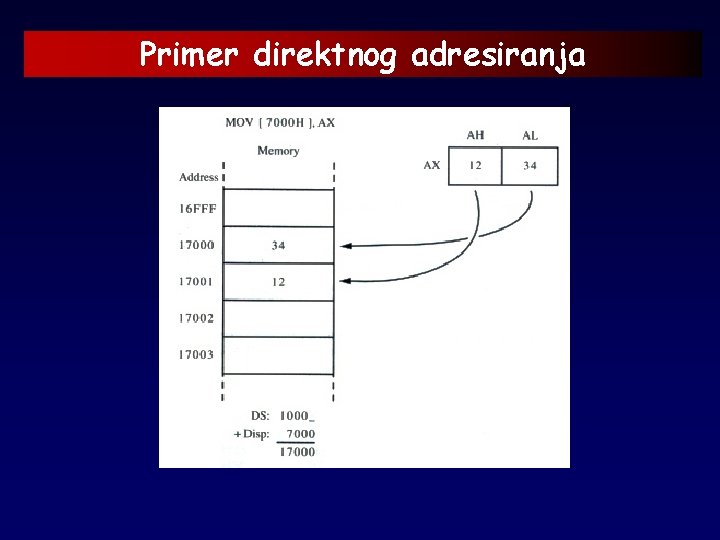

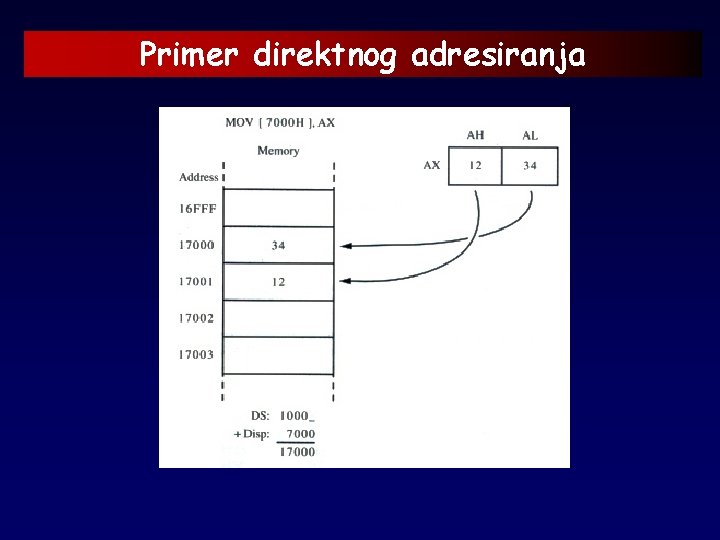

Primer direktnog adresiranja

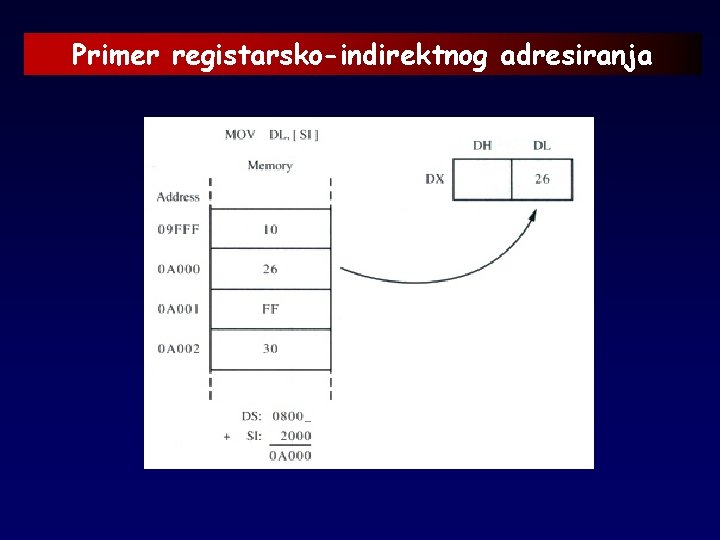

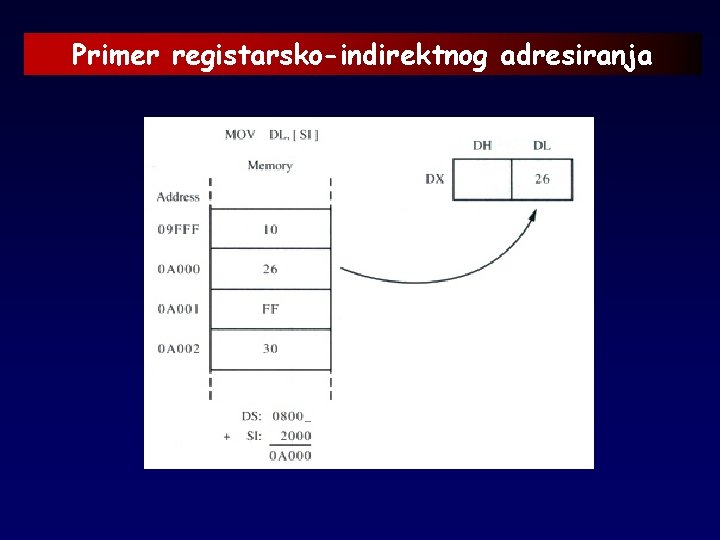

Primer registarsko-indirektnog adresiranja

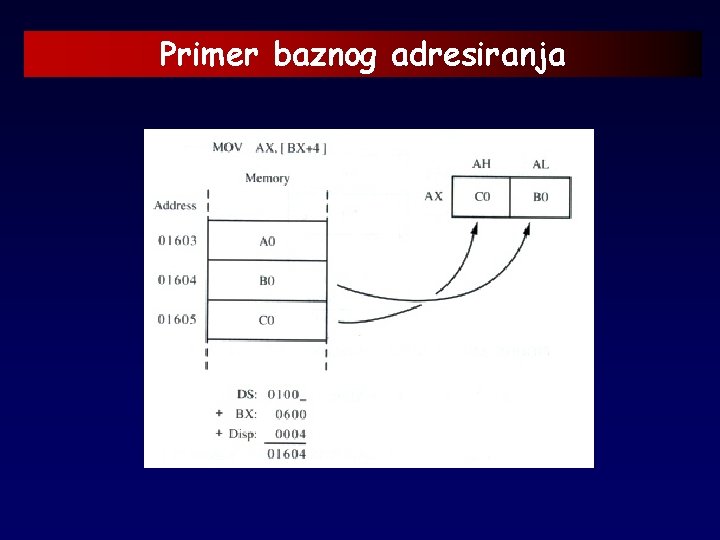

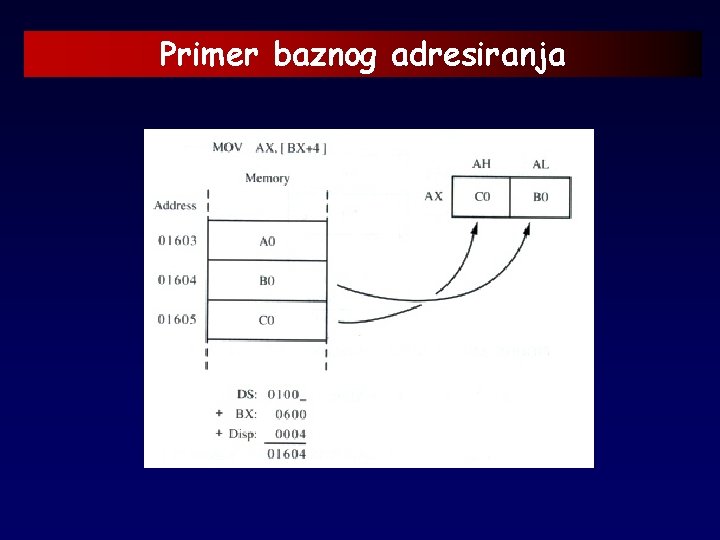

Primer baznog adresiranja

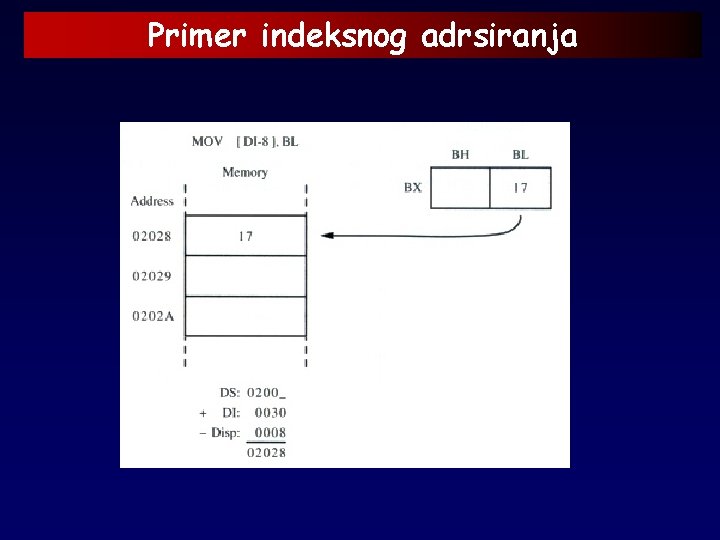

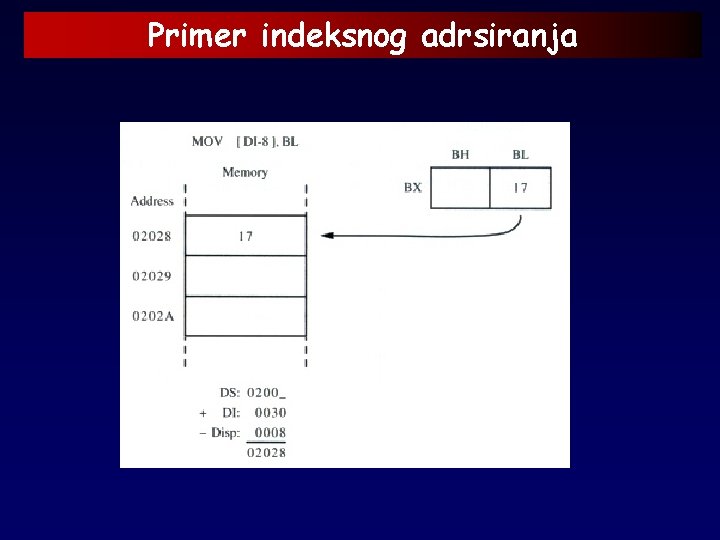

Primer indeksnog adrsiranja

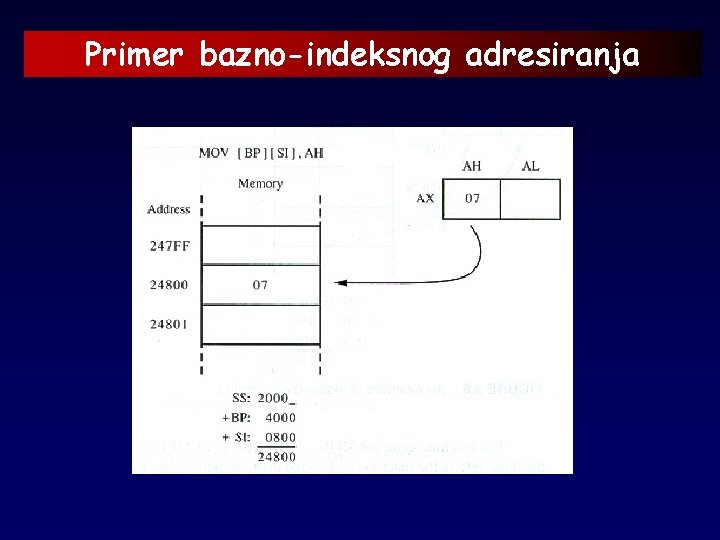

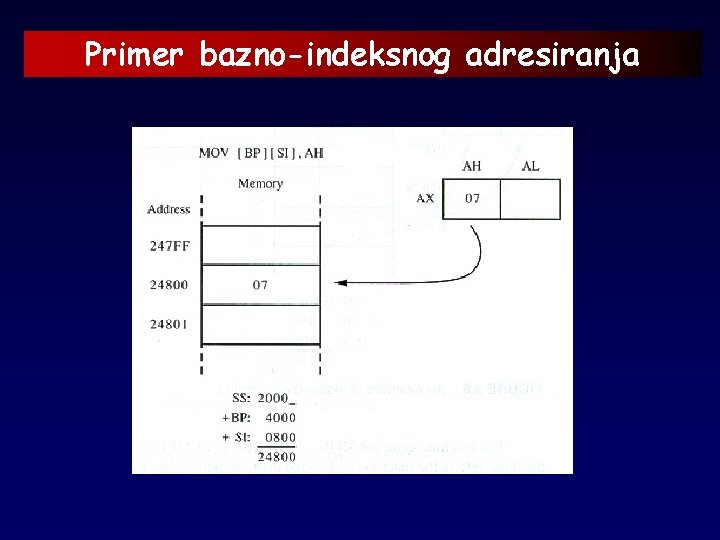

Primer bazno-indeksnog adresiranja

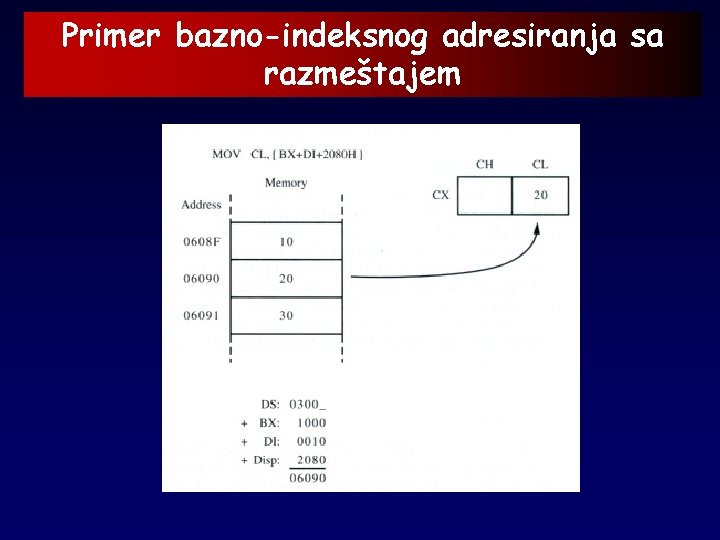

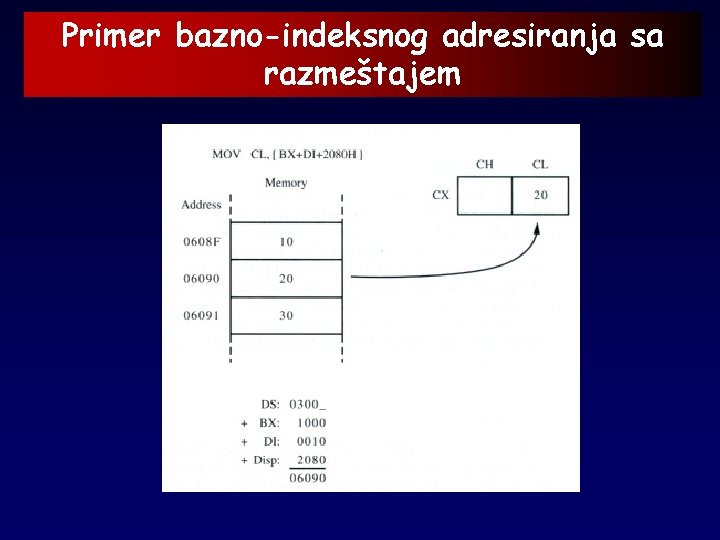

Primer bazno-indeksnog adresiranja sa razmeštajem

Format instrukcija

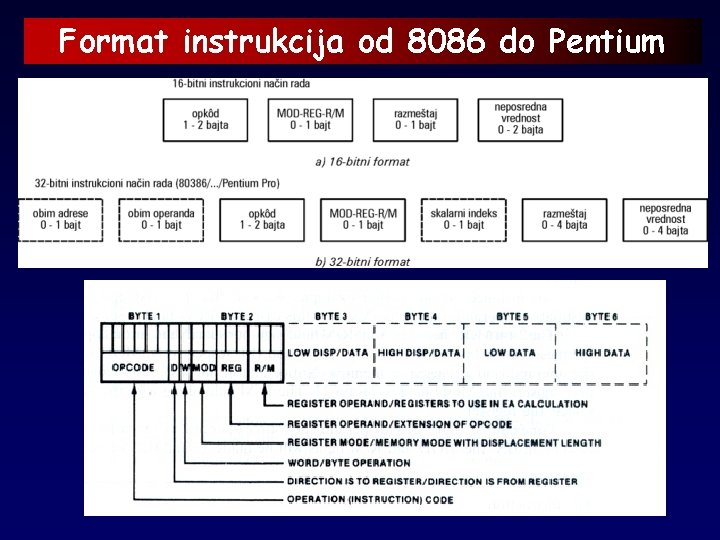

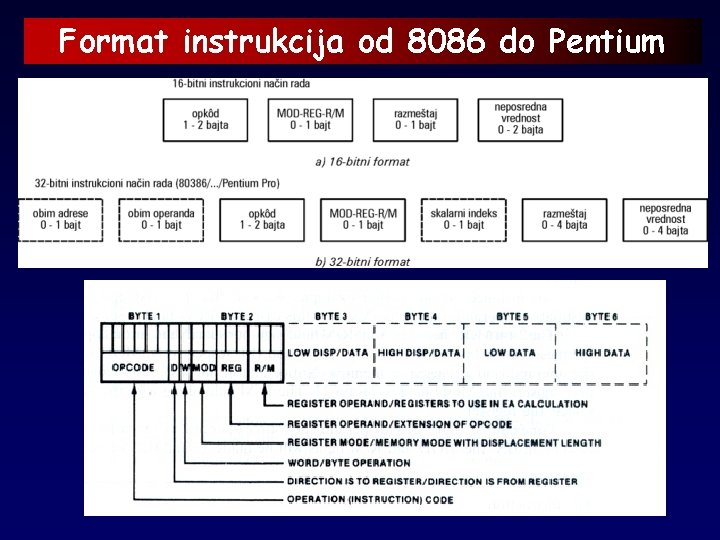

Format instrukcija od 8086 do Pentium

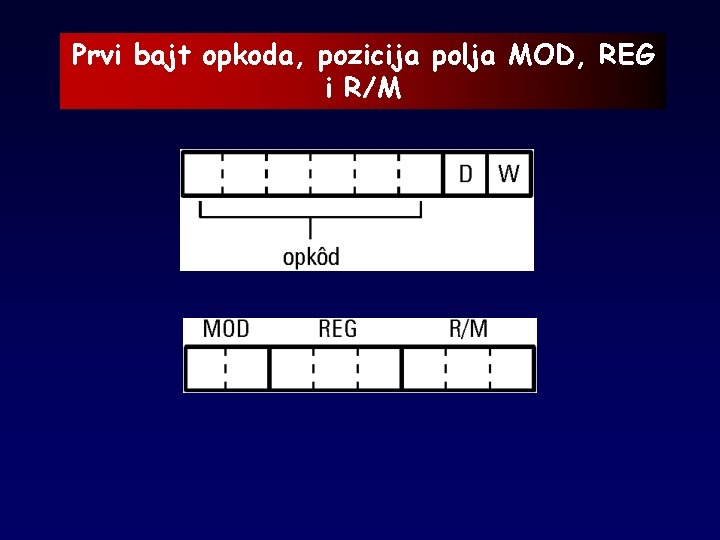

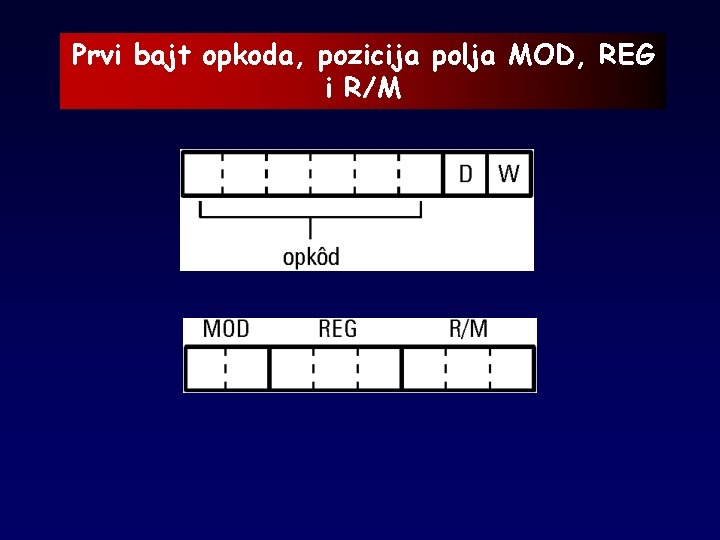

Prvi bajt opkoda, pozicija polja MOD, REG i R/M

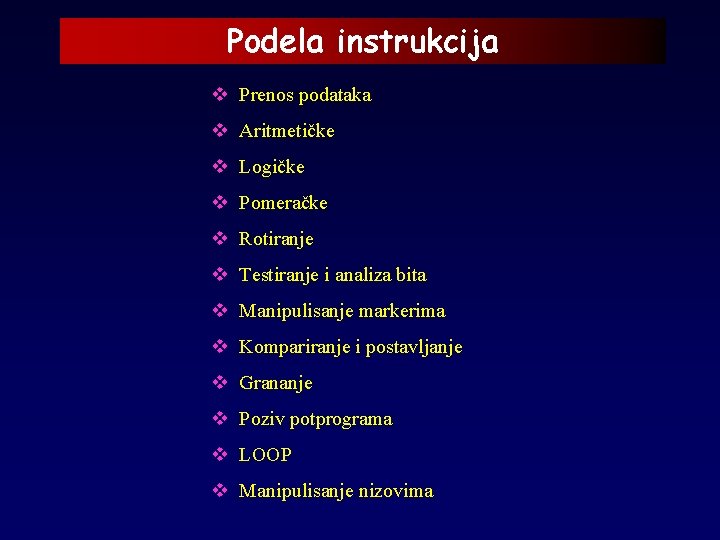

Tipovi instrukcija kod 8086

Podela instrukcija v Prenos podataka v Aritmetičke v Logičke v Pomeračke v Rotiranje v Testiranje i analiza bita v Manipulisanje markerima v Kompariranje i postavljanje v Grananje v Poziv potprograma v LOOP v Manipulisanje nizovima

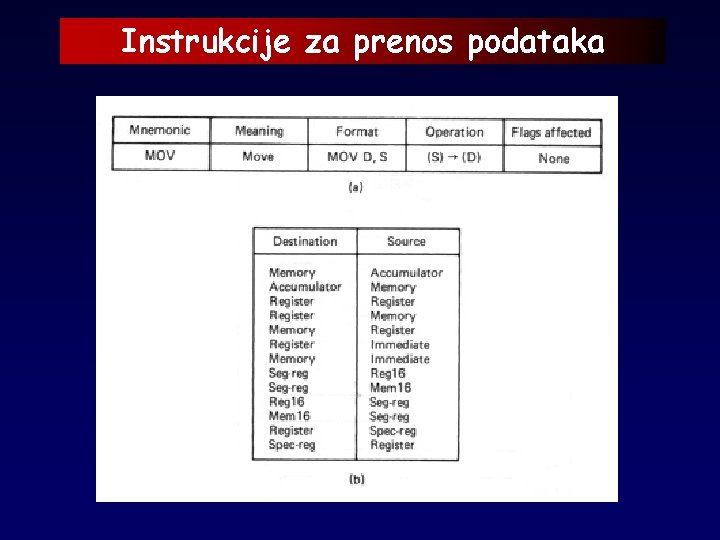

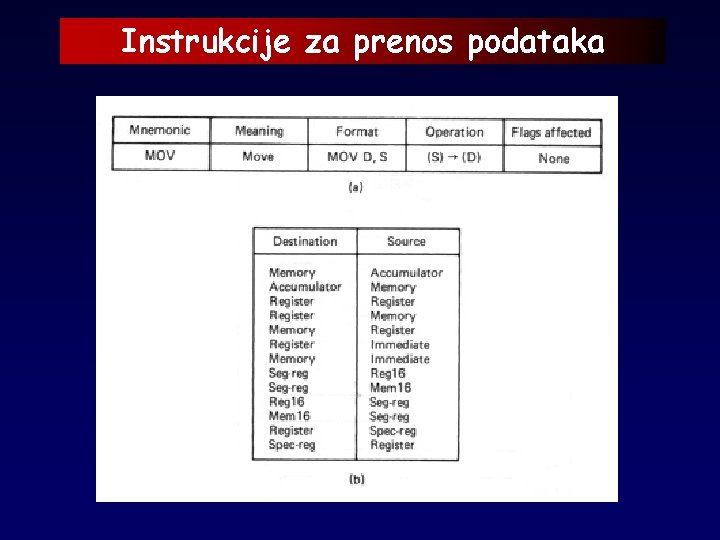

Instrukcije za prenos podataka

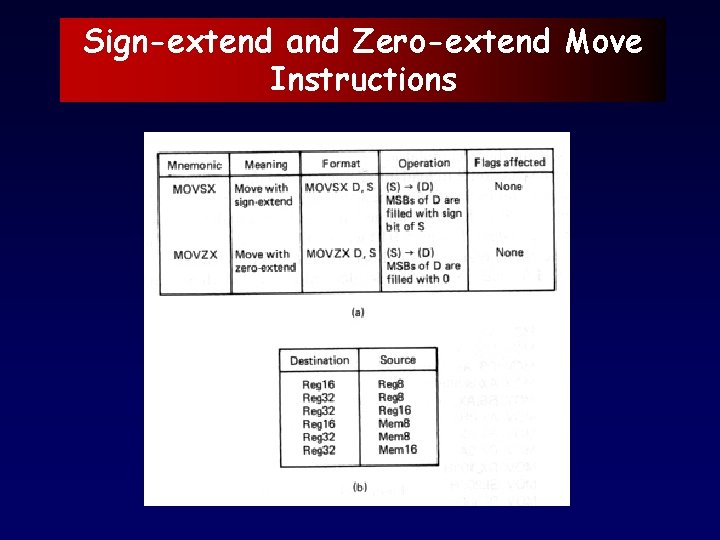

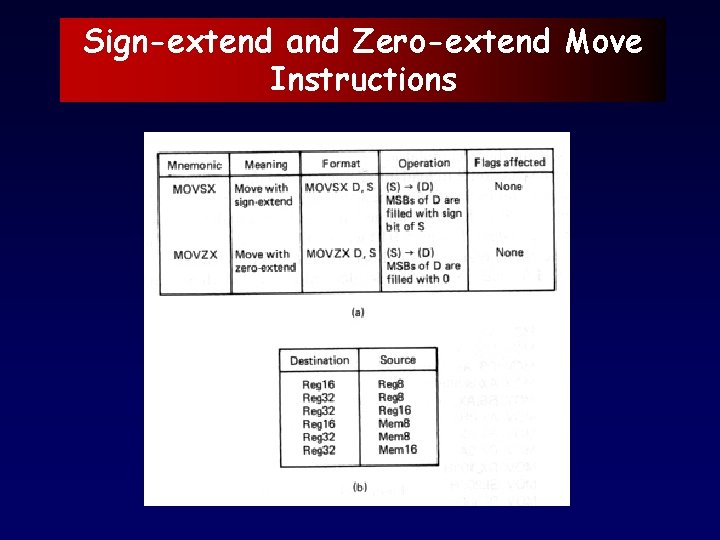

Sign-extend and Zero-extend Move Instructions

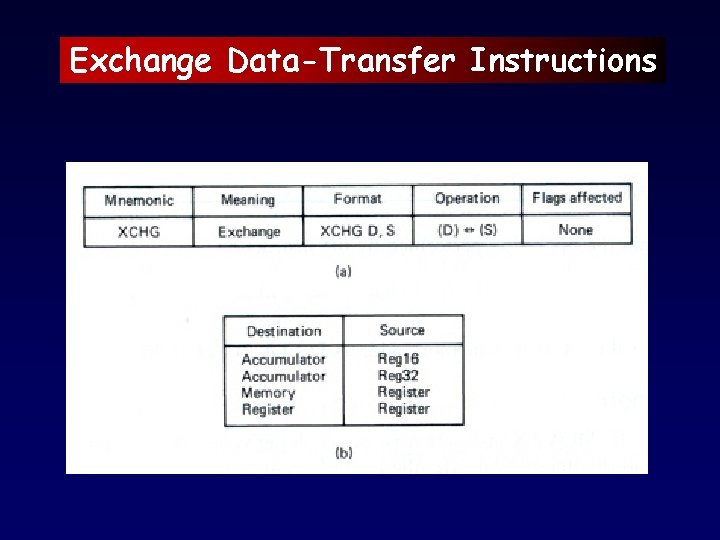

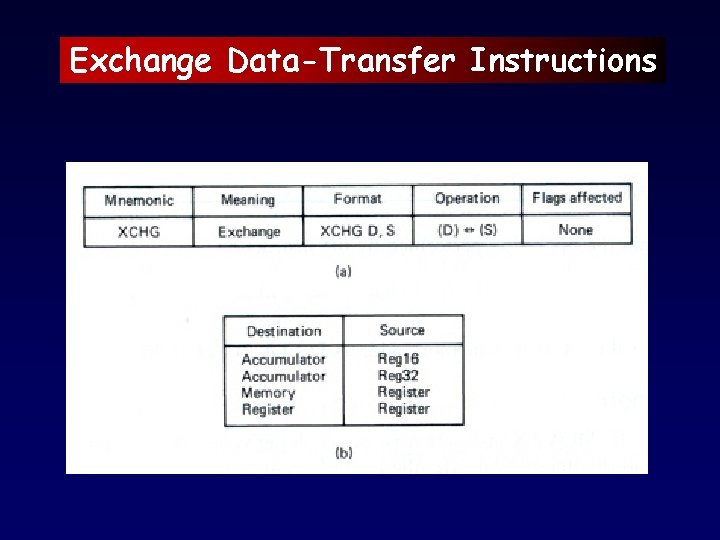

Exchange Data-Transfer Instructions

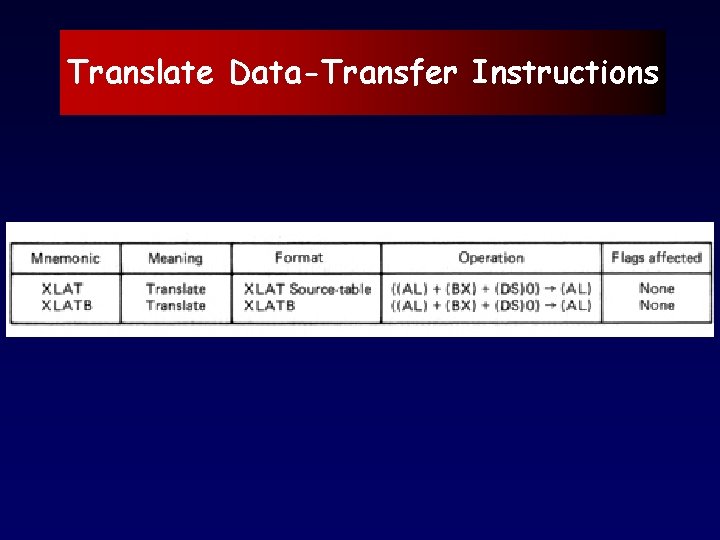

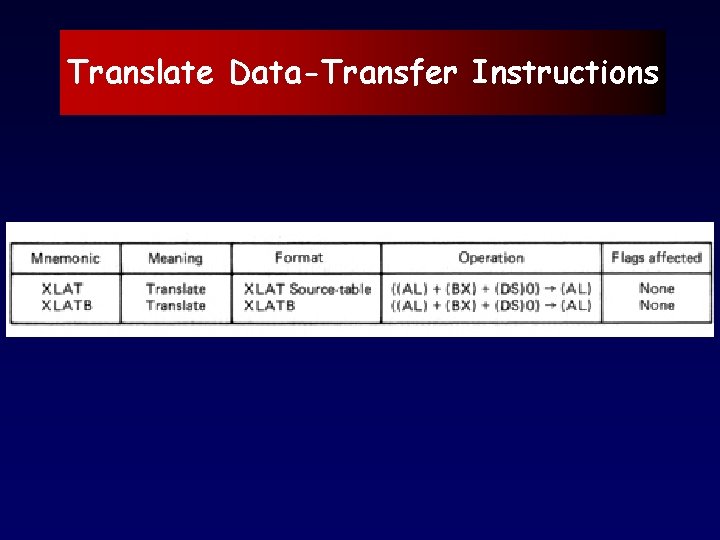

Translate Data-Transfer Instructions

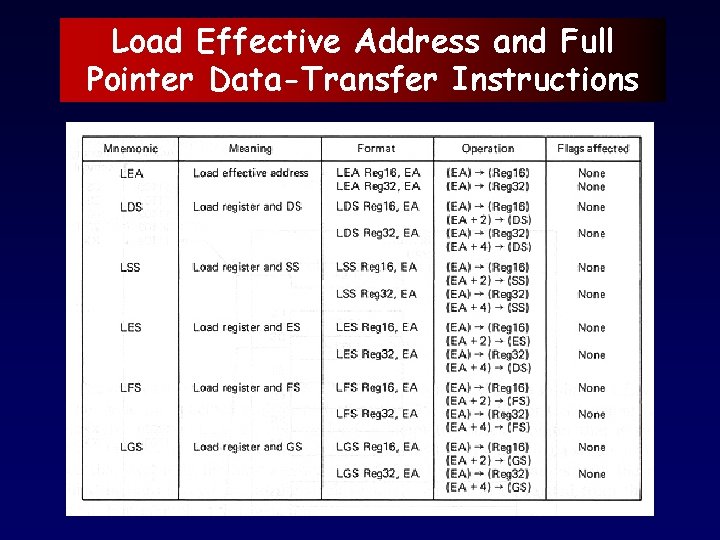

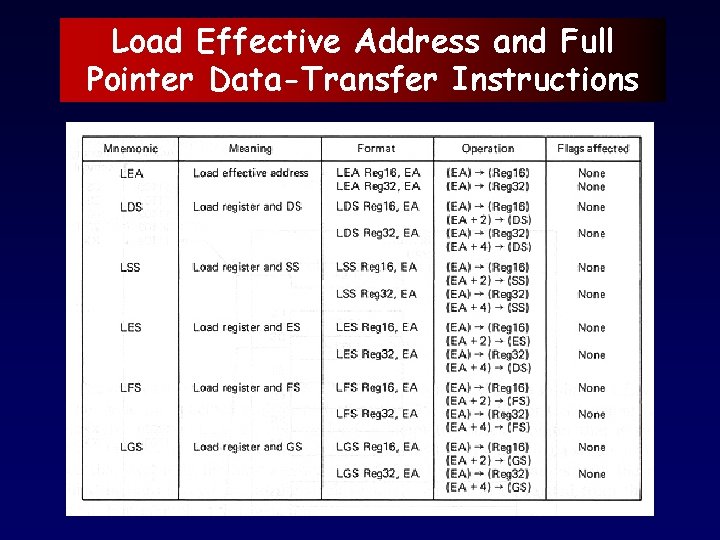

Load Effective Address and Full Pointer Data-Transfer Instructions

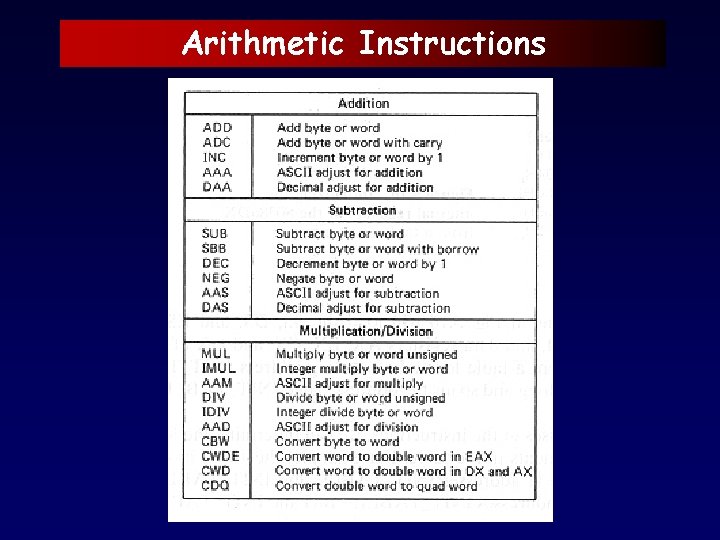

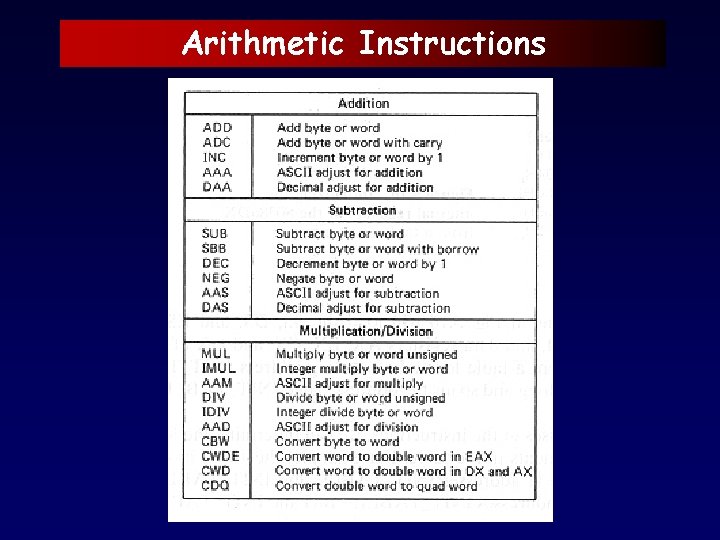

Arithmetic Instructions

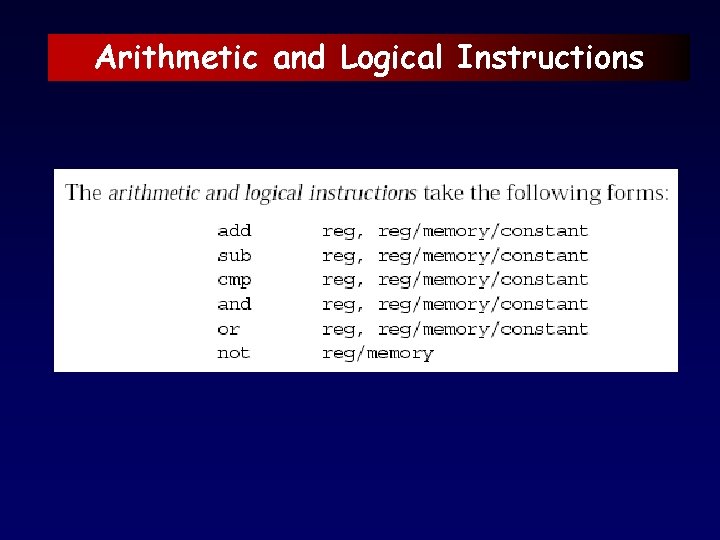

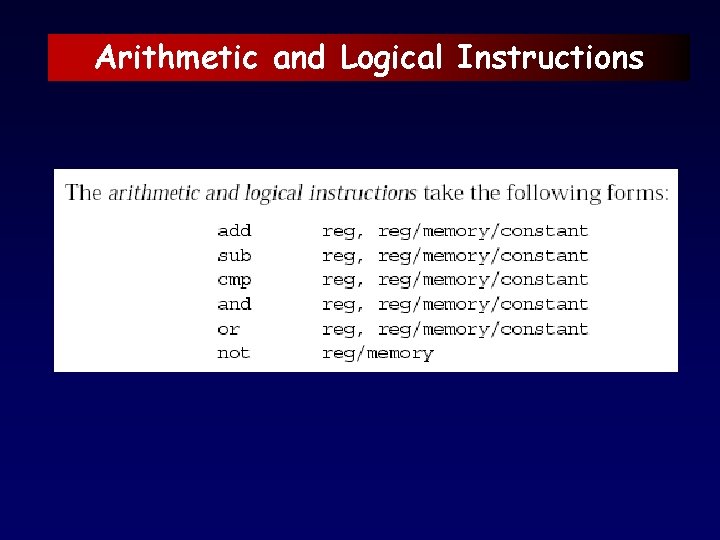

Arithmetic and Logical Instructions

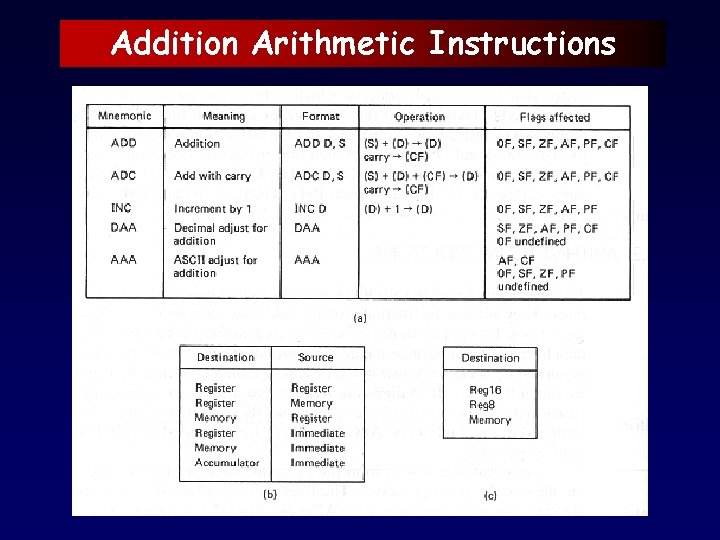

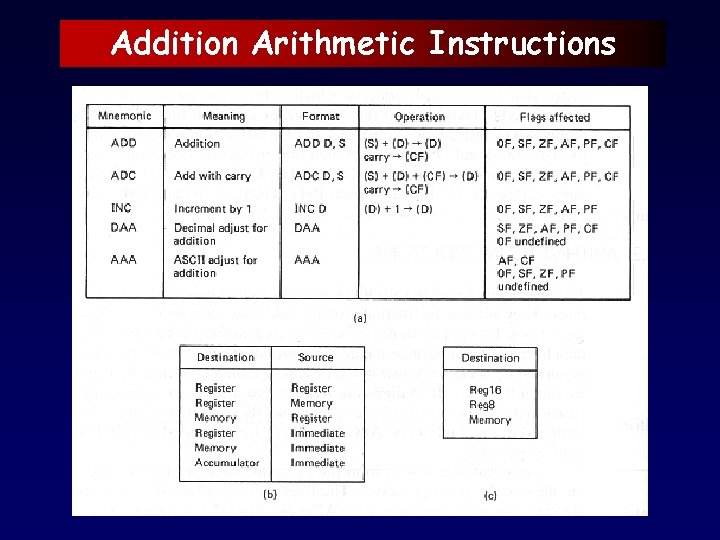

Addition Arithmetic Instructions

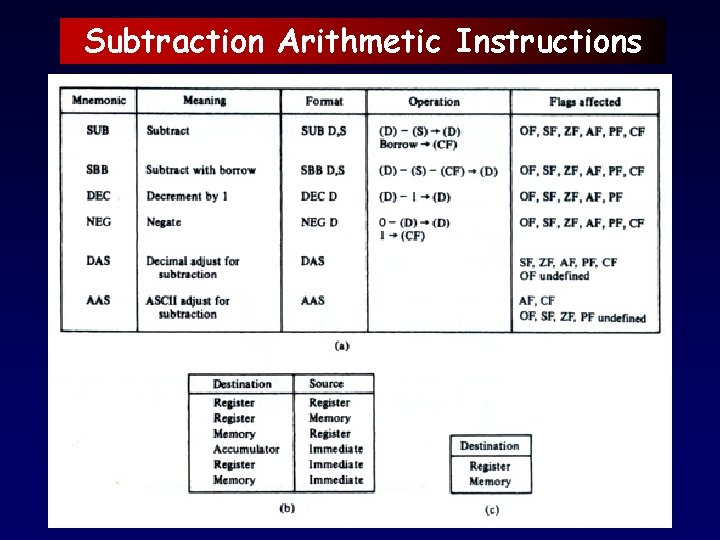

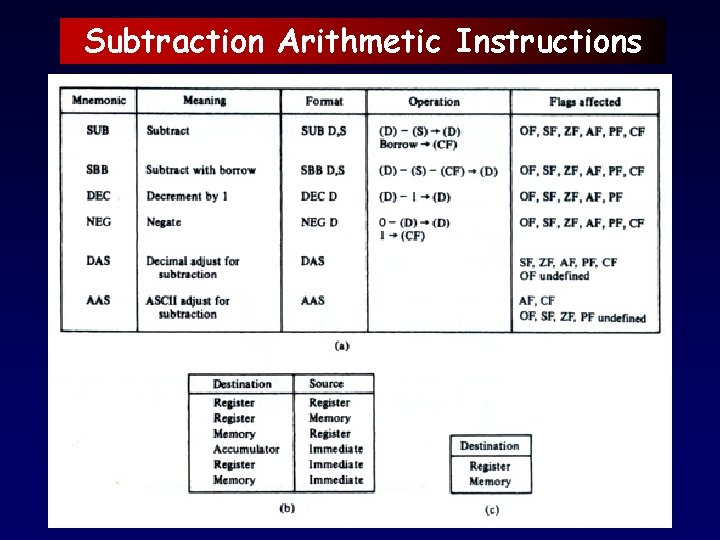

Subtraction Arithmetic Instructions

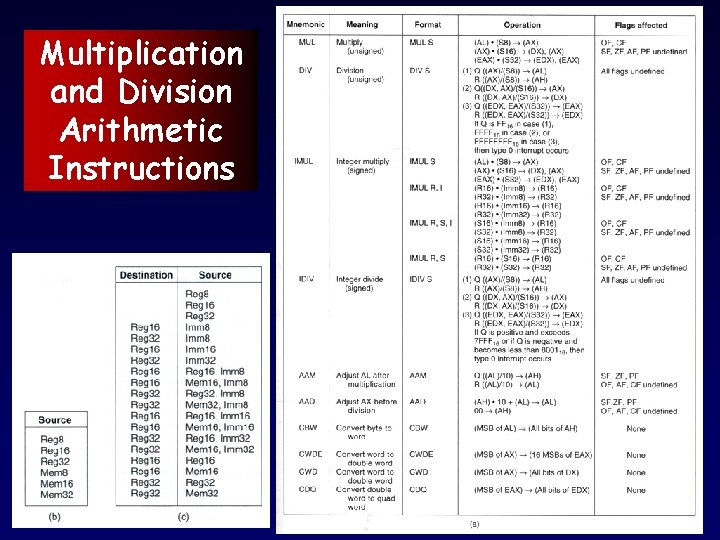

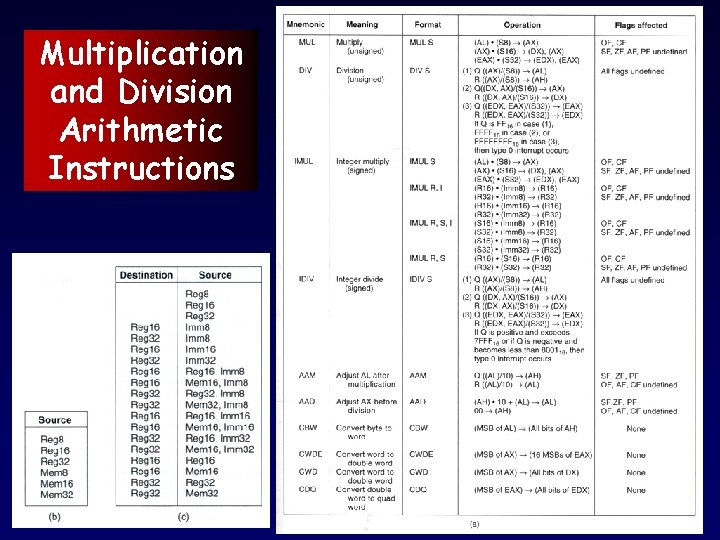

Multiplication and Division Arithmetic Instructions

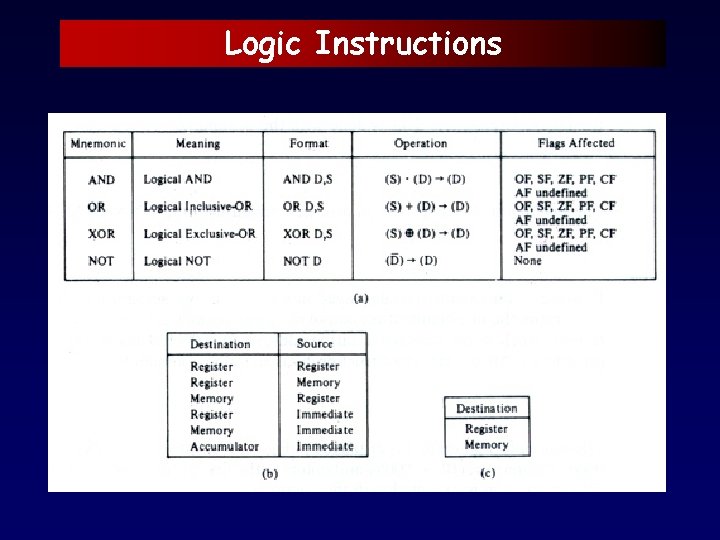

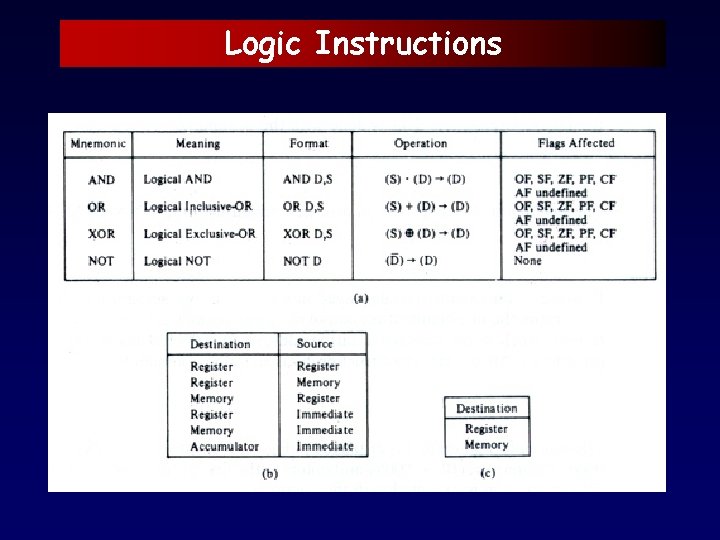

Logic Instructions

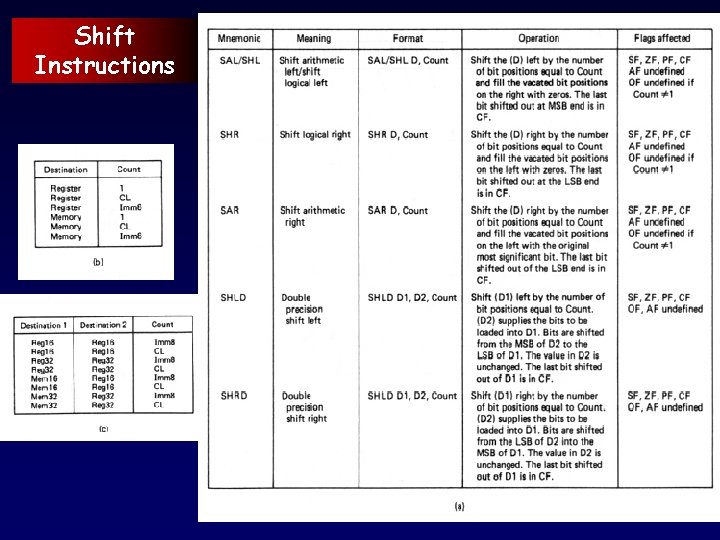

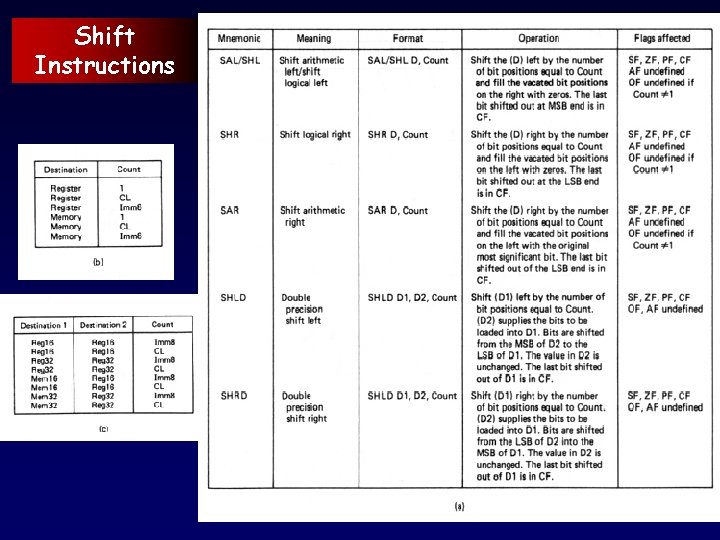

Shift Instructions

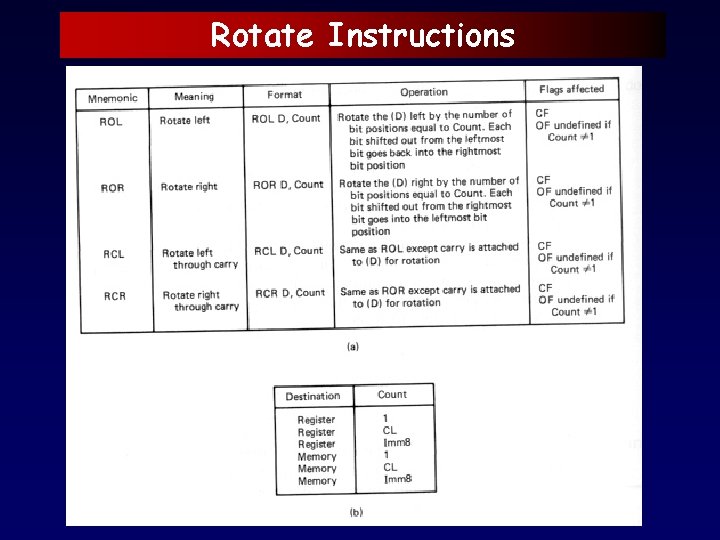

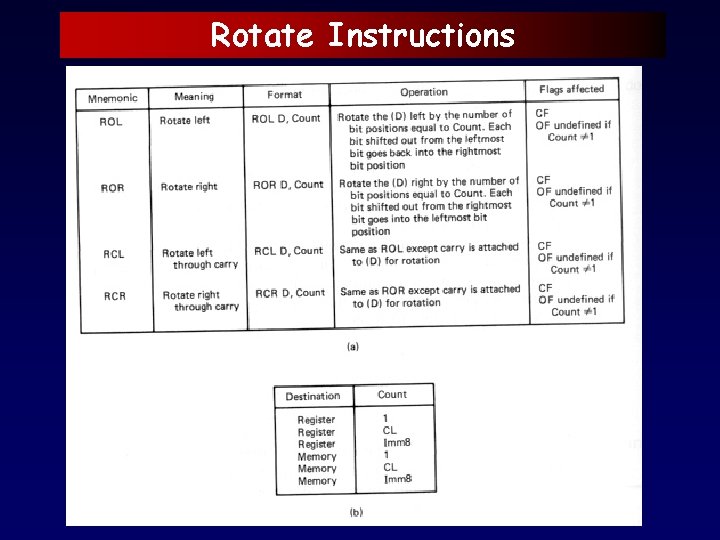

Rotate Instructions

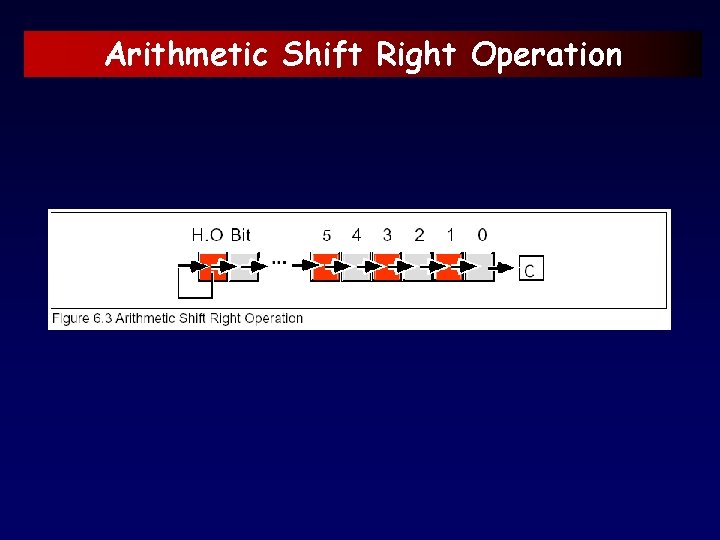

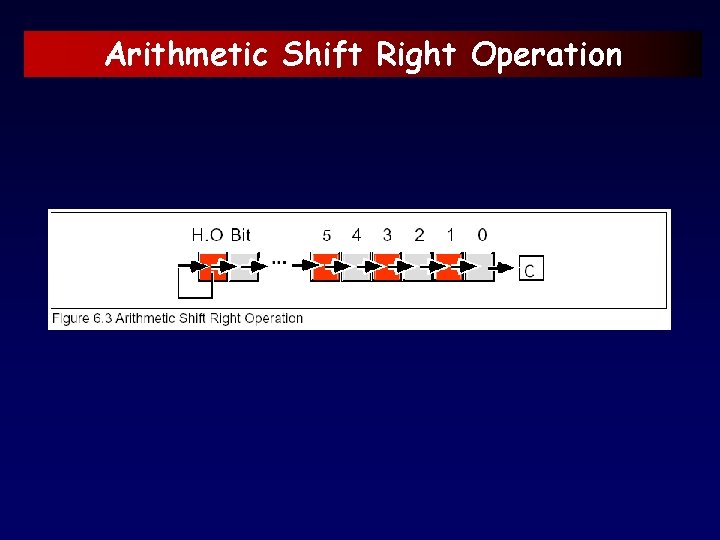

Arithmetic Shift Right Operation

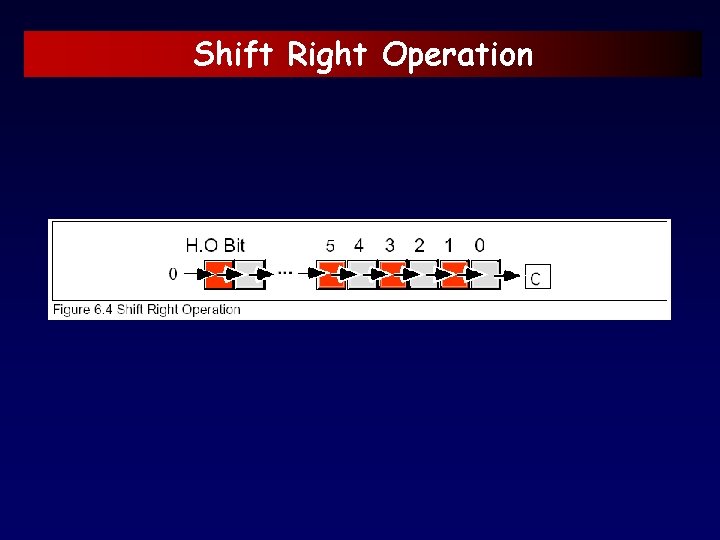

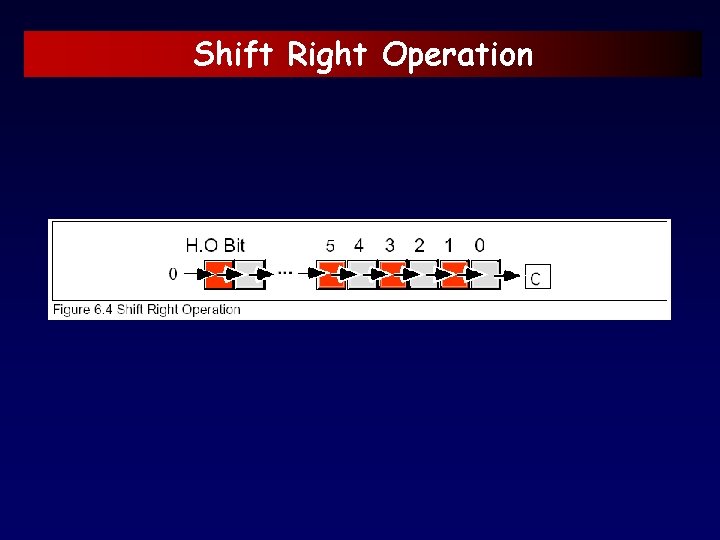

Shift Right Operation

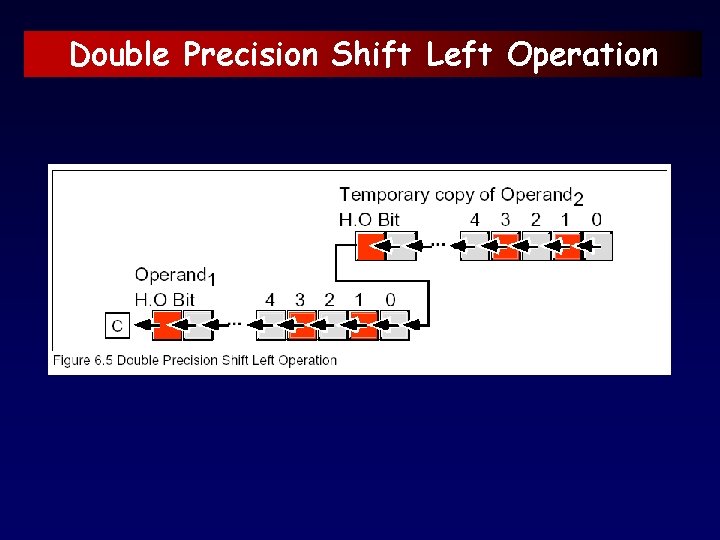

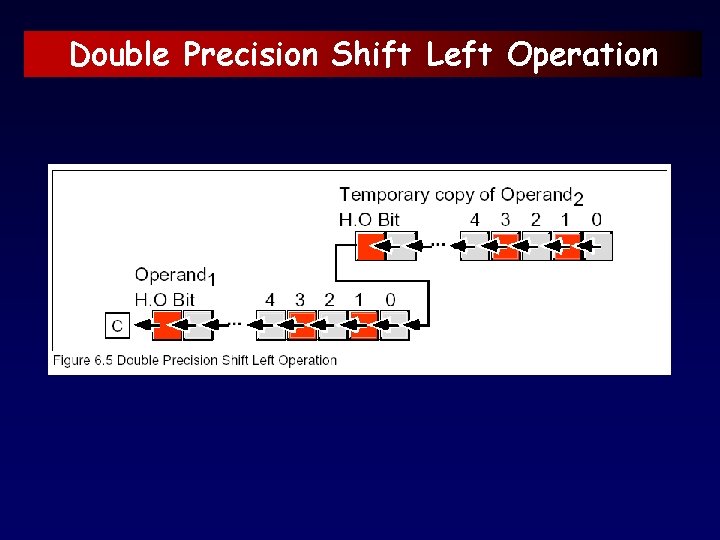

Double Precision Shift Left Operation

Double Precision Shift Right Operation

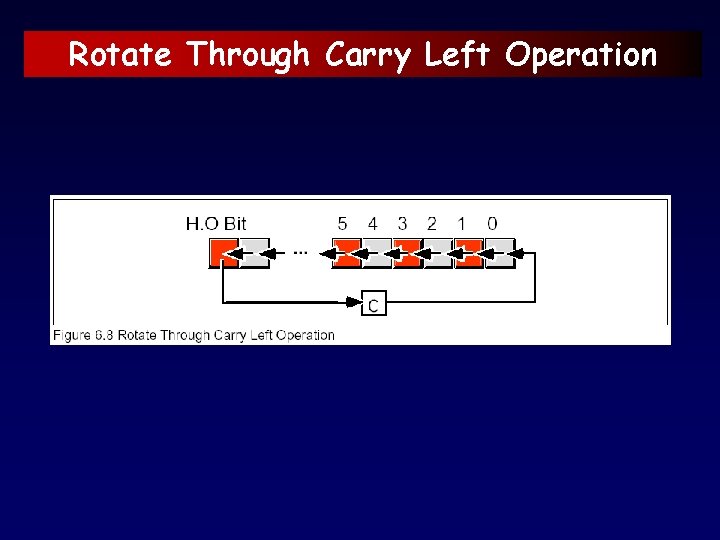

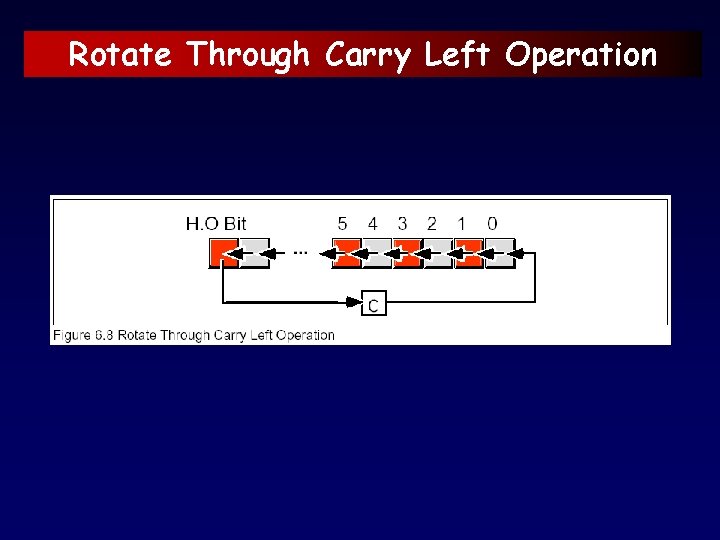

Rotate Through Carry Left Operation

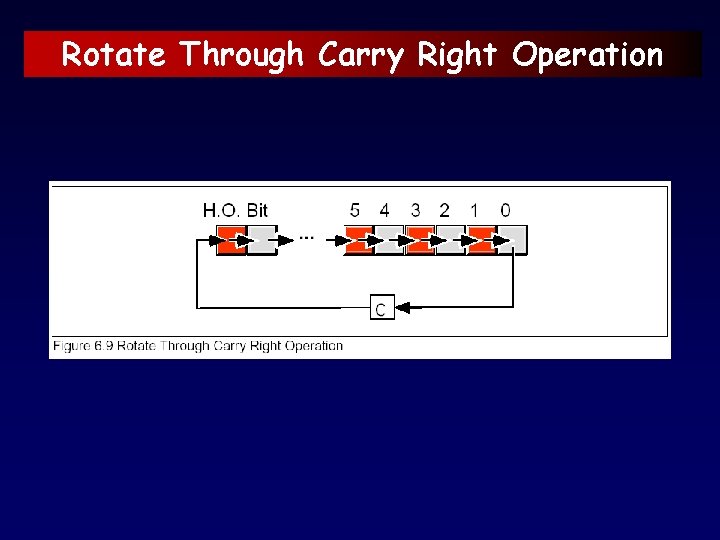

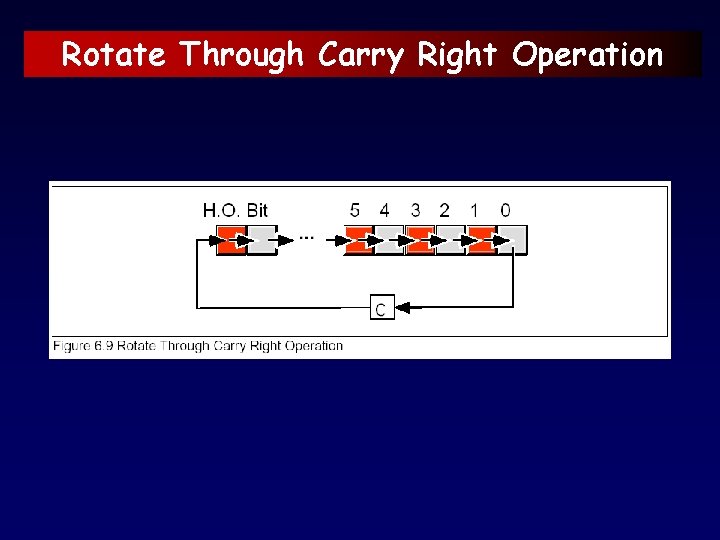

Rotate Through Carry Right Operation

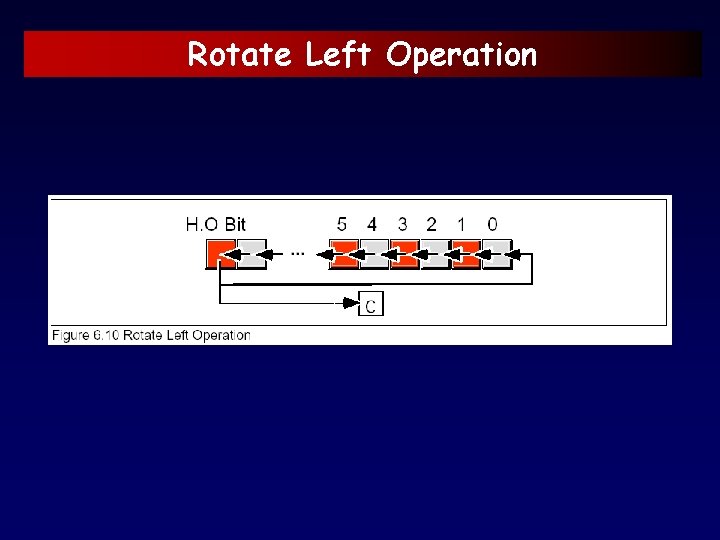

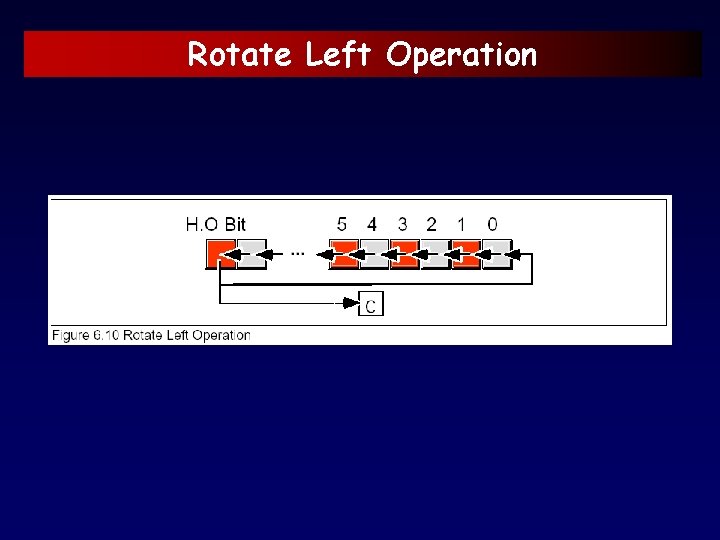

Rotate Left Operation

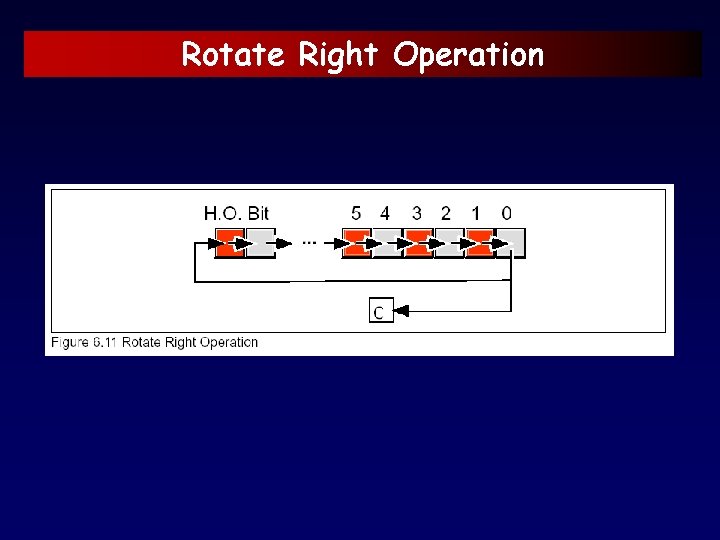

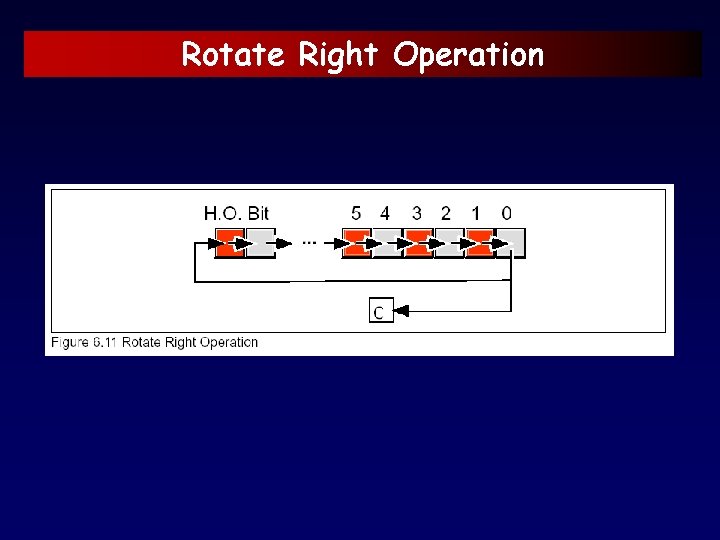

Rotate Right Operation

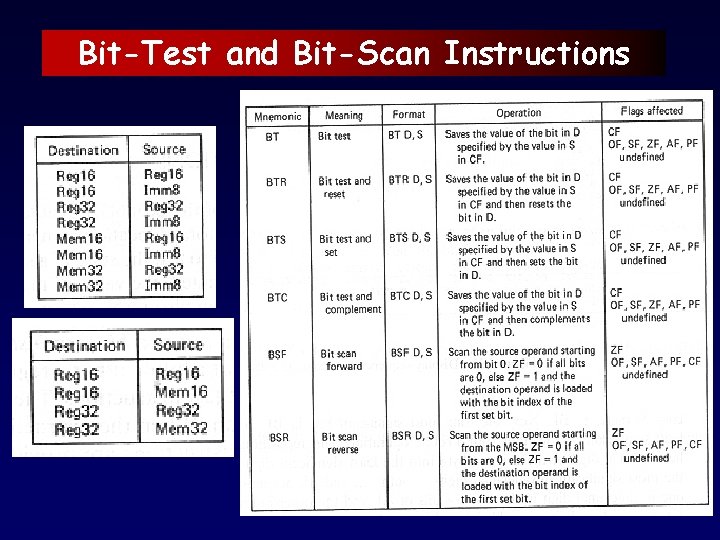

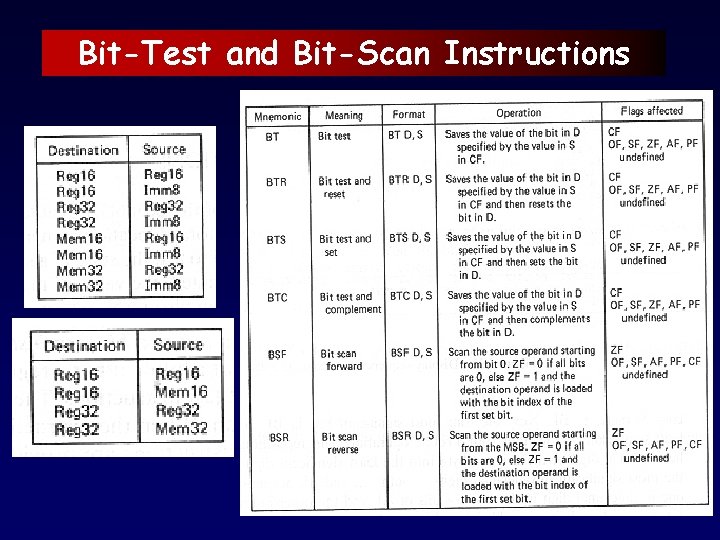

Bit-Test and Bit-Scan Instructions

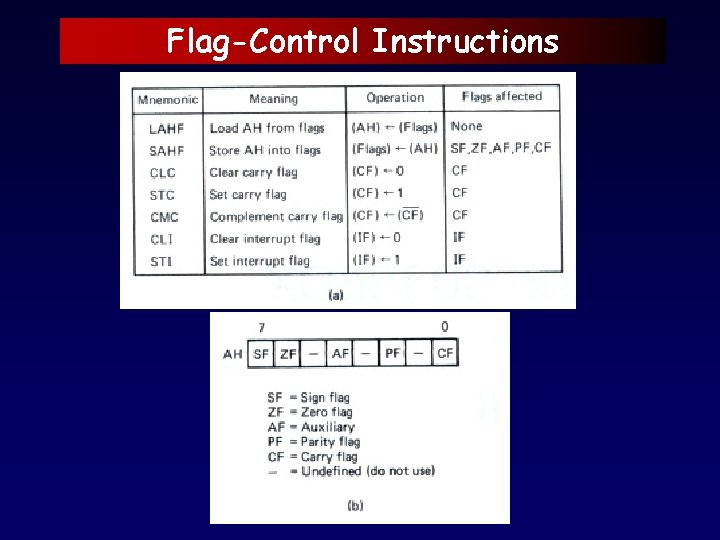

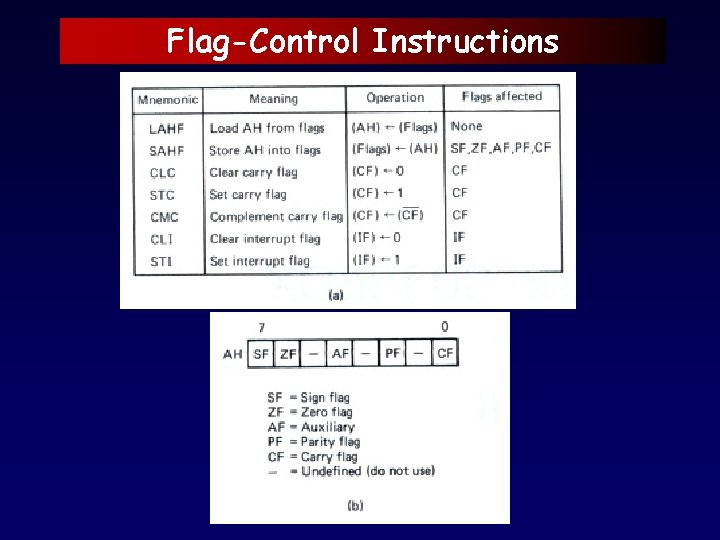

Flag-Control Instructions

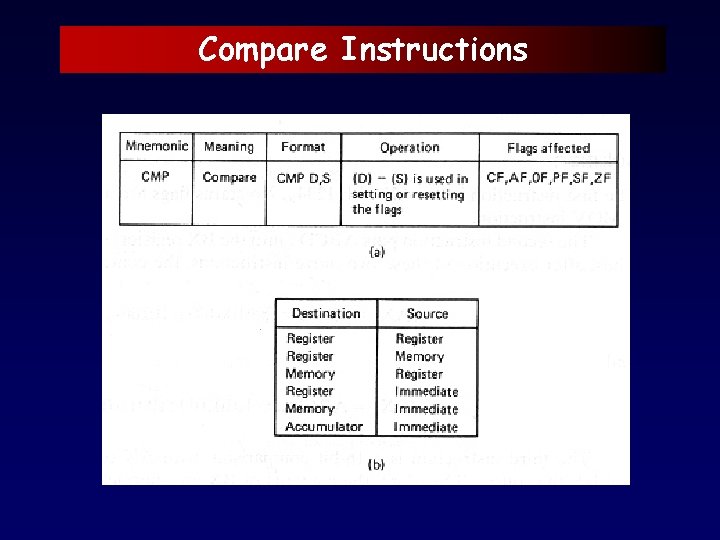

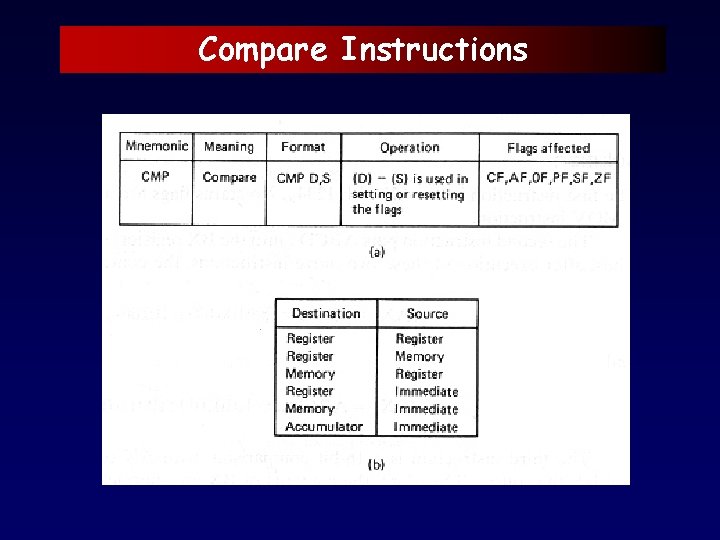

Compare Instructions

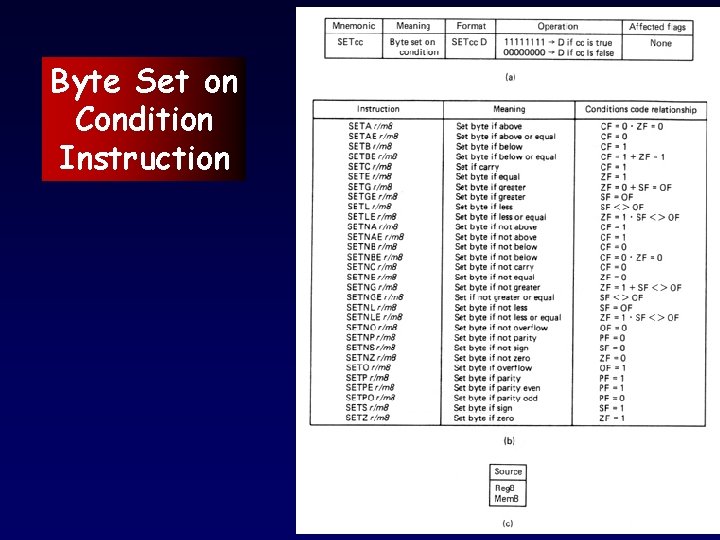

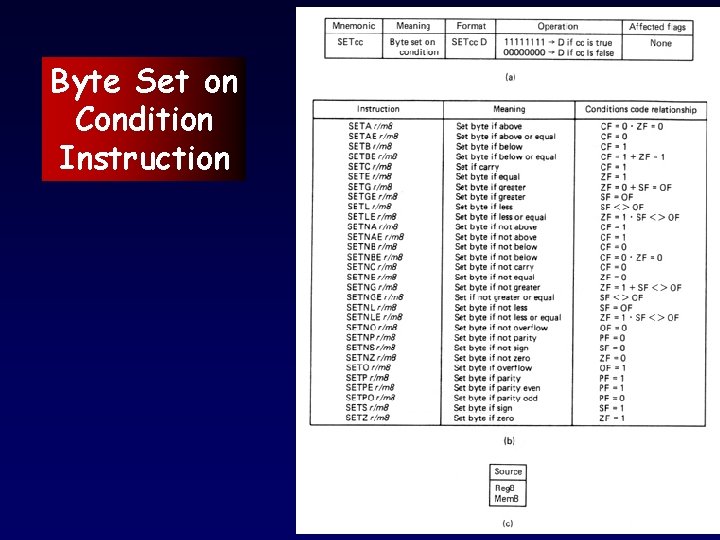

Byte Set on Condition Instruction

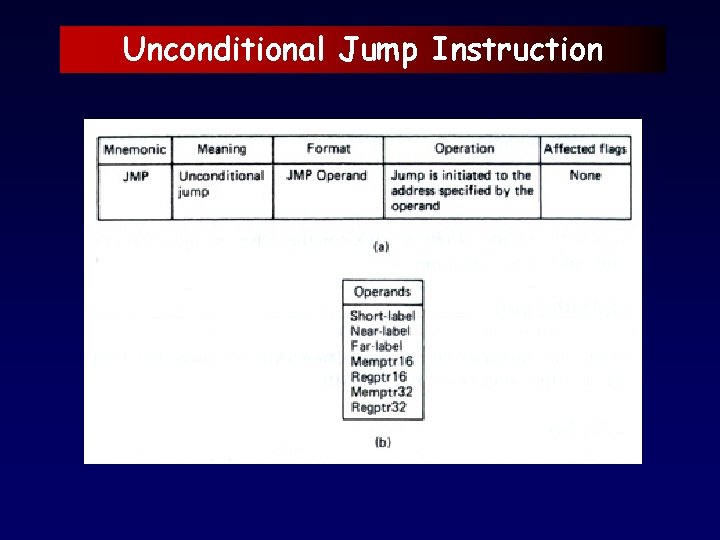

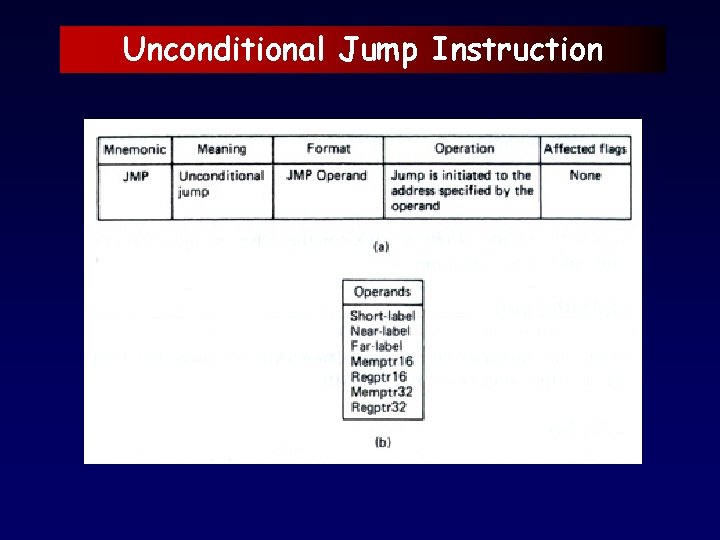

Unconditional Jump Instruction

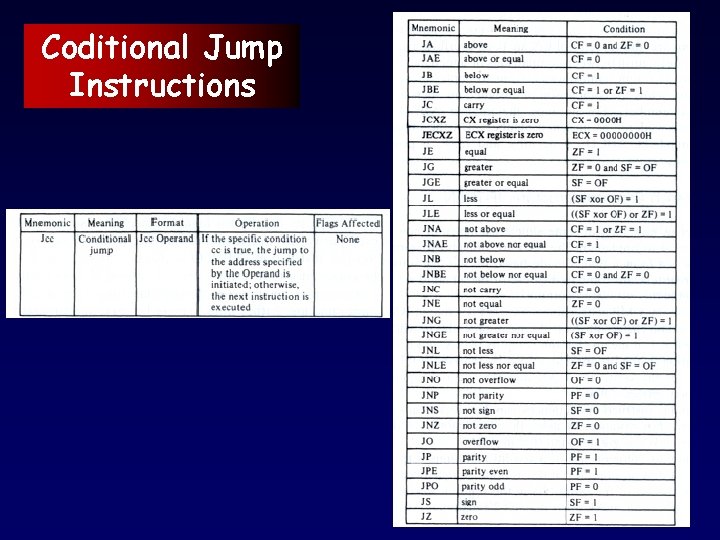

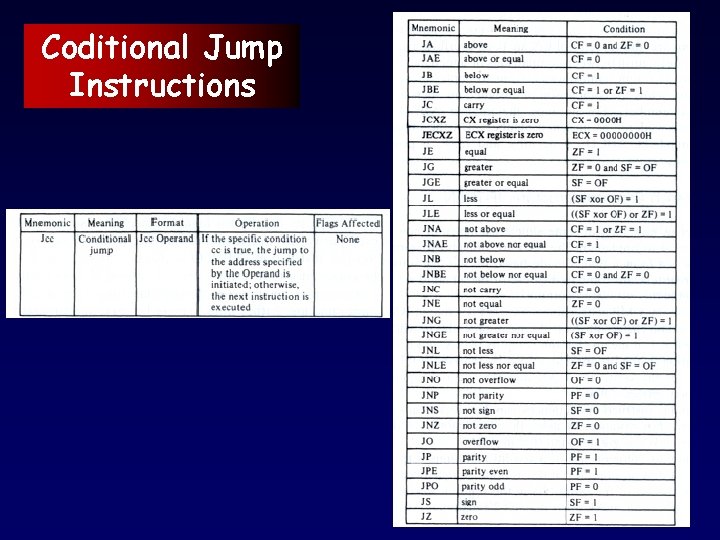

Coditional Jump Instructions

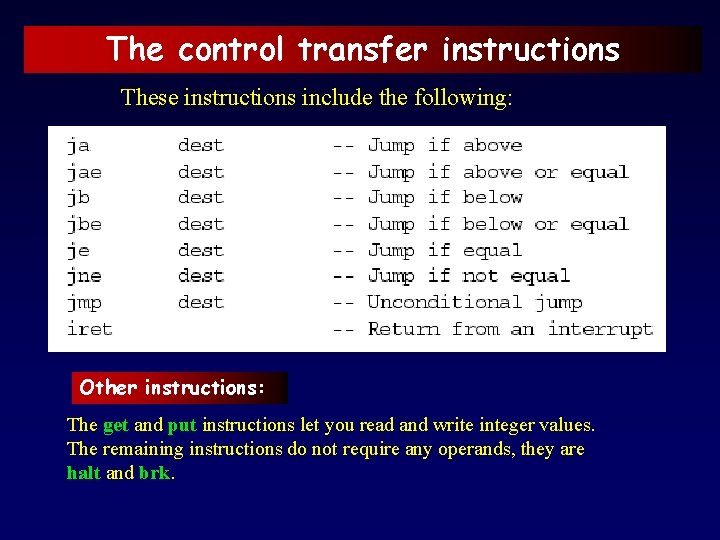

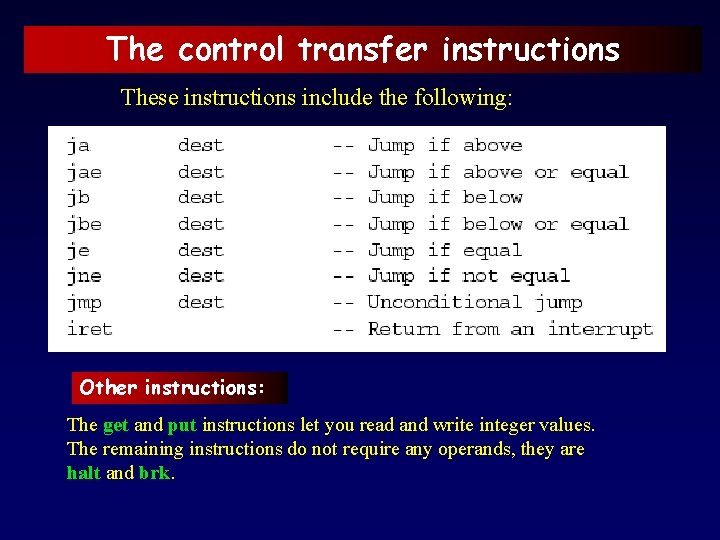

The control transfer instructions These instructions include the following: Other instructions: The get and put instructions let you read and write integer values. The remaining instructions do not require any operands, they are halt and brk.

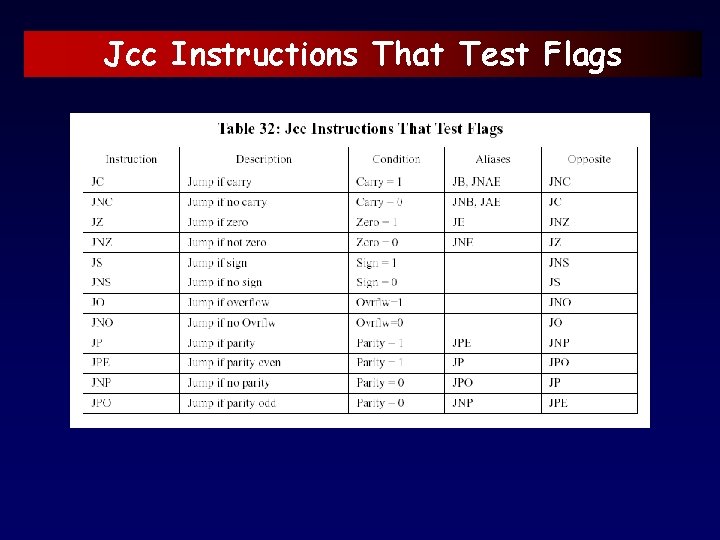

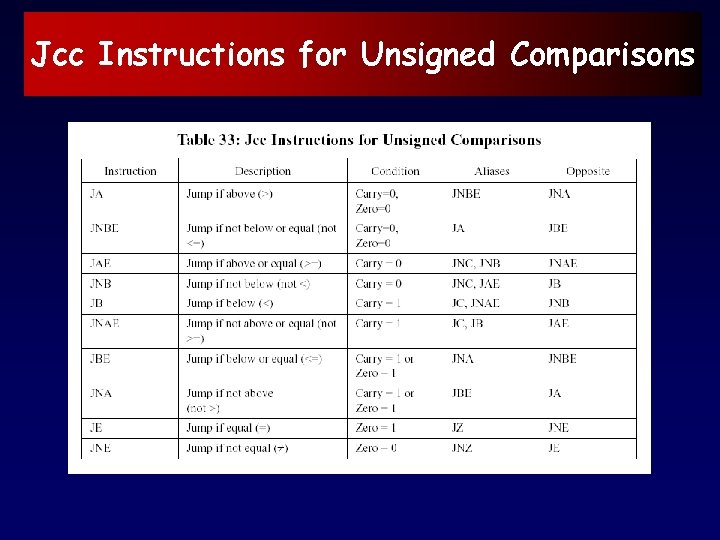

Jcc Instructions That Test Flags

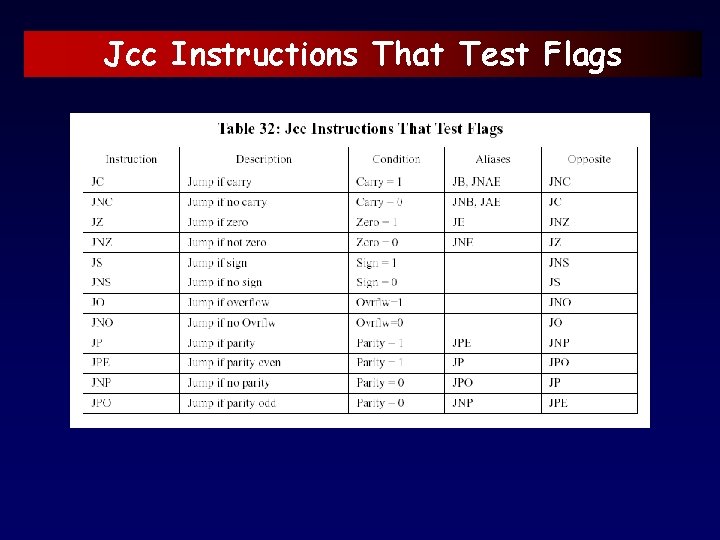

Jcc Instructions for Unsigned Comparisons

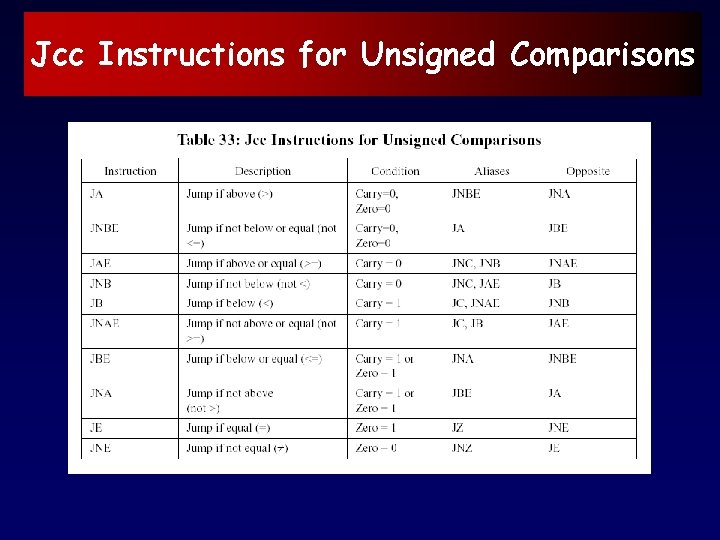

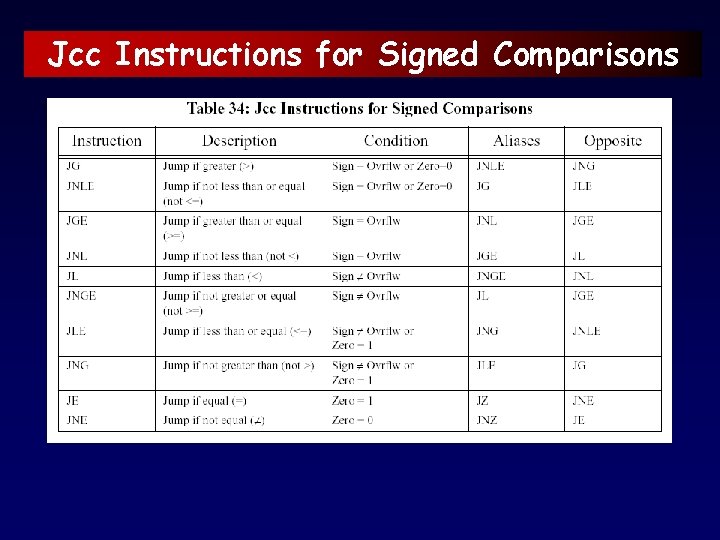

Jcc Instructions for Signed Comparisons

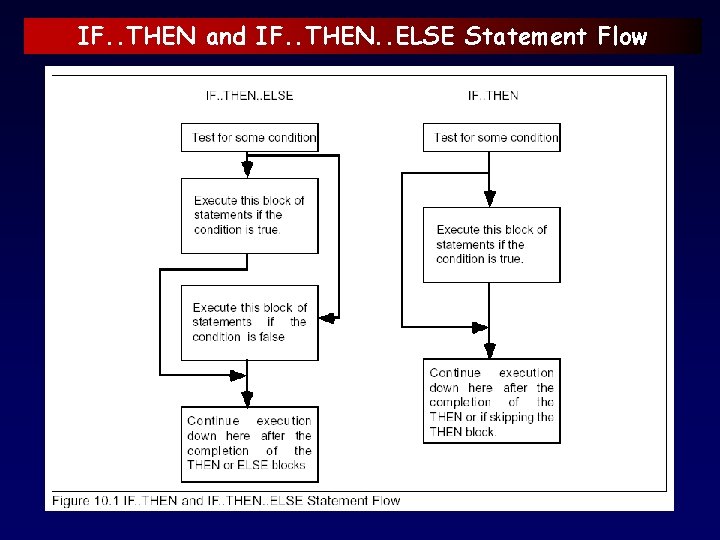

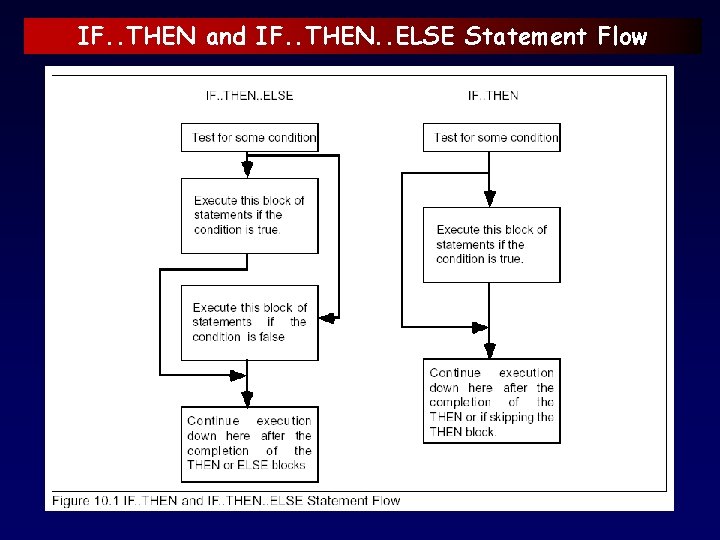

IF. . THEN and IF. . THEN. . ELSE Statement Flow

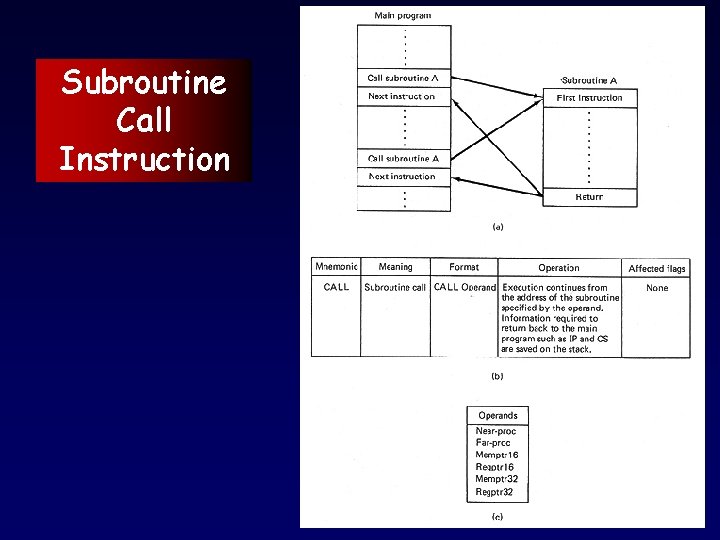

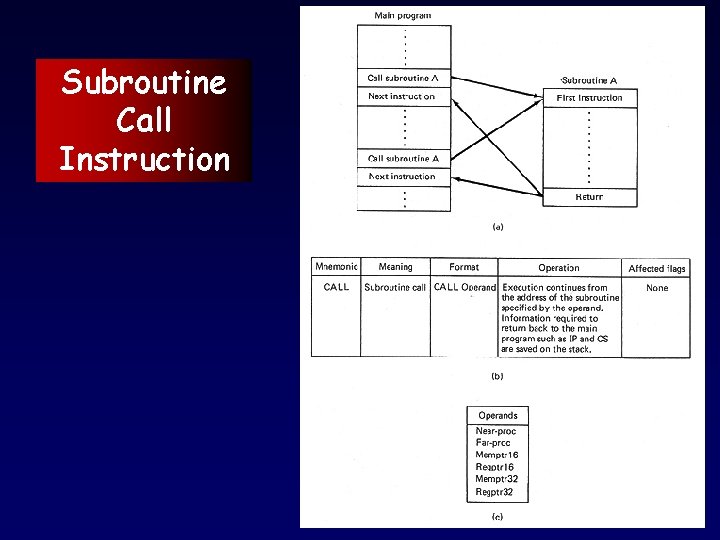

Subroutine Call Instruction

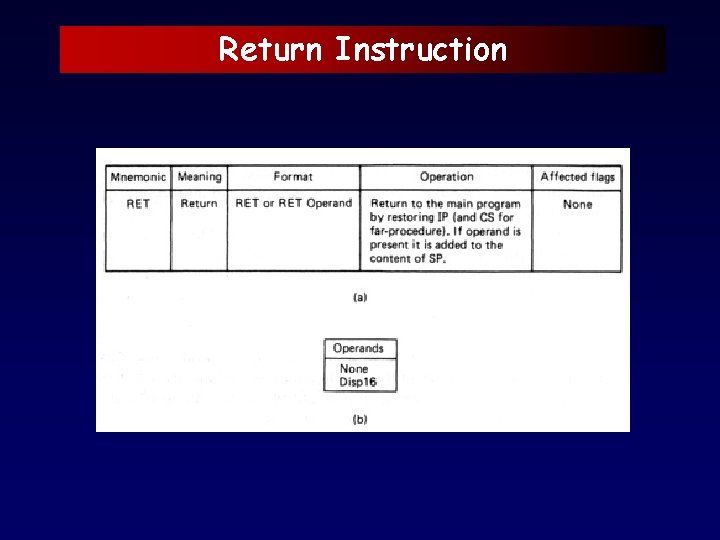

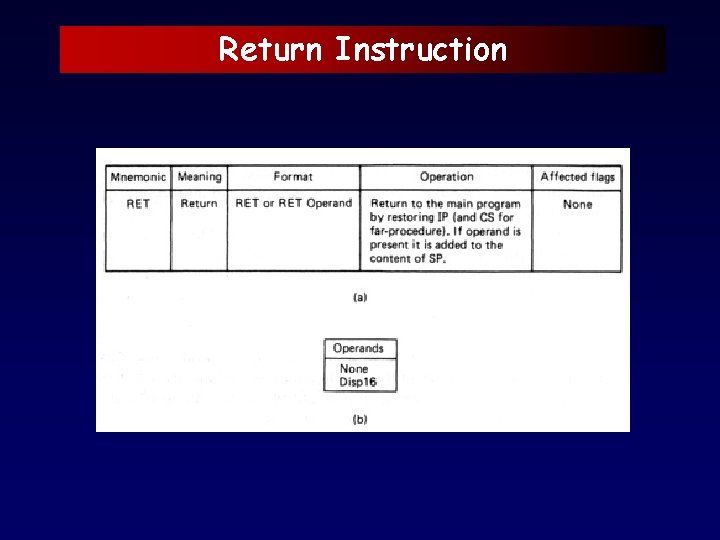

Return Instruction

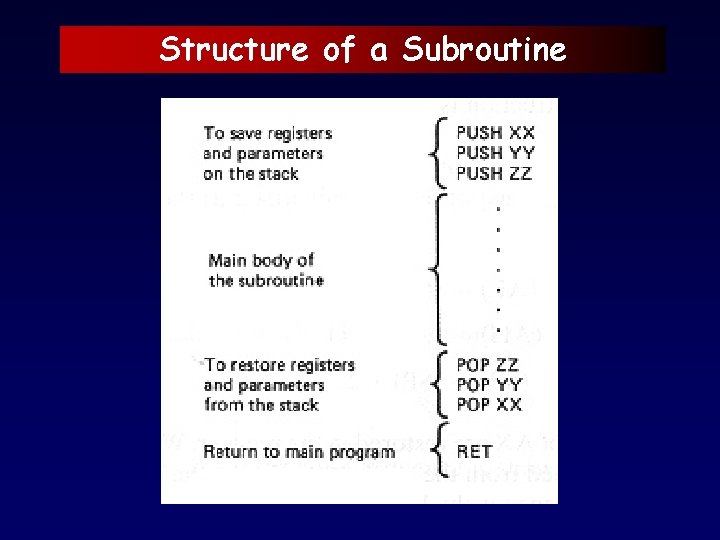

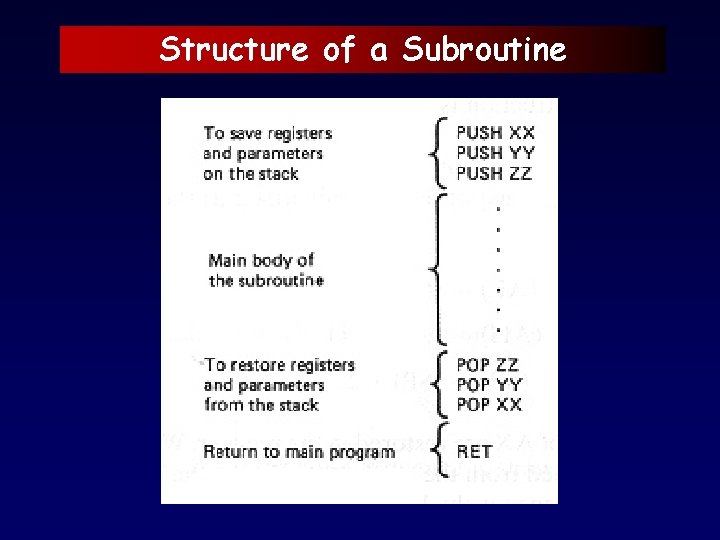

Structure of a Subroutine

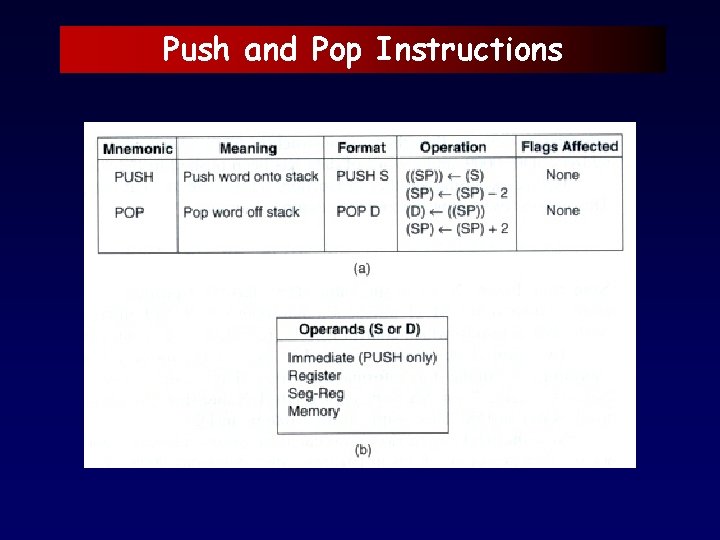

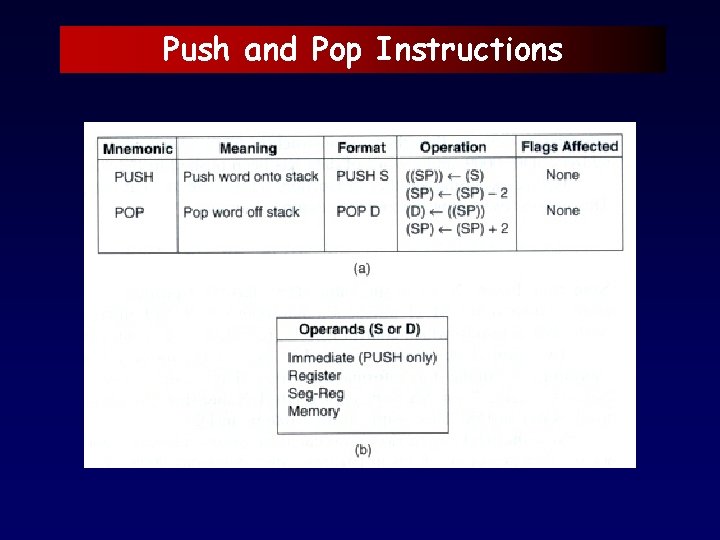

Push and Pop Instructions

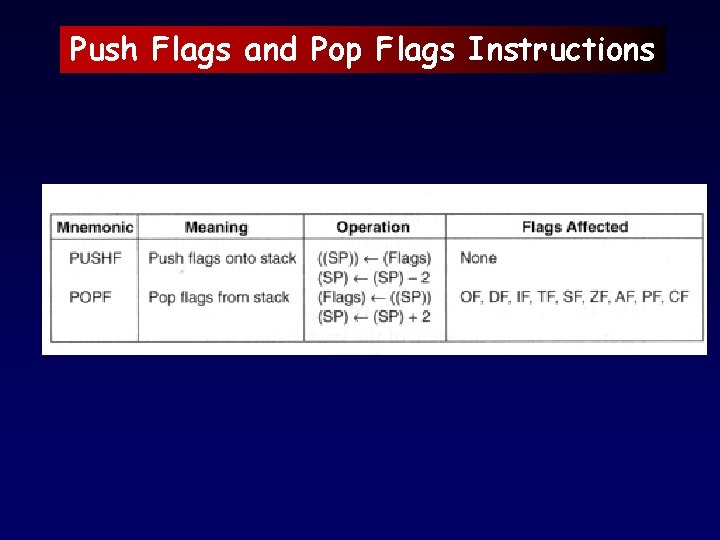

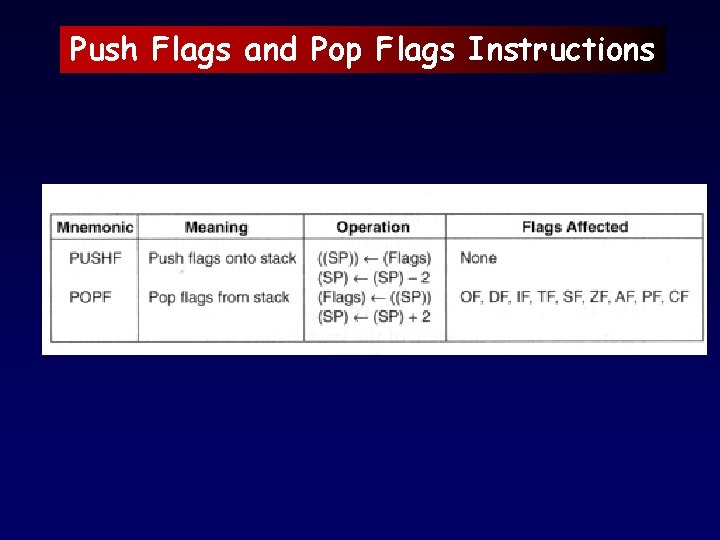

Push Flags and Pop Flags Instructions

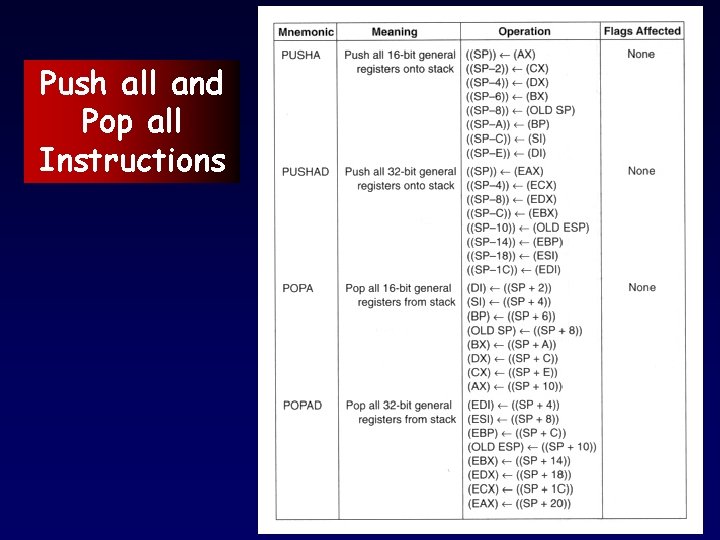

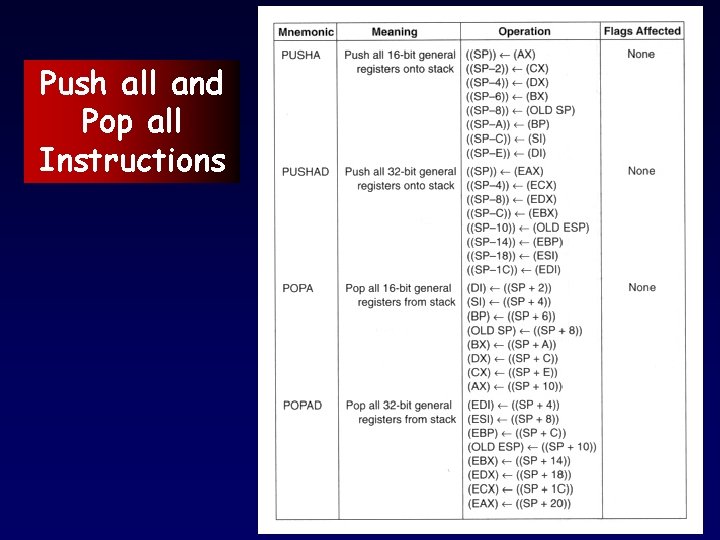

Push all and Pop all Instructions

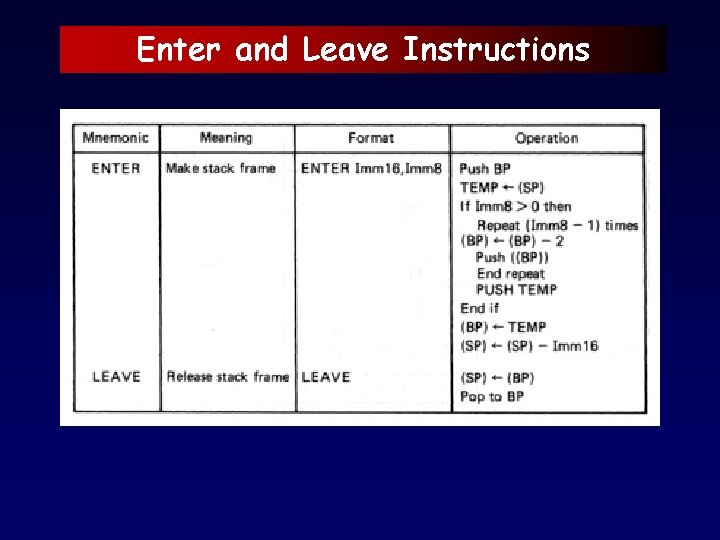

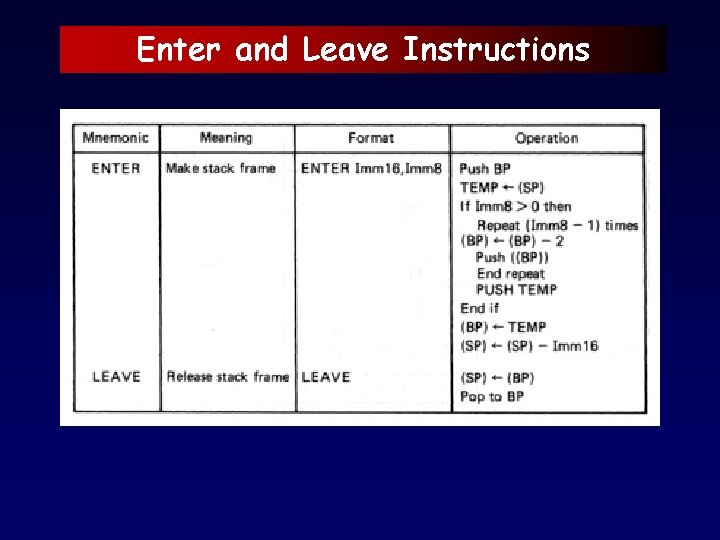

Enter and Leave Instructions

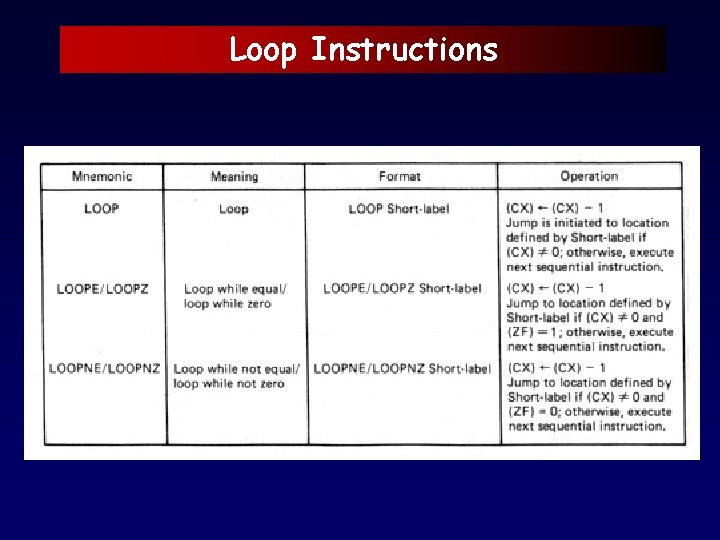

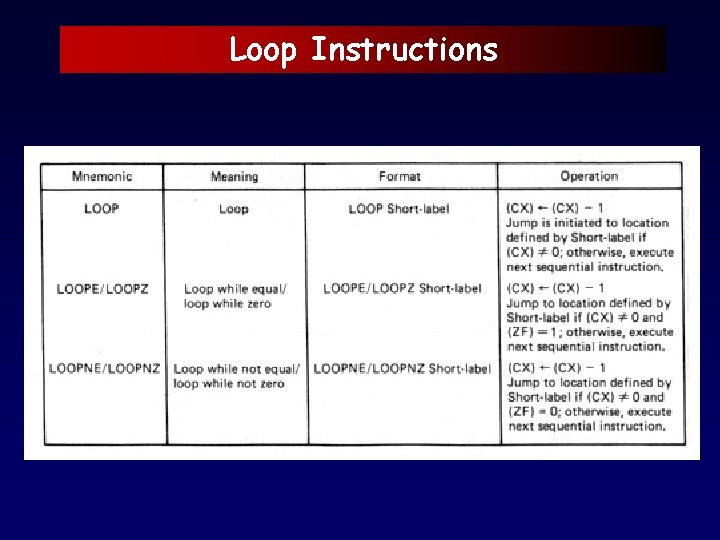

Loop Instructions

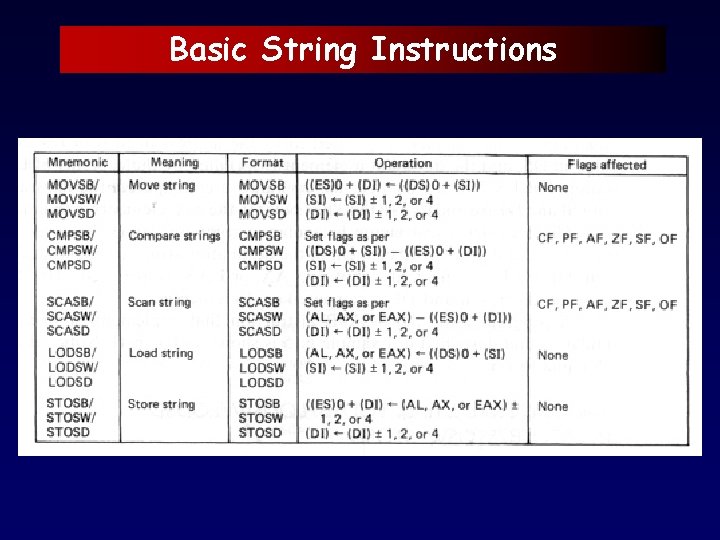

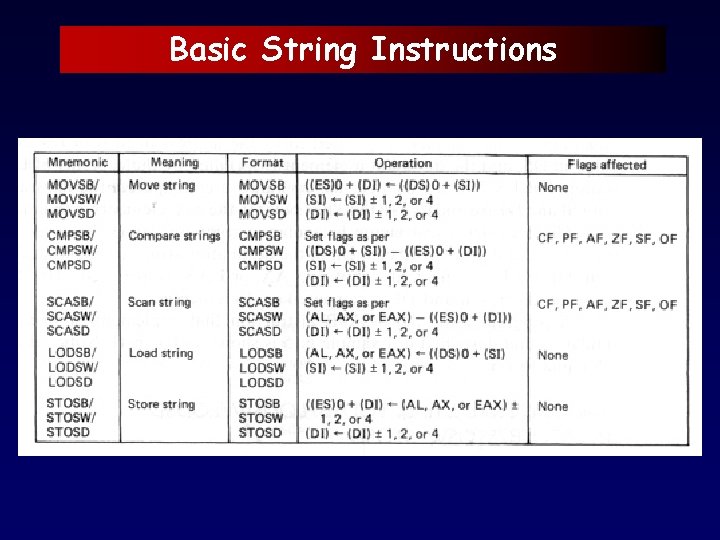

Basic String Instructions

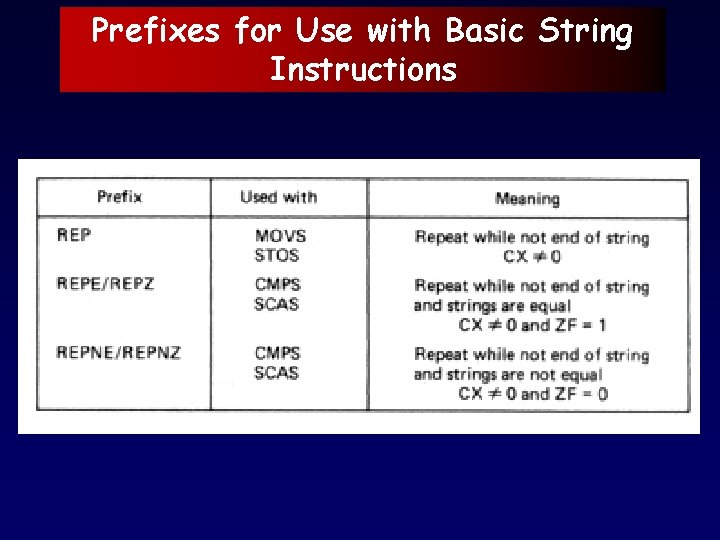

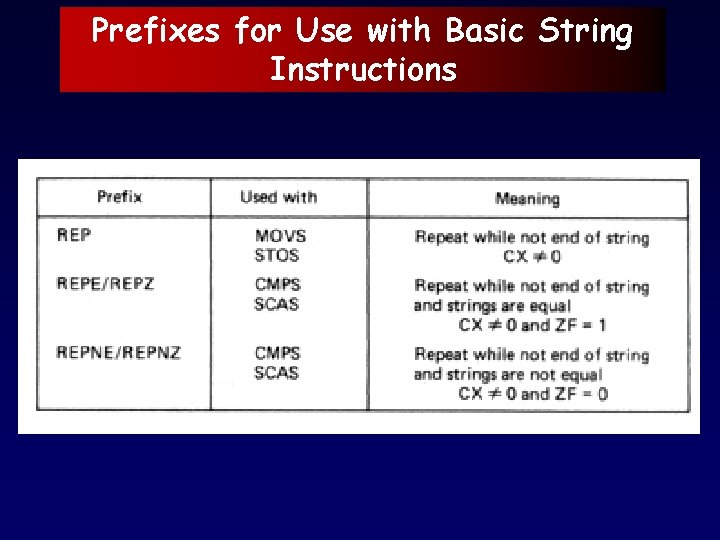

Prefixes for Use with Basic String Instructions

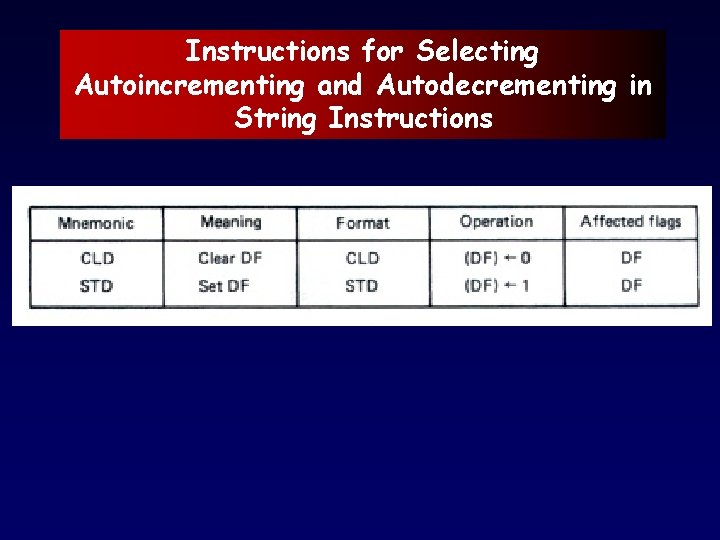

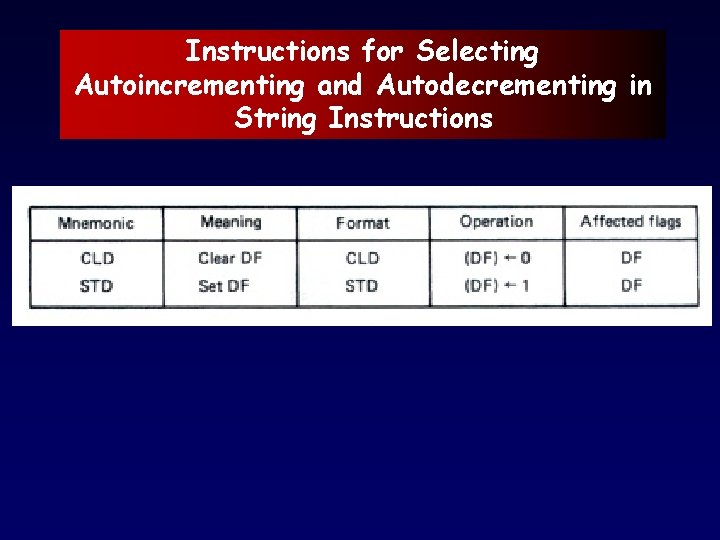

Instructions for Selecting Autoincrementing and Autodecrementing in String Instructions

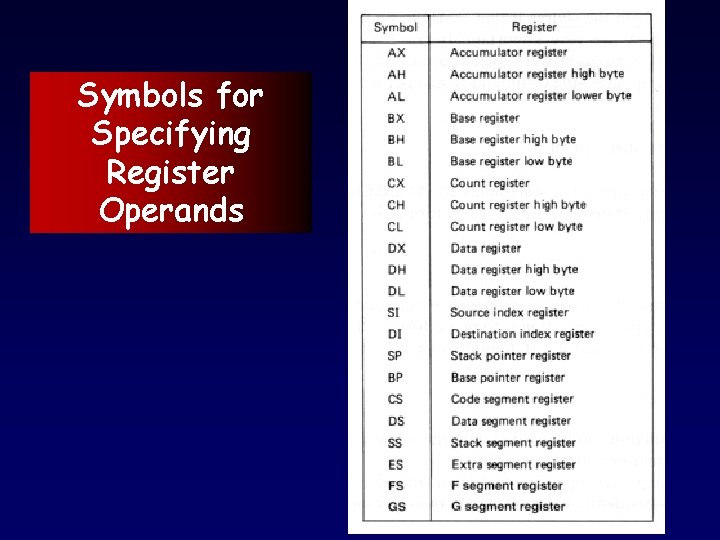

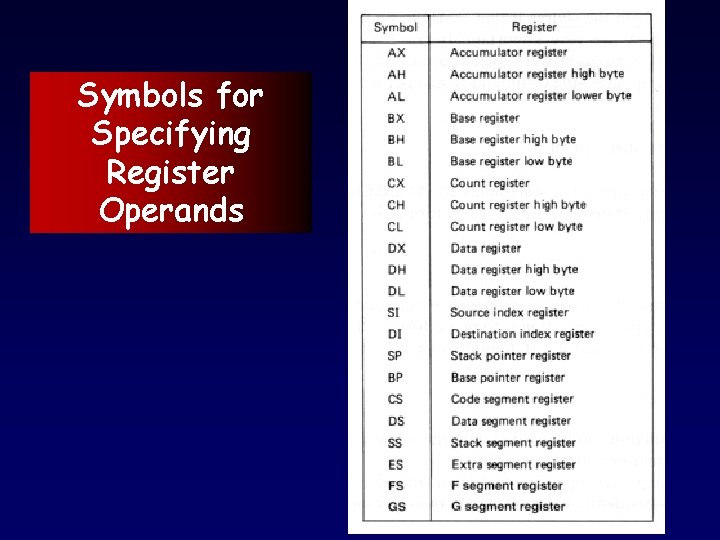

Symbols for Specifying Register Operands

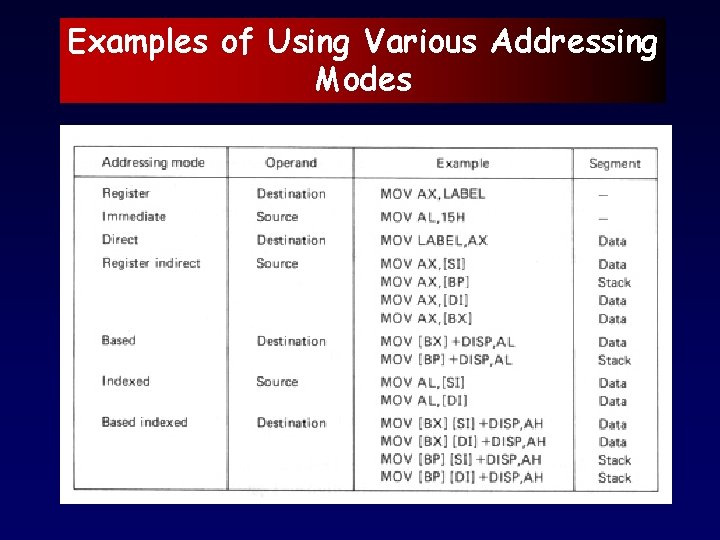

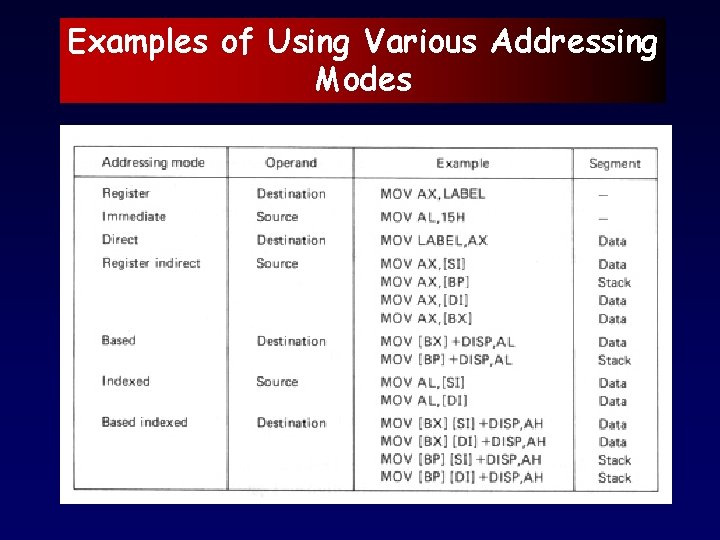

Examples of Using Various Addressing Modes

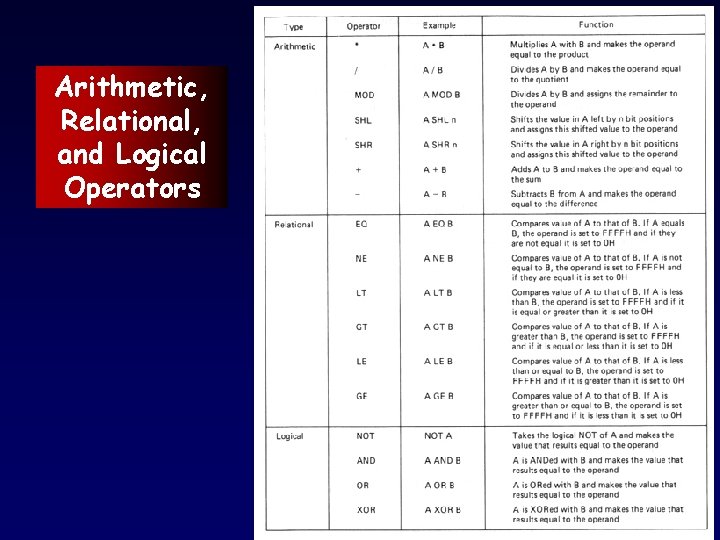

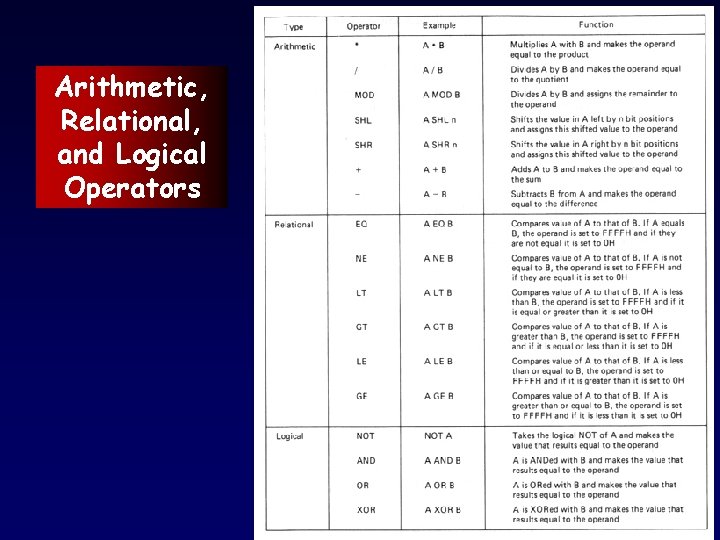

Arithmetic, Relational, and Logical Operators

Value-Returning and Attribute Operators

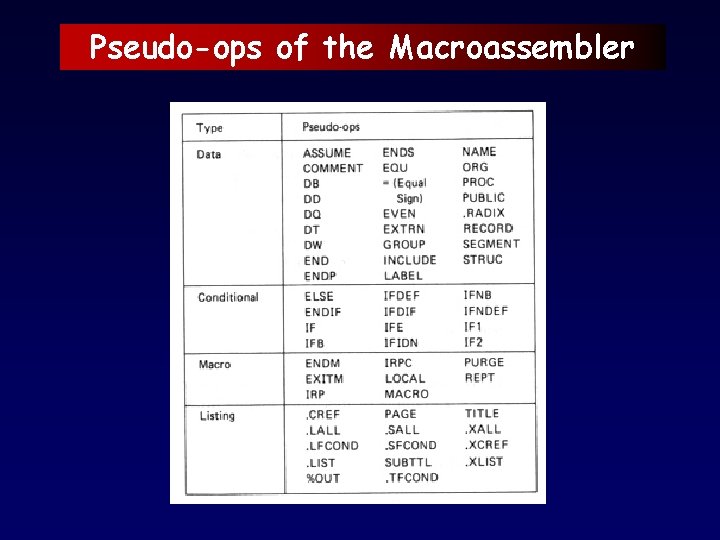

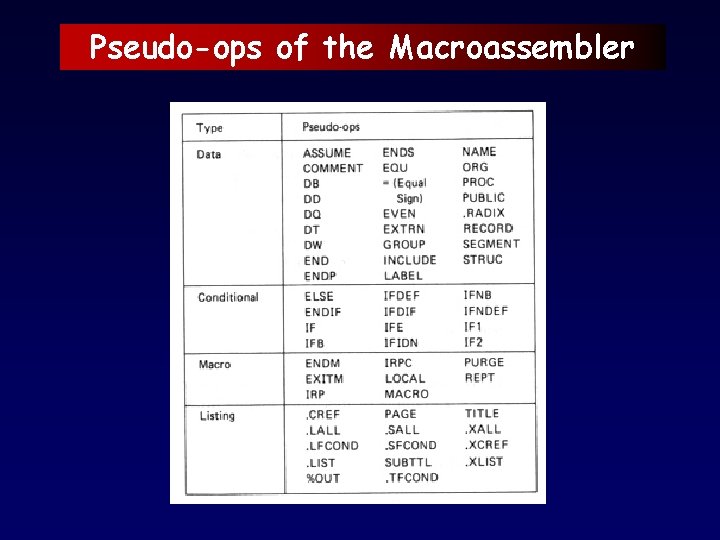

Pseudo-ops of the Macroassembler

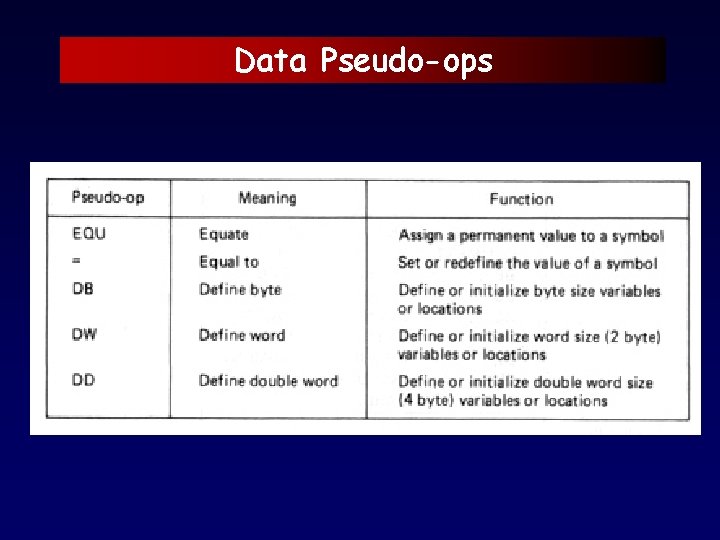

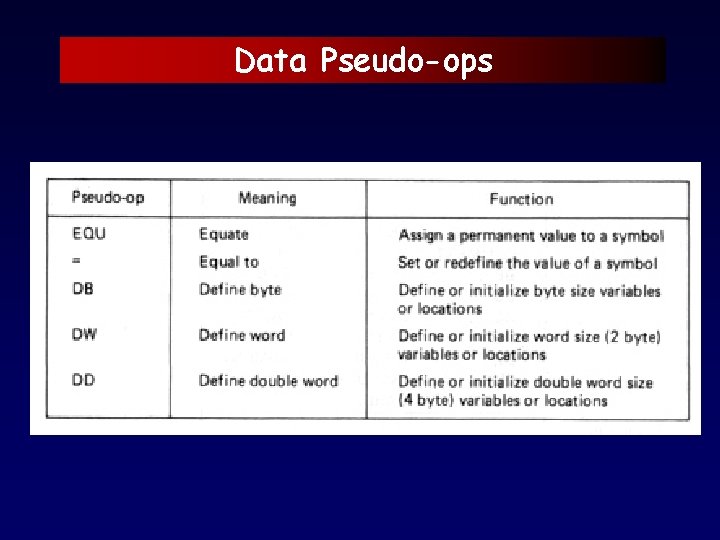

Data Pseudo-ops

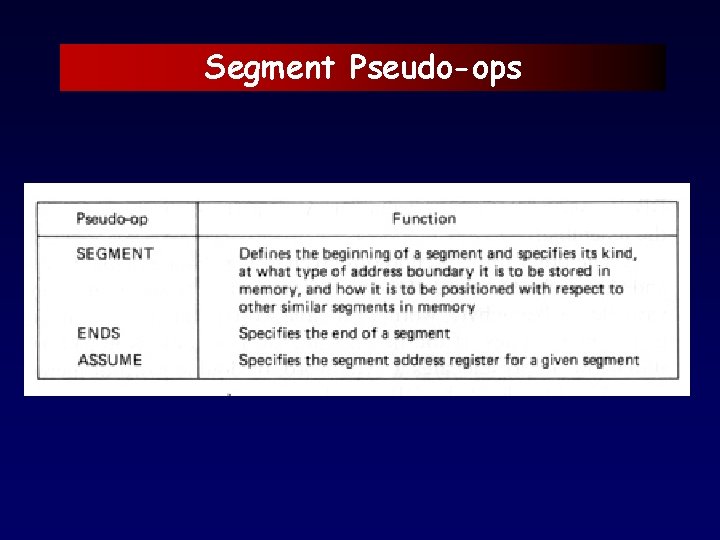

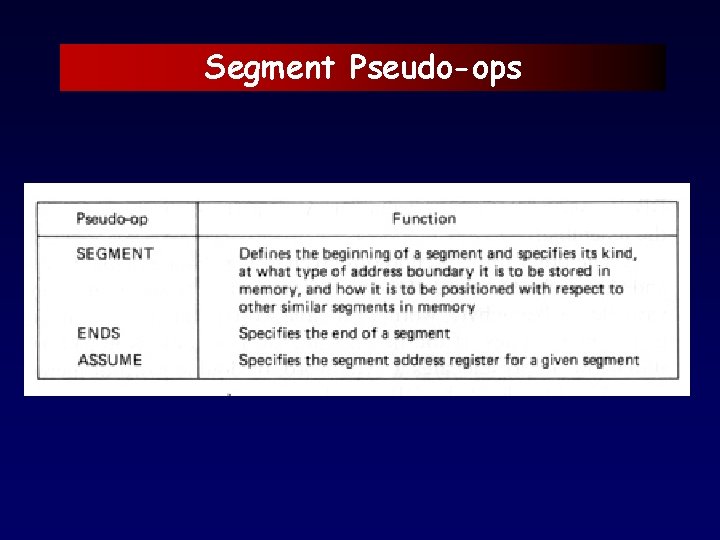

Segment Pseudo-ops

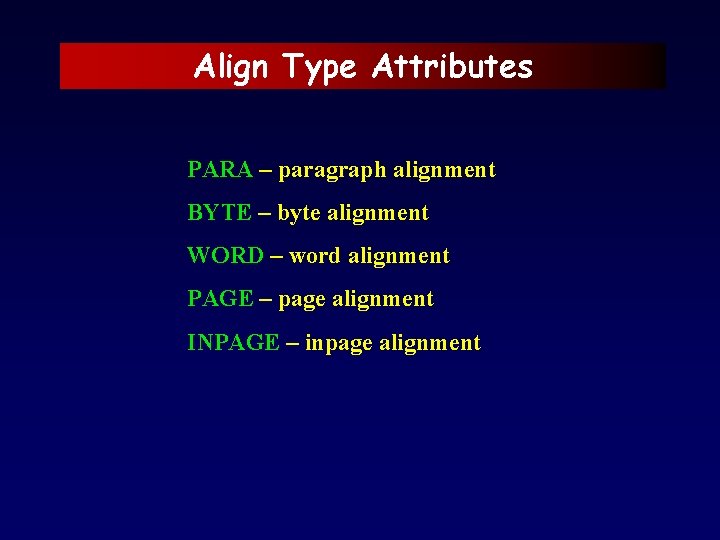

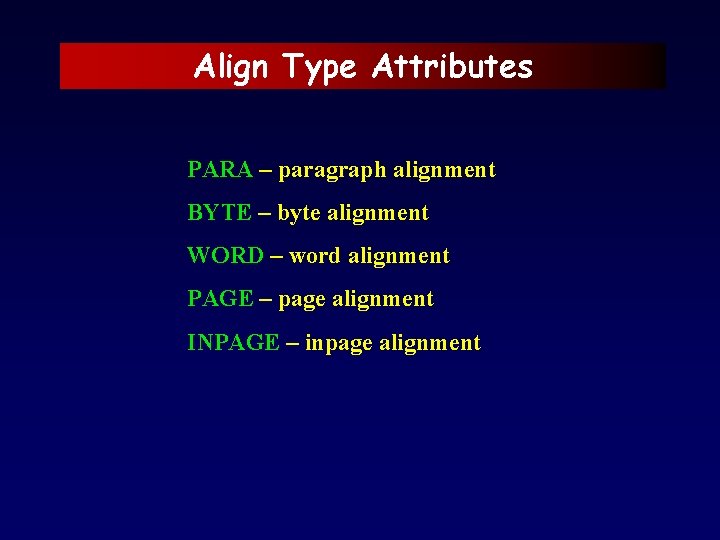

Align Type Attributes PARA – paragraph alignment BYTE – byte alignment WORD – word alignment PAGE – page alignment INPAGE – inpage alignment

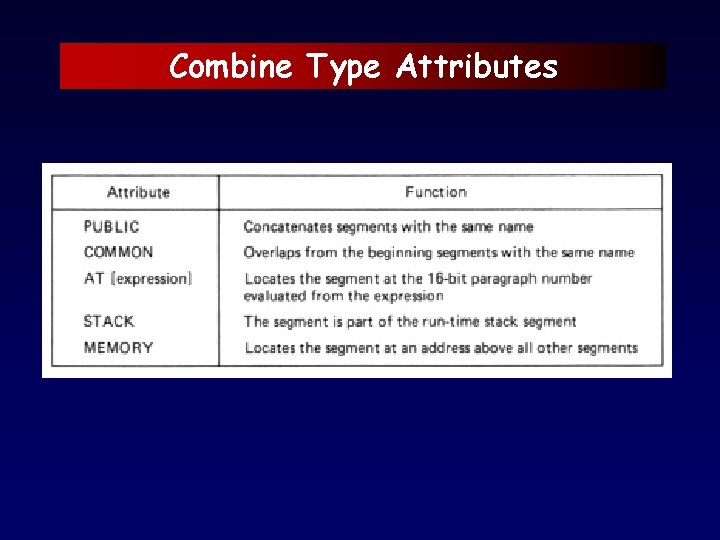

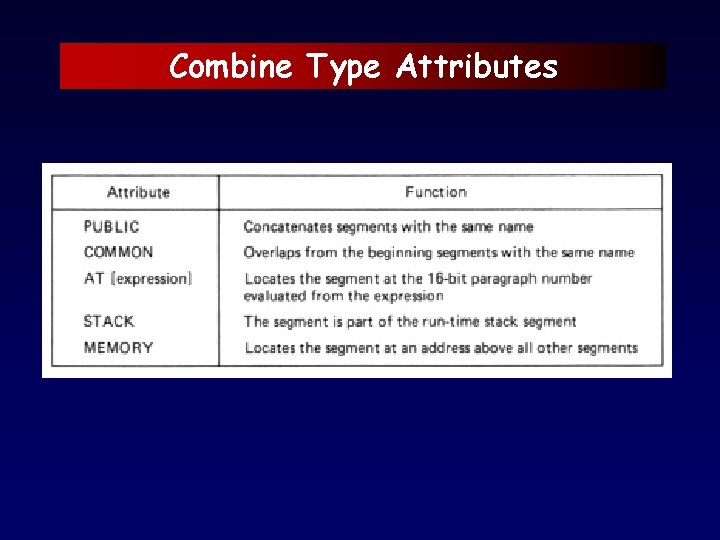

Combine Type Attributes

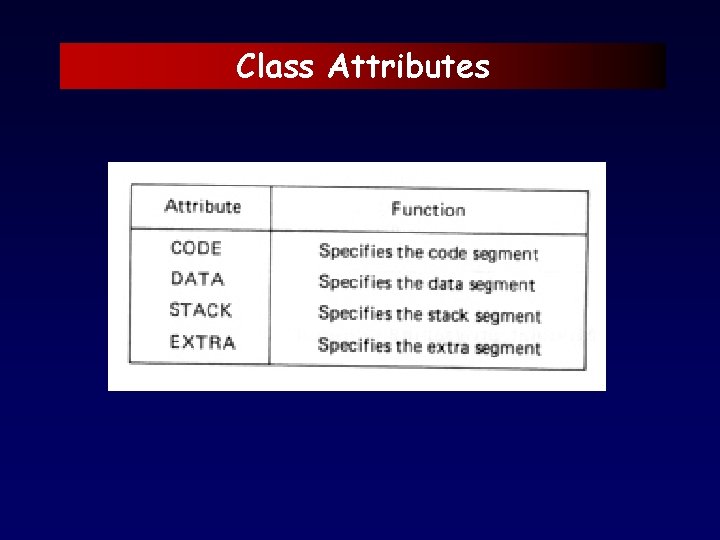

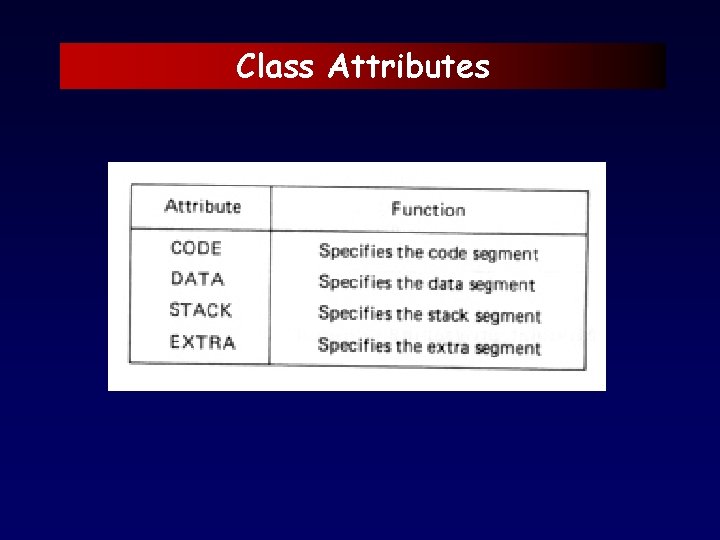

Class Attributes

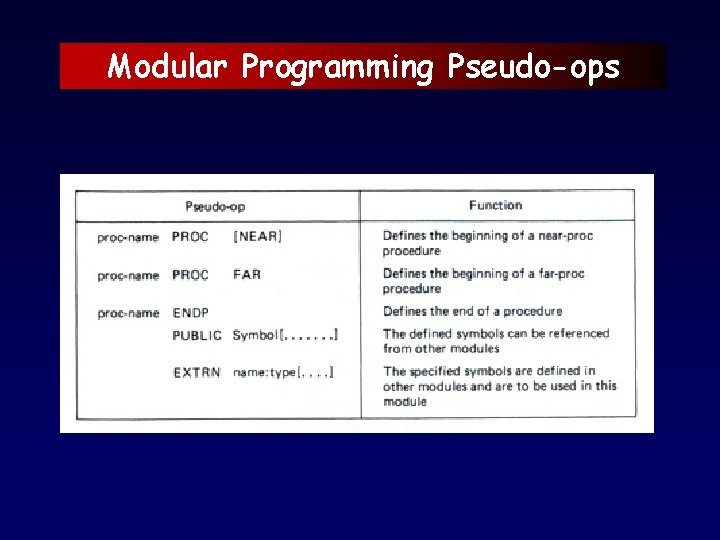

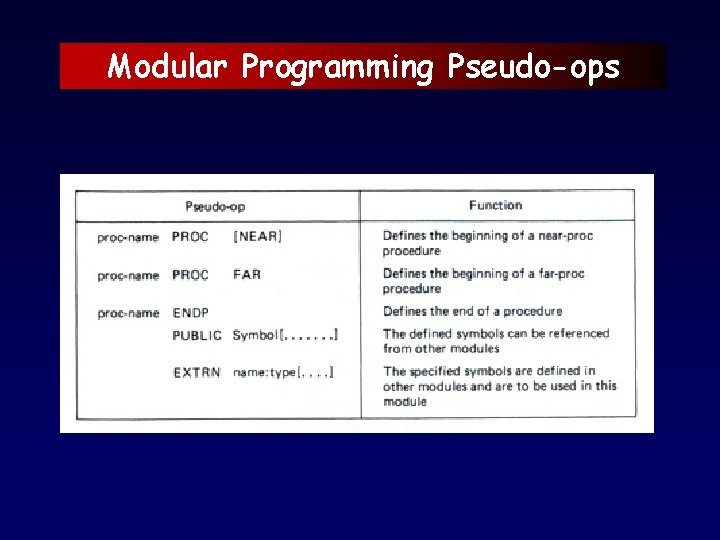

Modular Programming Pseudo-ops

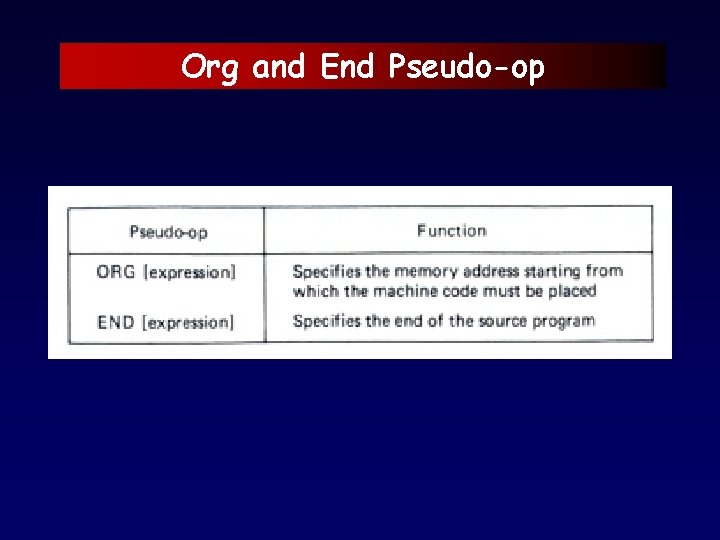

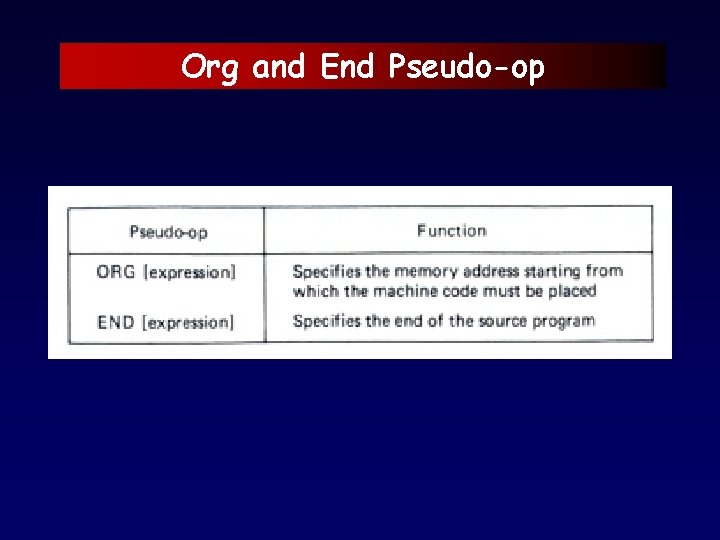

Org and End Pseudo-op

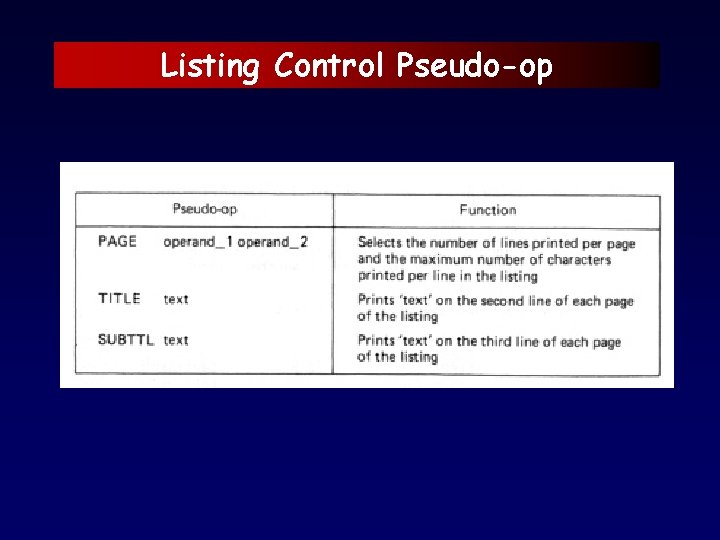

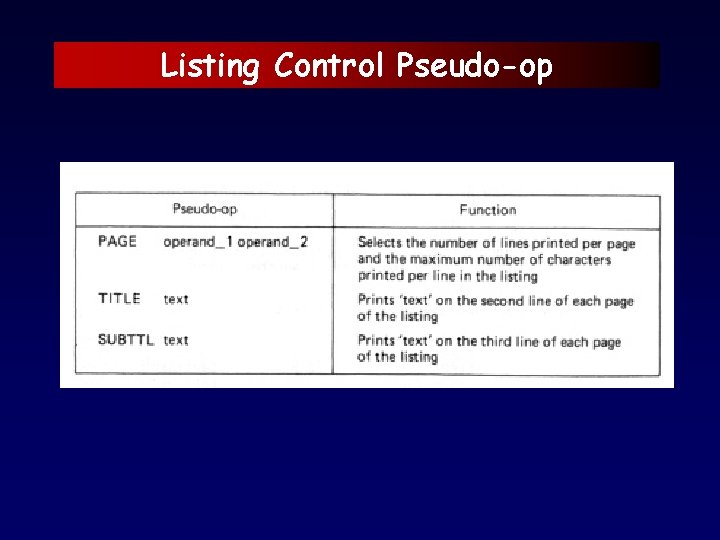

Listing Control Pseudo-op

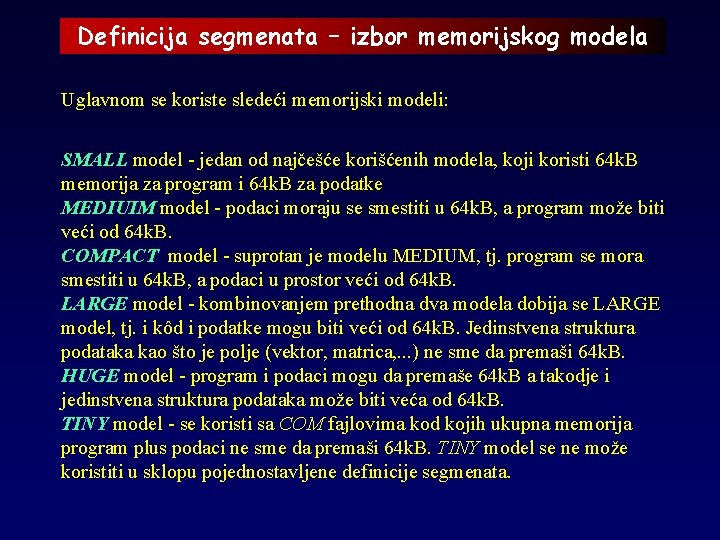

Definicija segmenata – izbor memorijskog modela Uglavnom se koriste sledeći memorijski modeli: SMALL model - jedan od najčešće korišćenih modela, koji koristi 64 k. B memorija za program i 64 k. B za podatke MEDIUIM model - podaci moraju se smestiti u 64 k. B, a program može biti veći od 64 k. B. COMPACT model - suprotan je modelu MEDIUM, tj. program se mora smestiti u 64 k. B, a podaci u prostor veći od 64 k. B. LARGE model - kombinovanjem prethodna dva modela dobija se LARGE model, tj. i kôd i podatke mogu biti veći od 64 k. B. Jedinstvena struktura podataka kao što je polje (vektor, matrica, . . . ) ne sme da premaši 64 k. B. HUGE model - program i podaci mogu da premaše 64 k. B a takodje i jedinstvena struktura podataka može biti veća od 64 k. B. TINY model - se koristi sa COM fajlovima kod kojih ukupna memorija program plus podaci ne sme da premaši 64 k. B. TINY model se ne može koristiti u sklopu pojednostavljene definicije segmenata.

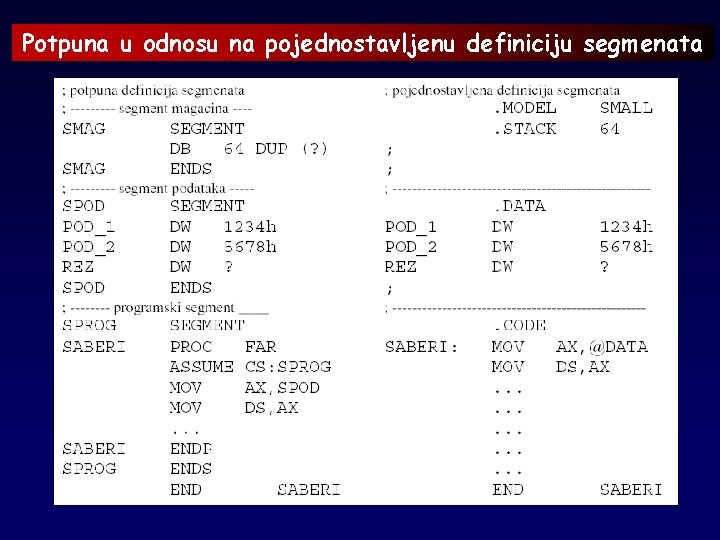

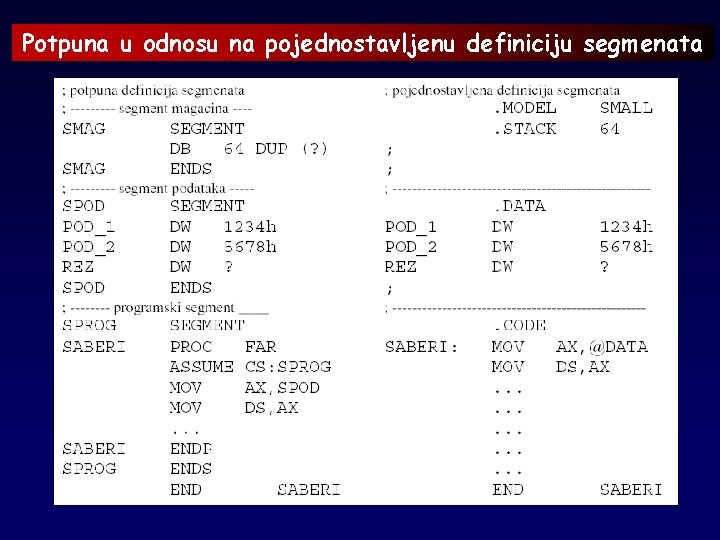

Potpuna u odnosu na pojednostavljenu definiciju segmenata

Uniqa incubis

Uniqa incubis Organizacija sastanka

Organizacija sastanka Giz organizacija

Giz organizacija Karta procesa

Karta procesa Organizacija podataka na racunaru

Organizacija podataka na racunaru Organizacija poslovanja

Organizacija poslovanja Pozivnica za poslovni sastanak

Pozivnica za poslovni sastanak Ikea pagrindinė organizacija

Ikea pagrindinė organizacija Organizacija definicija

Organizacija definicija Organizacija 5

Organizacija 5 Eba smjernice

Eba smjernice Lateralizacija značenje

Lateralizacija značenje Aukstais cehs

Aukstais cehs Organizacija 14

Organizacija 14 Uloga nevladinih organizacija

Uloga nevladinih organizacija Projektna organizacija

Projektna organizacija Organizacija

Organizacija Organizacija hotela

Organizacija hotela Organizacija 4

Organizacija 4 Kako se dijeli nervni sistem

Kako se dijeli nervni sistem Prostorna organizacija biocenoze

Prostorna organizacija biocenoze Vrste sastanaka

Vrste sastanaka Perceptivna organizacija

Perceptivna organizacija Gantogram projekta

Gantogram projekta Poslovni razgovor

Poslovni razgovor Sistema continuo definicion

Sistema continuo definicion Complejo mayor de histocompatibilidad

Complejo mayor de histocompatibilidad Sistema semashko o sistema centralizado

Sistema semashko o sistema centralizado Simbolo del sistema americano y europeo en dibujo tecnico

Simbolo del sistema americano y europeo en dibujo tecnico Novas abordagens da administração

Novas abordagens da administração Site:slidetodoc.com

Site:slidetodoc.com La familia como sistema

La familia como sistema Sistema operativo ms dos

Sistema operativo ms dos Circulacion cerrada doble incompleta

Circulacion cerrada doble incompleta Estructuras del sistema respiratorio

Estructuras del sistema respiratorio Fayol considerava a empresa como sistema racional de regras

Fayol considerava a empresa como sistema racional de regras Estrutura do sistema financeiro nacional

Estrutura do sistema financeiro nacional Sistema hazchem

Sistema hazchem Mi mntenimiento

Mi mntenimiento Paratiroidea

Paratiroidea Http://certificacion-electronica.sev.gob.mx/#/

Http://certificacion-electronica.sev.gob.mx/#/ Sistema trimetrico

Sistema trimetrico Pluto planta

Pluto planta Sistema escolar en alemania

Sistema escolar en alemania Manual sobre el sistema nacional anticorrupción

Manual sobre el sistema nacional anticorrupción Siss2009

Siss2009 Sistema harmonizado

Sistema harmonizado El sistema es un conjunto de

El sistema es un conjunto de Punto j en electrocardiograma

Punto j en electrocardiograma Ecuaciones no lineales ejemplos

Ecuaciones no lineales ejemplos Sistema nervoso autonomo

Sistema nervoso autonomo Kosti kao poluge

Kosti kao poluge Sistema informatico

Sistema informatico Sistema antero laterale

Sistema antero laterale Sistema nacional de control

Sistema nacional de control Gestão unificada de recursos institucionais

Gestão unificada de recursos institucionais Objetos do sistema solar

Objetos do sistema solar Desventajas de windows nt

Desventajas de windows nt Sistema nervioso y sus partes

Sistema nervioso y sus partes Sistema scolastico rumeno

Sistema scolastico rumeno Anemona do mar é equinodermo

Anemona do mar é equinodermo Diferencias sistemas operativos

Diferencias sistemas operativos Ejemplos de proyecciones financieras

Ejemplos de proyecciones financieras Sistemi di riferimento non inerziali

Sistemi di riferimento non inerziali Dibujo del sistema tegumentario

Dibujo del sistema tegumentario Estrela central

Estrela central Inmunidad activa y pasiva

Inmunidad activa y pasiva Sistema digestivo camarão

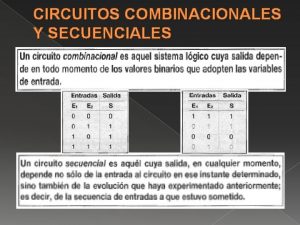

Sistema digestivo camarão Circuitos combinacionales y secuenciales

Circuitos combinacionales y secuenciales Priscila romano

Priscila romano Sistema operacional

Sistema operacional Sistema bibliotecario ateneo padova

Sistema bibliotecario ateneo padova Sistema sife

Sistema sife Que son las citas textuales

Que son las citas textuales Filiacion cromatica

Filiacion cromatica Language

Language Propulsión en el sistema digestivo

Propulsión en el sistema digestivo Desventajas del costeo absorbente

Desventajas del costeo absorbente Sistema nacional de contabilidad

Sistema nacional de contabilidad Sistema circulatório

Sistema circulatório La clasificación taxonómica

La clasificación taxonómica Sistema mecanico del microscopio

Sistema mecanico del microscopio Sistema nervoso autonomo

Sistema nervoso autonomo Sistema de proyeccion

Sistema de proyeccion Componentes de um sistema de remuneração funcional

Componentes de um sistema de remuneração funcional Sistema de ecuaciones incompatible

Sistema de ecuaciones incompatible Sistema de asesorias y tutorias uaeh

Sistema de asesorias y tutorias uaeh Cadastro de clientes do sistema financeiro nacional

Cadastro de clientes do sistema financeiro nacional Queerp

Queerp Sistema de informação transacional

Sistema de informação transacional Componentes del sistema solar

Componentes del sistema solar Sistema sppweb

Sistema sppweb Scala pqrst

Scala pqrst Sistemas eis

Sistemas eis Sistema nervoso entérico

Sistema nervoso entérico Reflexo patelar

Reflexo patelar Dimensión notacional

Dimensión notacional Momento torcente

Momento torcente Nefrona uzbūve

Nefrona uzbūve Ssnn

Ssnn Sistema endomembranoso

Sistema endomembranoso Entorno del sistema operativo windows

Entorno del sistema operativo windows Sistema digestivo titulo

Sistema digestivo titulo Che cos'è il controllo budgetario

Che cos'è il controllo budgetario Sistema sipac

Sistema sipac Hadopelagico

Hadopelagico Exoesqueleto

Exoesqueleto Introduccion del sistema respiratorio

Introduccion del sistema respiratorio Hormonas troficas

Hormonas troficas Saida mak sistema digestivo

Saida mak sistema digestivo Montiel jordan

Montiel jordan Sistema de doble circuito diagonal

Sistema de doble circuito diagonal Brojni sistemi pretvaranje

Brojni sistemi pretvaranje Gráfico y coloreó tres formas de célula del ser humano

Gráfico y coloreó tres formas de célula del ser humano Sistema hexadecimal

Sistema hexadecimal Propiedad en termodinamica

Propiedad en termodinamica Sistema egipcio

Sistema egipcio Sistema de ecuaciones

Sistema de ecuaciones Ser humano sistema abierto

Ser humano sistema abierto Propulsore voith schneider

Propulsore voith schneider Schiuma miscuglio omogeneo o eterogeneo

Schiuma miscuglio omogeneo o eterogeneo Tonsilax

Tonsilax Arreglo geométrico de un sistema de computadoras

Arreglo geométrico de un sistema de computadoras Agrocalidad zimbra

Agrocalidad zimbra Ovarium sinistrum

Ovarium sinistrum Sistemas de archivos distribuidos

Sistemas de archivos distribuidos