Arhitektura i organizacija raunara organizacja procesora Organizacija procesora

![[0 -5] [6 -10] [11 -15] [16 -20] [16 -31] [21 -31] [0 -5] [6 -10] [11 -15] [16 -20] [16 -31] [21 -31]](https://slidetodoc.com/presentation_image_h/f630e3408b816899834147519c869c30/image-30.jpg)

- Slides: 54

Arhitektura i organizacija računara organizacja procesora

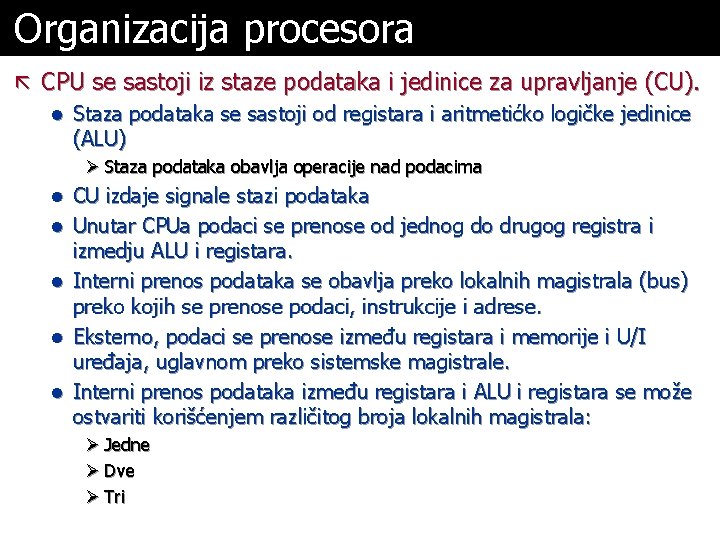

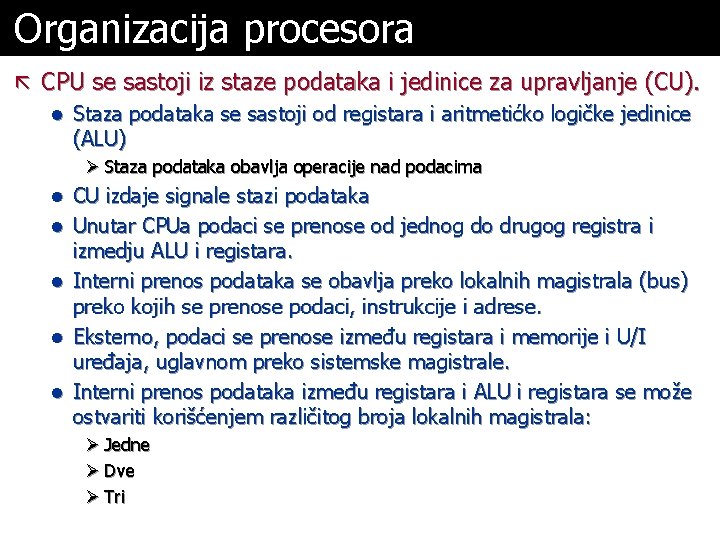

Organizacija procesora ã CPU se sastoji iz staze podataka i jedinice za upravljanje (CU). l Staza podataka se sastoji od registara i aritmetićko logičke jedinice (ALU) Ø Staza podataka obavlja operacije nad podacima l CU izdaje signale stazi podataka l Unutar CPUa podaci se prenose od jednog do drugog registra i l l l izmedju ALU i registara. Interni prenos podataka se obavlja preko lokalnih magistrala (bus) preko kojih se prenose podaci, instrukcije i adrese. Eksterno, podaci se prenose između registara i memorije i U/I uređaja, uglavnom preko sistemske magistrale. Interni prenos podataka između registara i ALU i registara se može ostvariti korišćenjem različitog broja lokalnih magistrala: Ø Jedne Ø Dve Ø Tri

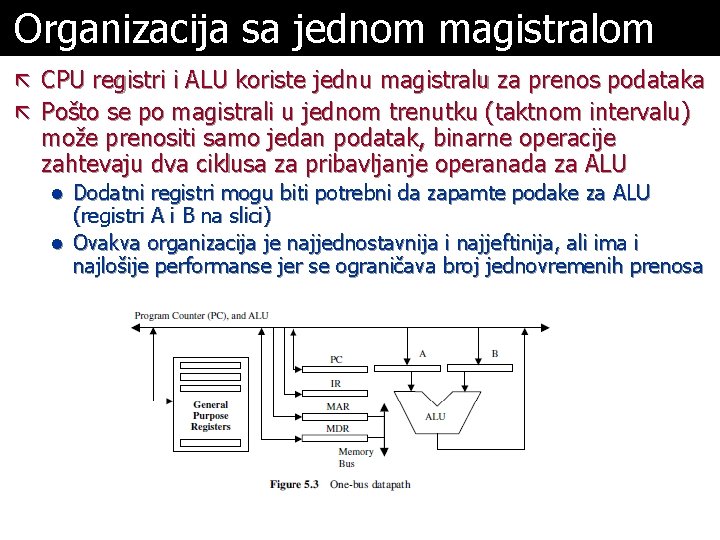

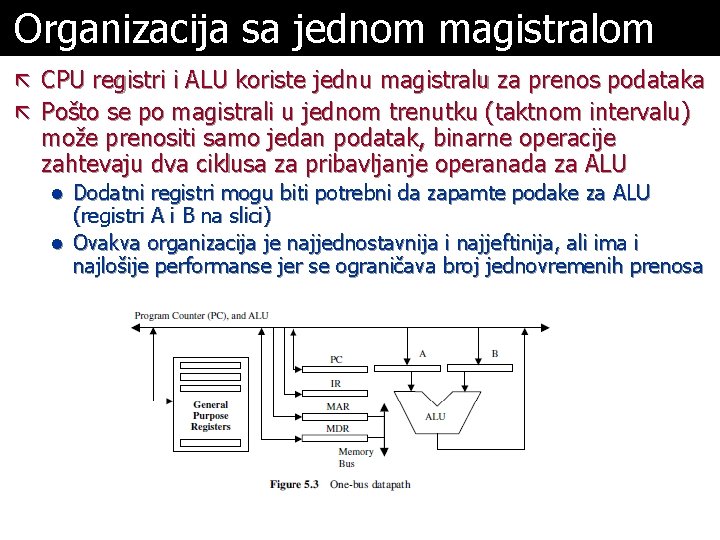

Organizacija sa jednom magistralom ã CPU registri i ALU koriste jednu magistralu za prenos podataka ã Pošto se po magistrali u jednom trenutku (taktnom intervalu) može prenositi samo jedan podatak, binarne operacije zahtevaju dva ciklusa za pribavljanje operanada za ALU l Dodatni registri mogu biti potrebni da zapamte podake za ALU (registri A i B na slici) l Ovakva organizacija je najjednostavnija i najjeftinija, ali ima i najlošije performanse jer se ograničava broj jednovremenih prenosa

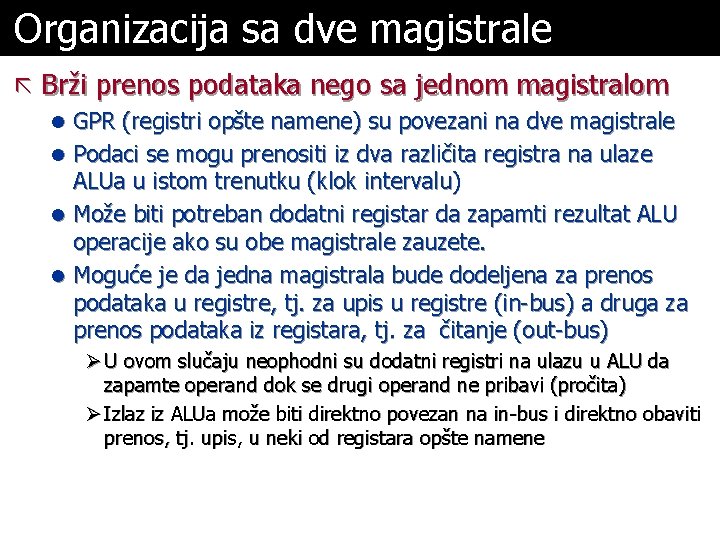

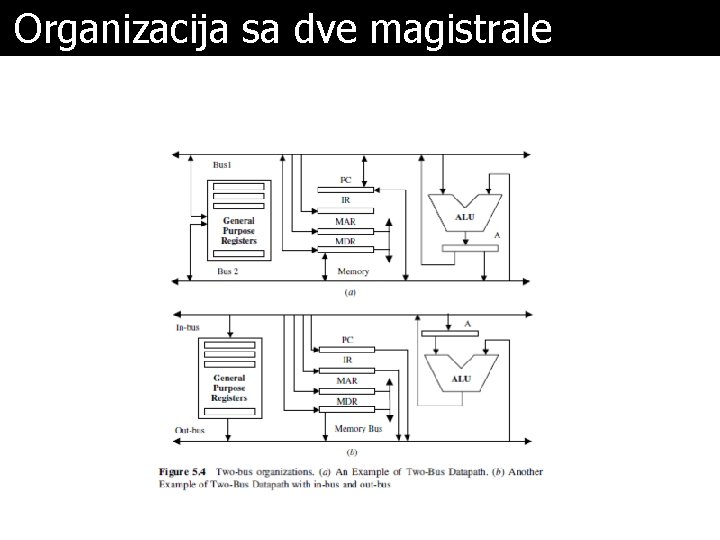

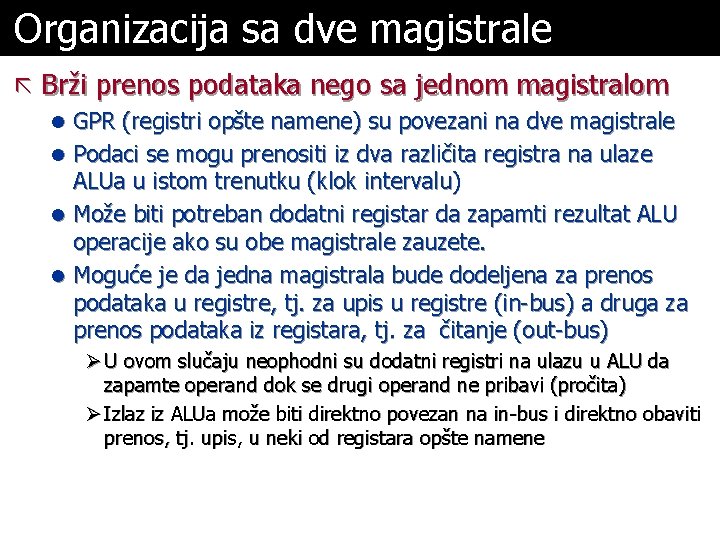

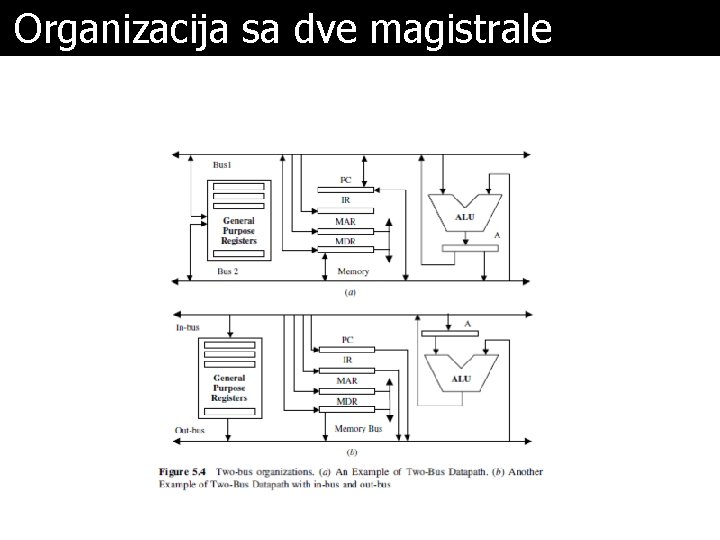

Organizacija sa dve magistrale ã Brži prenos podataka nego sa jednom magistralom l GPR (registri opšte namene) su povezani na dve magistrale l Podaci se mogu prenositi iz dva različita registra na ulaze ALUa u istom trenutku (klok intervalu) l Može biti potreban dodatni registar da zapamti rezultat ALU operacije ako su obe magistrale zauzete. l Moguće je da jedna magistrala bude dodeljena za prenos podataka u registre, tj. za upis u registre (in-bus) a druga za prenos podataka iz registara, tj. za čitanje (out-bus) Ø U ovom slučaju neophodni su dodatni registri na ulazu u ALU da zapamte operand dok se drugi operand ne pribavi (pročita) Ø Izlaz iz ALUa može biti direktno povezan na in-bus i direktno obaviti prenos, tj. upis, u neki od registara opšte namene

Organizacija sa dve magistrale

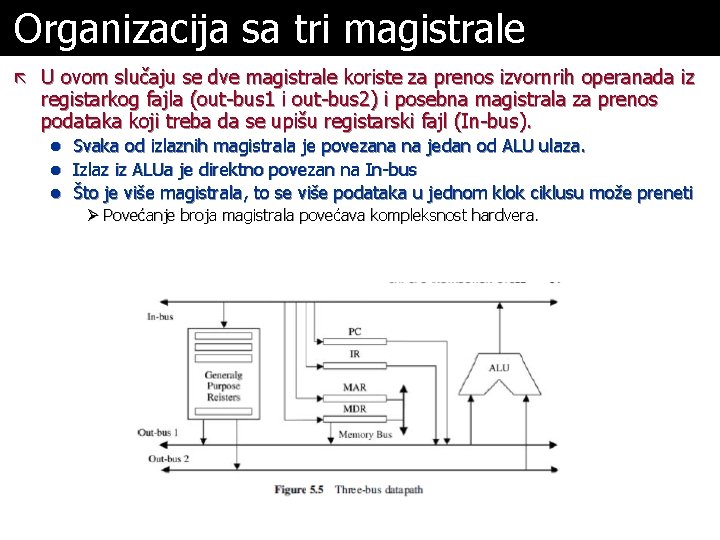

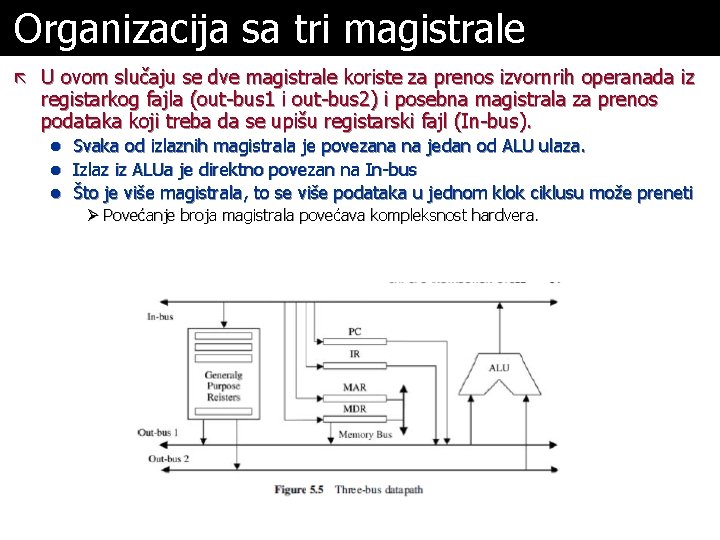

Organizacija sa tri magistrale ã U ovom slučaju se dve magistrale koriste za prenos izvornrih operanada iz registarkog fajla (out-bus 1 i out-bus 2) i posebna magistrala za prenos podataka koji treba da se upišu registarski fajl (In-bus). Svaka od izlaznih magistrala je povezana na jedan od ALU ulaza. Izlaz iz ALUa je direktno povezan na In-bus l Što je više magistrala, to se više podataka u jednom klok ciklusu može preneti l l Ø Povećanje broja magistrala povećava kompleksnost hardvera.

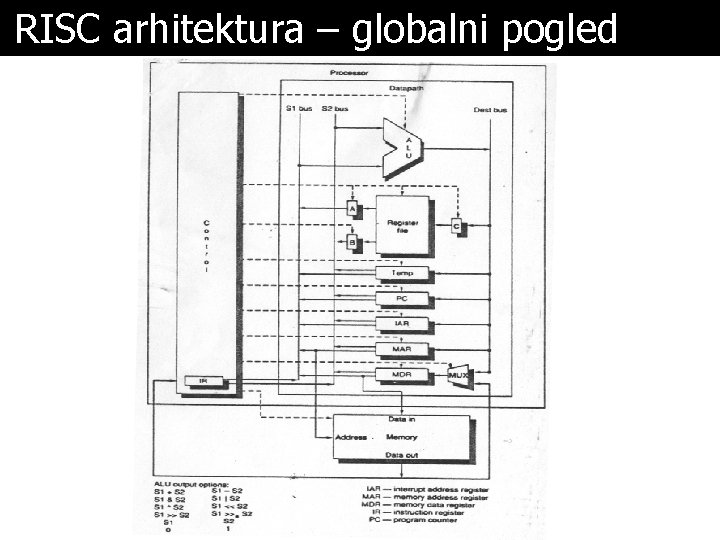

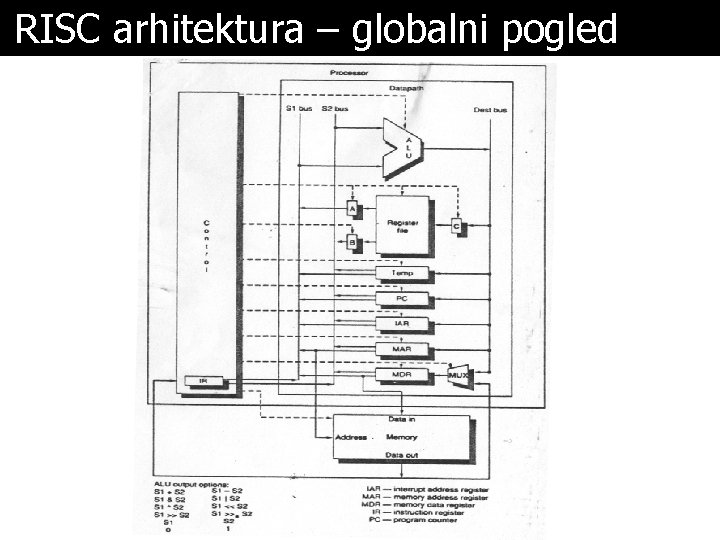

RISC arhitektura – globalni pogled

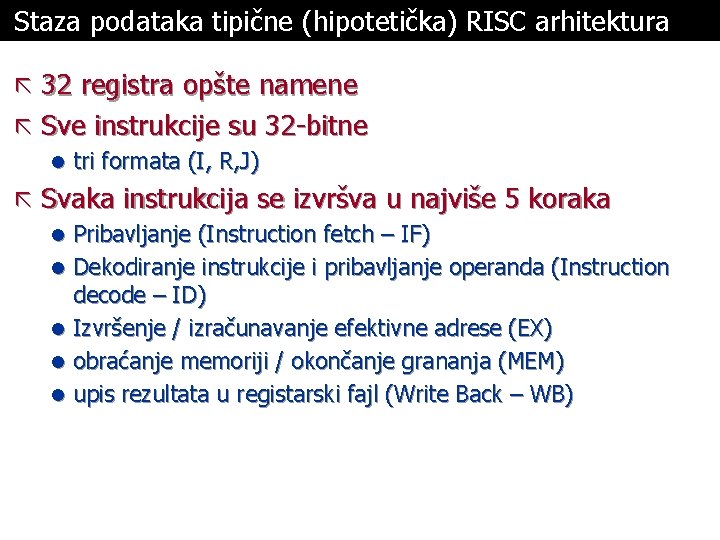

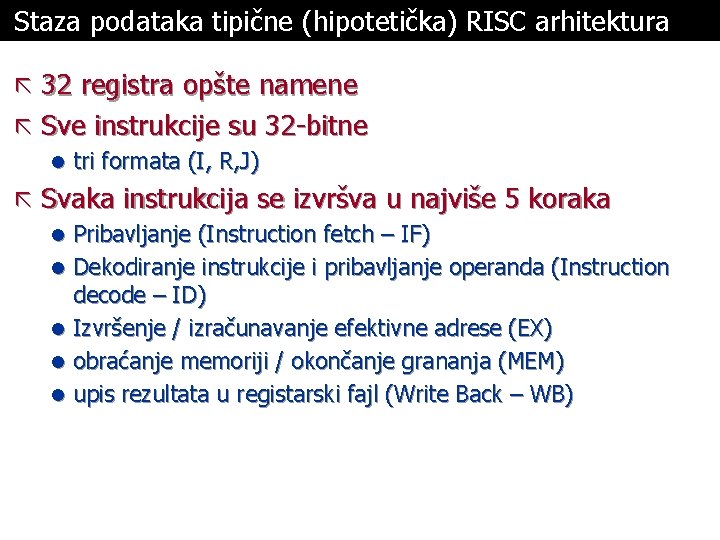

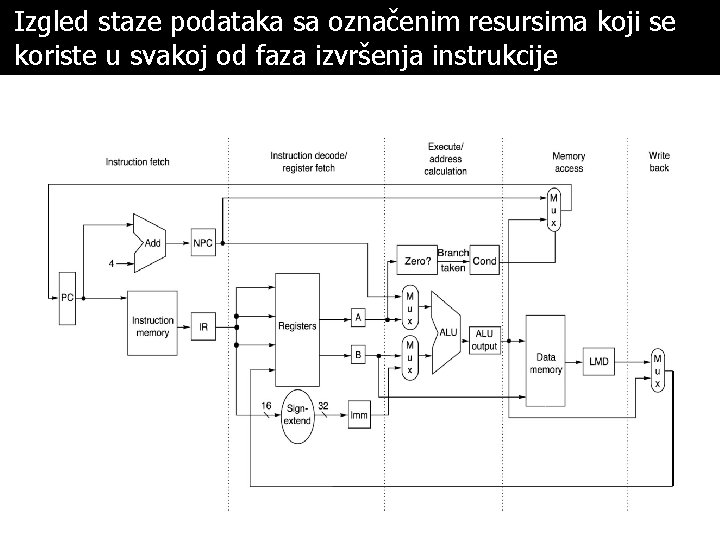

Staza podataka tipične (hipotetička) RISC arhitektura ã 32 registra opšte namene ã Sve instrukcije su 32 -bitne l tri formata (I, R, J) ã Svaka instrukcija se izvršva u najviše 5 koraka l Pribavljanje (Instruction fetch – IF) l Dekodiranje instrukcije i pribavljanje operanda (Instruction decode – ID) l Izvršenje / izračunavanje efektivne adrese (EX) l obraćanje memoriji / okončanje grananja (MEM) l upis rezultata u registarski fajl (Write Back – WB)

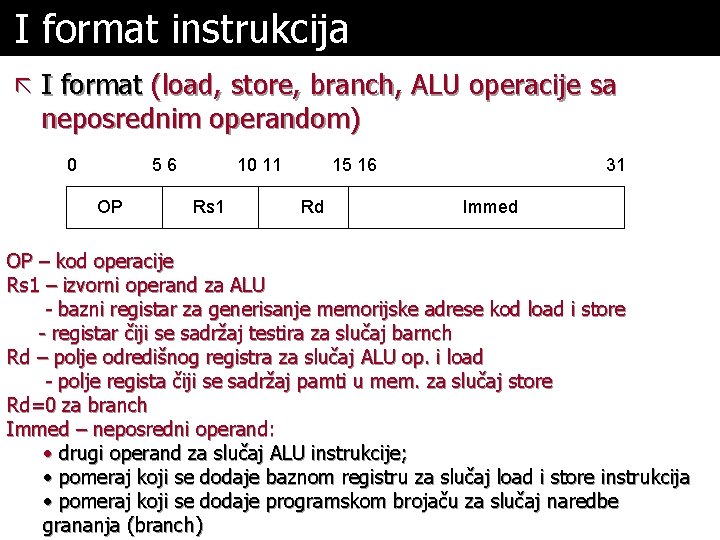

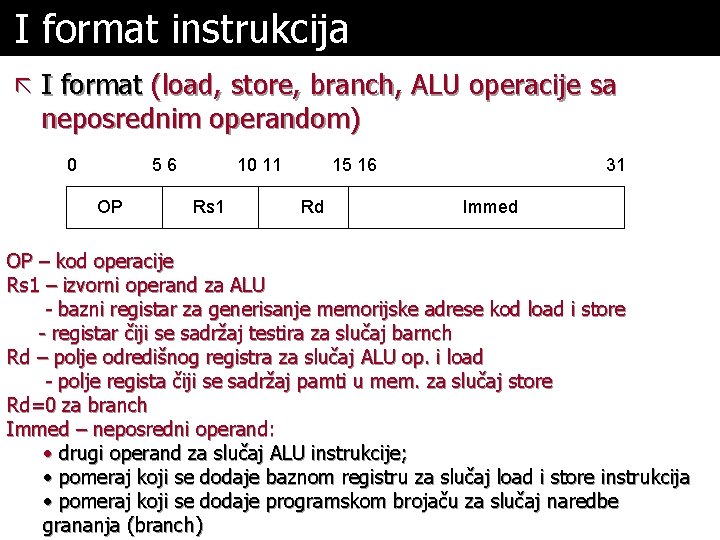

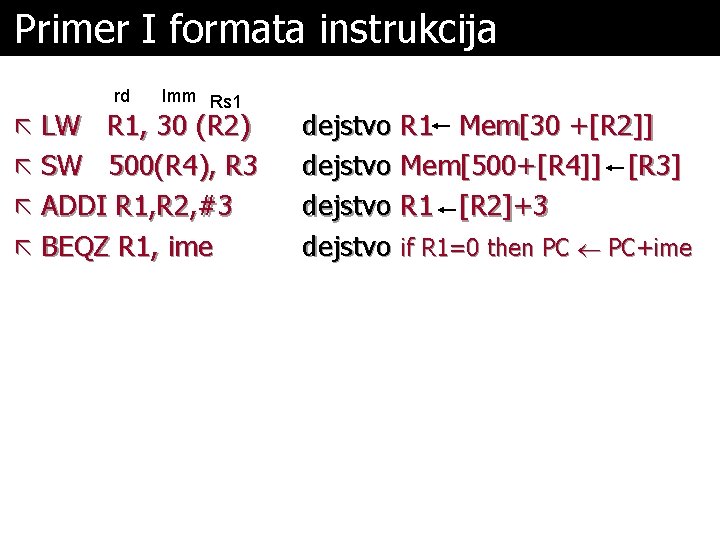

I format instrukcija ã I format (load, store, branch, ALU operacije sa neposrednim operandom) 0 56 OP 10 11 Rs 1 15 16 Rd 31 Immed OP – kod operacije Rs 1 – izvorni operand za ALU - bazni registar za generisanje memorijske adrese kod load i store - registar čiji se sadržaj testira za slučaj barnch Rd – polje odredišnog registra za slučaj ALU op. i load - polje regista čiji se sadržaj pamti u mem. za slučaj store Rd=0 za branch Immed – neposredni operand: • drugi operand za slučaj ALU instrukcije; • pomeraj koji se dodaje baznom registru za slučaj load i store instrukcija • pomeraj koji se dodaje programskom brojaču za slučaj naredbe grananja (branch)

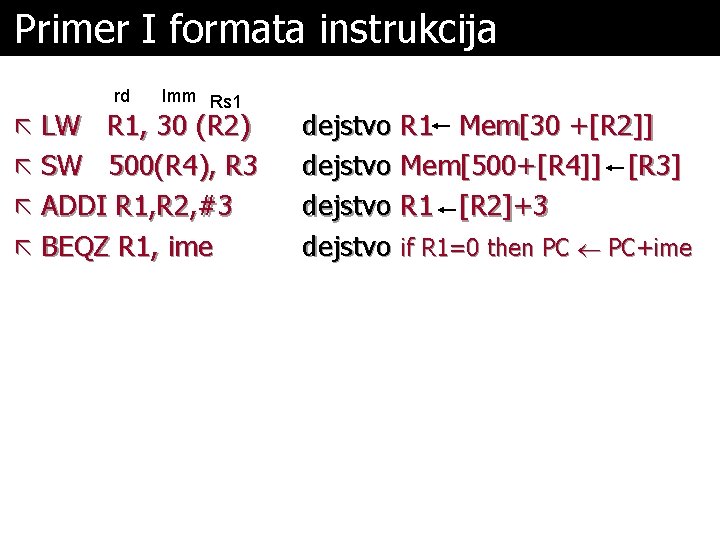

Primer I formata instrukcija rd ã LW Imm Rs 1 R 1, 30 (R 2) ã SW 500(R 4), R 3 ã ADDI R 1, R 2, #3 ã BEQZ R 1, ime dejstvo R 1 Mem[30 +[R 2]] dejstvo Mem[500+[R 4]] [R 3] dejstvo R 1 [R 2]+3 dejstvo if R 1=0 then PC PC+ime

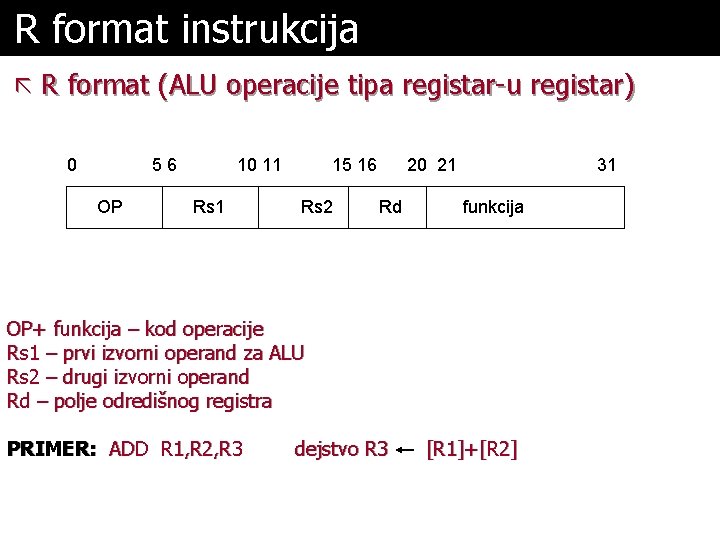

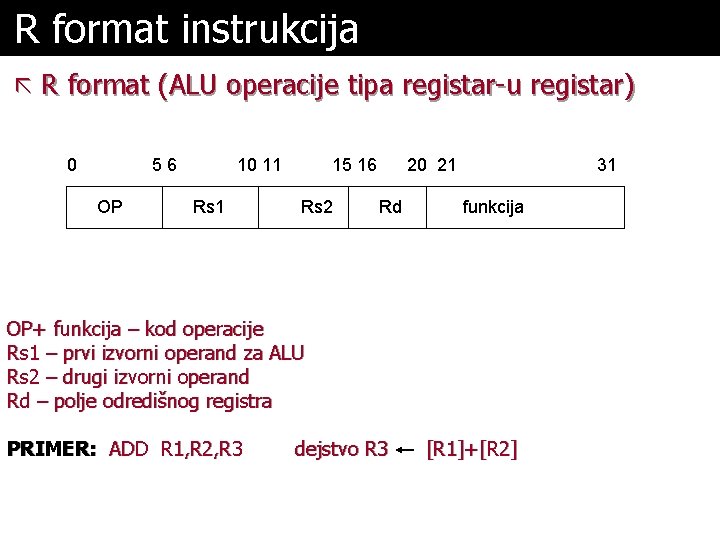

R format instrukcija ã R format (ALU operacije tipa registar-u registar) 0 56 OP 10 11 Rs 1 15 16 Rs 2 20 21 Rd 31 funkcija OP+ funkcija – kod operacije Rs 1 – prvi izvorni operand za ALU Rs 2 – drugi izvorni operand Rd – polje odredišnog registra PRIMER: ADD R 1, R 2, R 3 dejstvo R 3 [R 1]+[R 2]

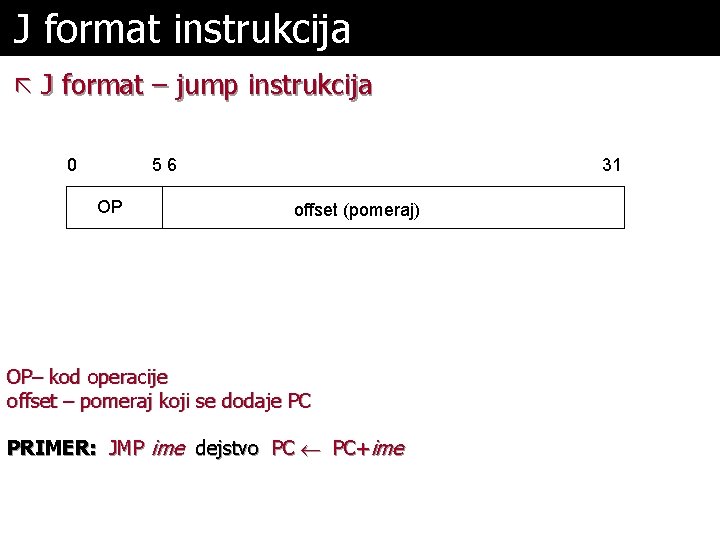

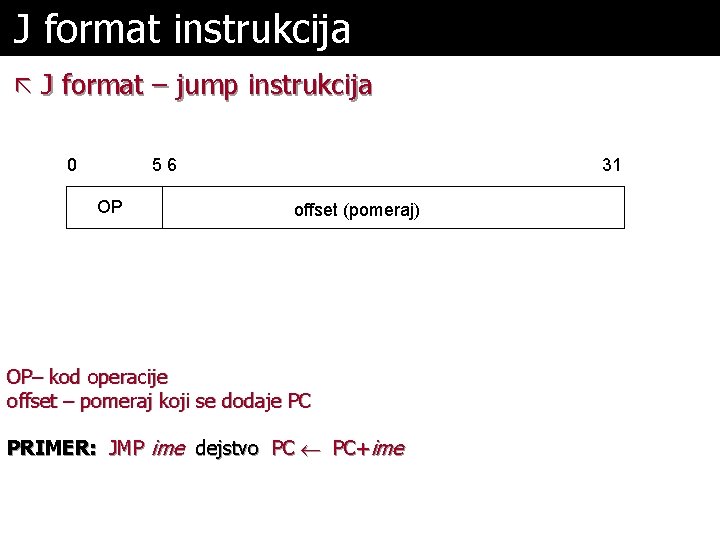

J format instrukcija ã J format – jump instrukcija 0 56 OP 31 offset (pomeraj) OP– kod operacije offset – pomeraj koji se dodaje PC PRIMER: JMP ime dejstvo PC PC+ime

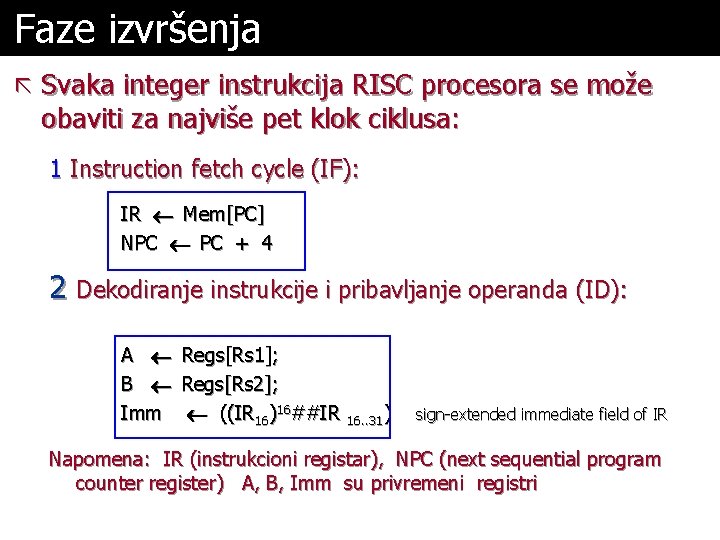

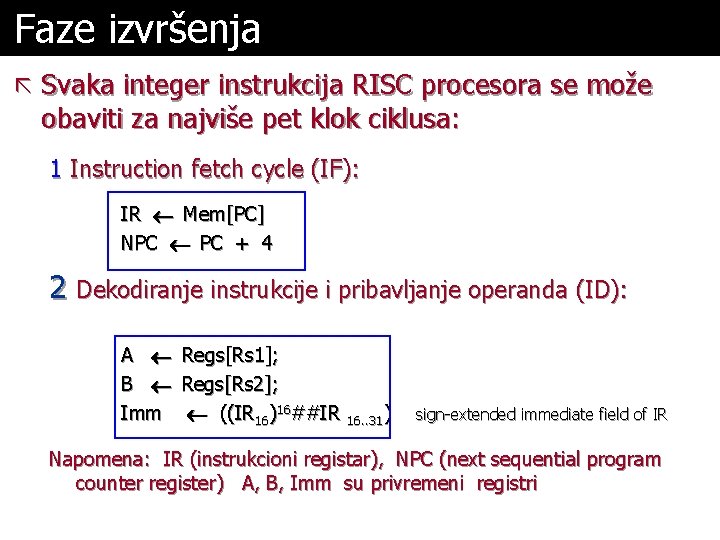

Faze izvršenja ã Svaka integer instrukcija RISC procesora se može obaviti za najviše pet klok ciklusa: 1 Instruction fetch cycle (IF): IR ¬ Mem[PC] NPC ¬ PC + 4 2 Dekodiranje instrukcije i pribavljanje operanda (ID): A ¬ B ¬ Imm Regs[Rs 1]; Regs[Rs 2]; ¬ ((IR 16)16##IR 16. . 31) sign-extended immediate field of IR Napomena: IR (instrukcioni registar), NPC (next sequential program counter register) A, B, Imm su privremeni registri

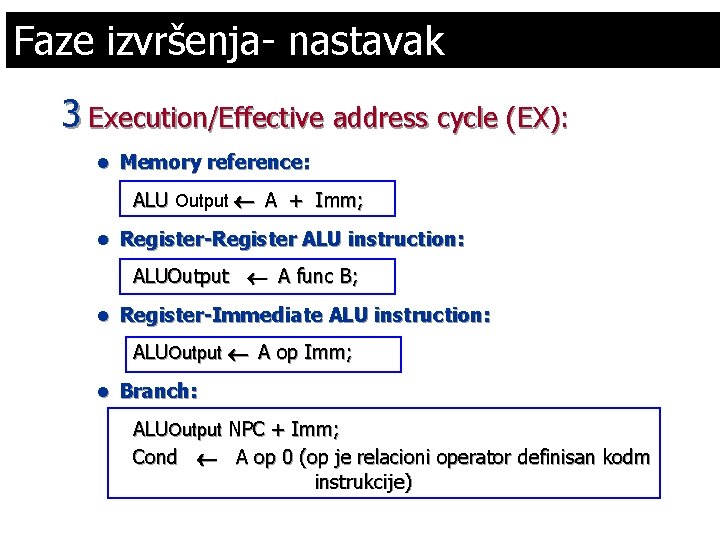

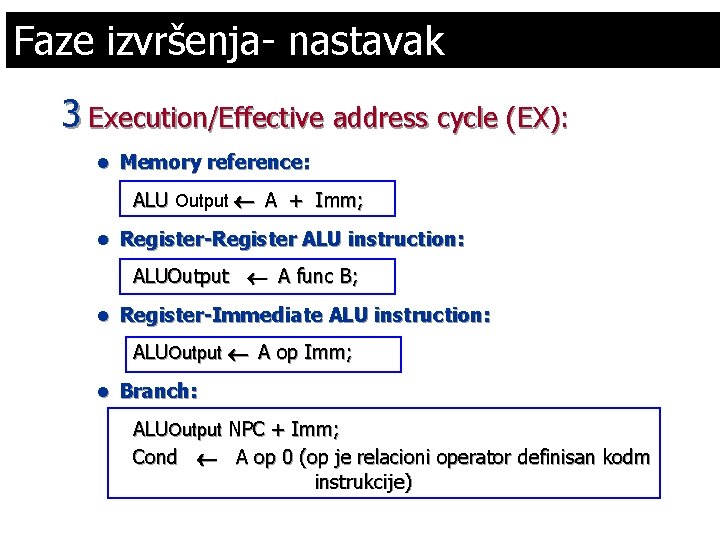

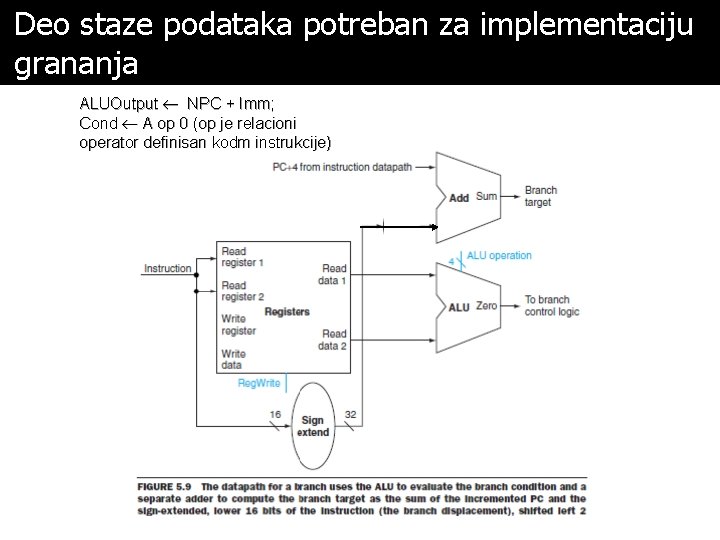

Faze izvršenja- nastavak 3 Execution/Effective address cycle (EX): l Memory reference: ALU Output ¬ A + Imm; l Register-Register ALU instruction: ALUOutput ¬ A func B; l Register-Immediate ALU instruction: ALUOutput ¬ A op Imm; l Branch: ALUOutput NPC + Imm; Cond ¬ A op 0 (op je relacioni operator definisan kodm instrukcije)

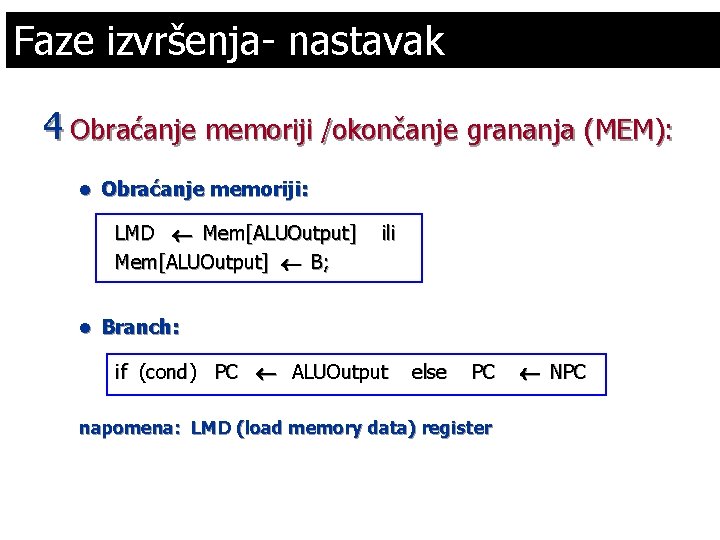

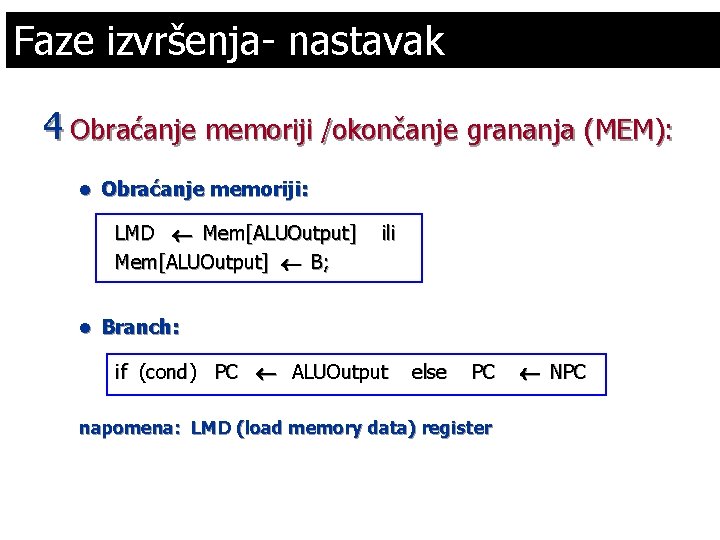

Faze izvršenja- nastavak 4 Obraćanje memoriji /okončanje grananja (MEM): l Obraćanje memoriji: LMD ¬ Mem[ALUOutput] ¬ B; ili l Branch: if (cond) PC ¬ ALUOutput else PC napomena: LMD (load memory data) register ¬ NPC

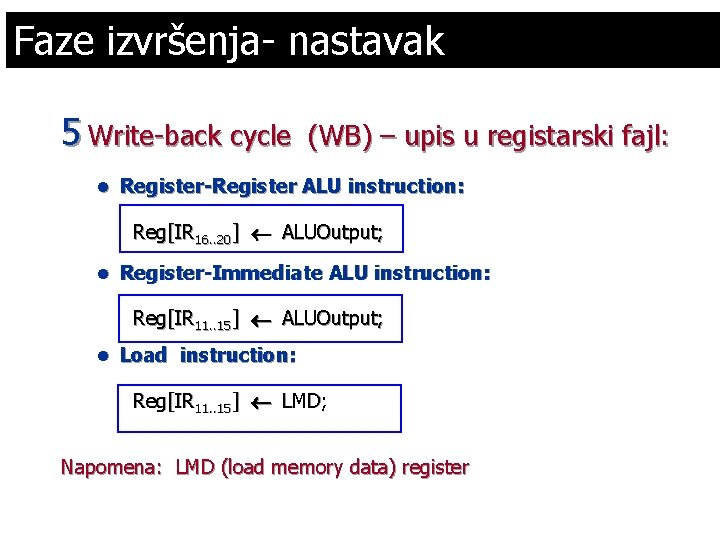

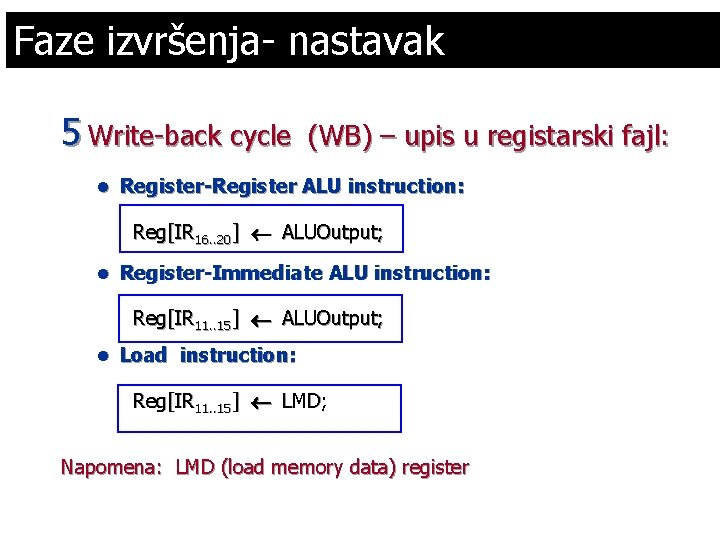

Faze izvršenja- nastavak 5 Write-back cycle (WB) – upis u registarski fajl: l Register-Register ALU instruction: Reg[IR 16. . 20] ¬ ALUOutput; l Register-Immediate ALU instruction: Reg[IR 11. . 15] ¬ ALUOutput; l Load instruction: Reg[IR 11. . 15] ¬ LMD; Napomena: LMD (load memory data) register

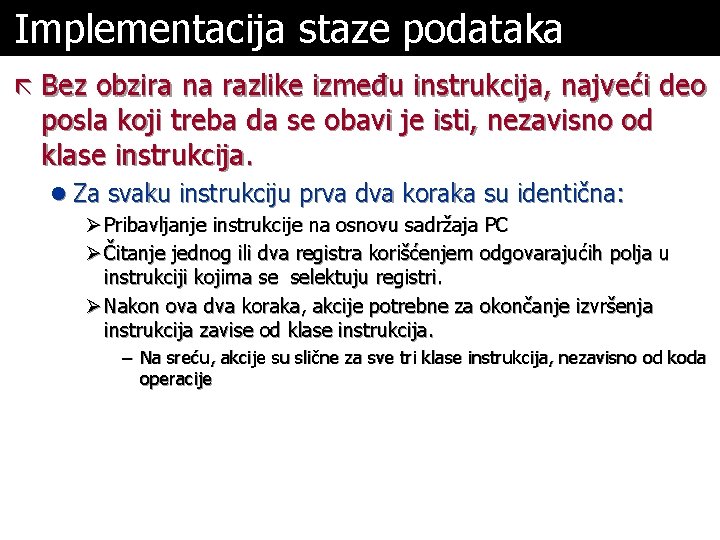

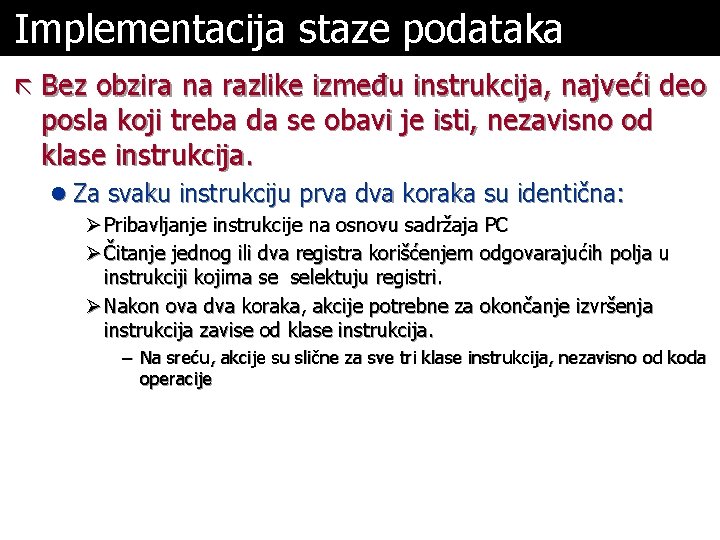

Implementacija staze podataka ã Bez obzira na razlike između instrukcija, najveći deo posla koji treba da se obavi je isti, nezavisno od klase instrukcija. l Za svaku instrukciju prva dva koraka su identična: Ø Pribavljanje instrukcije na osnovu sadržaja PC Ø Čitanje jednog ili dva registra korišćenjem odgovarajućih polja u instrukciji kojima se selektuju registri. Ø Nakon ova dva koraka, akcije potrebne za okončanje izvršenja instrukcija zavise od klase instrukcija. – Na sreću, akcije su slične za sve tri klase instrukcija, nezavisno od koda operacije

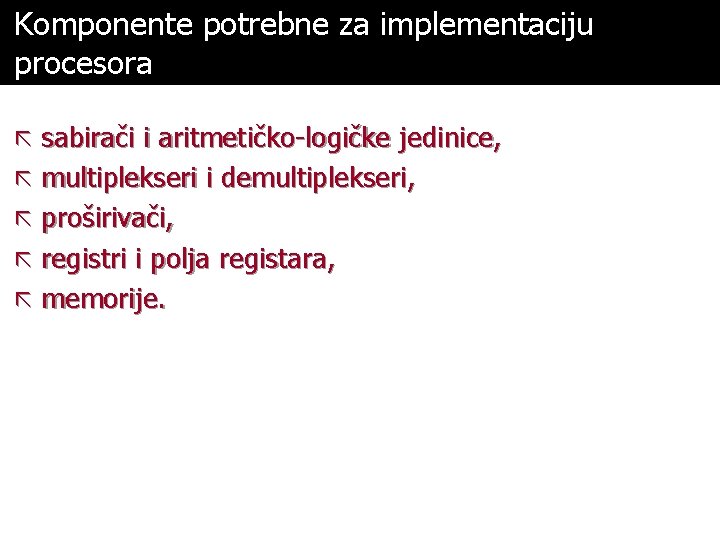

Komponente potrebne za implementaciju procesora ã sabirači i aritmetičko-logičke jedinice, ã multiplekseri i demultiplekseri, ã proširivači, ã registri i polja registara, ã memorije.

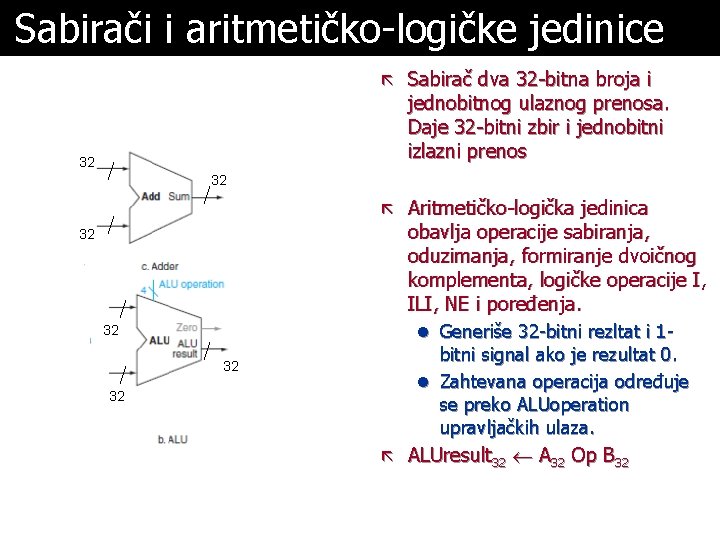

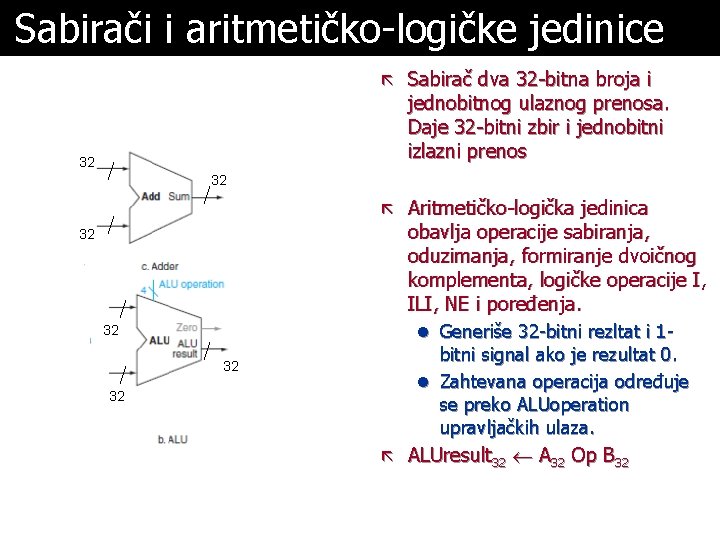

Sabirači i aritmetičko-logičke jedinice ã Sabirač dva 32 -bitna broja i jednobitnog ulaznog prenosa. Daje 32 -bitni zbir i jednobitni izlazni prenos 32 32 ã Aritmetičko-logička jedinica obavlja operacije sabiranja, oduzimanja, formiranje dvoičnog komplementa, logičke operacije I, ILI, NE i poređenja. 32 l Generiše 32 -bitni rezltat i 1 - 32 32 32 bitni signal ako je rezultat 0. l Zahtevana operacija određuje se preko ALUoperation upravljačkih ulaza. ã ALUresult 32 A 32 Op B 32

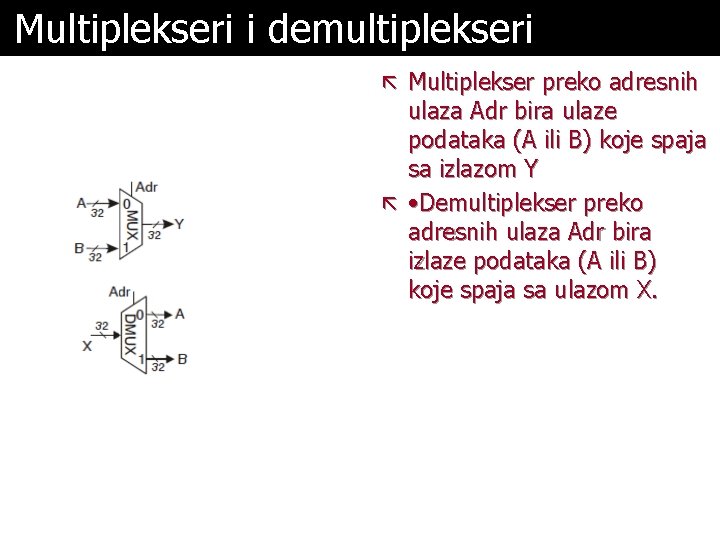

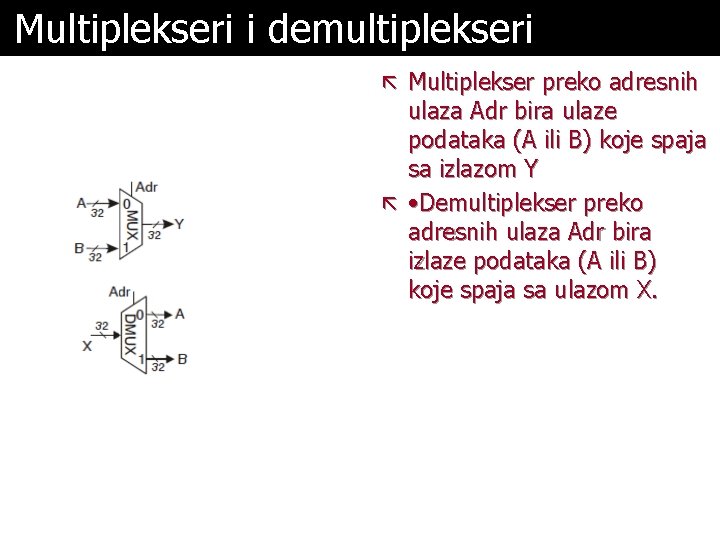

Multiplekseri i demultiplekseri ã Multiplekser preko adresnih ulaza Adr bira ulaze podataka (A ili B) koje spaja sa izlazom Y ã • Demultiplekser preko adresnih ulaza Adr bira izlaze podataka (A ili B) koje spaja sa ulazom X.

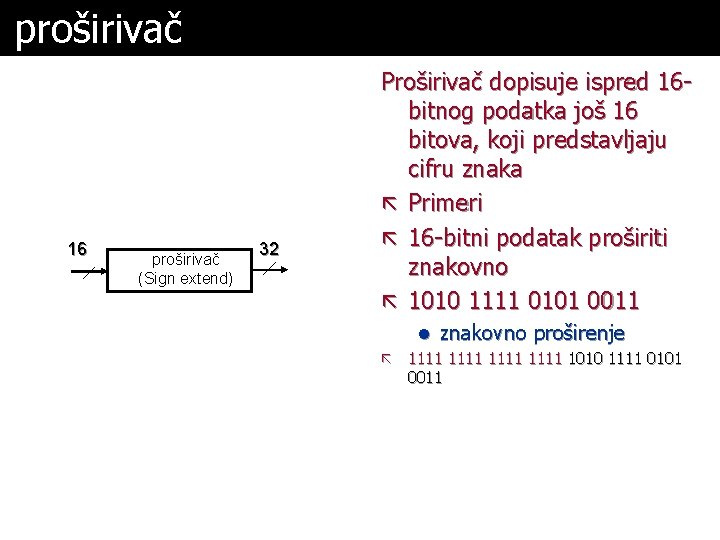

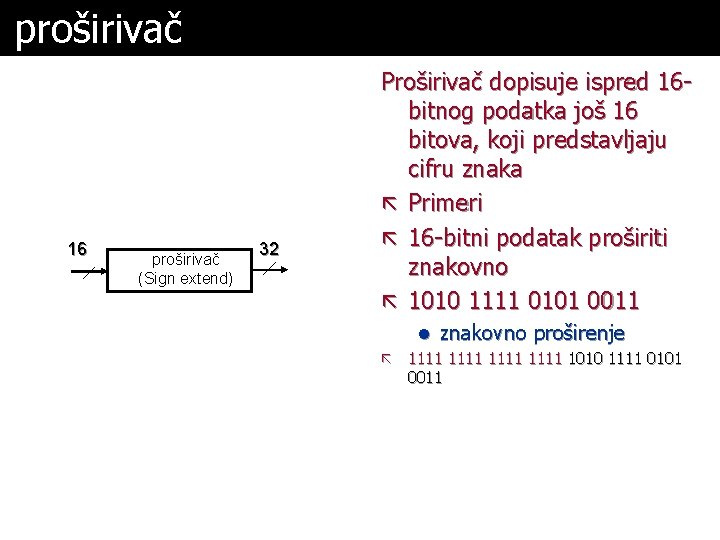

proširivač 16 proširivač (Sign extend) 32 Proširivač dopisuje ispred 16 bitnog podatka još 16 bitova, koji predstavljaju cifru znaka ã Primeri ã 16 -bitni podatak proširiti znakovno ã 1010 1111 0101 0011 l znakovno proširenje ã 1111 1010 1111 0101 0011

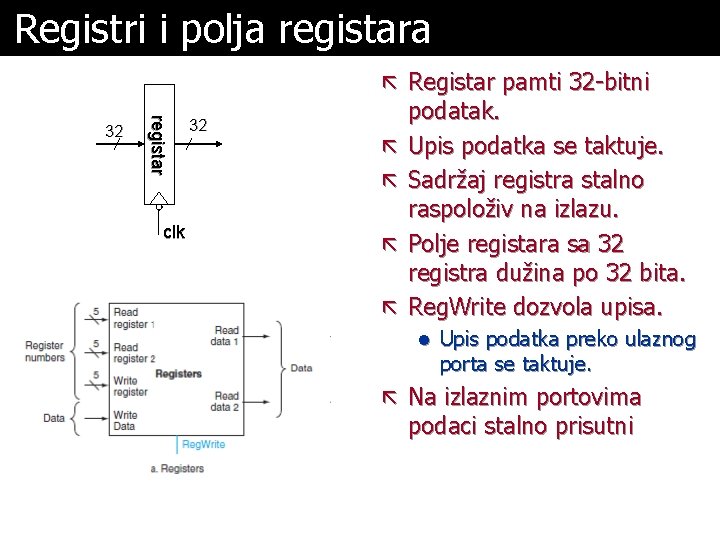

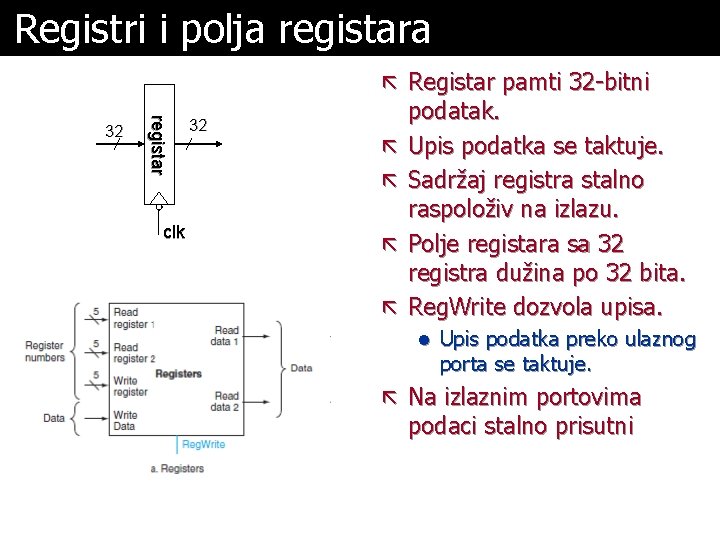

Registri i polja registara ã Registar pamti 32 -bitni registar 32 clk 32 ã ã podatak. Upis podatka se taktuje. Sadržaj registra stalno raspoloživ na izlazu. Polje registara sa 32 registra dužina po 32 bita. Reg. Write dozvola upisa. l Upis podatka preko ulaznog porta se taktuje. ã Na izlaznim portovima podaci stalno prisutni

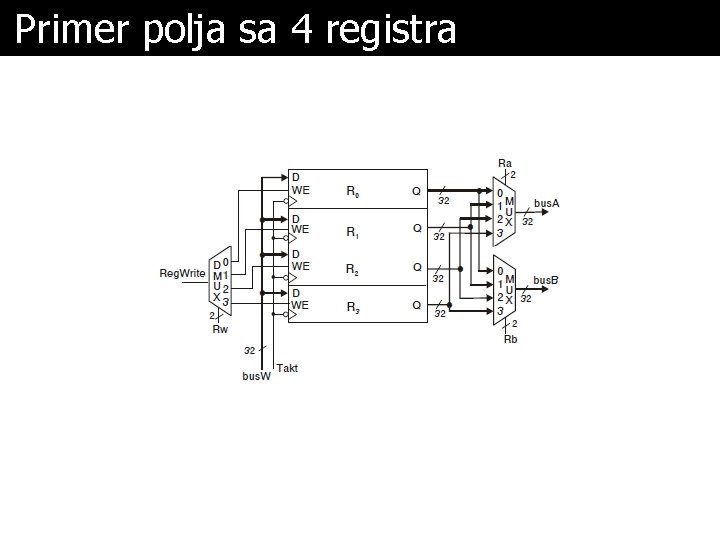

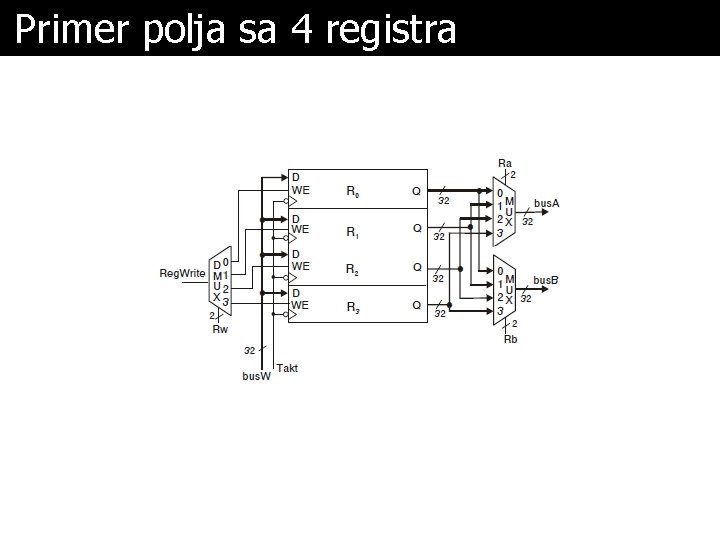

Primer polja sa 4 registra

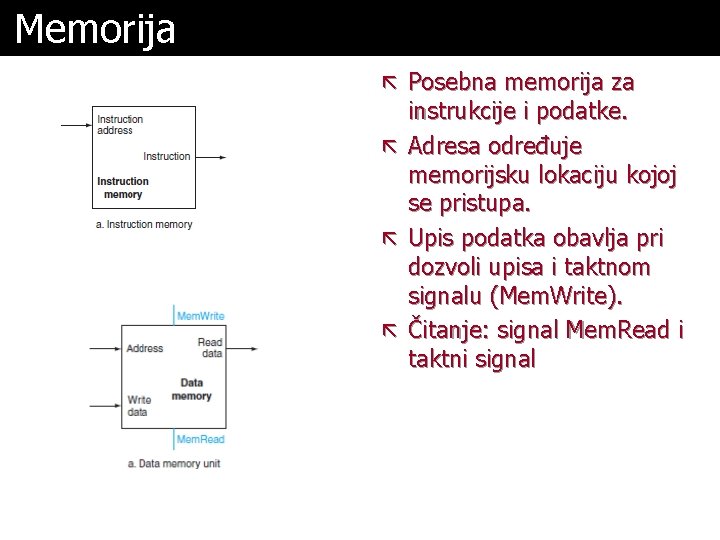

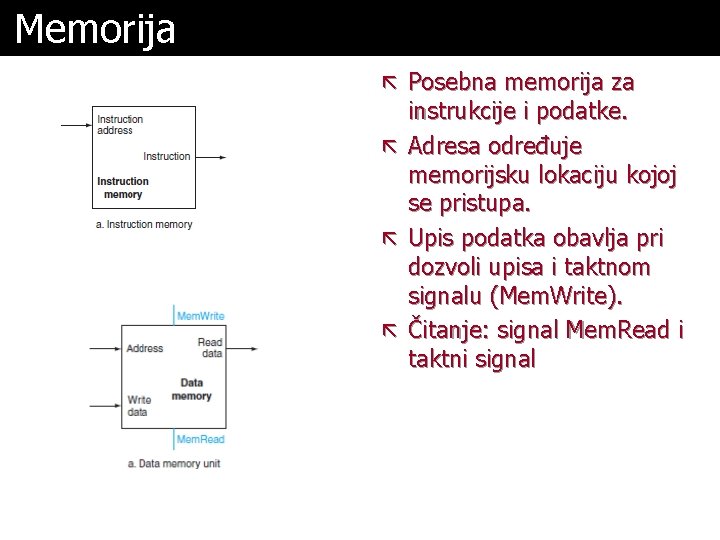

Memorija ã Posebna memorija za instrukcije i podatke. ã Adresa određuje memorijsku lokaciju kojoj se pristupa. ã Upis podatka obavlja pri dozvoli upisa i taktnom signalu (Mem. Write). ã Čitanje: signal Mem. Read i taktni signal

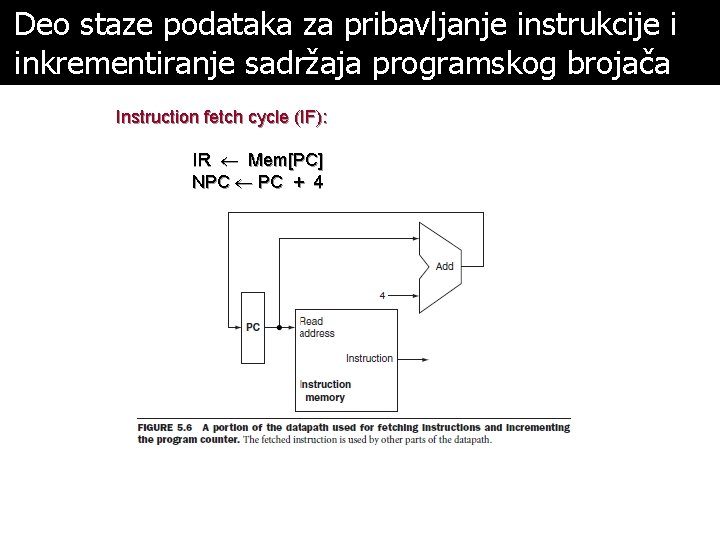

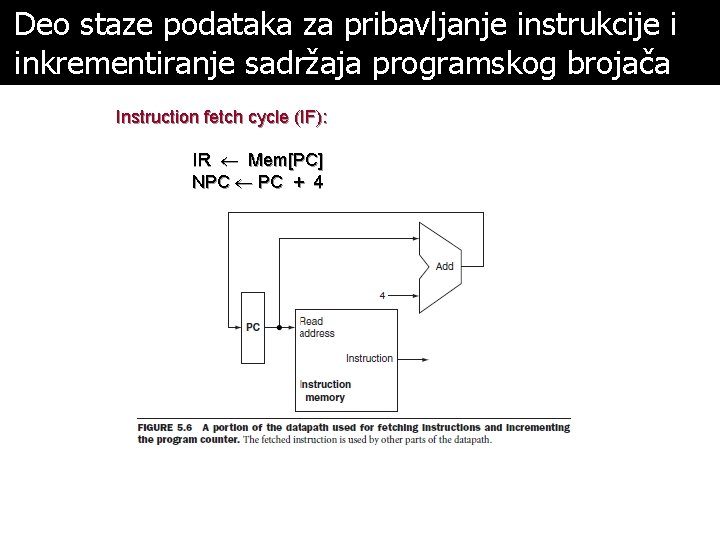

Deo staze podataka za pribavljanje instrukcije i inkrementiranje sadržaja programskog brojača Instruction fetch cycle (IF): IR Mem[PC] NPC PC + 4

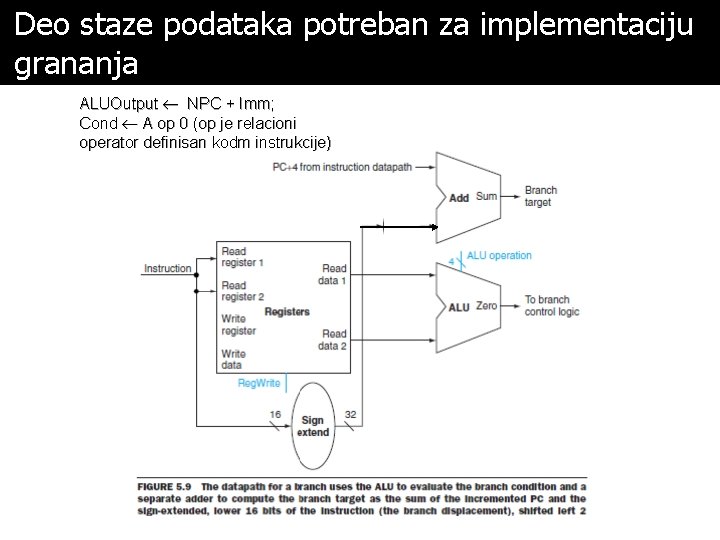

Deo staze podataka potreban za implementaciju grananja ALUOutput NPC + Imm; Cond A op 0 (op je relacioni operator definisan kodm instrukcije)

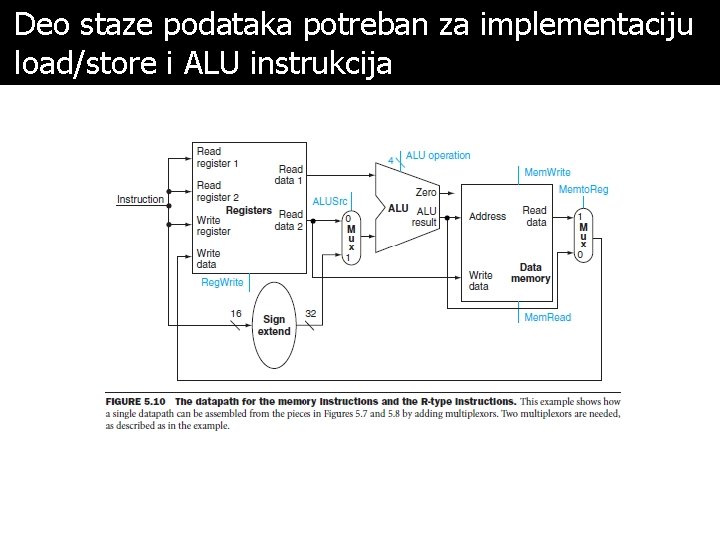

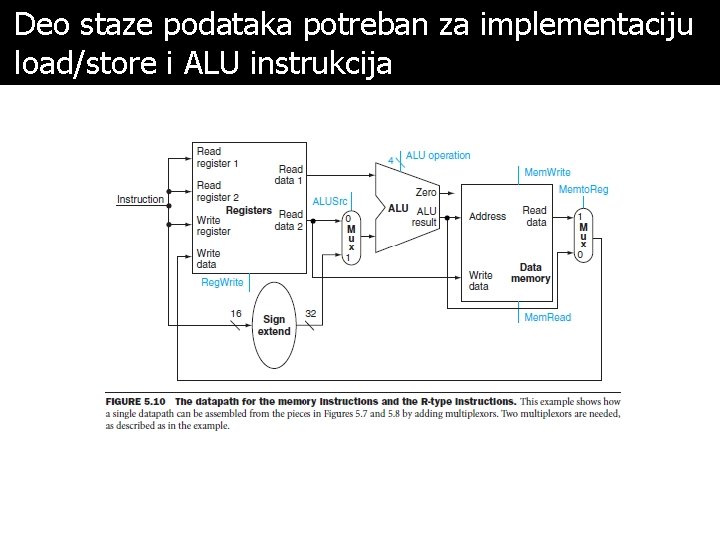

Deo staze podataka potreban za implementaciju load/store i ALU instrukcija

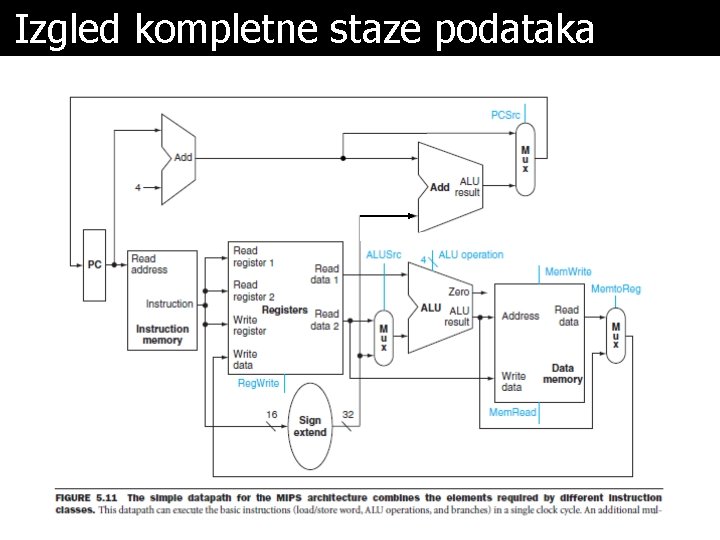

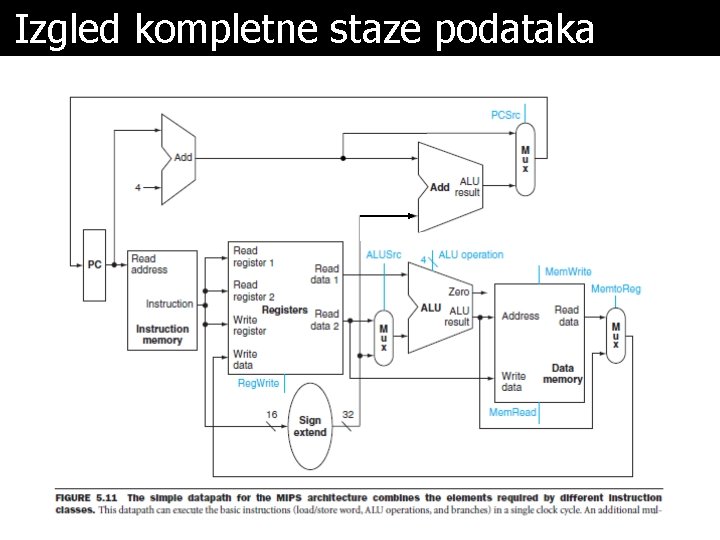

Izgled kompletne staze podataka

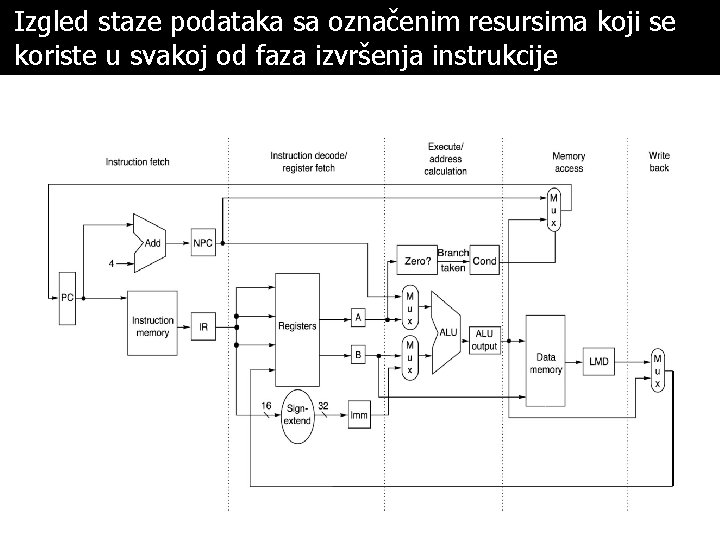

Izgled staze podataka sa označenim resursima koji se koriste u svakoj od faza izvršenja instrukcije

![0 5 6 10 11 15 16 20 16 31 21 31 [0 -5] [6 -10] [11 -15] [16 -20] [16 -31] [21 -31]](https://slidetodoc.com/presentation_image_h/f630e3408b816899834147519c869c30/image-30.jpg)

[0 -5] [6 -10] [11 -15] [16 -20] [16 -31] [21 -31]

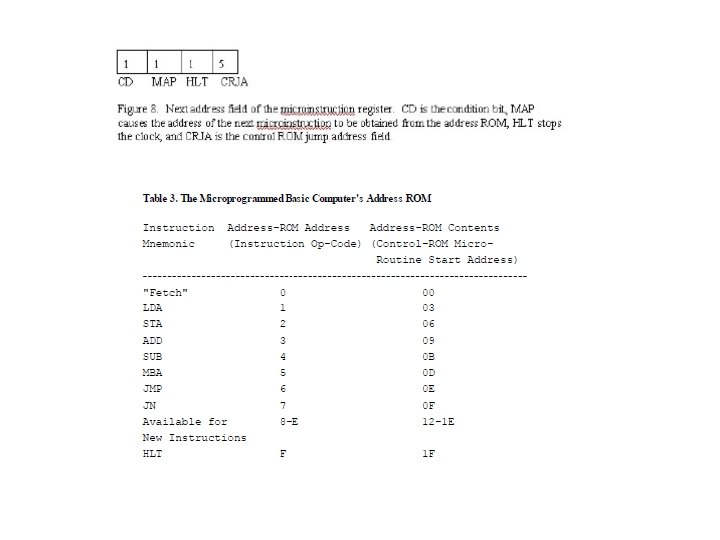

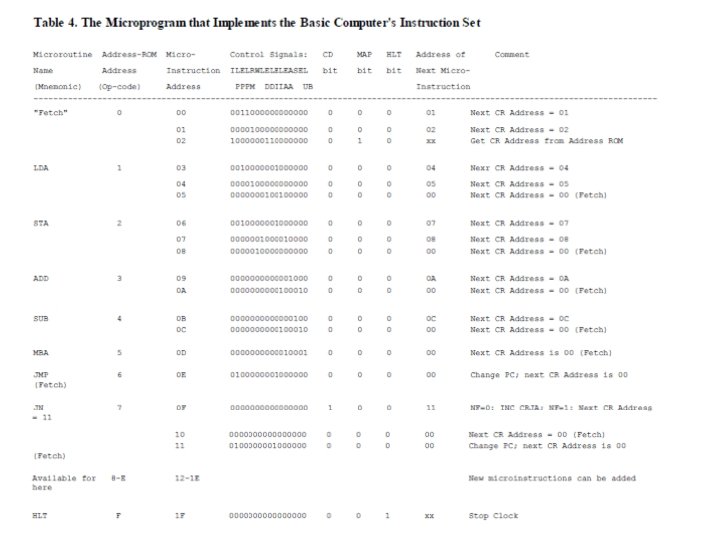

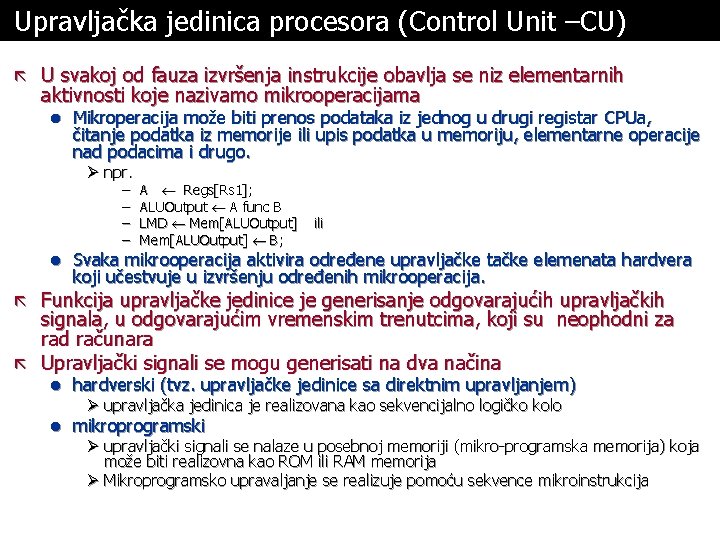

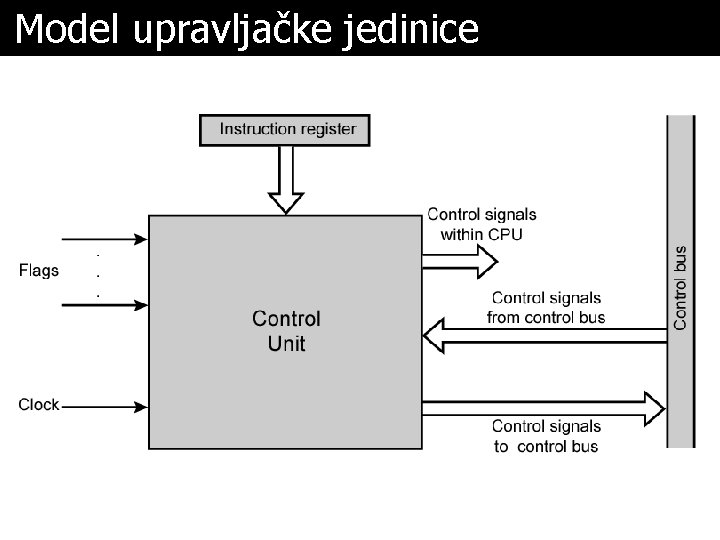

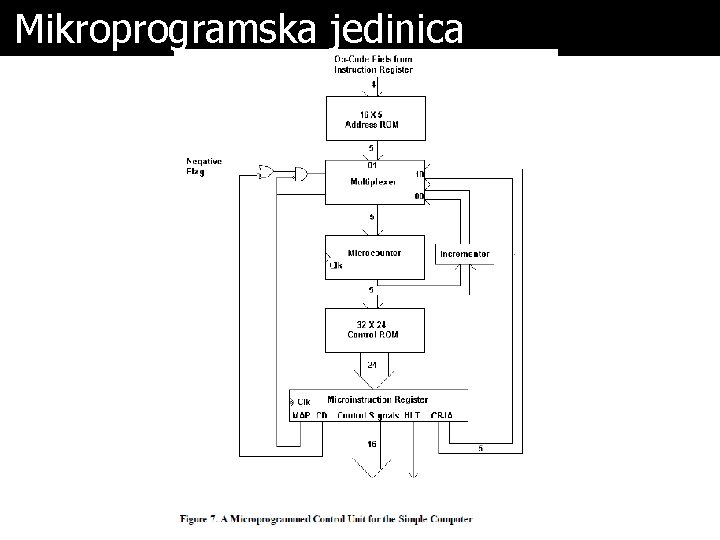

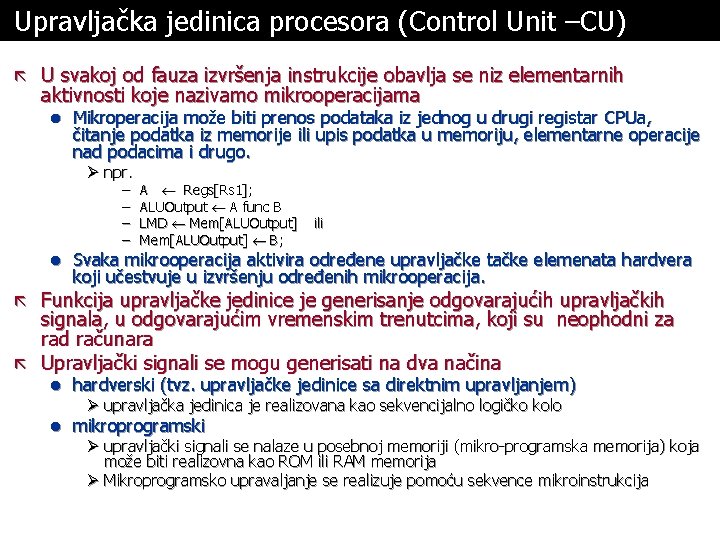

Upravljačka jedinica procesora (Control Unit –CU) ã U svakoj od fauza izvršenja instrukcije obavlja se niz elementarnih aktivnosti koje nazivamo mikrooperacijama l Mikroperacija može biti prenos podataka iz jednog u drugi registar CPUa, čitanje podatka iz memorije ili upis podatka u memoriju, elementarne operacije nad podacima i drugo. Ø npr. – – A Regs[Rs 1]; ALUOutput A func B LMD Mem[ALUOutput] B; ili l Svaka mikrooperacija aktivira određene upravljačke tačke elemenata hardvera koji učestvuje u izvršenju određenih mikrooperacija. ã Funkcija upravljačke jedinice je generisanje odgovarajućih upravljačkih signala, u odgovarajućim vremenskim trenutcima, koji su neophodni za rad računara ã Upravljački signali se mogu generisati na dva načina l hardverski (tvz. upravljačke jedinice sa direktnim upravljanjem) Ø upravljačka jedinica je realizovana kao sekvencijalno logičko kolo l mikroprogramski Ø upravljački signali se nalaze u posebnoj memoriji (mikro-programska memorija) koja može biti realizovna kao ROM ili RAM memorija Ø Mikroprogramsko upravaljanje se realizuje pomoću sekvence mikroinstrukcija

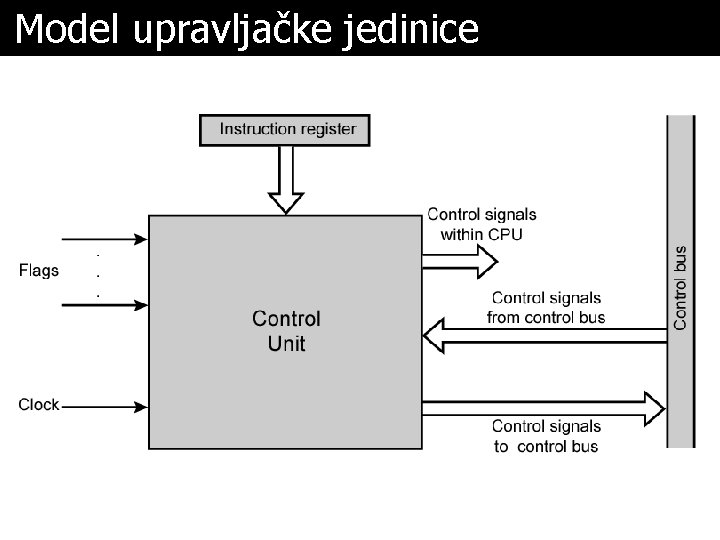

Model upravljačke jedinice

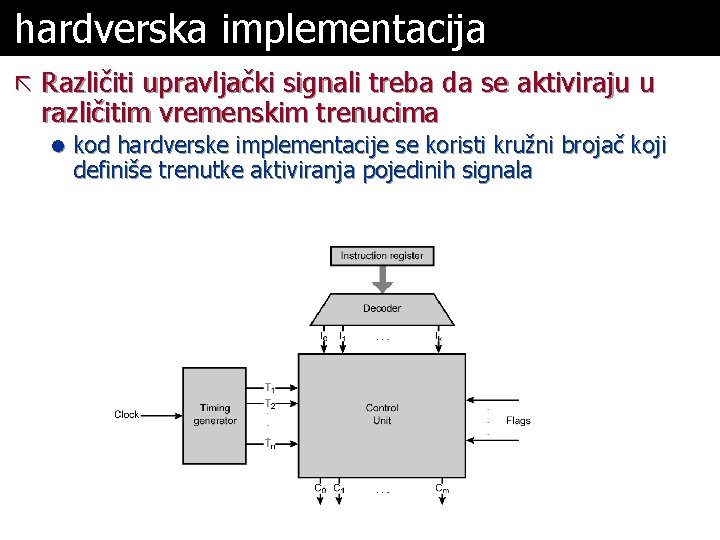

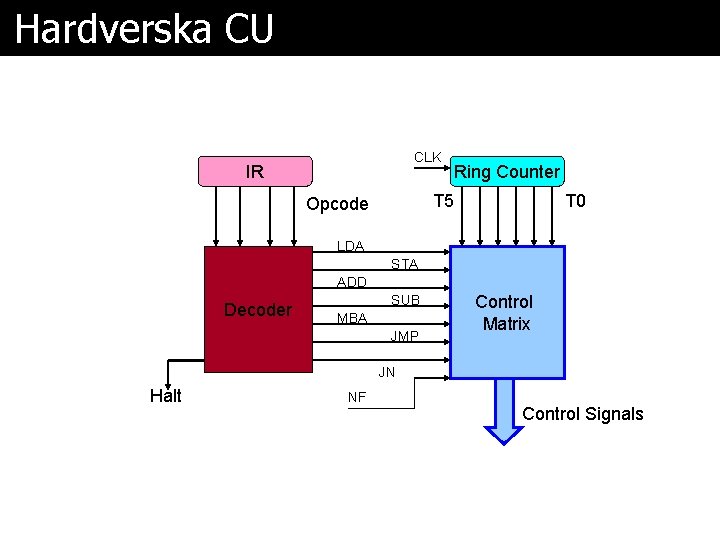

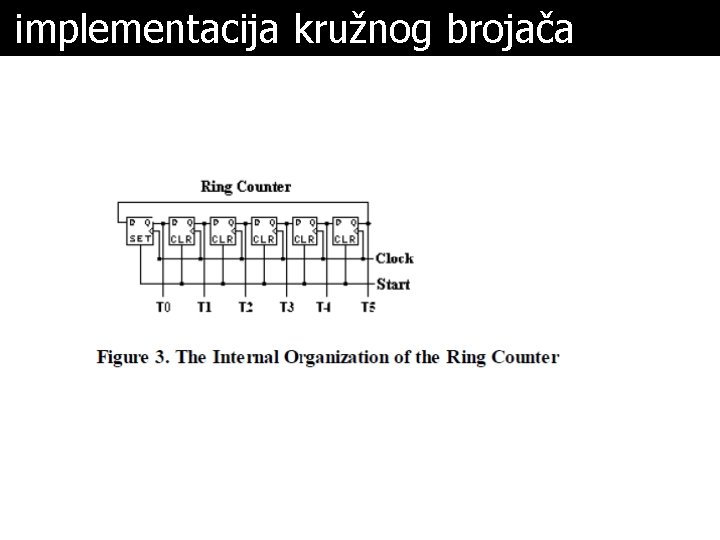

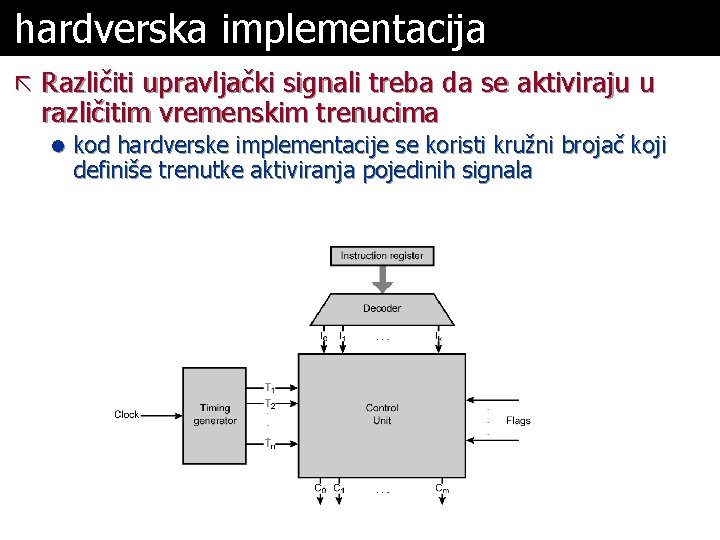

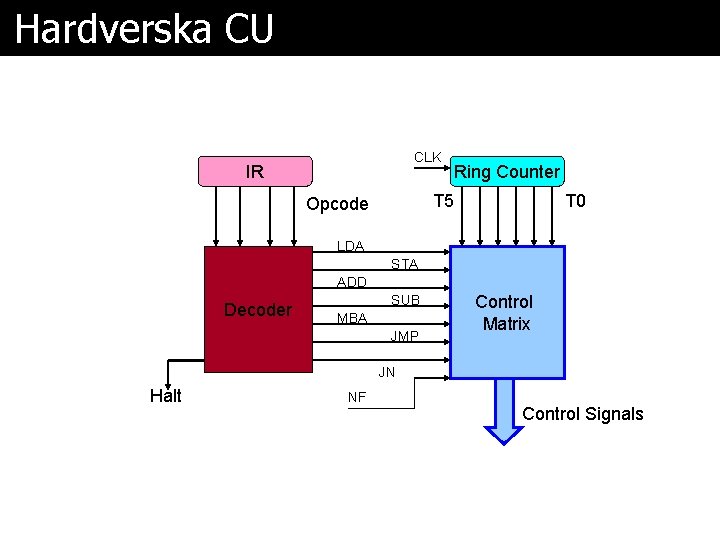

hardverska implementacija ã Različiti upravljački signali treba da se aktiviraju u različitim vremenskim trenucima l kod hardverske implementacije se koristi kružni brojač koji definiše trenutke aktiviranja pojedinih signala

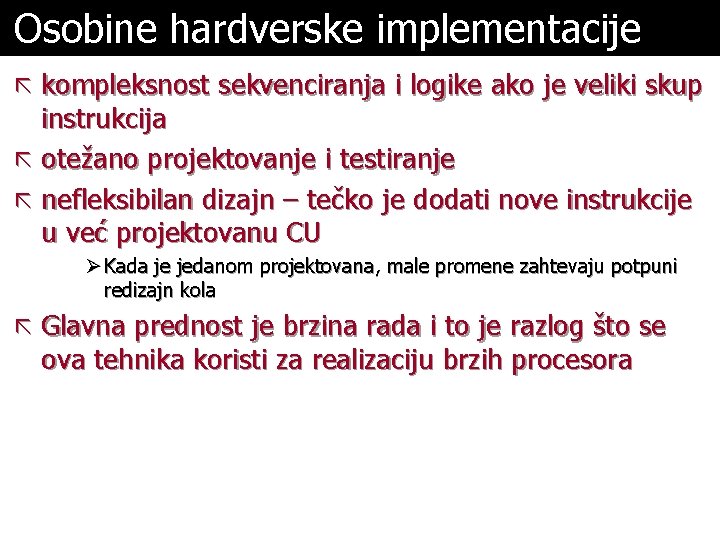

Osobine hardverske implementacije ã kompleksnost sekvenciranja i logike ako je veliki skup instrukcija ã otežano projektovanje i testiranje ã nefleksibilan dizajn – tečko je dodati nove instrukcije u već projektovanu CU Ø Kada je jedanom projektovana, male promene zahtevaju potpuni redizajn kola ã Glavna prednost je brzina rada i to je razlog što se ova tehnika koristi za realizaciju brzih procesora

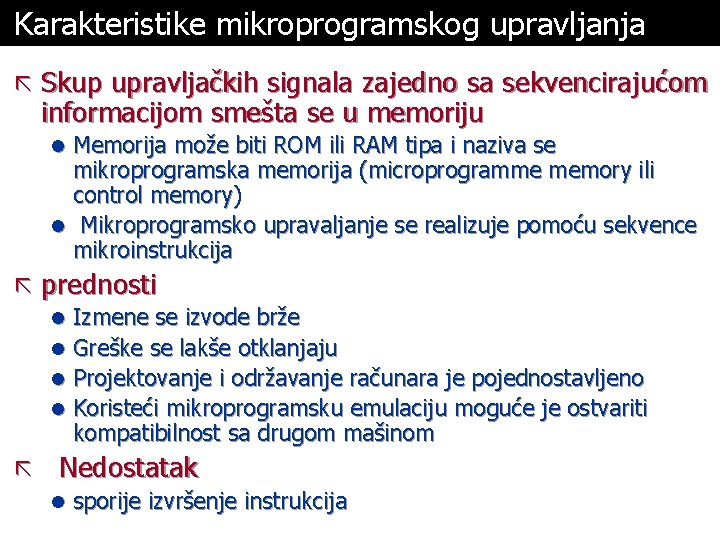

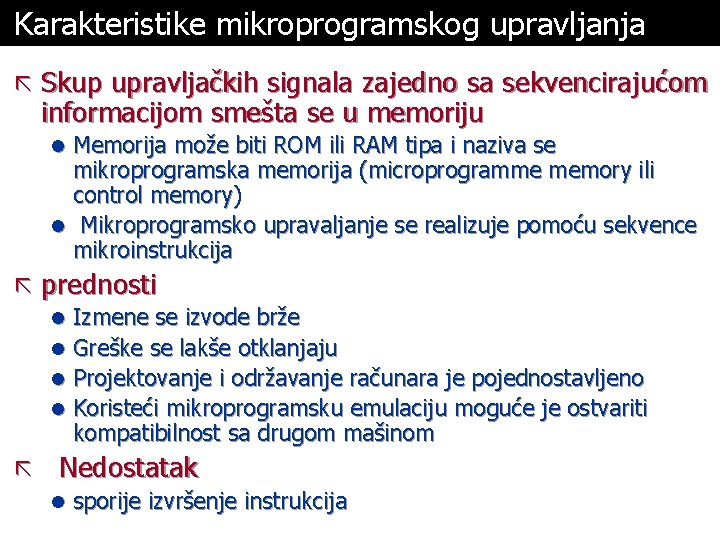

Karakteristike mikroprogramskog upravljanja ã Skup upravljačkih signala zajedno sa sekvencirajućom informacijom smešta se u memoriju l Memorija može biti ROM ili RAM tipa i naziva se mikroprogramska memorija (microprogramme memory ili control memory) l Mikroprogramsko upravaljanje se realizuje pomoću sekvence mikroinstrukcija ã prednosti l Izmene se izvode brže l Greške se lakše otklanjaju l Projektovanje i održavanje računara je pojednostavljeno l Koristeći mikroprogramsku emulaciju moguće je ostvariti kompatibilnost sa drugom mašinom ã Nedostatak l sporije izvršenje instrukcija

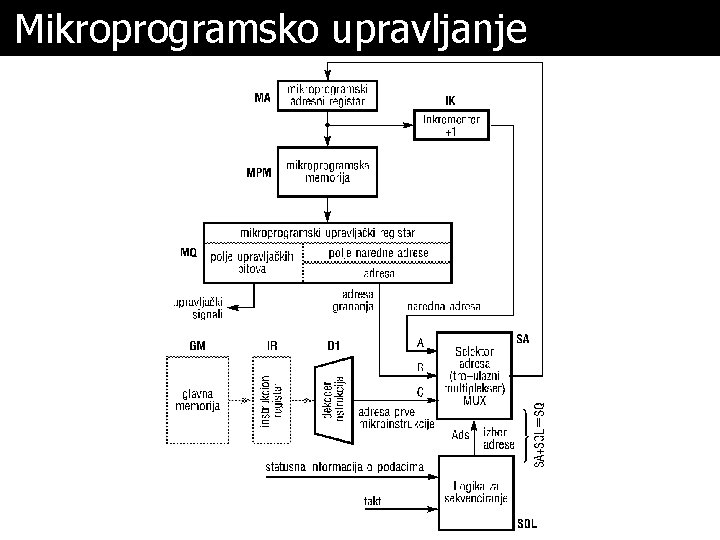

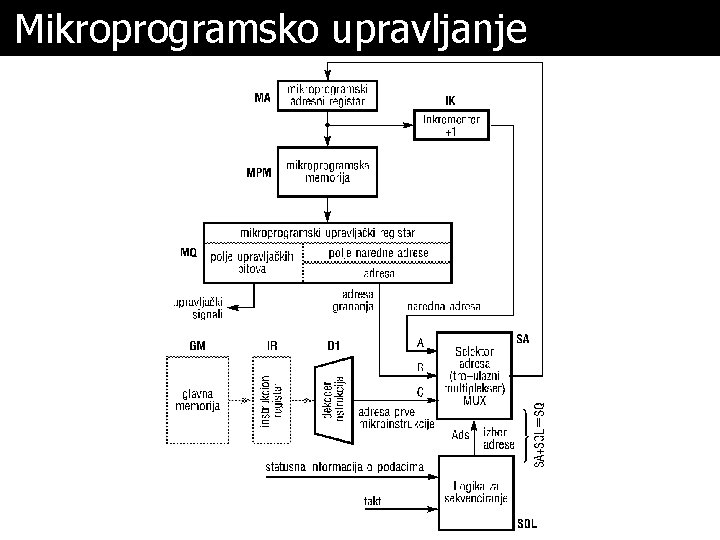

Mikroprogramsko upravljanje

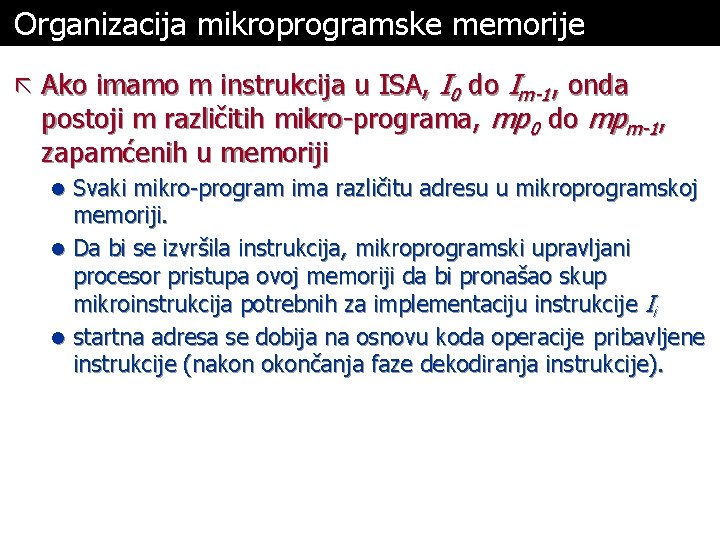

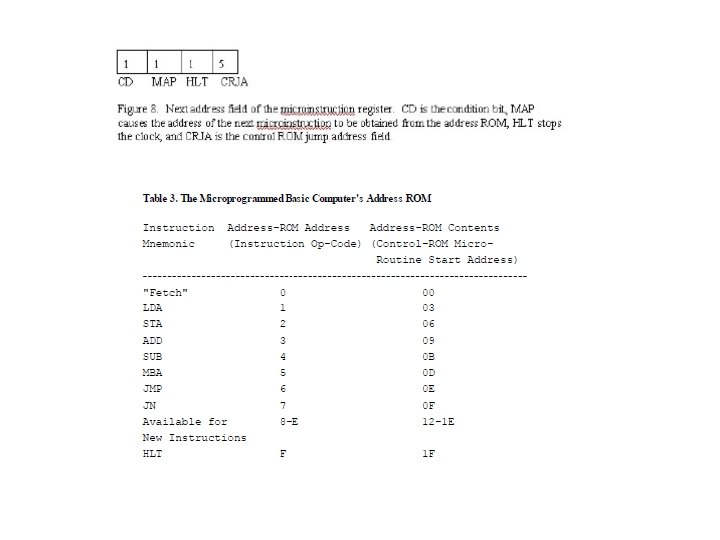

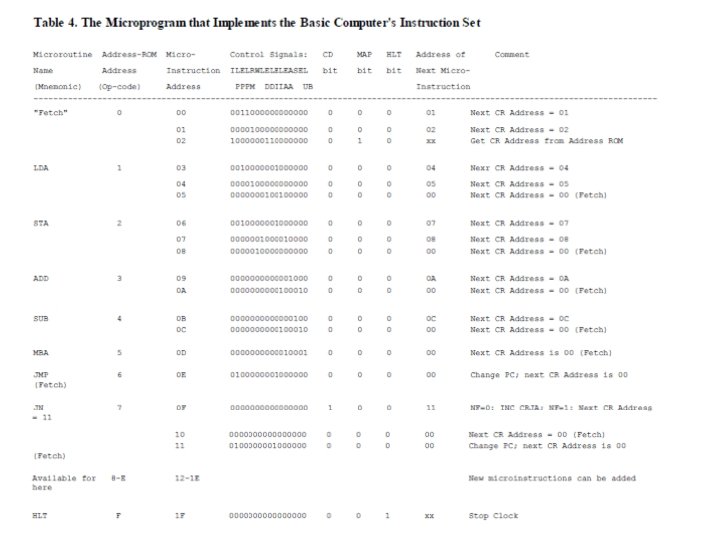

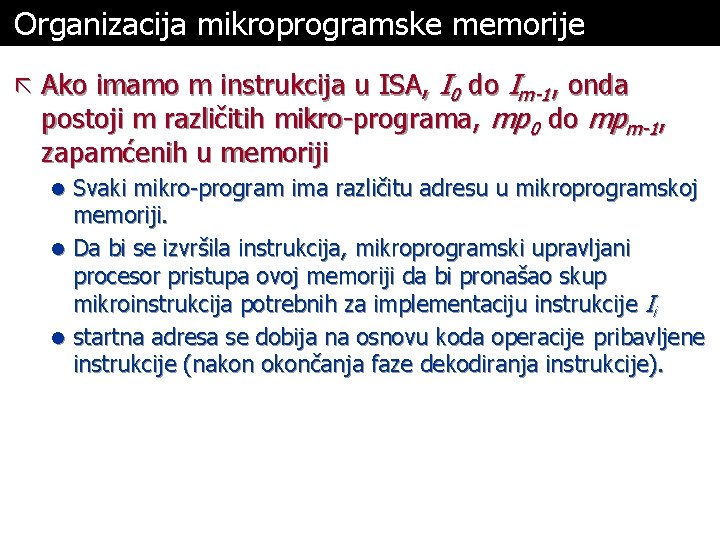

Organizacija mikroprogramske memorije ã Ako imamo m instrukcija u ISA, I 0 do Im-1, onda postoji m različitih mikro-programa, mp 0 do mpm-1, zapamćenih u memoriji l Svaki mikro-program ima različitu adresu u mikroprogramskoj memoriji. l Da bi se izvršila instrukcija, mikroprogramski upravljani procesor pristupa ovoj memoriji da bi pronašao skup mikroinstrukcija potrebnih za implementaciju instrukcije Ii l startna adresa se dobija na osnovu koda operacije pribavljene instrukcije (nakon okončanja faze dekodiranja instrukcije).

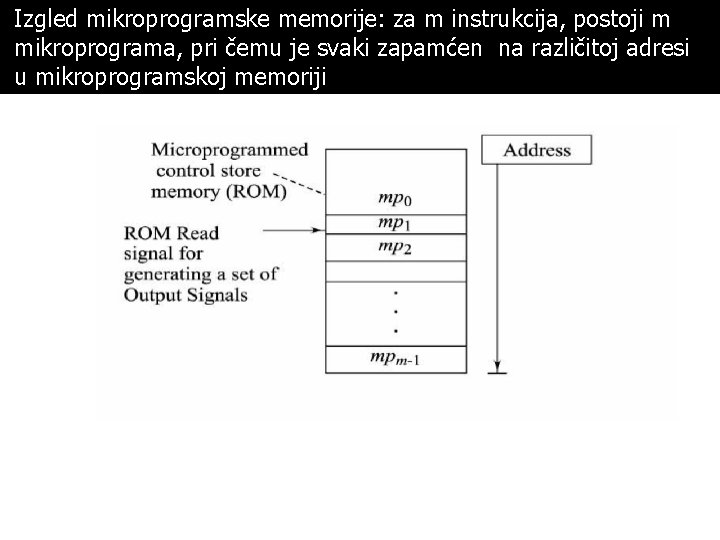

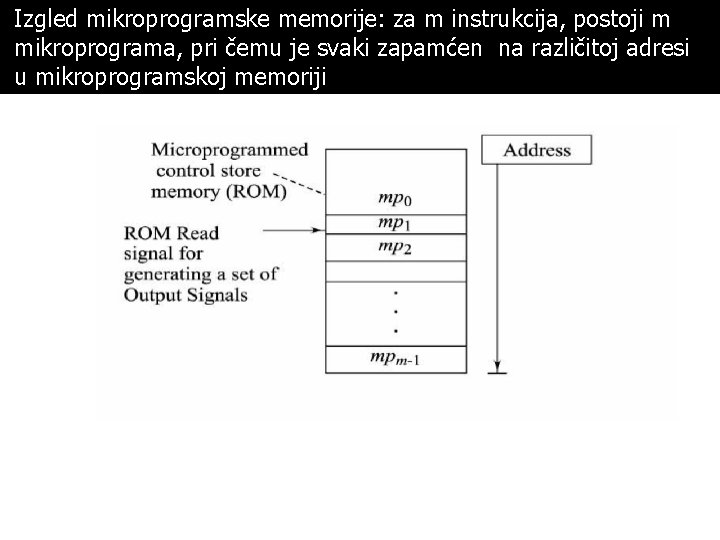

Izgled mikroprogramske memorije: za m instrukcija, postoji m mikroprograma, pri čemu je svaki zapamćen na različitoj adresi u mikroprogramskoj memoriji

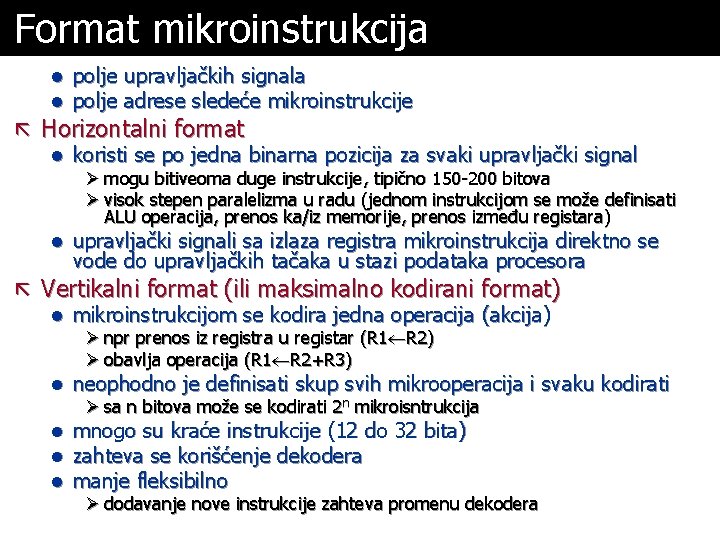

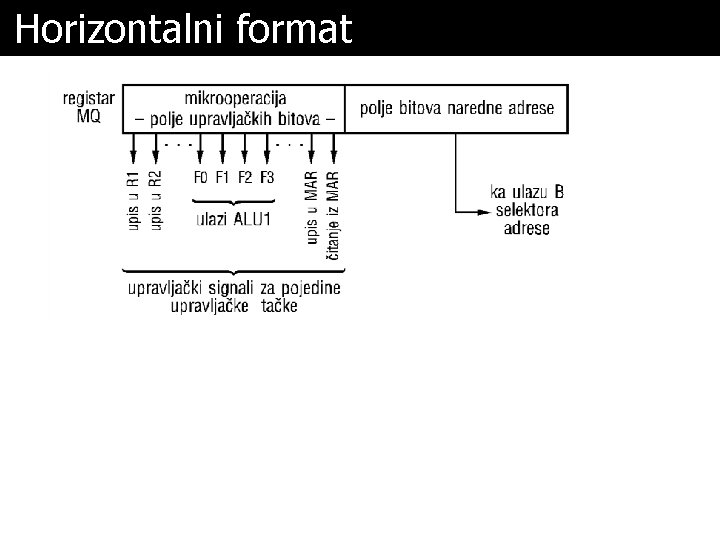

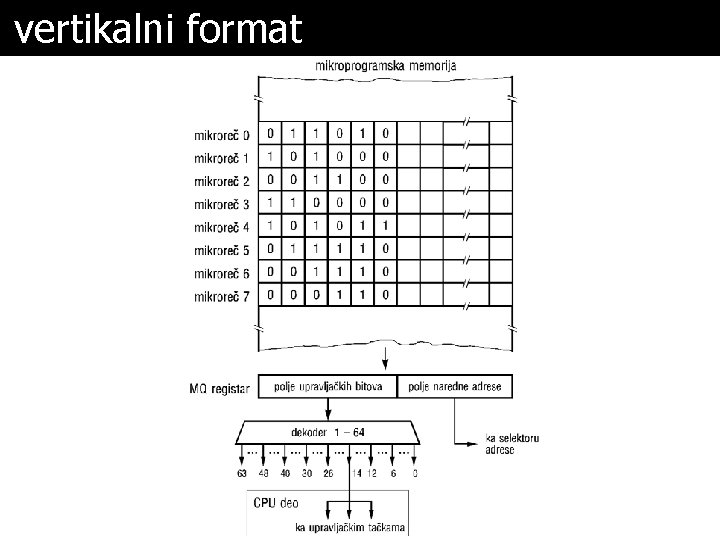

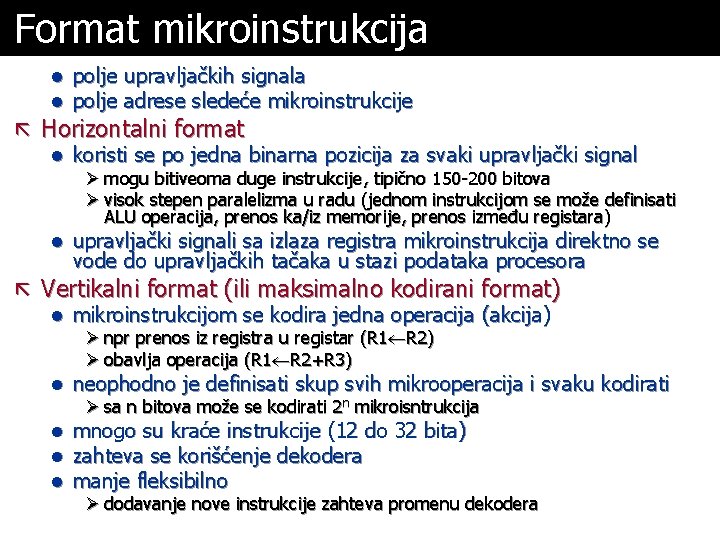

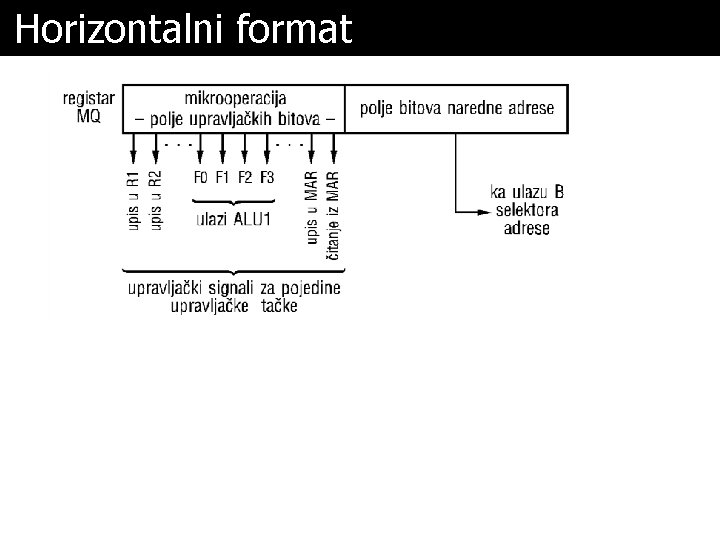

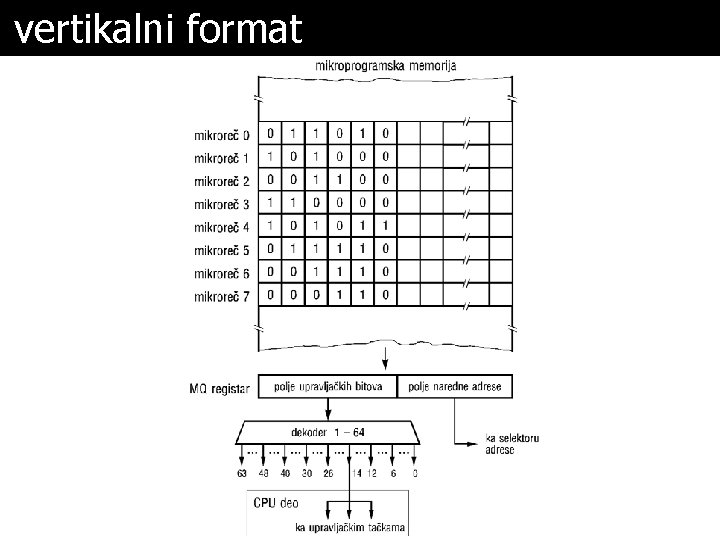

Format mikroinstrukcija l polje upravljačkih signala l polje adrese sledeće mikroinstrukcije ã Horizontalni format l koristi se po jedna binarna pozicija za svaki upravljački signal Ø mogu bitiveoma duge instrukcije, tipično 150 -200 bitova Ø visok stepen paralelizma u radu (jednom instrukcijom se može definisati ALU operacija, prenos ka/iz memorije, prenos između registara) l upravljački signali sa izlaza registra mikroinstrukcija direktno se vode do upravljačkih tačaka u stazi podataka procesora ã Vertikalni format (ili maksimalno kodirani format) l mikroinstrukcijom se kodira jedna operacija (akcija) Ø npr prenos iz registra u registar (R 1 R 2) Ø obavlja operacija (R 1 R 2+R 3) l neophodno je definisati skup svih mikrooperacija i svaku kodirati Ø sa n bitova može se kodirati 2 n mikroisntrukcija l mnogo su kraće instrukcije (12 do 32 bita) l zahteva se korišćenje dekodera l manje fleksibilno Ø dodavanje nove instrukcije zahteva promenu dekodera

Horizontalni format

vertikalni format

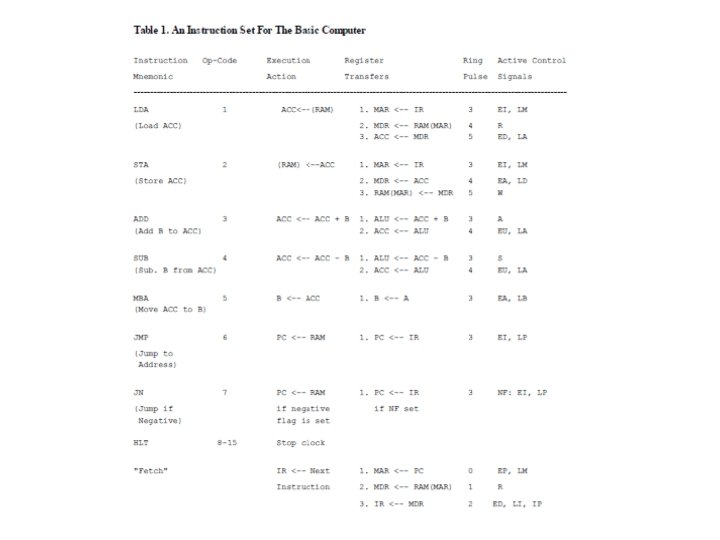

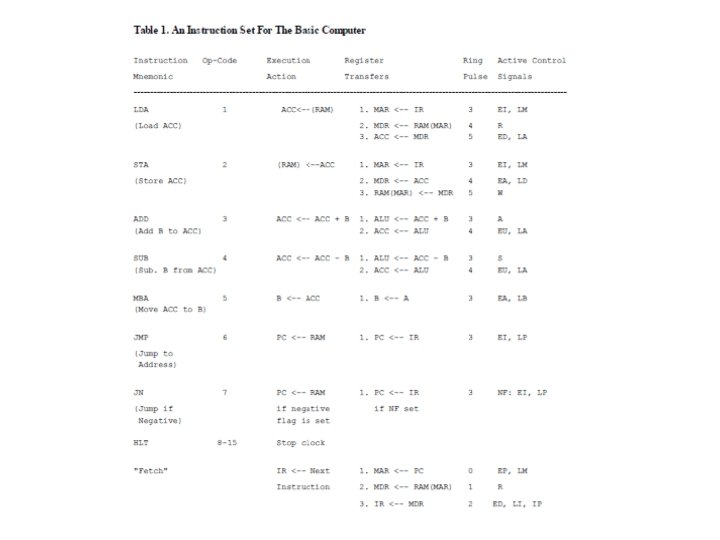

Jednostavni primer projektovanja CU - hardverska CU - mikroprogramska CU

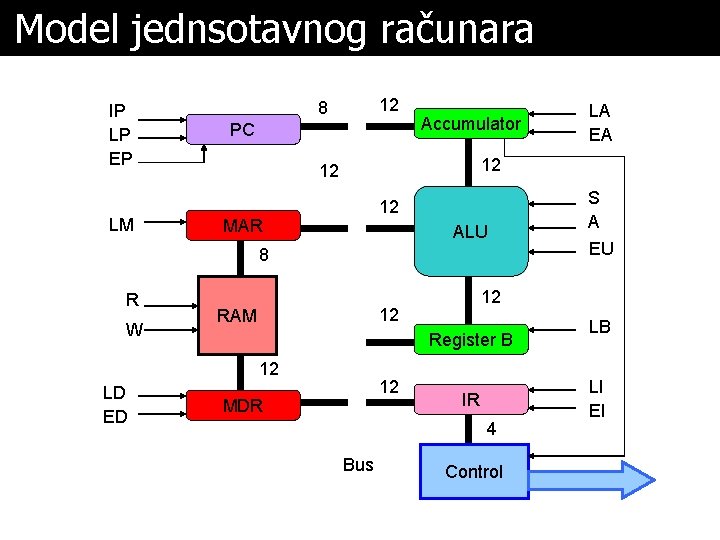

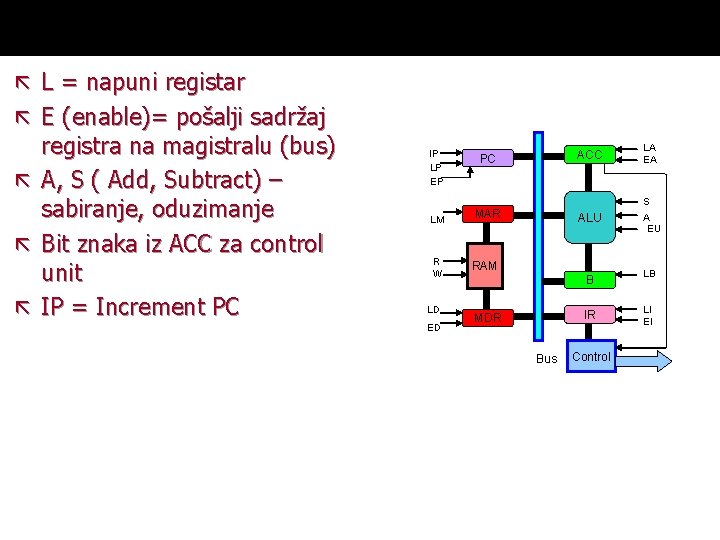

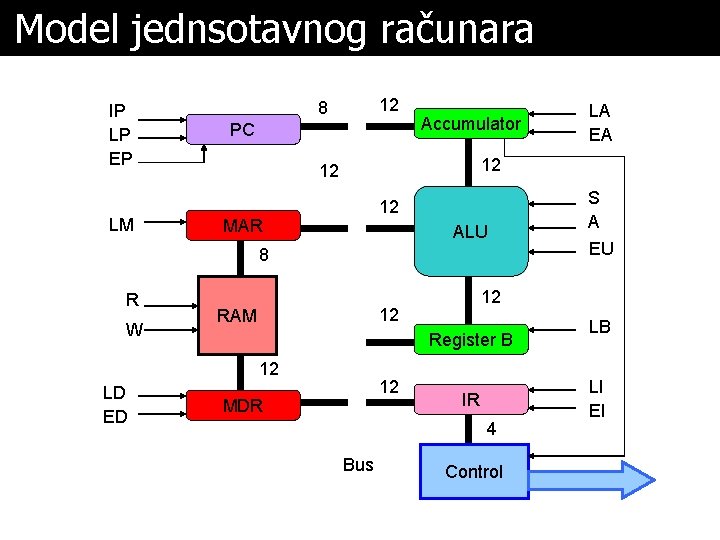

Model jednsotavnog računara IP LP EP LM 12 8 PC Accumulator 12 12 12 MAR ALU 8 R W Register B 12 MDR IR 4 Bus S A EU 12 12 RAM 12 LD ED LA EA Control LB LI EI

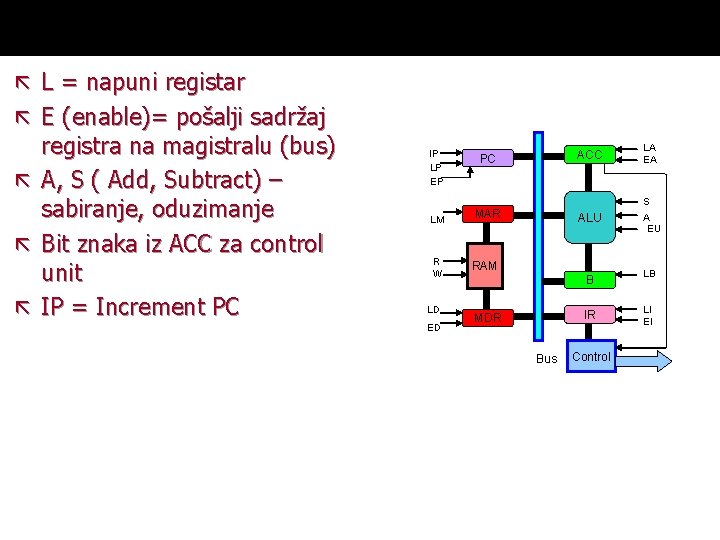

ã L = napuni registar ã E (enable)= pošalji sadržaj ã ã ã registra na magistralu (bus) A, S ( Add, Subtract) – sabiranje, oduzimanje Bit znaka iz ACC za control unit IP = Increment PC IP LP EP LM R W LD ED ACC PC LA EA S MAR ALU RAM B IR MDR Bus Control A EU LB LI EI

Hardverska CU CLK IR Ring Counter T 5 Opcode T 0 LDA STA ADD Decoder SUB MBA JMP Control Matrix JN Halt NF Control Signals

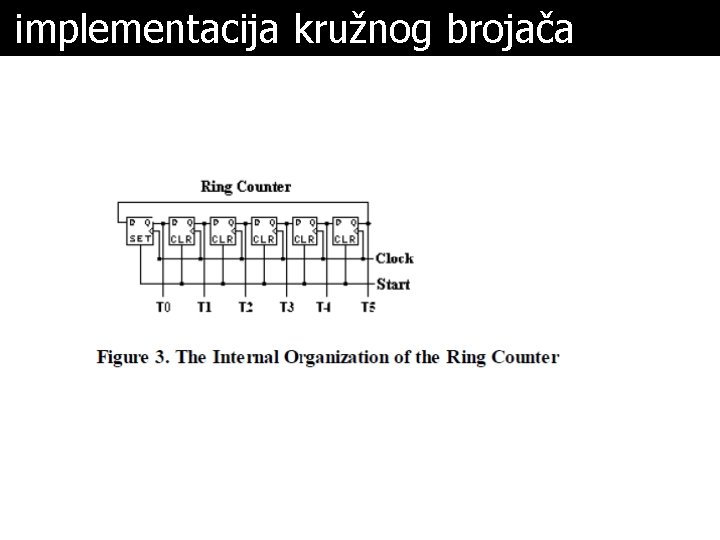

implementacija kružnog brojača

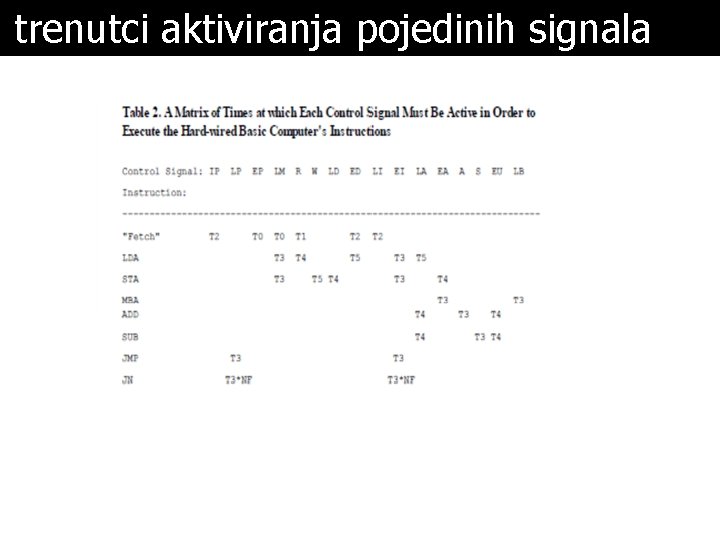

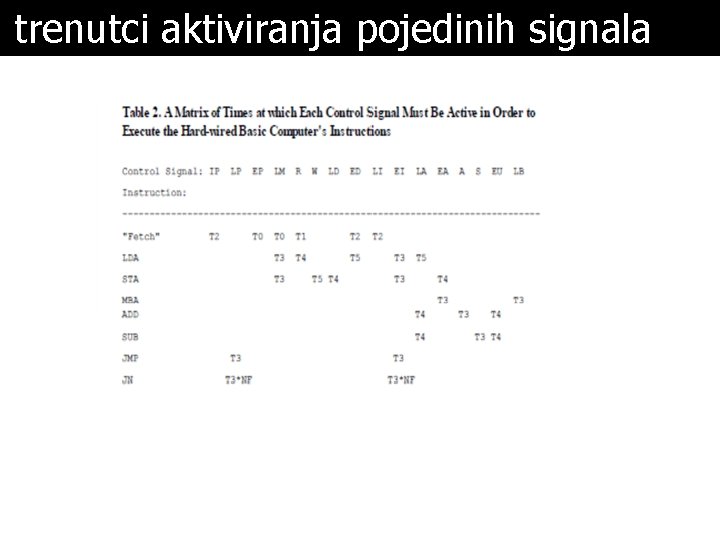

trenutci aktiviranja pojedinih signala

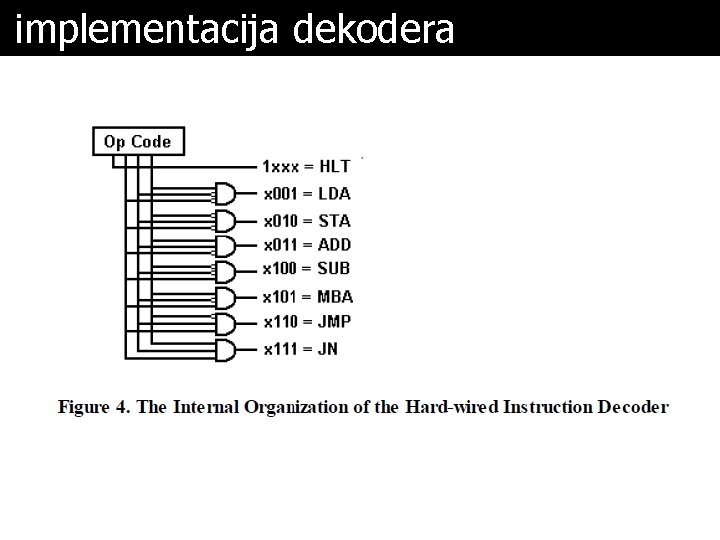

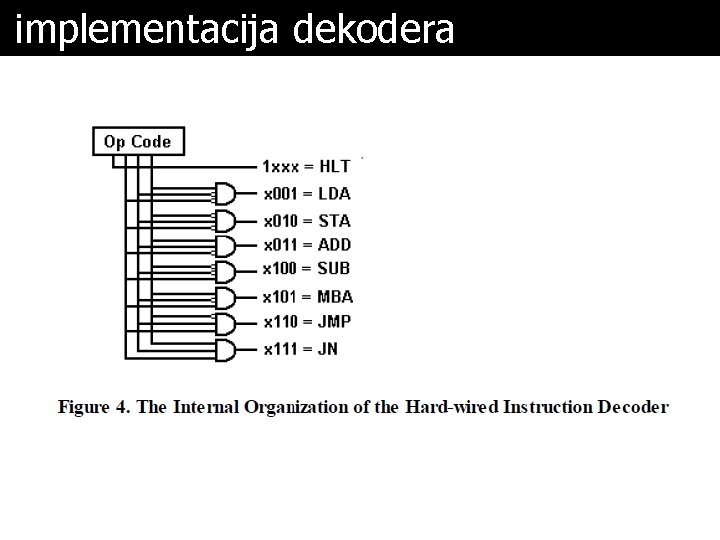

implementacija dekodera

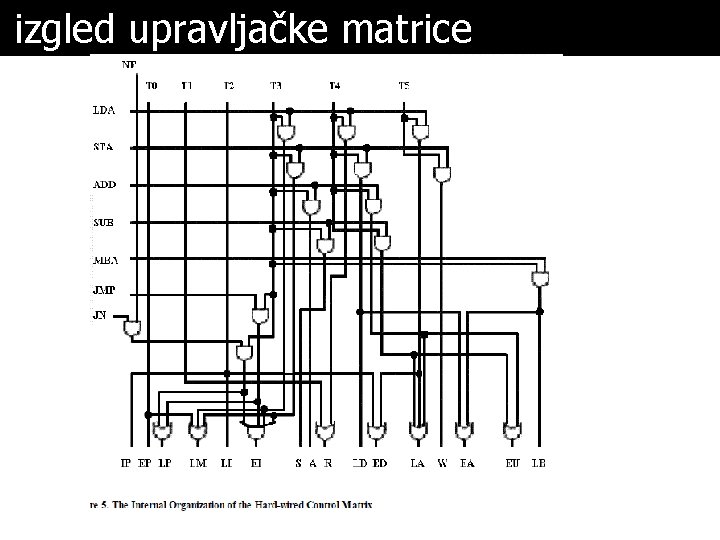

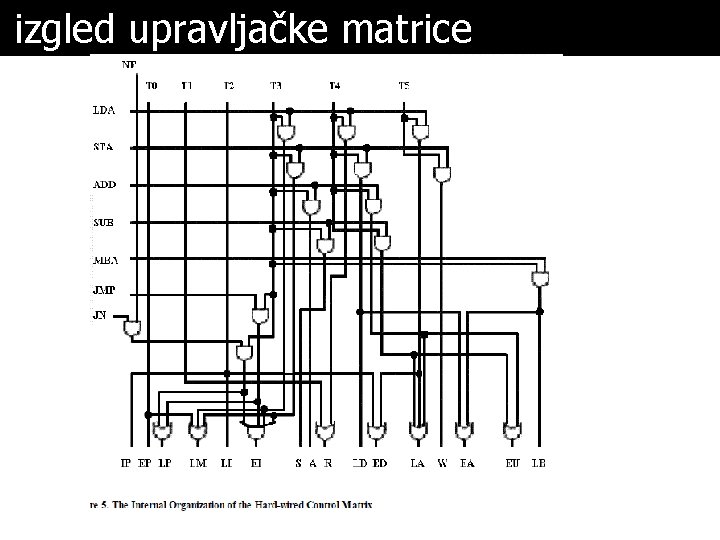

izgled upravljačke matrice

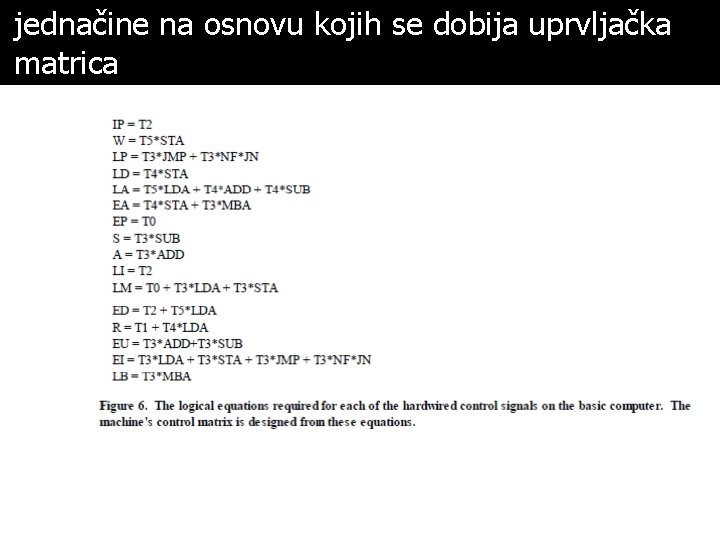

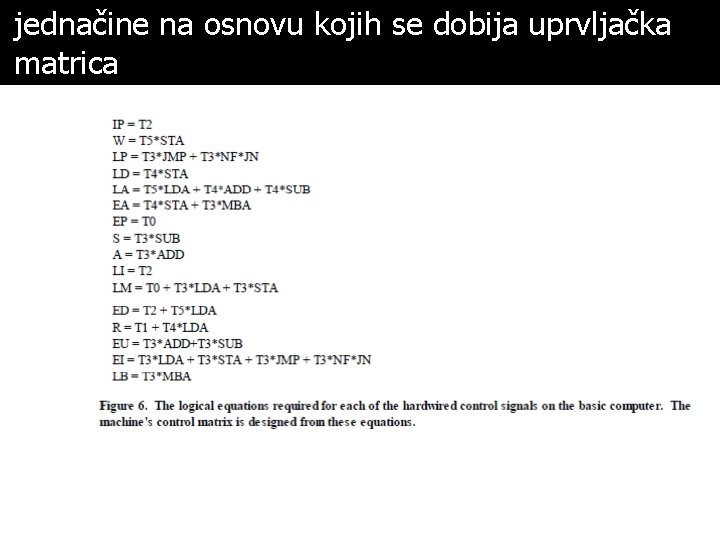

jednačine na osnovu kojih se dobija uprvljačka matrica

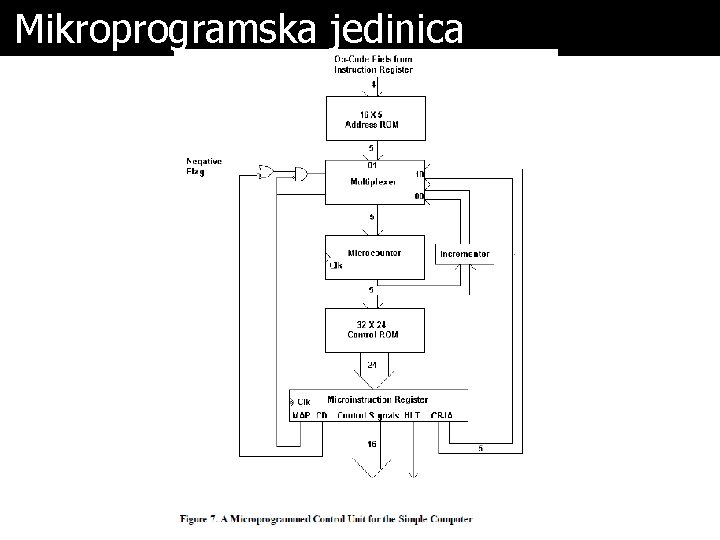

Mikroprogramska jedinica