Programovateln logick pole Pokud chceme realizovat urit funkce

- Slides: 97

Programovatelná logická pole

Pokud chceme realizovat určité funkce, pak se vždy jedná o nějakou předem specifikovanou součást či součásti, které jsou již nějakým způsobem definované. Těchto součástí je nepřeberná řada počínaje jednoduchými hradly a konče procesory. Všechny součásti včetně procesorů však mají zcela definovány vstupy a výstupy, většinou však jinak než potřebujeme. Toto je však jen jeden z pohledů na problematiku. Další pohledy jsou například cena, rozměr, stupeň integrace, spolehlivost, spotřeba atd. Při tom řada požadavků si často odporuje. Celá řada složitějších číslicových systémů je realizována obvody LSI, které však potřebují pro svou činnost celou řadu dalších pomocných obvodů.

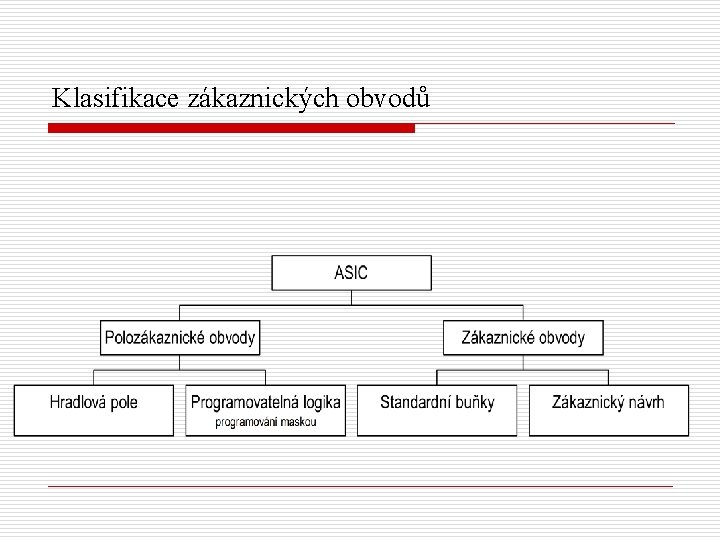

Alternativou k takovýmto řešením jsou zákaznické obvody z nichž je možno realizovat požadovaný obvod bez dalších pomocných obvodů. Do této kategorie se zařazují i hradlová pole a programovatelné obvody. Tyto obvody jsou založeny buď na standardních buňkách nebo čistě zákaznických obvodech.

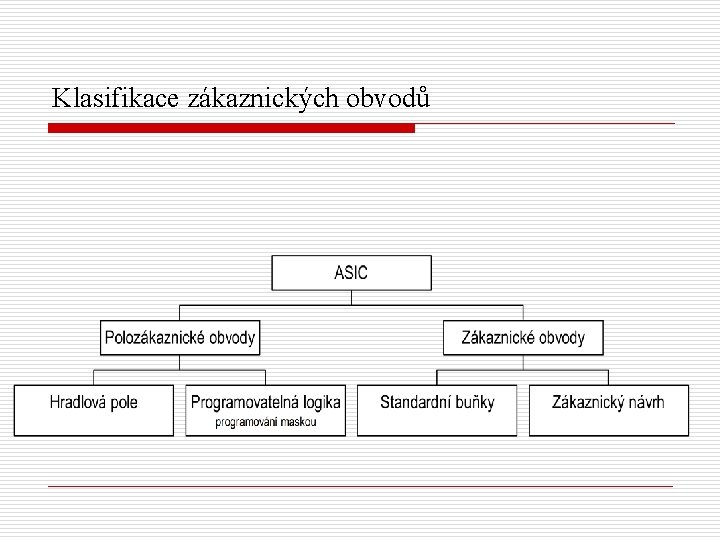

Klasifikace zákaznických obvodů

Výhodou číslicových zákaznických obvodů je : o snadná modifikace systému bez požadavku na změnu desky, případně i již zapájené obvody o vyšší spolehlivost vyplývající ze zmenšení počtu použitých integrovaných obvodů o vyšší výkonnost daná vyšší rychlostí systému a nižší spotřebou o nižší cena systému vyplývající z použití hromadně vyráběných obvodů LSI a VLSI, čímž dochází k podstatnému snížení ceny jak prvků, tak i zmenšení velikosti plošných spojů a zjednodušení návrhu

Návrhy založené na plně zákaznických obvodech se nehodí pro kusovou či malosériovou výrobu, protože příprava vyžaduje složité a drahé vývojové prostředí.

Nástup programovatelných obvodů začal měnit pozici návrháře, jeho zvyky, přístupy a kritéria při volbě kompromisních stavebních dílů. Tyto programovatelné obvody se nazývají PLD (Programmable Logic Device). Programovatelná logická pole byla vyvinuta s cílem poskytnout vývojářům pracujícím s číslicovou technikou prostředky pro realizaci jednodušších či až středně náročných obvodů. Má umožnit modifikovatelnost návrhů, volbu jak vstupů, tak i výstupů a to vše za přijatelnou cenu i při kusové nebo malosériové výrobě. Je to vlastně oblast ležící mezi základními obvody a procesory.

Oproti zákaznickým obvodům návrhy systémů s PLD lze realizovat na relativně levných prostředcích jak technických, tak i programových.

Základní používané pojmy a názvosloví Nejprve je třeba uvést zkratky a pojmy, protože názvosloví je zatím ještě neustálené a Vám neznámé. . Jako základní pojmy se používají následující zkratky : ASIC (Application Specific Integrated Circuits) – jedná se název zákaznických obvodů PLA (Programmable Logic Arrays) – programovatelná logická pole (též dřívější označení součástí PLD) PLD (Programmable Logic Device) – programovatelné logické součásti, kde výsledná funkce číslicového obvodu je naprogramována přímo uživatelem

Pin – vývod ze součásti. Obecně signálový nebo napájecí kontakt LCE (Logic Control Element) – matice programovatelných propojovacích spínačů umožňující propojení různých části celého obvodu Macro. Cell – makrobuňka PAL (Programmable Array Logic) – jedná se označení obvodů PLD s programovatelným polem hradel AND a pevným polem hradel OR FPLA (Field Programmable Logic Array) – jedná se o programovatelné pole hradel AND a současně programovatelné pole hradel OR

FPLS (Field Programmable Logic Sequencer) – přidáním klopných obvodů k FPLA vznikne FPLS, takže s tímto obvodem lze realizovat i složité stavové automaty EPLD (Erasable Programmable Logic Device) – je označení obvodů PLD, které jsou přeprogramovatelné a u nichž se mazání provádí UV zářením. JEDEC – jedná se o výbor Join Electron Device Engineering Counsil GAL (Generic Array Logic) – obvody s možností mazání elektrickým signálem

IOB (Input Output Block) – programovatelné vstupní a výstupní bloky CLB (Cofigurable Logic Blocks) – přeprogramovatelné logické buňky LCA (Logic Cell Array) – jedná se firemní označení pro architekturu FPGA OPAL (Open Programmable Architecture Language) – otevřený jazyk programovatelné architektury

MAPL (Multiple Array Programmable Logic) – jedná se vícenásobná programovatelná logická pole obsahující jak již název napovídá několik programovatelných logických polí u nichž lze vstupy a výstupy vzájemně propojovat včetně vstupů celého obvodu FPGA (Field Programmable Gate Array) - obvody nahrazující standardní vícevstupová hradla. Obsahují programovatelná hradel AND s výstupy majícími programovatelnou polaritu (např. AND/NAND)

ACB (Architecture Control Block) – blok určený pro řízení architektury PI (Programmable Interconnect) – přeprogramovatelné spojovací trasy MACH (Macro Array CMOS High-density) –tyto obvody obsahují několik nezávislých bloků PAL vzájemně propojených spojovacím polem

Konečné automaty Každý číslicový systém lze popsat prostřednictvím vstupů, výstupů a přenosové funkce. Přes vstupy do systému přichází nezávislé logické proměnné x 1, x 2, x 3, …, xn jako vstupní signály. Jejich zpracování se definuje přenosovou funkcí F. Výstupní signály y 1, y 2, y 3, …. , yn jsou generovány jako závisle proměnné v závislosti na vstupních proměnných a přenosové funkci. Jedná se vždy o konečný počet jak vstupních, tak i výstupních proměnných. Soubor hodnot na vstupu se označuje jako vstupní stav systému a soubor hodnot na výstupu jako výstupní stav systému.

Počet všech možných vstupních stavů číslicového systému se nazývá abeceda systému. Pro logické operace platí vše co bylo probráno ve všech předchozích kapitolách. Jen je zde nutné připomenout, že funkce může být zapsána ve dvou tvarech : o úplná součtová normální forma o úplná součinová normální forma

Základní součtový tvar je součet základních součinů (mintermů) a to jak přímých, tak i negovaných. f = x. y. z + x. y. z + x. y. z Poznámka Obrácené lomítko za proměnnou (např. x) znamená negaci.

Pokud se jedná o kombinační obvod, lze ho popsat : o pravdivostní tabulkou o Karnaughovou mapou o Algebraickým tvarem Sekvenční obvod lze takto popsat též, ale vzhledem k závislosti sekvenčních funkcí na vstupních hodnotách je to nevhodné. Proto se pro sekvenční funkce používá matematického modelu, který se nazývá konečný automat (protože má konečný počet vnitřních stavů).

Konečný automat přijímá vstupní nezávisle proměnné symboly z množiny vstupních hodnot (in I)a vydává výstupní symboly z množiny výstupních hodnot (on O). Obě množiny jsou omezené. Jak vstupní proměnné a výstupní proměnné, tak i vnitřní proměnné (qi Q) jsou sledovány v diskrétních časových okamžicích. Proto lze tento automat popsat stavovou tabulkou, kdy každý řádek odpovídá každému vnitřnímu stavu (qi) a každý sloupec každému vstupnímu stavu (in). Pak prvek v řádku qi a sloupci ik vyjadřuje následující stav a výstupní stav oj v případě, že je na vstupech vstupní nezávislá proměnná ik a automat ve stavu qi.

Proto funkce, která definuje podle okamžitého vnitřního stavu a vstupní nezávisle proměnné následující stav se nazývá přechodová funkce N(q ik). Funkce, která definuje novou výstupní závisle proměnnou na základě aktuálního vnitřního stavu a vstupní nezávisle proměnné se nazývá výstupní funkce Z(q ik). V teorii konečných automatů je pak automat popsán a tím definován následovně : Κ ={I, O, Q, N, Z}

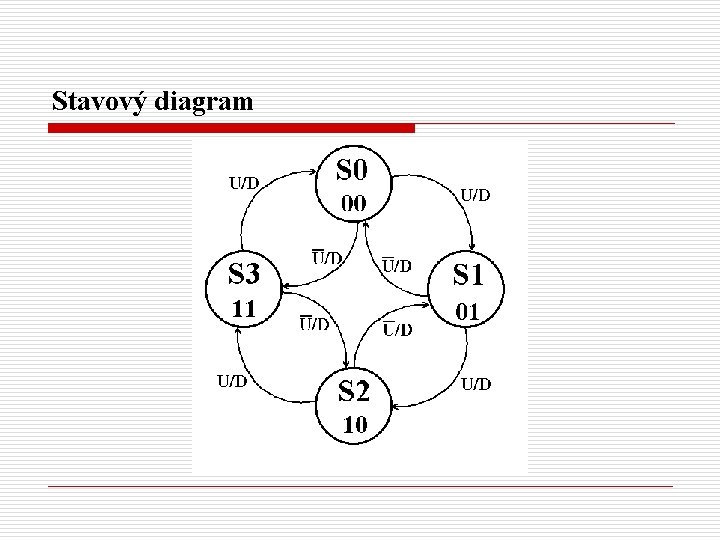

Běžně se rozlišují 2 typy automatů : o Mealyho – byl výše popsán o Moorův – kde výstupní závisle proměnné jsou jen funkcí vnitřního stavu Jinou formou popisu sekvenčních funkcí jsou stavové diagramy a přechodové tabulky, což je vlastně grafické znázornění takovéhoto automatu. Stavy jsou znázorněny kroužky a přechody mezi jednotlivými stavy orientovanými spoji, které jsou popsány vstupními a výstupními symboly.

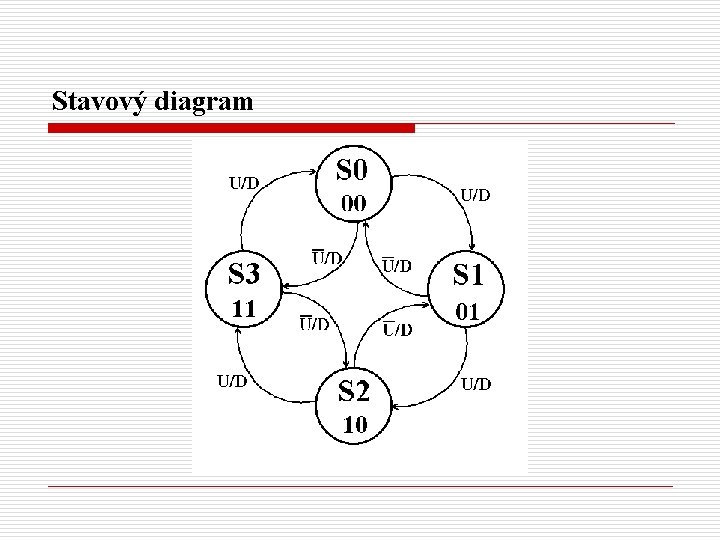

Stavový diagram

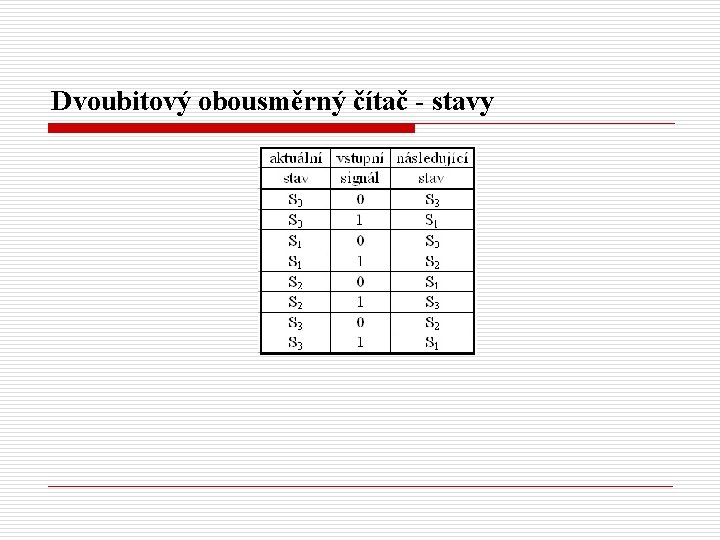

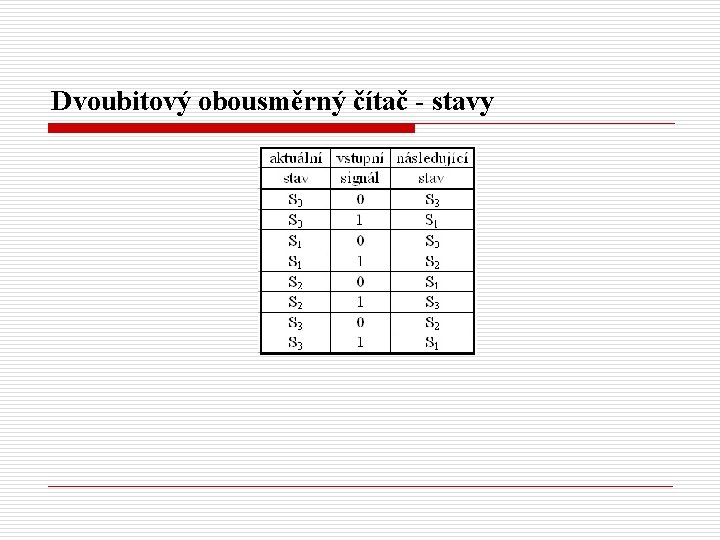

Dvoubitový obousměrný čítač - stavy

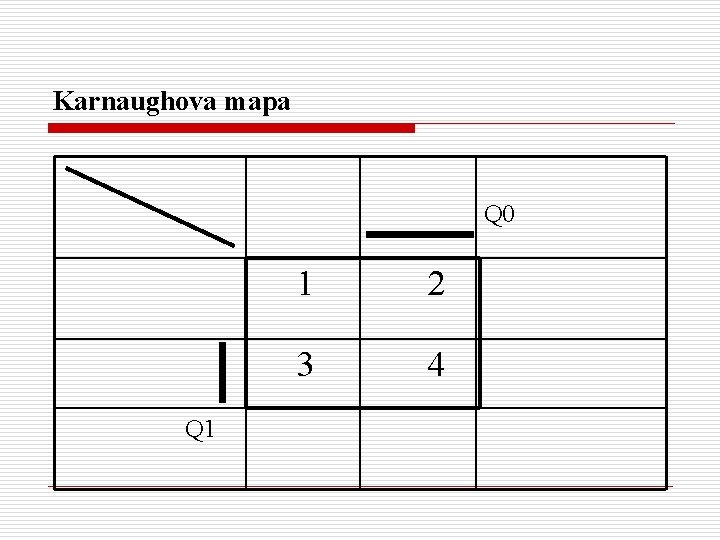

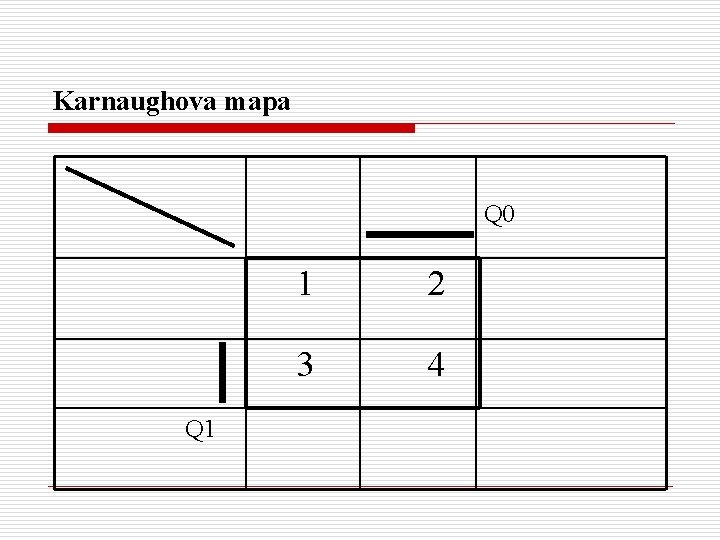

Karnaughova mapa Q 0 Q 1 1 2 3 4

Jak již bylo řečeno v předchozích kapitolách jsou vstupní a výstupní signály časově určeny řídícími impulsy (hodinkami), zabezpečujícími změnu všech logických proměnných. Současná změna však u asynchronních sekvenčních obvodů není zajištěna z důvodu rychlosti šíření signálu (vznik dynamického hazardu).

Minimalizace Procesy minimalizace lze rozdělit do 2 skupin : o Manuální minimalizační metody, ke kterým patří například algebraická minimalizace a minimalizace Karnaughovou mapou. Tyto metody jsou zvládnutelné jen pro několik málo proměnných. o Algoritmická minimalizační metoda je vhodná též jen pro omezený počet logických proměnných. Mezi tyto metody patří Ø Metoda Quine-Mc. Clusky Ø algoritmus PRESTO Ø algoritmus ESPRESSO II-MV

Architektura obvodů PLD Filosofie těchto obvodů je založena na tom, že libovolný kombinační obvod lze vyjádřit buď jako součet součinů, nebo jako součin součtů booleovských funkcí. Proto je lze realizovat pomocí vhodného propojení hradel AND a OR. V těchto obvodech se však především používá součet součinů. Díky možnosti naprogramování propojení vstupů, výstupů, hradel AND a OR se zrealizují nejprve součiny a poté součty. Uživatel toho pak využije při programování obvodu PLD a stanoví, která propojení budou realizována a která nikoliv.

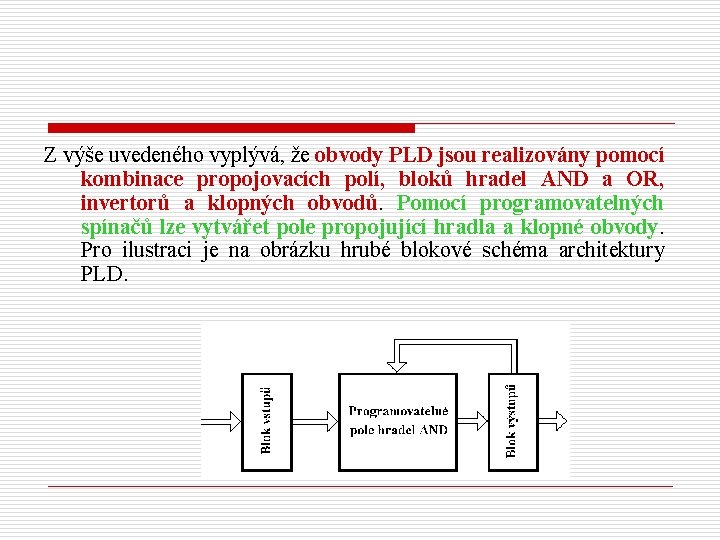

Z výše uvedeného vyplývá, že obvody PLD jsou realizovány pomocí kombinace propojovacích polí, bloků hradel AND a OR, invertorů a klopných obvodů. Pomocí programovatelných spínačů lze vytvářet pole propojující hradla a klopné obvody. Pro ilustraci je na obrázku hrubé blokové schéma architektury PLD.

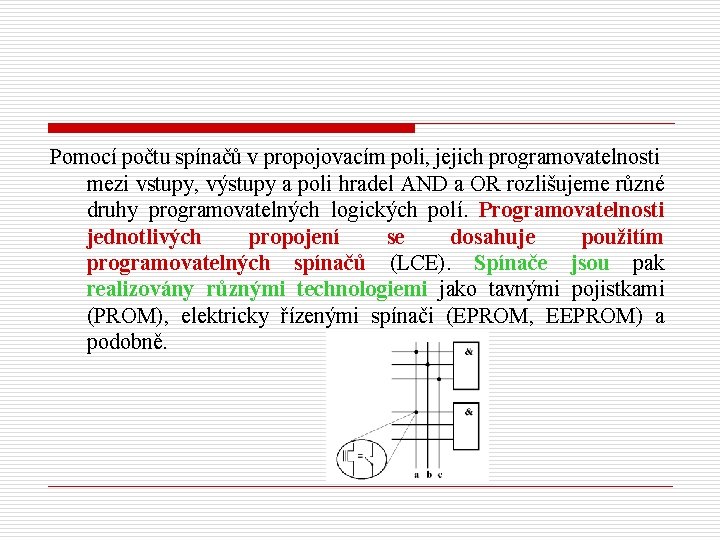

Pomocí počtu spínačů v propojovacím poli, jejich programovatelnosti mezi vstupy, výstupy a poli hradel AND a OR rozlišujeme různé druhy programovatelných logických polí. Programovatelnosti jednotlivých propojení se dosahuje použitím programovatelných spínačů (LCE). Spínače jsou pak realizovány různými technologiemi jako tavnými pojistkami (PROM), elektricky řízenými spínači (EPROM, EEPROM) a podobně.

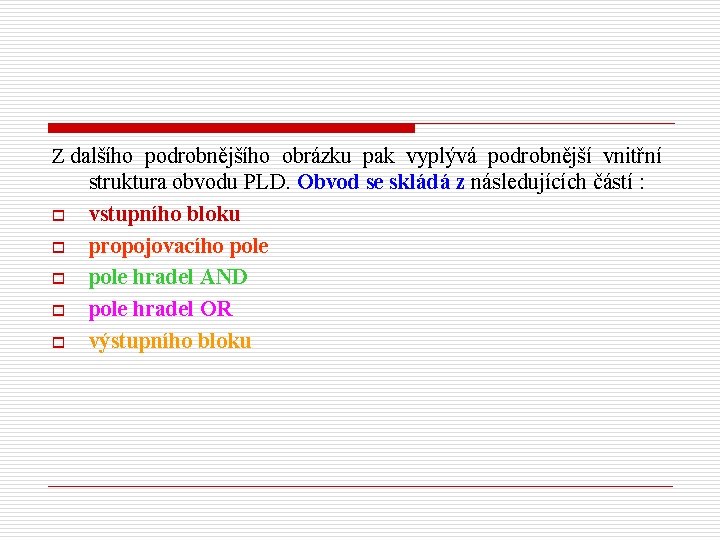

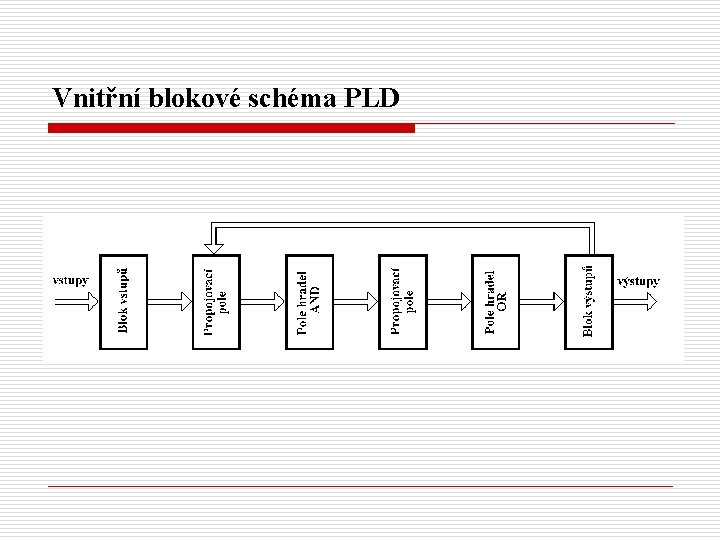

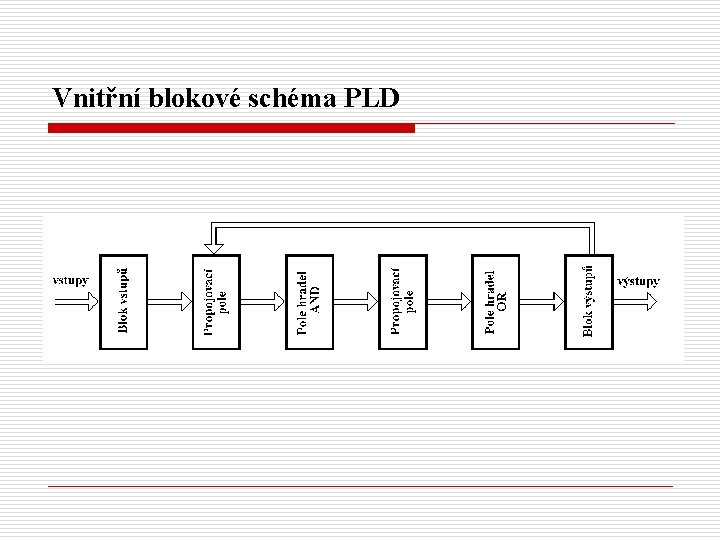

Z dalšího podrobnějšího obrázku pak vyplývá podrobnější vnitřní struktura obvodu PLD. Obvod se skládá z následujících částí : o o o vstupního bloku propojovacího pole hradel AND pole hradel OR výstupního bloku

Vnitřní blokové schéma PLD

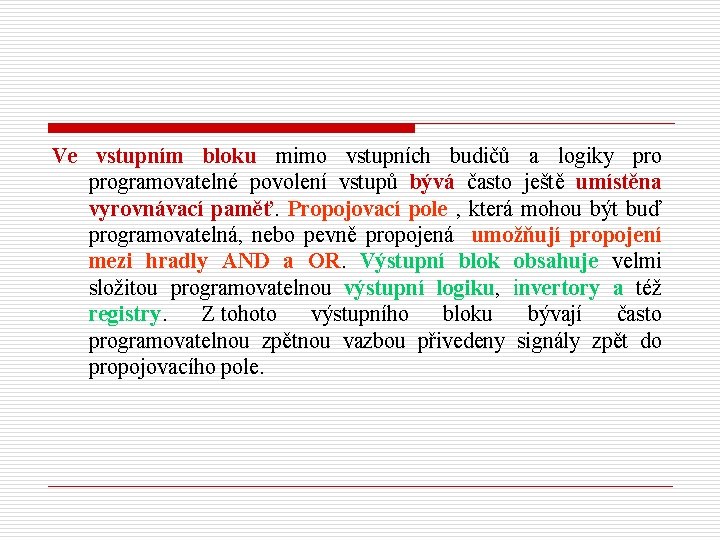

Ve vstupním bloku mimo vstupních budičů a logiky programovatelné povolení vstupů bývá často ještě umístěna vyrovnávací paměť. Propojovací pole , která mohou být buď programovatelná, nebo pevně propojená umožňují propojení mezi hradly AND a OR. Výstupní blok obsahuje velmi složitou programovatelnou výstupní logiku, invertory a též registry. Z tohoto výstupního bloku bývají často programovatelnou zpětnou vazbou přivedeny signály zpět do propojovacího pole.

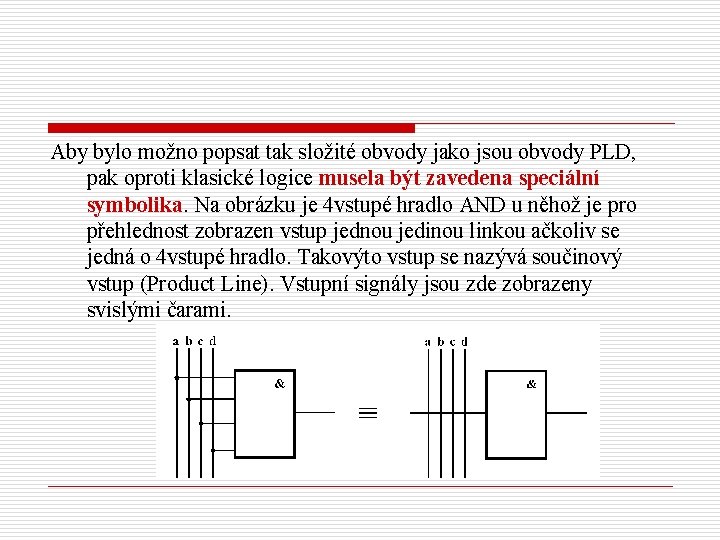

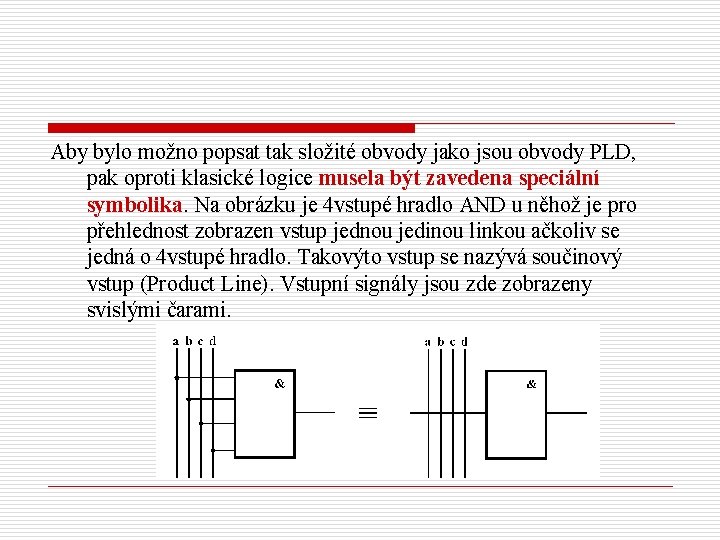

Aby bylo možno popsat tak složité obvody jako jsou obvody PLD, pak oproti klasické logice musela být zavedena speciální symbolika. Na obrázku je 4 vstupé hradlo AND u něhož je pro přehlednost zobrazen vstup jednou jedinou linkou ačkoliv se jedná o 4 vstupé hradlo. Takovýto vstup se nazývá součinový vstup (Product Line). Vstupní signály jsou zde zobrazeny svislými čarami.

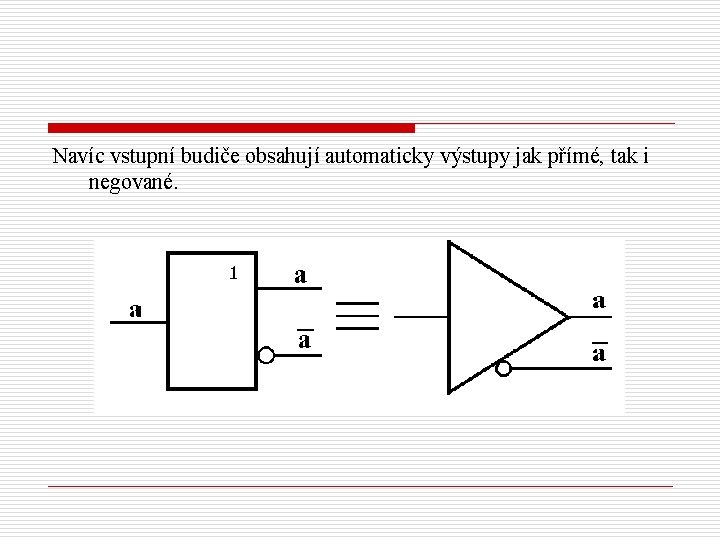

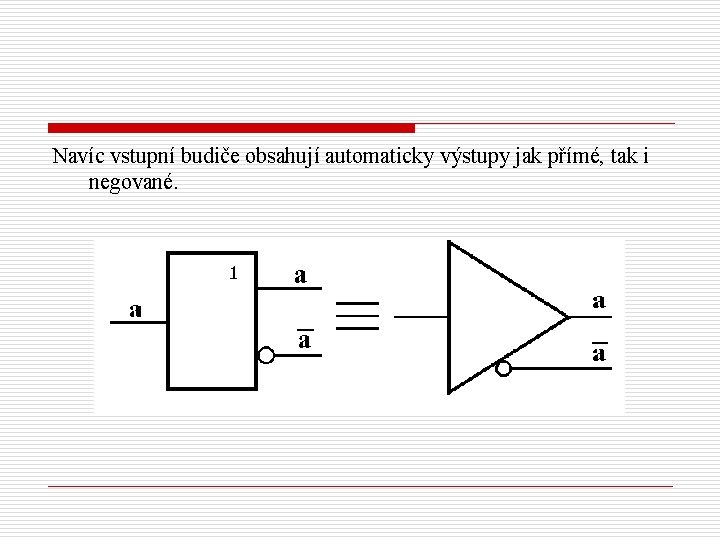

Navíc vstupní budiče obsahují automaticky výstupy jak přímé, tak i negované.

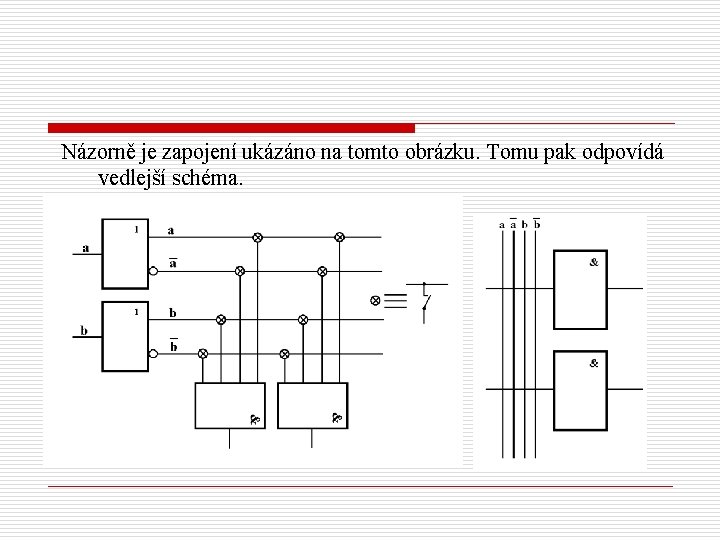

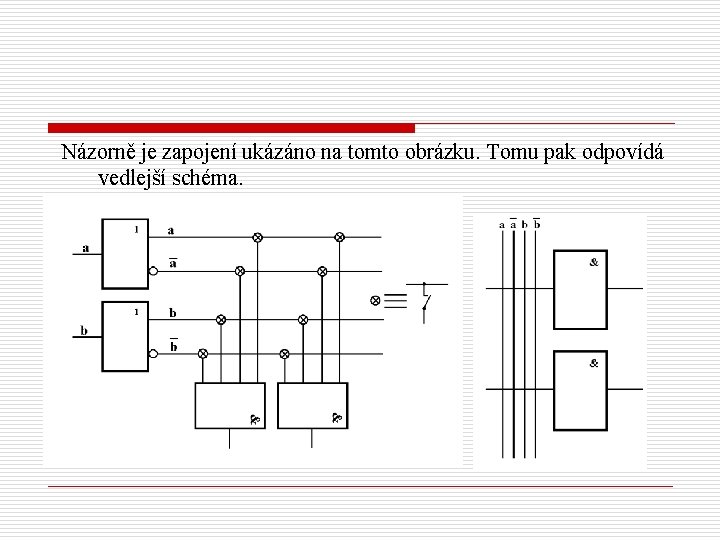

Názorně je zapojení ukázáno na tomto obrázku. Tomu pak odpovídá vedlejší schéma.

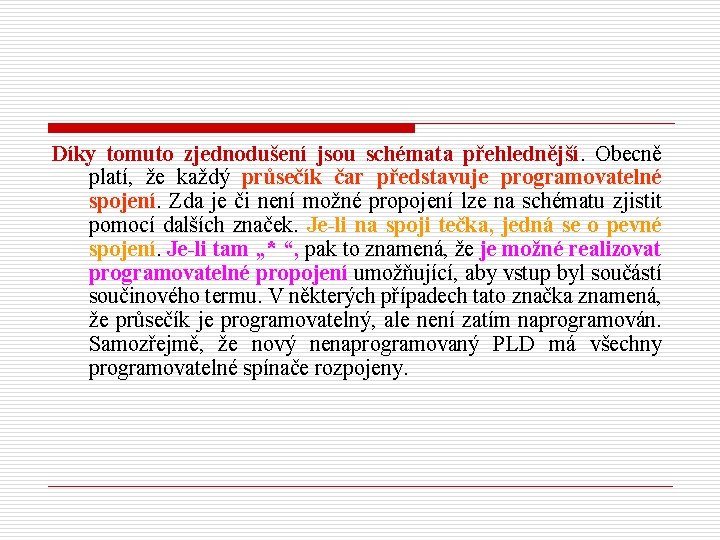

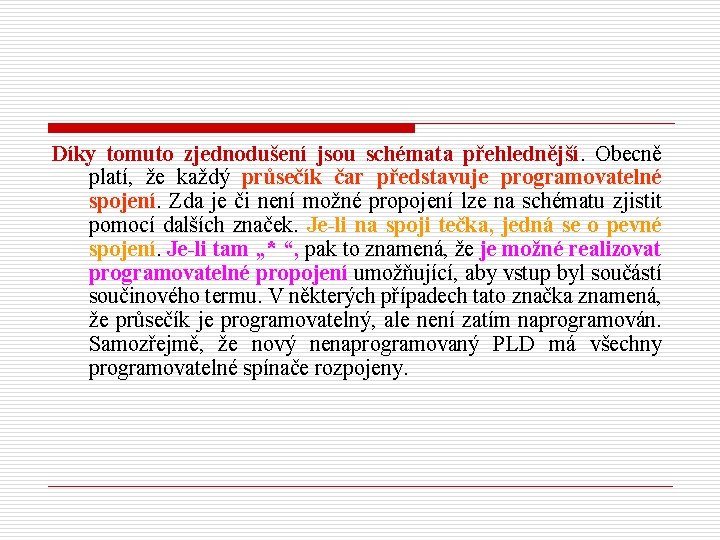

Díky tomuto zjednodušení jsou schémata přehlednější. Obecně platí, že každý průsečík čar představuje programovatelné spojení. Zda je či není možné propojení lze na schématu zjistit pomocí dalších značek. Je-li na spoji tečka, jedná se o pevné spojení. Je-li tam „* “, pak to znamená, že je možné realizovat programovatelné propojení umožňující, aby vstup byl součástí součinového termu. V některých případech tato značka znamená, že průsečík je programovatelný, ale není zatím naprogramován. Samozřejmě, že nový nenaprogramovaný PLD má všechny programovatelné spínače rozpojeny.

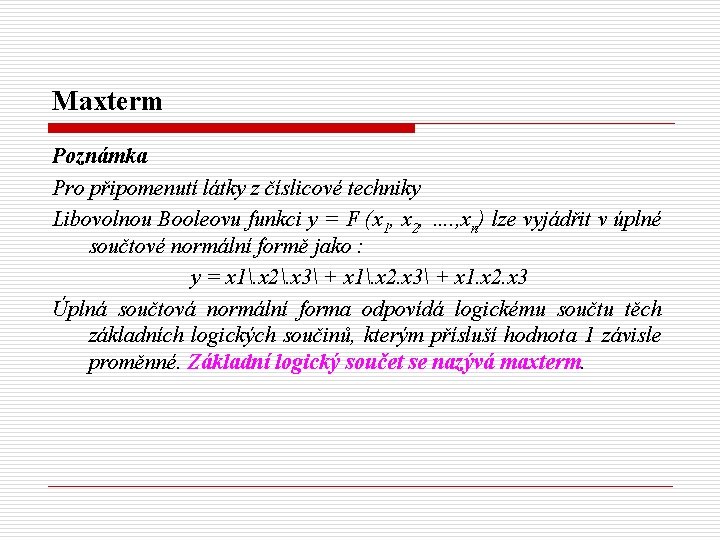

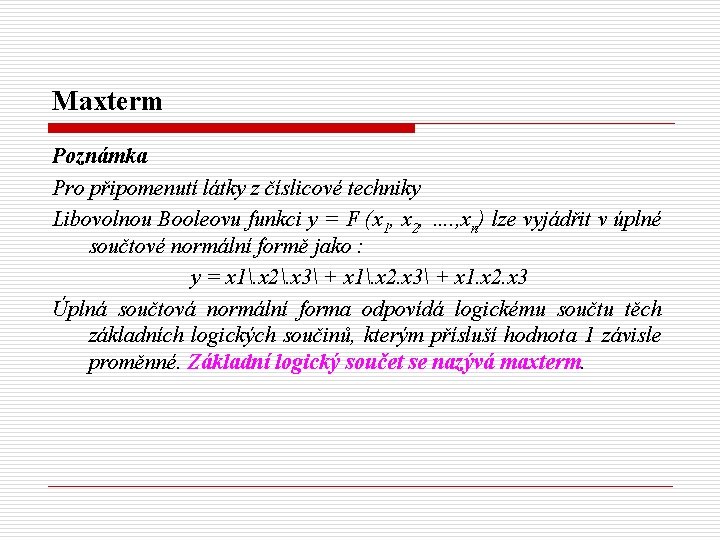

Maxterm Poznámka Pro připomenutí látky z číslicové techniky Libovolnou Booleovu funkci y = F (x 1, x 2, …. , xn) lze vyjádřit v úplné součtové normální formě jako : y = x 1. x 2. x 3 + x 1. x 2. x 3 + x 1. x 2. x 3 Úplná součtová normální forma odpovídá logickému součtu těch základních logických součinů, kterým přísluší hodnota 1 závisle proměnné. Základní logický součet se nazývá maxterm.

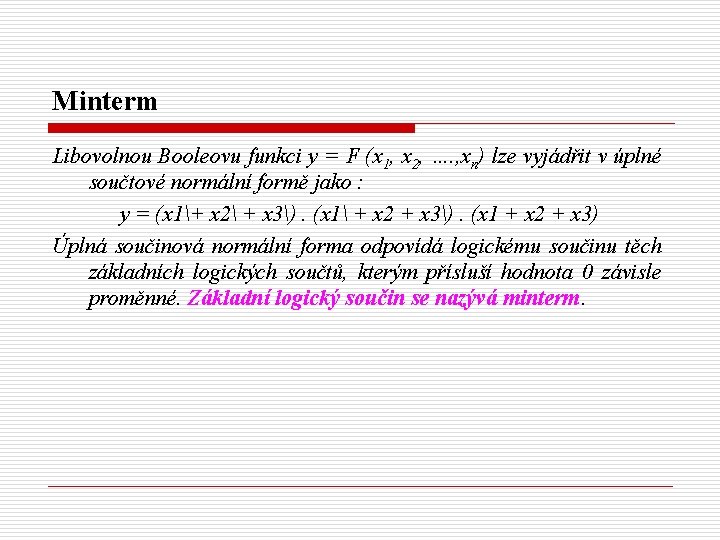

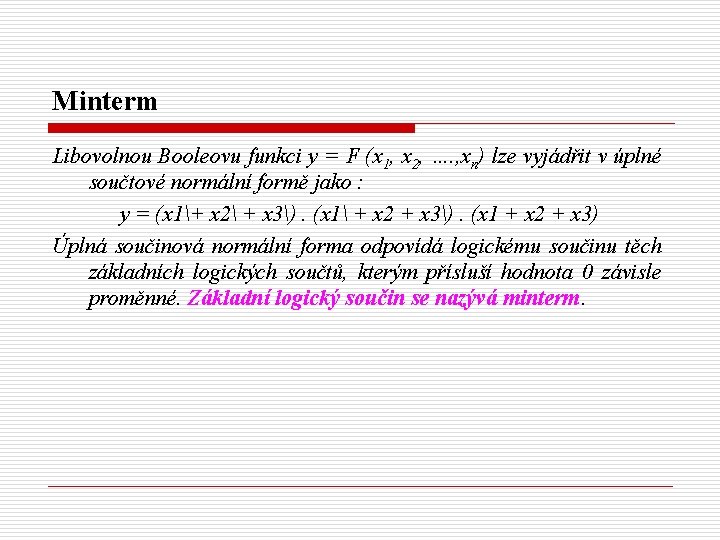

Minterm Libovolnou Booleovu funkci y = F (x 1, x 2, …. , xn) lze vyjádřit v úplné součtové normální formě jako : y = (x 1+ x 2 + x 3). (x 1 + x 2 + x 3). (x 1 + x 2 + x 3) Úplná součinová normální forma odpovídá logickému součinu těch základních logických součtů, kterým přísluší hodnota 0 závisle proměnné. Základní logický součin se nazývá minterm.

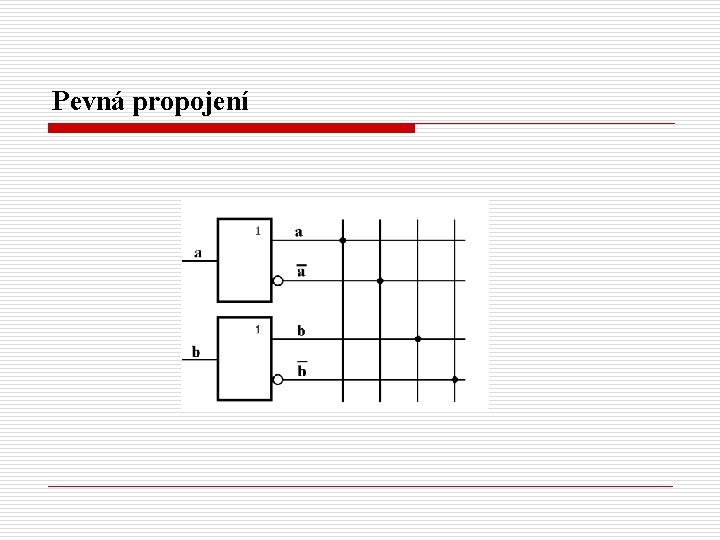

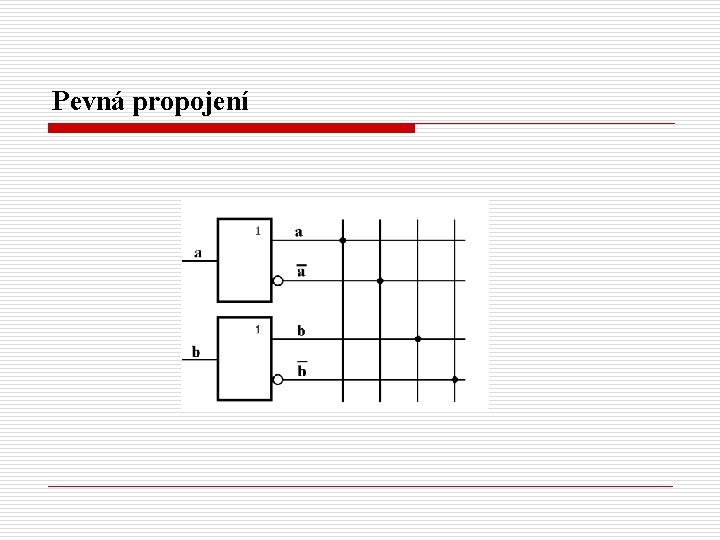

Pevná propojení

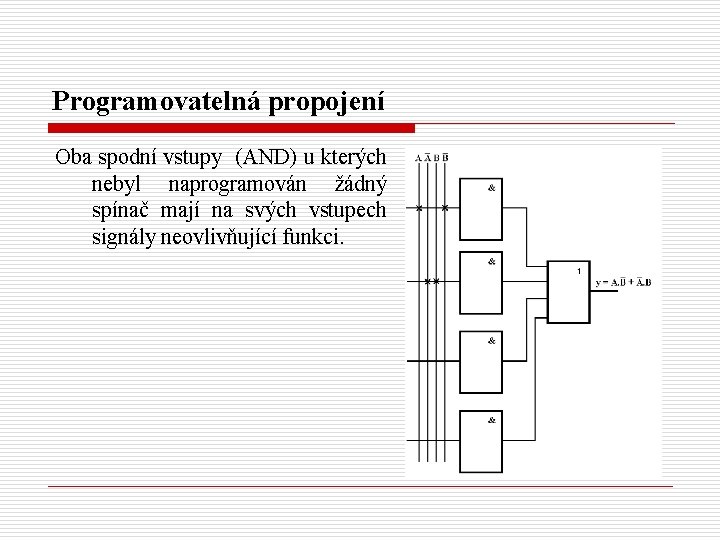

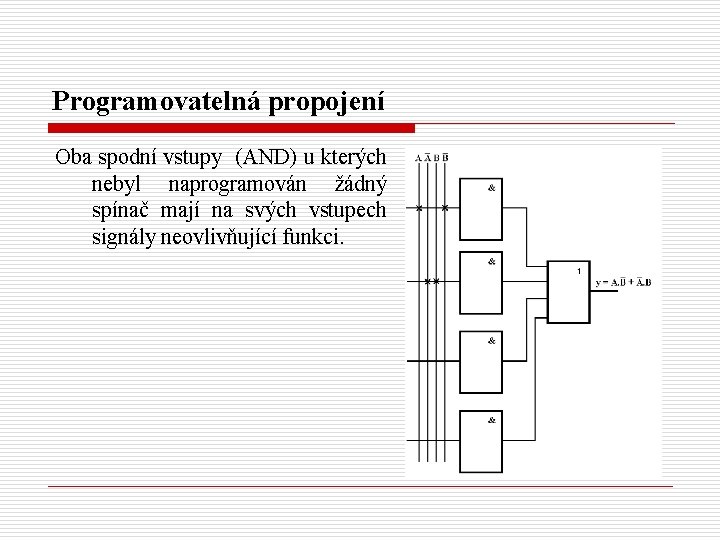

Programovatelná propojení Oba spodní vstupy (AND) u kterých nebyl naprogramován žádný spínač mají na svých vstupech signály neovlivňující funkci.

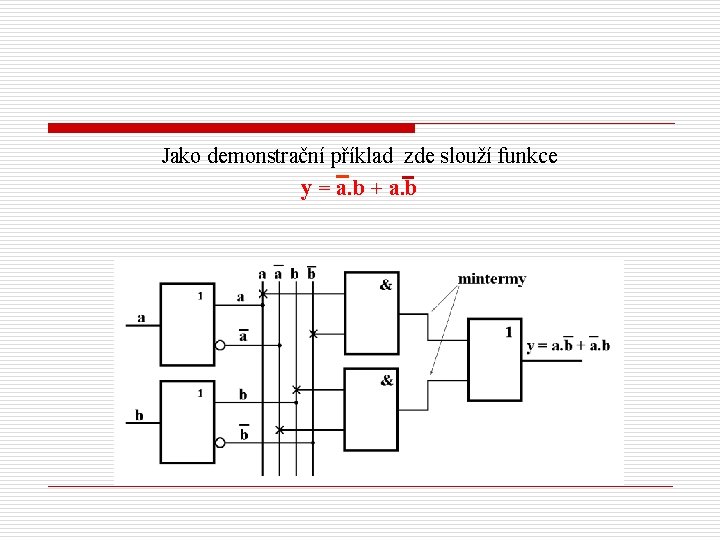

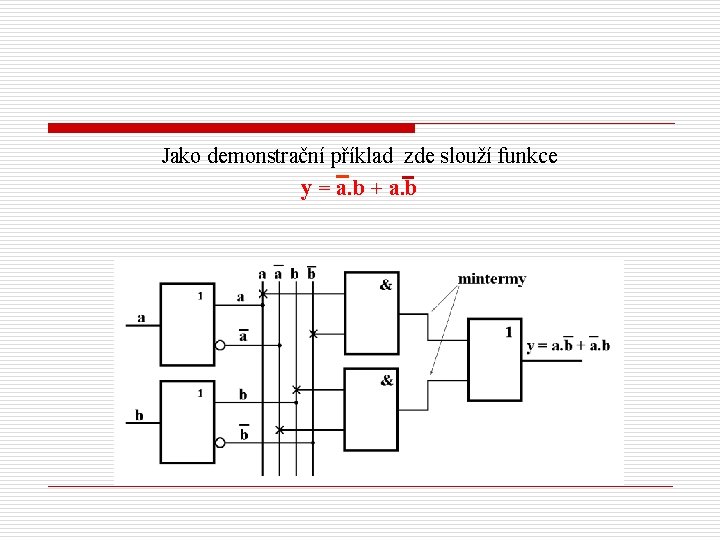

Jako demonstrační příklad zde slouží funkce y = a. b + a. b

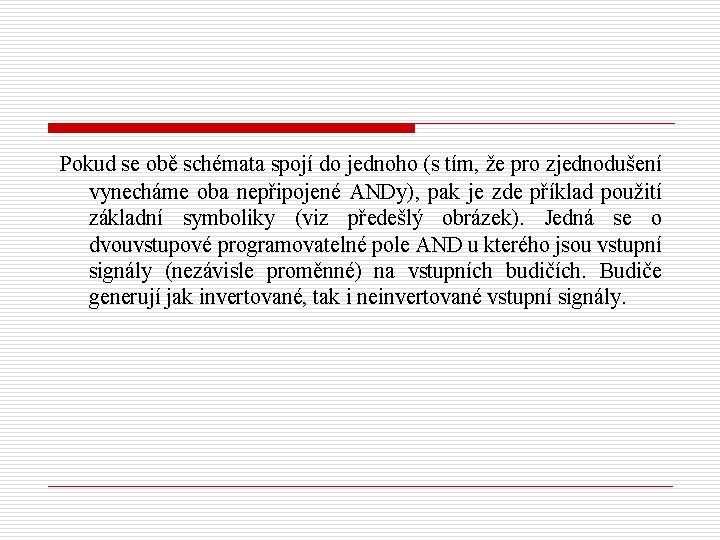

Pokud se obě schémata spojí do jednoho (s tím, že pro zjednodušení vynecháme oba nepřipojené ANDy), pak je zde příklad použití základní symboliky (viz předešlý obrázek). Jedná se o dvouvstupové programovatelné pole AND u kterého jsou vstupní signály (nezávisle proměnné) na vstupních budičích. Budiče generují jak invertované, tak i neinvertované vstupní signály.

Křížení vstupních proměnných a součinových vstupů realizují programovatelné propojovací pole logických součinů (AND) a to o 4 vstupní signály a, b, o 4 čtyřvstupá hradla AND, což se označuje jako rozměr 4 x 4.

Výstupy hradel logických součinů (AND) jsou napevno propojeny se vstupy hradla logického součtu (OR). Obdobně jako je zde předvedeno propojení vstupů s hradly AND, je možné v řadě případů propojit i výstupy hradel AND napevno nebo programovatelným polem k hradlům OR.

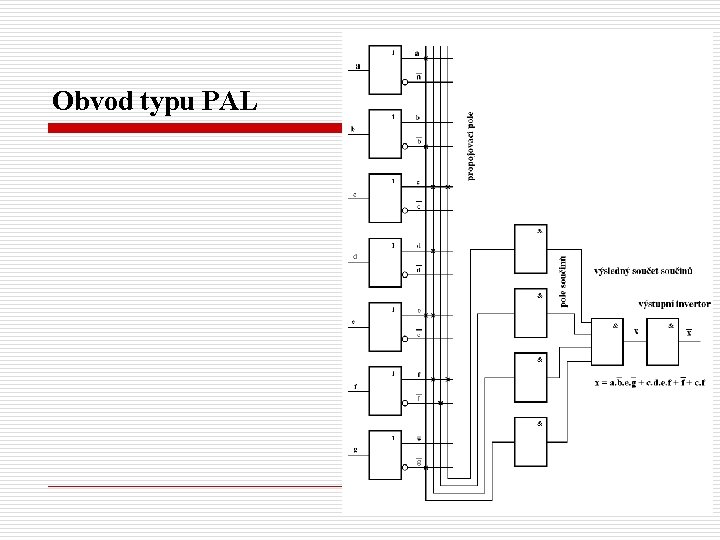

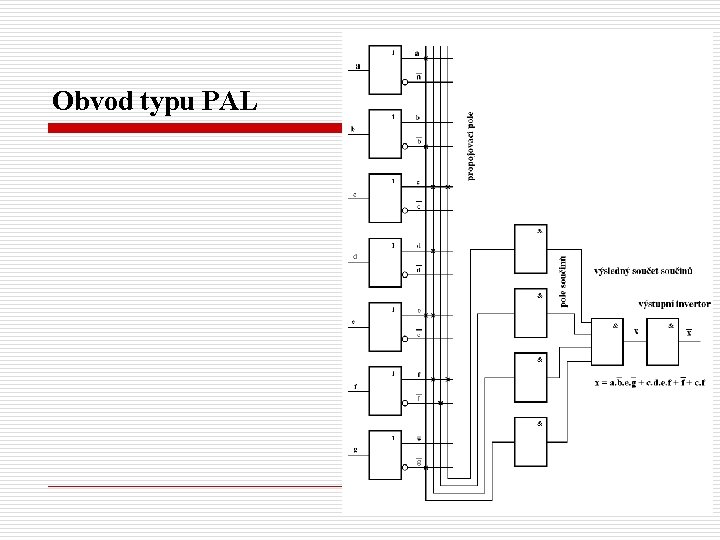

Jako příklad takovéto symboliky může sloužit obvod typu PAL (viz následující obrázek). Vstupní signály a až g jsou přivedeny na vstupní budiče poskytující možnost programového připojení signálu (přímého i invertovaného) do pole součinů (pole AND) programovatelných spínačů (Fuses). Výstupy hradel AND se nazývají součinovými termy (minterm). Z obrázku je vidět jak levý minterm prezentuje funkci : a. b. e. g

Obvod typu PAL

Výsledná výstupní proměnná x jakožto součet součinů je : x = a. b. c. g + c. d. e. f + c. f Je však nezbytné upozornit na schematické značky, kdy je pro logické znaky americkými firmami doposud používána stará americká norma MIL. Výstupní blok obvodu PLD může být realizován různými obvody jako jsou registry, invertory, výstupní makrobuňky (makrocell) atd. Makrobuňka pak nahrazuje hradle OR a klopné obvody pomocí programovatelných obvodů. Tímto způsobem je možno velkou variabilitu obvodu, aniž by bylo nezbytné realizovat celou řadu typů daného obvodu.

Díky tomu je možno naprogramovat výstup jako : o aktivní L nebo H, o registr s klopným obvodem typu D či T, případně klopný obvod zamaskovat, takže se chová jako kombinační obvod o zavést zpětnou vazbu z výstupu do některé části obvodu o oba nastavovací vstupy (CL, P) jsou programovatelné jak o synchronní, tak i asynchronní o hodinové pulsy mohou být použity jako externí, tak i z vnitřního termu o povolení výstupu OE (Output Enable) může být opět jako externí či z vnitřního termu

o o vstupní signály a až g jsou přivedeny na vstupní budiče poskytující možnost programového vstupem klopného obvodu může být i výstup hradle OR jehož vstupy jsou termy

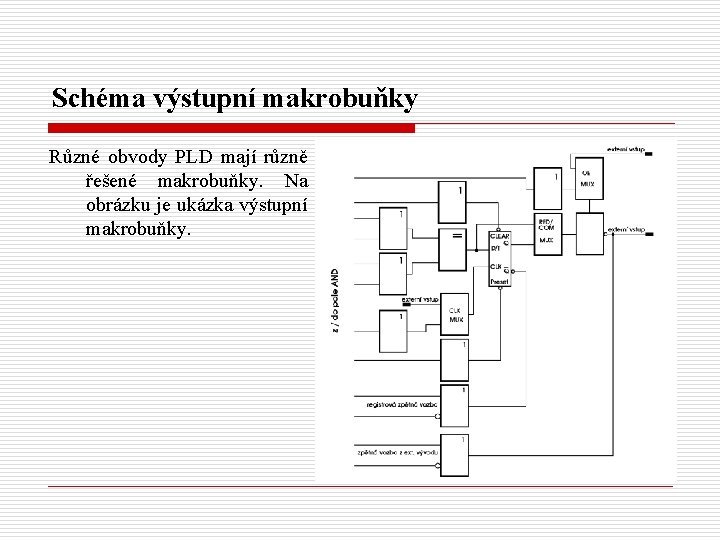

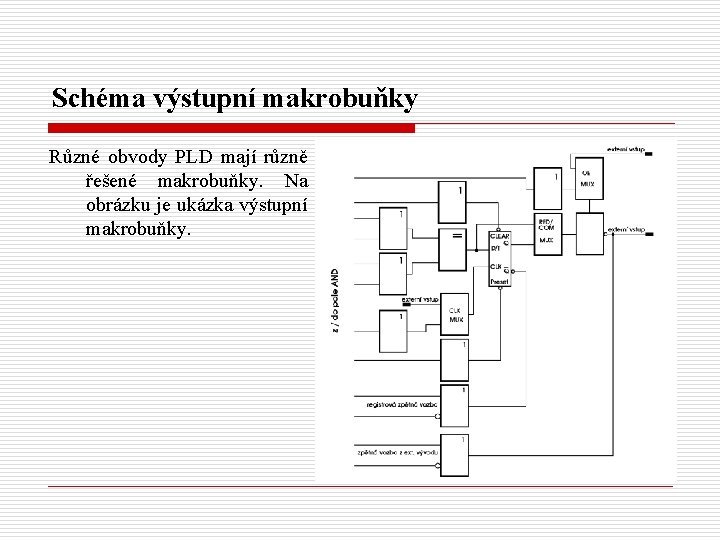

Schéma výstupní makrobuňky Různé obvody PLD mají různě řešené makrobuňky. Na obrázku je ukázka výstupní makrobuňky.

Obvody této skupiny lze podle vlastností propojovacího pole rozdělit do následujících skupin: o PAL, GAL, EPLD – tato skupina má programovatelnou matici AND a pevnou propojovací matici OR. Matice OR realizuje většinou součet 8 součinů. Architektura obvodů je pevná bez možnosti větších změn. o PLA, PLS/PSG - tato skupina má programovatelné matice AND i OR s tím, že umožňují realizaci velkého počtu součinů. Některé obvody mají též i řadu registrů s vnitřní zpětnou vazbou nepřístupnou uživateli. o MAX, MACH, +LOGIC – tato skupina má víceúrovňovou programovatelnou matici rozšiřovatelnou i polem hradel a programovatelných makrobuněk.

Typy PLD Obvody v jednotlivých skupinách se dost podstatným způsobem od sebe liší. Vzhledem k tomu, že se s většinou z nich nesetkáme, bude se prováděný popis týkat jen různých základních částí obvodů, které jsou si velmi podobné či vylepšení použitých prvně.

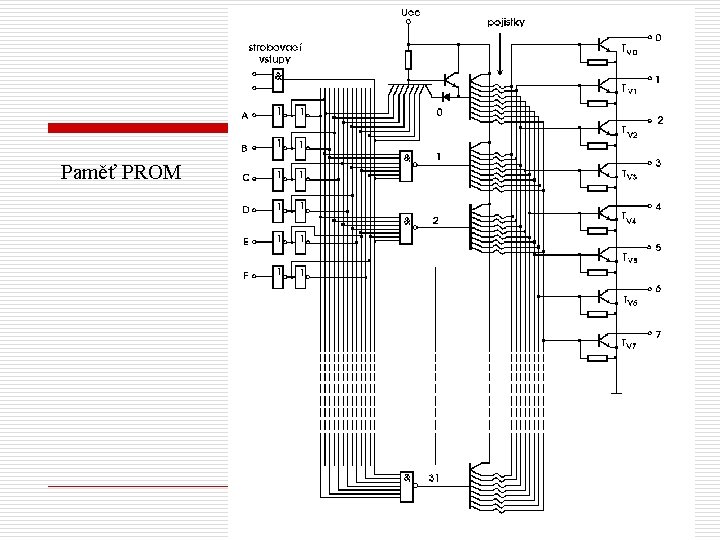

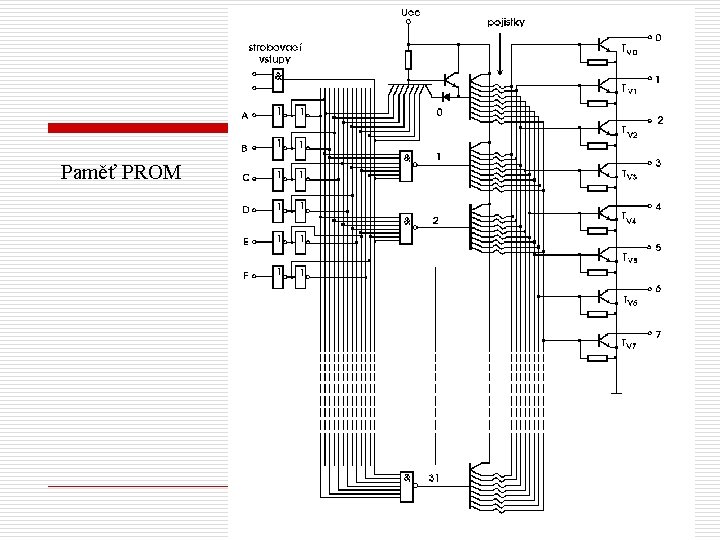

PLD typu PROM Obvod PROM je vlastně matice paměťových buněk adresovatelných vstupními signály. Datové sloupce jsou pak výstupní signály. Z toho vyplývá, že velikost paměťové matice je určena jak adresovými, tak i datovými signály. Jako příklad může sloužit paměť 74188 (viz následující obrázek) s 5 adresovými vstupy, čemuž odpovídá 32 adres a 8 datových signálů. Výsledná paměť má 256 paměťových buněk (32 adres x 8 bitů).

Paměť PROM

V architektuře PLD mají obvody PROM pevné propojovací pole hradel AND a programovatelné pole OR. Tato kombinace dovoluje, aby různé kombinace výstupních hodnot byla pomocí programu přiřazena různé kombinaci vstupních hodnot. Pro obvody jsou vhodné aplikace vyžadující aby na každou kombinaci vstupních signálů byla realizována jiná odezva signálů výstupních. Nevýhodou je : o omezený počet vstupních signálů o velikost programovací matice.

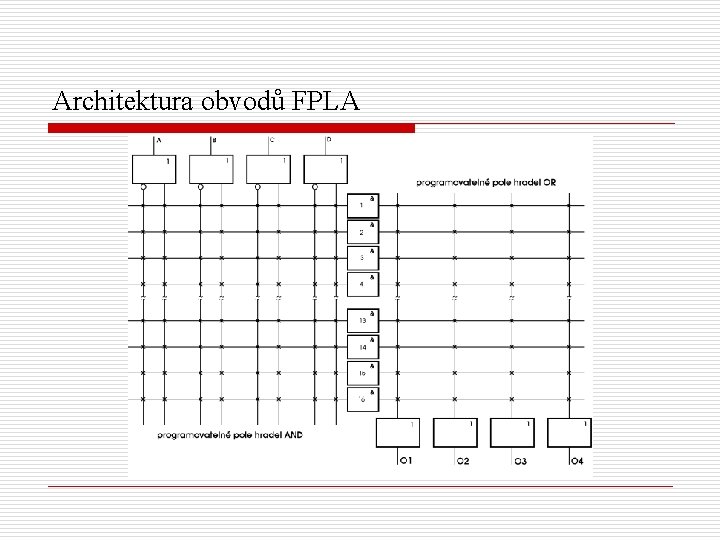

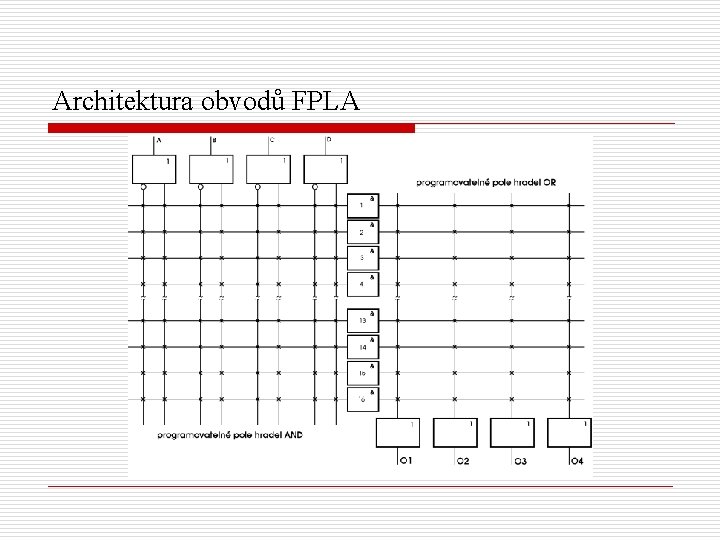

PLD typu FPLA Obvody Field Programmable Logic Array (FPLA) obsahují jak programovatelné pole AND, tak i programovatelné pole OR. Vstupní nezávisle proměnné jsou přiváděny do pole AND a to jak v přímém, tak i invertovaném tvaru. Součinové pole je programovatelné a vytváří se na něm součinové termy, které jsou přiváděny do programovatelného součtového pole. Je zde umožněno propojení libovolného termu k libovolnému součtovému hradlu (OR), případně i na více těchto hradel. Tato vlastnost se nazývá sdílení termů (Product Term Sharing). Poté je součet součinů vyveden na výstup.

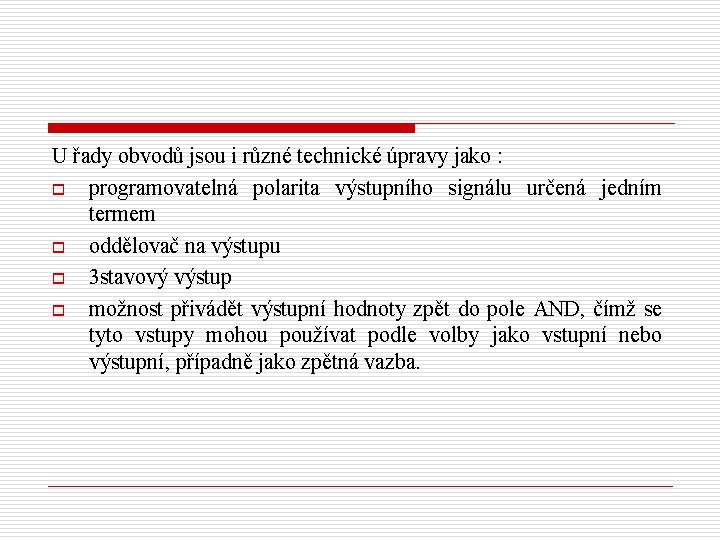

U řady obvodů jsou i různé technické úpravy jako : o programovatelná polarita výstupního signálu určená jedním termem o oddělovač na výstupu o 3 stavový výstup o možnost přivádět výstupní hodnoty zpět do pole AND, čímž se tyto vstupy mohou používat podle volby jako vstupní nebo výstupní, případně jako zpětná vazba.

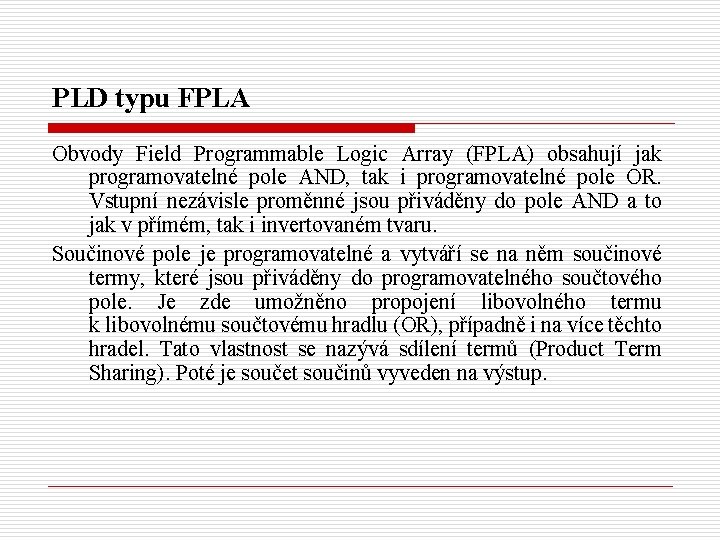

Architektura obvodů FPLA

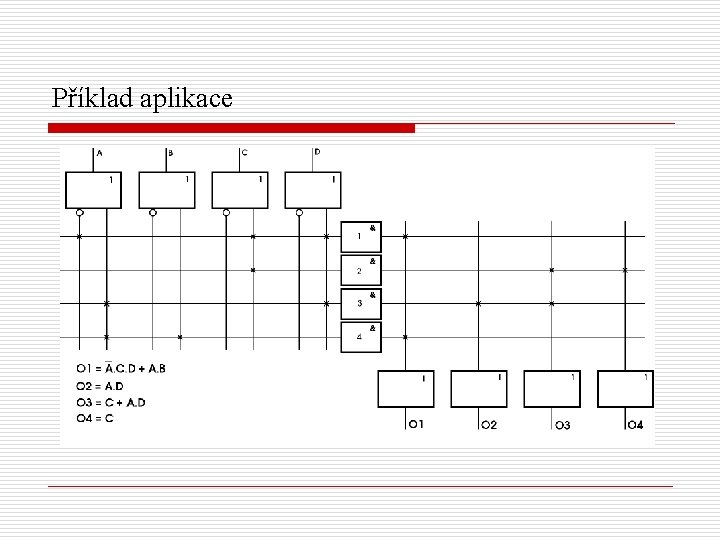

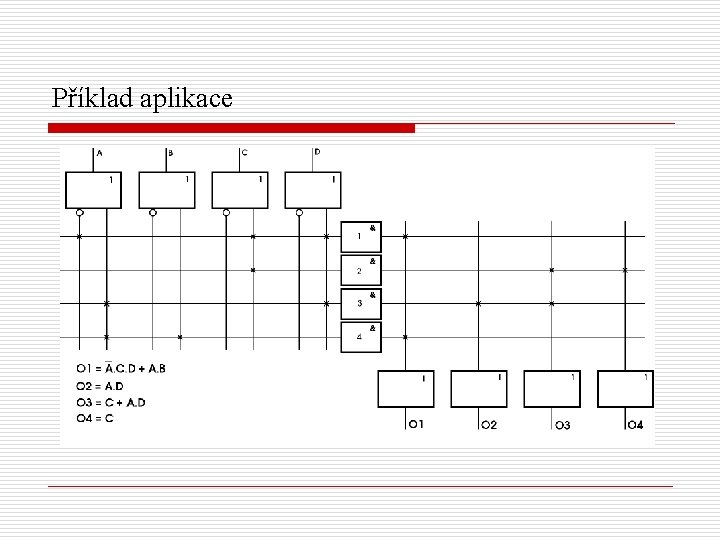

Příklad aplikace

Některé obvody jsou popisovány tak, že označují jejich možnosti. Například 18 x 42 x 10 znamená, že obvod má : o 18 vstupů pole AND o maximálně 42 termů o 10 výstupních signálů Pokud byla logika FPLA vybavena navíc klopnými obvody, pak se tato kombinace nazývala FPLS (Field Programmable Logic Sequencer). Díky této kombinaci bylo možno dosáhnout implementace nejrůznějších stavových automatů.

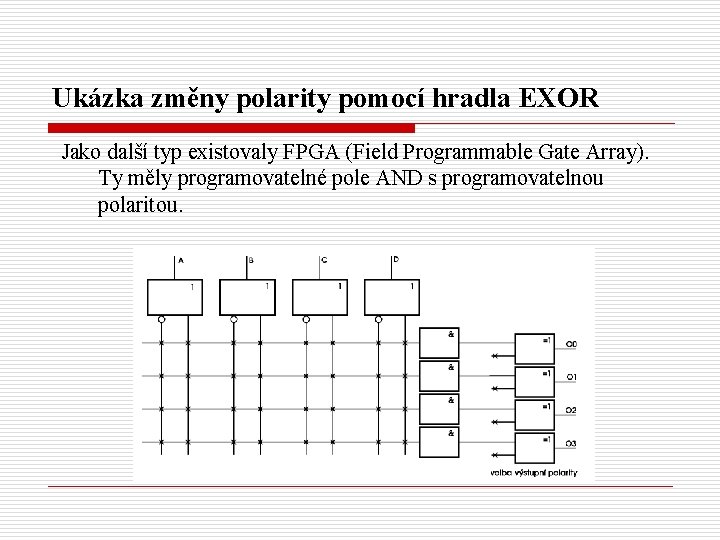

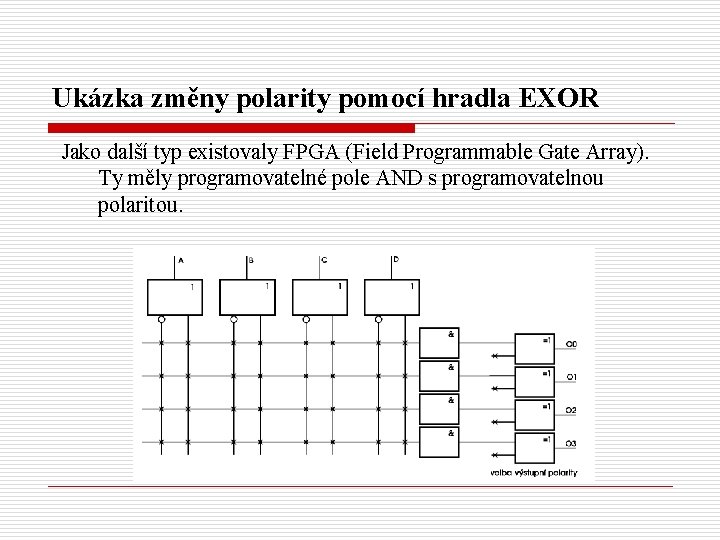

Ukázka změny polarity pomocí hradla EXOR Jako další typ existovaly FPGA (Field Programmable Gate Array). Ty měly programovatelné pole AND s programovatelnou polaritou.

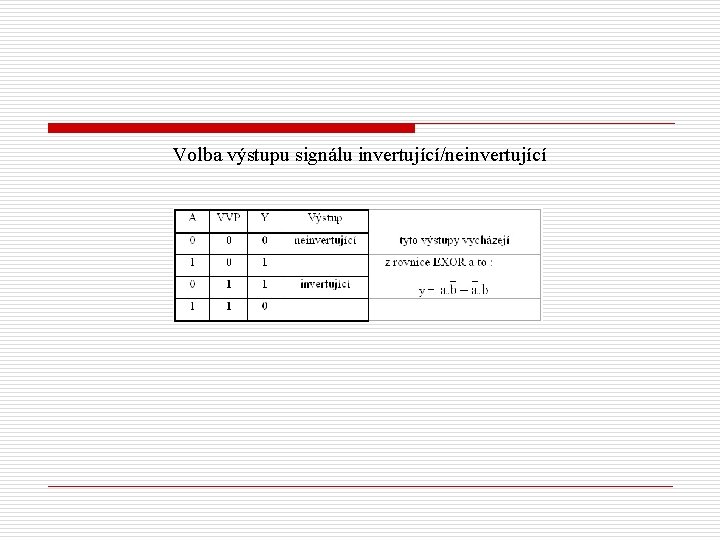

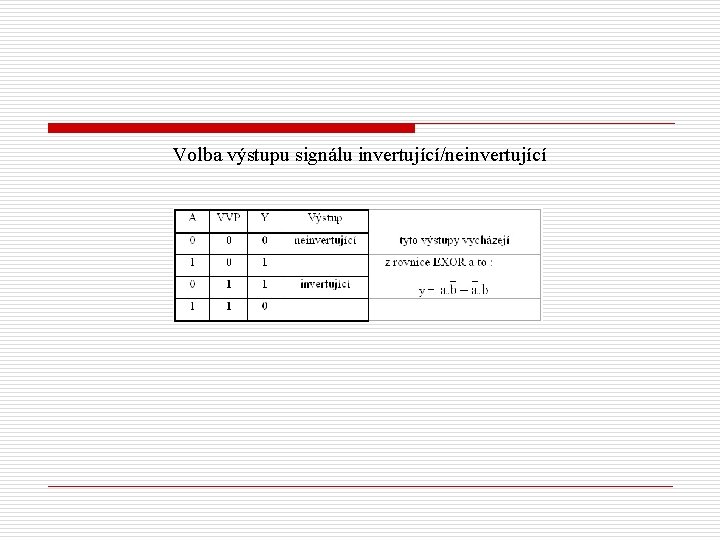

Volba výstupu signálu invertující/neinvertující

To však byla významná obvodová změna, protože z hradla AND lze za pomoci inverze realizovat NAND, případně NOR či OR. Z toho vyplývá, že libovolné základní hradlo AND se může vhodným propojením přeměnit na jiné libovolné výše uvedené hradlo.

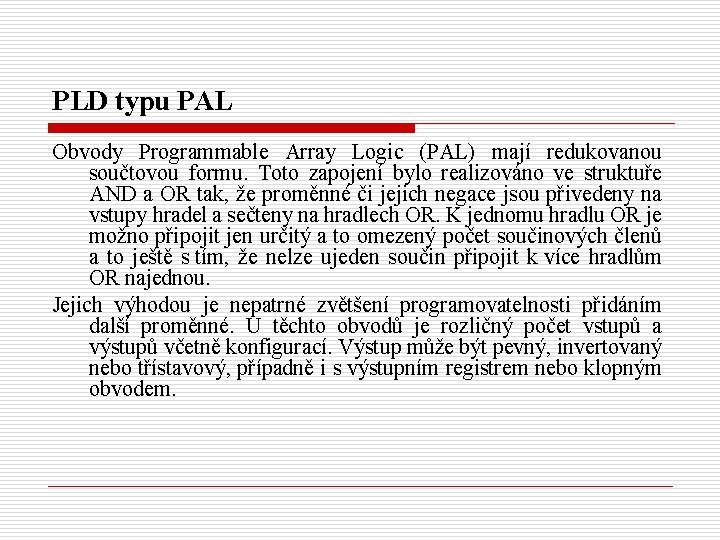

PLD typu PAL Obvody Programmable Array Logic (PAL) mají redukovanou součtovou formu. Toto zapojení bylo realizováno ve struktuře AND a OR tak, že proměnné či jejich negace jsou přivedeny na vstupy hradel a sečteny na hradlech OR. K jednomu hradlu OR je možno připojit jen určitý a to omezený počet součinových členů a to ještě s tím, že nelze ujeden součin připojit k více hradlům OR najednou. Jejich výhodou je nepatrné zvětšení programovatelnosti přidáním další proměnné. U těchto obvodů je rozličný počet vstupů a výstupů včetně konfigurací. Výstup může být pevný, invertovaný nebo třístavový, případně i s výstupním registrem nebo klopným obvodem.

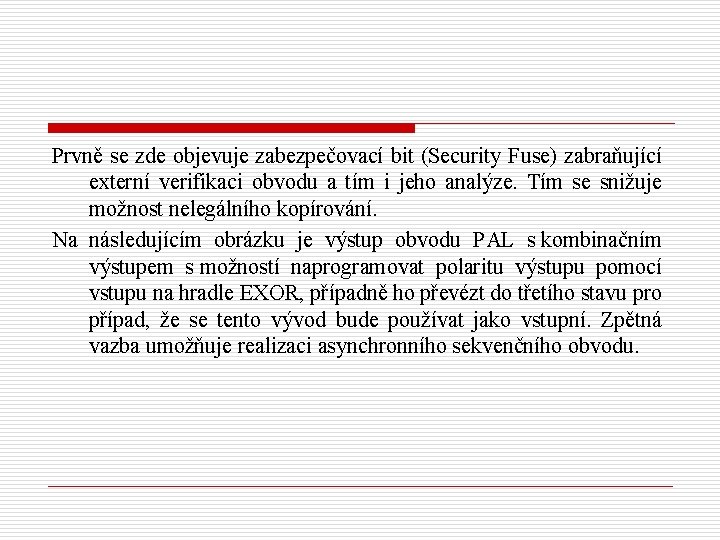

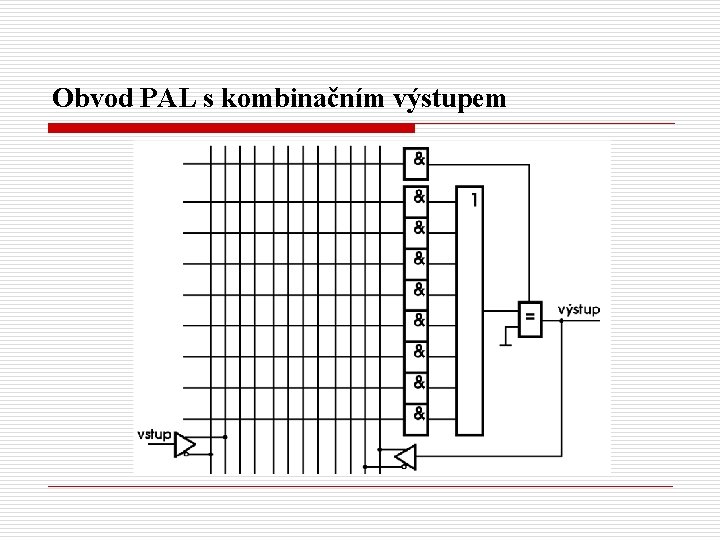

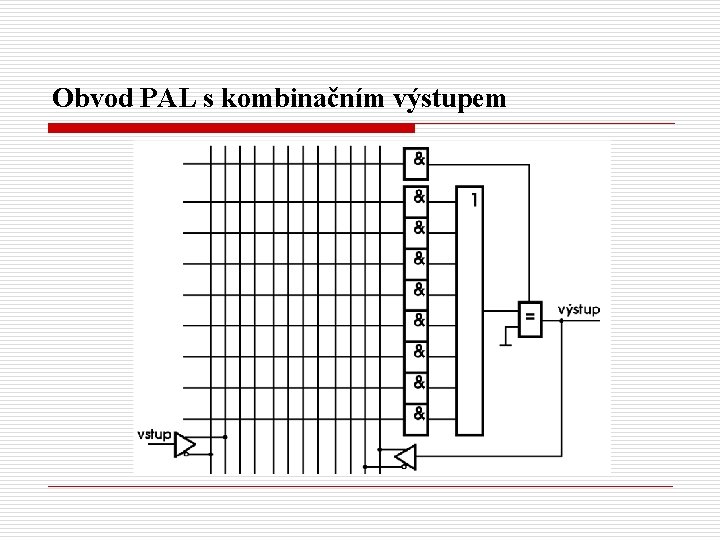

Prvně se zde objevuje zabezpečovací bit (Security Fuse) zabraňující externí verifikaci obvodu a tím i jeho analýze. Tím se snižuje možnost nelegálního kopírování. Na následujícím obrázku je výstup obvodu PAL s kombinačním výstupem s možností naprogramovat polaritu výstupu pomocí vstupu na hradle EXOR, případně ho převézt do třetího stavu pro případ, že se tento vývod bude používat jako vstupní. Zpětná vazba umožňuje realizaci asynchronního sekvenčního obvodu.

Obvod PAL s kombinačním výstupem

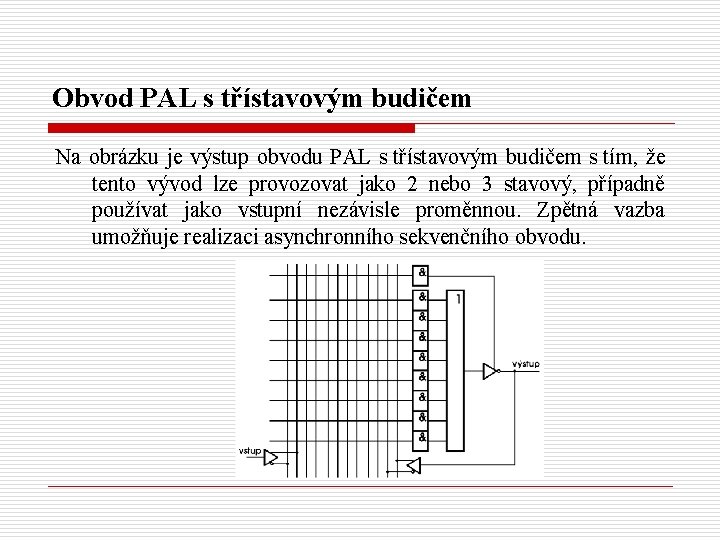

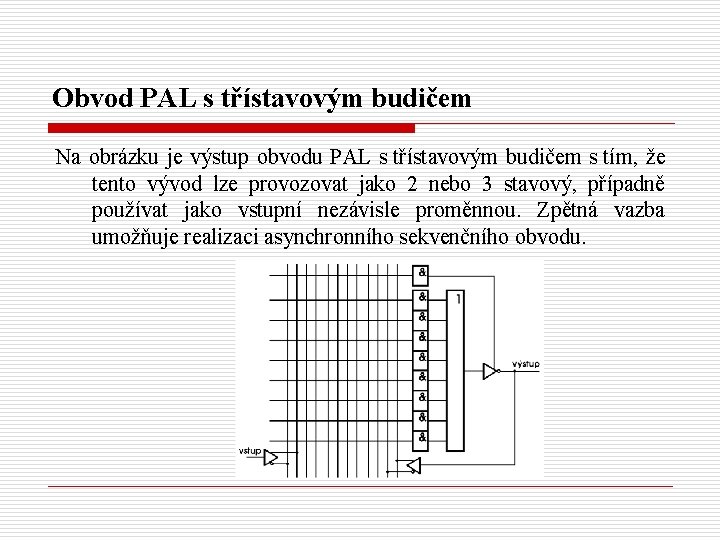

Obvod PAL s třístavovým budičem Na obrázku je výstup obvodu PAL s třístavovým budičem s tím, že tento vývod lze provozovat jako 2 nebo 3 stavový, případně používat jako vstupní nezávisle proměnnou. Zpětná vazba umožňuje realizaci asynchronního sekvenčního obvodu.

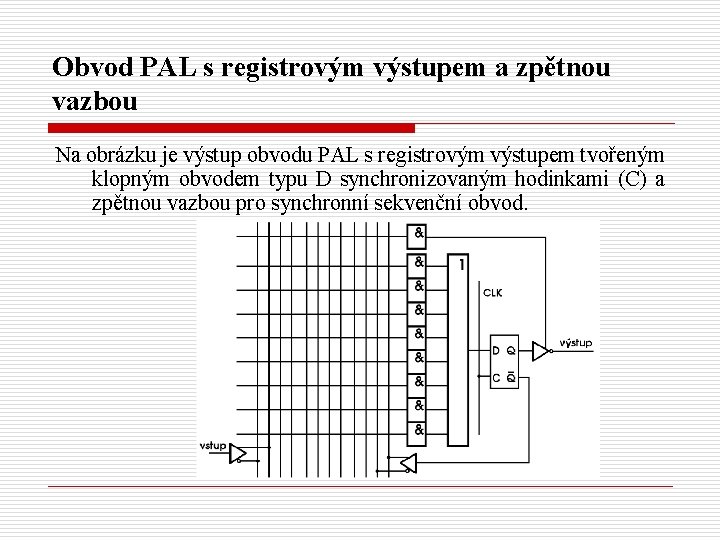

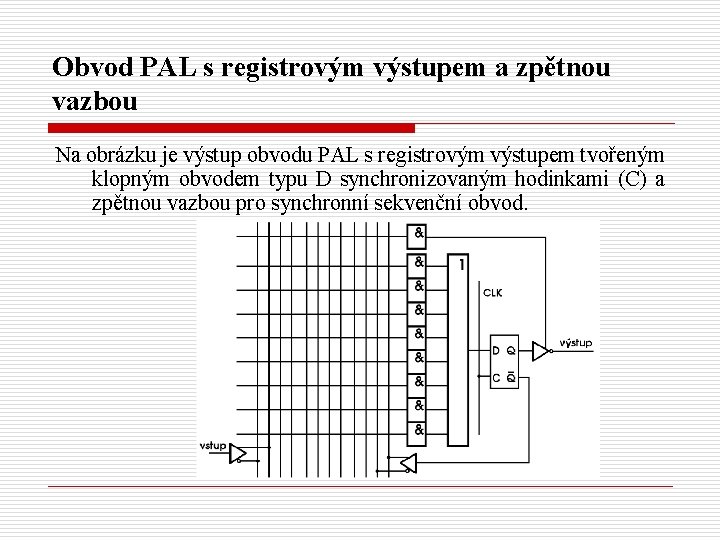

Obvod PAL s registrovým výstupem a zpětnou vazbou Na obrázku je výstup obvodu PAL s registrovým výstupem tvořeným klopným obvodem typu D synchronizovaným hodinkami (C) a zpětnou vazbou pro synchronní sekvenční obvod.

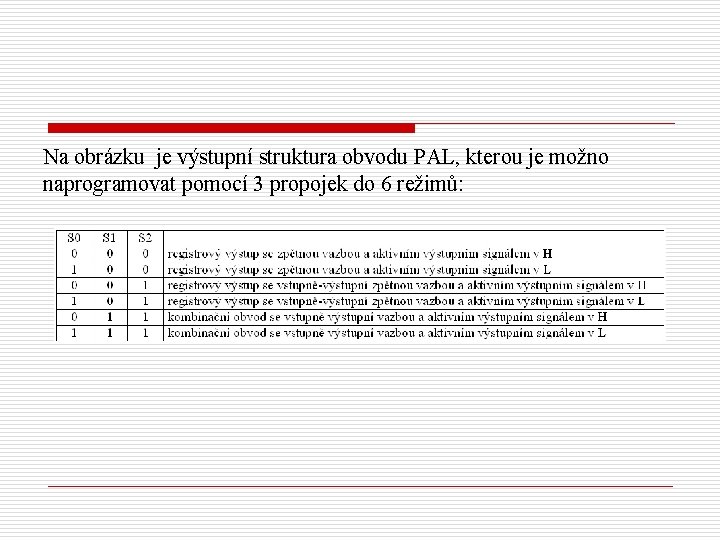

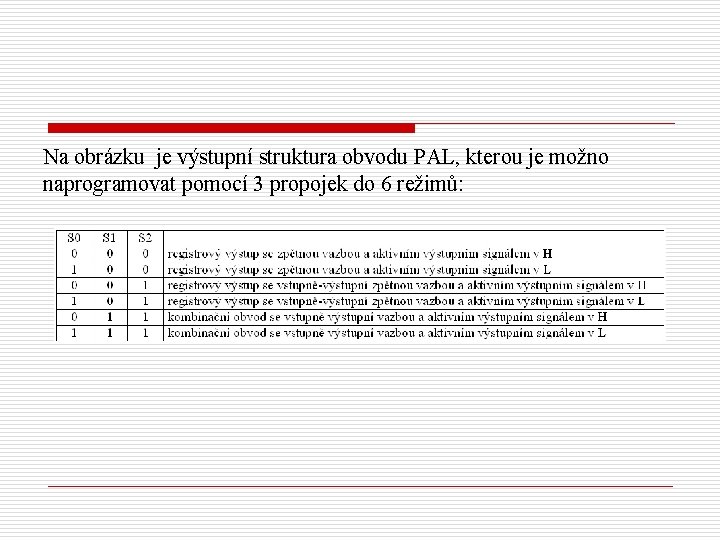

Na obrázku je výstupní struktura obvodu PAL, kterou je možno naprogramovat pomocí 3 propojek do 6 režimů:

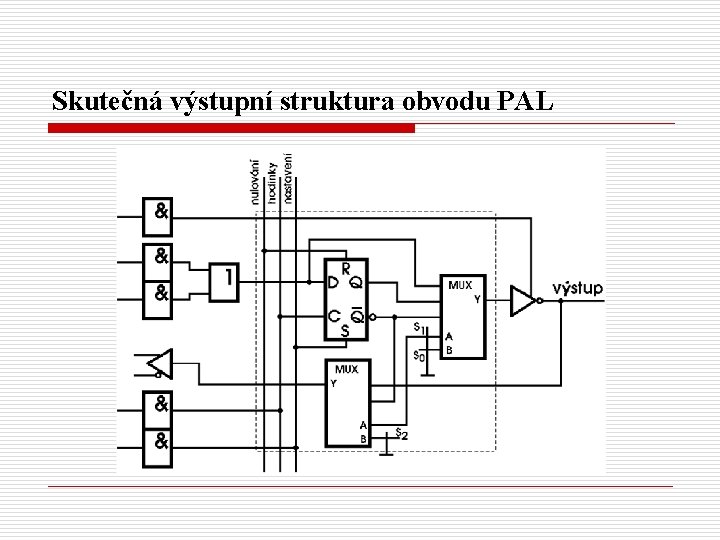

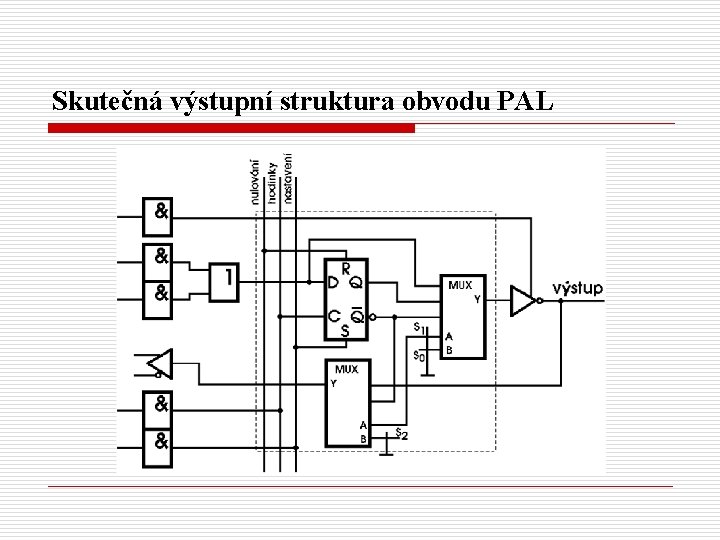

Skutečná výstupní struktura obvodu PAL

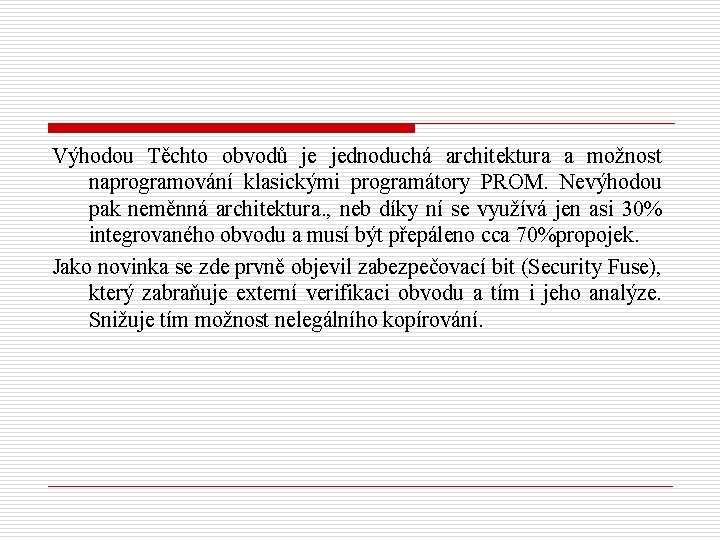

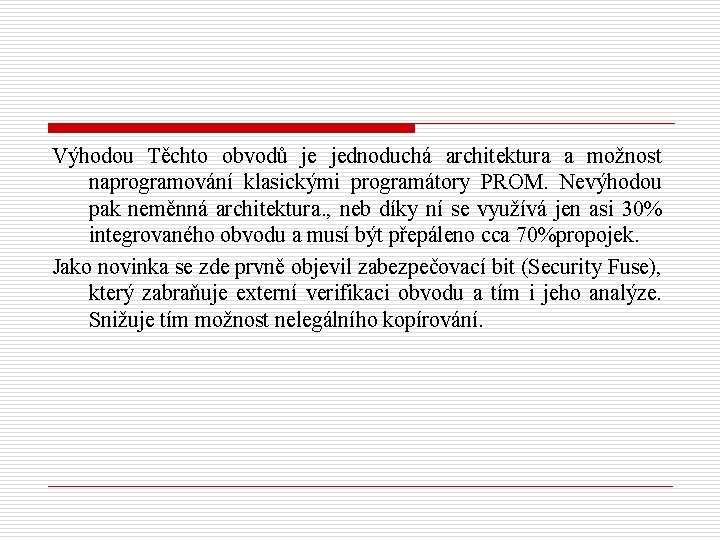

Výhodou Těchto obvodů je jednoduchá architektura a možnost naprogramování klasickými programátory PROM. Nevýhodou pak neměnná architektura. , neb díky ní se využívá jen asi 30% integrovaného obvodu a musí být přepáleno cca 70%propojek. Jako novinka se zde prvně objevil zabezpečovací bit (Security Fuse), který zabraňuje externí verifikaci obvodu a tím i jeho analýze. Snižuje tím možnost nelegálního kopírování.

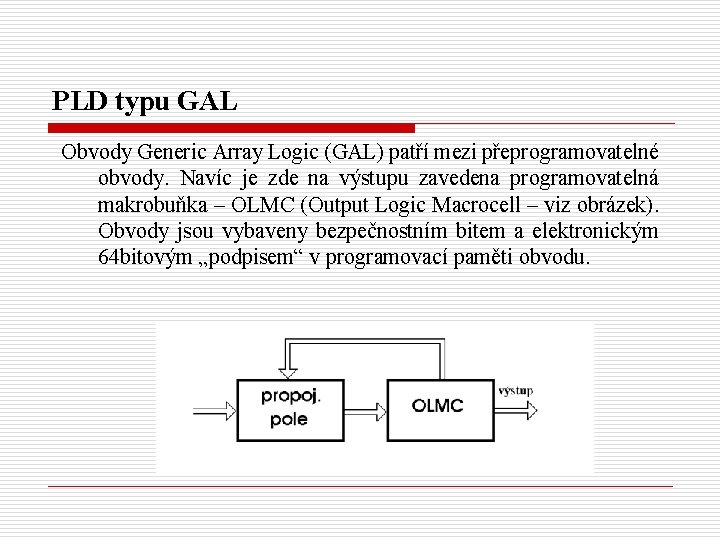

PLD typu GAL Obvody Generic Array Logic (GAL) patří mezi přeprogramovatelné obvody. Navíc je zde na výstupu zavedena programovatelná makrobuňka – OLMC (Output Logic Macrocell – viz obrázek). Obvody jsou vybaveny bezpečnostním bitem a elektronickým 64 bitovým „podpisem“ v programovací paměti obvodu.

Každá makrobuňka může být naprogramována do některého z následujících režimů : o kombinační výstup s programovatelnou výstupní polaritou o registrový výstup s programovatelnou výstupní polaritou o kombinační výstup s programovatelnou výstupní úrovní a zpětnou vazbou I/O o registrový výstup s programovatelnou výstupní úrovní a zpětnou vazbou I/O o kombinační výstup s registrovou zpětnou vazbou a aktivní úrovní L na výstupu o registrový vstup do pole AND-OR

Konfigurovatelná logická výstupní makrobuňka se nazývá OLMC (Output Logic Macrocell). Na všechna tyto makrobuňky je přiveden signál OE (Output Enable) – povolení výstupu signálu. Pokud není výstup signálu povolen, je vývod ve třetím stavu.

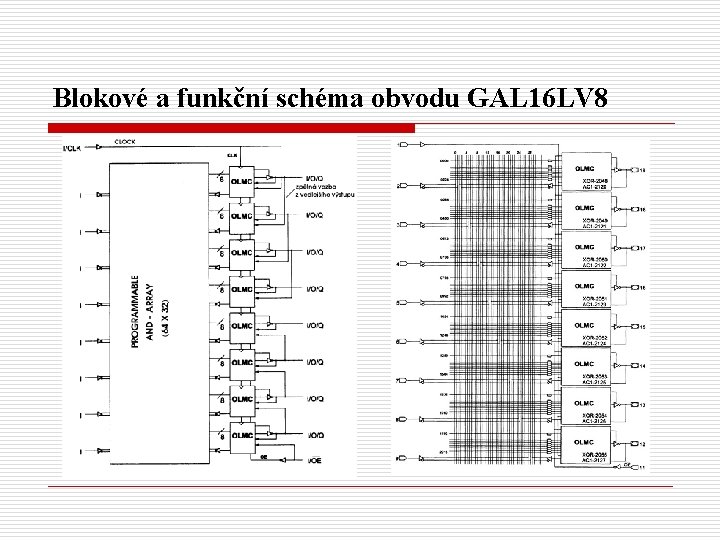

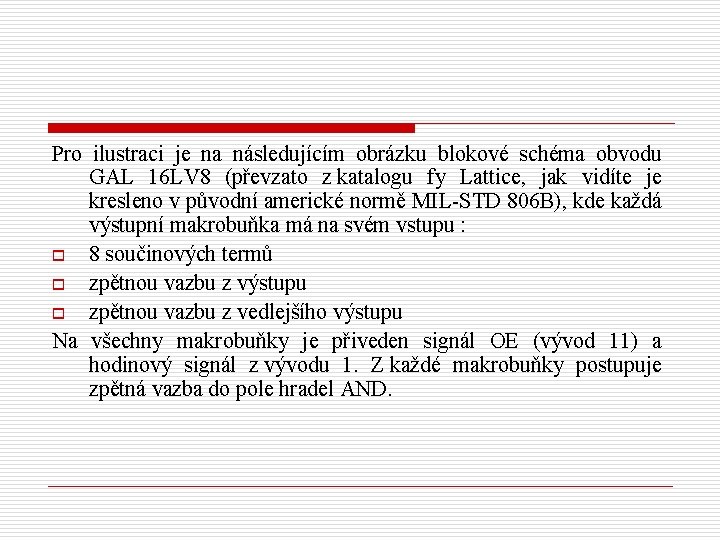

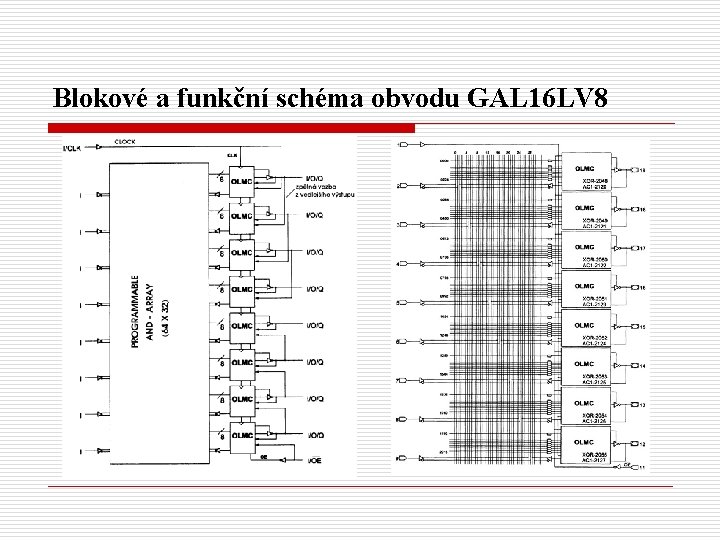

Pro ilustraci je na následujícím obrázku blokové schéma obvodu GAL 16 LV 8 (převzato z katalogu fy Lattice, jak vidíte je kresleno v původní americké normě MIL-STD 806 B), kde každá výstupní makrobuňka má na svém vstupu : o 8 součinových termů o zpětnou vazbu z výstupu o zpětnou vazbu z vedlejšího výstupu Na všechny makrobuňky je přiveden signál OE (vývod 11) a hodinový signál z vývodu 1. Z každé makrobuňky postupuje zpětná vazba do pole hradel AND.

Blokové a funkční schéma obvodu GAL 16 LV 8

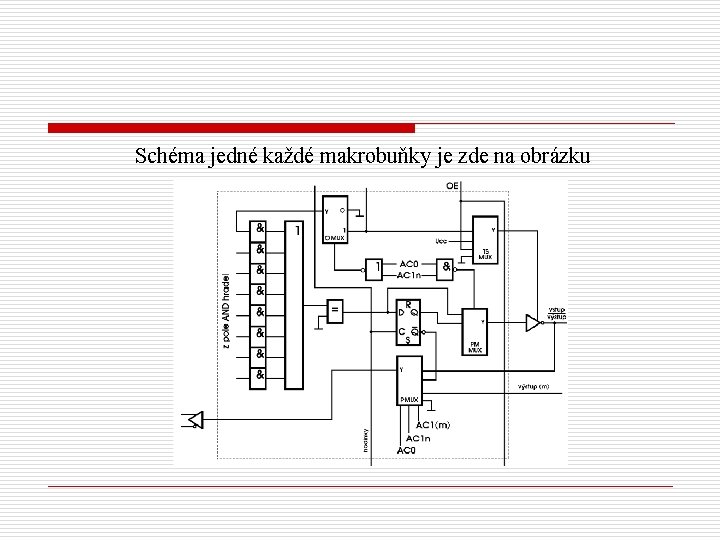

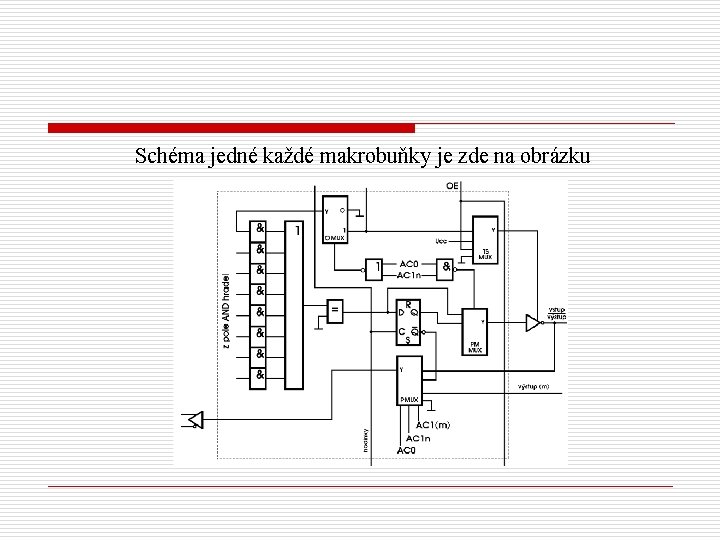

Schéma jedné každé makrobuňky je zde na obrázku

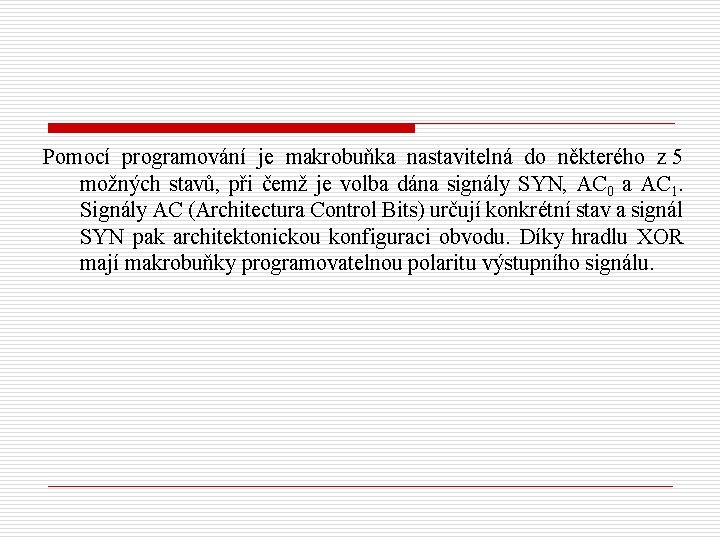

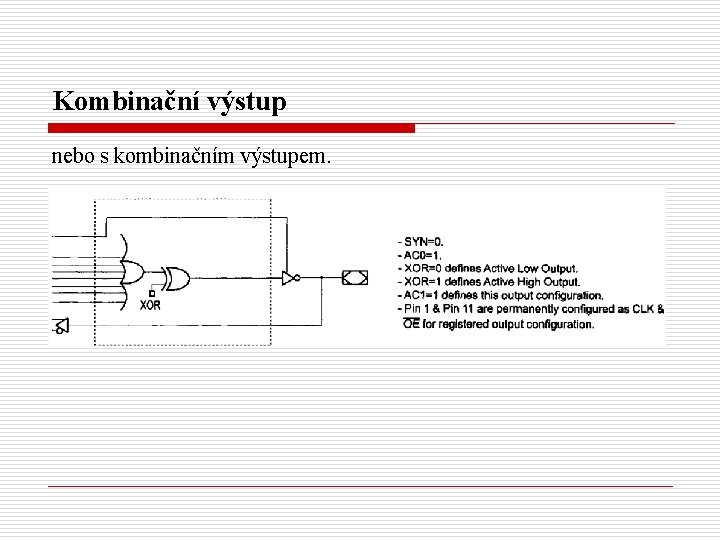

Pomocí programování je makrobuňka nastavitelná do některého z 5 možných stavů, při čemž je volba dána signály SYN, AC 0 a AC 1. Signály AC (Architectura Control Bits) určují konkrétní stav a signál SYN pak architektonickou konfiguraci obvodu. Díky hradlu XOR mají makrobuňky programovatelnou polaritu výstupního signálu.

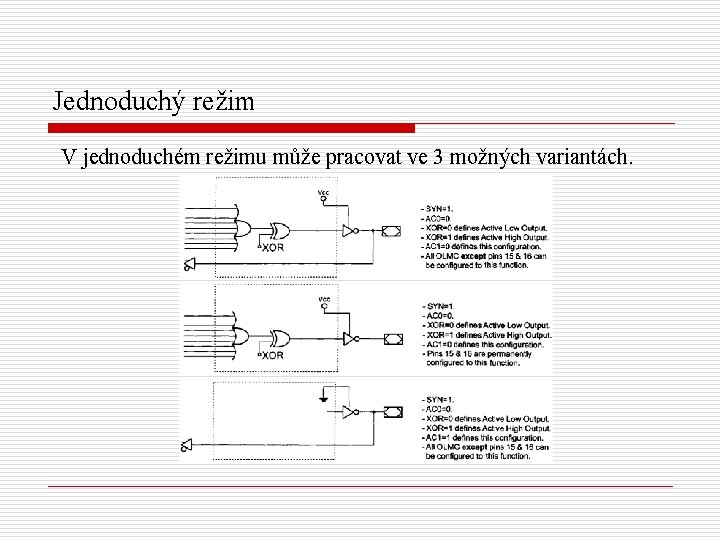

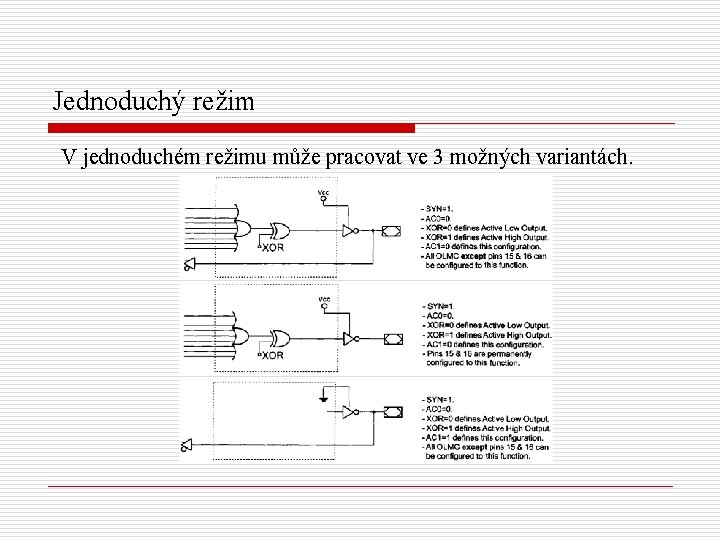

Jednoduchý režim V jednoduchém režimu může pracovat ve 3 možných variantách.

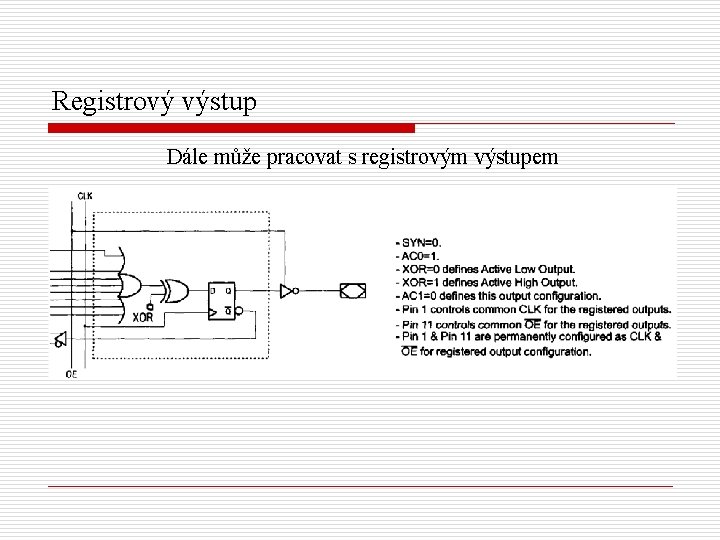

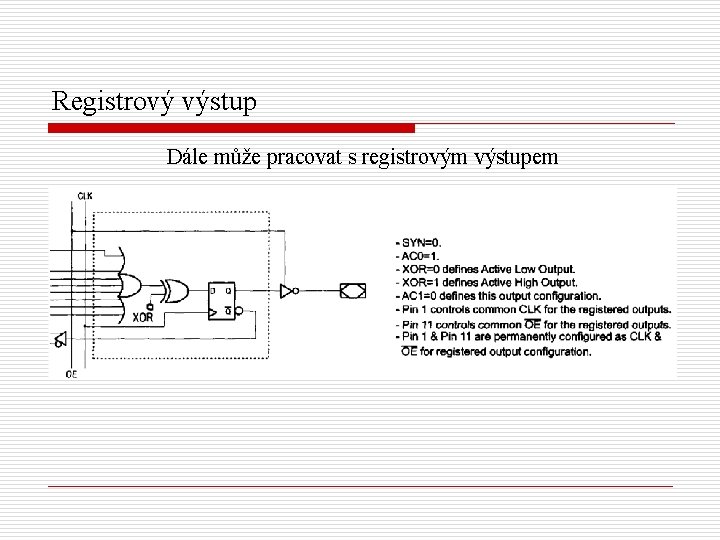

Registrový výstup Dále může pracovat s registrovým výstupem

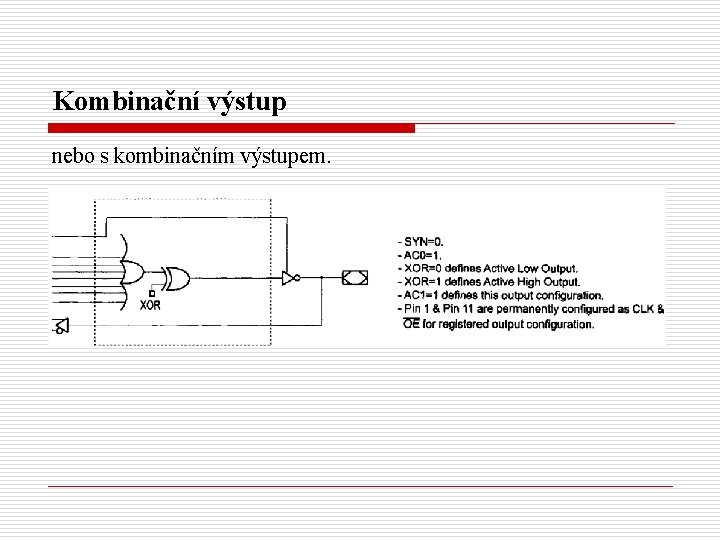

Kombinační výstup nebo s kombinačním výstupem.

PLD typu EPLD Obvody Erasable Programmable Logic Device jsou přeprogramovatelné obvody, které lze naprogramovat jako paměti EPROM a UV zářením mazat. Struktura je podobná jako u u obvodů PAL. Nový prvek je řízení architektury ACB (Architecture Control Block), což je zjednodušeně řečeno makrobuňka zodpovědná za nastavení potřebné konfigurace výstupní makrobuňky.

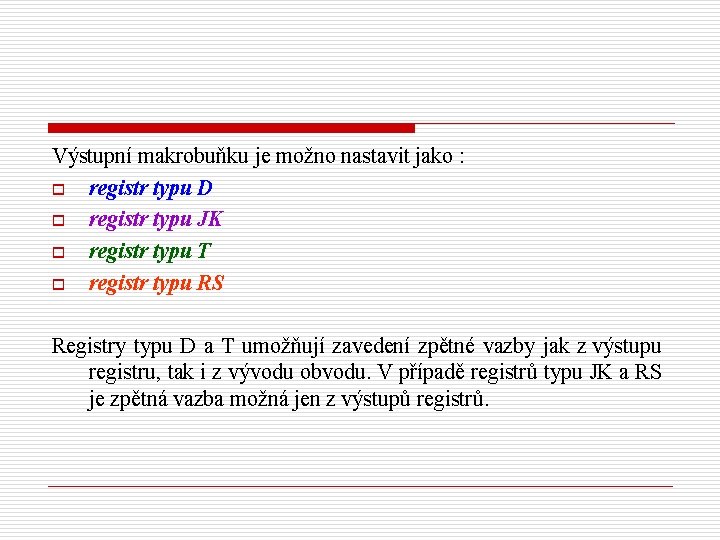

Výstupní makrobuňku je možno nastavit jako : o registr typu D o registr typu JK o registr typu T o registr typu RS Registry typu D a T umožňují zavedení zpětné vazby jak z výstupu registru, tak i z vývodu obvodu. V případě registrů typu JK a RS je zpětná vazba možná jen z výstupů registrů.

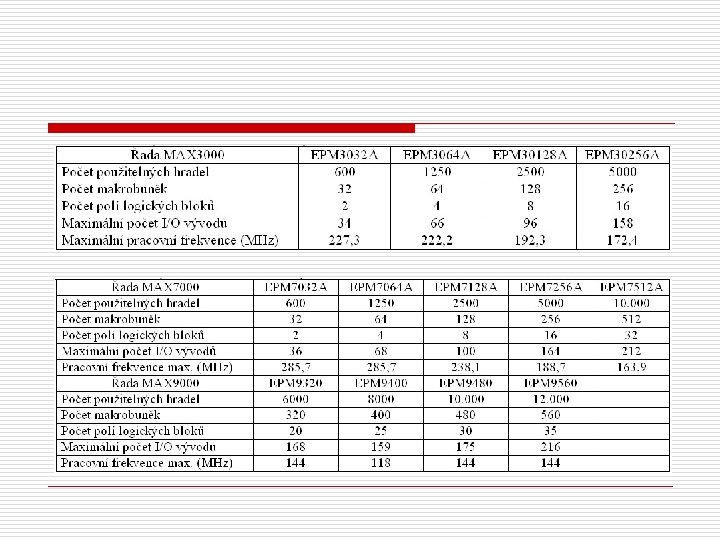

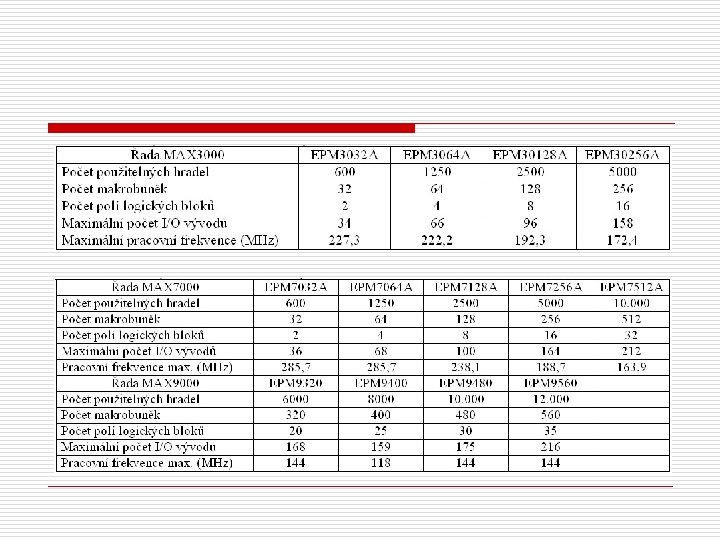

Typickým představitelem takovýchto obvodů jsou perspektivní obvody fy Altera, které budou dále vysvětleny. Nejprve však přiblížení možností těchto obvodů. Vezměme nejjednodušší obvody řady EPM 3032 A a porovnejme počty použitelných hradel a pracovní frekvence s možnostmi běžných číslicových obvodů. Zjistíme, že již i jednodušší zapojení z běžných číslicových obvodů lze 1 obvodem výhodně nahradit. Pokud bychom potřebovali větší množství použitelných hradel, pak lze použít i řady s většími možnostmi.

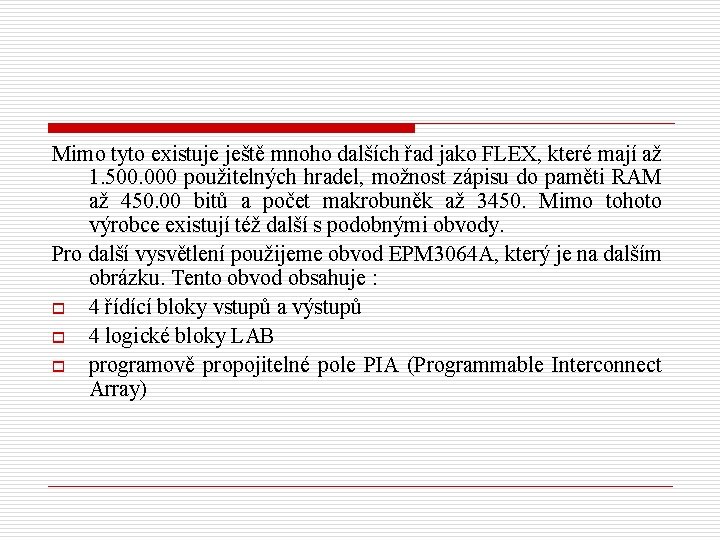

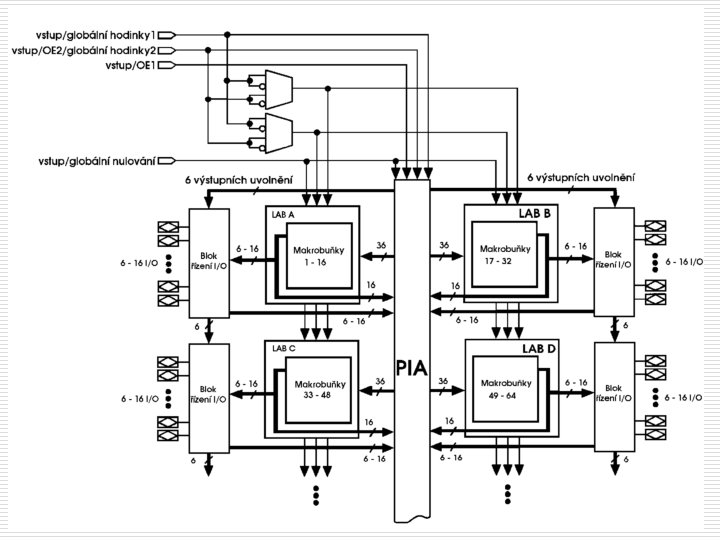

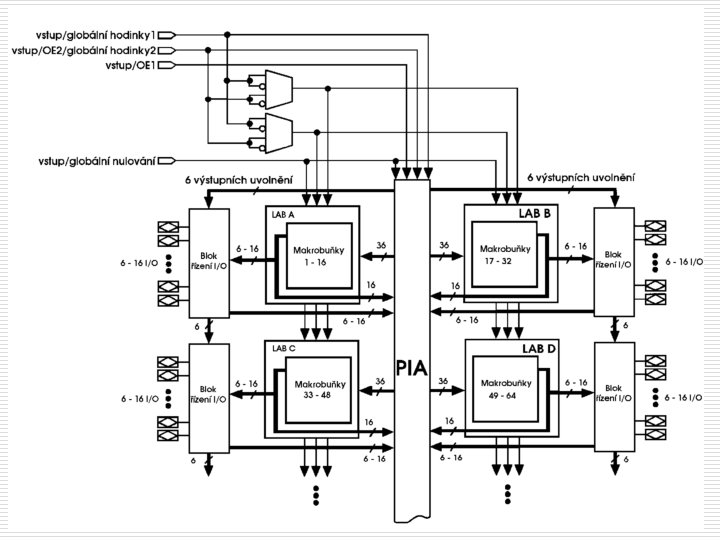

Mimo tyto existuje ještě mnoho dalších řad jako FLEX, které mají až 1. 500. 000 použitelných hradel, možnost zápisu do paměti RAM až 450. 00 bitů a počet makrobuněk až 3450. Mimo tohoto výrobce existují též další s podobnými obvody. Pro další vysvětlení použijeme obvod EPM 3064 A, který je na dalším obrázku. Tento obvod obsahuje : o 4 řídící bloky vstupů a výstupů o 4 logické bloky LAB o programově propojitelné pole PIA (Programmable Interconnect Array)

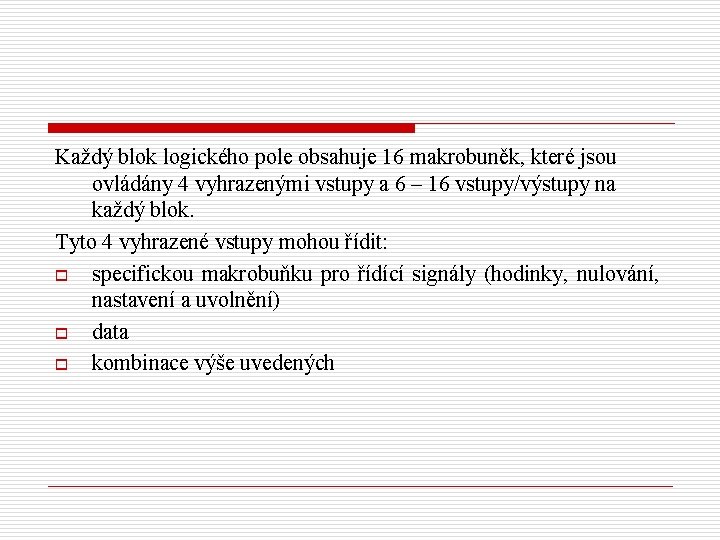

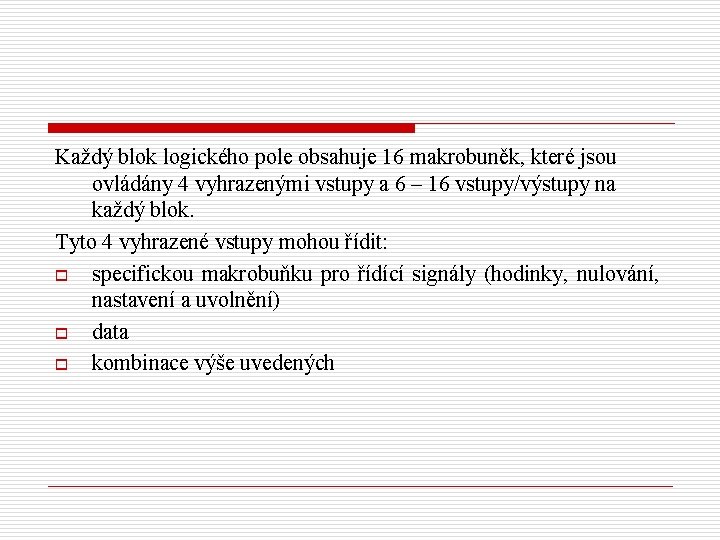

Každý blok logického pole obsahuje 16 makrobuněk, které jsou ovládány 4 vyhrazenými vstupy a 6 – 16 vstupy/výstupy na každý blok. Tyto 4 vyhrazené vstupy mohou řídit: o specifickou makrobuňku pro řídící signály (hodinky, nulování, nastavení a uvolnění) o data o kombinace výše uvedených

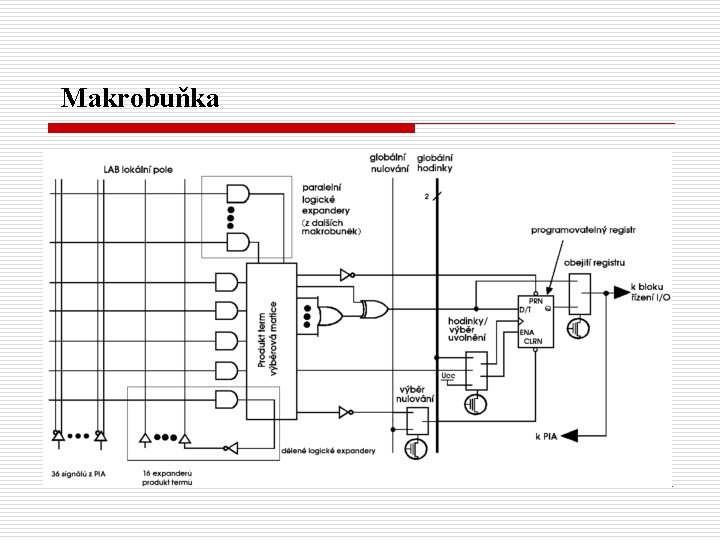

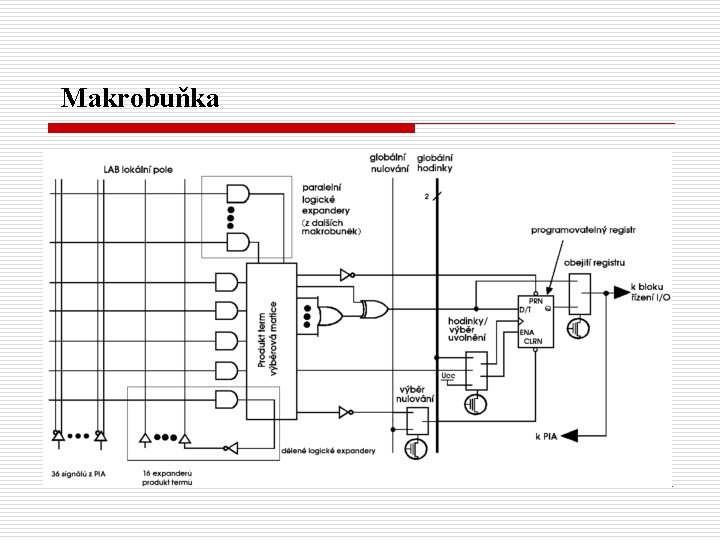

Makrobuňka

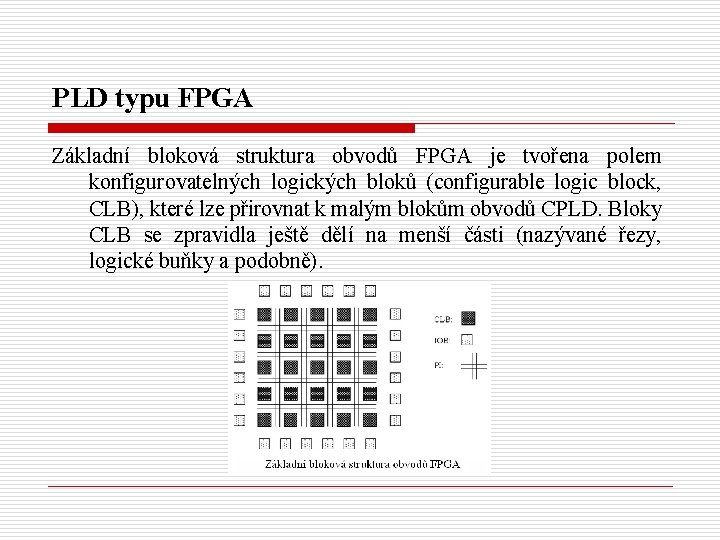

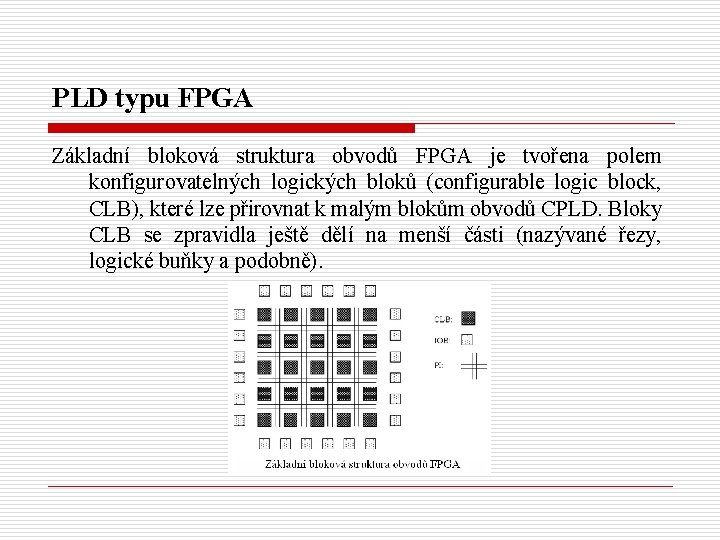

PLD typu FPGA Základní bloková struktura obvodů FPGA je tvořena polem konfigurovatelných logických bloků (configurable logic block, CLB), které lze přirovnat k malým blokům obvodů CPLD. Bloky CLB se zpravidla ještě dělí na menší části (nazývané řezy, logické buňky a podobně).

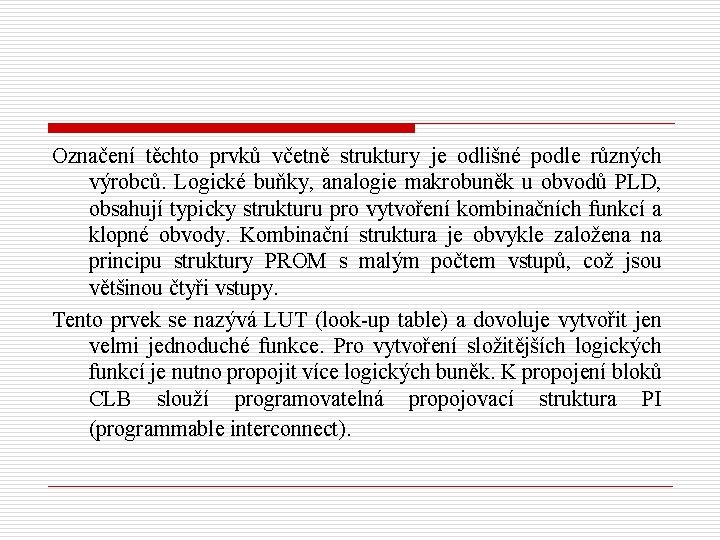

Označení těchto prvků včetně struktury je odlišné podle různých výrobců. Logické buňky, analogie makrobuněk u obvodů PLD, obsahují typicky strukturu pro vytvoření kombinačních funkcí a klopné obvody. Kombinační struktura je obvykle založena na principu struktury PROM s malým počtem vstupů, což jsou většinou čtyři vstupy. Tento prvek se nazývá LUT (look-up table) a dovoluje vytvořit jen velmi jednoduché funkce. Pro vytvoření složitějších logických funkcí je nutno propojit více logických buněk. K propojení bloků CLB slouží programovatelná propojovací struktura PI (programmable interconnect).

Pole bloků CLB je obklopeno vstupně/výstupními bloky (input/output block, IOB), které zajišťují podobné funkce jako vstupní a výstupní zesilovače obvodů PLD. Obvykle také obsahují klopné obvody, nikoli však kombinační logiku. Jsou připojeny k vývodům obvodu FPGA a jejich úkolem je propojení vnějších signálů se signály v poli bloků CLB.

Mimo logických buněk, které jsou základními univerzálními prvky, obsahují bloky CLB ještě specializované prvky sloužící ke snadnějšímu a efektivnímu vytvoření často používaných zapojení. Jedná se hlavně o multiplexory používané jako spínače ppro propojování logických buněk do celků. Dále mají obvody FPGA vytvořeny struktury pro použití většího množství hodinových signálů, speciální struktury pro generování rychlého přenosového signálu u sčítaček a jiné.

V poli bloků CLB jsou též rozmístěny další bloky, které nejsou pro jednoduchost nakresleny. Jedné se například o bloky pro zpracování a úpravu hodinových signálů, hardwarové násobičky, blokové paměti RAM/ROM, struktury pro rychlou sériovou komunikaci včetně procesorových jader Power PC. Má-li být konstruktér schopen všechny tyto vlastnosti obvodů FPGA využít, musí mít dostatek znalostí o nich. Z toho, co bylo uvedeno vyplývá, že s výjimkou nejjednodušších funkcí je každá funkce vytvořena v této struktuře svým vlastním specifickým propojením celé řady logických buněk, a to na rozdíl od obvodů PLD, kde i funkce střední složitosti bývají implementovány do jedné makrobuňky.

Výběr obvodů FPGA Výběr FPGA obvodu pro konkrétní aplikaci není vůbec jednoduchým úkolem. Proto jsou zde shrnuta kriteria, které by jste měli při výběru obvodu brát v potaz: o účel pro který tyto obvody chceme použít (řídící funkce, pro výpořet aj. ). Řada výrobců vyrábí svoje obvody v různých řadách podle charakteru použití – i stejně velká FPGA se pak liší v počtech integrovaných násobiček, pamětí, atd. o velikost a rychlost budoucího obvodu (potřebná hodinová frekvence). Výrobci obvodů vštšinou uvádí u svých produktů velikost hradlového pole v tzv. ekvivalentních hradlech pro odhad, zda je pro daný účel obvod použitelný. Toto číslo je nicméně nutno brát s rezervou, protože udávané hodnoty jednotlivých výrobců nelze srovnávat a to ani u produktů od jednoho výrobce. To samé se týké i ryhlosti obvodů.

o o o počet vstupních a výstupních signálů – počet potřebných I/O linek obvodu implementovaného do FPGA je třeba zohlednit při volbě vhodného pouzdra obvodu. spolehlivost finální aplikace (rozsah okolních teplot, přepěťovou odolnost, rušení). možnost rekonfigurace zařízení. startup time aplikace, a to pokud chceme, aby systém byl plně funkční hned po zapnutí napájecího napětí, pak nelze použít obvody SRAM FPGA. spotřeba energie. Se spotřebou energie souvisí i teplo vyzářené obvodem během normální práce systému. Podle množství uvolňovaného tepla a prostorových nároků aplikace je třeba zvolit vhodné pouzdro obvodu FPGA , případně navrhnout i dodatečné chlazení. zabezpečení duševního vlastnictví.

Návrh obvodů s FPGA V počátcích programovatelných obvodů se pro návrh používaly proprietární jazyky (např. ABEL) či kreslení schemat. Dnes je standardem pro návrh FPGA obvodů použití příslušného jazyka pro popis hardware (HDL, Hardware Description Language) na RTL úrovni (Register Transfer Level). Pro popis se používají nejčastěji dva jazyky – buď VHDL, nebo Verilog.