MOS FieldEffect Transistors MOSFETs Microelectronic Circuits Fifth Edition

- Slides: 110

MOS Field-Effect Transistors (MOSFETs) Microelectronic Circuits - Fifth Edition Sedra/Smith 1

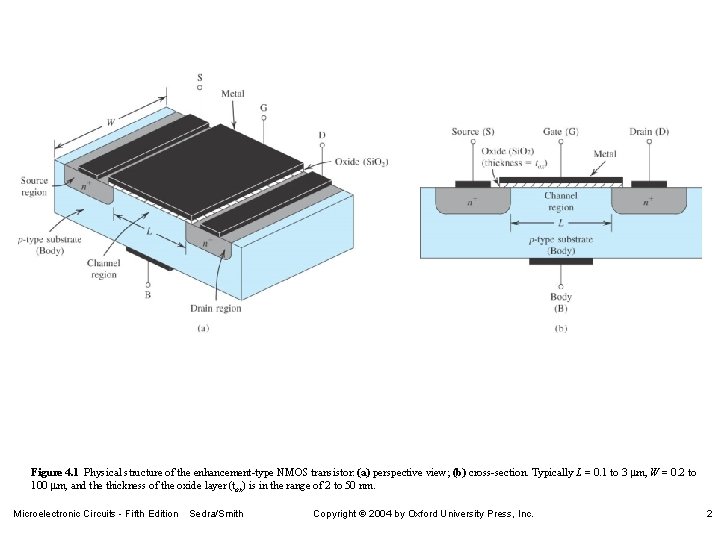

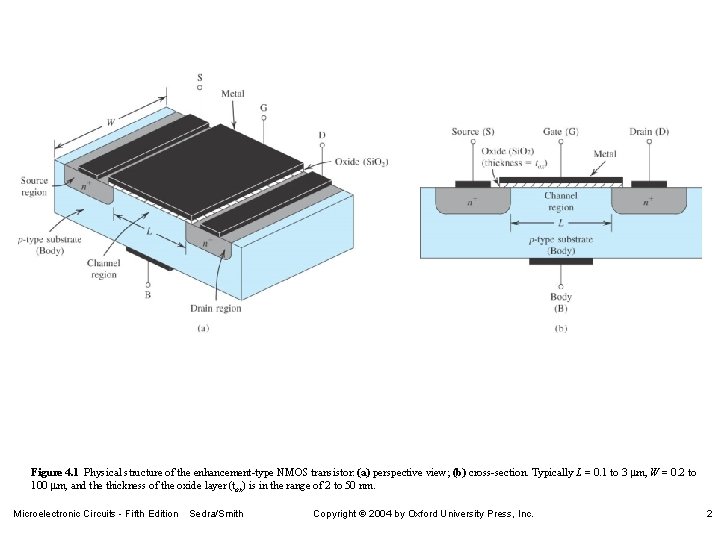

Figure 4. 1 Physical structure of the enhancement-type NMOS transistor: (a) perspective view; (b) cross-section. Typically L = 0. 1 to 3 mm, W = 0. 2 to 100 mm, and the thickness of the oxide layer (tox) is in the range of 2 to 50 nm. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 2

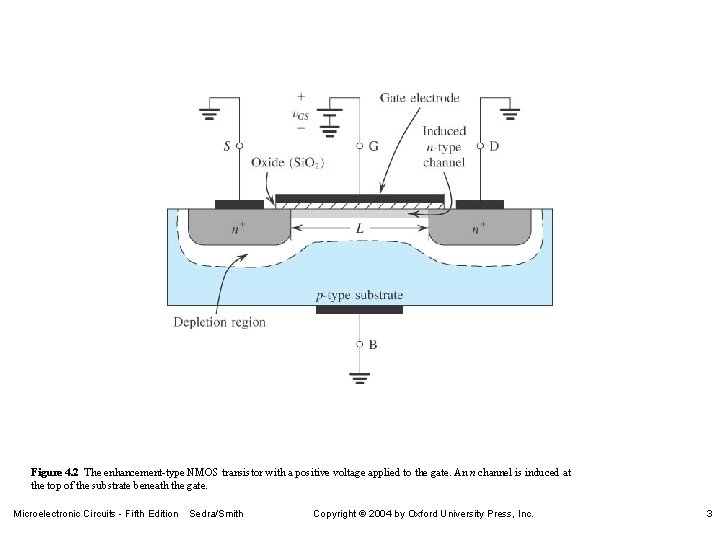

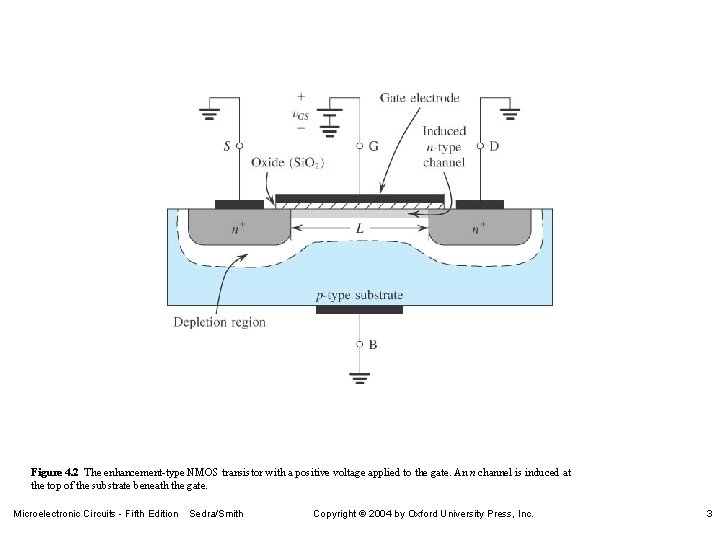

Figure 4. 2 The enhancement-type NMOS transistor with a positive voltage applied to the gate. An n channel is induced at the top of the substrate beneath the gate. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 3

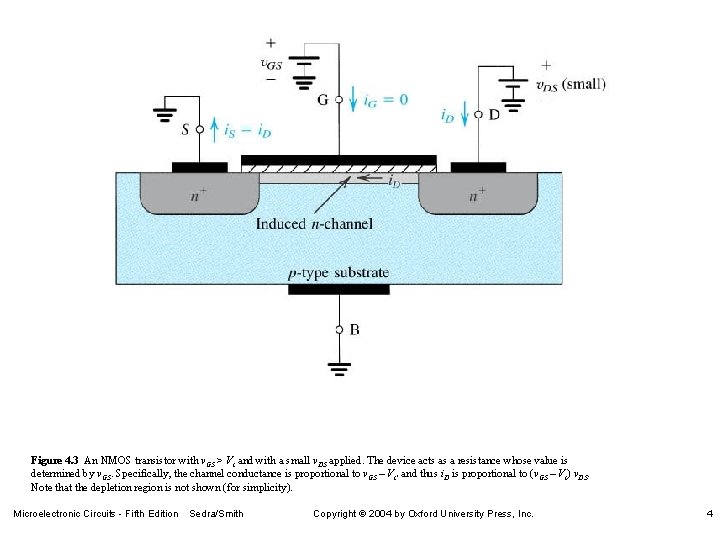

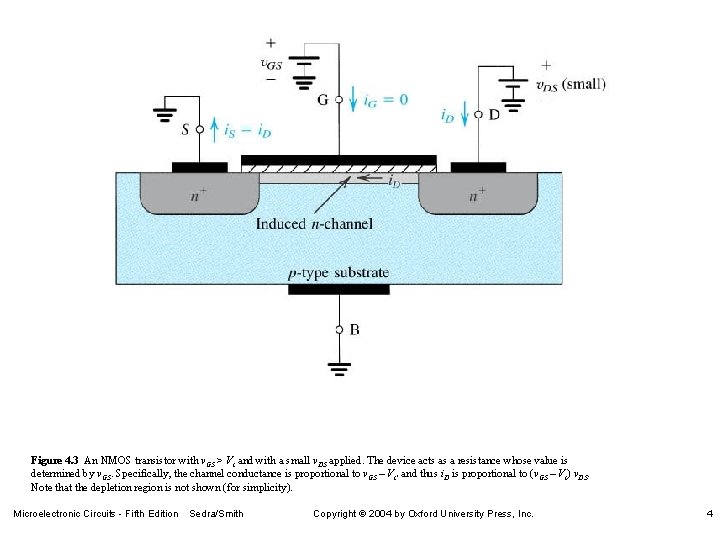

Figure 4. 3 An NMOS transistor with v. GS > Vt and with a small v. DS applied. The device acts as a resistance whose value is determined by v. GS. Specifically, the channel conductance is proportional to v. GS – Vt’ and thus i. D is proportional to (v. GS – Vt) v. DS. Note that the depletion region is not shown (for simplicity). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 4

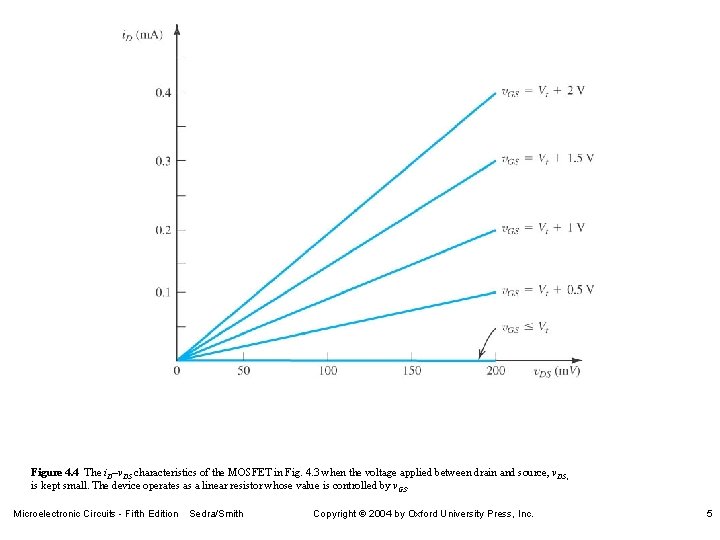

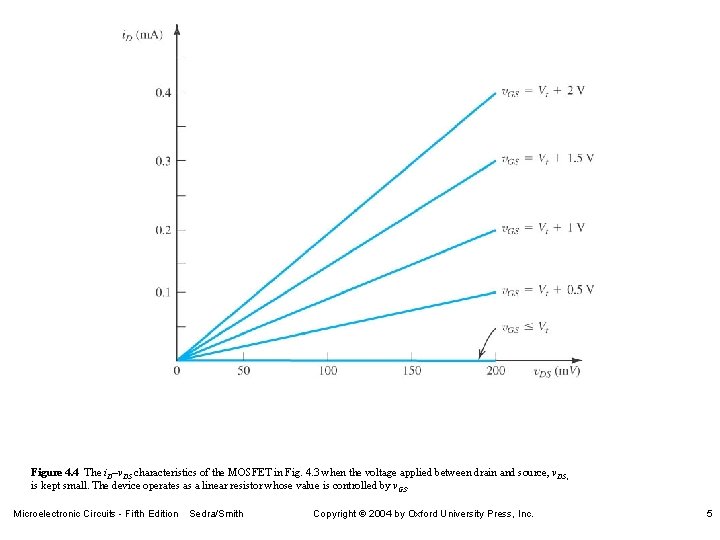

Figure 4. 4 The i. D–v. DS characteristics of the MOSFET in Fig. 4. 3 when the voltage applied between drain and source, v. DS, is kept small. The device operates as a linear resistor whose value is controlled by v. GS. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 5

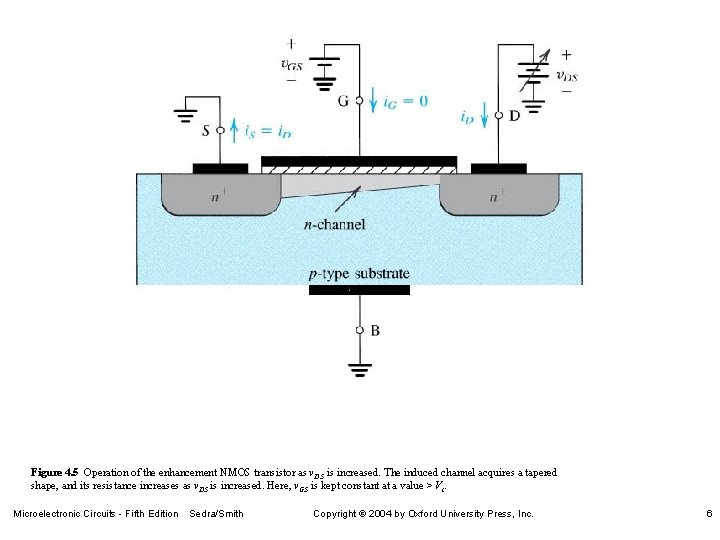

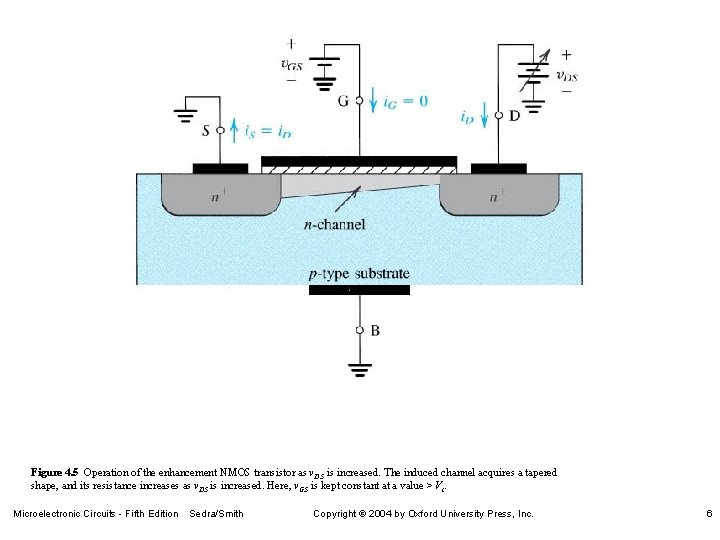

Figure 4. 5 Operation of the enhancement NMOS transistor as v. DS is increased. The induced channel acquires a tapered shape, and its resistance increases as v. DS is increased. Here, v. GS is kept constant at a value > Vt. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 6

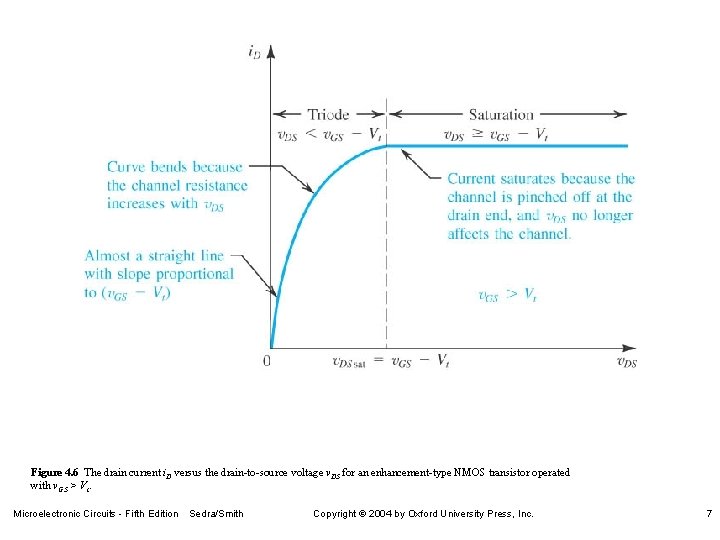

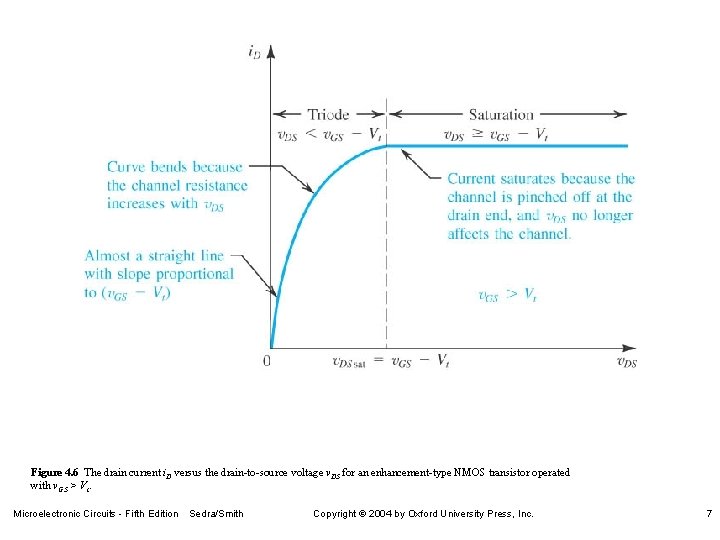

Figure 4. 6 The drain current i. D versus the drain-to-source voltage v. DS for an enhancement-type NMOS transistor operated with v. GS > Vt. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 7

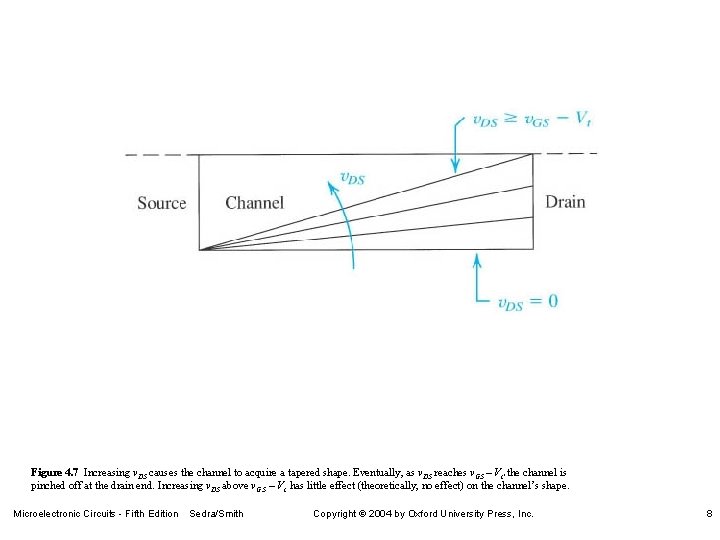

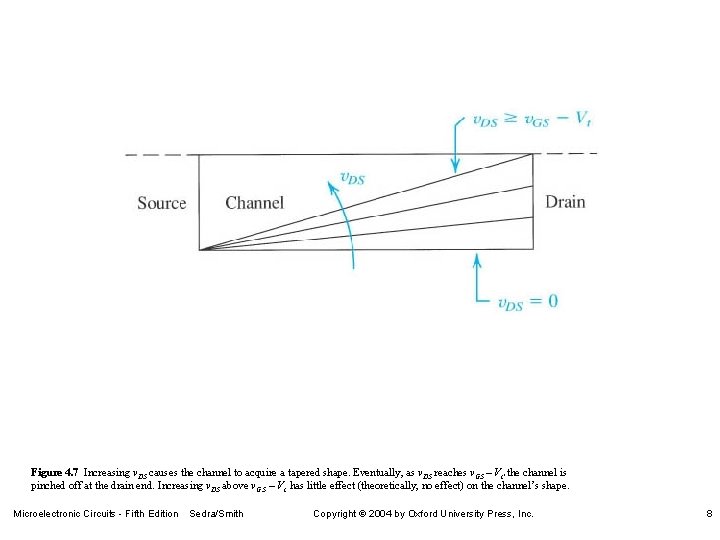

Figure 4. 7 Increasing v. DS causes the channel to acquire a tapered shape. Eventually, as v. DS reaches v. GS – Vt’ the channel is pinched off at the drain end. Increasing v. DS above v. GS – Vt has little effect (theoretically, no effect) on the channel’s shape. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 8

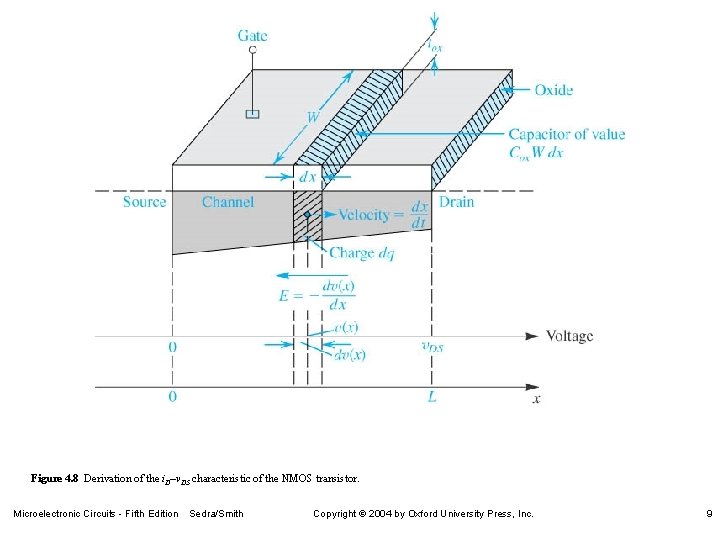

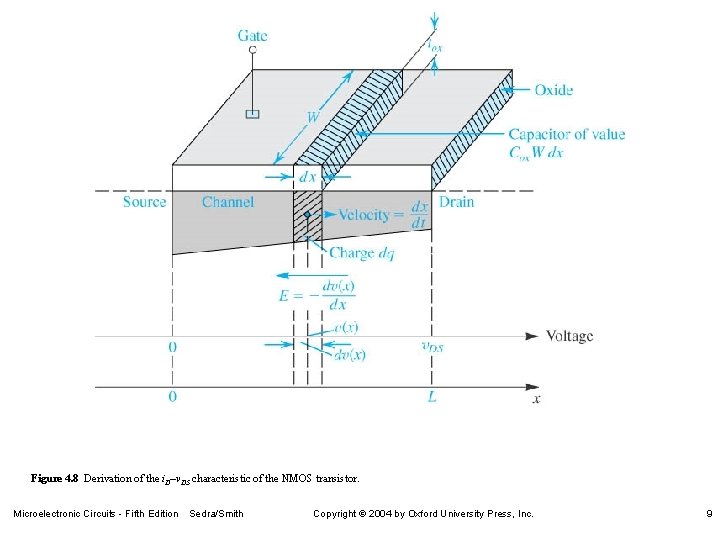

Figure 4. 8 Derivation of the i. D–v. DS characteristic of the NMOS transistor. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 9

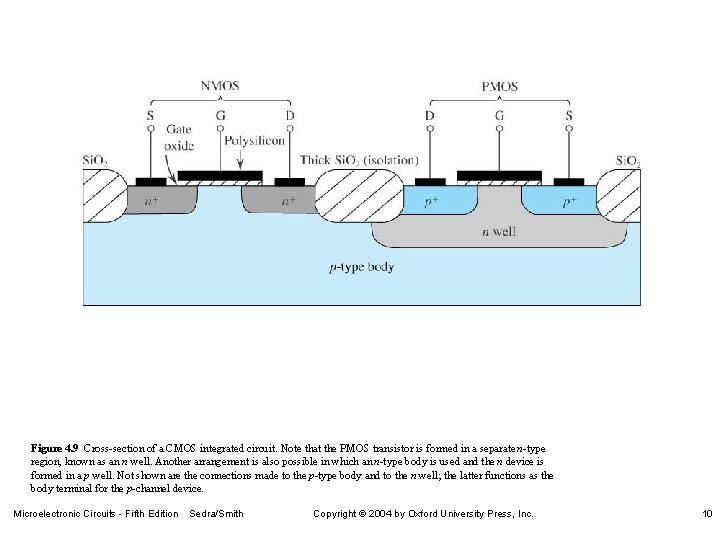

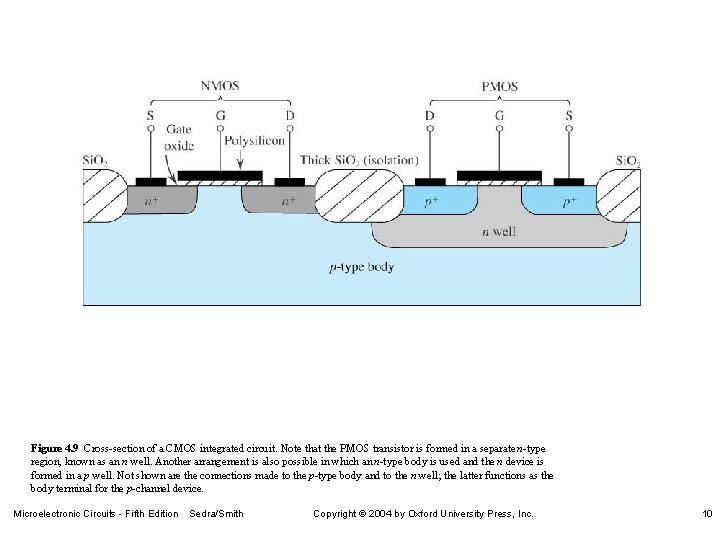

Figure 4. 9 Cross-section of a CMOS integrated circuit. Note that the PMOS transistor is formed in a separate n-type region, known as an n well. Another arrangement is also possible in which an n-type body is used and the n device is formed in a p well. Not shown are the connections made to the p-type body and to the n well; the latter functions as the body terminal for the p-channel device. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 10

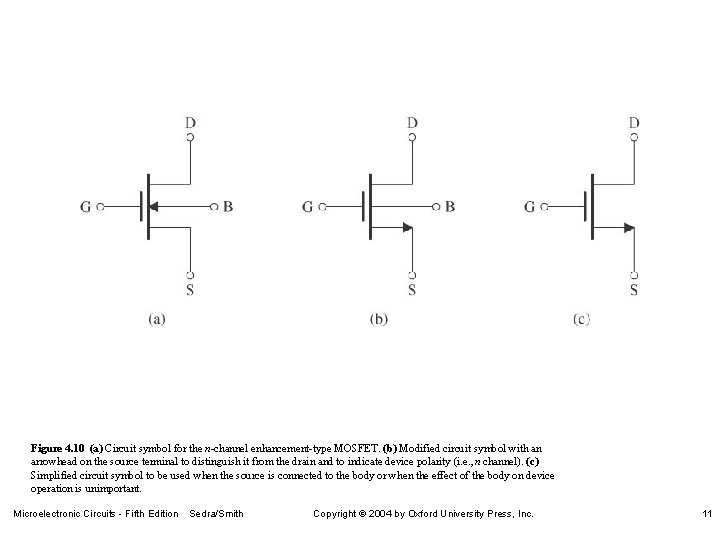

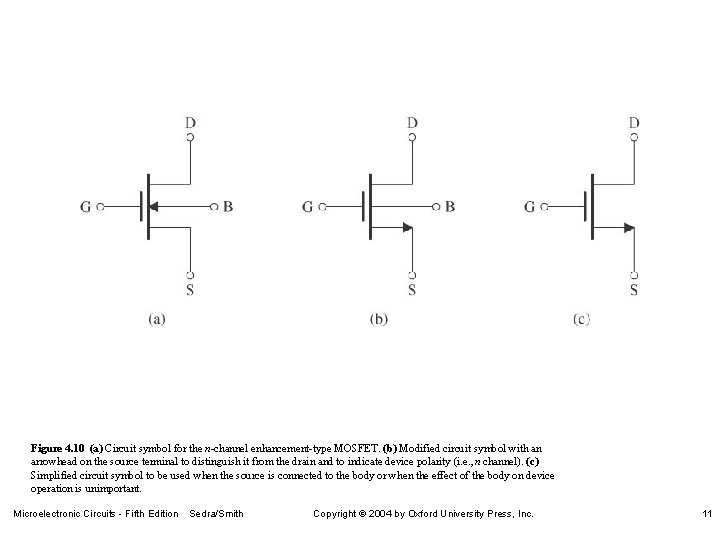

Figure 4. 10 (a) Circuit symbol for the n-channel enhancement-type MOSFET. (b) Modified circuit symbol with an arrowhead on the source terminal to distinguish it from the drain and to indicate device polarity (i. e. , n channel). (c) Simplified circuit symbol to be used when the source is connected to the body or when the effect of the body on device operation is unimportant. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 11

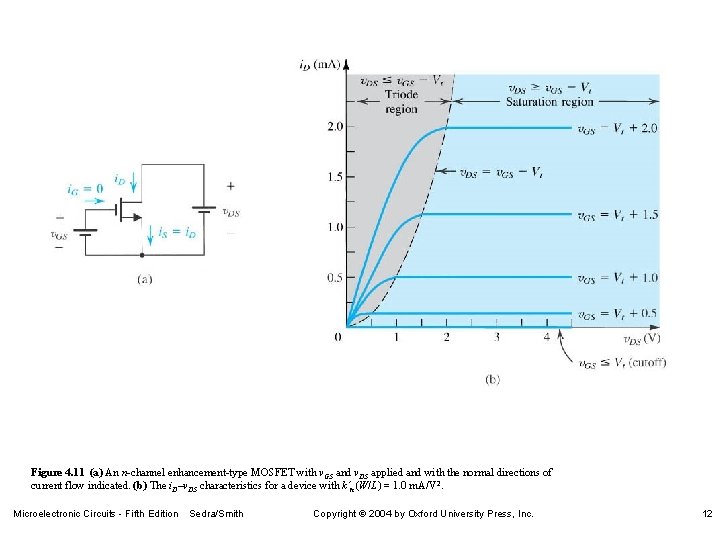

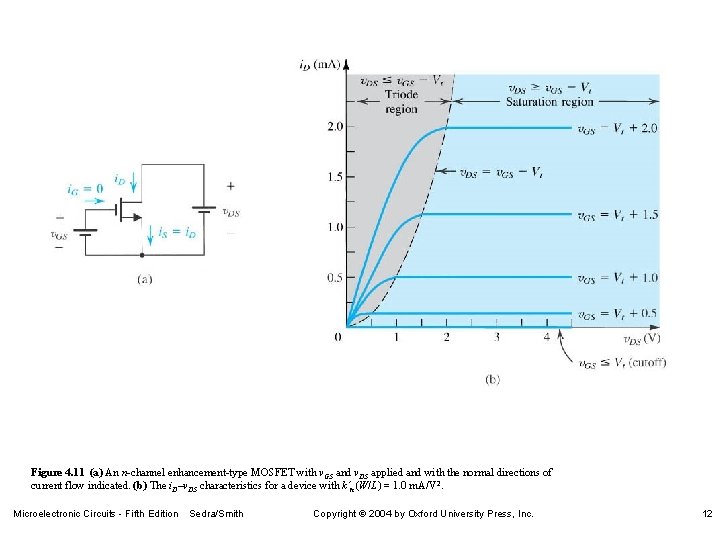

Figure 4. 11 (a) An n-channel enhancement-type MOSFET with v. GS and v. DS applied and with the normal directions of current flow indicated. (b) The i. D–v. DS characteristics for a device with k’n (W/L) = 1. 0 m. A/V 2. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 12

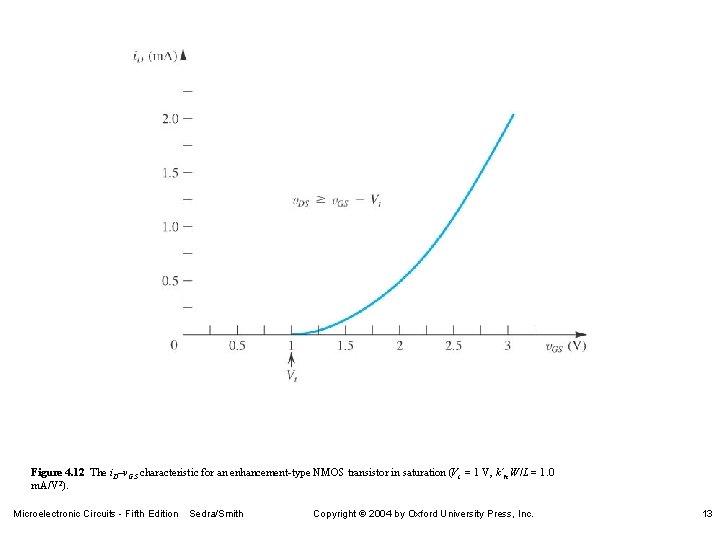

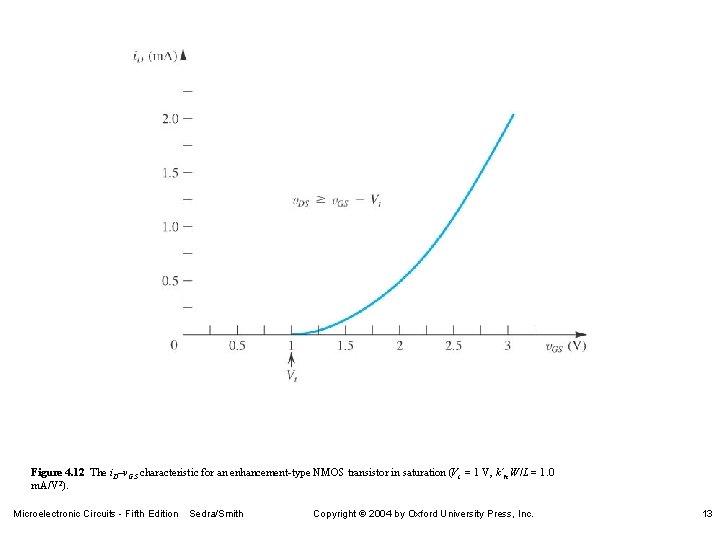

Figure 4. 12 The i. D–v. GS characteristic for an enhancement-type NMOS transistor in saturation (Vt = 1 V, k’n W/L = 1. 0 m. A/V 2). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 13

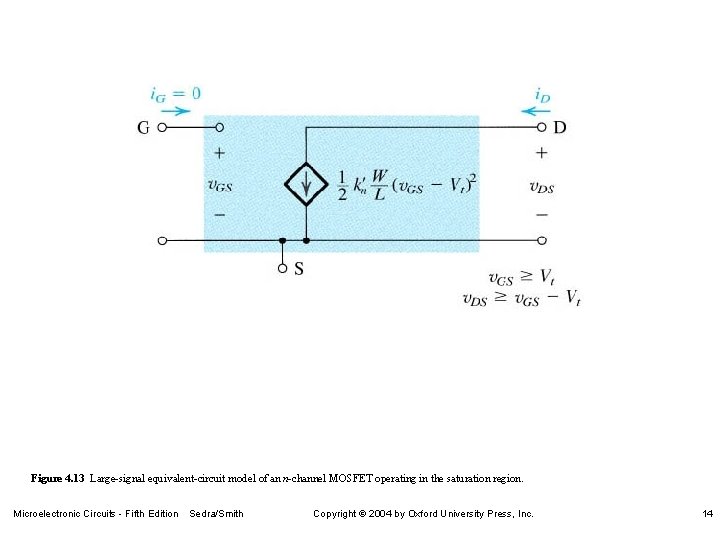

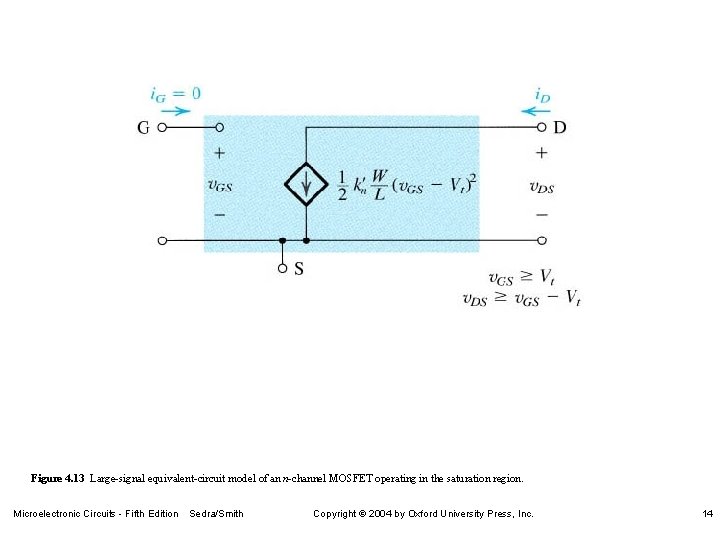

Figure 4. 13 Large-signal equivalent-circuit model of an n-channel MOSFET operating in the saturation region. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 14

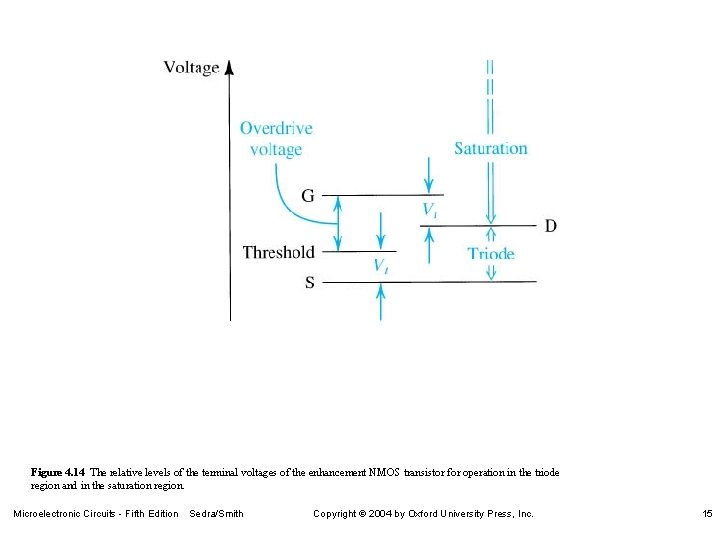

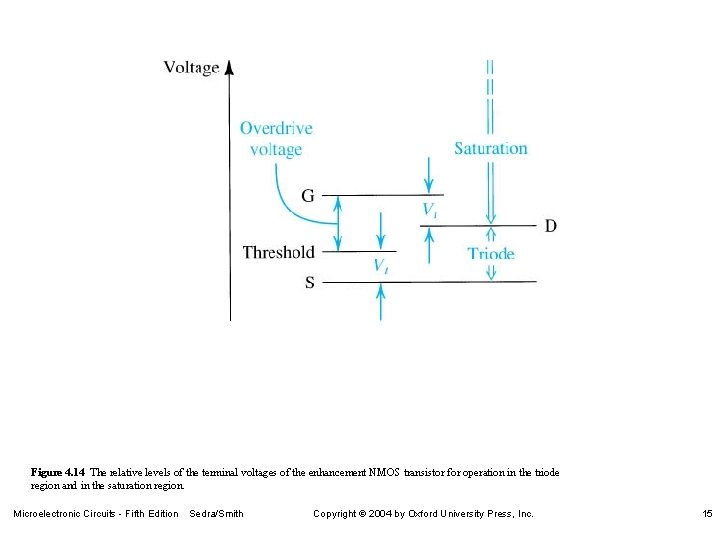

Figure 4. 14 The relative levels of the terminal voltages of the enhancement NMOS transistor for operation in the triode region and in the saturation region. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 15

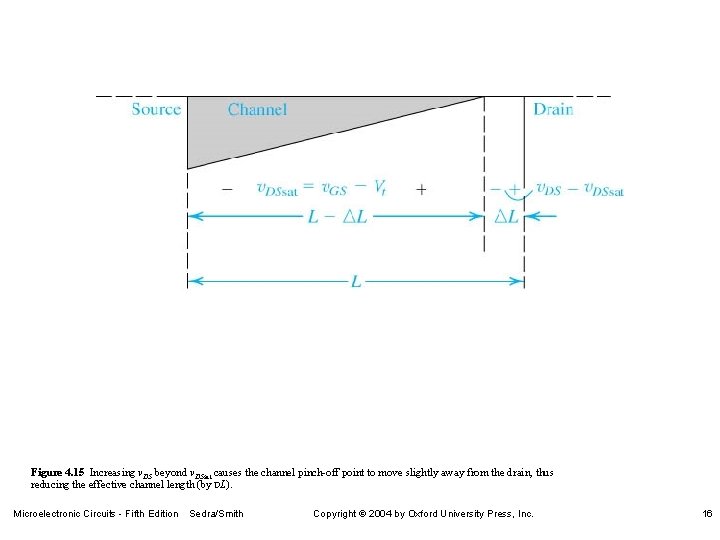

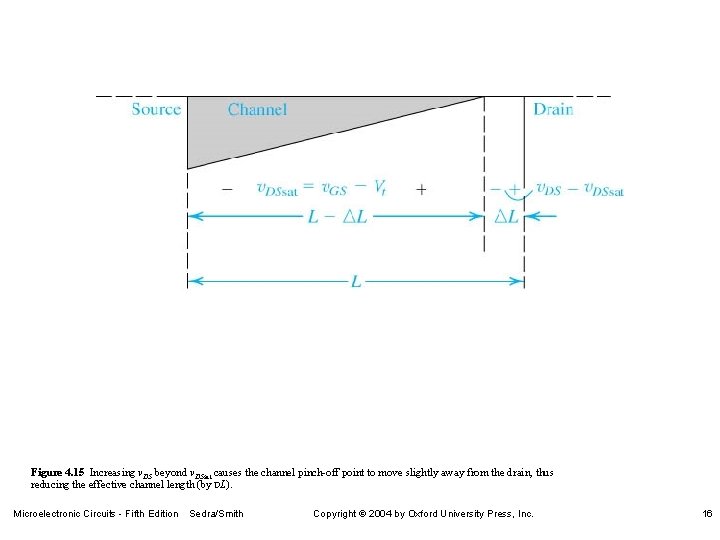

Figure 4. 15 Increasing v. DS beyond v. DSsat causes the channel pinch-off point to move slightly away from the drain, thus reducing the effective channel length (by DL). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 16

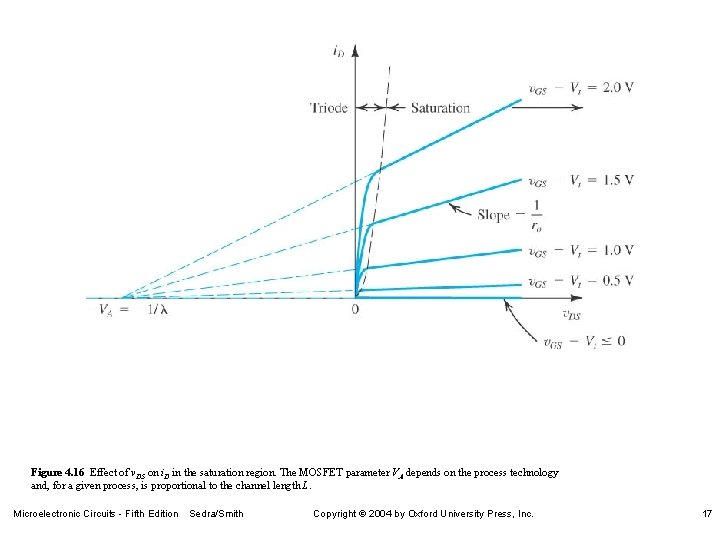

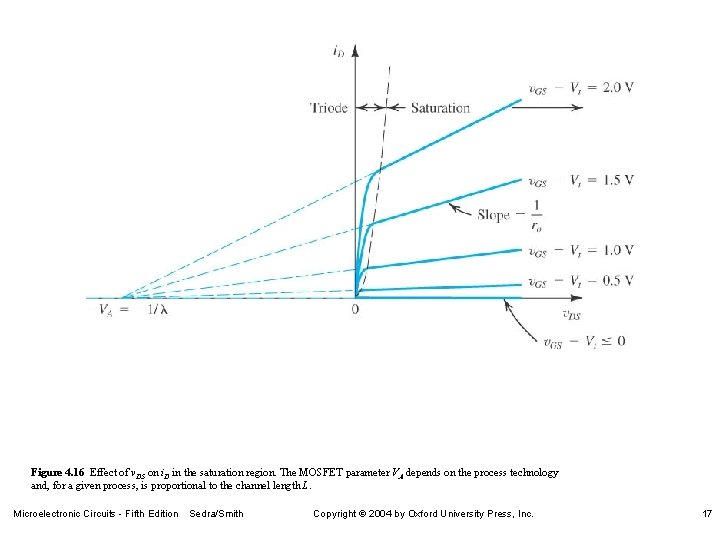

Figure 4. 16 Effect of v. DS on i. D in the saturation region. The MOSFET parameter VA depends on the process technology and, for a given process, is proportional to the channel length L. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 17

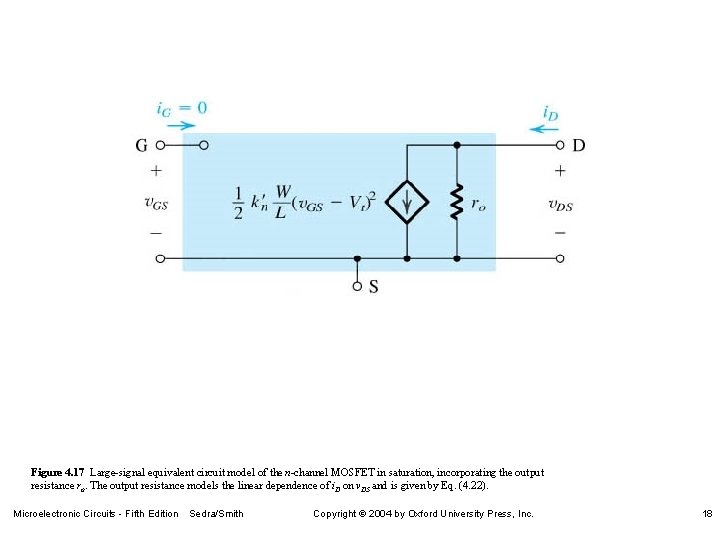

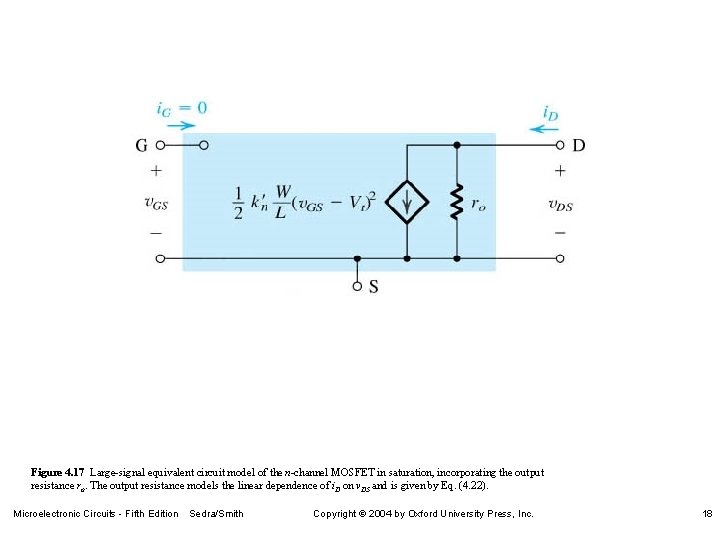

Figure 4. 17 Large-signal equivalent circuit model of the n-channel MOSFET in saturation, incorporating the output resistance ro. The output resistance models the linear dependence of i. D on v. DS and is given by Eq. (4. 22). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 18

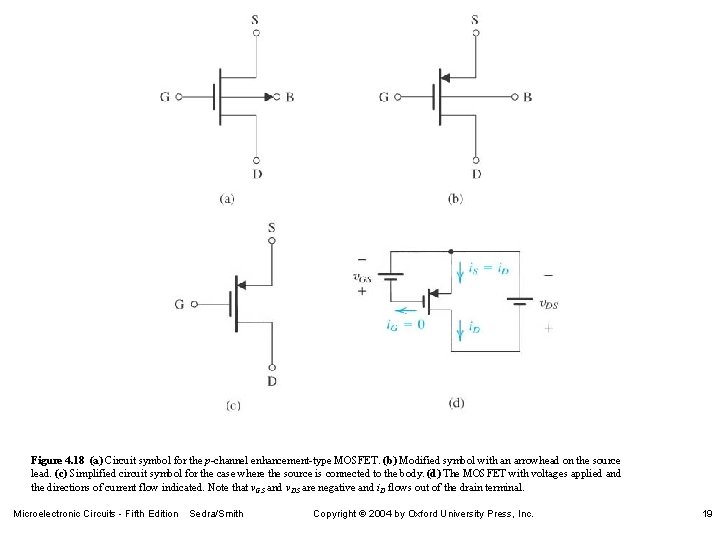

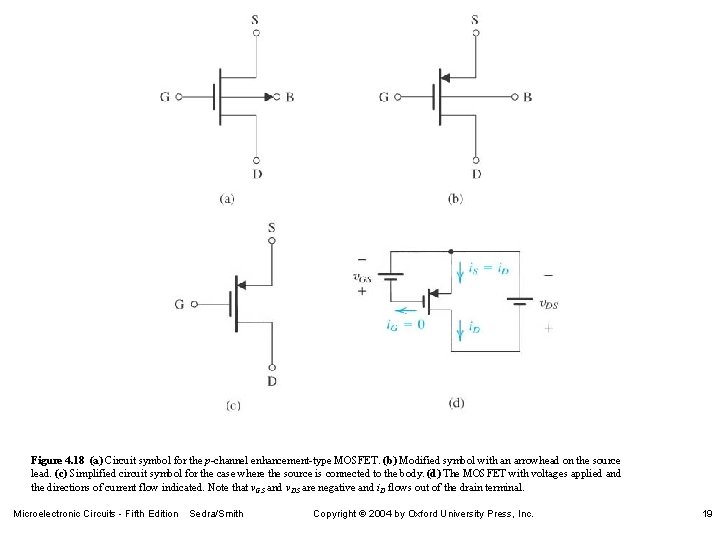

Figure 4. 18 (a) Circuit symbol for the p-channel enhancement-type MOSFET. (b) Modified symbol with an arrowhead on the source lead. (c) Simplified circuit symbol for the case where the source is connected to the body. (d) The MOSFET with voltages applied and the directions of current flow indicated. Note that v. GS and v. DS are negative and i. D flows out of the drain terminal. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 19

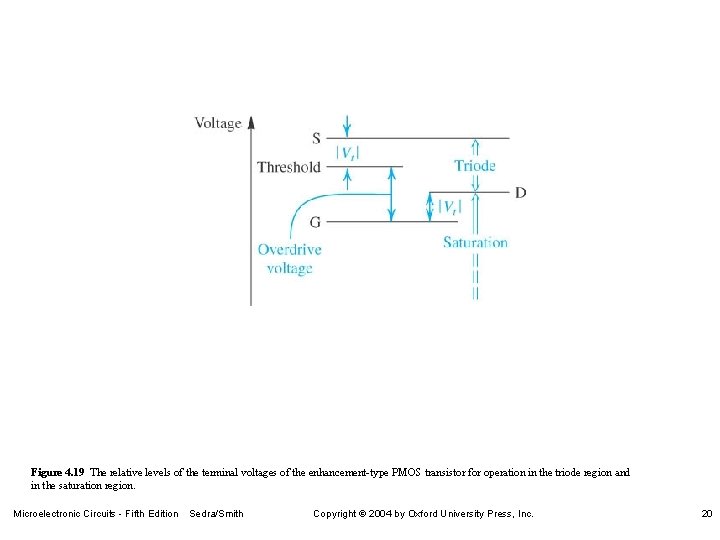

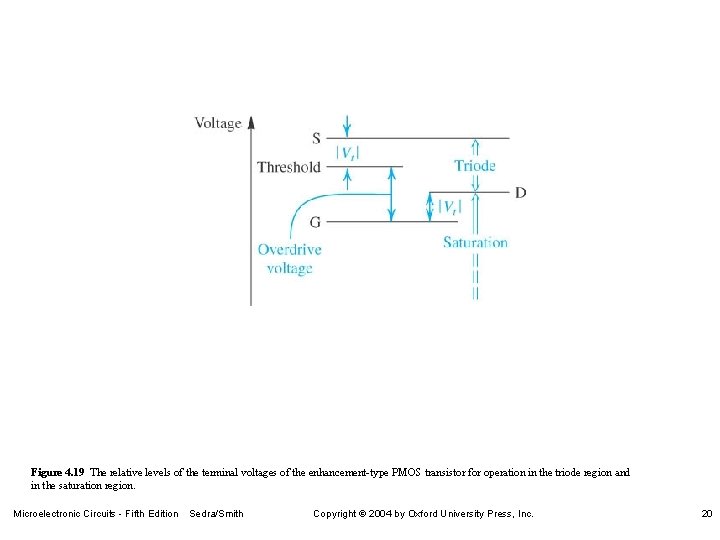

Figure 4. 19 The relative levels of the terminal voltages of the enhancement-type PMOS transistor for operation in the triode region and in the saturation region. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 20

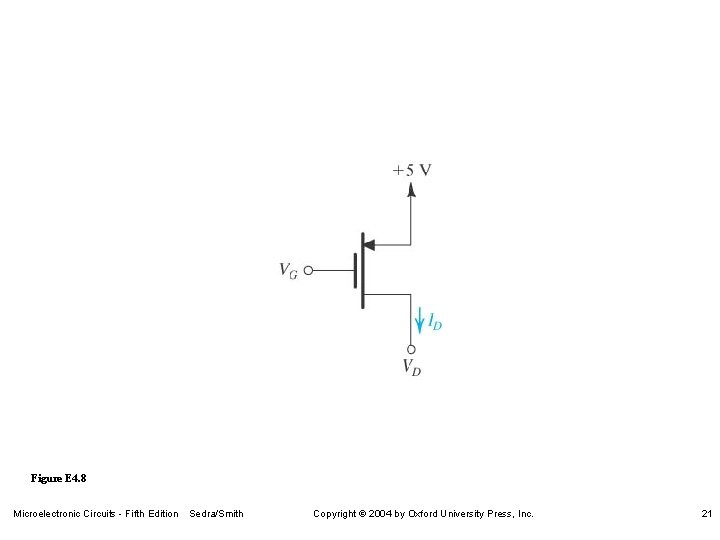

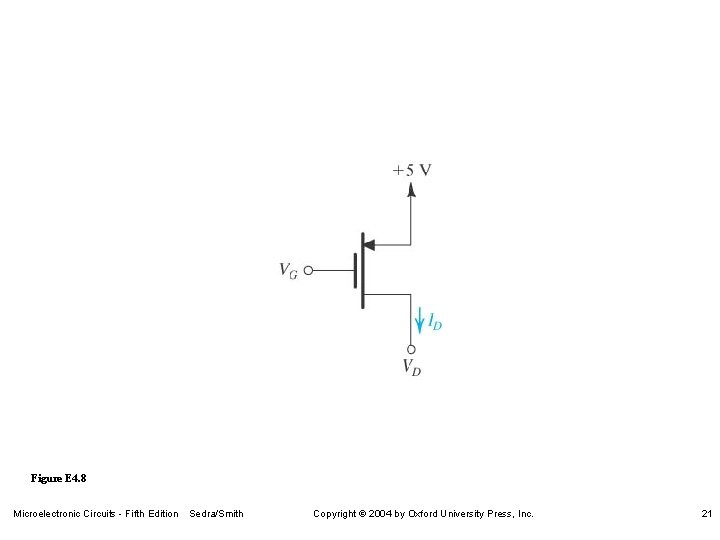

Figure E 4. 8 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 21

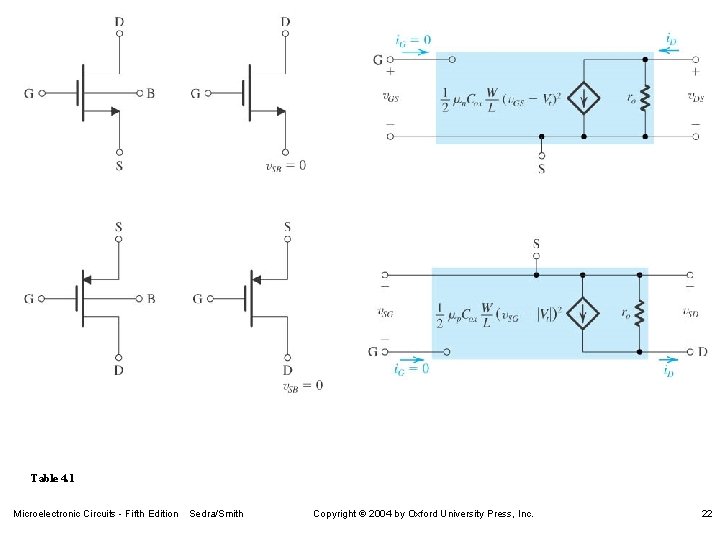

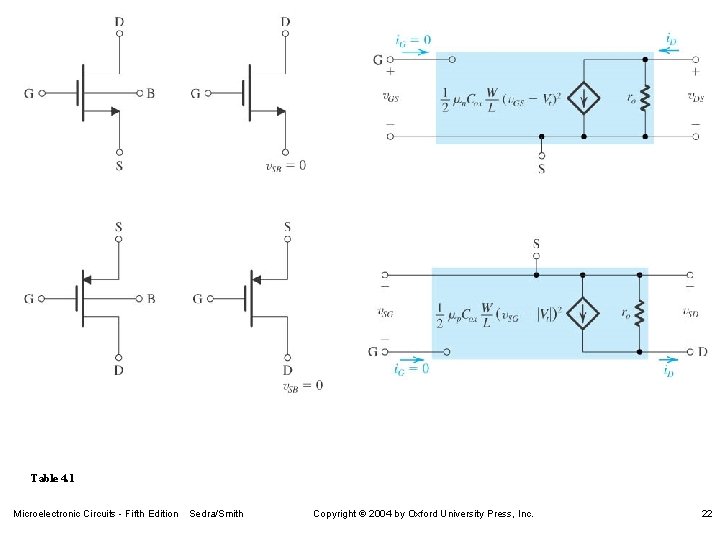

Table 4. 1 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 22

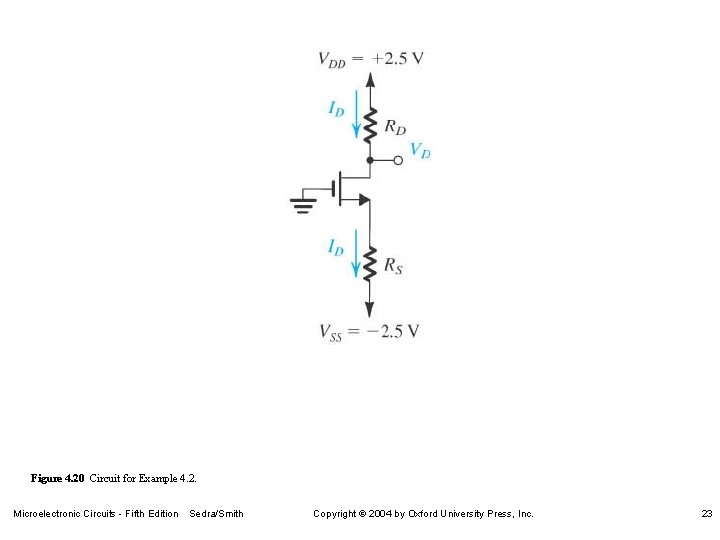

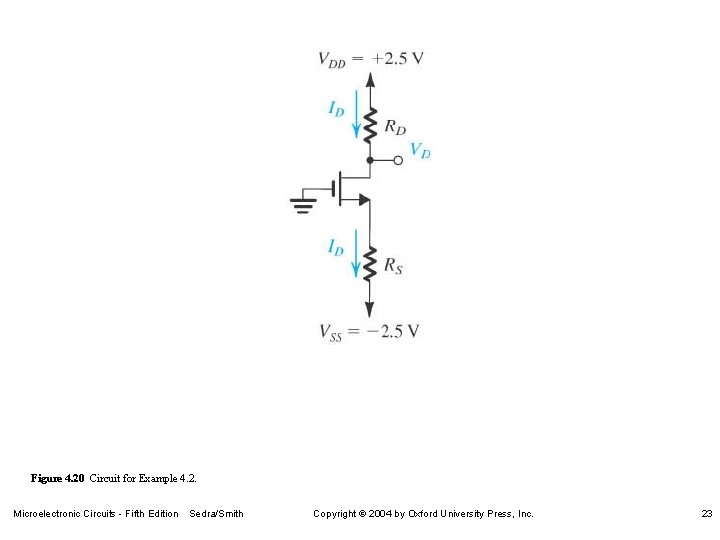

Figure 4. 20 Circuit for Example 4. 2. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 23

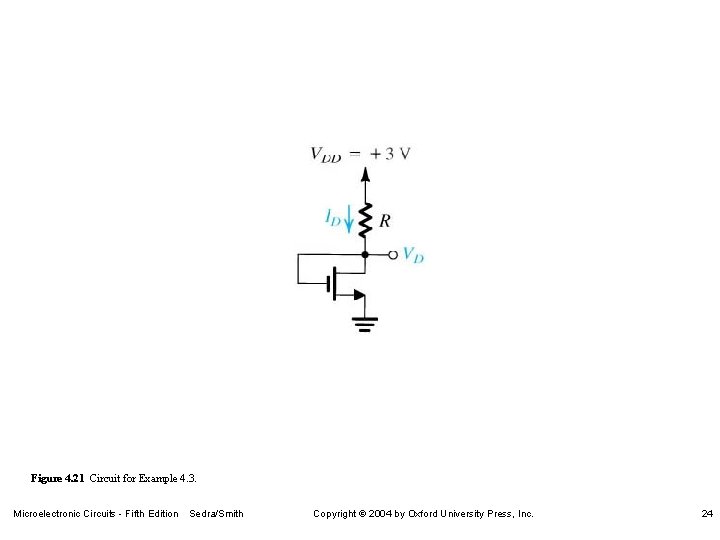

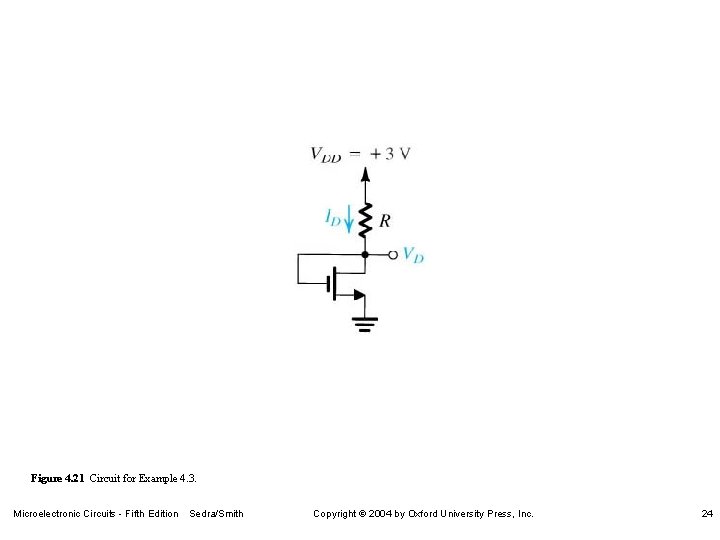

Figure 4. 21 Circuit for Example 4. 3. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 24

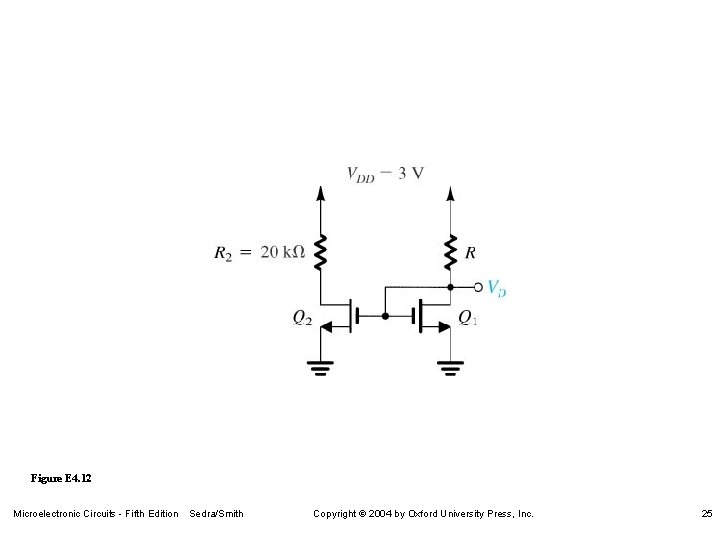

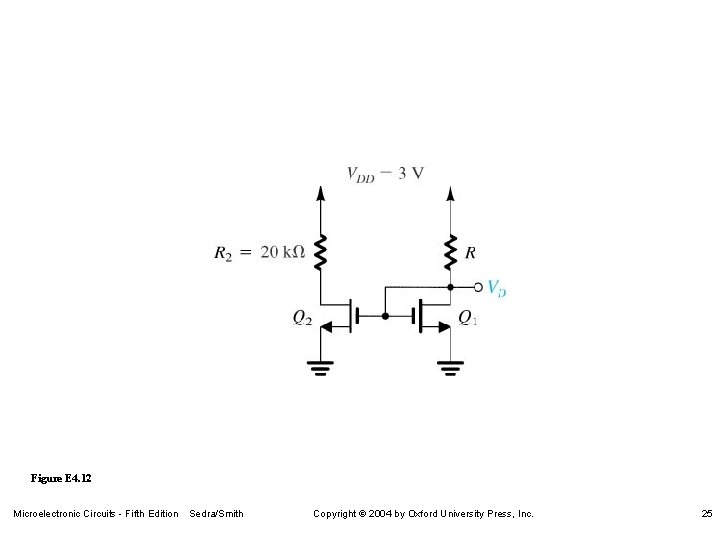

Figure E 4. 12 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 25

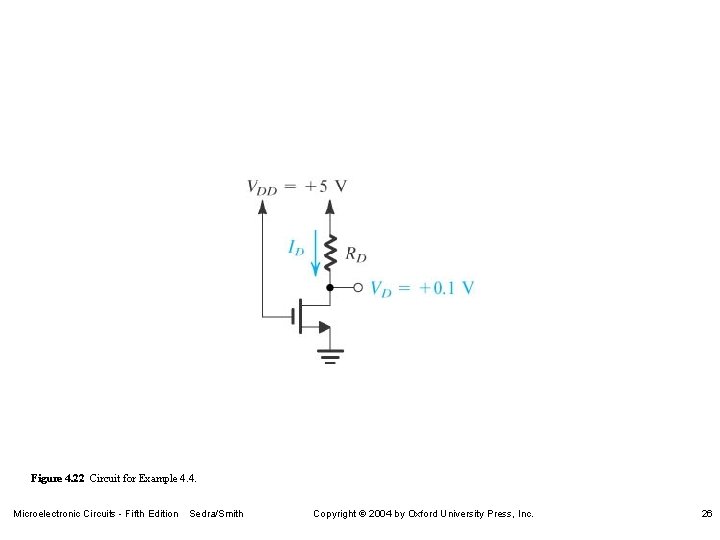

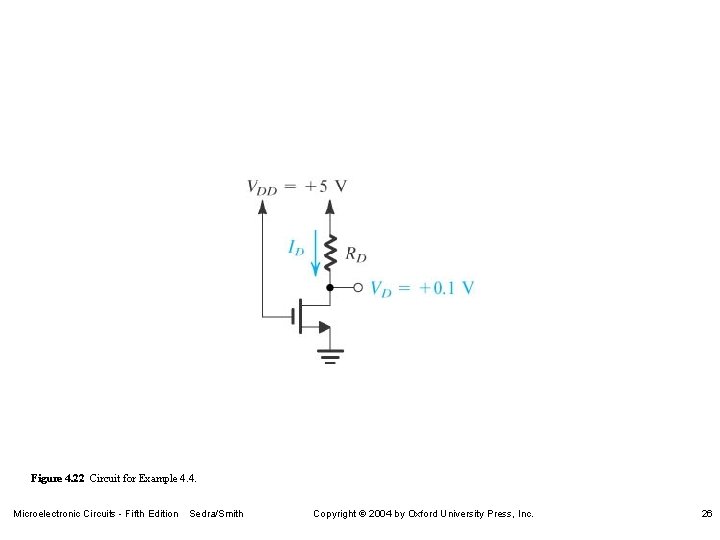

Figure 4. 22 Circuit for Example 4. 4. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 26

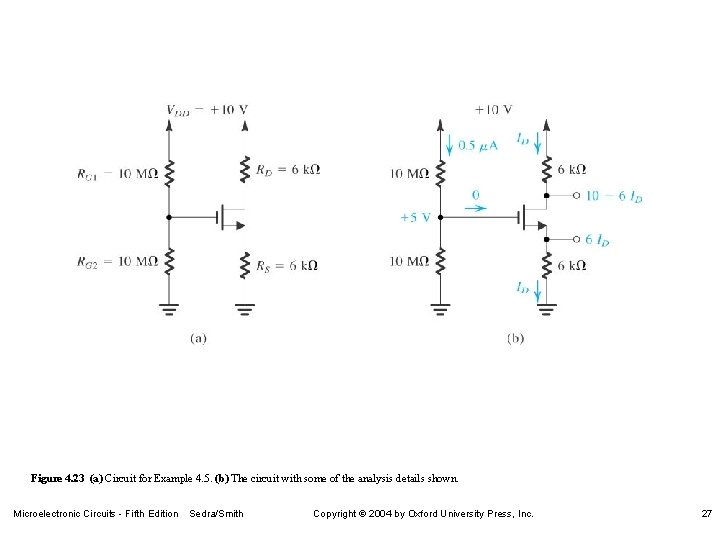

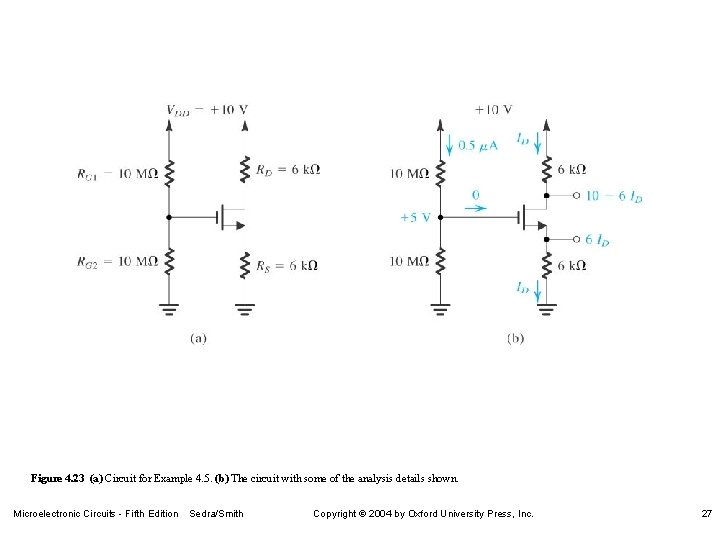

Figure 4. 23 (a) Circuit for Example 4. 5. (b) The circuit with some of the analysis details shown. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 27

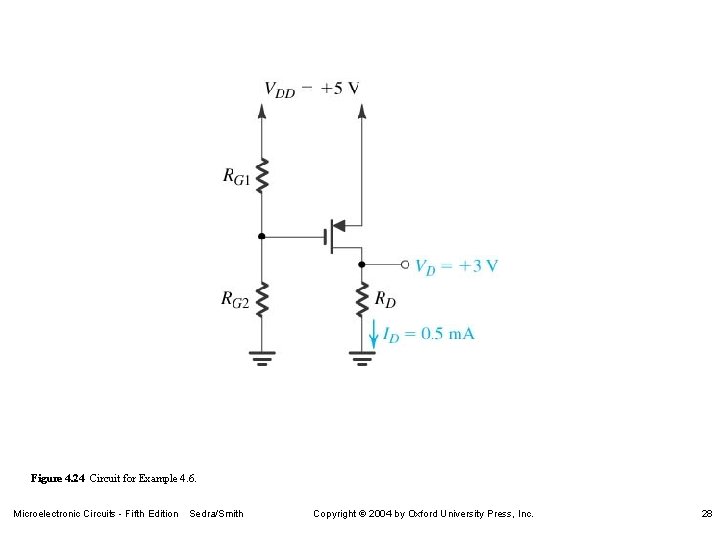

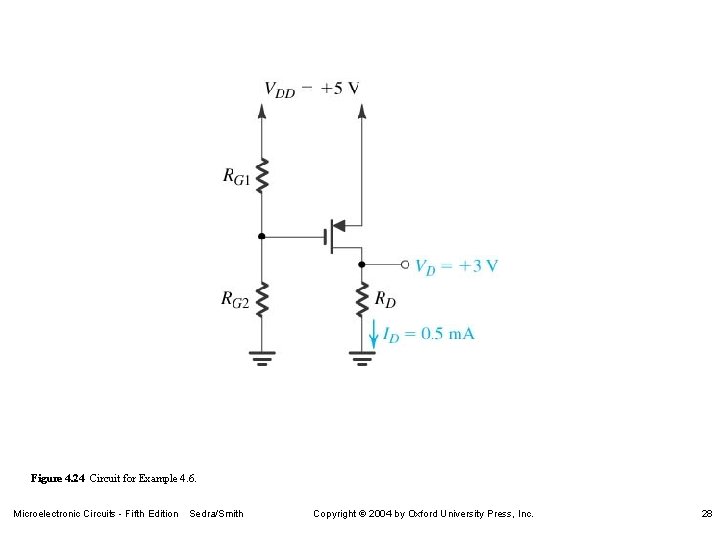

Figure 4. 24 Circuit for Example 4. 6. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 28

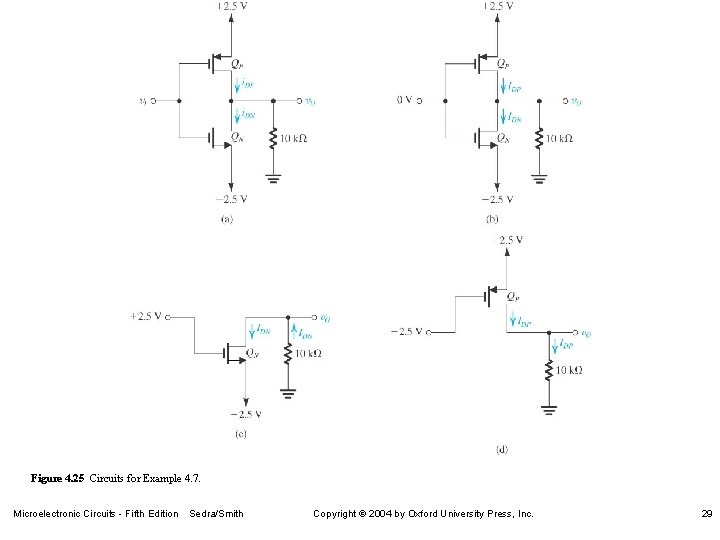

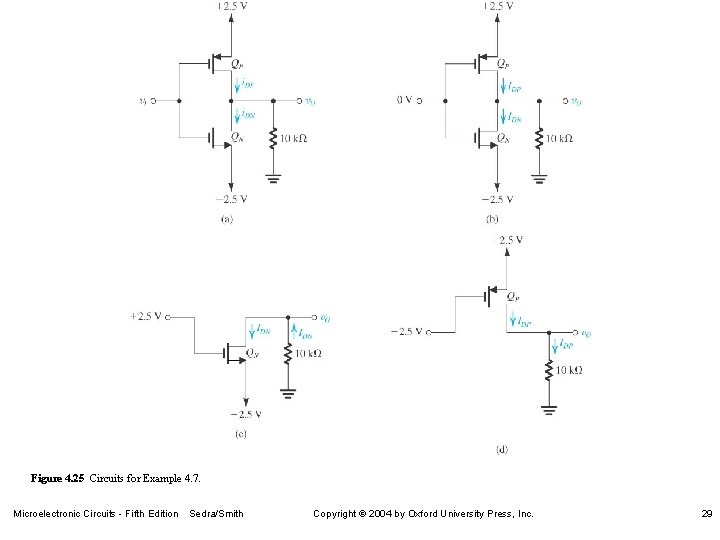

Figure 4. 25 Circuits for Example 4. 7. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 29

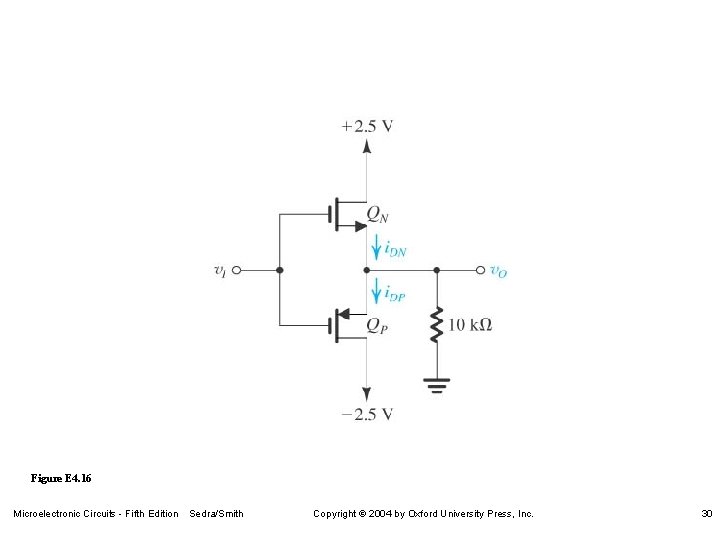

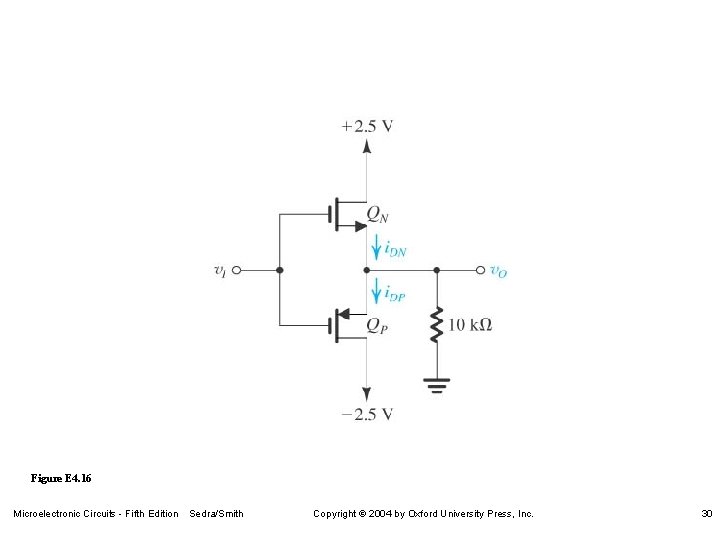

Figure E 4. 16 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 30

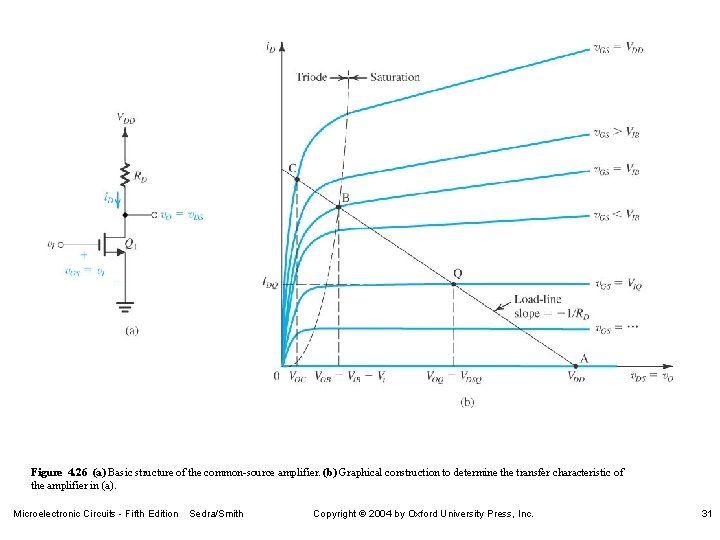

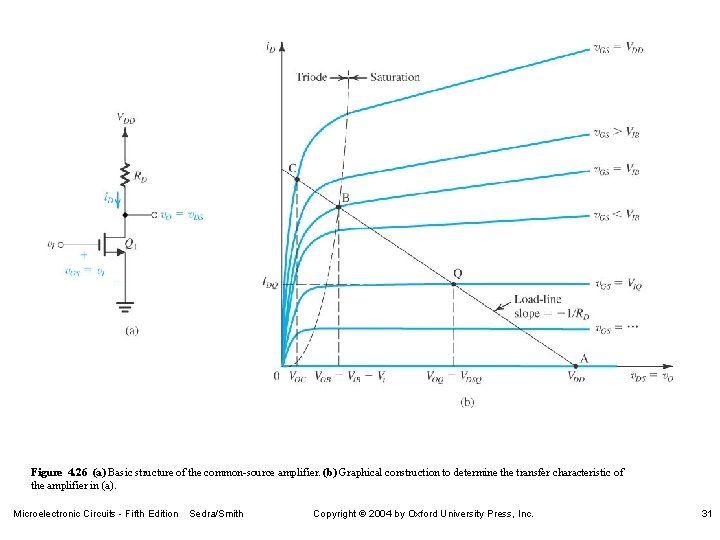

Figure 4. 26 (a) Basic structure of the common-source amplifier. (b) Graphical construction to determine the transfer characteristic of the amplifier in (a). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 31

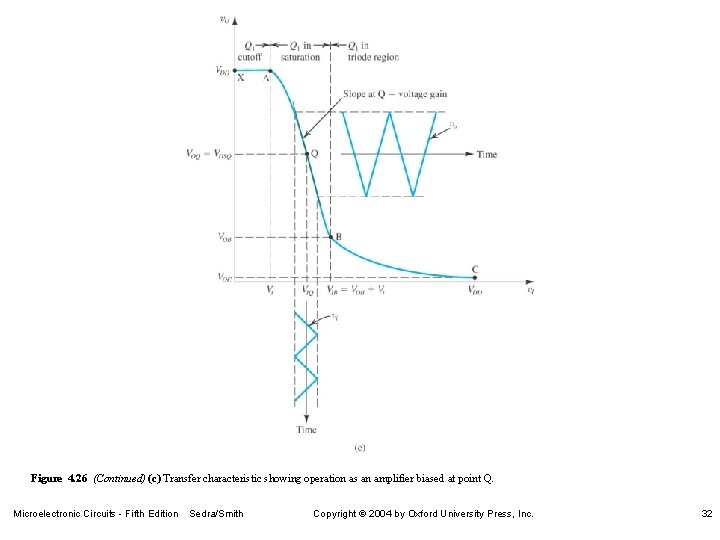

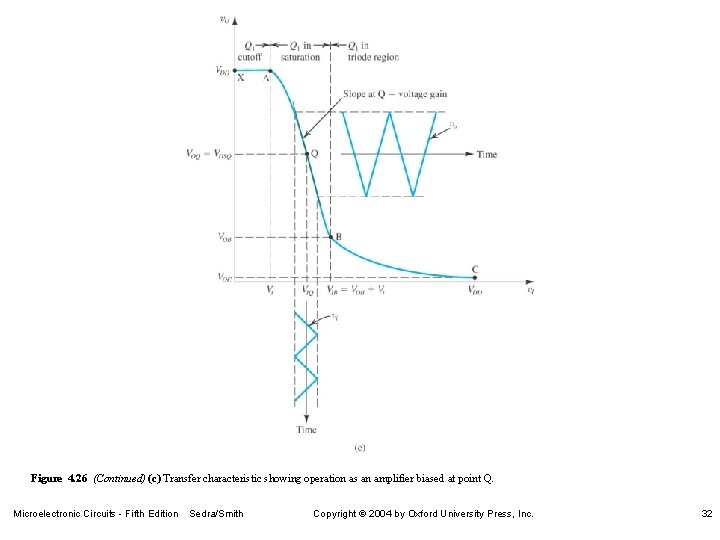

Figure 4. 26 (Continued) (c) Transfer characteristic showing operation as an amplifier biased at point Q. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 32

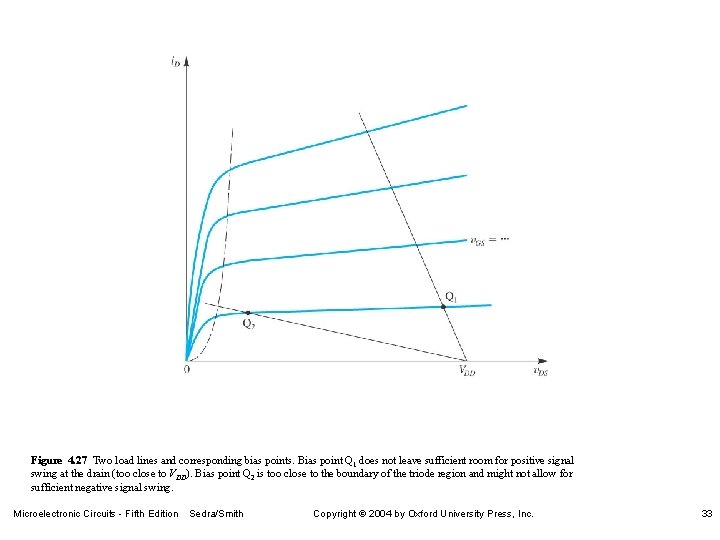

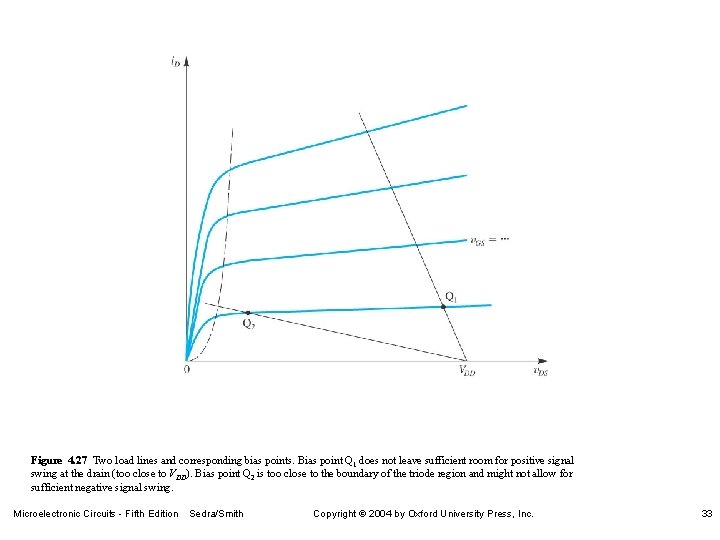

Figure 4. 27 Two load lines and corresponding bias points. Bias point Q 1 does not leave sufficient room for positive signal swing at the drain (too close to VDD). Bias point Q 2 is too close to the boundary of the triode region and might not allow for sufficient negative signal swing. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 33

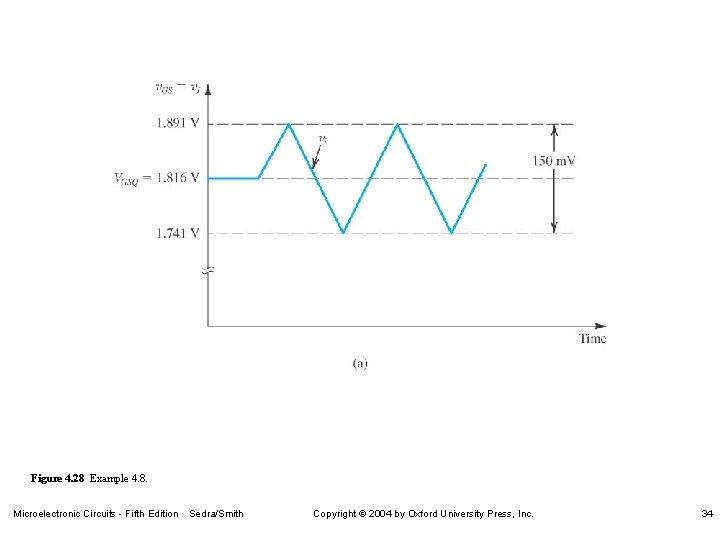

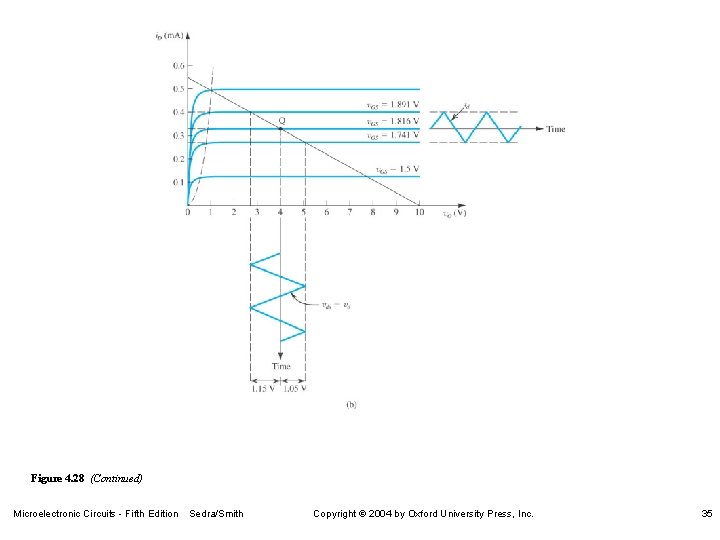

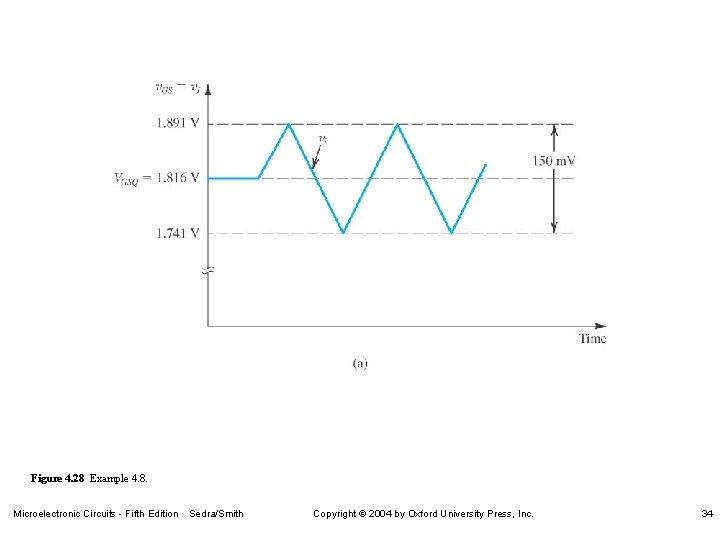

Figure 4. 28 Example 4. 8. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 34

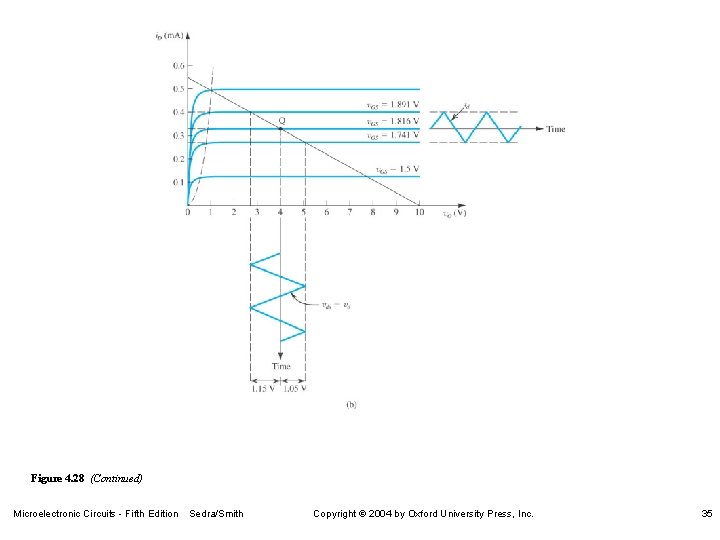

Figure 4. 28 (Continued) Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 35

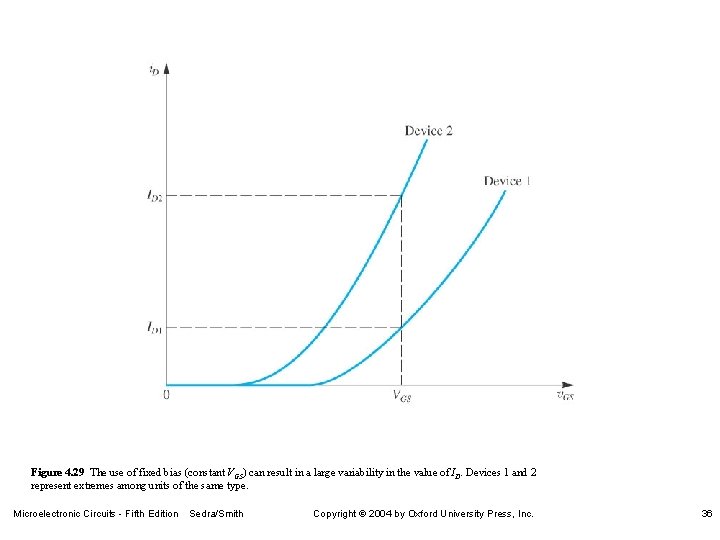

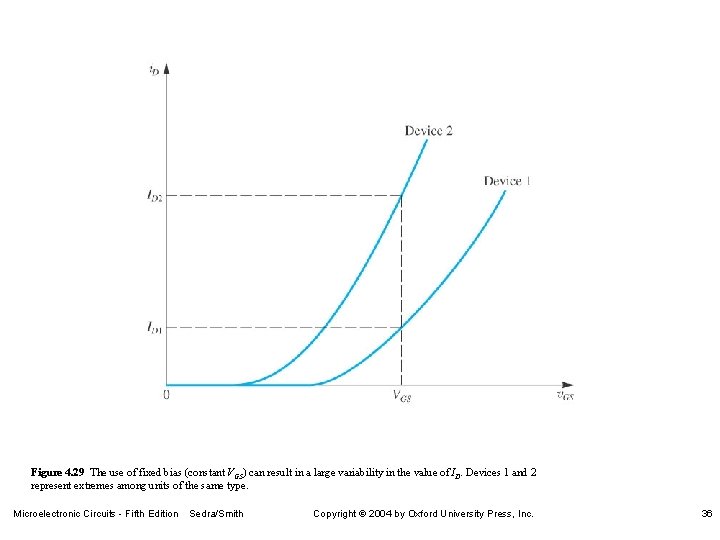

Figure 4. 29 The use of fixed bias (constant VGS) can result in a large variability in the value of ID. Devices 1 and 2 represent extremes among units of the same type. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 36

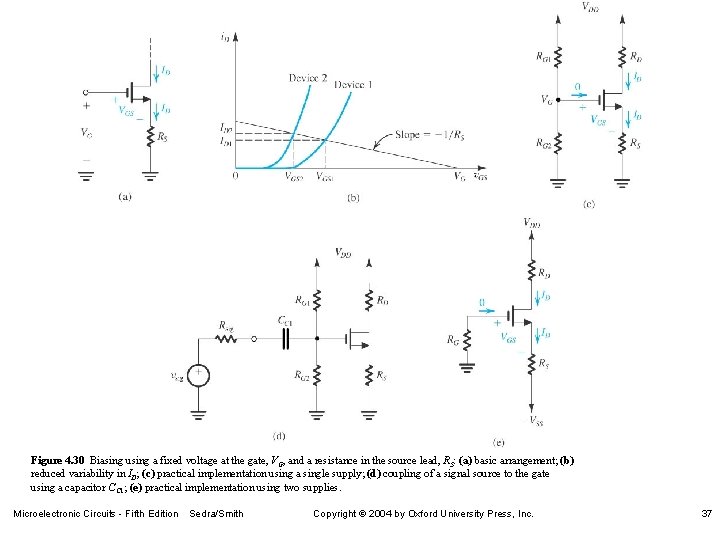

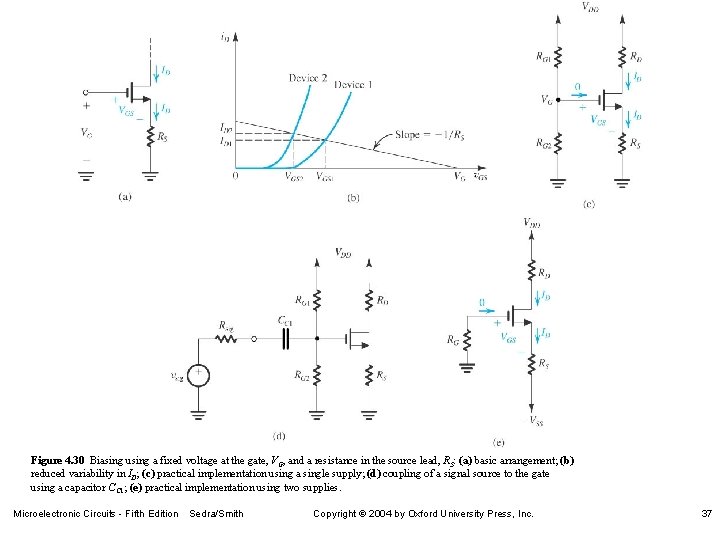

Figure 4. 30 Biasing using a fixed voltage at the gate, VG, and a resistance in the source lead, RS: (a) basic arrangement; (b) reduced variability in ID; (c) practical implementation using a single supply; (d) coupling of a signal source to the gate using a capacitor CC 1; (e) practical implementation using two supplies. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 37

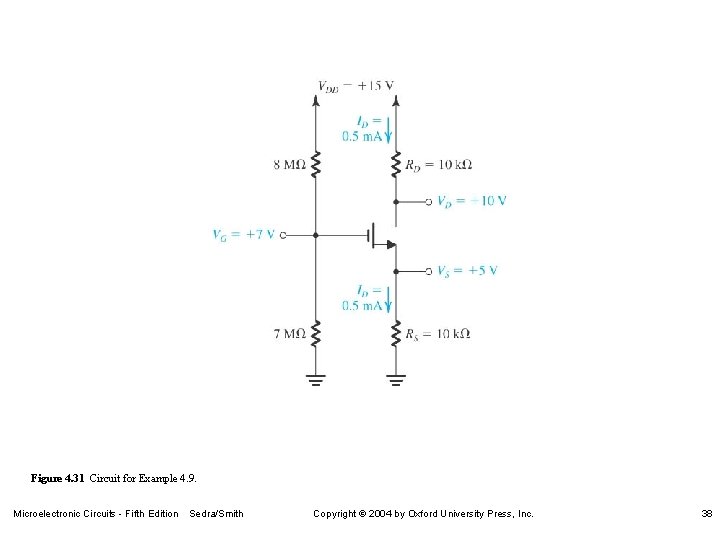

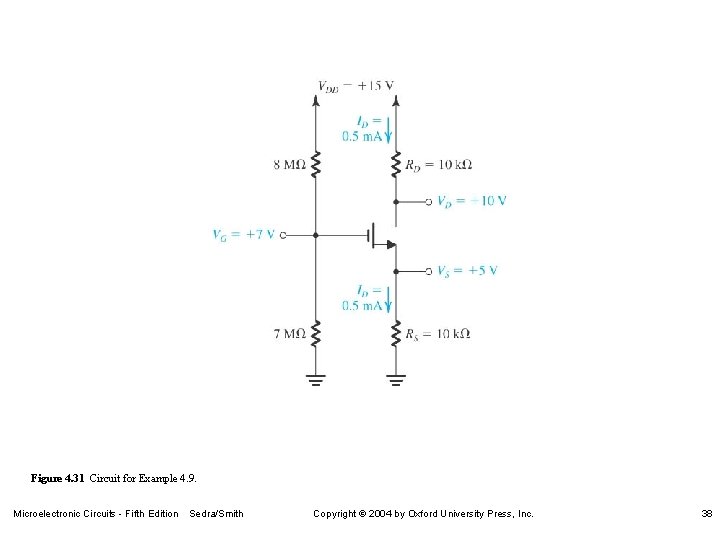

Figure 4. 31 Circuit for Example 4. 9. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 38

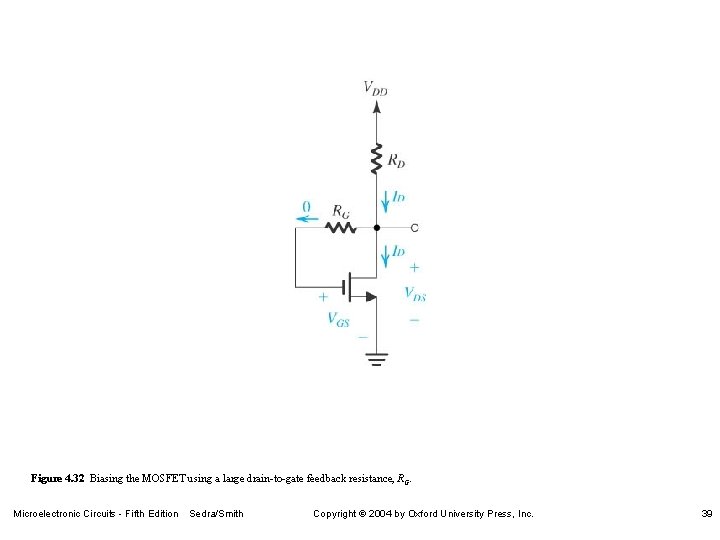

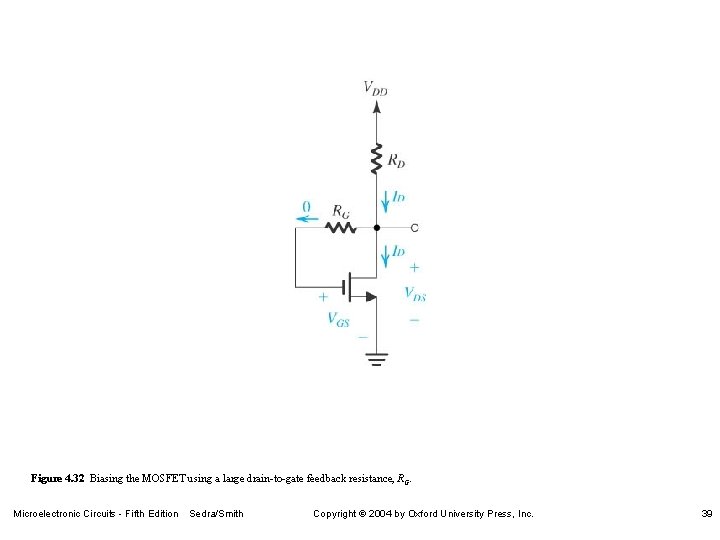

Figure 4. 32 Biasing the MOSFET using a large drain-to-gate feedback resistance, RG. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 39

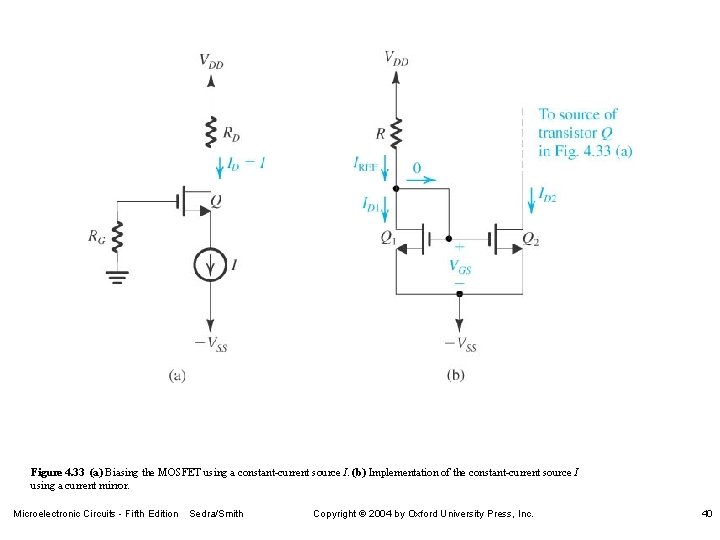

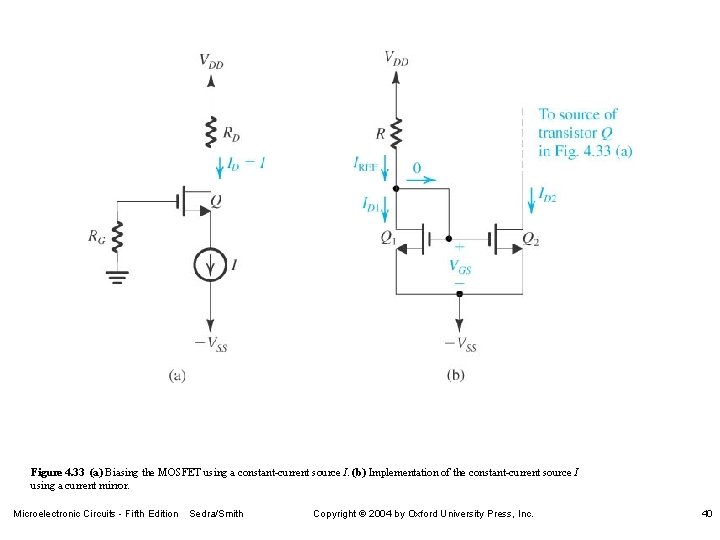

Figure 4. 33 (a) Biasing the MOSFET using a constant-current source I. (b) Implementation of the constant-current source I using a current mirror. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 40

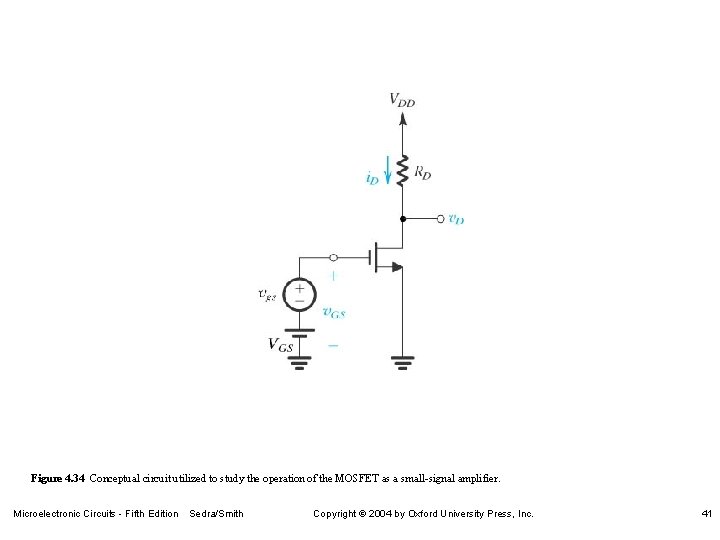

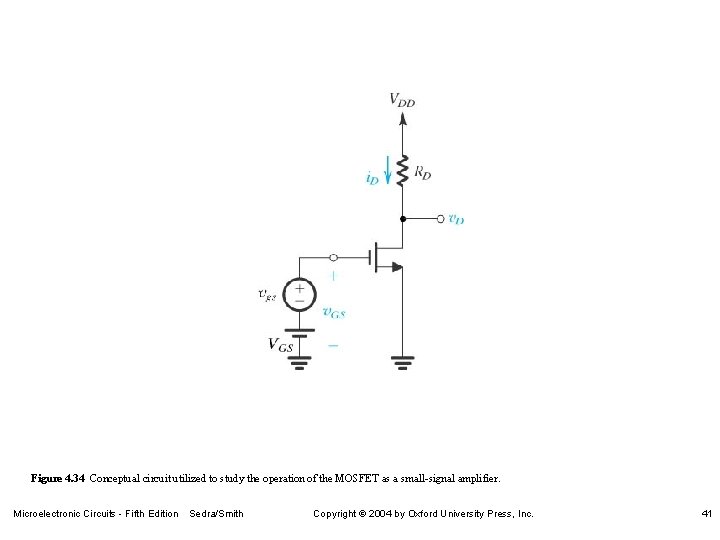

Figure 4. 34 Conceptual circuit utilized to study the operation of the MOSFET as a small-signal amplifier. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 41

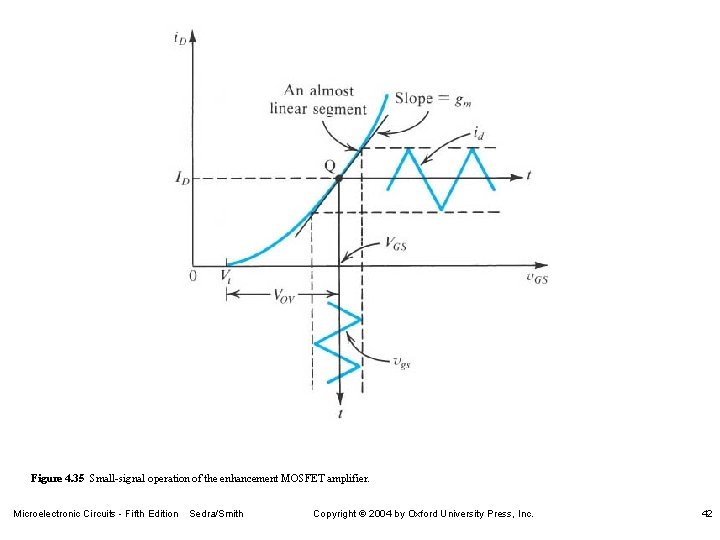

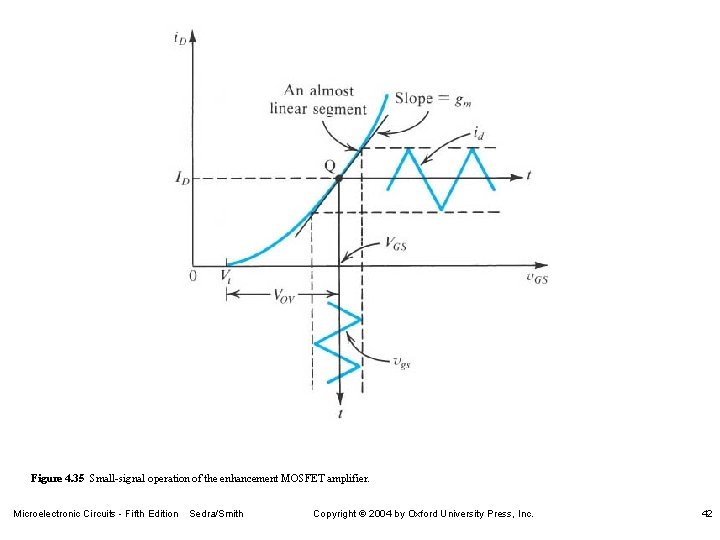

Figure 4. 35 Small-signal operation of the enhancement MOSFET amplifier. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 42

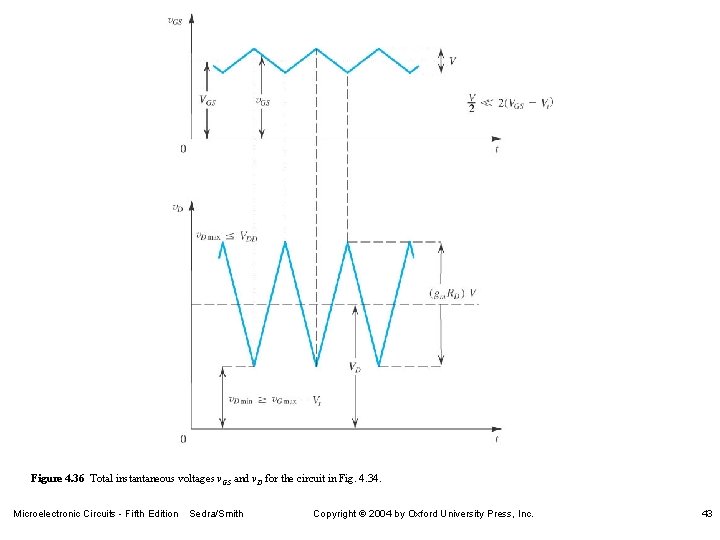

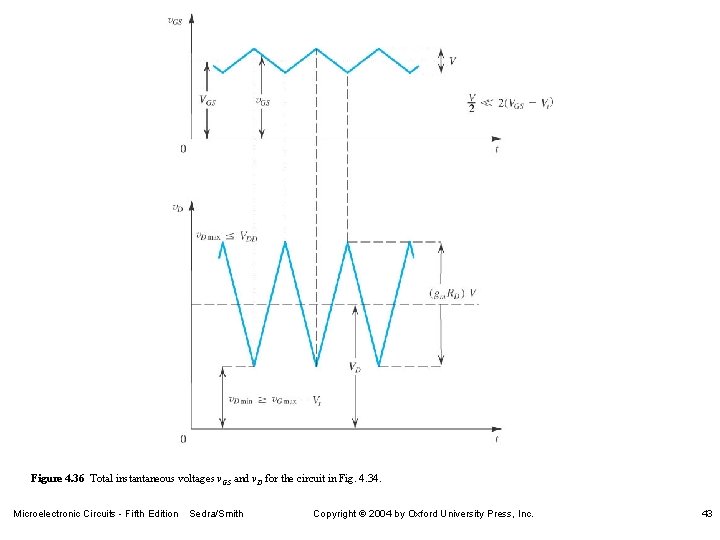

Figure 4. 36 Total instantaneous voltages v. GS and v. D for the circuit in Fig. 4. 34. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 43

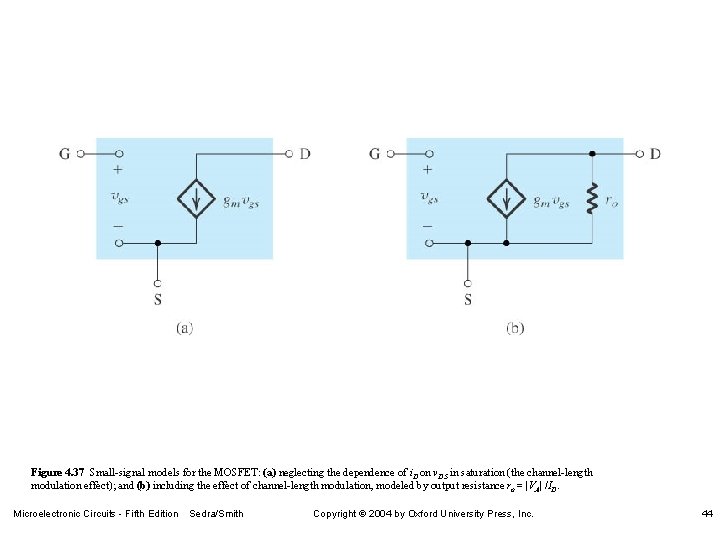

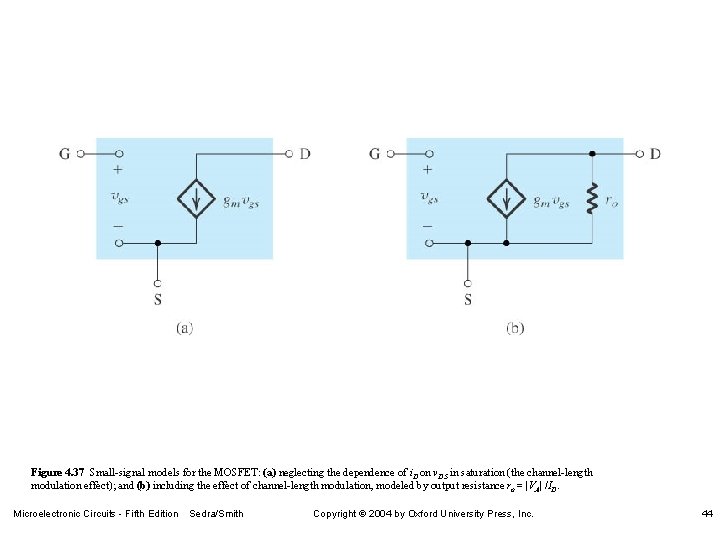

Figure 4. 37 Small-signal models for the MOSFET: (a) neglecting the dependence of i. D on v. DS in saturation (the channel-length modulation effect); and (b) including the effect of channel-length modulation, modeled by output resistance ro = |VA| /ID. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 44

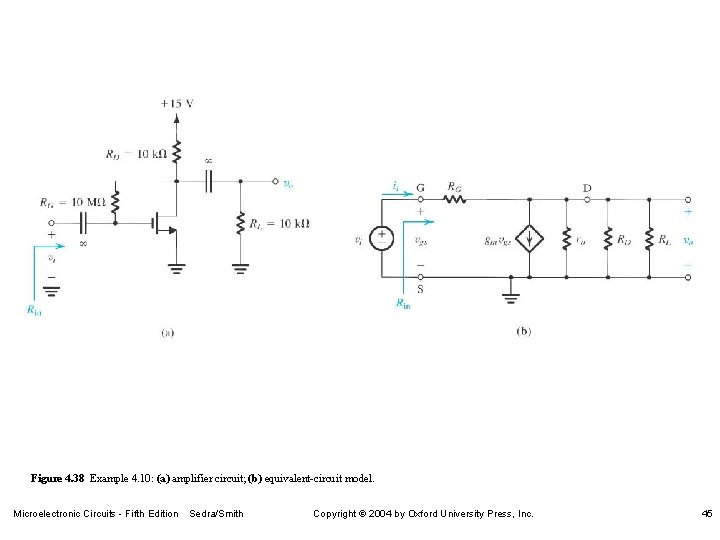

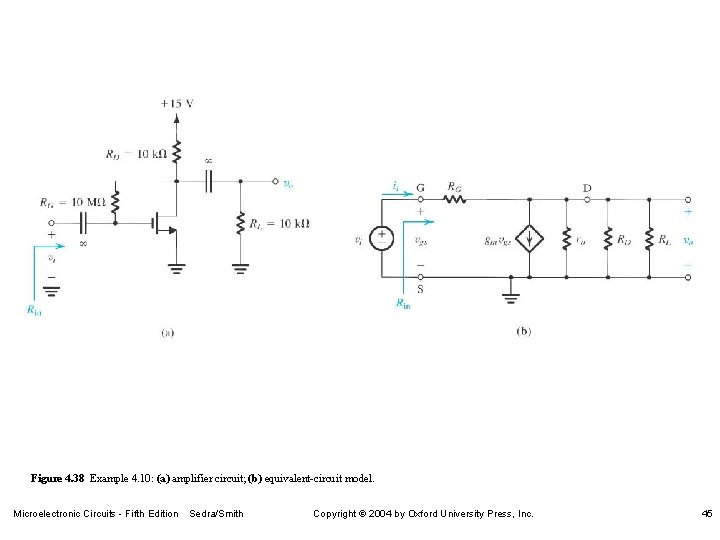

Figure 4. 38 Example 4. 10: (a) amplifier circuit; (b) equivalent-circuit model. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 45

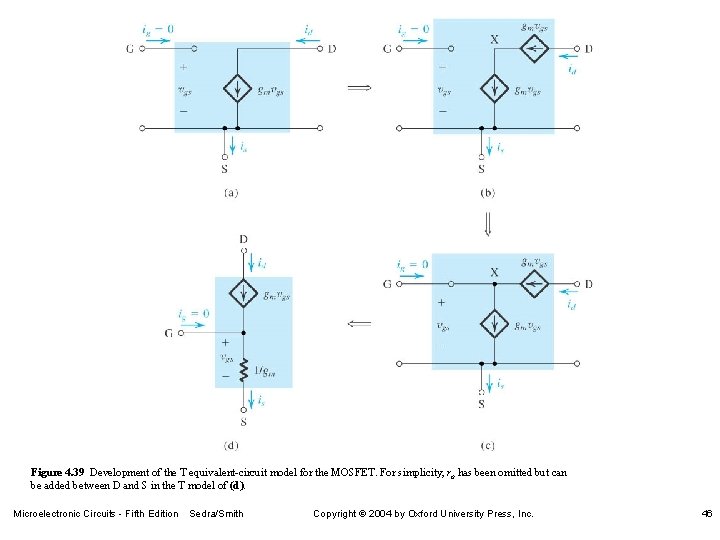

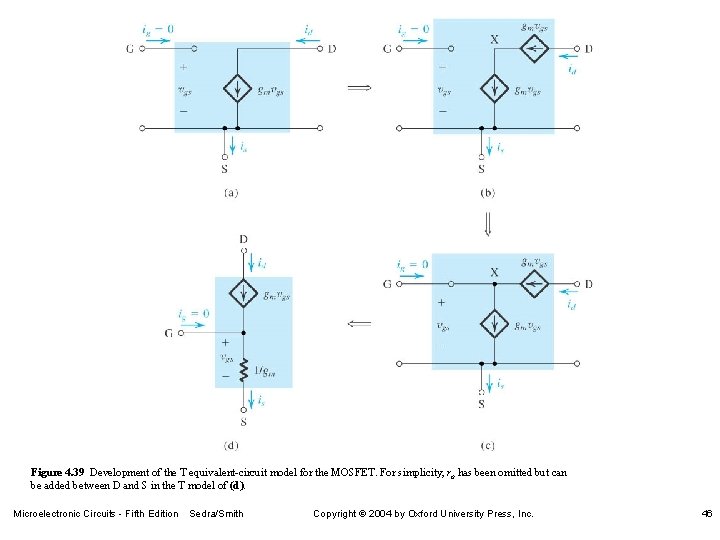

Figure 4. 39 Development of the T equivalent-circuit model for the MOSFET. For simplicity, ro has been omitted but can be added between D and S in the T model of (d). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 46

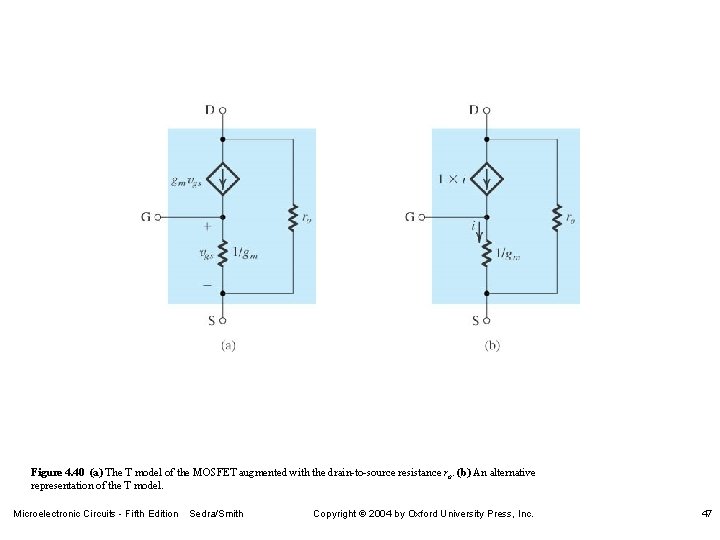

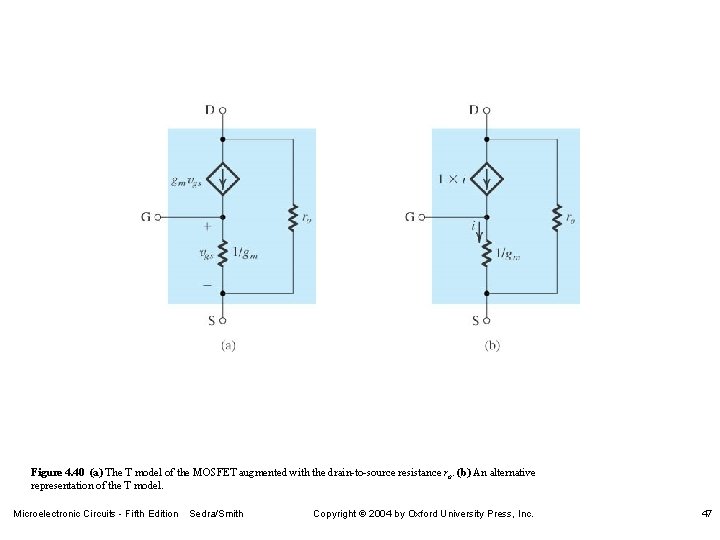

Figure 4. 40 (a) The T model of the MOSFET augmented with the drain-to-source resistance ro. (b) An alternative representation of the T model. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 47

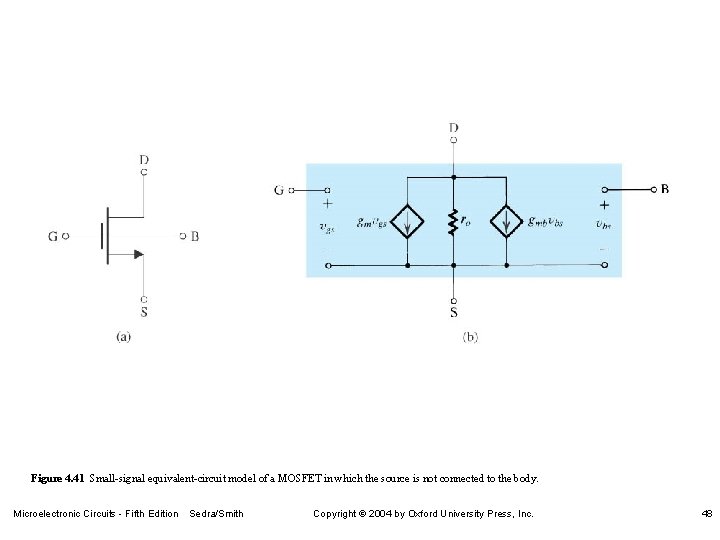

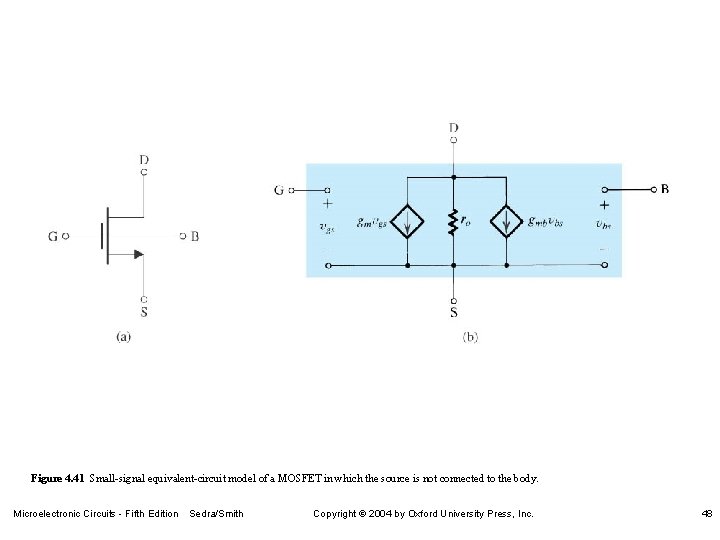

Figure 4. 41 Small-signal equivalent-circuit model of a MOSFET in which the source is not connected to the body. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 48

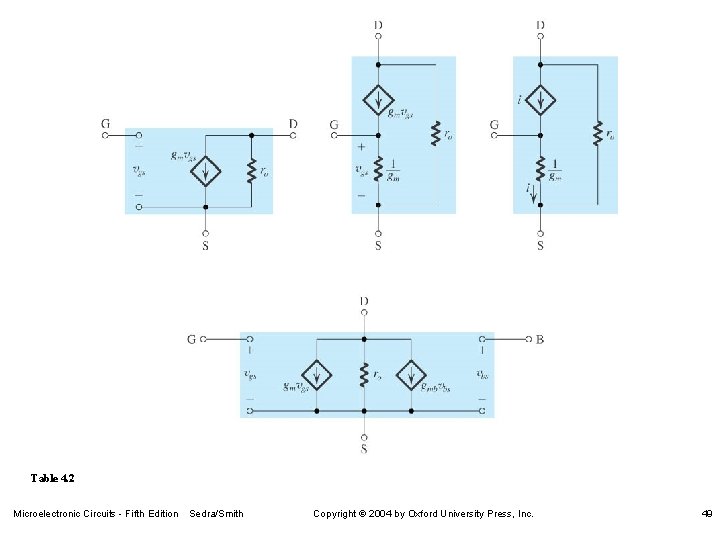

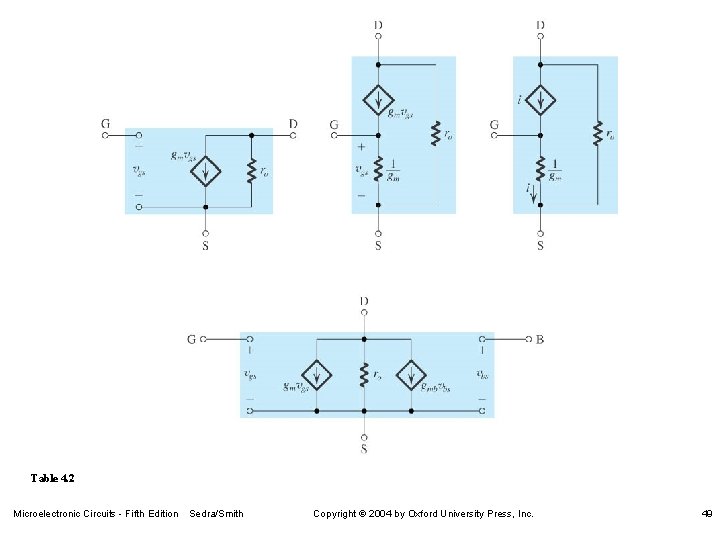

Table 4. 2 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 49

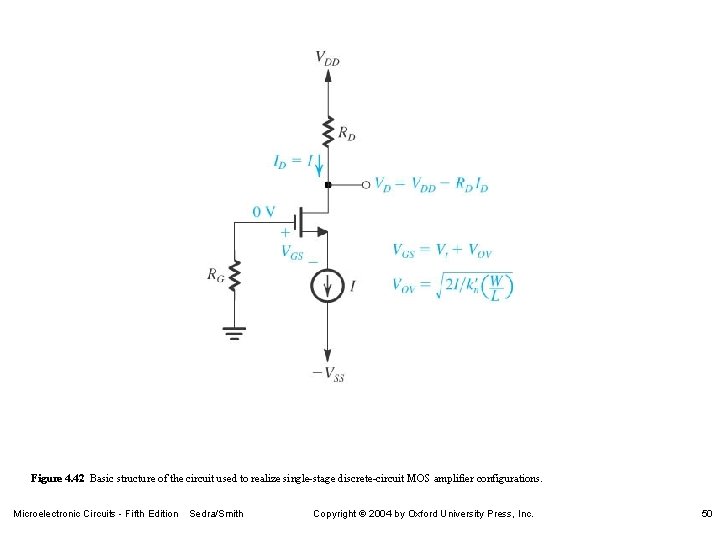

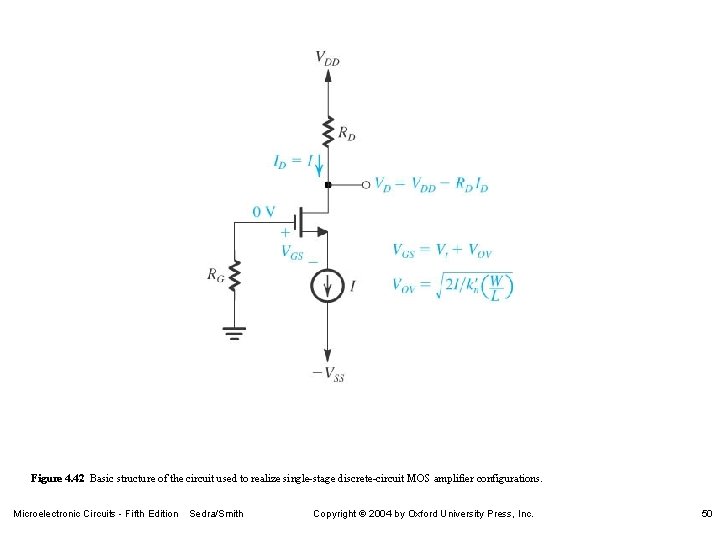

Figure 4. 42 Basic structure of the circuit used to realize single-stage discrete-circuit MOS amplifier configurations. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 50

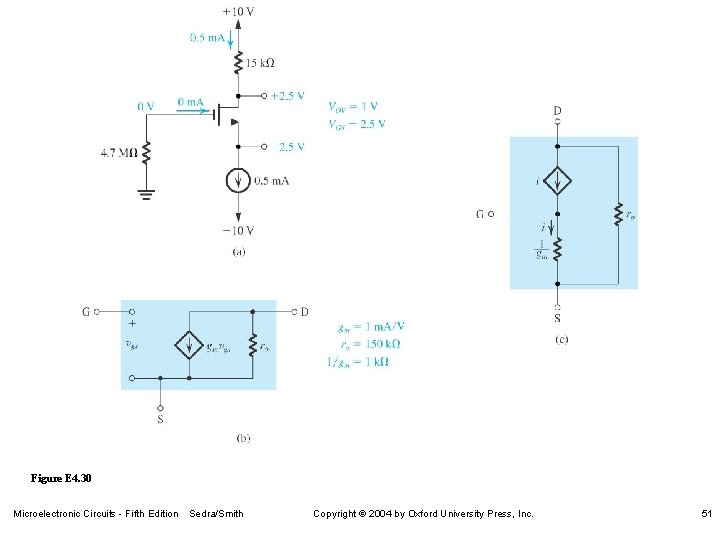

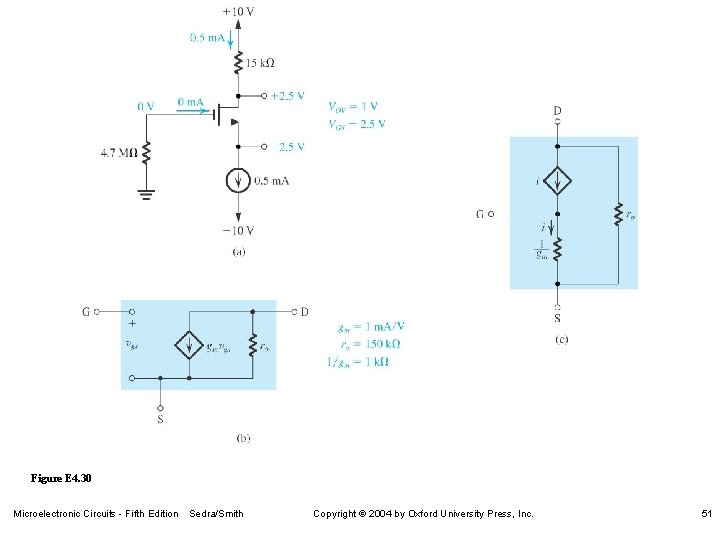

Figure E 4. 30 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 51

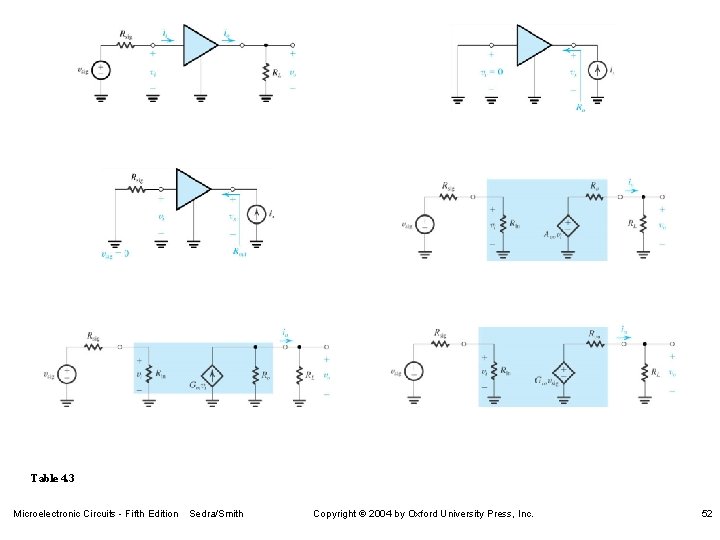

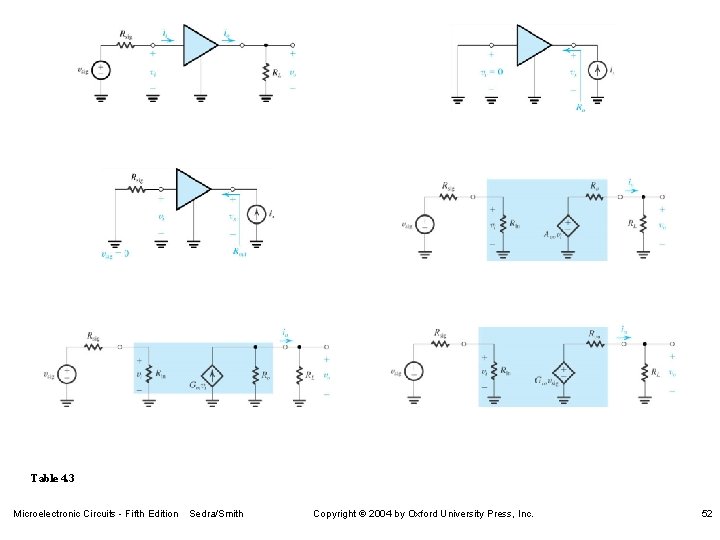

Table 4. 3 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 52

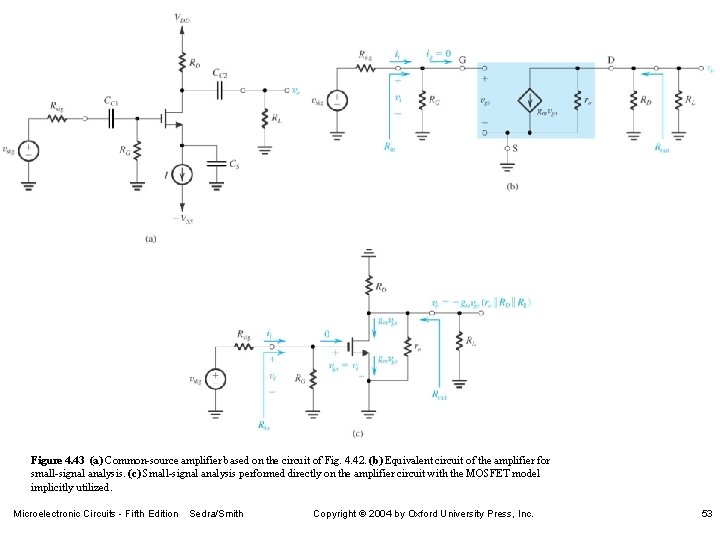

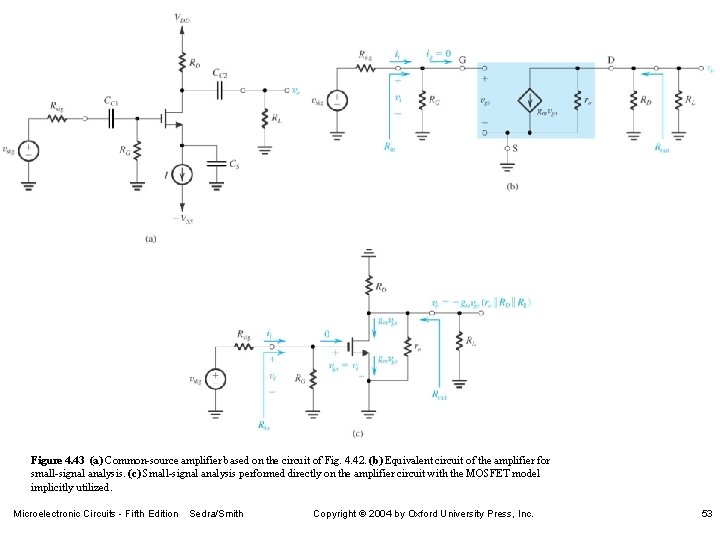

Figure 4. 43 (a) Common-source amplifier based on the circuit of Fig. 4. 42. (b) Equivalent circuit of the amplifier for small-signal analysis. (c) Small-signal analysis performed directly on the amplifier circuit with the MOSFET model implicitly utilized. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 53

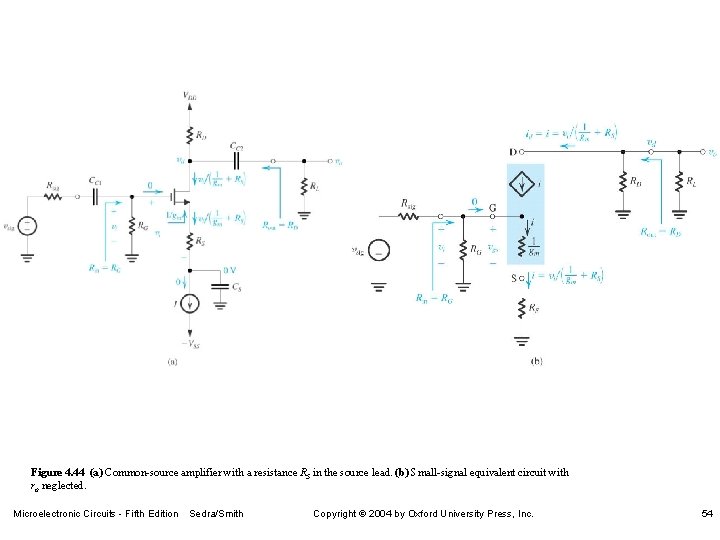

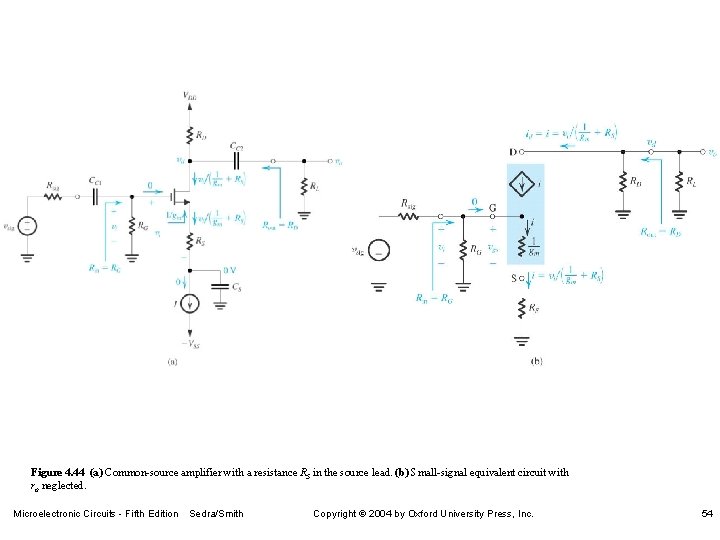

Figure 4. 44 (a) Common-source amplifier with a resistance RS in the source lead. (b) Small-signal equivalent circuit with ro neglected. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 54

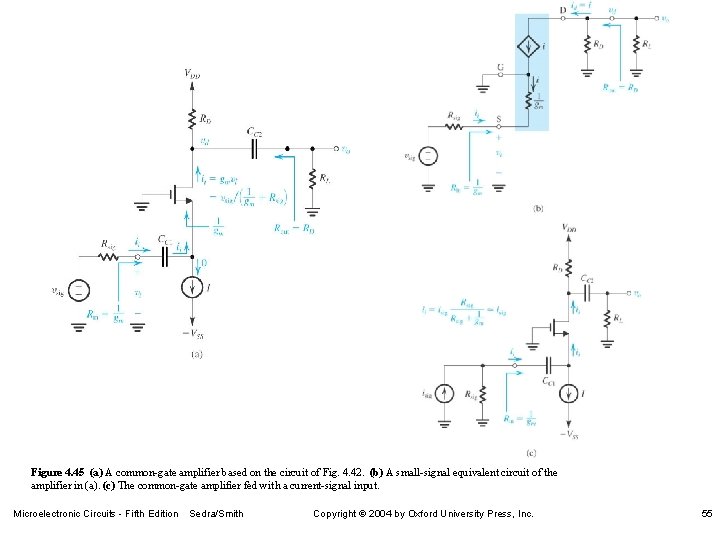

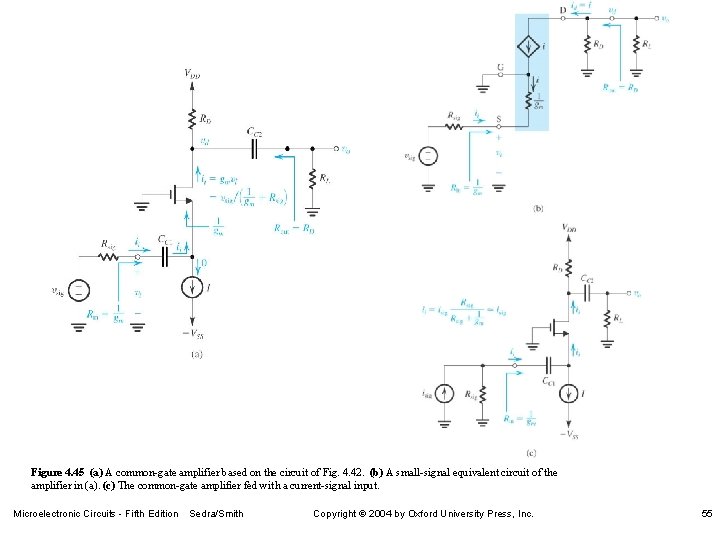

Figure 4. 45 (a) A common-gate amplifier based on the circuit of Fig. 4. 42. (b) A small-signal equivalent circuit of the amplifier in (a). (c) The common-gate amplifier fed with a current-signal input. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 55

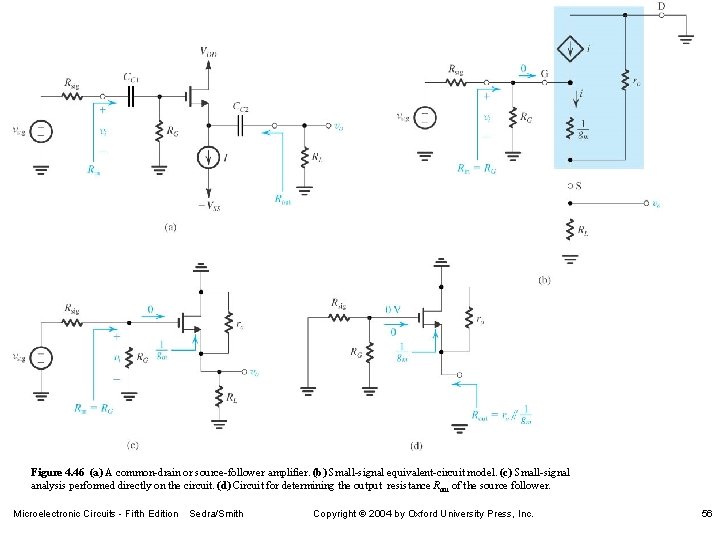

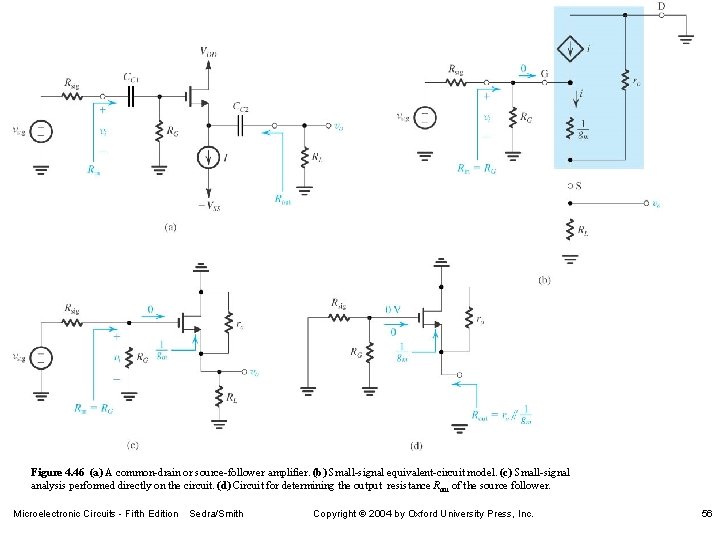

Figure 4. 46 (a) A common-drain or source-follower amplifier. (b) Small-signal equivalent-circuit model. (c) Small-signal analysis performed directly on the circuit. (d) Circuit for determining the output resistance Rout of the source follower. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 56

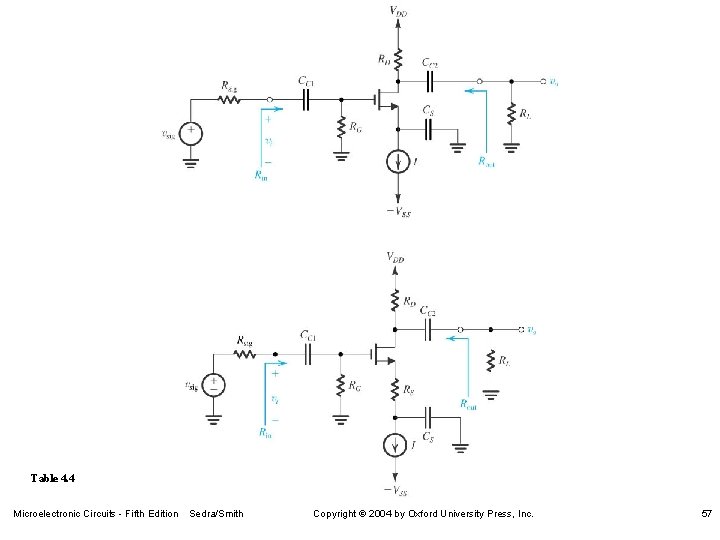

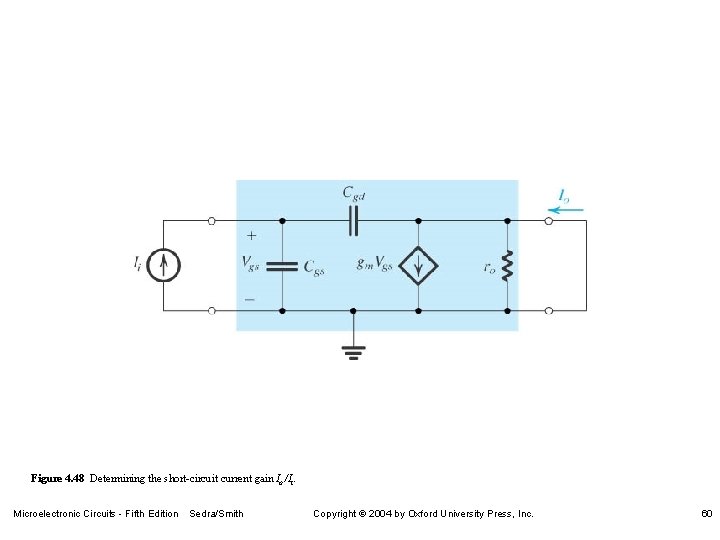

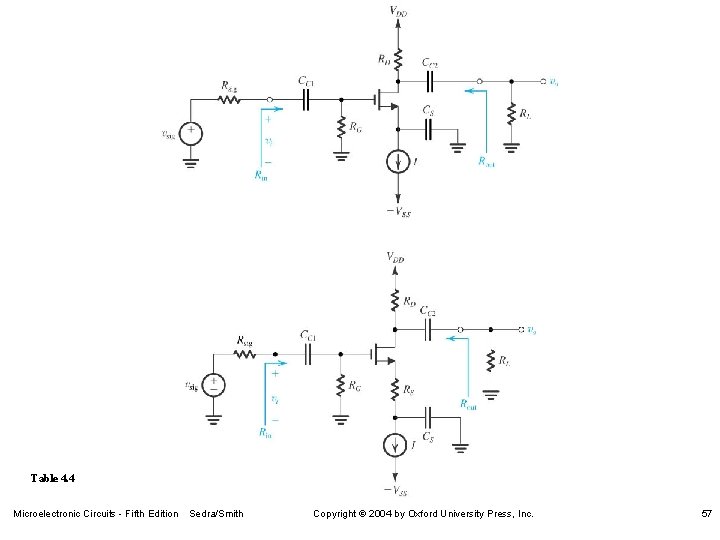

Table 4. 4 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 57

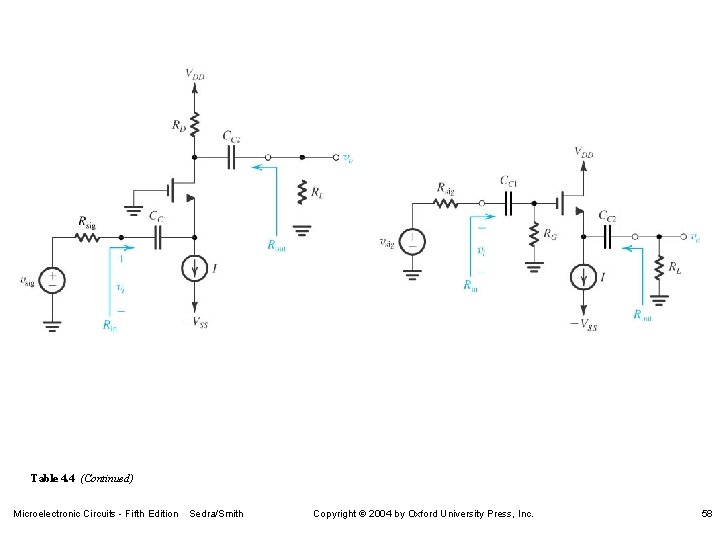

Table 4. 4 (Continued) Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 58

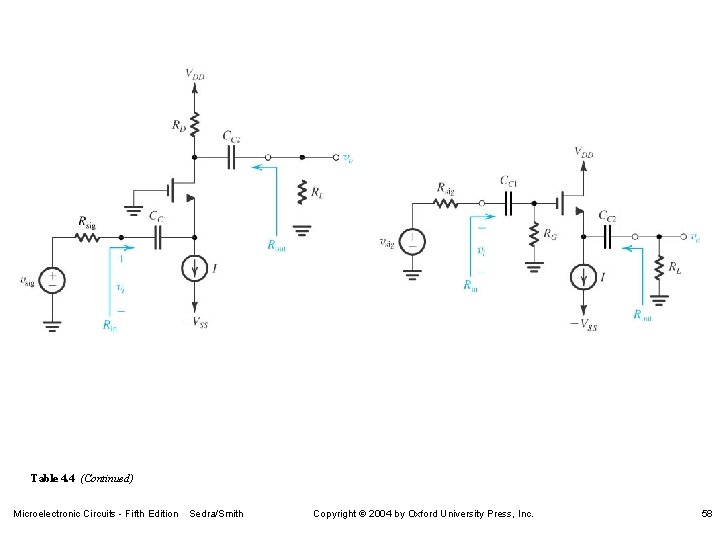

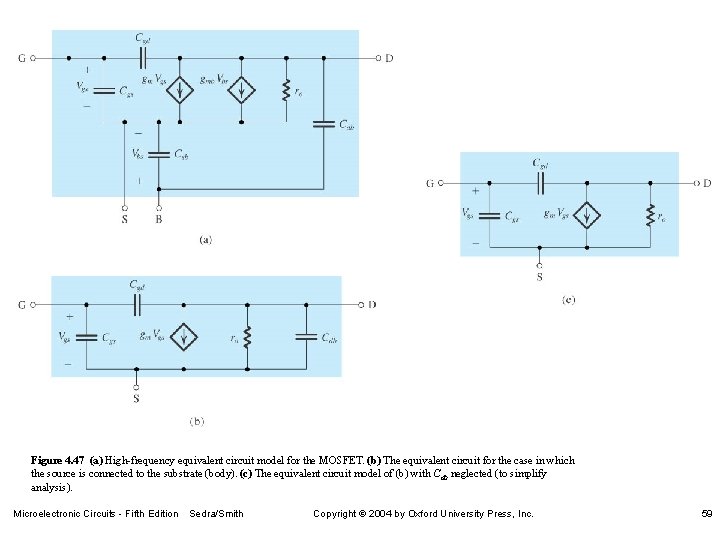

Figure 4. 47 (a) High-frequency equivalent circuit model for the MOSFET. (b) The equivalent circuit for the case in which the source is connected to the substrate (body). (c) The equivalent circuit model of (b) with Cdb neglected (to simplify analysis). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 59

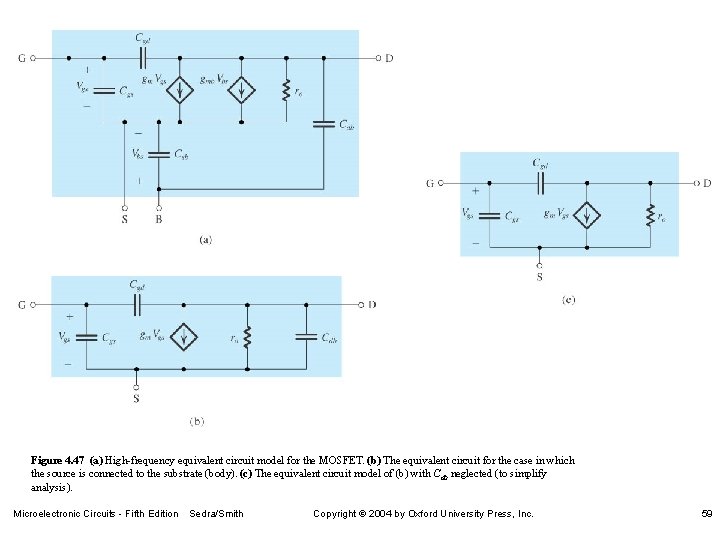

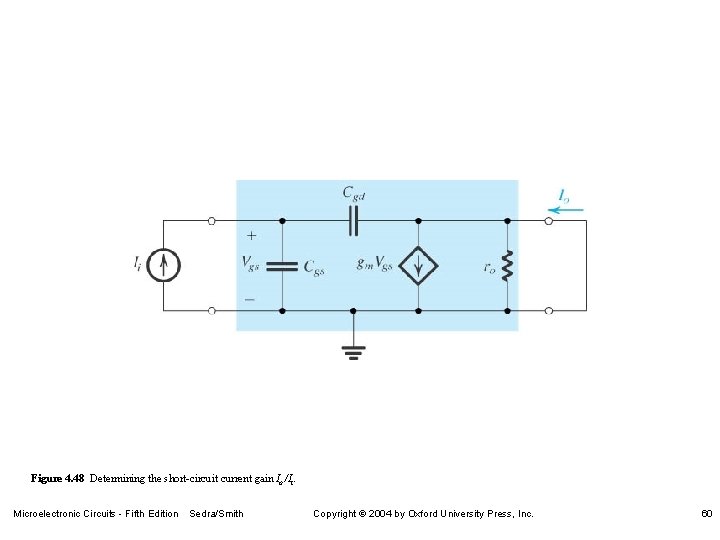

Figure 4. 48 Determining the short-circuit current gain Io /Ii. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 60

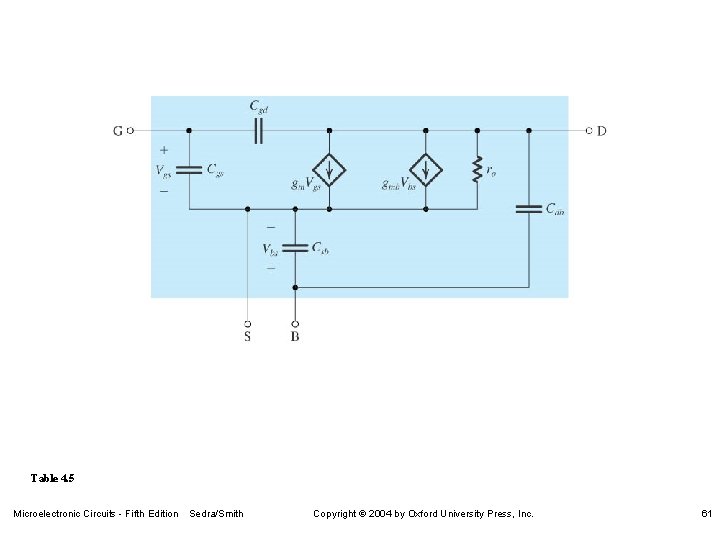

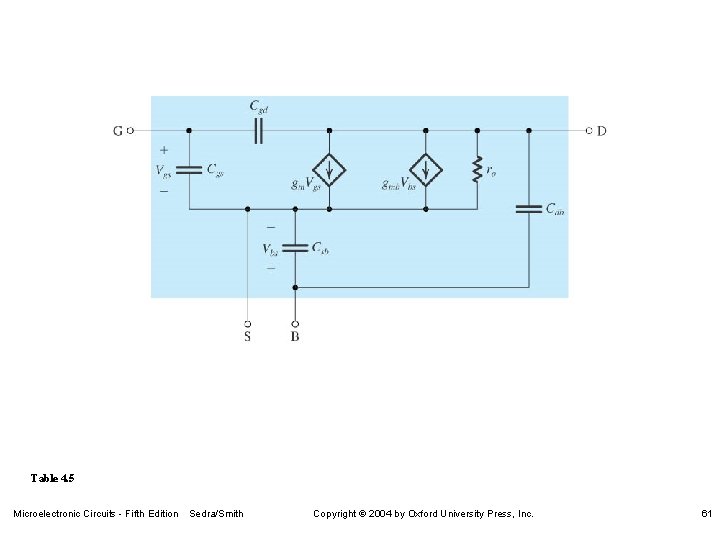

Table 4. 5 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 61

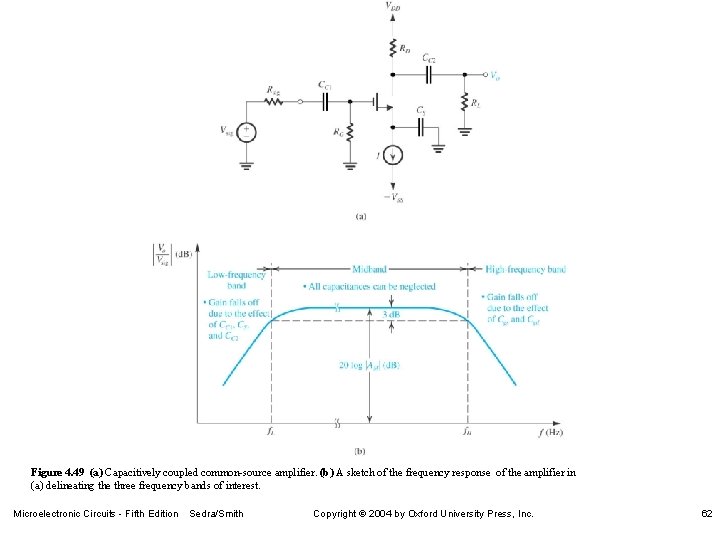

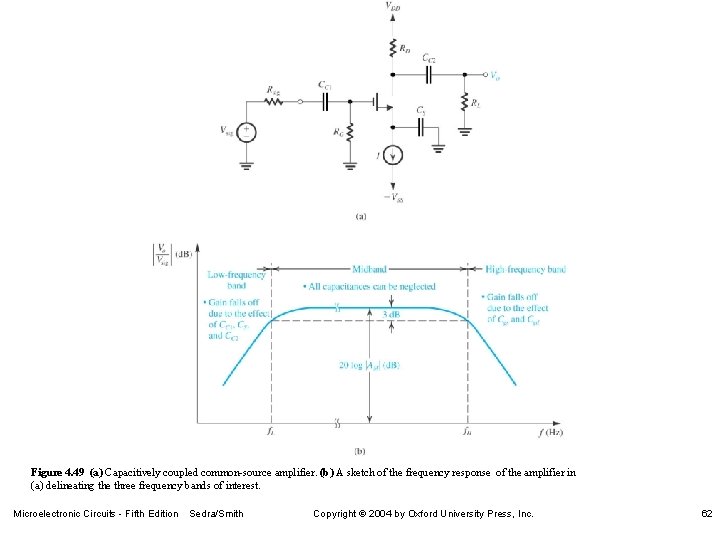

Figure 4. 49 (a) Capacitively coupled common-source amplifier. (b) A sketch of the frequency response of the amplifier in (a) delineating the three frequency bands of interest. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 62

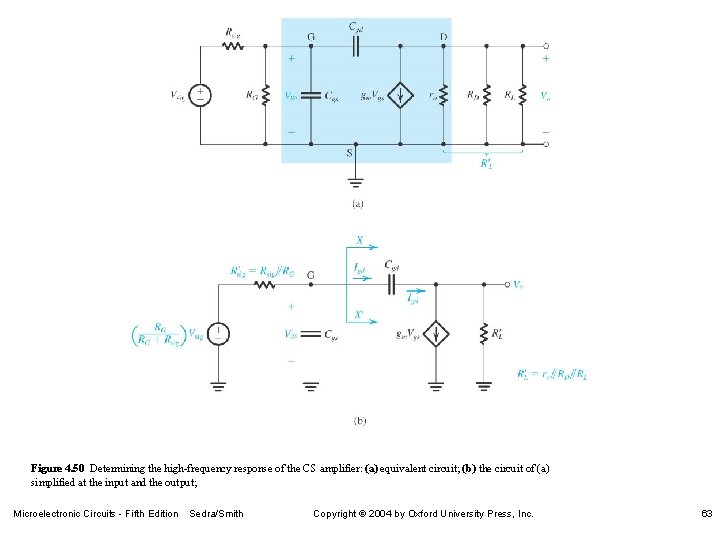

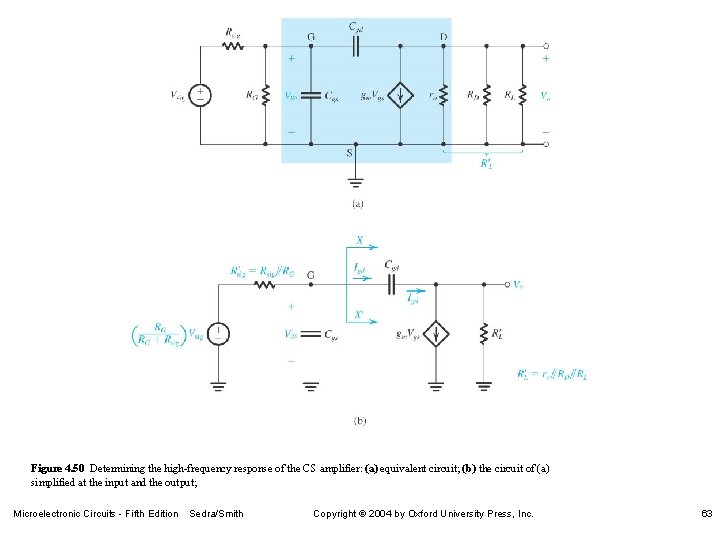

Figure 4. 50 Determining the high-frequency response of the CS amplifier: (a) equivalent circuit; (b) the circuit of (a) simplified at the input and the output; Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 63

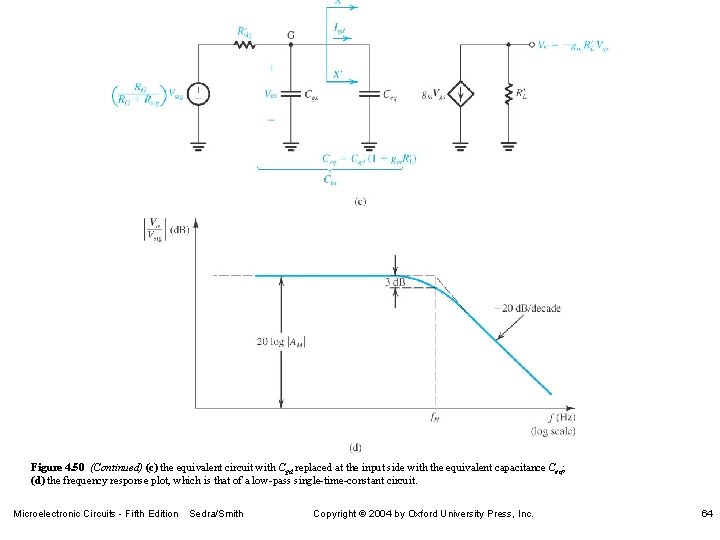

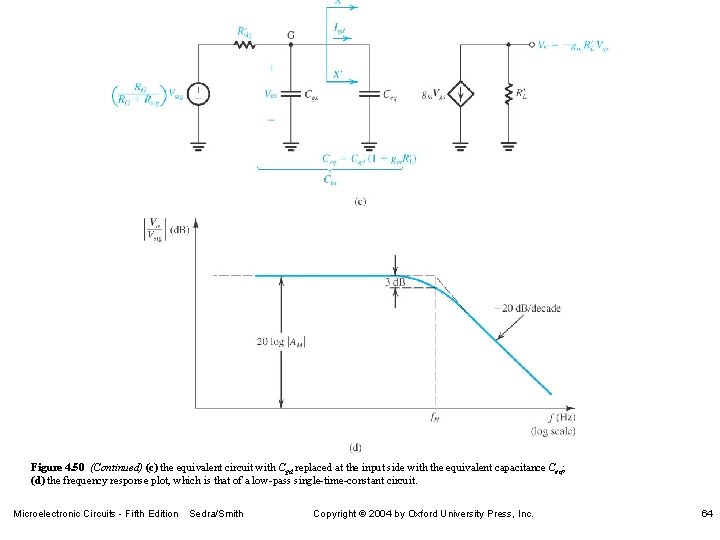

Figure 4. 50 (Continued) (c) the equivalent circuit with Cgd replaced at the input side with the equivalent capacitance Ceq; (d) the frequency response plot, which is that of a low-pass single-time-constant circuit. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 64

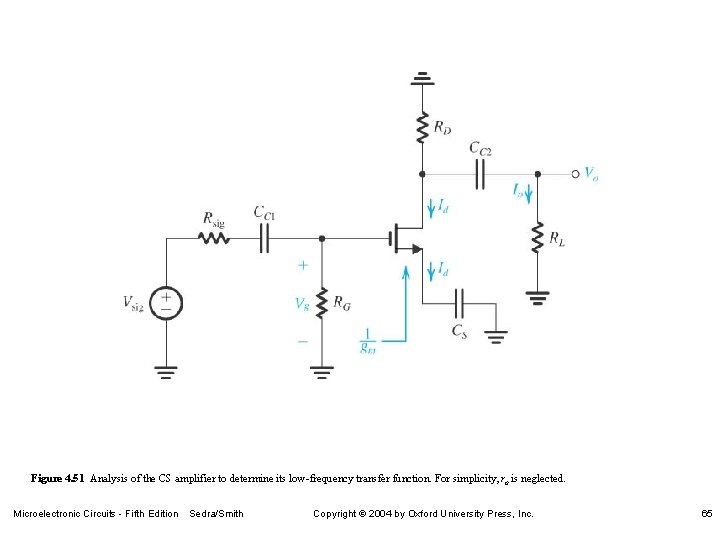

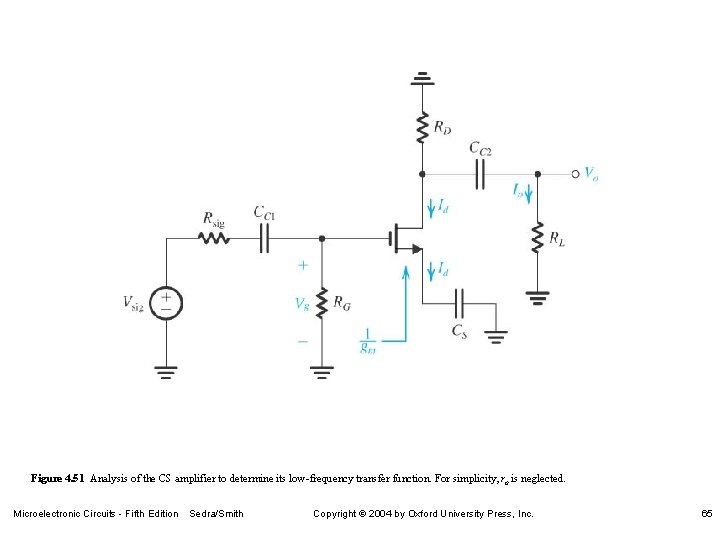

Figure 4. 51 Analysis of the CS amplifier to determine its low-frequency transfer function. For simplicity, ro is neglected. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 65

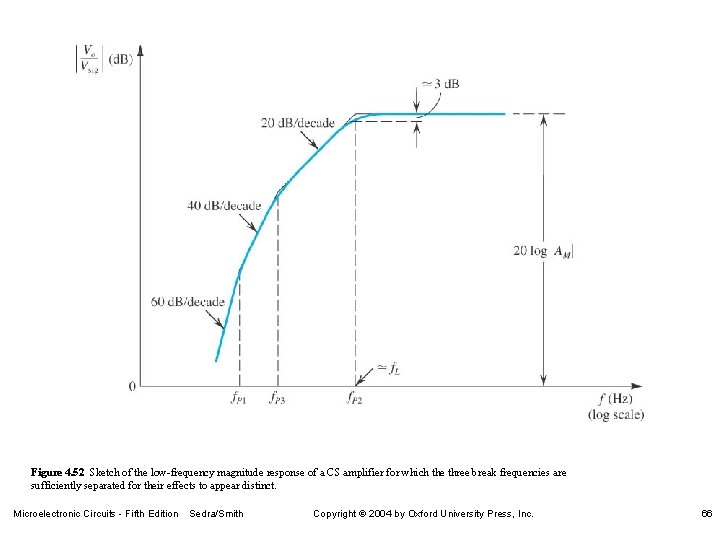

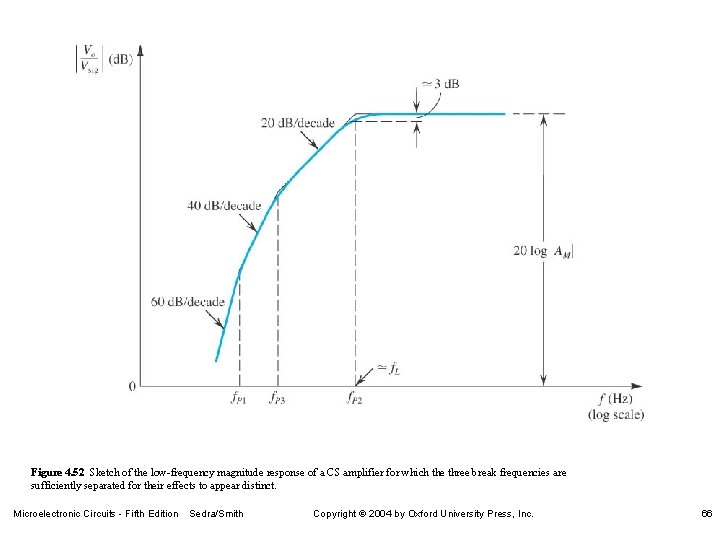

Figure 4. 52 Sketch of the low-frequency magnitude response of a CS amplifier for which the three break frequencies are sufficiently separated for their effects to appear distinct. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 66

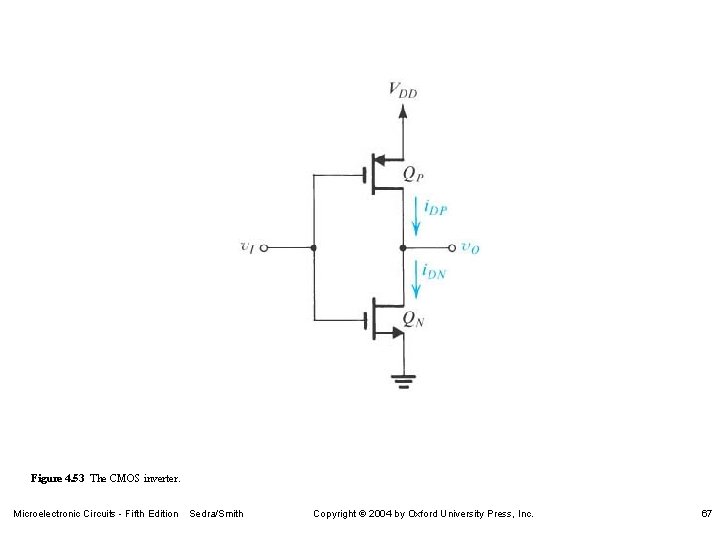

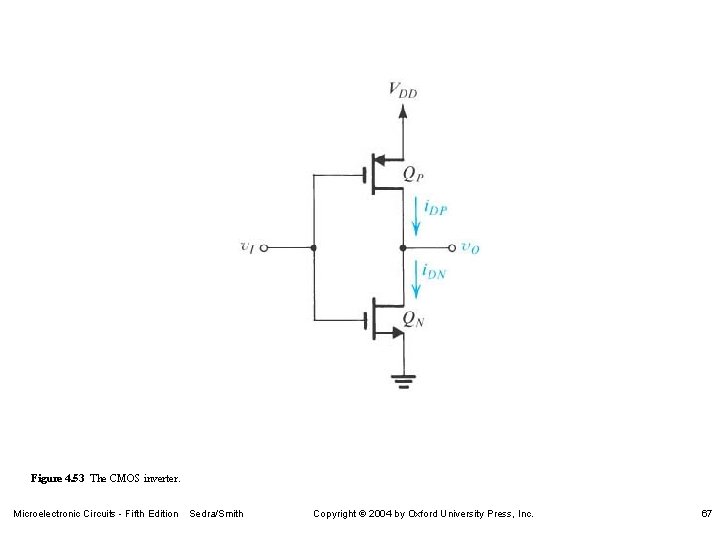

Figure 4. 53 The CMOS inverter. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 67

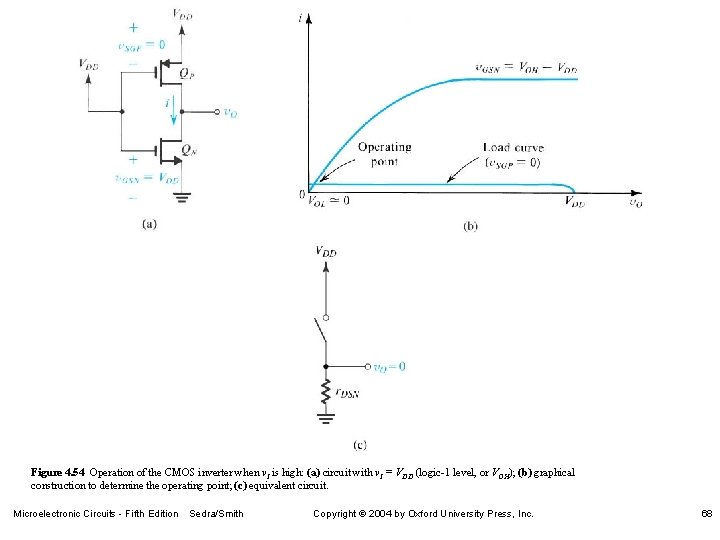

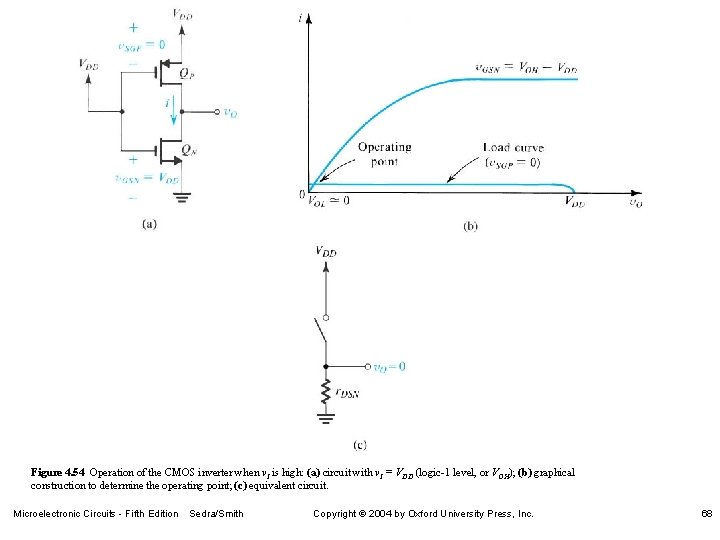

Figure 4. 54 Operation of the CMOS inverter when v. I is high: (a) circuit with v. I = VDD (logic-1 level, or VOH); (b) graphical construction to determine the operating point; (c) equivalent circuit. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 68

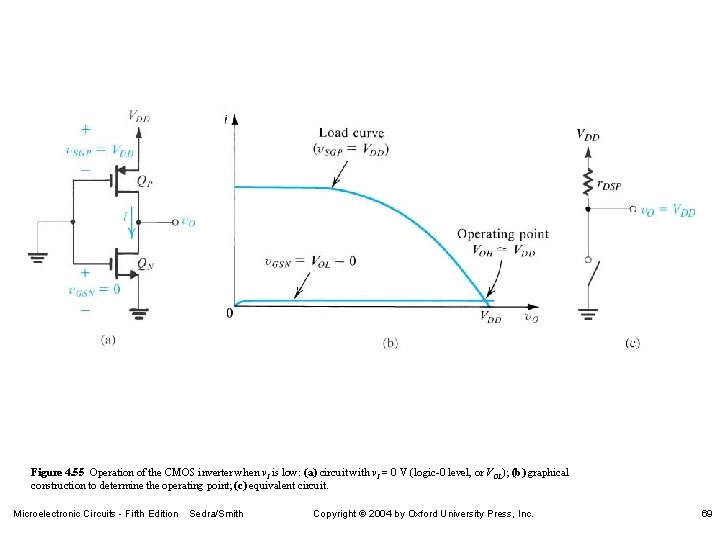

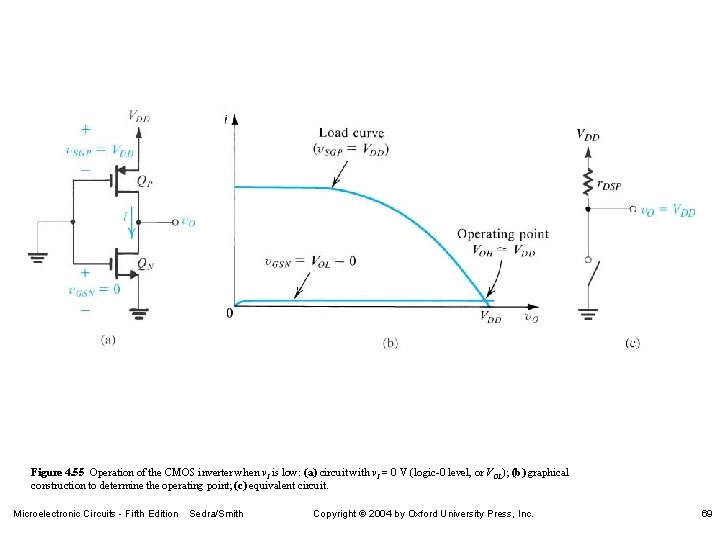

Figure 4. 55 Operation of the CMOS inverter when v. I is low: (a) circuit with v. I = 0 V (logic-0 level, or VOL); (b) graphical construction to determine the operating point; (c) equivalent circuit. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 69

Figure 4. 56 The voltage transfer characteristic of the CMOS inverter. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 70

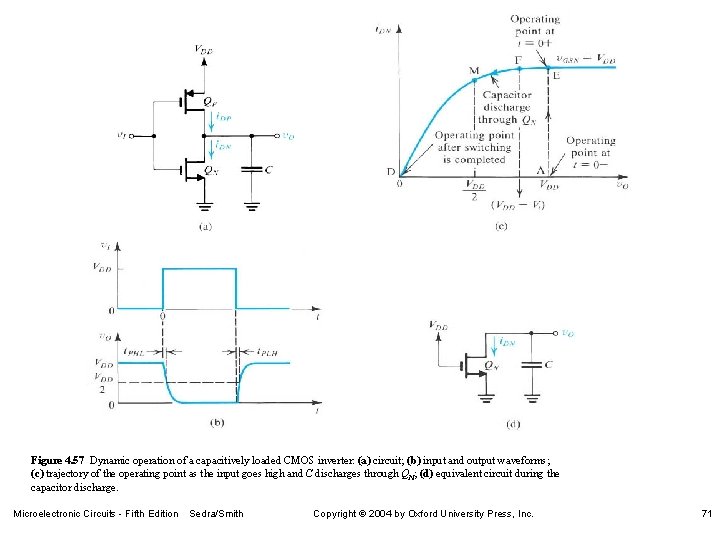

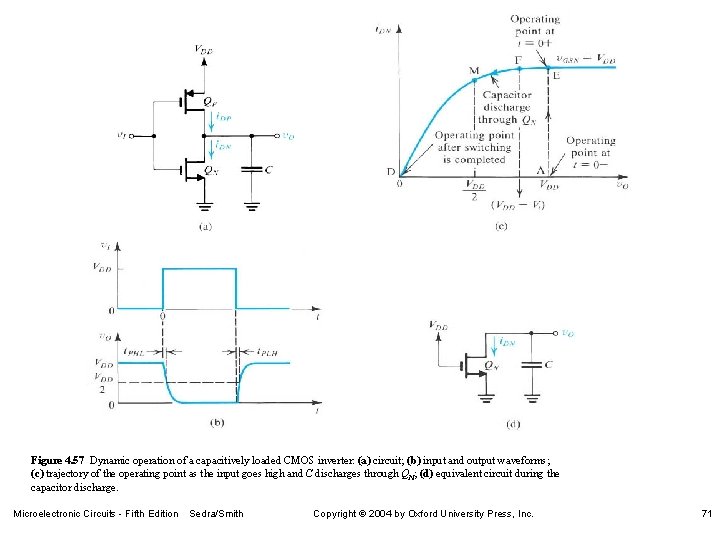

Figure 4. 57 Dynamic operation of a capacitively loaded CMOS inverter: (a) circuit; (b) input and output waveforms; (c) trajectory of the operating point as the input goes high and C discharges through QN; (d) equivalent circuit during the capacitor discharge. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 71

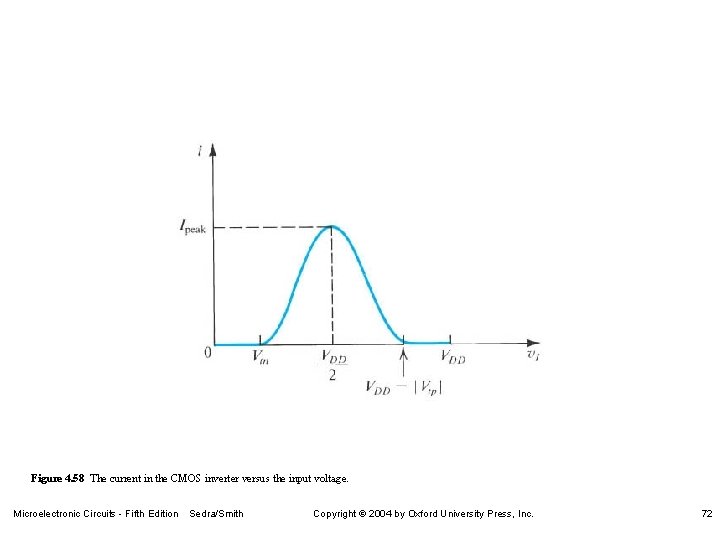

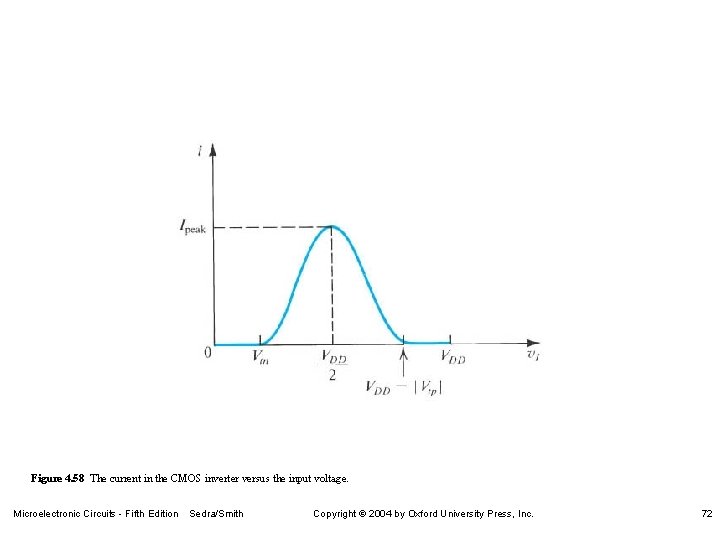

Figure 4. 58 The current in the CMOS inverter versus the input voltage. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 72

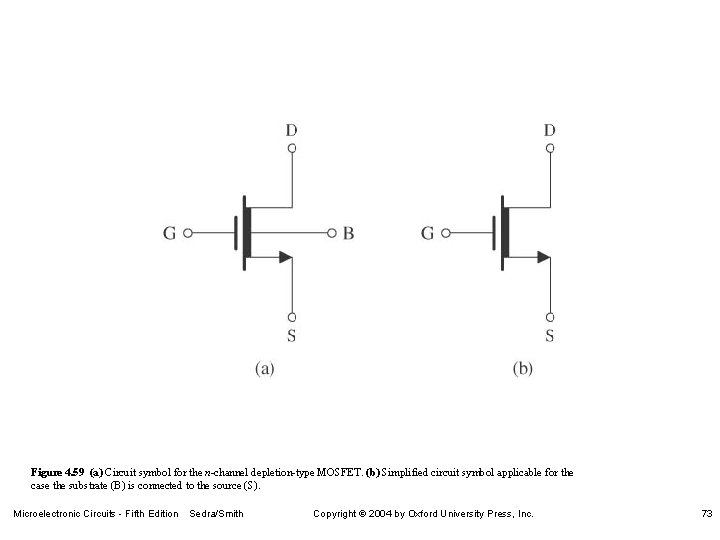

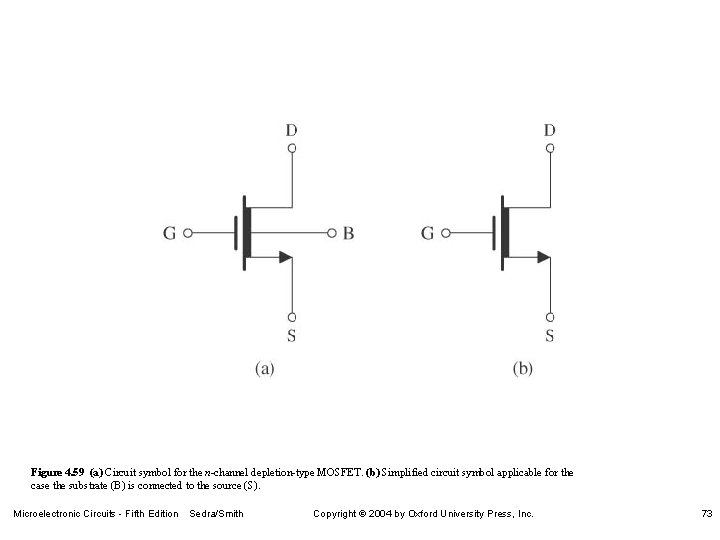

Figure 4. 59 (a) Circuit symbol for the n-channel depletion-type MOSFET. (b) Simplified circuit symbol applicable for the case the substrate (B) is connected to the source (S). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 73

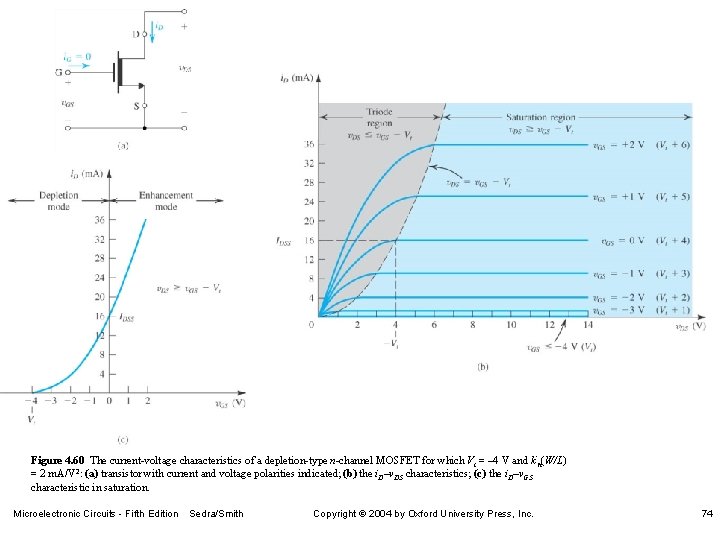

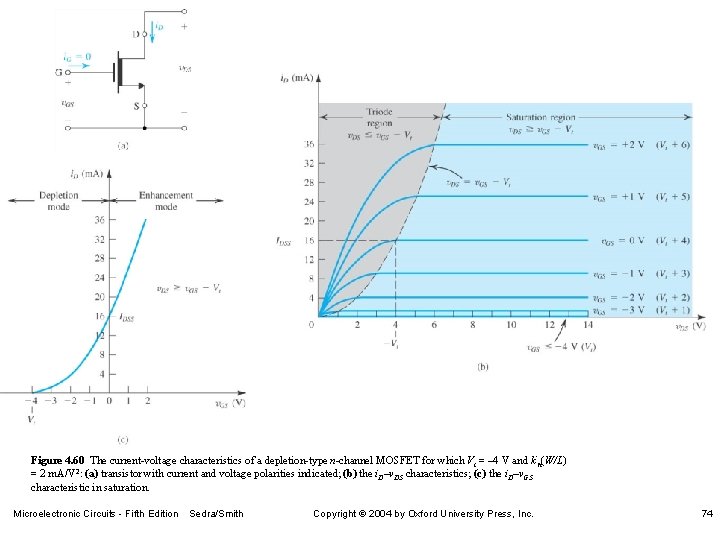

Figure 4. 60 The current-voltage characteristics of a depletion-type n-channel MOSFET for which Vt = – 4 V and k¢n(W/L) = 2 m. A/V 2: (a) transistor with current and voltage polarities indicated; (b) the i. D–v. DS characteristics; (c) the i. D–v. GS characteristic in saturation. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 74

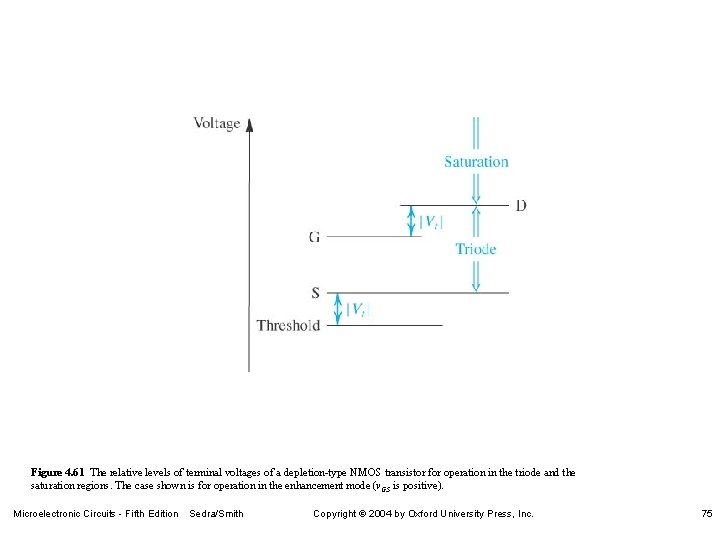

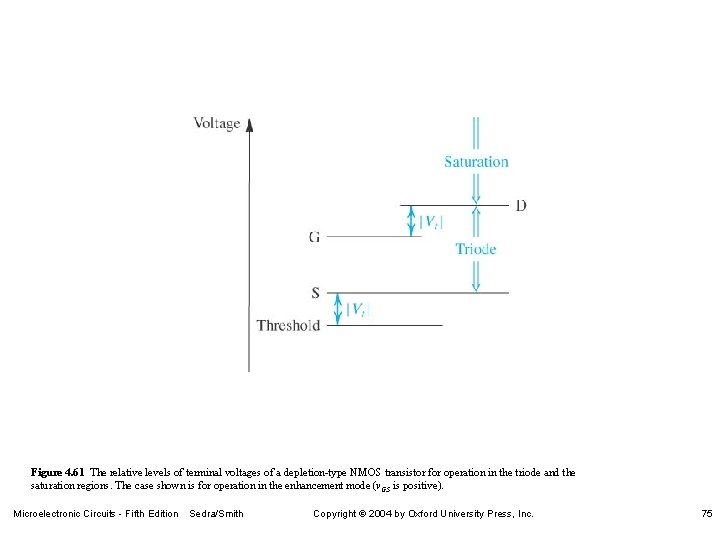

Figure 4. 61 The relative levels of terminal voltages of a depletion-type NMOS transistor for operation in the triode and the saturation regions. The case shown is for operation in the enhancement mode (v. GS is positive). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 75

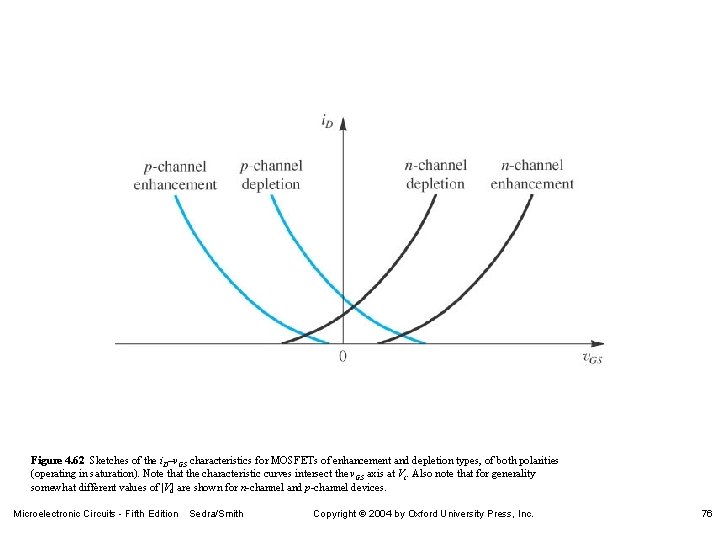

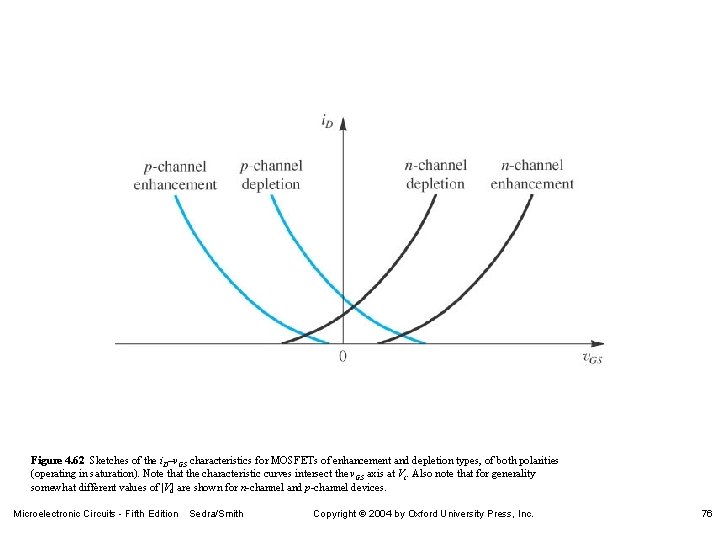

Figure 4. 62 Sketches of the i. D–v. GS characteristics for MOSFETs of enhancement and depletion types, of both polarities (operating in saturation). Note that the characteristic curves intersect the v. GS axis at Vt. Also note that for generality somewhat different values of |Vt| are shown for n-channel and p-channel devices. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 76

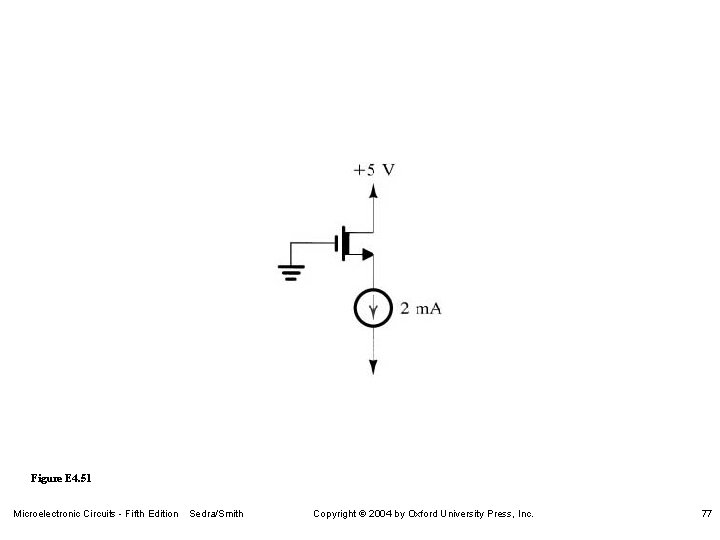

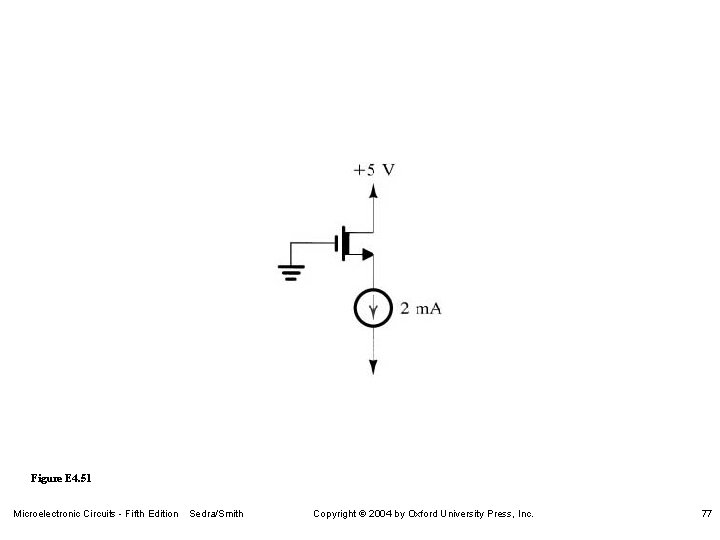

Figure E 4. 51 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 77

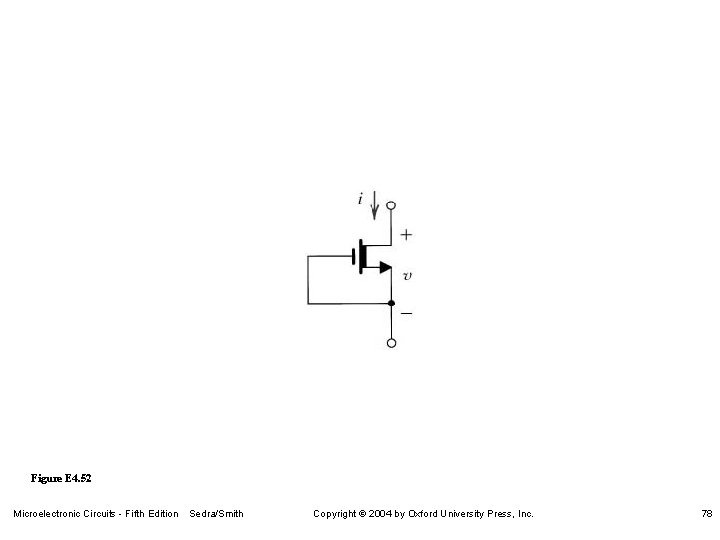

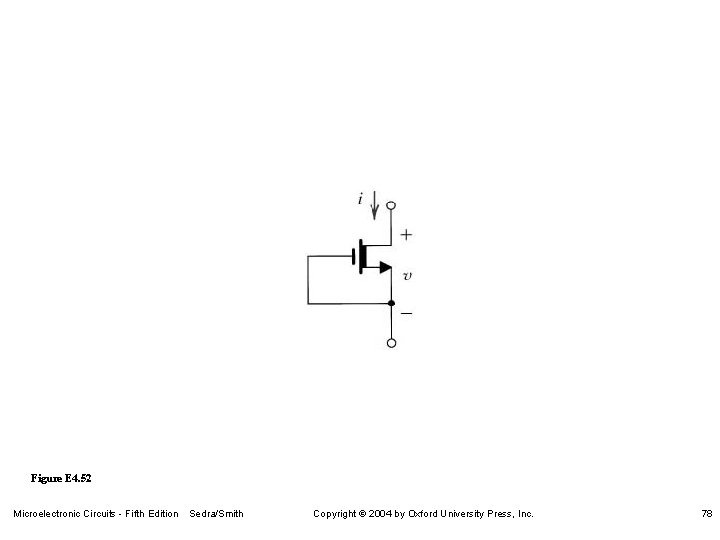

Figure E 4. 52 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 78

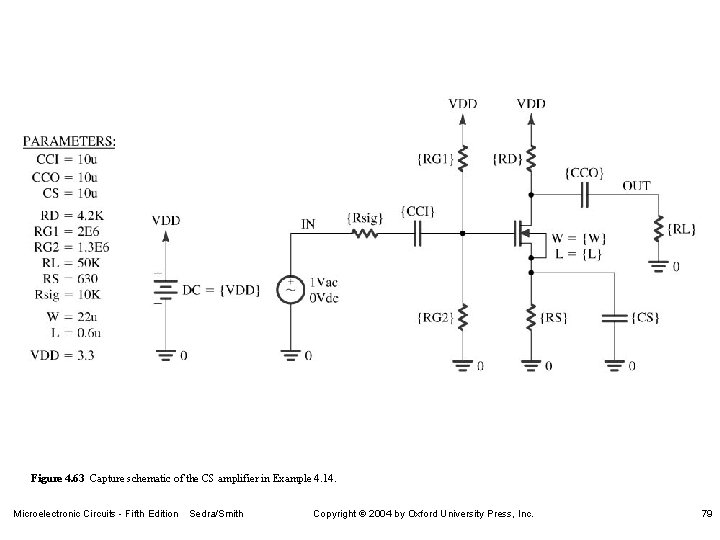

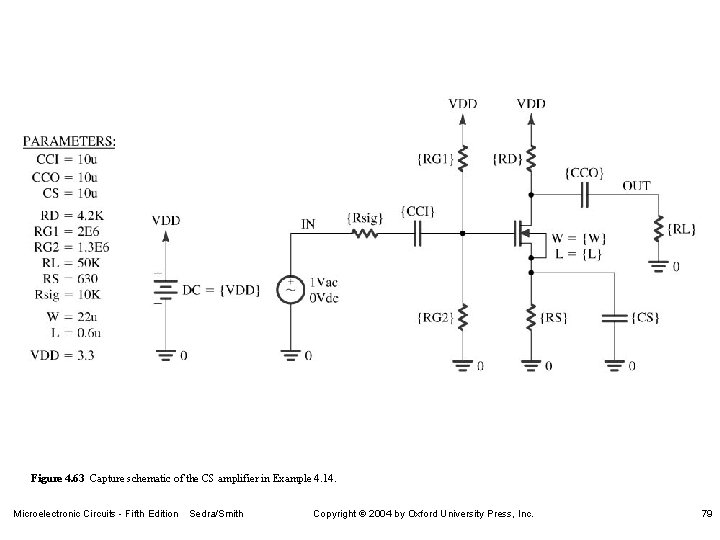

Figure 4. 63 Capture schematic of the CS amplifier in Example 4. 14. Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 79

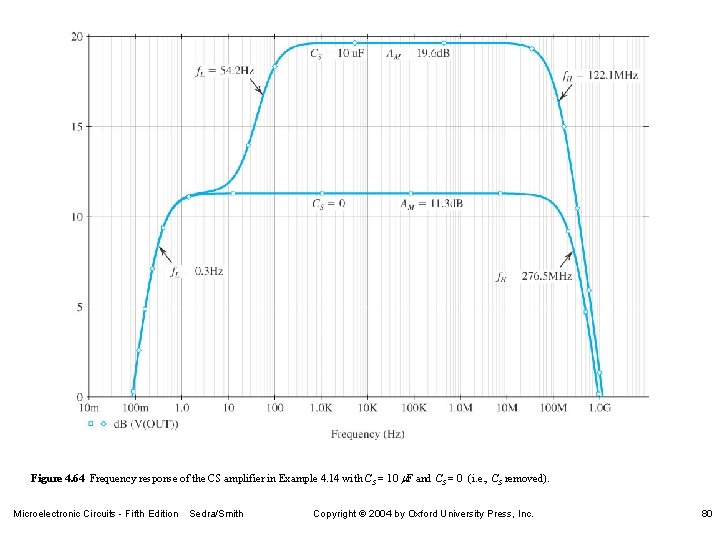

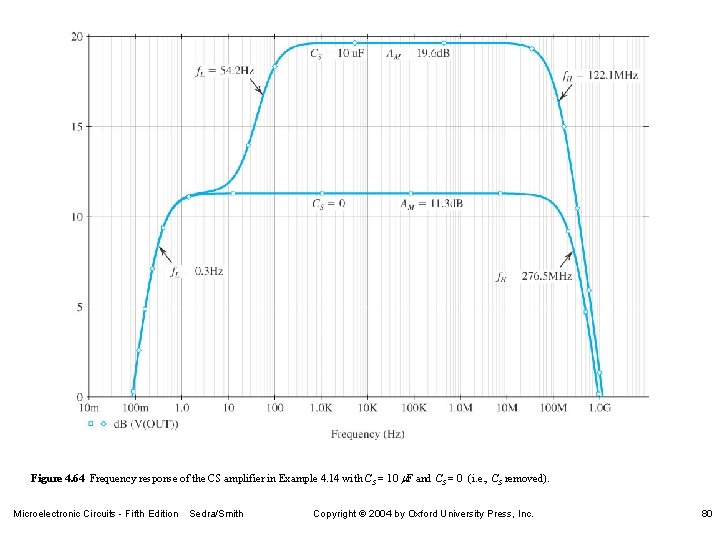

Figure 4. 64 Frequency response of the CS amplifier in Example 4. 14 with CS = 10 m. F and CS = 0 (i. e. , CS removed). Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 80

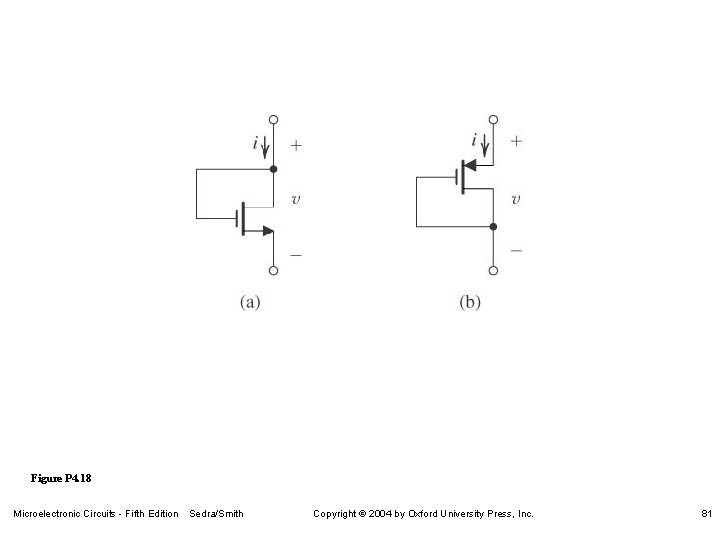

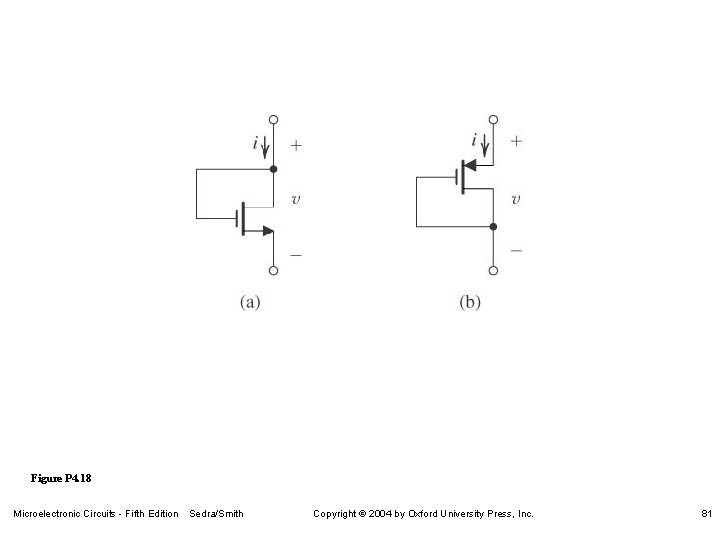

Figure P 4. 18 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 81

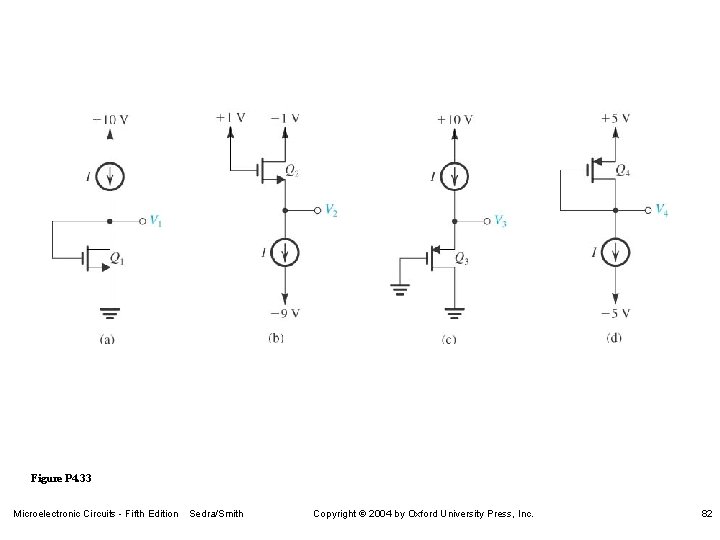

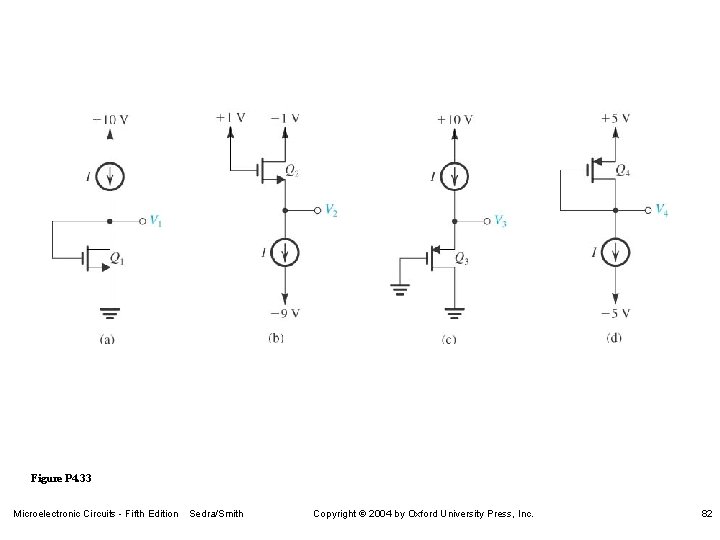

Figure P 4. 33 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 82

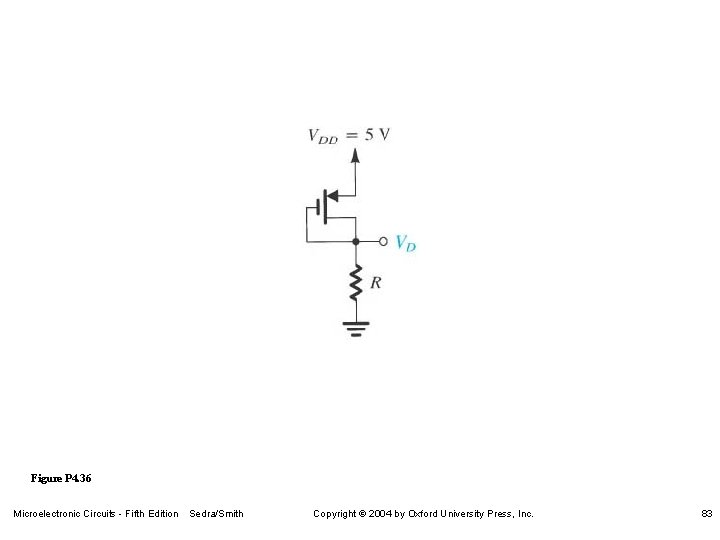

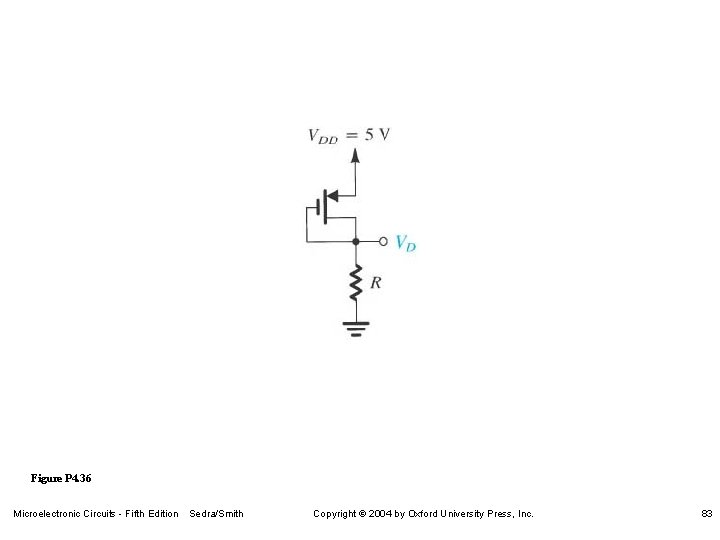

Figure P 4. 36 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 83

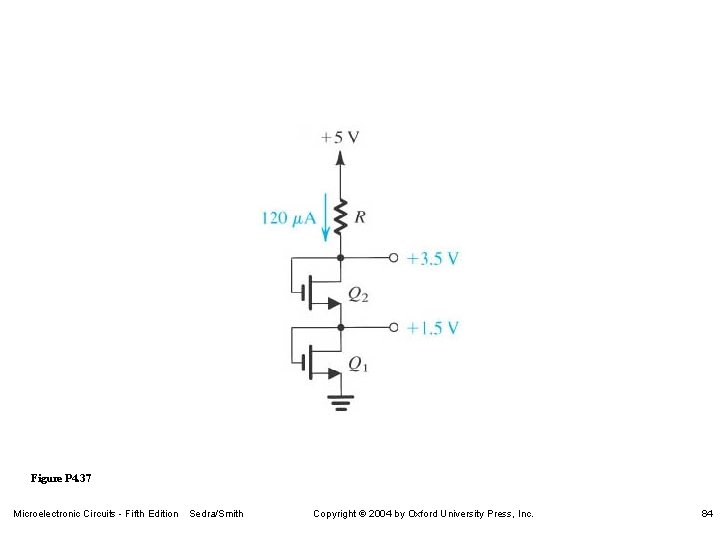

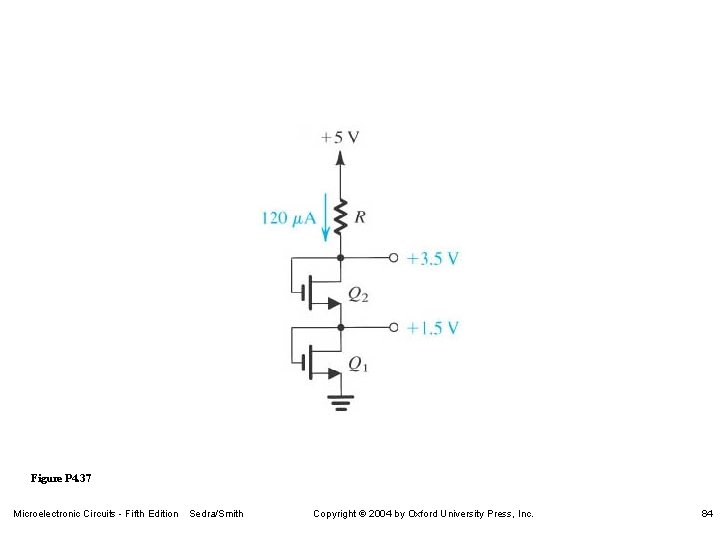

Figure P 4. 37 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 84

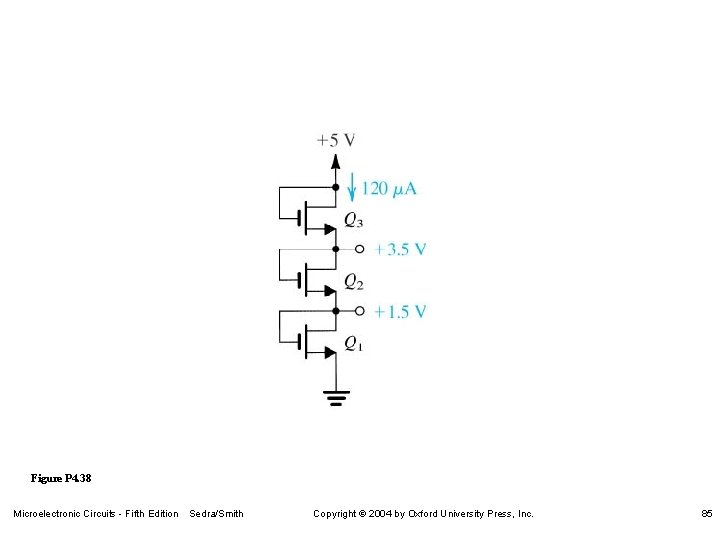

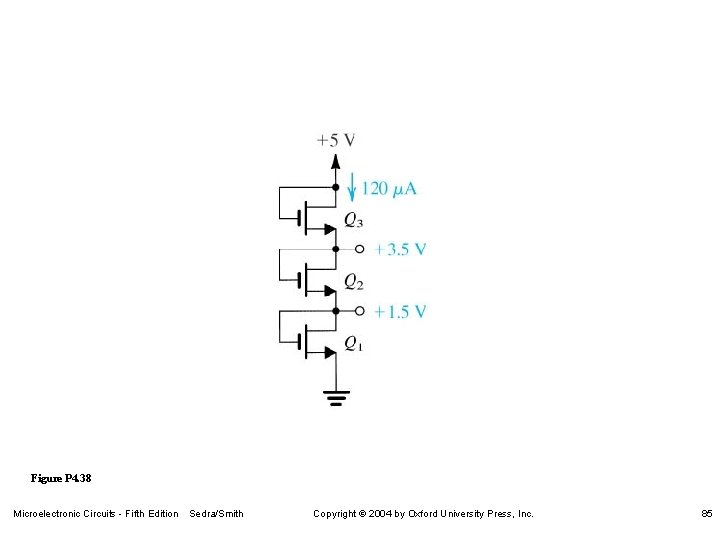

Figure P 4. 38 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 85

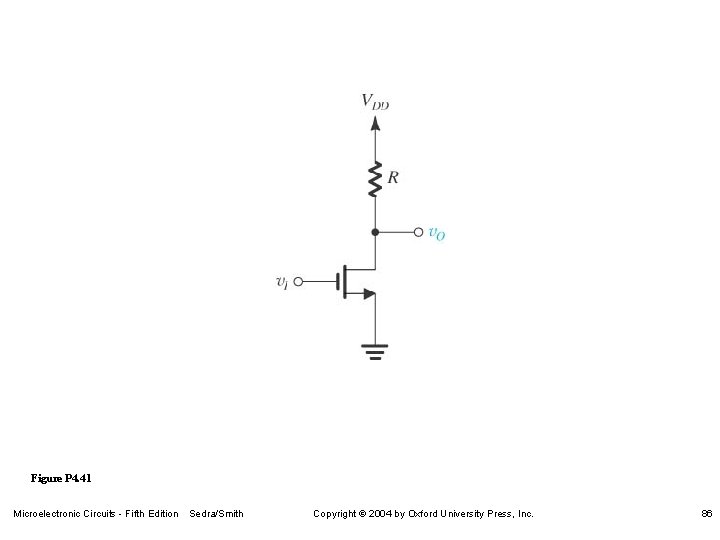

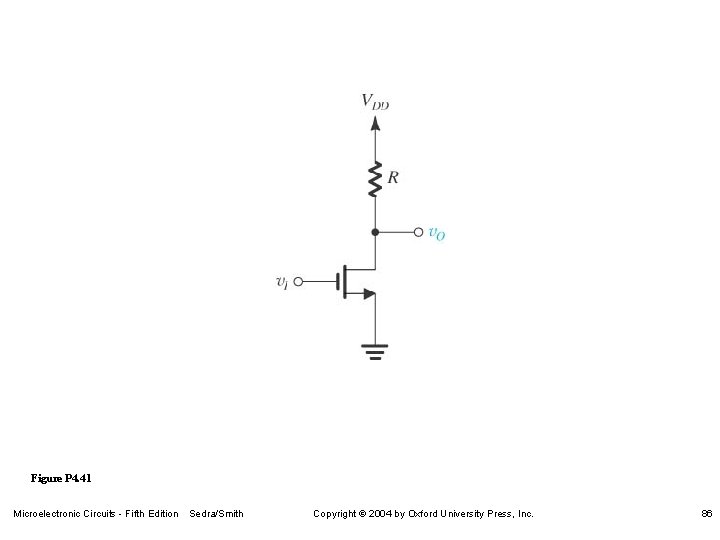

Figure P 4. 41 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 86

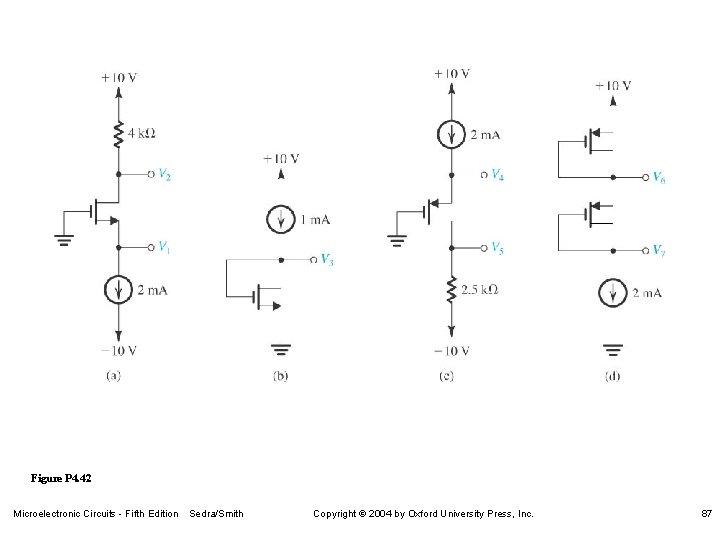

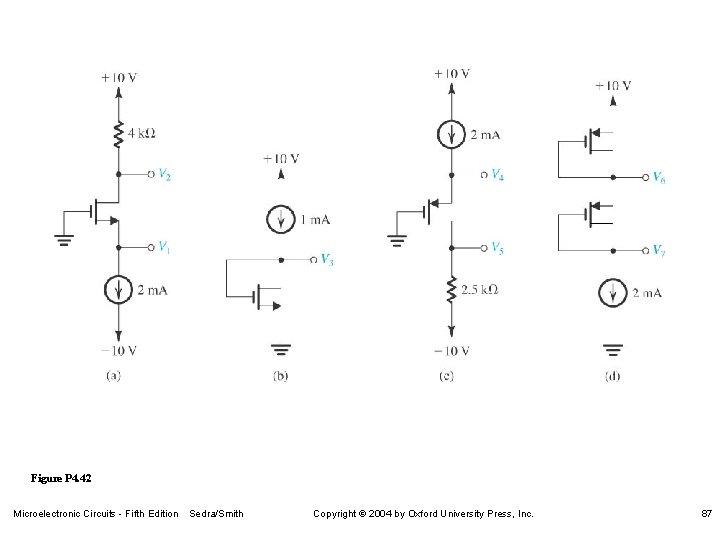

Figure P 4. 42 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 87

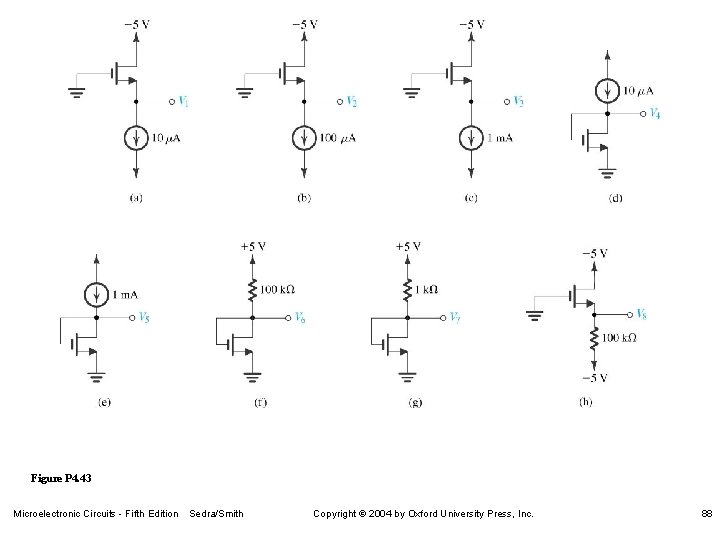

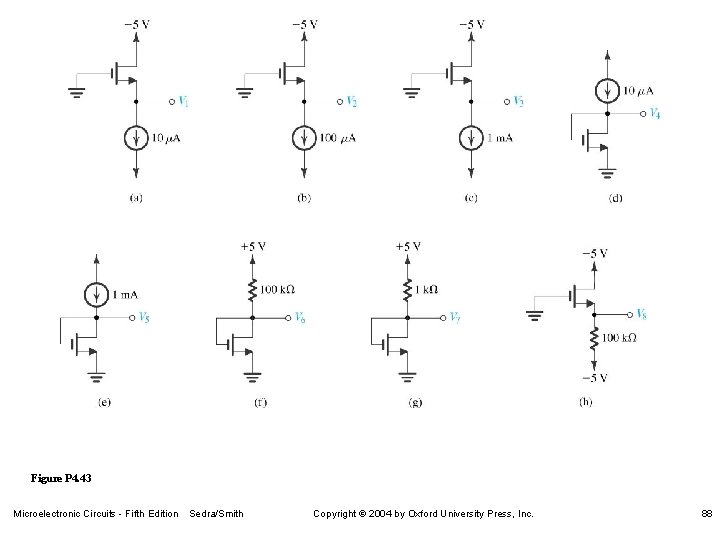

Figure P 4. 43 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 88

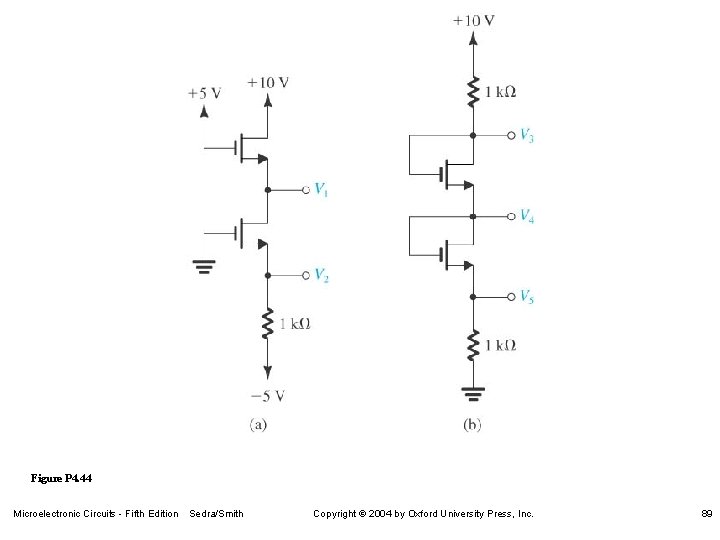

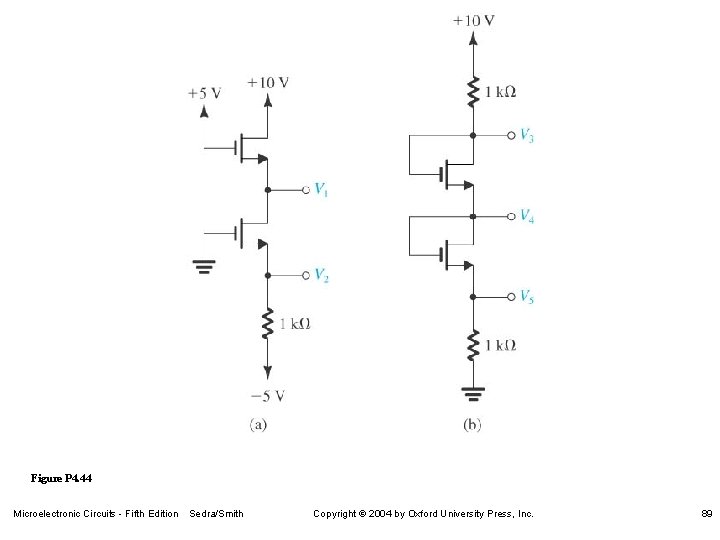

Figure P 4. 44 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 89

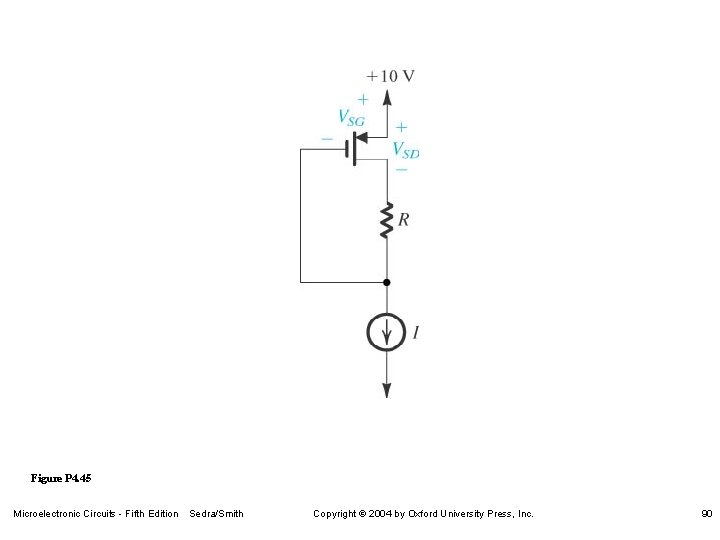

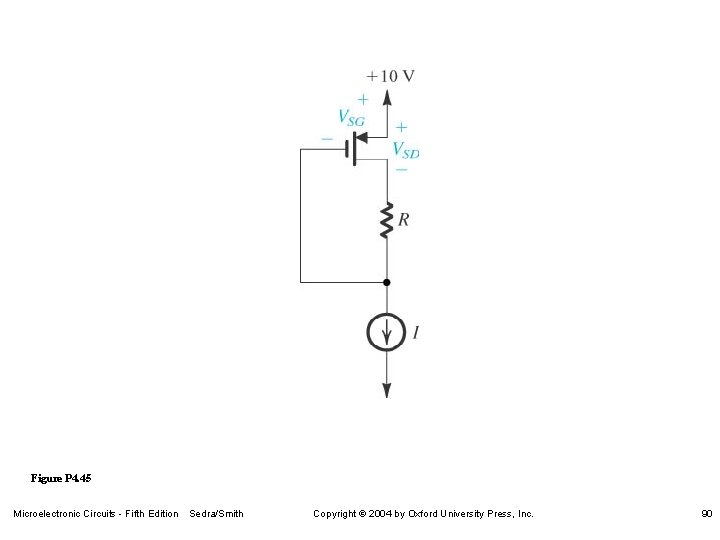

Figure P 4. 45 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 90

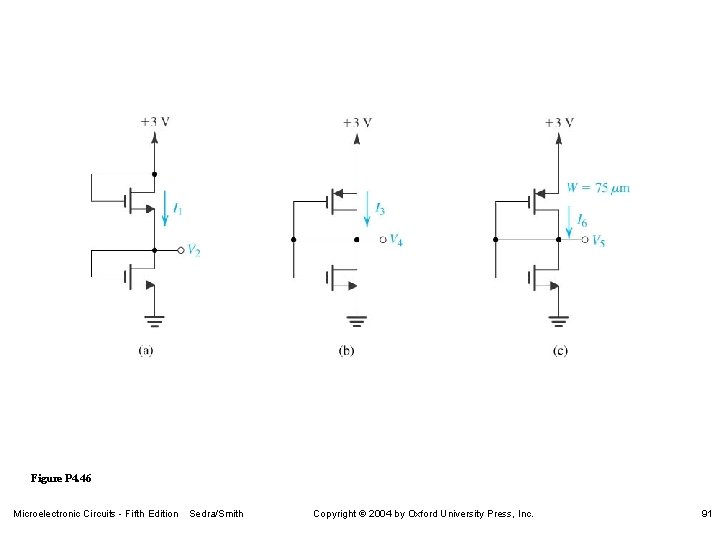

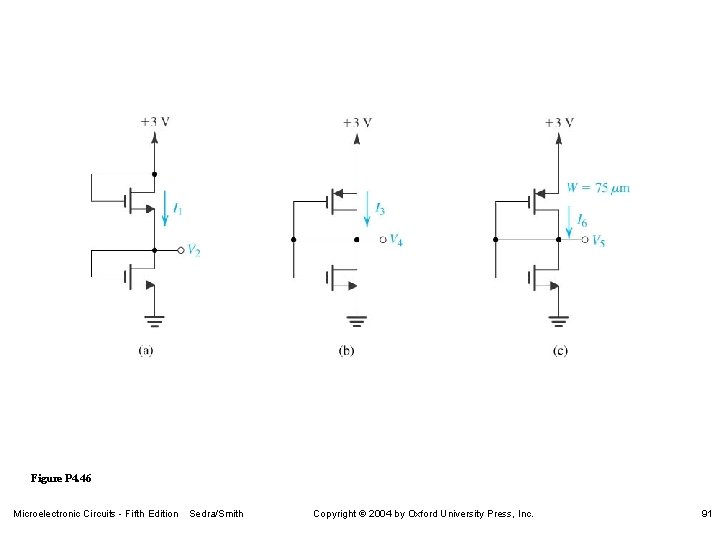

Figure P 4. 46 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 91

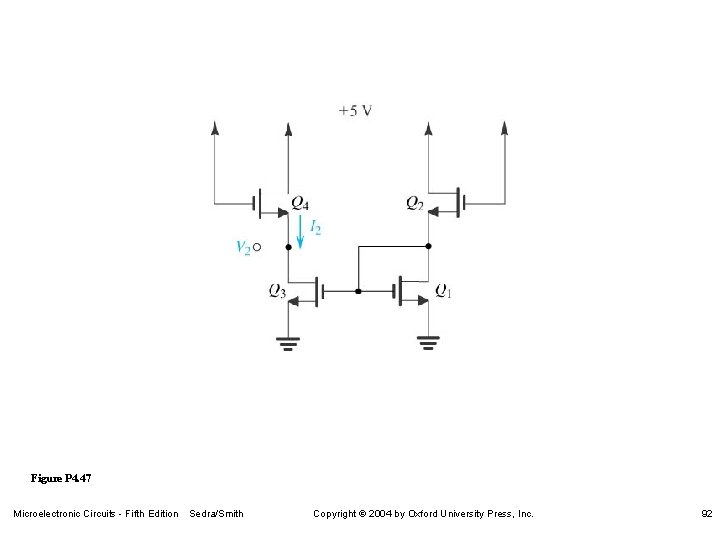

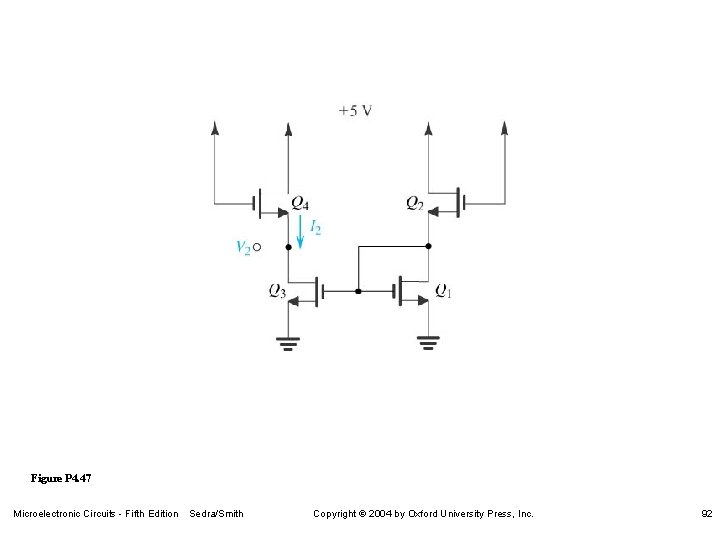

Figure P 4. 47 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 92

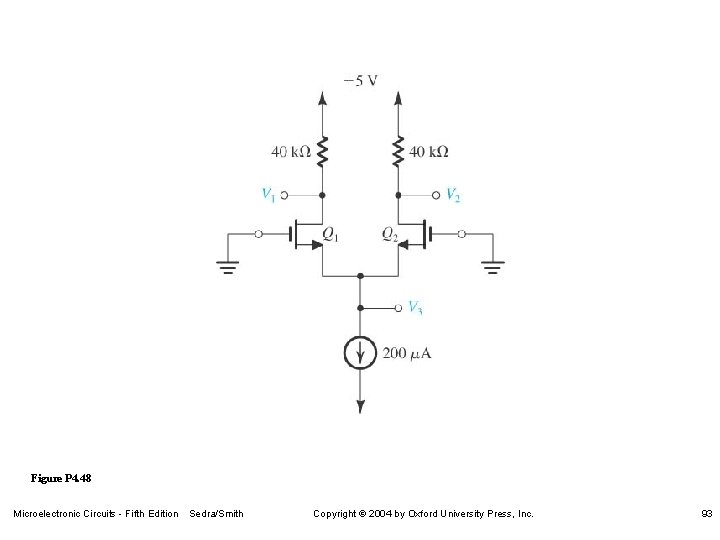

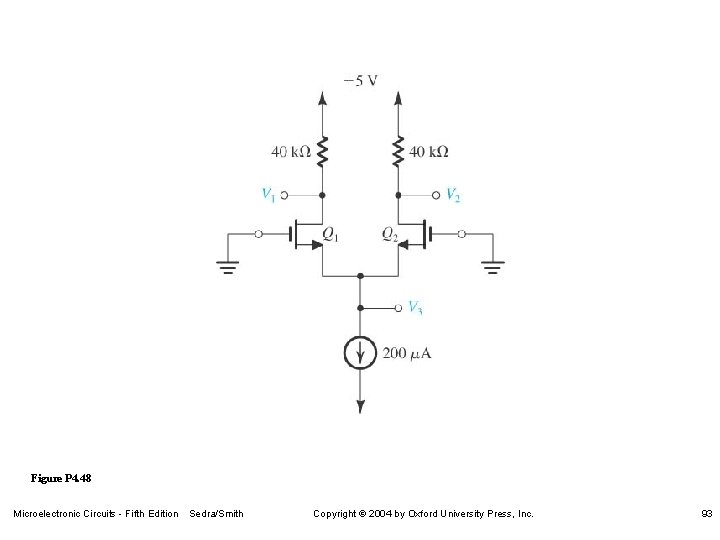

Figure P 4. 48 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 93

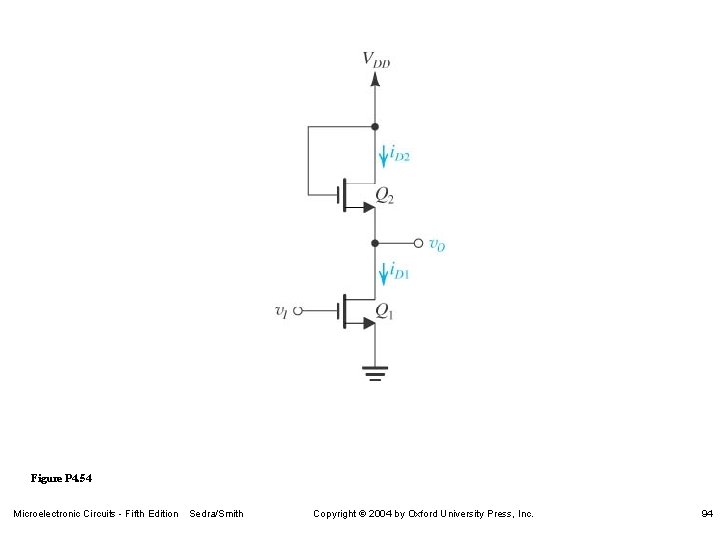

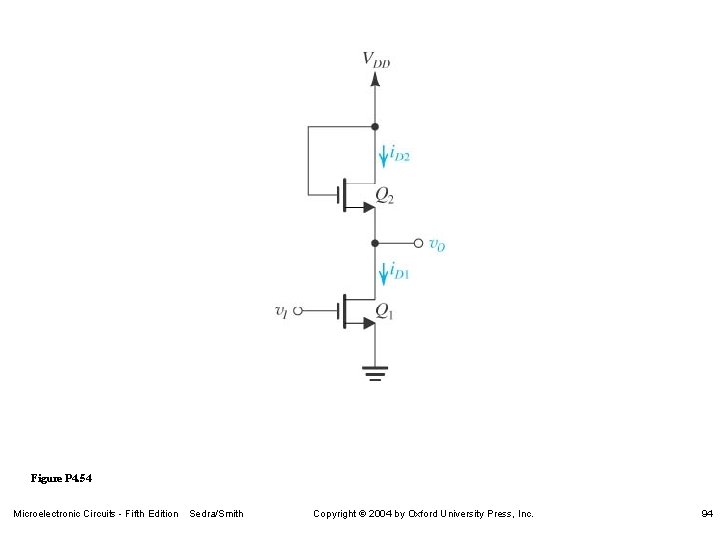

Figure P 4. 54 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 94

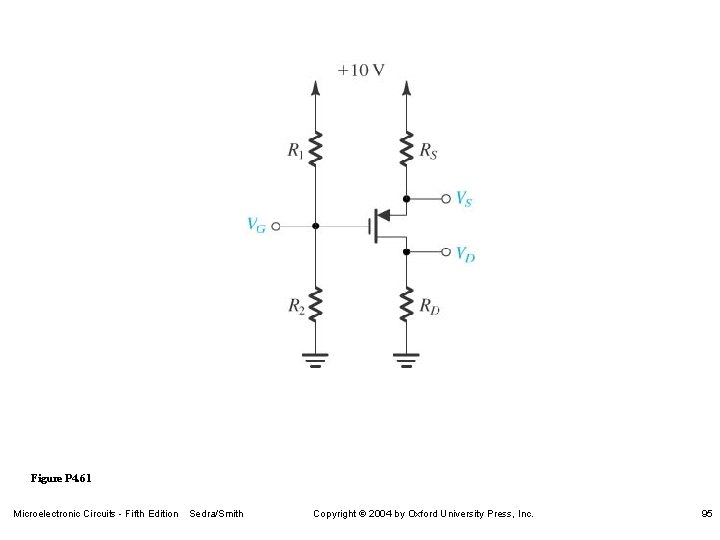

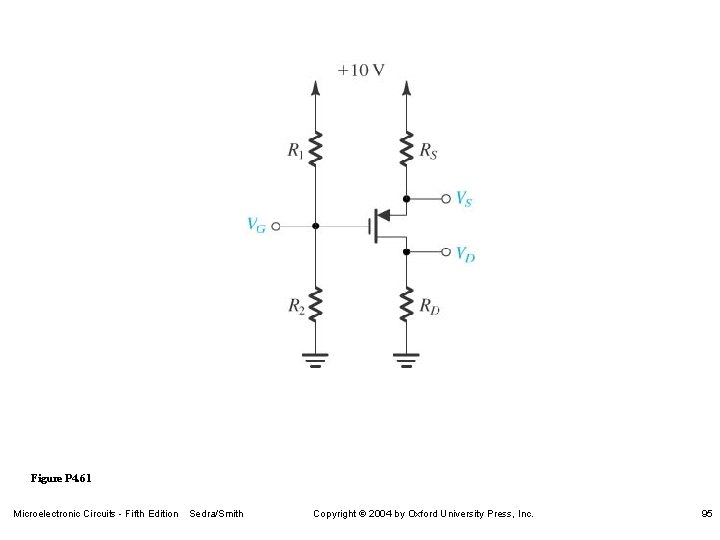

Figure P 4. 61 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 95

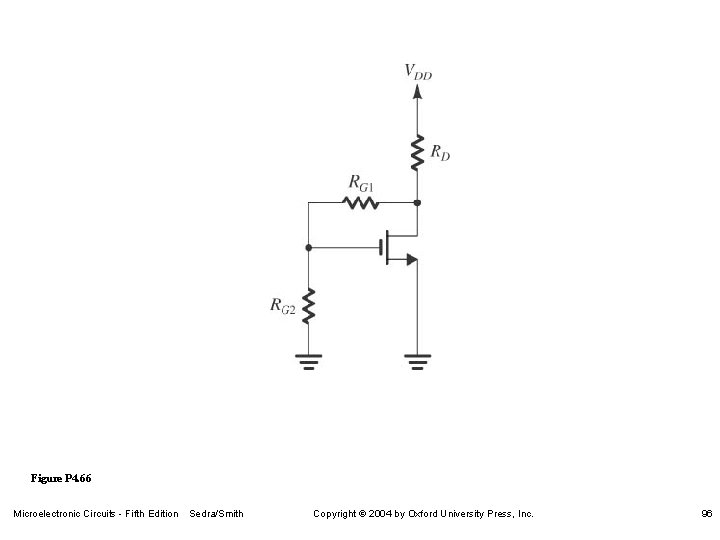

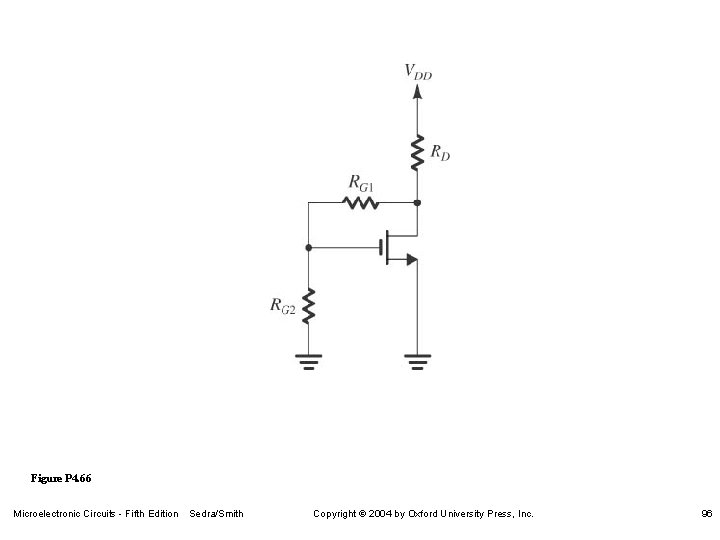

Figure P 4. 66 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 96

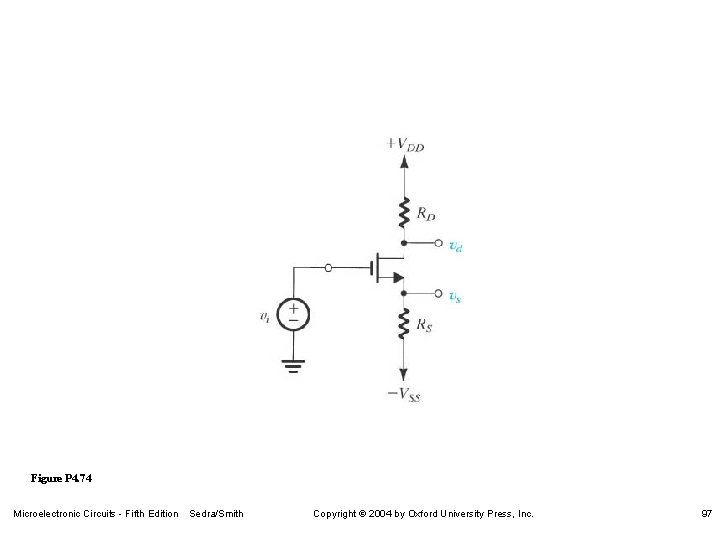

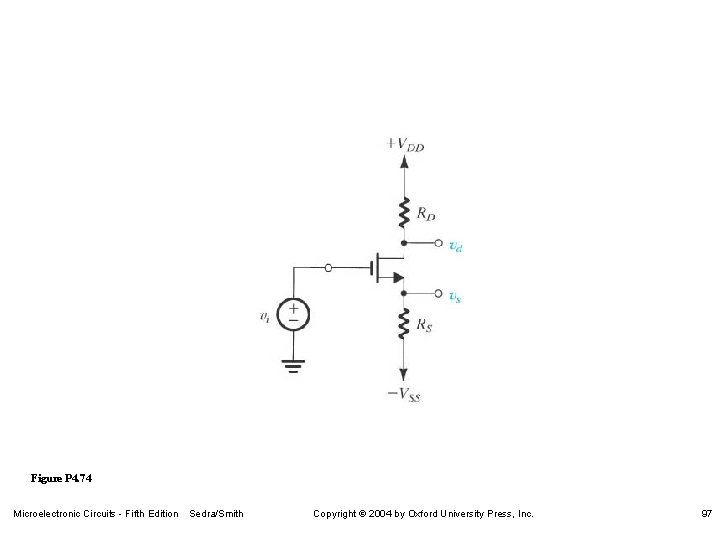

Figure P 4. 74 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 97

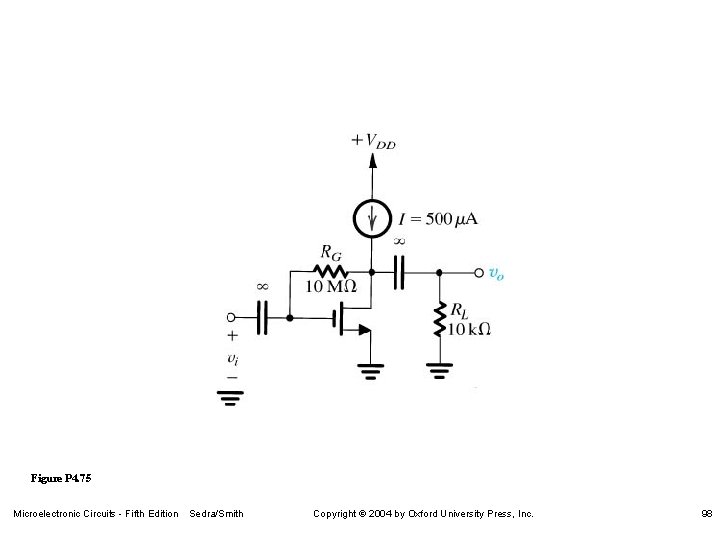

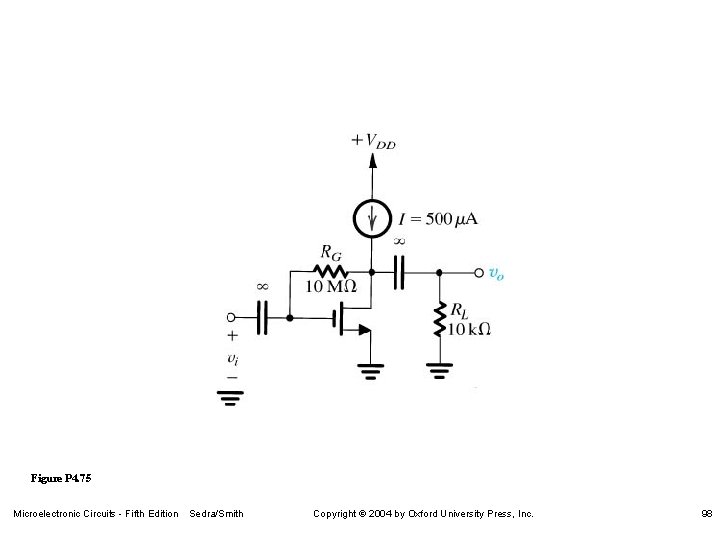

Figure P 4. 75 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 98

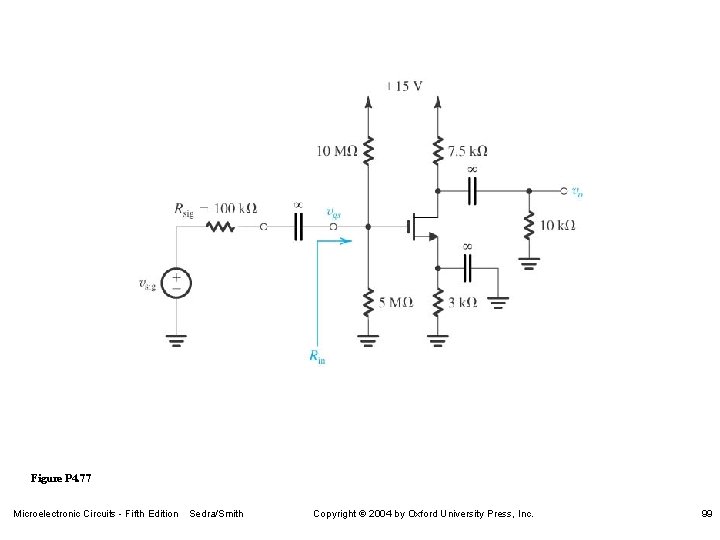

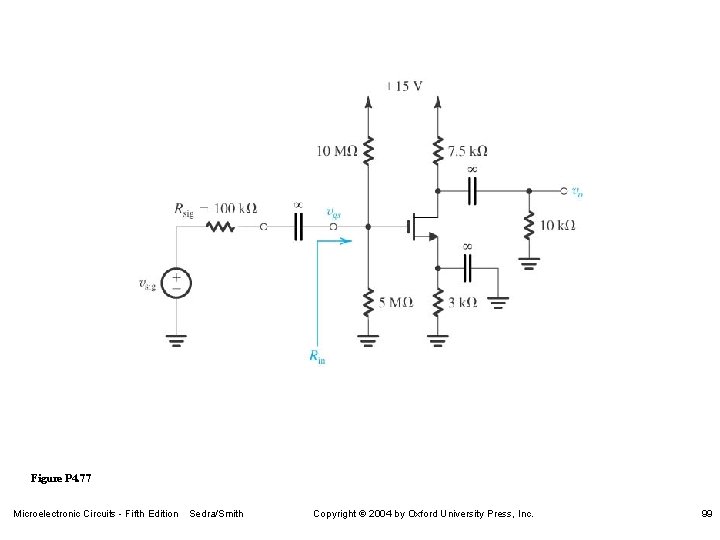

Figure P 4. 77 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 99

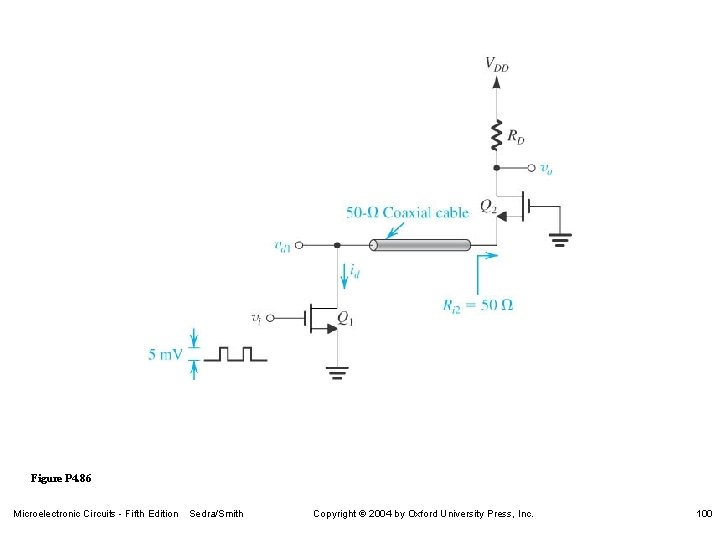

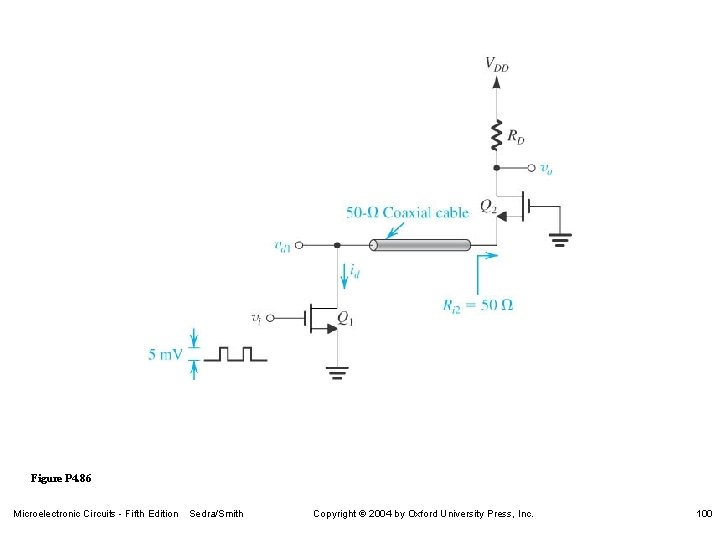

Figure P 4. 86 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 100

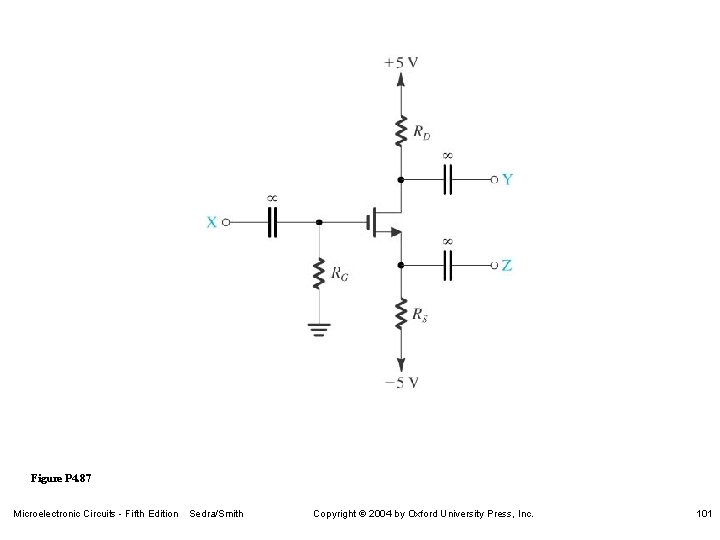

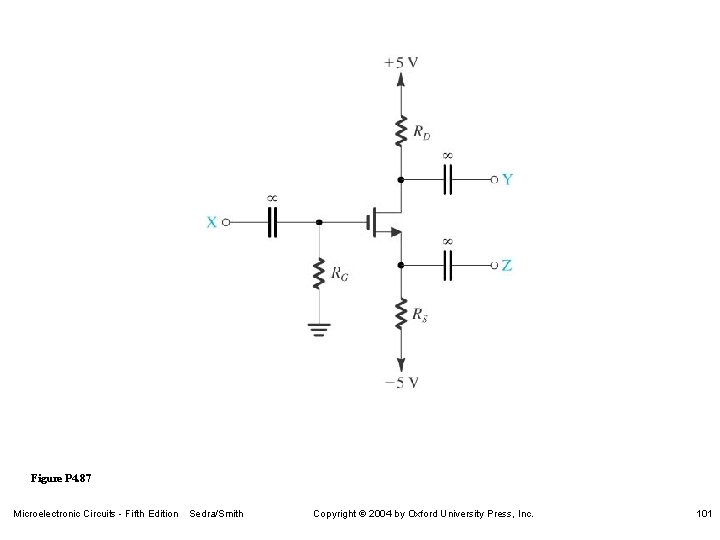

Figure P 4. 87 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 101

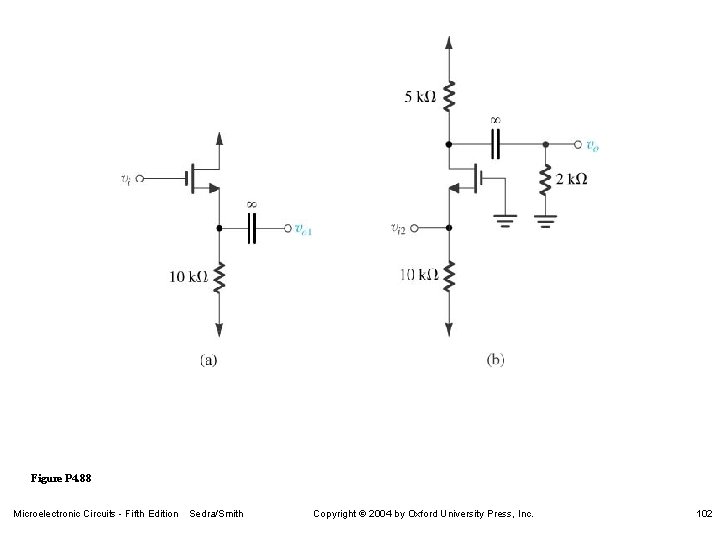

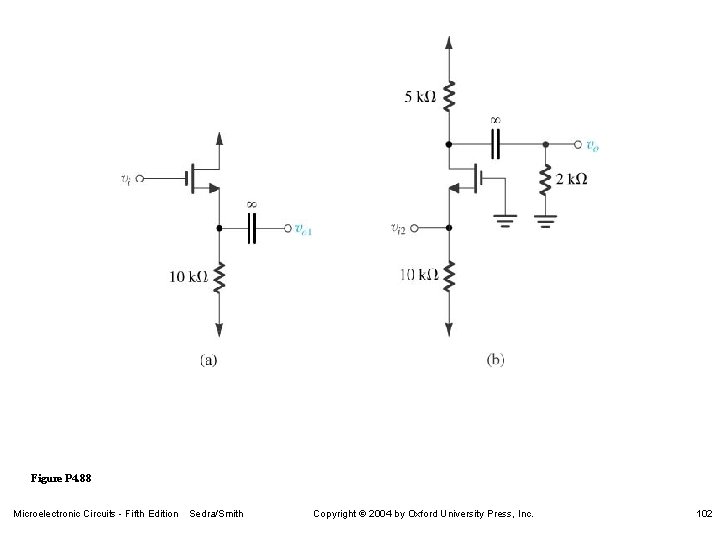

Figure P 4. 88 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 102

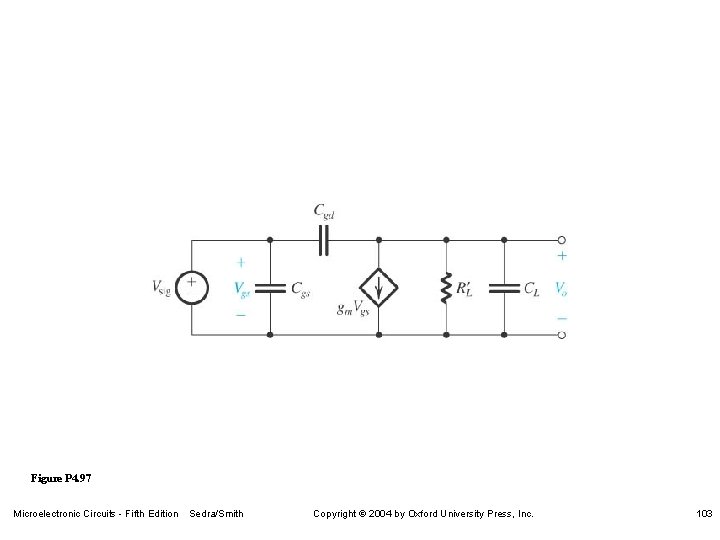

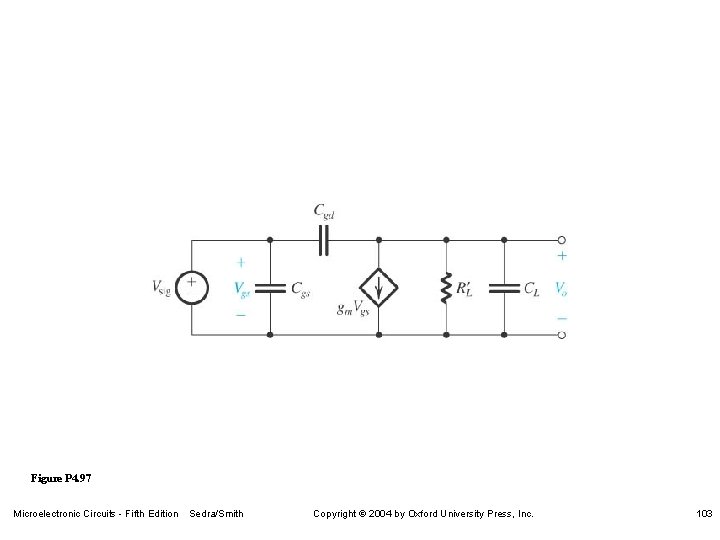

Figure P 4. 97 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 103

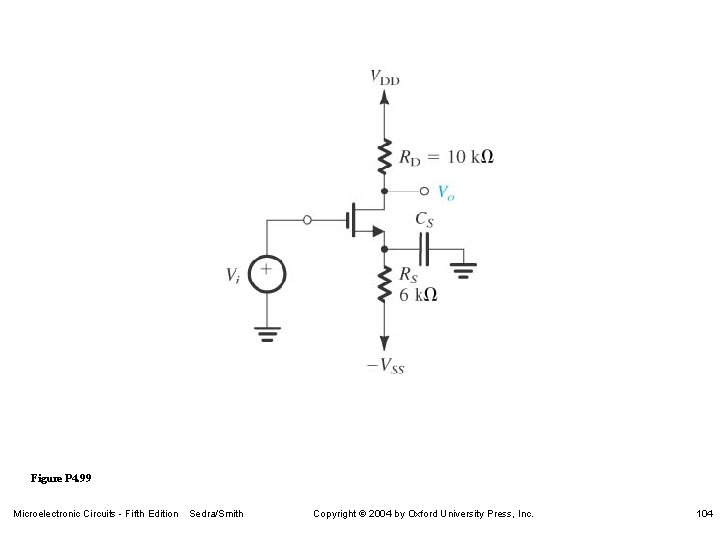

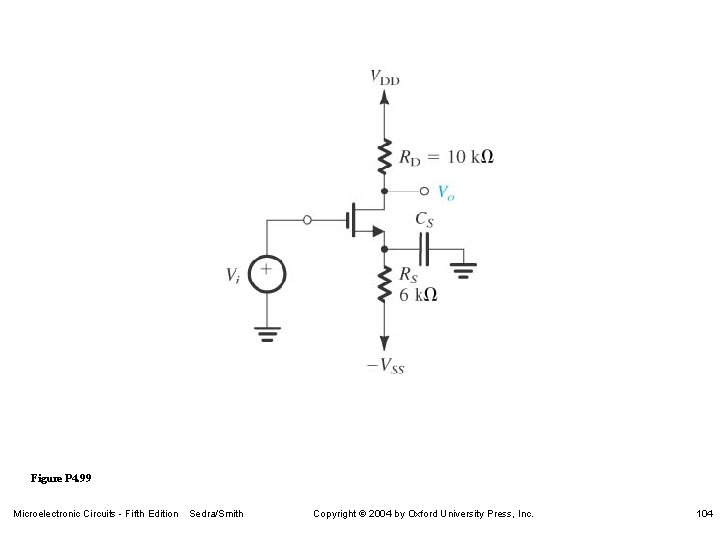

Figure P 4. 99 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 104

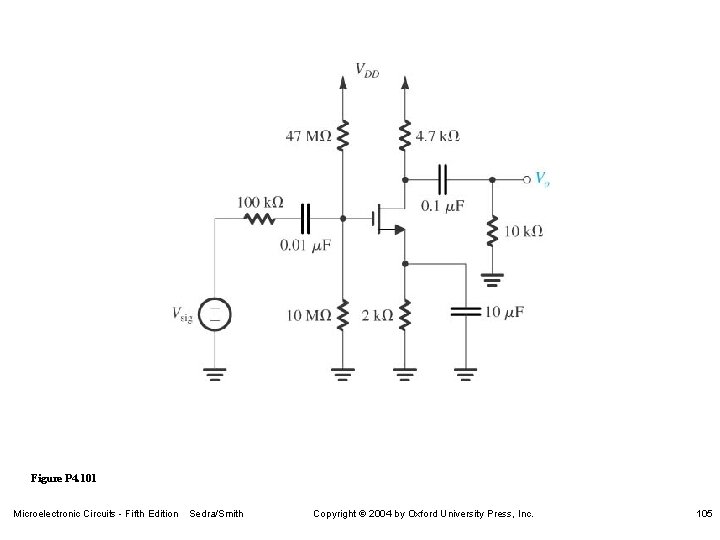

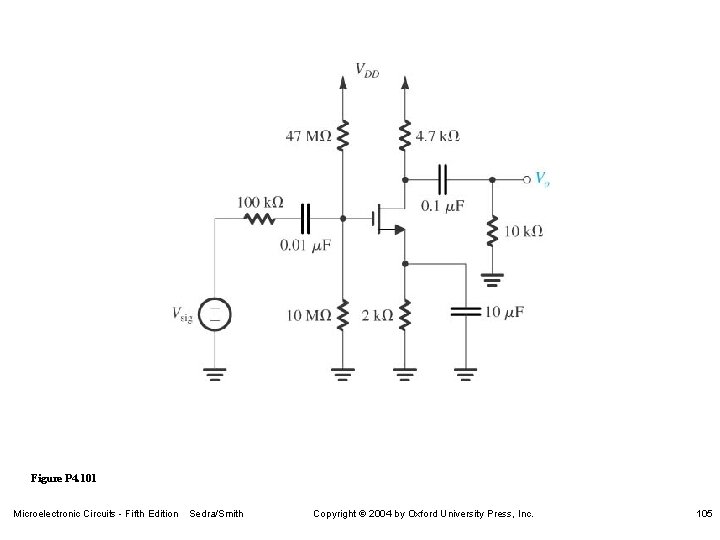

Figure P 4. 101 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 105

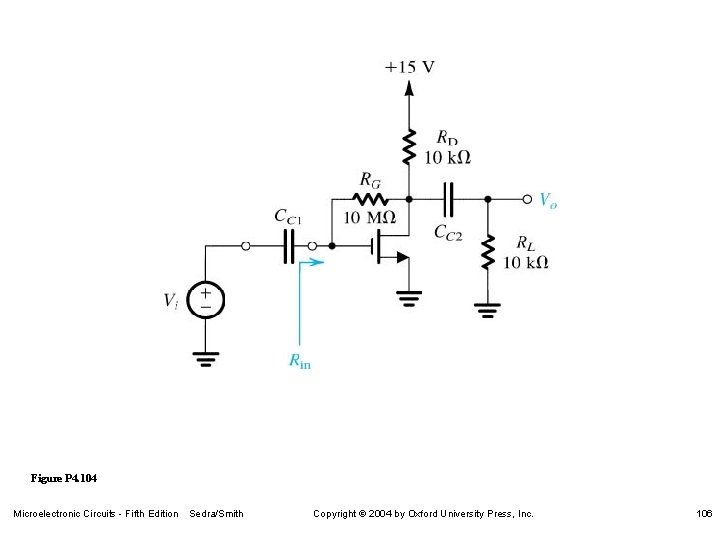

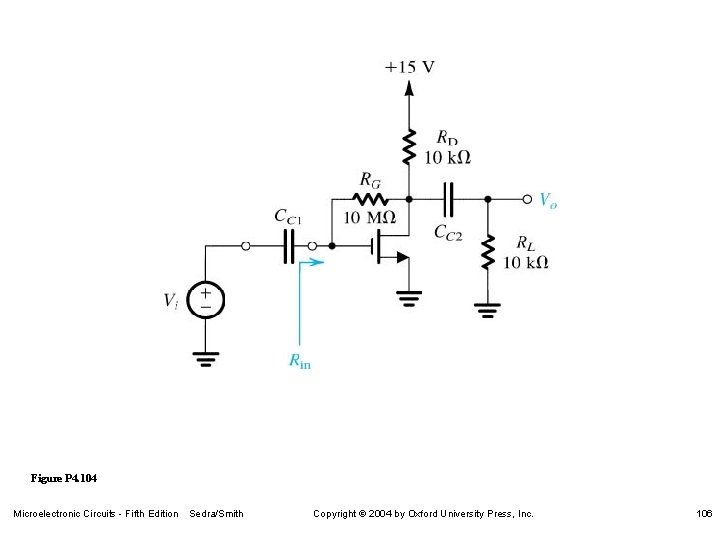

Figure P 4. 104 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 106

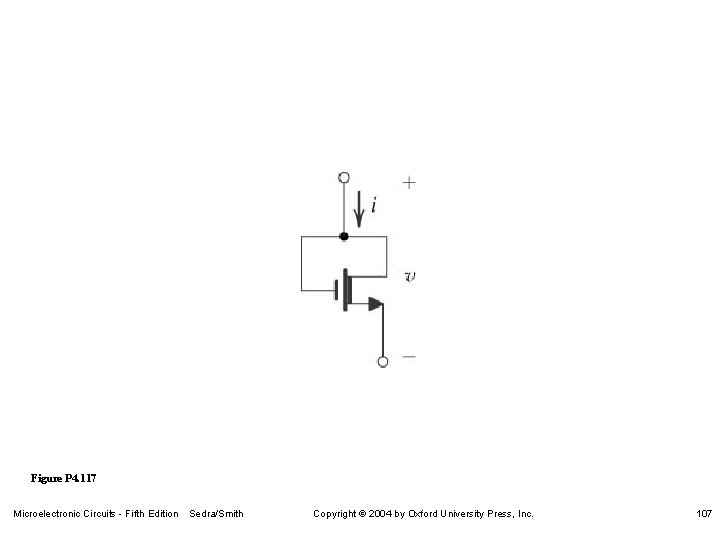

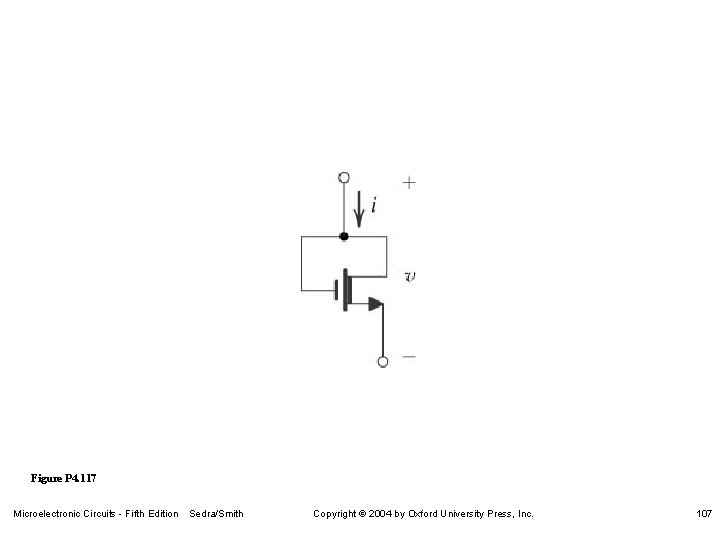

Figure P 4. 117 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 107

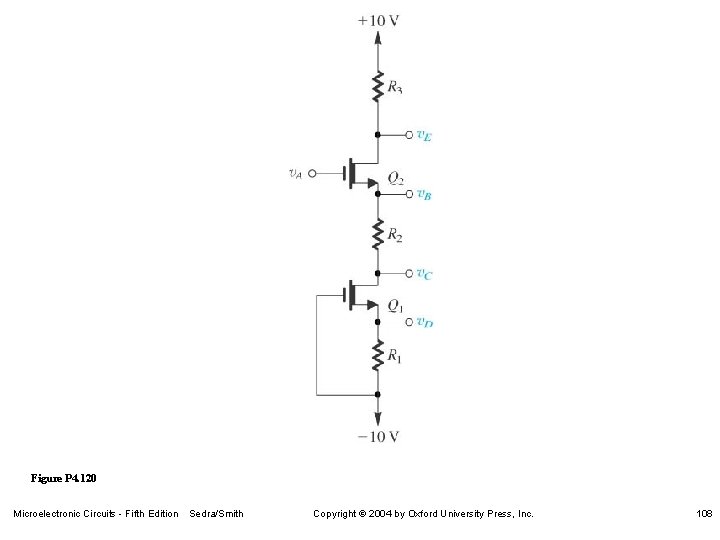

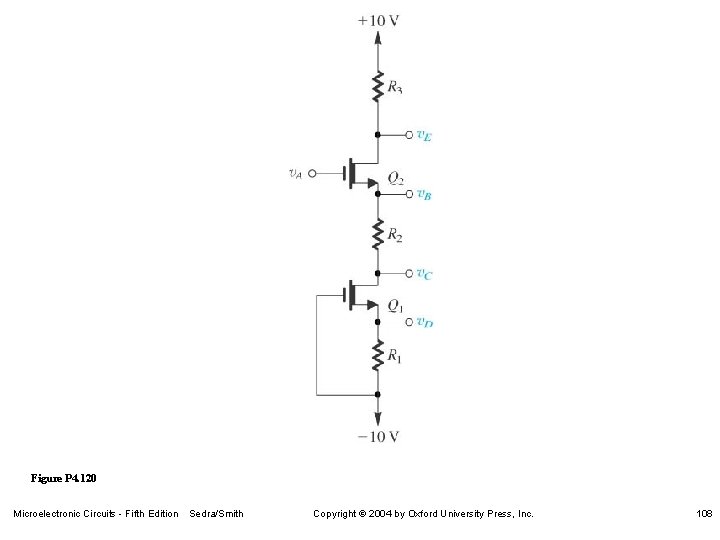

Figure P 4. 120 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 108

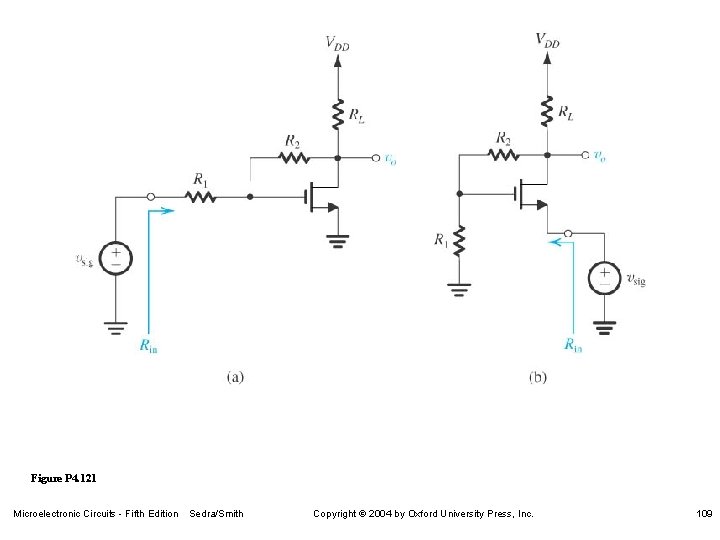

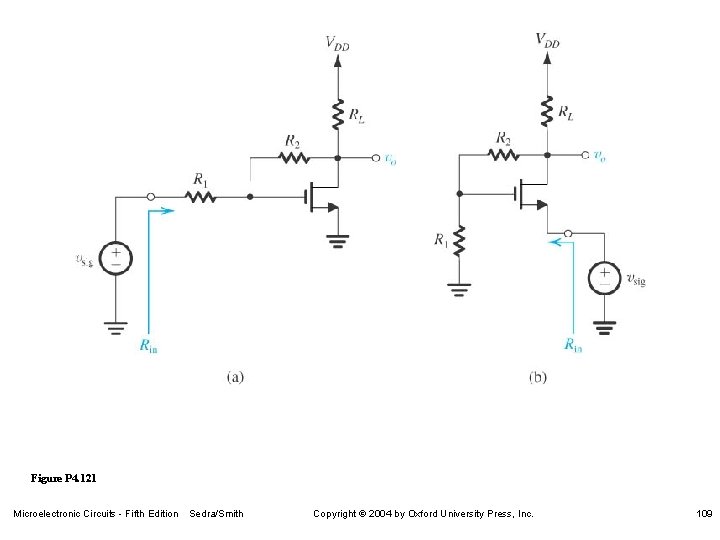

Figure P 4. 121 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 109

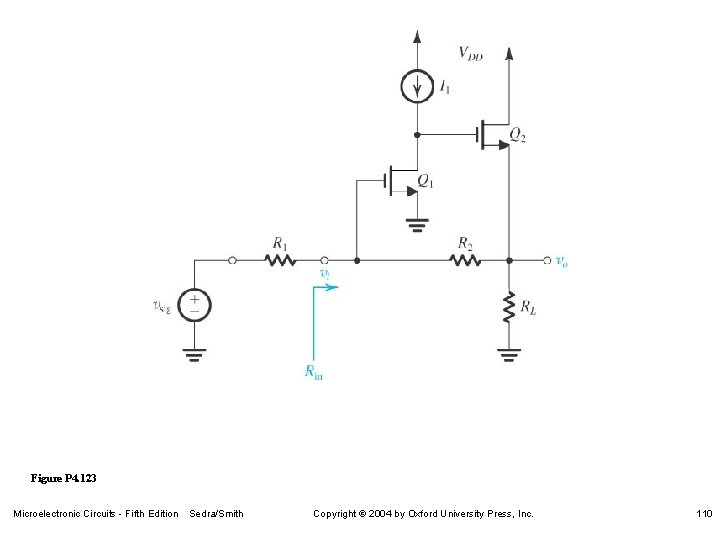

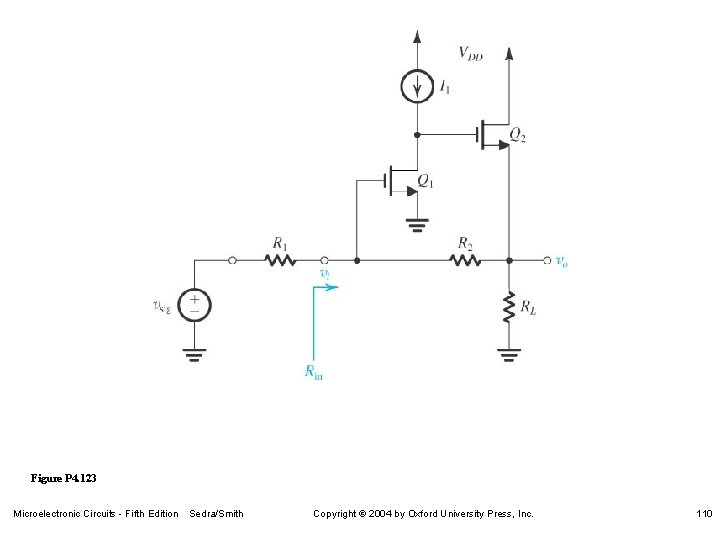

Figure P 4. 123 Microelectronic Circuits - Fifth Edition Sedra/Smith Copyright 2004 by Oxford University Press, Inc. 110