ECE 340 Lecture 38 MOS capacitor Threshold Voltage

- Slides: 13

ECE 340 Lecture 38 MOS capacitor Threshold Voltage • Inversion: at V > VT (for NMOS), many electrons drawn to surface, which is now “inverted” vs. the p-doped substrate. Draw charge distribution: • Draw energy bands at inversion: © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 1

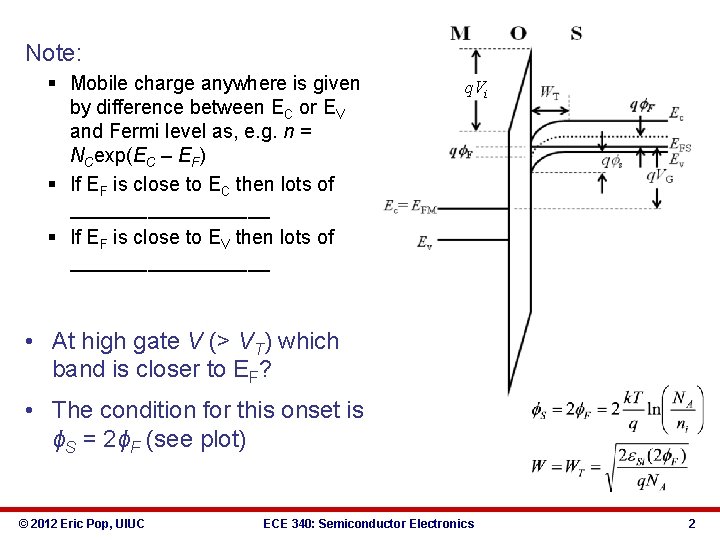

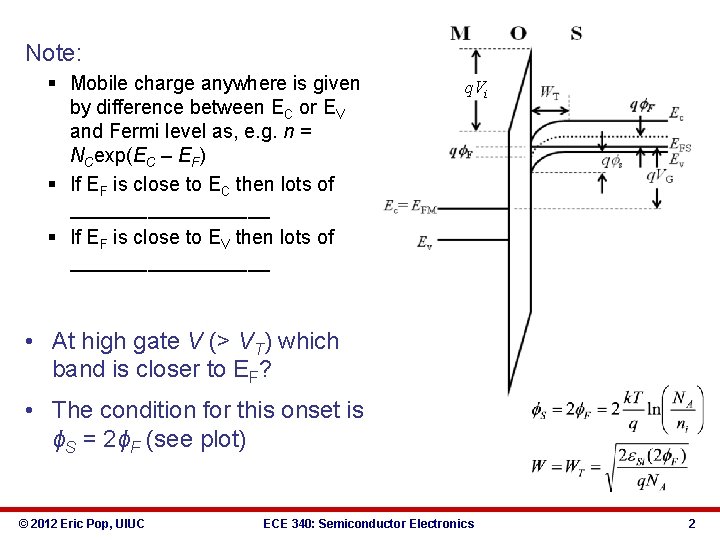

Note: § Mobile charge anywhere is given by difference between EC or EV and Fermi level as, e. g. n = NCexp(EC – EF) § If EF is close to EC then lots of _________ § If EF is close to EV then lots of _________ q. Vi • At high gate V (> VT) which band is closer to EF? • The condition for this onset is ϕS = 2ϕF (see plot) © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 2

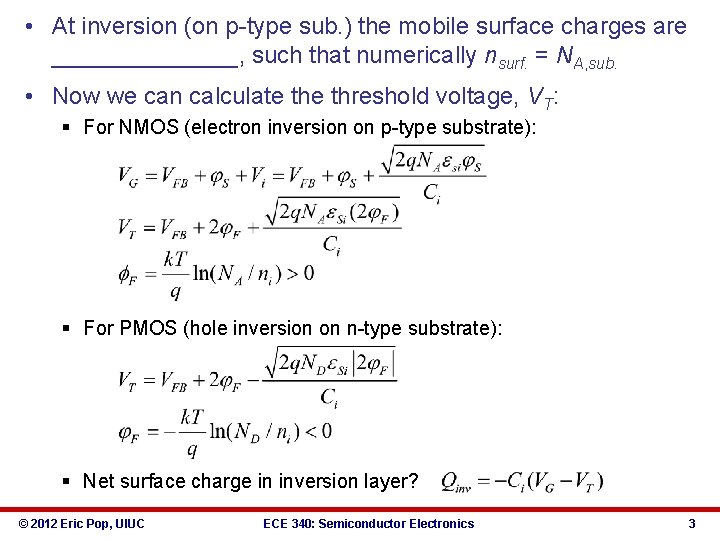

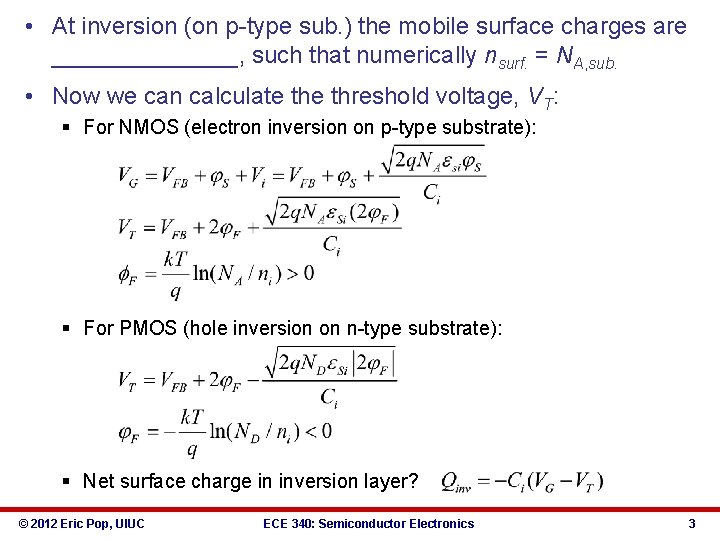

• At inversion (on p-type sub. ) the mobile surface charges are _______, such that numerically nsurf. = NA, sub. • Now we can calculate threshold voltage, VT: § For NMOS (electron inversion on p-type substrate): § For PMOS (hole inversion on n-type substrate): § Net surface charge in inversion layer? © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 3

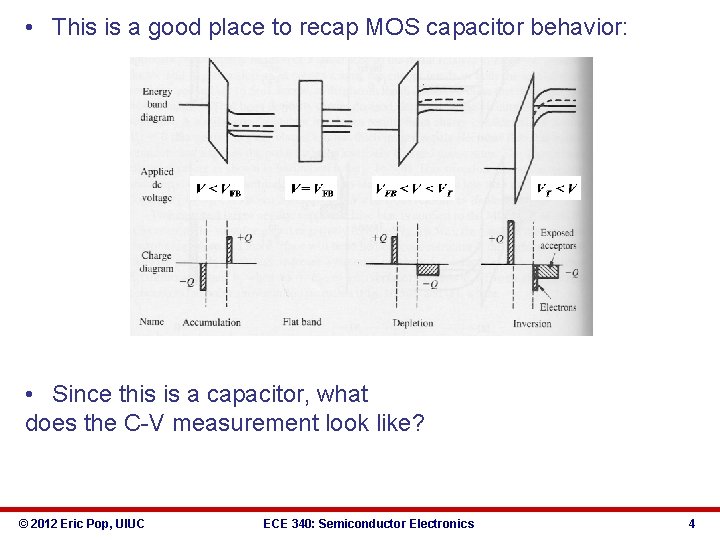

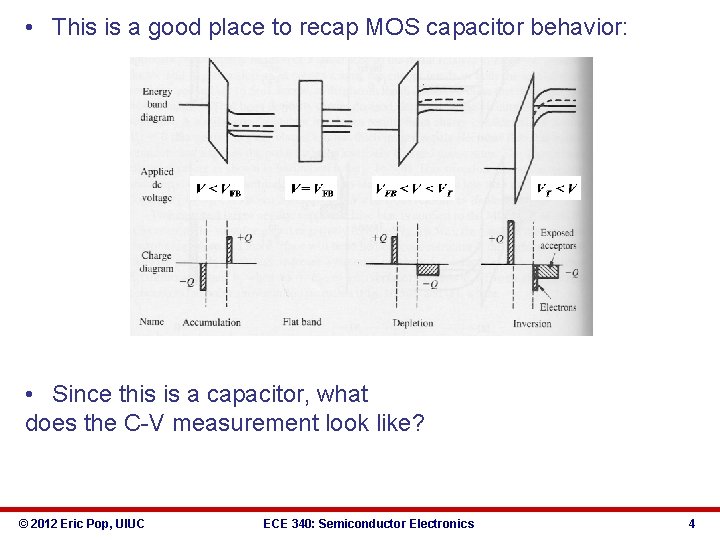

• This is a good place to recap MOS capacitor behavior: • Since this is a capacitor, what does the C-V measurement look like? © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 4

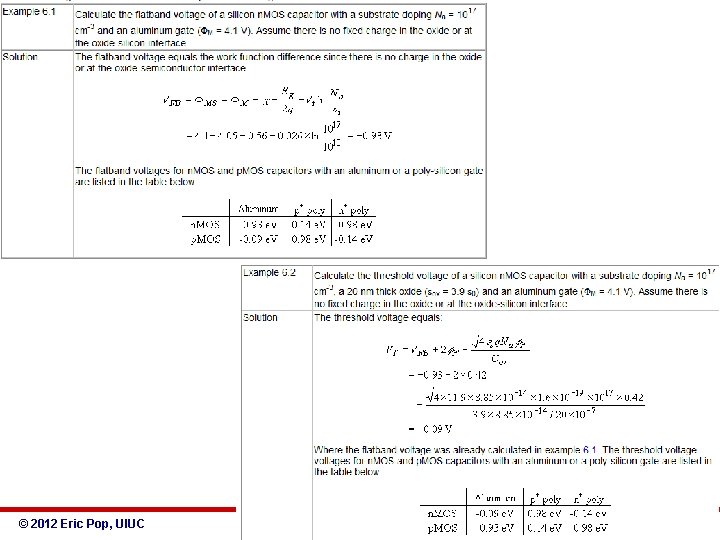

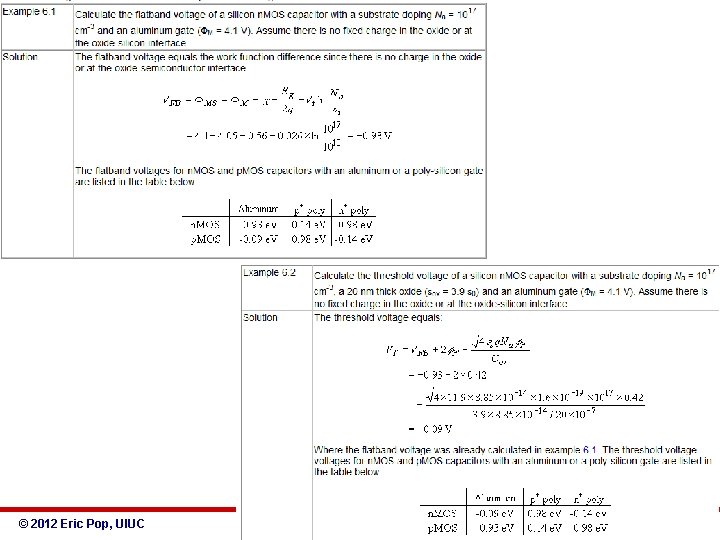

© 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 5

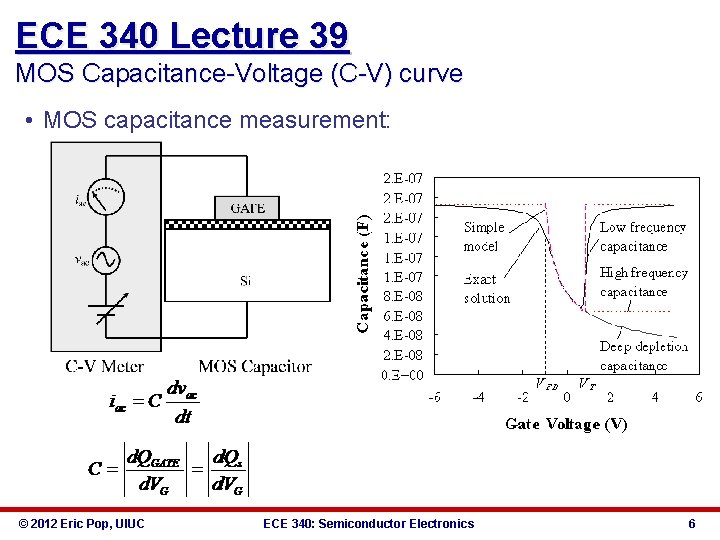

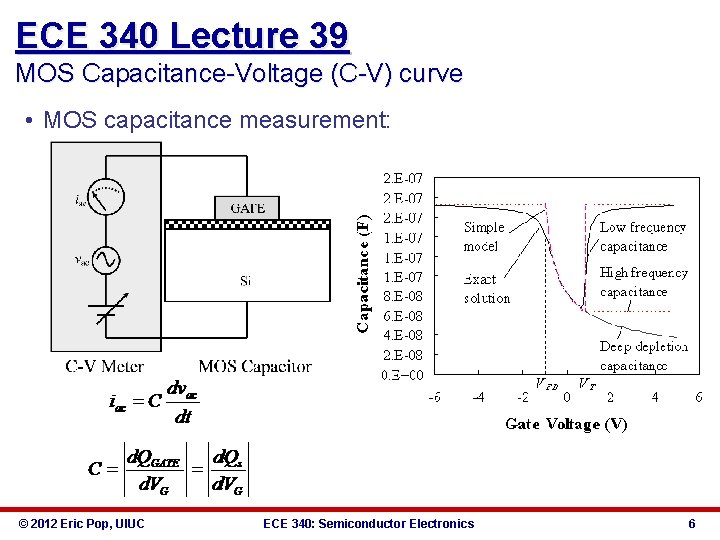

ECE 340 Lecture 39 MOS Capacitance-Voltage (C-V) curve • MOS capacitance measurement: © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 6

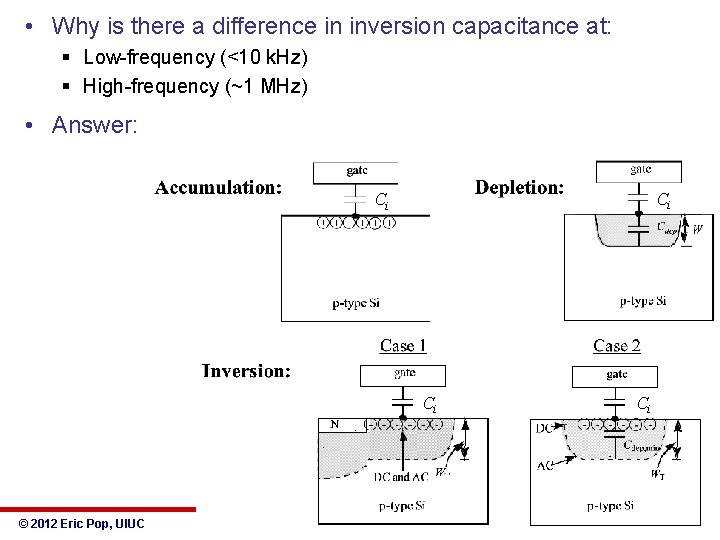

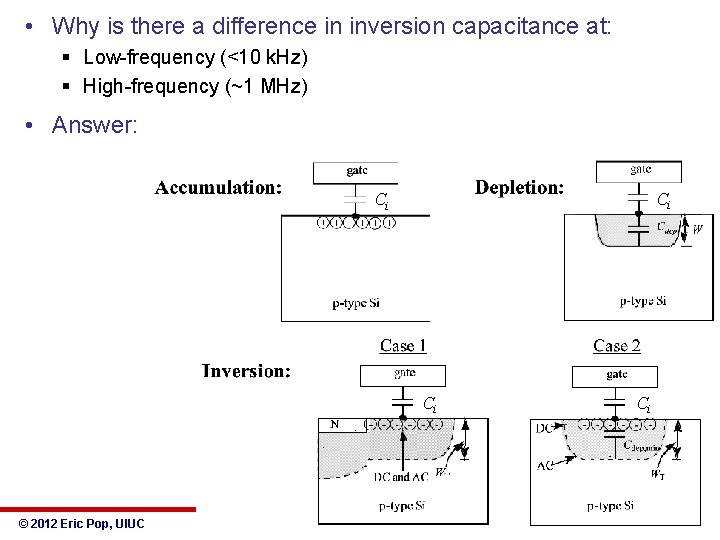

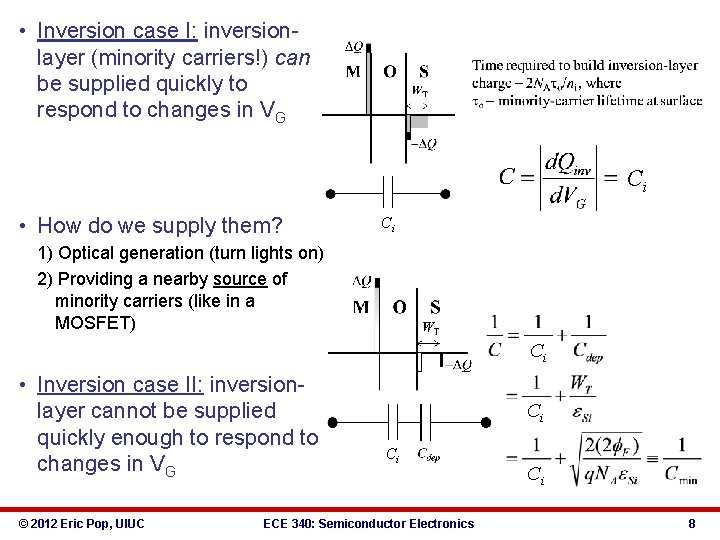

• Why is there a difference in inversion capacitance at: § Low-frequency (<10 k. Hz) § High-frequency (~1 MHz) • Answer: Ci Ci Ci © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics Ci 7

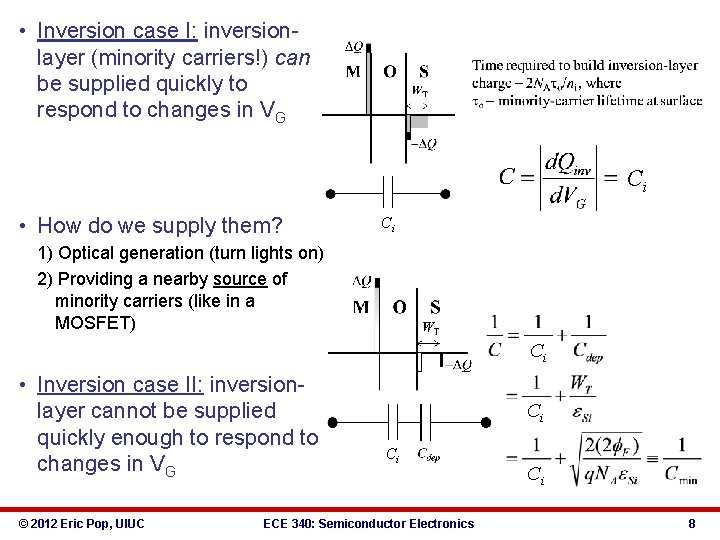

• Inversion case I: inversionlayer (minority carriers!) can be supplied quickly to respond to changes in VG Ci • How do we supply them? Ci 1) Optical generation (turn lights on) 2) Providing a nearby source of minority carriers (like in a MOSFET) Ci • Inversion case II: inversionlayer cannot be supplied quickly enough to respond to changes in VG © 2012 Eric Pop, UIUC Ci Ci ECE 340: Semiconductor Electronics Ci 8

• Ex: plot and label the C-V curve of a PMOS capacitor with P+ gate, substrate doping ND=5 x 1017 cm-3 and Si. O 2 d=2 nm © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 9

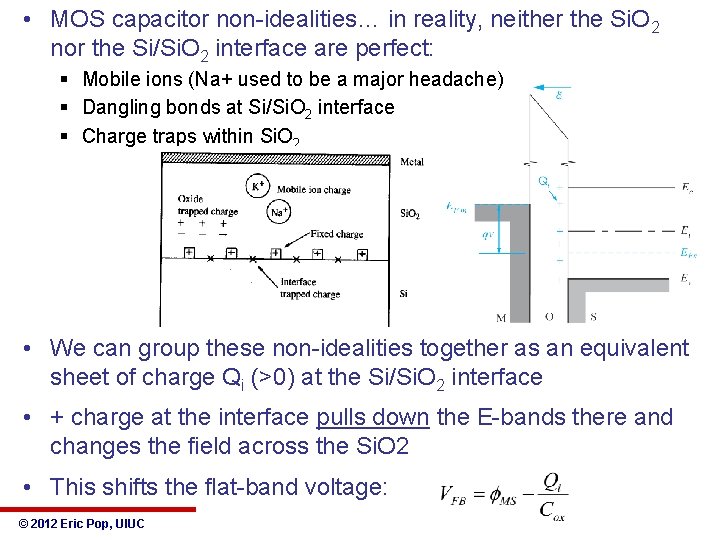

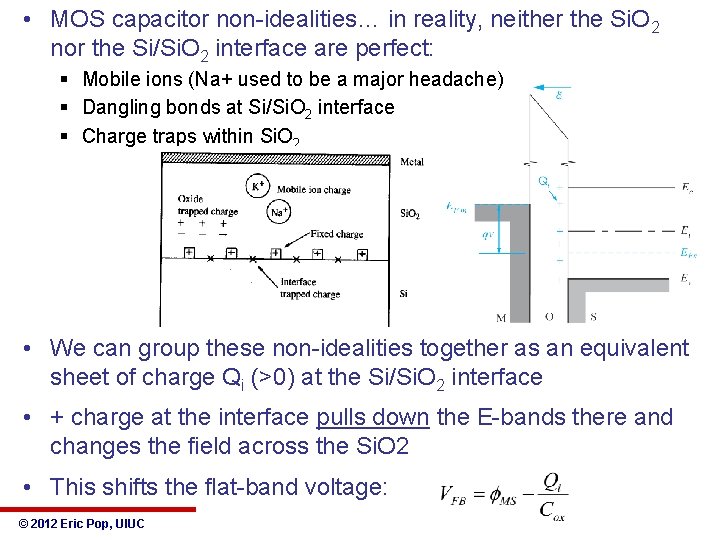

• MOS capacitor non-idealities… in reality, neither the Si. O 2 nor the Si/Si. O 2 interface are perfect: § Mobile ions (Na+ used to be a major headache) § Dangling bonds at Si/Si. O 2 interface § Charge traps within Si. O 2 • We can group these non-idealities together as an equivalent sheet of charge Qi (>0) at the Si/Si. O 2 interface • + charge at the interface pulls down the E-bands there and changes the field across the Si. O 2 • This shifts the flat-band voltage: © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 10

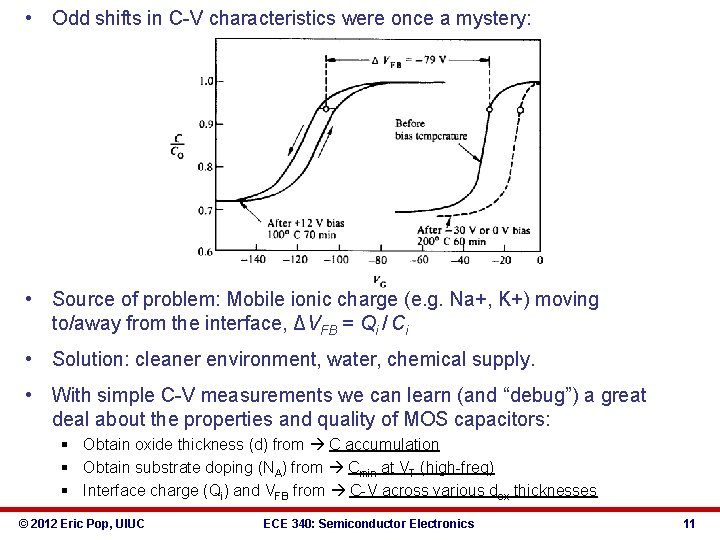

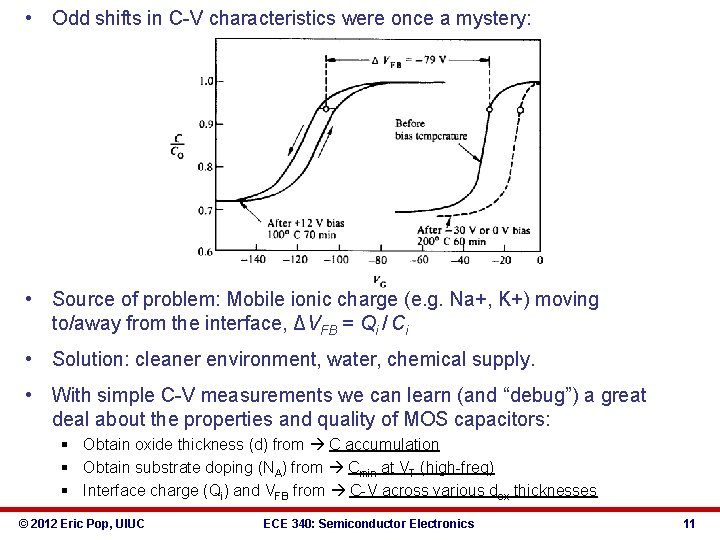

• Odd shifts in C-V characteristics were once a mystery: • Source of problem: Mobile ionic charge (e. g. Na+, K+) moving to/away from the interface, ΔVFB = Qi / Ci • Solution: cleaner environment, water, chemical supply. • With simple C-V measurements we can learn (and “debug”) a great deal about the properties and quality of MOS capacitors: § Obtain oxide thickness (d) from C accumulation § Obtain substrate doping (NA) from Cmin at VT (high-freq) § Interface charge (Qi) and VFB from C-V across various dox thicknesses © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 11

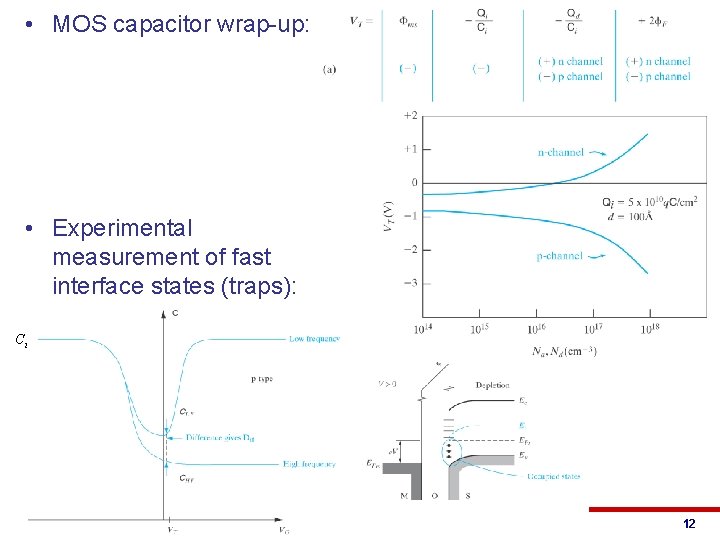

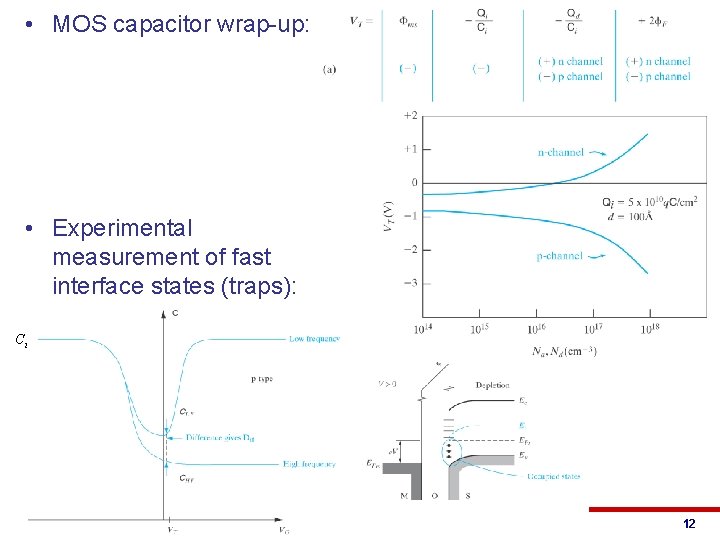

• MOS capacitor wrap-up: • Experimental measurement of fast interface states (traps): Ci © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 12

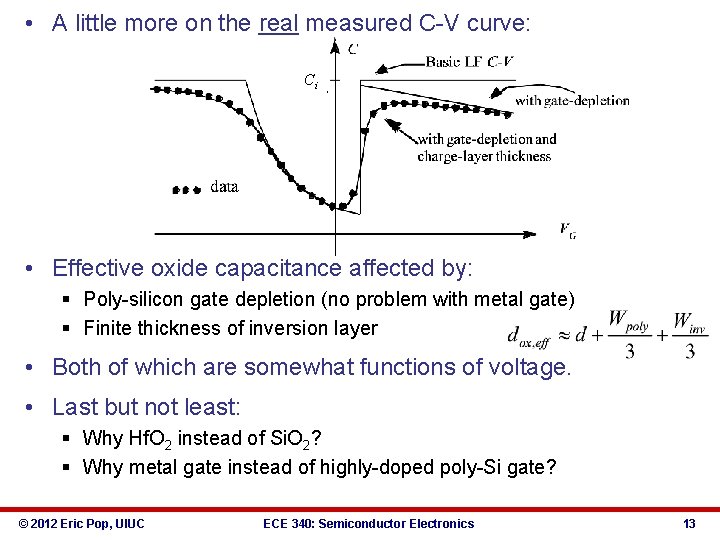

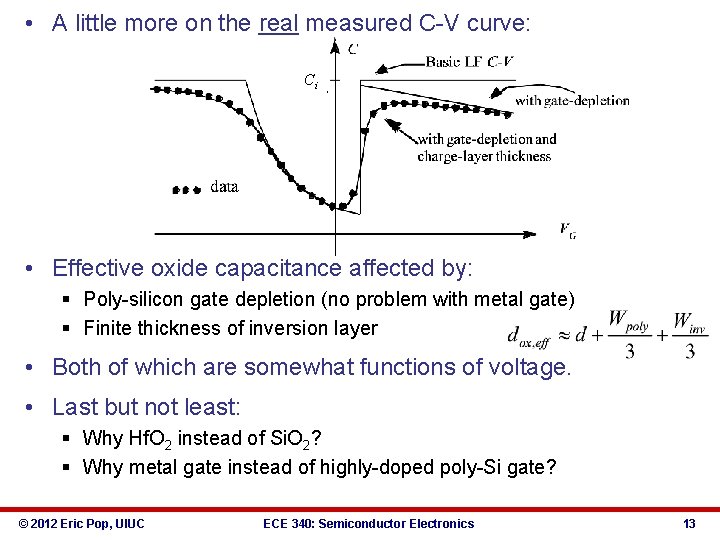

• A little more on the real measured C-V curve: Ci • Effective oxide capacitance affected by: § Poly-silicon gate depletion (no problem with metal gate) § Finite thickness of inversion layer • Both of which are somewhat functions of voltage. • Last but not least: § Why Hf. O 2 instead of Si. O 2? § Why metal gate instead of highly-doped poly-Si gate? © 2012 Eric Pop, UIUC ECE 340: Semiconductor Electronics 13