Differential Amplifiers Why differential Well suited for integrated

- Slides: 10

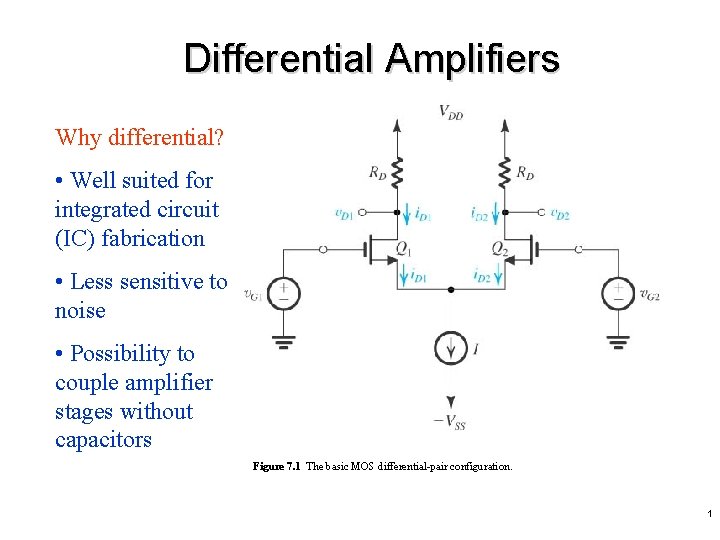

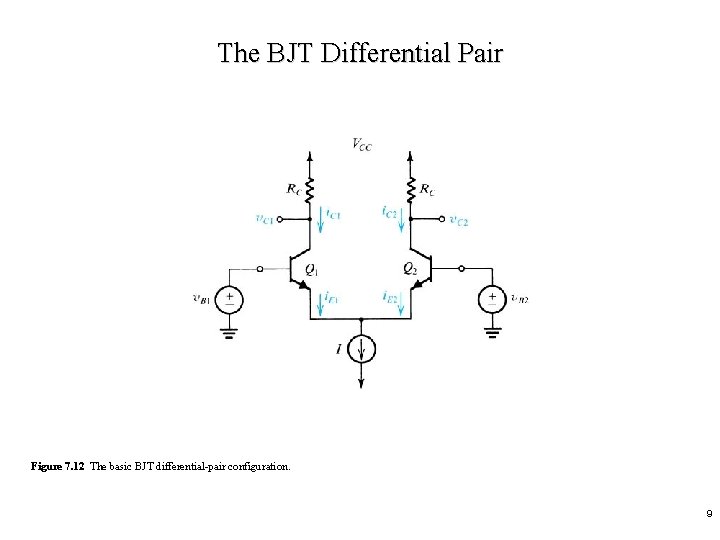

Differential Amplifiers Why differential? • Well suited for integrated circuit (IC) fabrication • Less sensitive to noise • Possibility to couple amplifier stages without capacitors Figure 7. 1 The basic MOS differential-pair configuration. 1

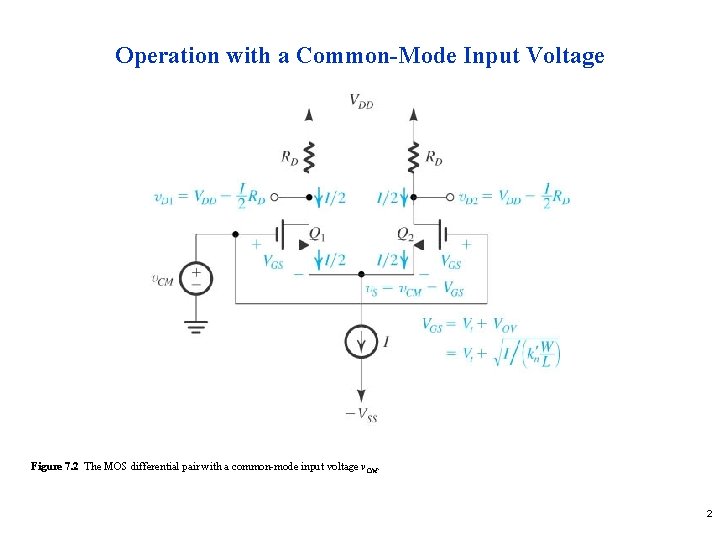

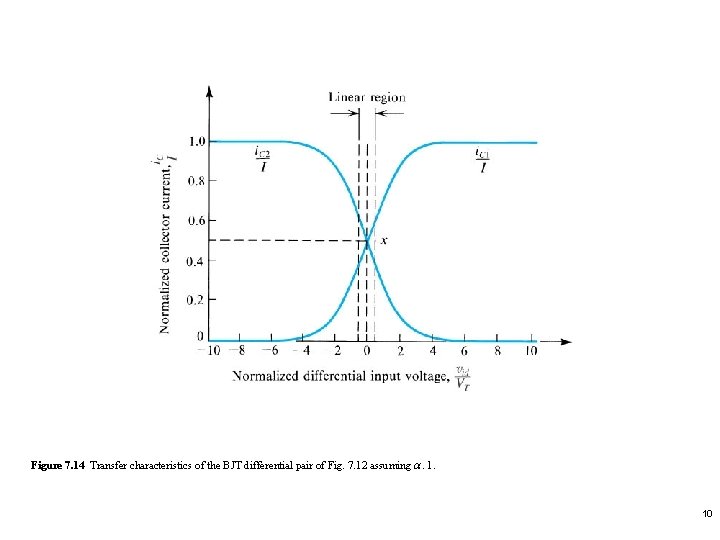

Operation with a Common-Mode Input Voltage Figure 7. 2 The MOS differential pair with a common-mode input voltage v. CM. 2

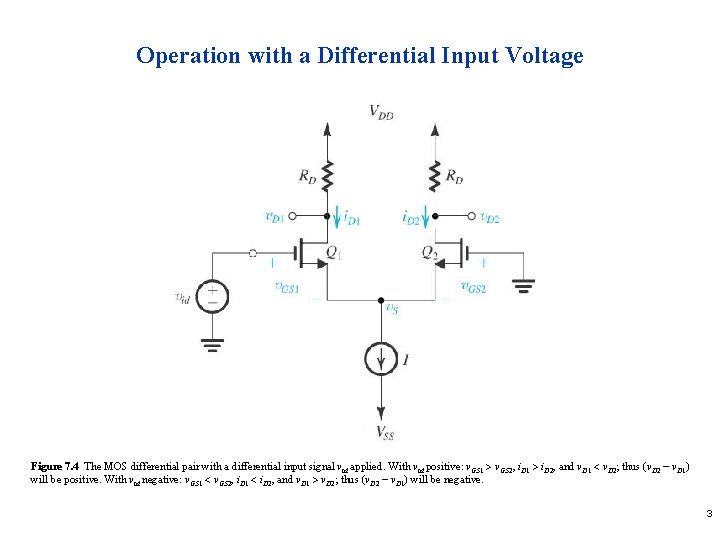

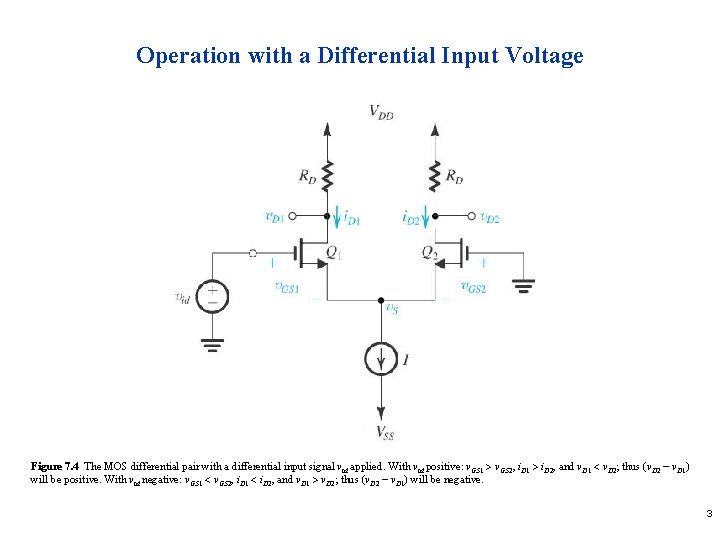

Operation with a Differential Input Voltage Figure 7. 4 The MOS differential pair with a differential input signal vid applied. With vid positive: v. GS 1 > v. GS 2, i. D 1 > i. D 2, and v. D 1 < v. D 2; thus (v. D 2 - v. D 1) will be positive. With vid negative: v. GS 1 < v. GS 2, i. D 1 < i. D 2, and v. D 1 > v. D 2; thus (v. D 2 - v. D 1) will be negative. 3

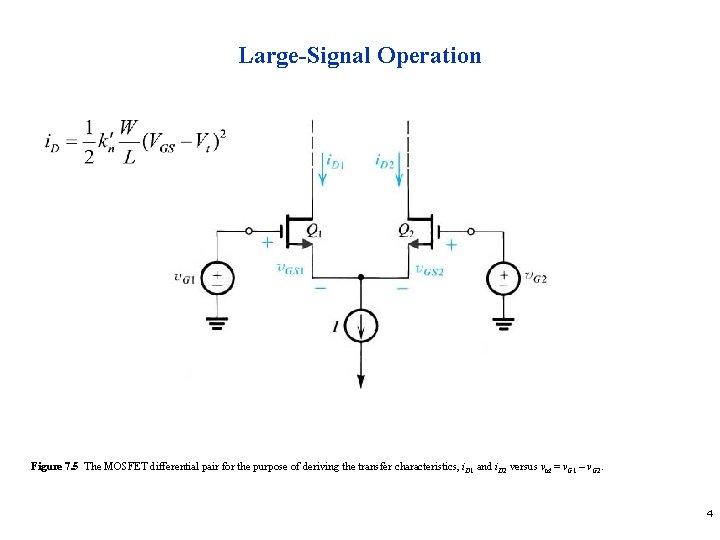

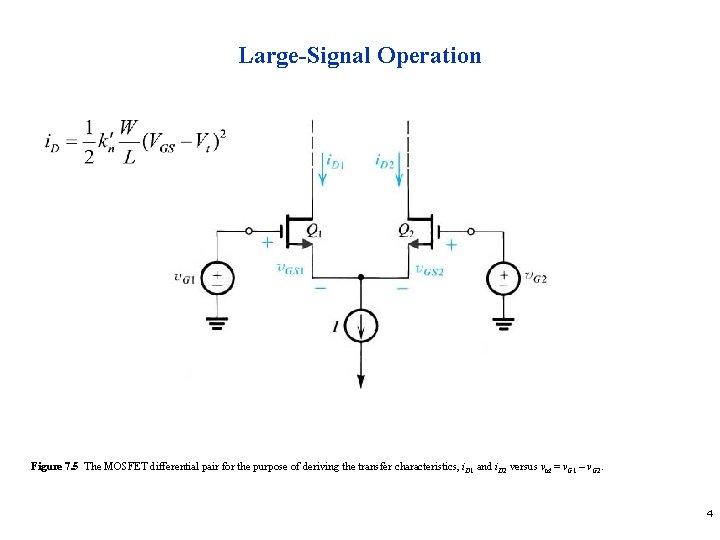

Large-Signal Operation Figure 7. 5 The MOSFET differential pair for the purpose of deriving the transfer characteristics, i. D 1 and i. D 2 versus vid = v. G 1 – v. G 2. 4

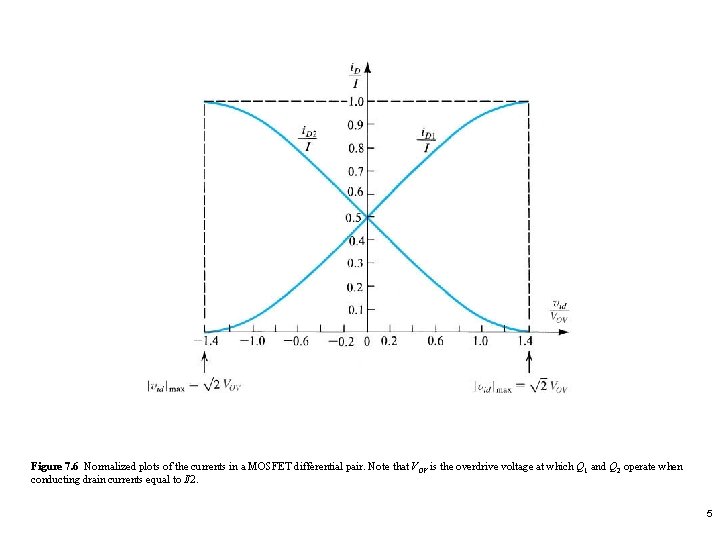

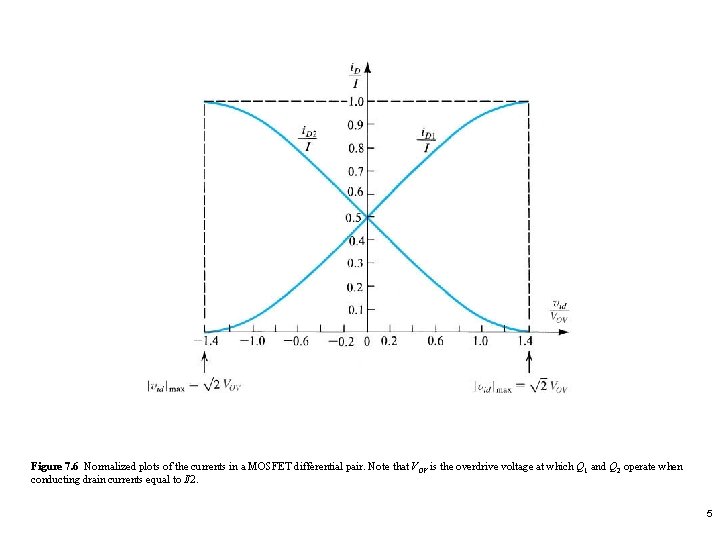

Figure 7. 6 Normalized plots of the currents in a MOSFET differential pair. Note that VOV is the overdrive voltage at which Q 1 and Q 2 operate when conducting drain currents equal to I/2. 5

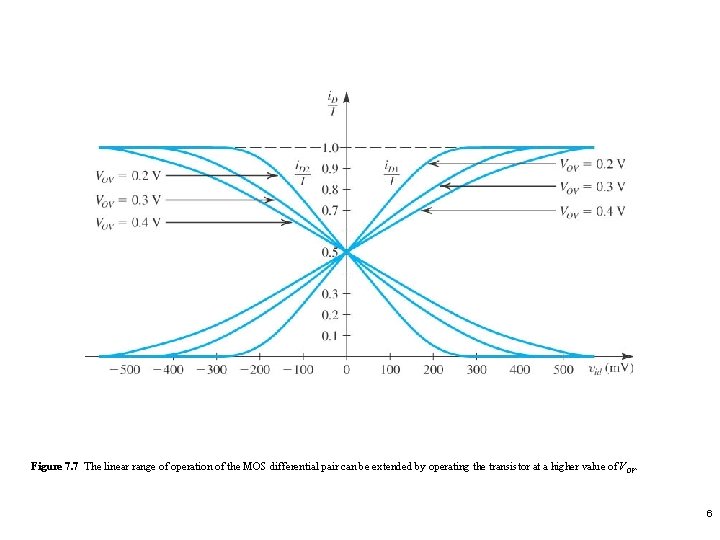

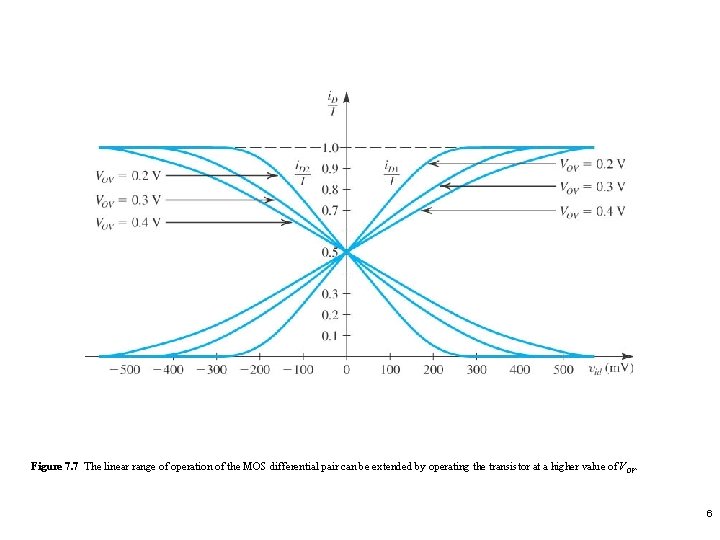

Figure 7. 7 The linear range of operation of the MOS differential pair can be extended by operating the transistor at a higher value of VOV. 6

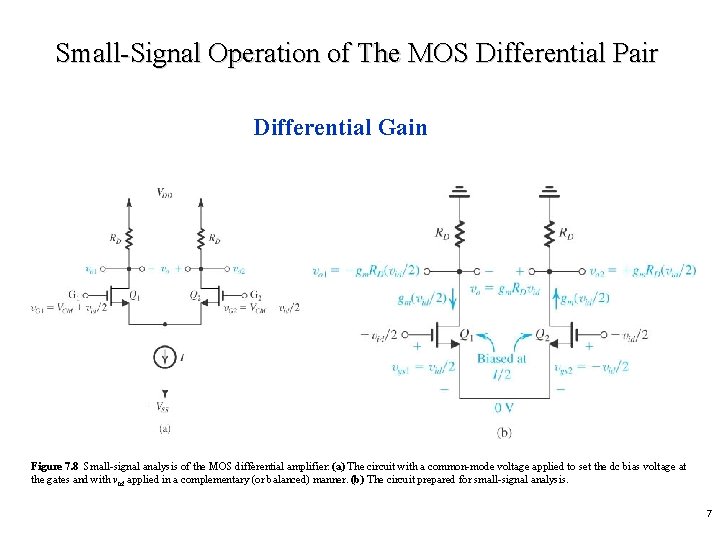

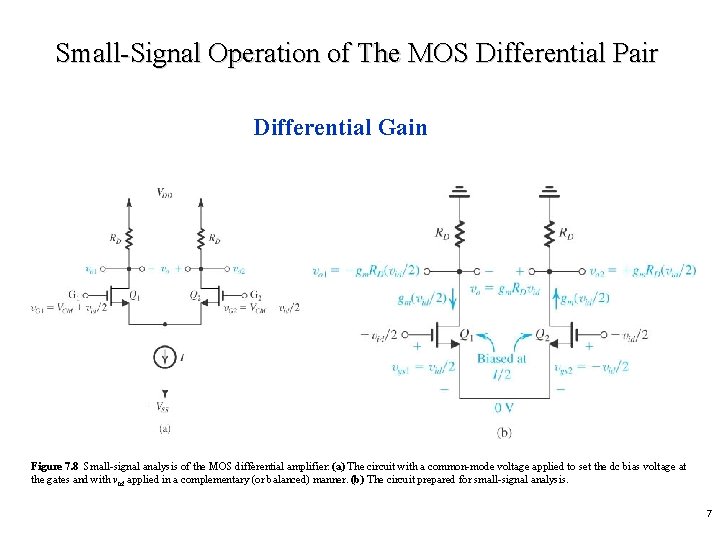

Small-Signal Operation of The MOS Differential Pair Differential Gain Figure 7. 8 Small-signal analysis of the MOS differential amplifier: (a) The circuit with a common-mode voltage applied to set the dc bias voltage at the gates and with vid applied in a complementary (or balanced) manner. (b) The circuit prepared for small-signal analysis. 7

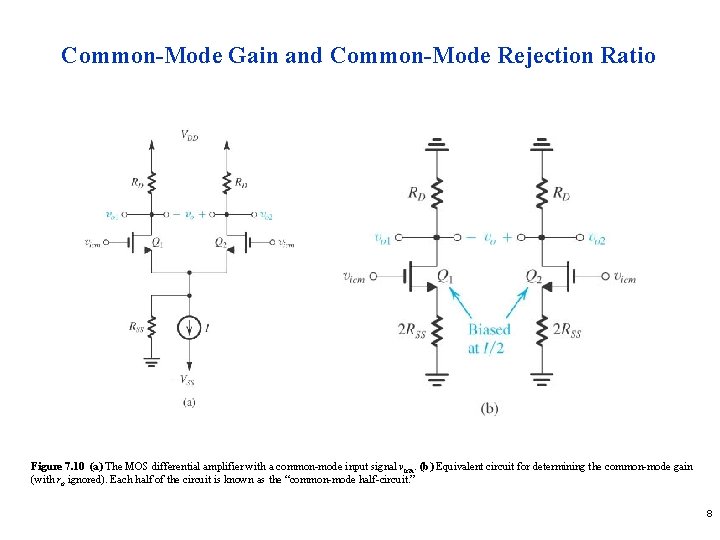

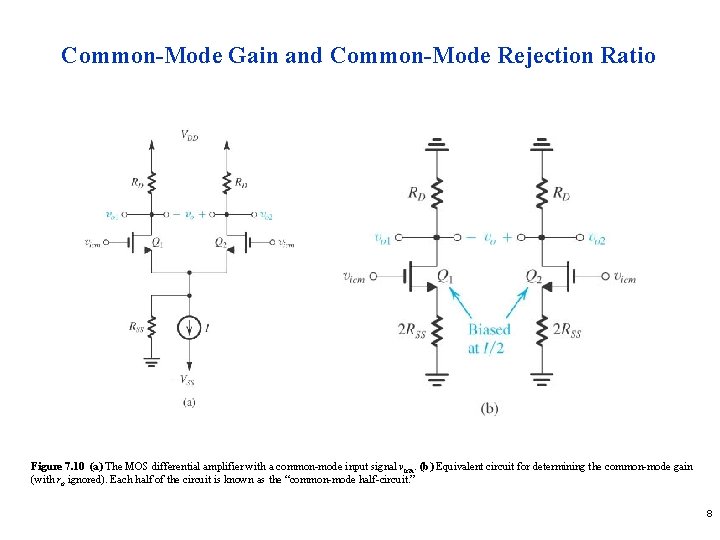

Common-Mode Gain and Common-Mode Rejection Ratio Figure 7. 10 (a) The MOS differential amplifier with a common-mode input signal vicm. (b) Equivalent circuit for determining the common-mode gain (with ro ignored). Each half of the circuit is known as the “common-mode half-circuit. ” 8

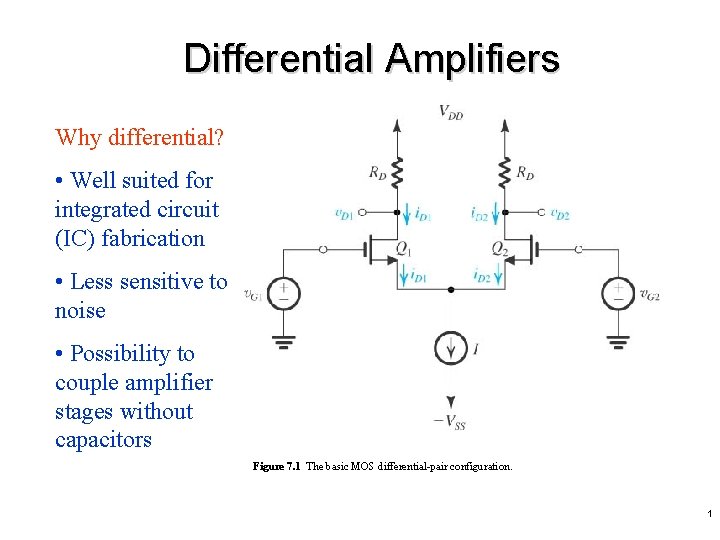

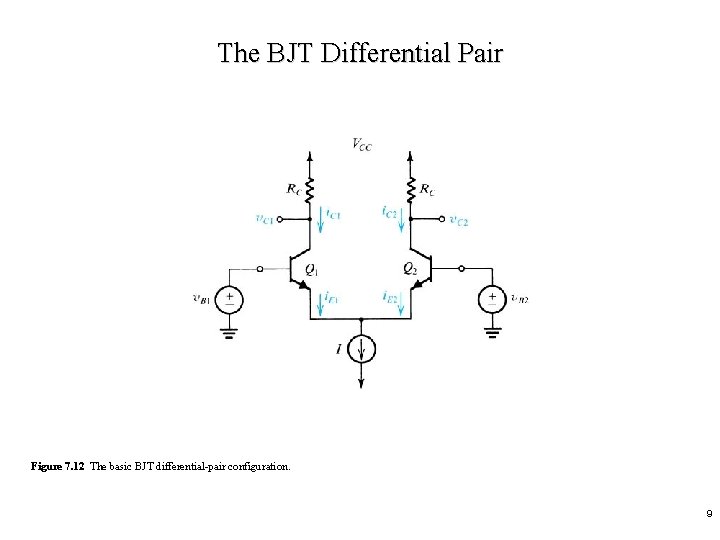

The BJT Differential Pair Figure 7. 12 The basic BJT differential-pair configuration. 9

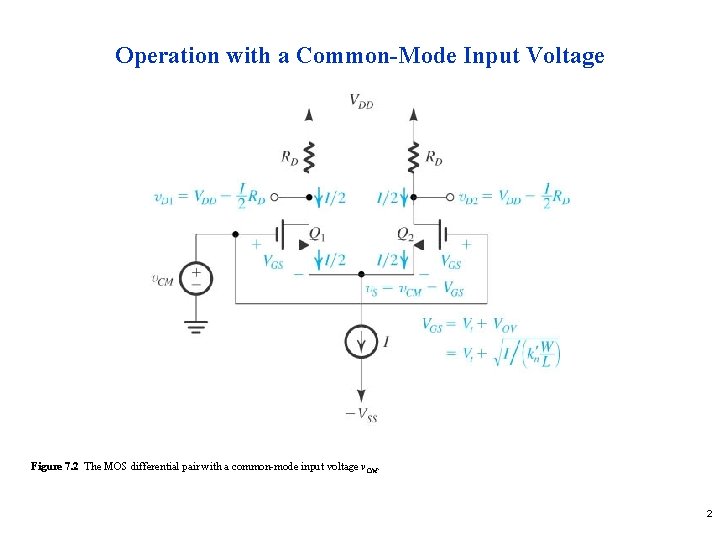

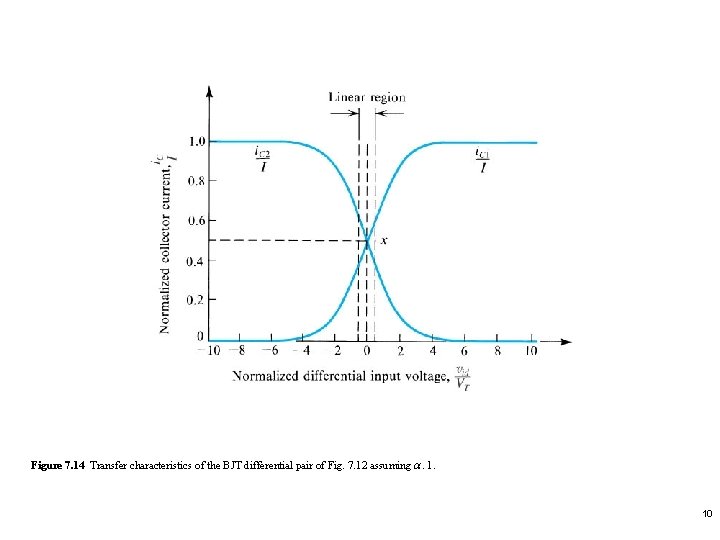

Figure 7. 14 Transfer characteristics of the BJT differential pair of Fig. 7. 12 assuming a. 1. 10