Design of Digital Circuits Lecture 20 SIMD Processors

![Scalar Code Example n For I = 0 to 49 q n C[i] = Scalar Code Example n For I = 0 to 49 q n C[i] =](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-24.jpg)

![Gather/Scatter Operations Want to vectorize loops with indirect accesses: for (i=0; i<N; i++) A[i] Gather/Scatter Operations Want to vectorize loops with indirect accesses: for (i=0; i<N; i++) A[i]](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-32.jpg)

![Another Example with Masking for (i = 0; i < 64; ++i) if (a[i] Another Example with Masking for (i = 0; i < 64; ++i) if (a[i]](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-35.jpg)

![Automatic Code Vectorization for (i=0; i < N; i++) C[i] = A[i] + B[i]; Automatic Code Vectorization for (i=0; i < N; i++) C[i] = A[i] + B[i];](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-47.jpg)

![How Can You Exploit Parallelism Here? for (i=0; i < N; i++) C[i] = How Can You Exploit Parallelism Here? for (i=0; i < N; i++) C[i] =](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-56.jpg)

![for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 1: for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 1:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-57.jpg)

![for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 2: for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 2:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-58.jpg)

![for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3: for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-59.jpg)

![for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3: for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-60.jpg)

![Multithreading of Warps n n n for (i=0; i < N; i++) C[i] = Multithreading of Warps n n n for (i=0; i < N; i++) C[i] =](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-65.jpg)

![Warp Execution (Recall the Slide) 32 -thread warp executing ADD A[tid], B[tid] C[tid] Execution Warp Execution (Recall the Slide) 32 -thread warp executing ADD A[tid], B[tid] C[tid] Execution](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-69.jpg)

- Slides: 89

Design of Digital Circuits Lecture 20: SIMD Processors Prof. Onur Mutlu ETH Zurich Spring 2017 11 May 2017

Agenda for Today & Next Few Lectures n Single-cycle Microarchitectures n Multi-cycle and Microprogrammed Microarchitectures n Pipelining n Issues in Pipelining: Control & Data Dependence Handling, State Maintenance and Recovery, … n Out-of-Order Execution n Other Execution Paradigms 2

Readings for Today n Lindholm et al. , "NVIDIA Tesla: A Unified Graphics and Computing Architecture, " IEEE Micro 2008. 3

Lecture Announcement n n n n May 15, 2017 17: 15 -18: 15 HG F 30, Audi Max Onur Mutlu Inaugural Lecture Future Computing Architectures https: //www. ethz. ch/en/news-andevents/details. html? event. Feed. Id=35821 4

Other Approaches to Concurrency (or Instruction Level Parallelism)

Approaches to (Instruction-Level) Concurrency n Pipelining n n n n Out-of-order execution Dataflow (at the ISA level) Superscalar Execution VLIW SIMD Processing (Vector and array processors, GPUs) Decoupled Access Execute Systolic Arrays 6

SIMD Processing: Exploiting Regular (Data) Parallelism

Review: SIMD Processing n Single instruction operates on multiple data elements q In time or in space n Multiple processing elements n Time-space duality q q Array processor: Instruction operates on multiple data elements at the same time using different spaces Vector processor: Instruction operates on multiple data elements in consecutive time steps using the same space 8

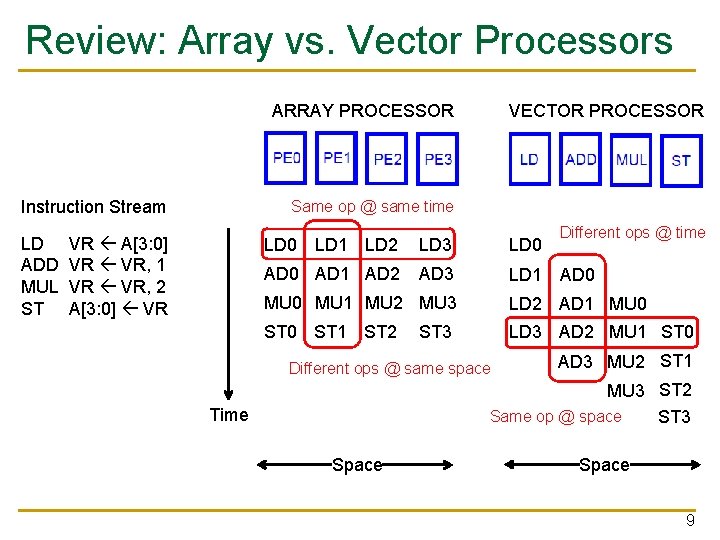

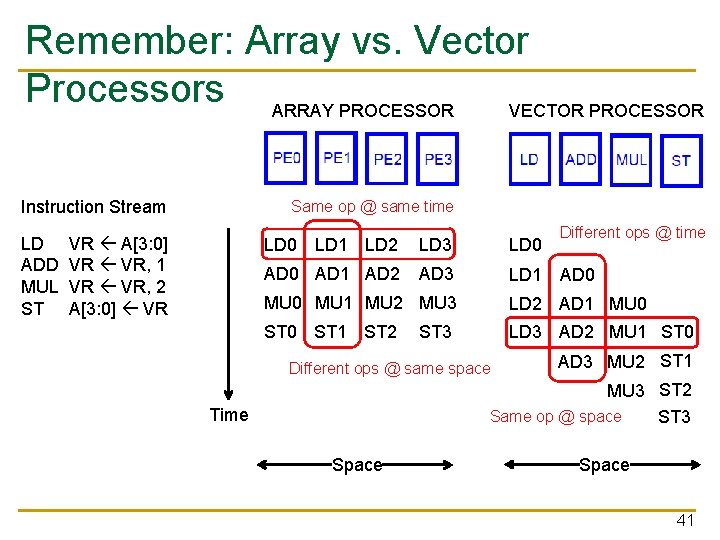

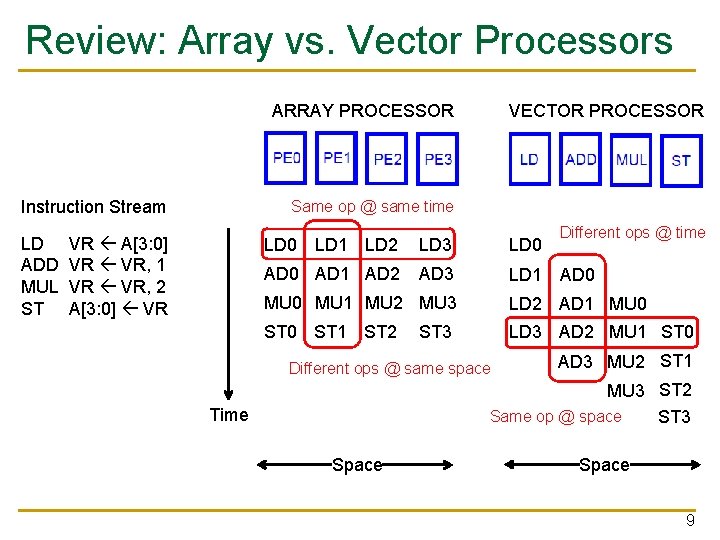

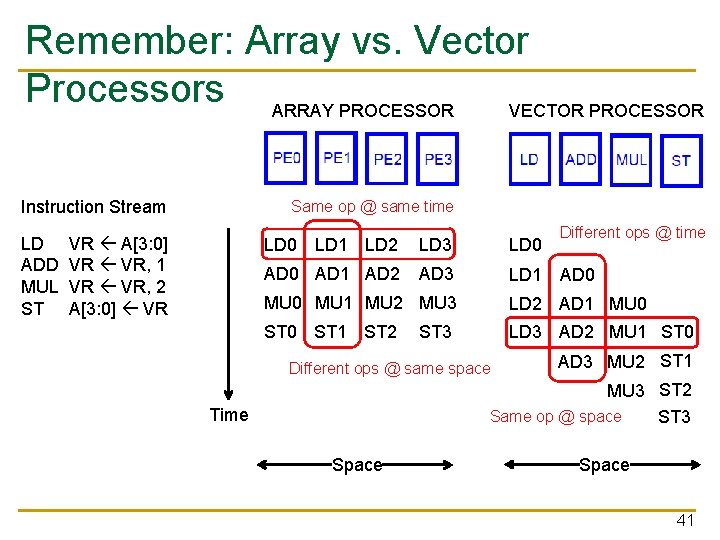

Review: Array vs. Vector Processors ARRAY PROCESSOR Instruction Stream LD ADD MUL ST VECTOR PROCESSOR Same op @ same time VR A[3: 0] VR VR, 1 VR VR, 2 A[3: 0] VR Different ops @ time LD 0 LD 1 LD 2 LD 3 LD 0 AD 1 AD 2 AD 3 LD 1 AD 0 MU 1 MU 2 MU 3 LD 2 AD 1 MU 0 ST 1 ST 2 LD 3 AD 2 MU 1 ST 0 ST 3 Different ops @ same space AD 3 MU 2 ST 1 MU 3 ST 2 Same op @ space ST 3 Time Space 9

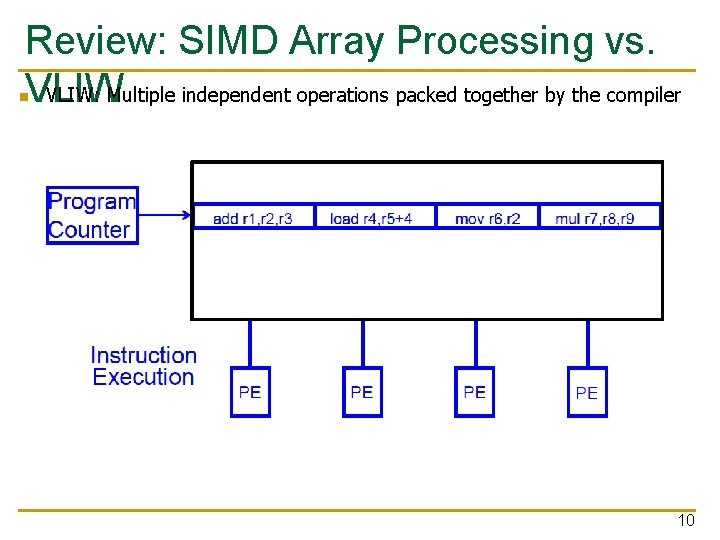

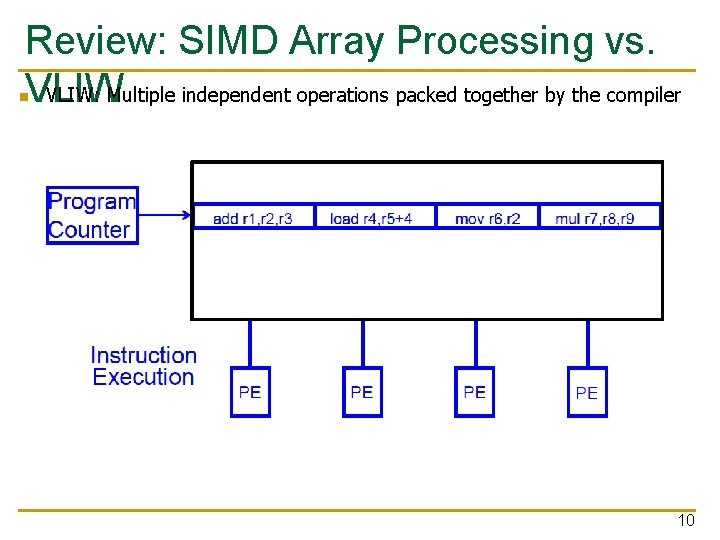

Review: SIMD Array Processing vs. VLIW: Multiple independent operations packed together by the compiler VLIW n 10

Review: SIMD Array Processing vs. Array processor: Single operation on multiple (different) data elements VLIW n 11

Review: Vector Processors n n A vector is a one-dimensional array of numbers Many scientific/commercial programs use vectors for (i = 0; i<=49; i++) C[i] = (A[i] + B[i]) / 2 n n A vector processor is one whose instructions operate on vectors rather than scalar (single data) values Basic requirements q q q Need to load/store vectors vector registers (contain vectors) Need to operate on vectors of different lengths vector length register (VLEN) Elements of a vector might be stored apart from each other in memory vector stride register (VSTR) n Stride: distance between two elements of a vector 12

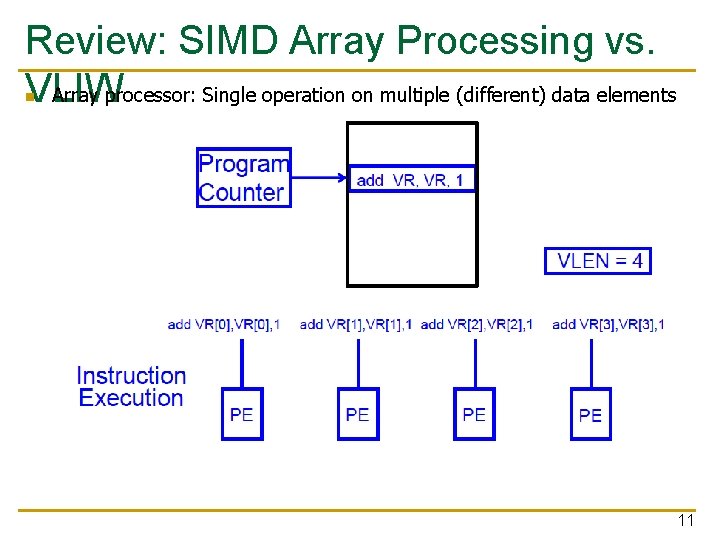

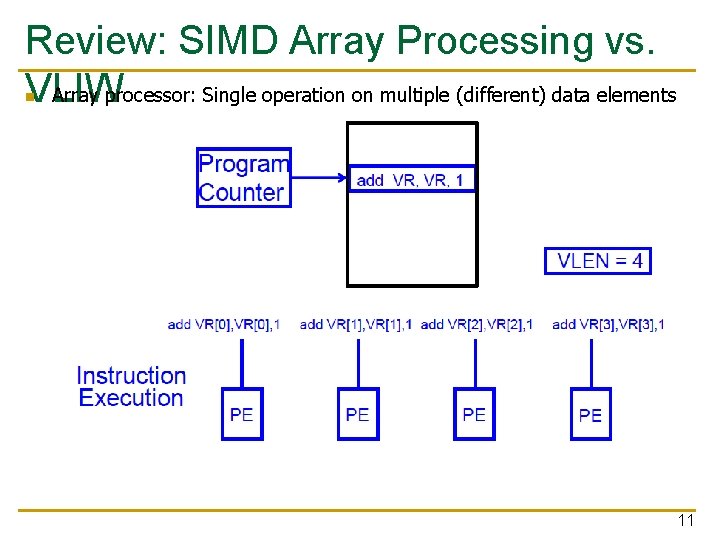

Review: Vector Processors (II) n A vector instruction performs an operation on each element in consecutive cycles q q n Vector functional units are pipelined Each pipeline stage operates on a different data element Vector instructions allow deeper pipelines q q q No intra-vector dependencies no hardware interlocking needed within a vector No control flow within a vector Known stride allows easy address calculation for all vector elements n Enables prefetching of vectors into registers/cache/memory 13

Vector Processor Advantages + No dependencies within a vector q q Pipelining. parallelization work really well Can have very deep pipelines, no dependencies! + Each instruction generates a lot of work q Reduces instruction fetch bandwidth requirements + Highly regular memory access pattern + No need to explicitly code loops q Fewer branches in the instruction sequence 14

Vector Processor Disadvantages -- Works (only) if parallelism is regular (data/SIMD parallelism) ++ Vector operations -- Very inefficient if parallelism is irregular -- How about searching for a key in a linked list? Fisher, “Very Long Instruction Word architectures and the ELI-512, ” ISCA 1983. 15

Vector Processor Limitations -- Memory (bandwidth) can easily become a bottleneck, especially if 1. compute/memory operation balance is not maintained 2. data is not mapped appropriately to memory banks 16

Vector Processing in More Depth

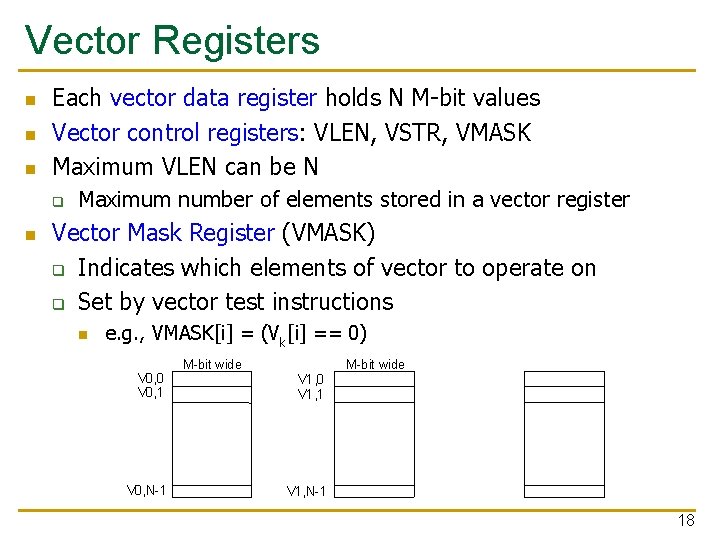

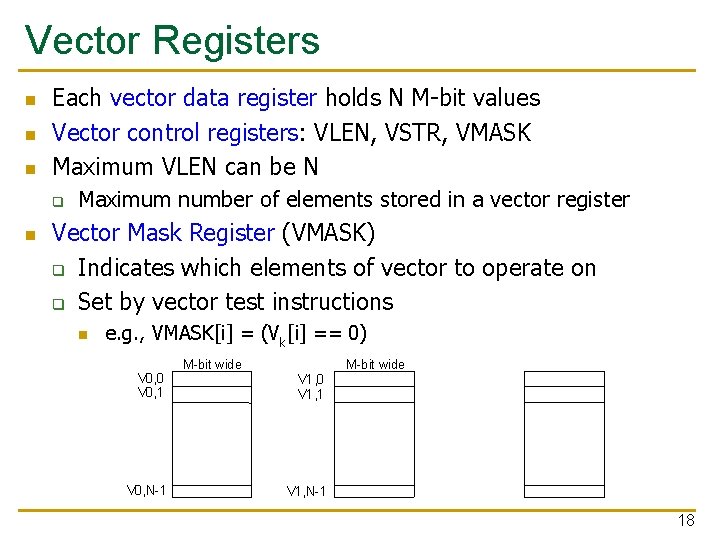

Vector Registers n n n Each vector data register holds N M-bit values Vector control registers: VLEN, VSTR, VMASK Maximum VLEN can be N q n Maximum number of elements stored in a vector register Vector Mask Register (VMASK) q Indicates which elements of vector to operate on q Set by vector test instructions n e. g. , VMASK[i] = (Vk[i] == 0) V 0, 0 V 0, 1 V 0, N-1 M-bit wide V 1, 0 V 1, 1 V 1, N-1 18

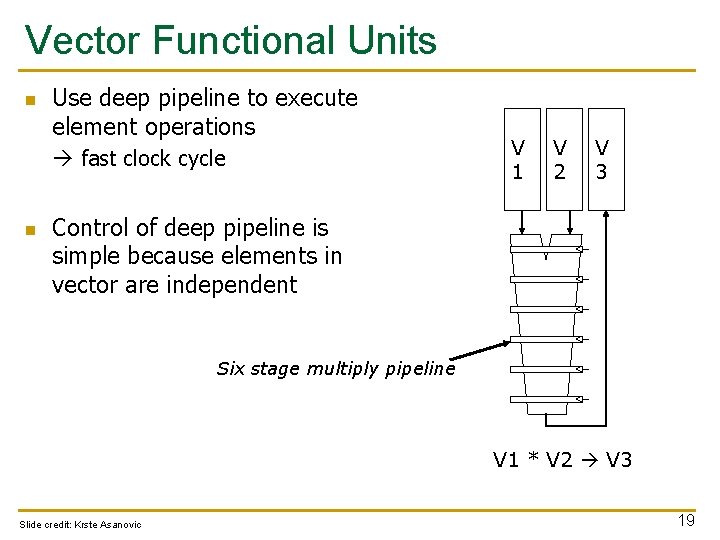

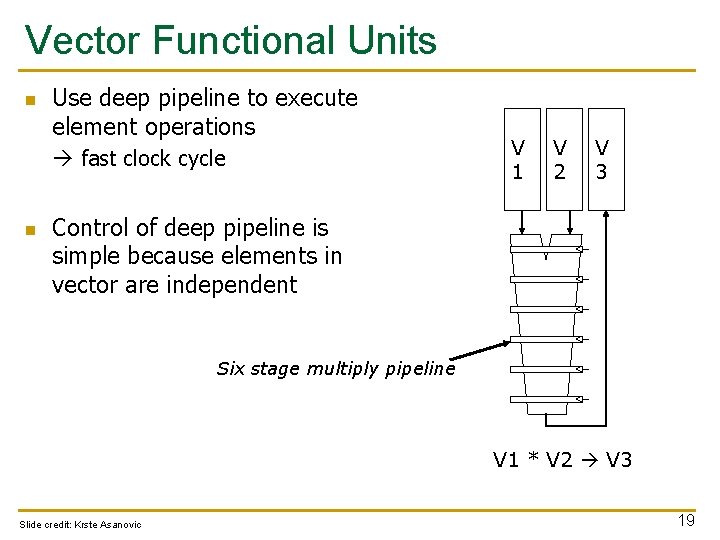

Vector Functional Units n Use deep pipeline to execute element operations fast clock cycle n V 1 V 2 V 3 Control of deep pipeline is simple because elements in vector are independent Six stage multiply pipeline V 1 * V 2 V 3 Slide credit: Krste Asanovic 19

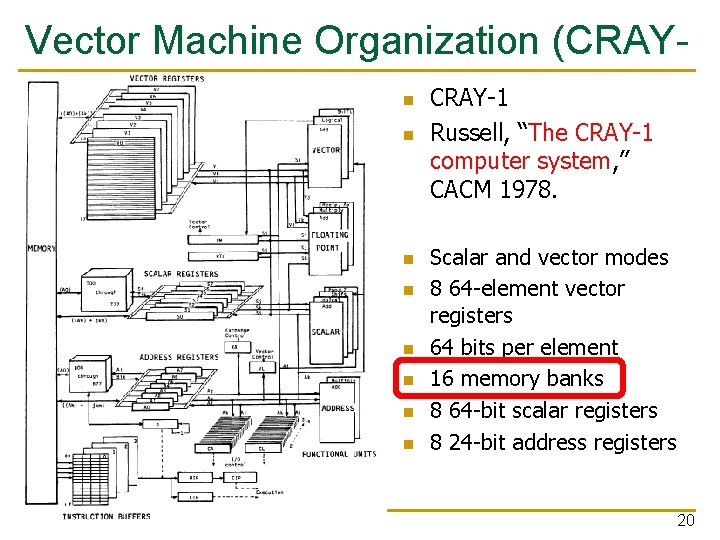

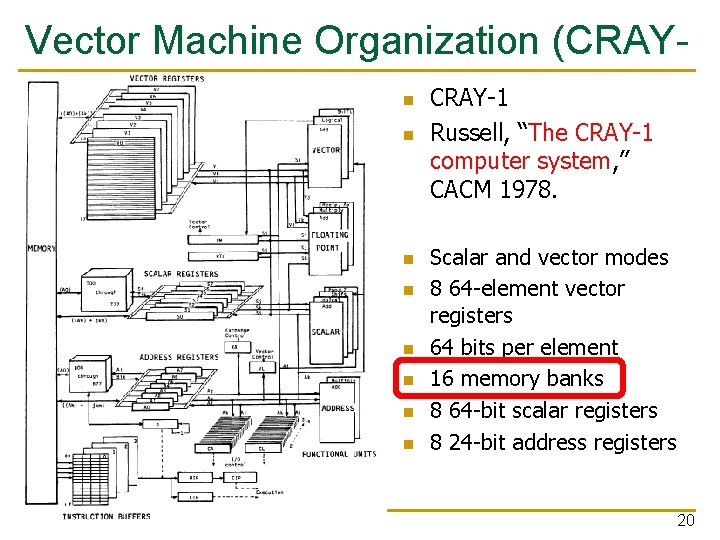

Vector Machine Organization (CRAY 1) n CRAY-1 n n n n Russell, “The CRAY-1 computer system, ” CACM 1978. Scalar and vector modes 8 64 -element vector registers 64 bits per element 16 memory banks 8 64 -bit scalar registers 8 24 -bit address registers 20

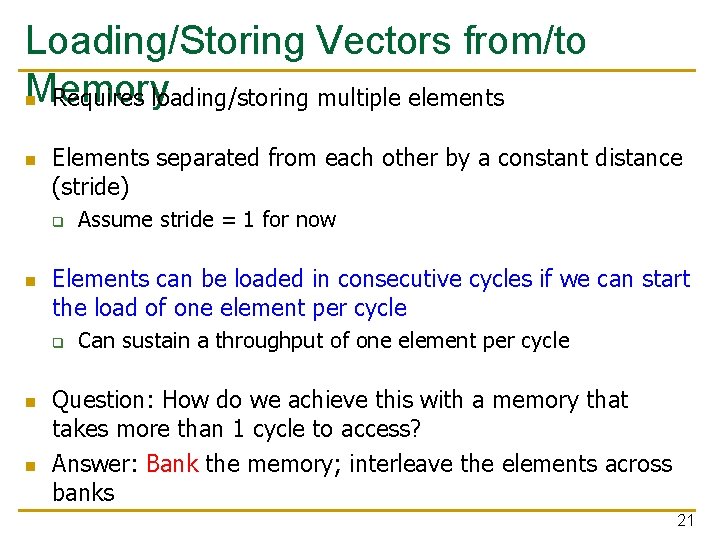

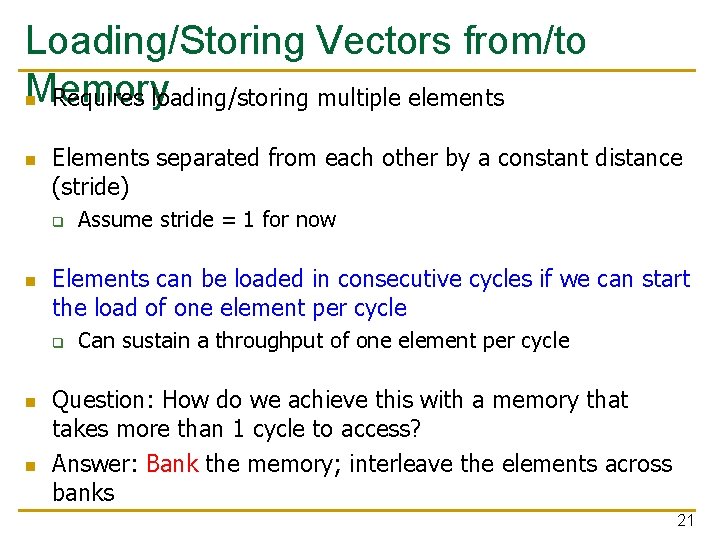

Loading/Storing Vectors from/to Memory n Requires loading/storing multiple elements n Elements separated from each other by a constant distance (stride) q n Elements can be loaded in consecutive cycles if we can start the load of one element per cycle q n n Assume stride = 1 for now Can sustain a throughput of one element per cycle Question: How do we achieve this with a memory that takes more than 1 cycle to access? Answer: Bank the memory; interleave the elements across banks 21

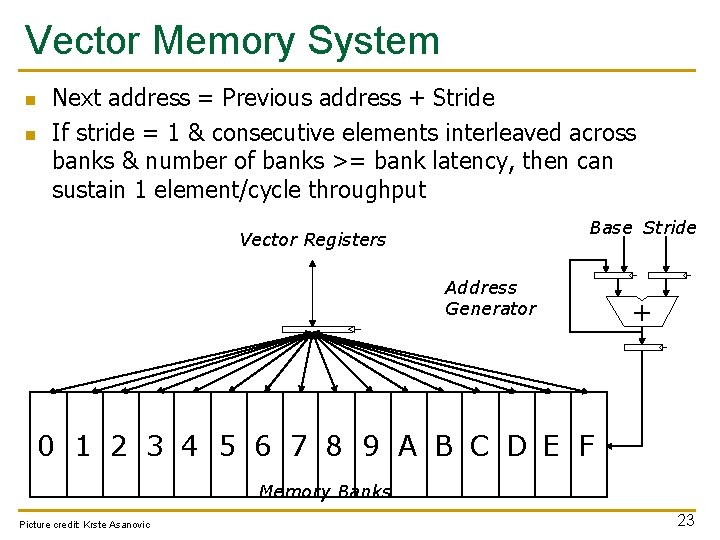

Memory Banking n n n Memory is divided into banks that can be accessed independently; banks share address and data buses (to minimize pin cost) Can start and complete one bank access per cycle Can sustain N parallel accesses if all N go to different banks Bank 0 MDR Bank 1 MAR MDR Bank 2 MAR MDR Bank 15 MAR MDR MAR Data bus Address bus CPU Picture credit: Derek Chiou 22

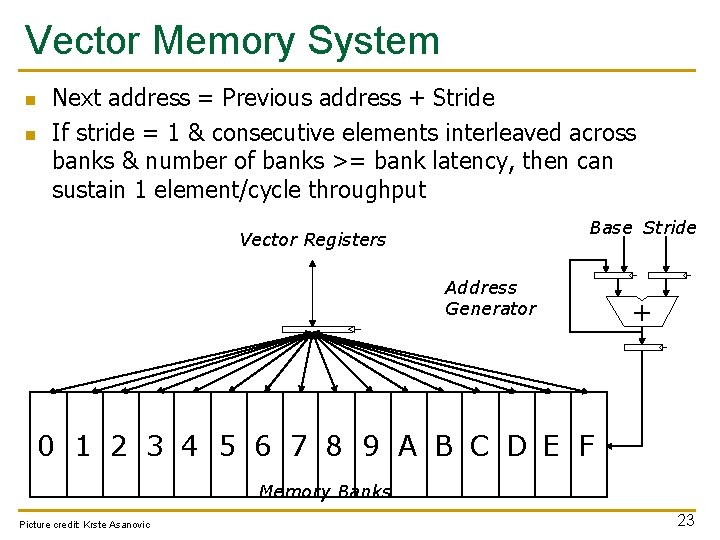

Vector Memory System n n Next address = Previous address + Stride If stride = 1 & consecutive elements interleaved across banks & number of banks >= bank latency, then can sustain 1 element/cycle throughput Base Stride Vector Registers Address Generator + 0 1 2 3 4 5 6 7 8 9 A B C D E F Memory Banks Picture credit: Krste Asanovic 23

![Scalar Code Example n For I 0 to 49 q n Ci Scalar Code Example n For I = 0 to 49 q n C[i] =](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-24.jpg)

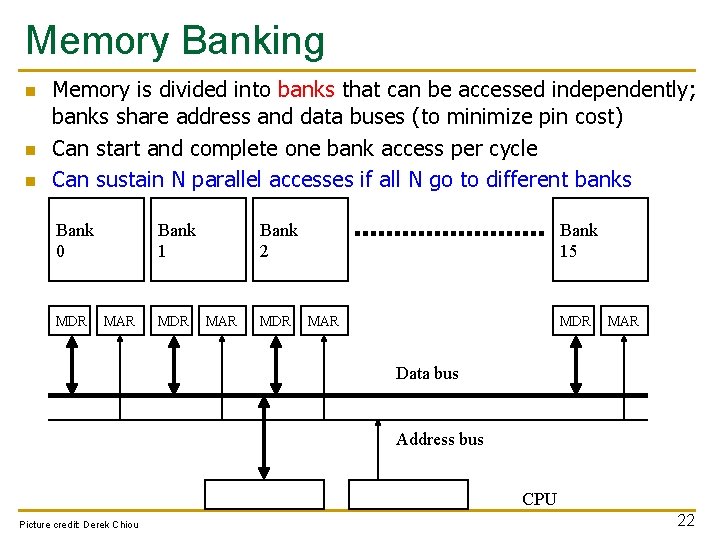

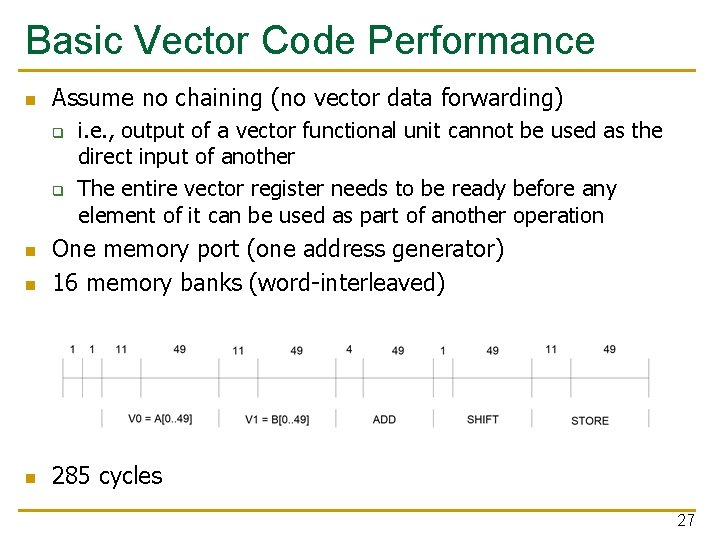

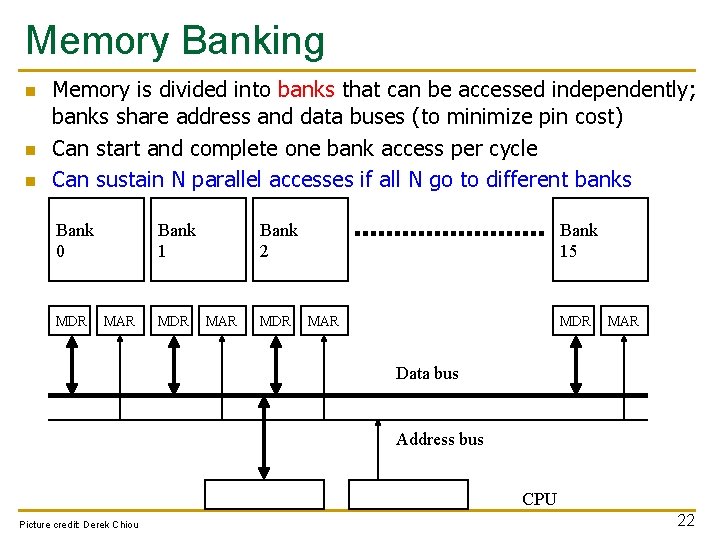

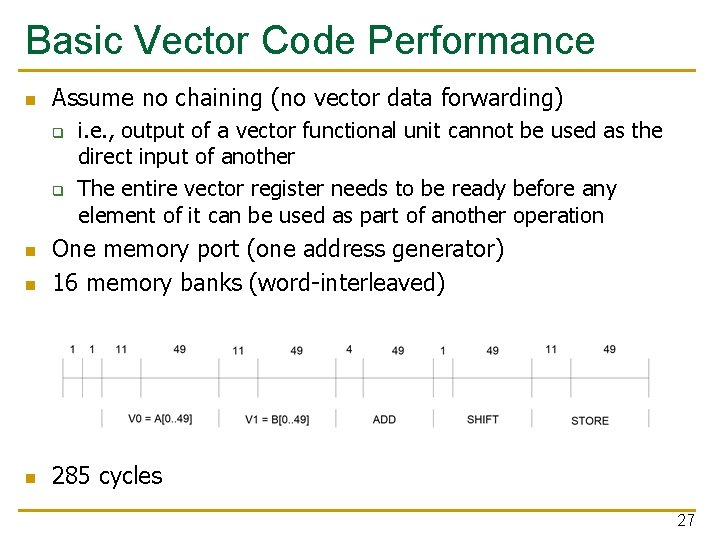

Scalar Code Example n For I = 0 to 49 q n C[i] = (A[i] + B[i]) / 2 Scalar code (instruction and its latency) MOVI R 0 = 50 MOVA R 1 = A MOVA R 2 = B MOVA R 3 = C X: LD R 4 = MEM[R 1++] LD R 5 = MEM[R 2++] ADD R 6 = R 4 + R 5 SHFR R 7 = R 6 >> 1 ST MEM[R 3++] = R 7 DECBNZ R 0, X 1 304 dynamic instructions 1 11 ; autoincrement addressing 11 4 1 11 2 ; decrement and branch if NZ 24

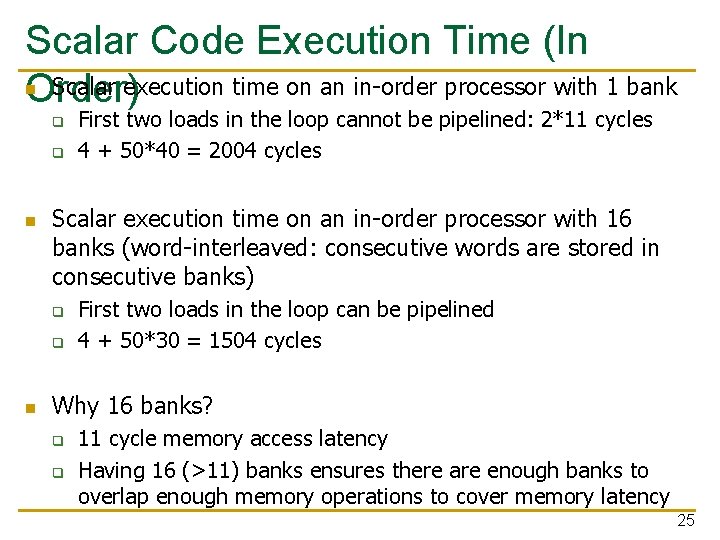

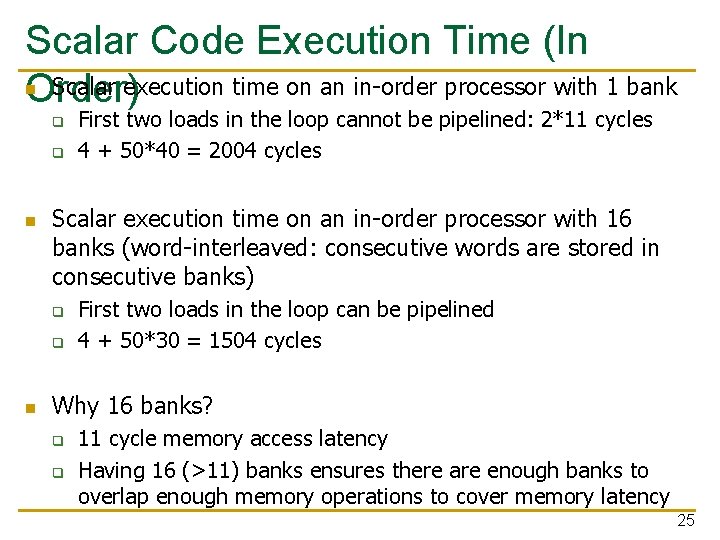

Scalar Code Execution Time (In n Scalar execution time on an in-order processor with 1 bank Order) q q n Scalar execution time on an in-order processor with 16 banks (word-interleaved: consecutive words are stored in consecutive banks) q q n First two loads in the loop cannot be pipelined: 2*11 cycles 4 + 50*40 = 2004 cycles First two loads in the loop can be pipelined 4 + 50*30 = 1504 cycles Why 16 banks? q q 11 cycle memory access latency Having 16 (>11) banks ensures there are enough banks to overlap enough memory operations to cover memory latency 25

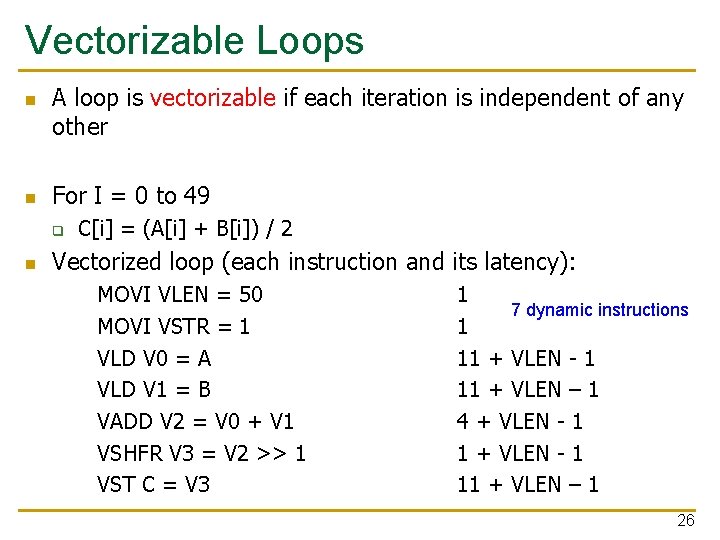

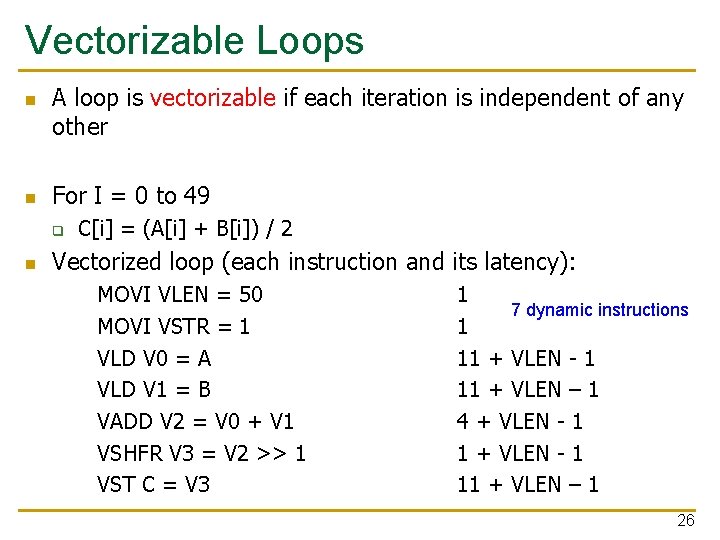

Vectorizable Loops n n A loop is vectorizable if each iteration is independent of any other For I = 0 to 49 q n C[i] = (A[i] + B[i]) / 2 Vectorized loop (each instruction and its latency): MOVI VLEN = 50 MOVI VSTR = 1 VLD V 0 = A VLD V 1 = B VADD V 2 = V 0 + V 1 VSHFR V 3 = V 2 >> 1 VST C = V 3 1 7 dynamic instructions 1 11 + VLEN - 1 11 + VLEN – 1 4 + VLEN - 1 11 + VLEN – 1 26

Basic Vector Code Performance n Assume no chaining (no vector data forwarding) q q i. e. , output of a vector functional unit cannot be used as the direct input of another The entire vector register needs to be ready before any element of it can be used as part of another operation n One memory port (one address generator) 16 memory banks (word-interleaved) n 285 cycles n 27

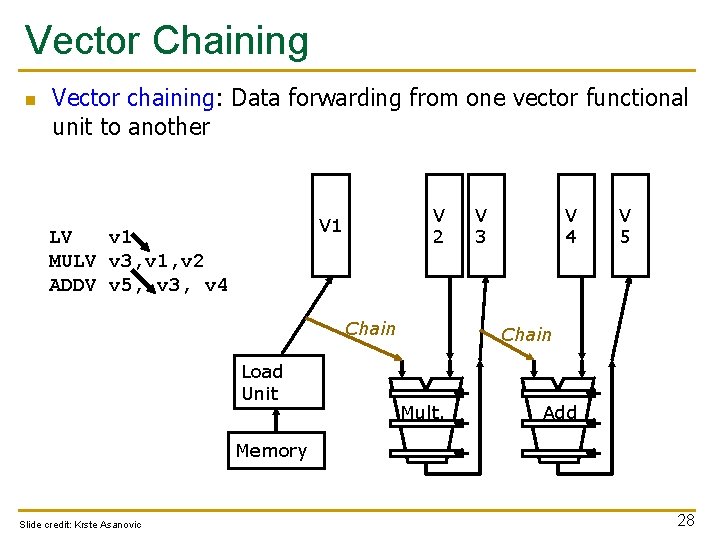

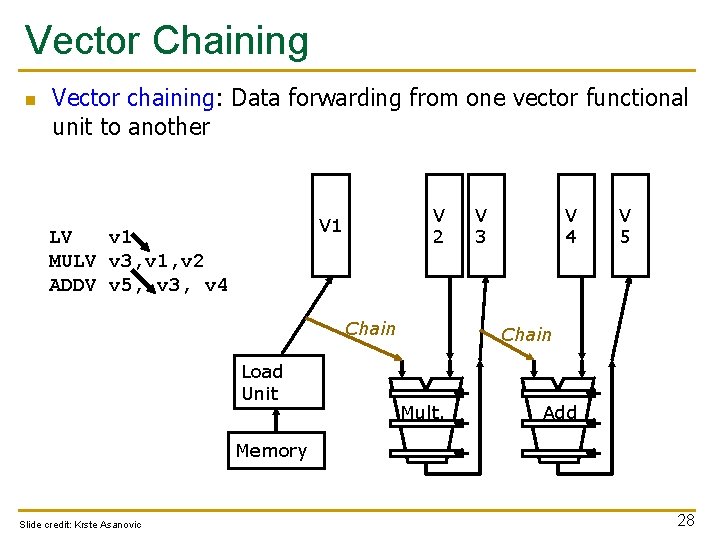

Vector Chaining n Vector chaining: Data forwarding from one vector functional unit to another V 2 V 1 LV v 1 MULV v 3, v 1, v 2 ADDV v 5, v 3, v 4 Chain Load Unit V 3 V 4 V 5 Chain Mult. Add Memory Slide credit: Krste Asanovic 28

Vector Code Performance - Chaining n Vector chaining: Data forwarding from one vector functional unit to another These two VLDs cannot be pipelined. WHY? n 182 cycles Strict assumption: Each memory bank has a single port (memory bandwidth bottleneck) VLD and VST cannot be pipelined. WHY? 29

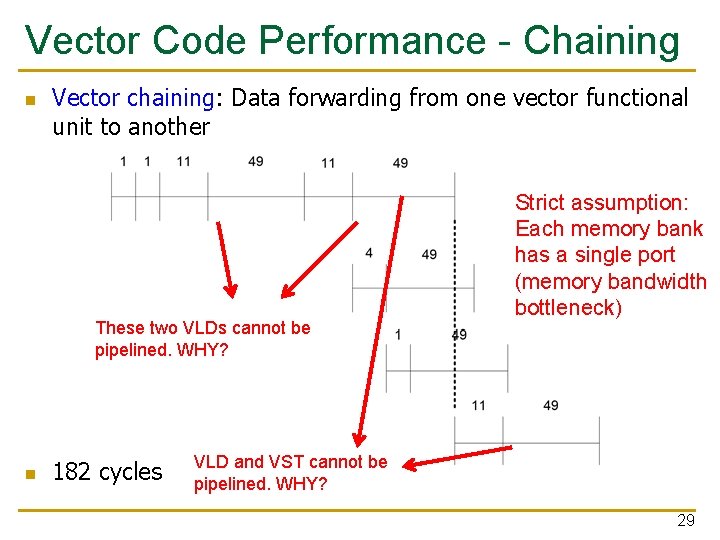

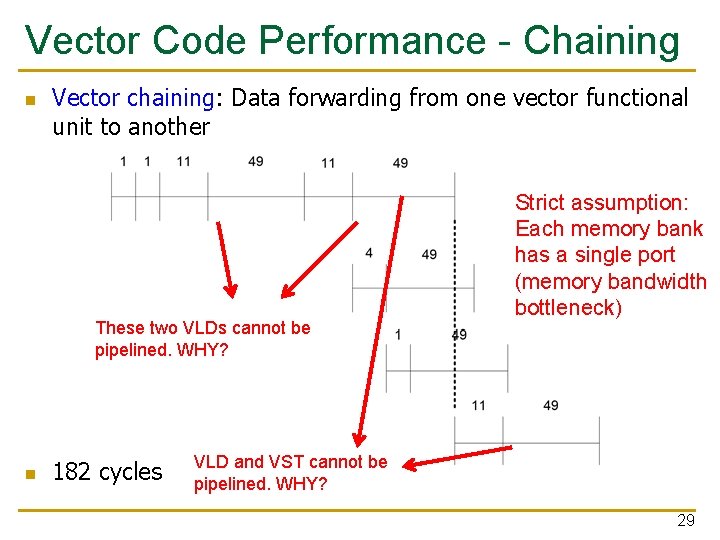

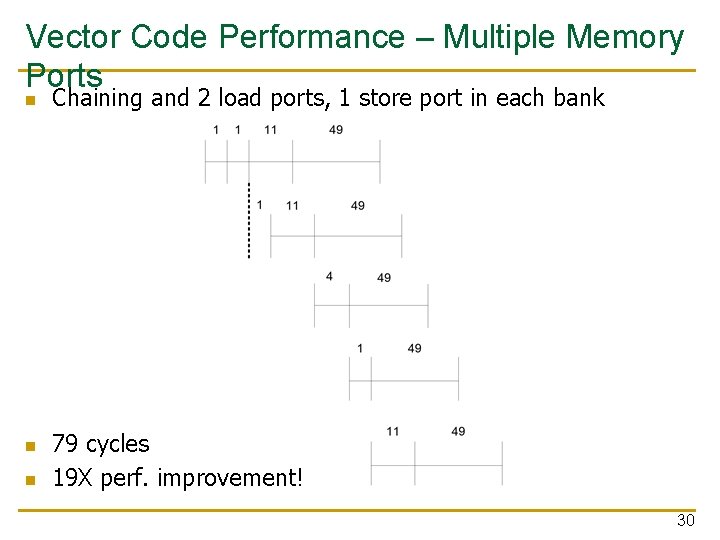

Vector Code Performance – Multiple Memory Ports n n n Chaining and 2 load ports, 1 store port in each bank 79 cycles 19 X perf. improvement! 30

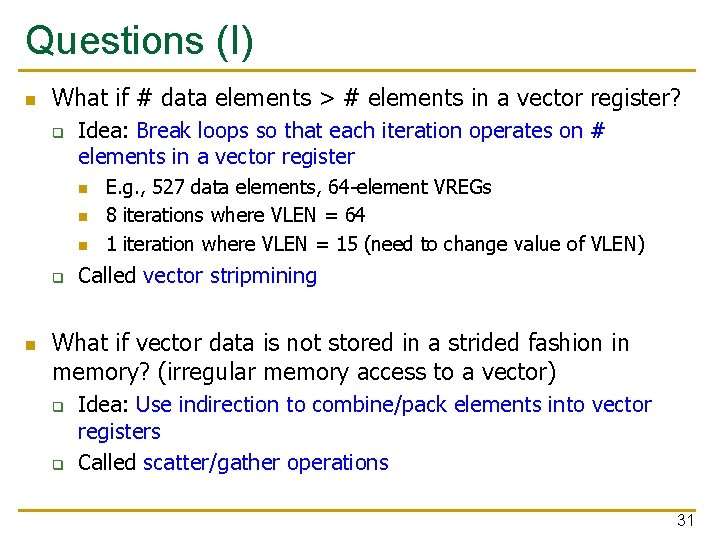

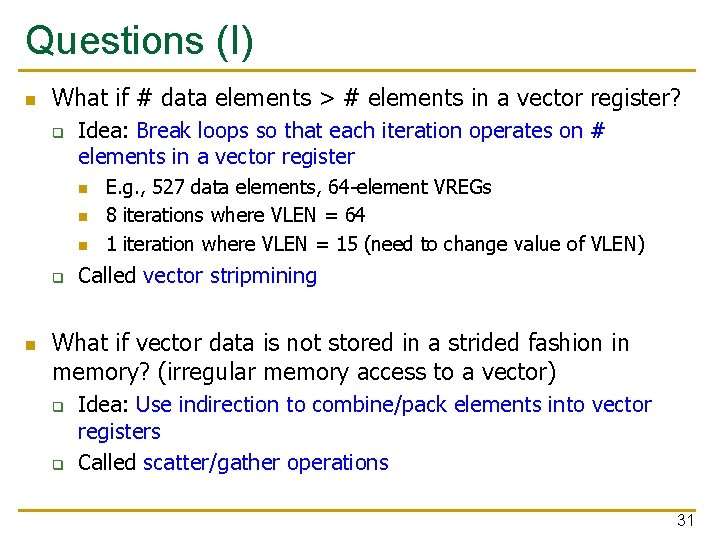

Questions (I) n What if # data elements > # elements in a vector register? q Idea: Break loops so that each iteration operates on # elements in a vector register n n n q n E. g. , 527 data elements, 64 -element VREGs 8 iterations where VLEN = 64 1 iteration where VLEN = 15 (need to change value of VLEN) Called vector stripmining What if vector data is not stored in a strided fashion in memory? (irregular memory access to a vector) q q Idea: Use indirection to combine/pack elements into vector registers Called scatter/gather operations 31

![GatherScatter Operations Want to vectorize loops with indirect accesses for i0 iN i Ai Gather/Scatter Operations Want to vectorize loops with indirect accesses: for (i=0; i<N; i++) A[i]](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-32.jpg)

Gather/Scatter Operations Want to vectorize loops with indirect accesses: for (i=0; i<N; i++) A[i] = B[i] + C[D[i]] Indexed load instruction (Gather) LV v. D, r. D LVI v. C, r. C, v. D LV v. B, r. B ADDV. D v. A, v. B, v. C SV v. A, r. A # # # Load indices in D vector Load indirect from r. C base Load B vector Do add Store result 32

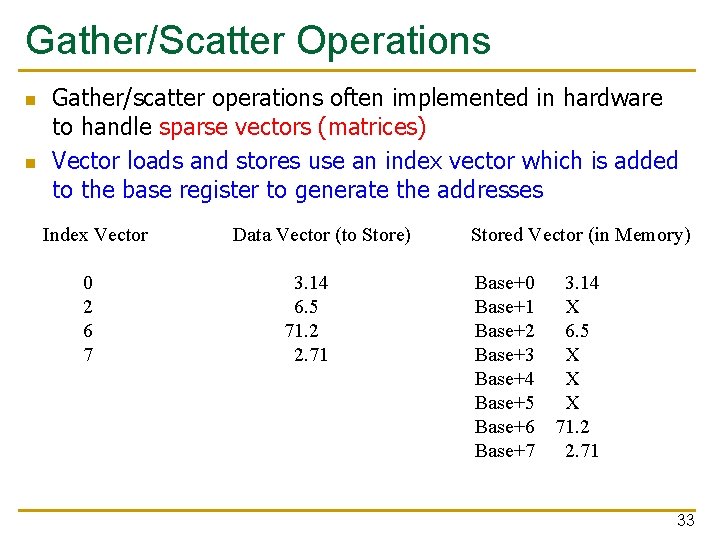

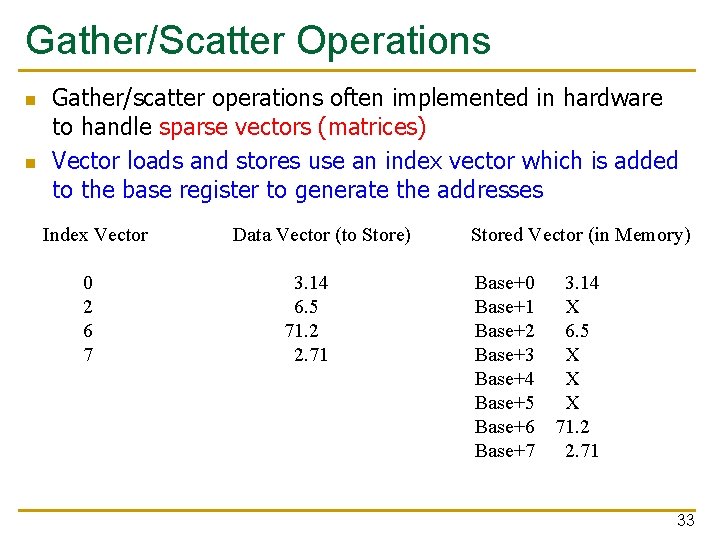

Gather/Scatter Operations n n Gather/scatter operations often implemented in hardware to handle sparse vectors (matrices) Vector loads and stores use an index vector which is added to the base register to generate the addresses Index Vector 0 2 6 7 Data Vector (to Store) 3. 14 6. 5 71. 2 2. 71 Stored Vector (in Memory) Base+0 3. 14 Base+1 X Base+2 6. 5 Base+3 X Base+4 X Base+5 X Base+6 71. 2 Base+7 2. 71 33

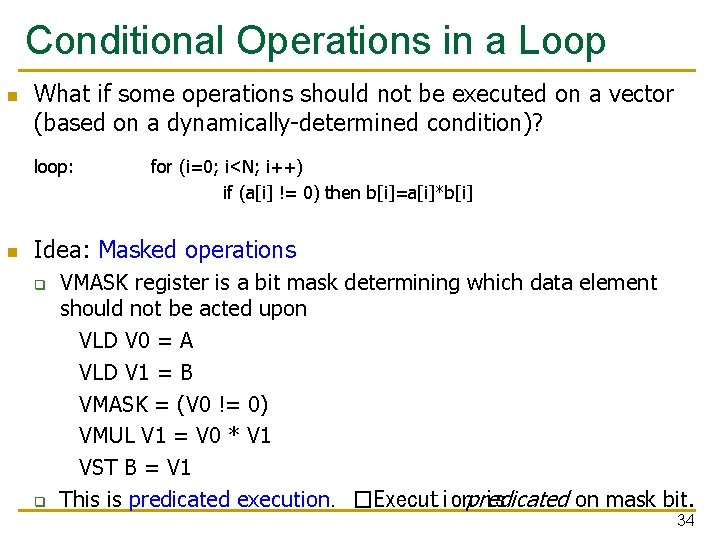

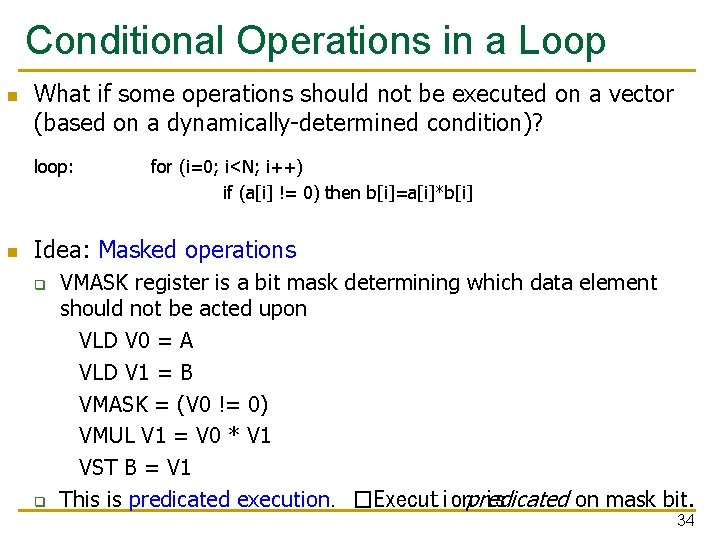

Conditional Operations in a Loop n What if some operations should not be executed on a vector (based on a dynamically-determined condition)? loop: n for (i=0; i<N; i++) if (a[i] != 0) then b[i]=a[i]*b[i] Idea: Masked operations q q VMASK register is a bit mask determining which data element should not be acted upon VLD V 0 = A VLD V 1 = B VMASK = (V 0 != 0) VMUL V 1 = V 0 * V 1 VST B = V 1 This is predicated execution. �Executionpredicated is on mask bit. 34

![Another Example with Masking for i 0 i 64 i if ai Another Example with Masking for (i = 0; i < 64; ++i) if (a[i]](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-35.jpg)

Another Example with Masking for (i = 0; i < 64; ++i) if (a[i] >= b[i]) c[i] = a[i] else c[i] = b[i] Steps to execute the loop in SIMD code 1. Compare A, B to get VMASK 2. Masked store of A into C A 1 2 3 4 -5 0 6 -7 B 2 2 2 10 -4 -3 5 -8 VMASK 0 1 1 0 0 1 1 1 3. Complement VMASK 4. Masked store of B into C 35

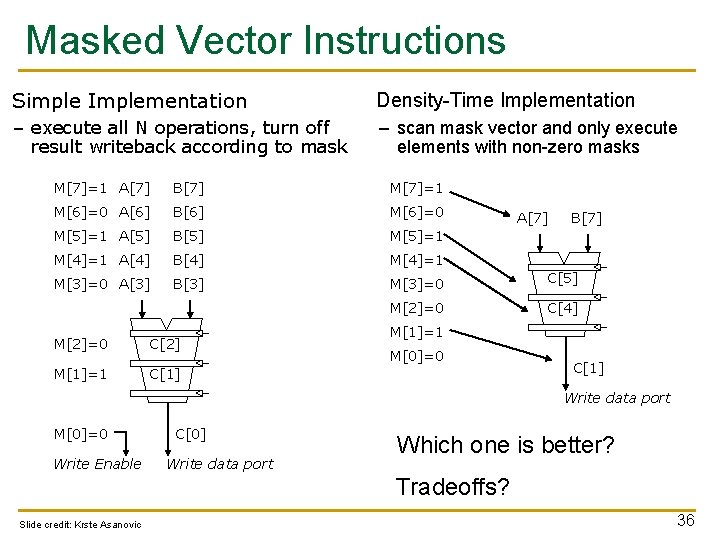

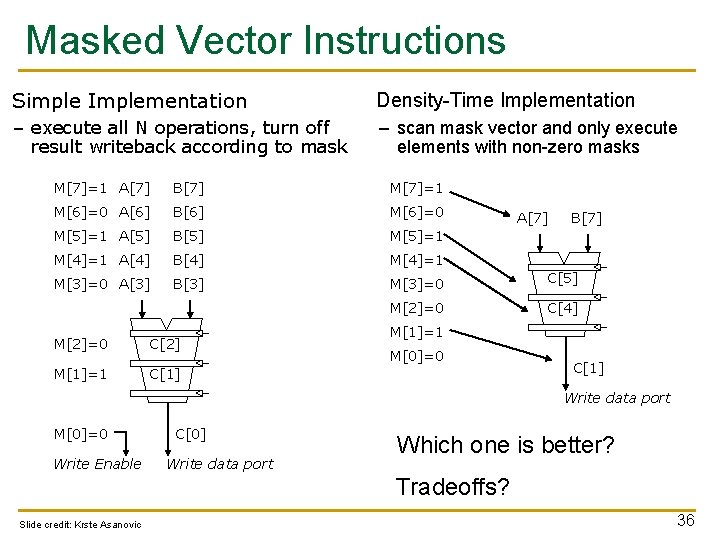

Masked Vector Instructions Simple Implementation Density-Time Implementation – execute all N operations, turn off result writeback according to mask – scan mask vector and only execute elements with non-zero masks M[7]=1 A[7] B[7] M[7]=1 M[6]=0 A[6] B[6] M[6]=0 M[5]=1 A[5] B[5] M[5]=1 M[4]=1 A[4] B[4] M[4]=1 M[3]=0 A[3] B[3] M[3]=0 C[5] M[2]=0 C[4] M[2]=0 C[2] M[1]=1 C[1] A[7] B[7] M[1]=1 M[0]=0 C[1] Write data port M[0]=0 Write Enable C[0] Write data port Which one is better? Tradeoffs? Slide credit: Krste Asanovic 36

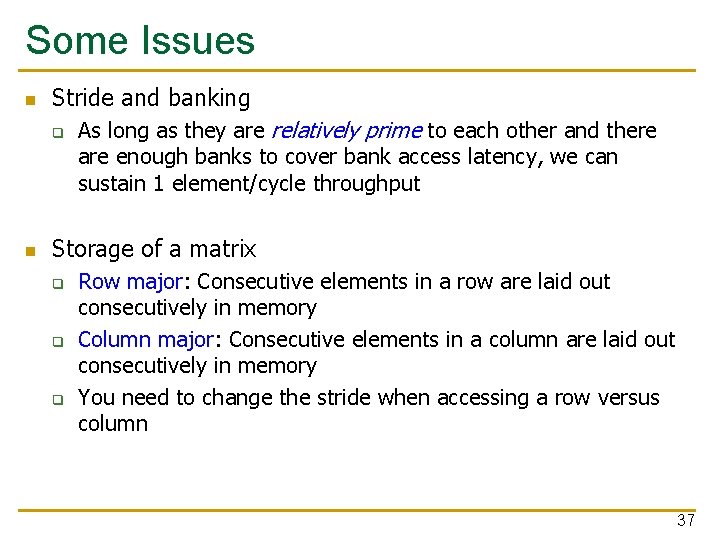

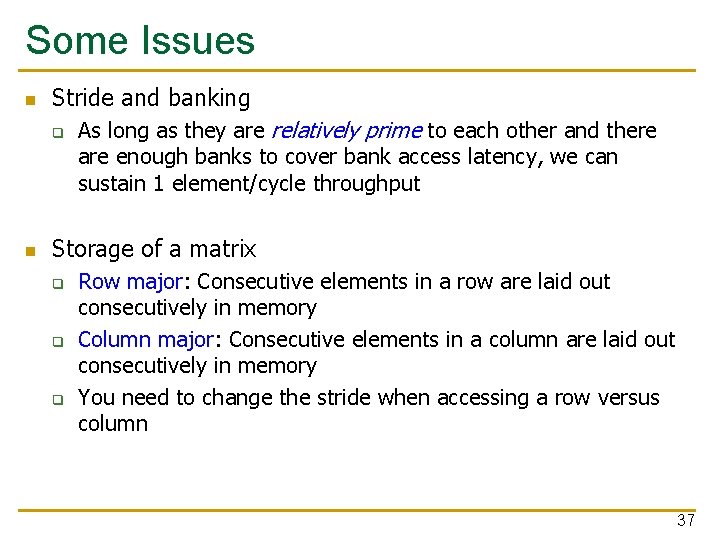

Some Issues n Stride and banking q n As long as they are relatively prime to each other and there are enough banks to cover bank access latency, we can sustain 1 element/cycle throughput Storage of a matrix q q q Row major: Consecutive elements in a row are laid out consecutively in memory Column major: Consecutive elements in a column are laid out consecutively in memory You need to change the stride when accessing a row versus column 37

38

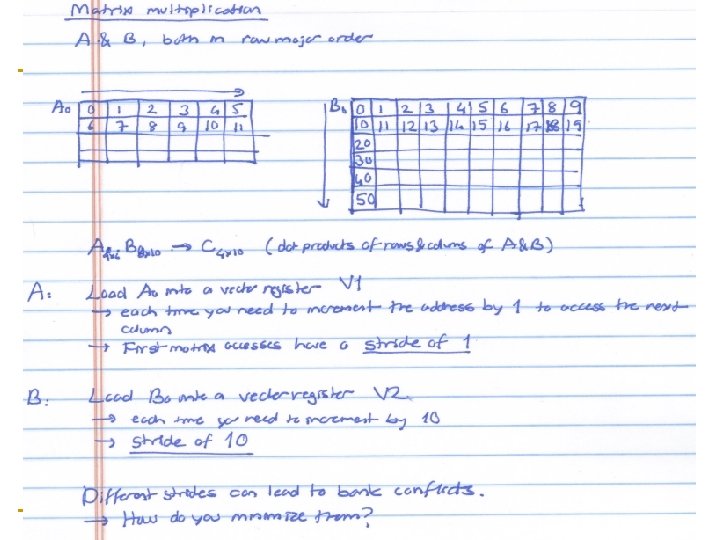

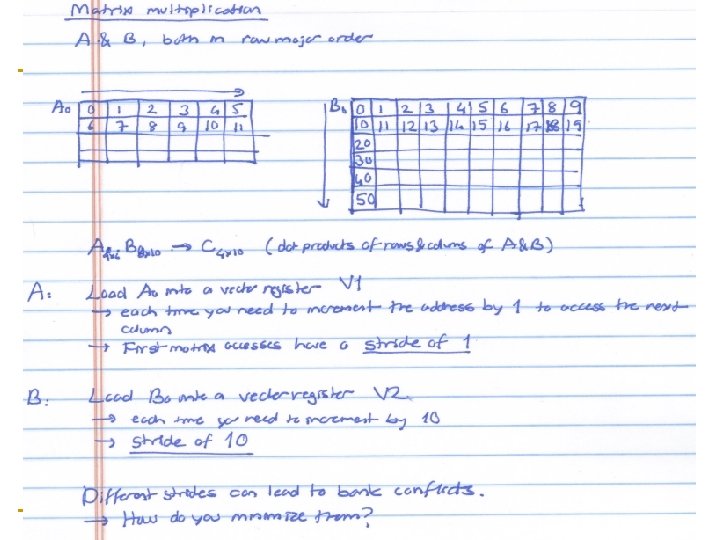

Minimizing Bank Conflicts n More banks n Better data layout to match the access pattern q n Is this always possible? Better mapping of address to bank q q E. g. , randomized mapping Rau, “Pseudo-randomly interleaved memory, ” ISCA 1991. 39

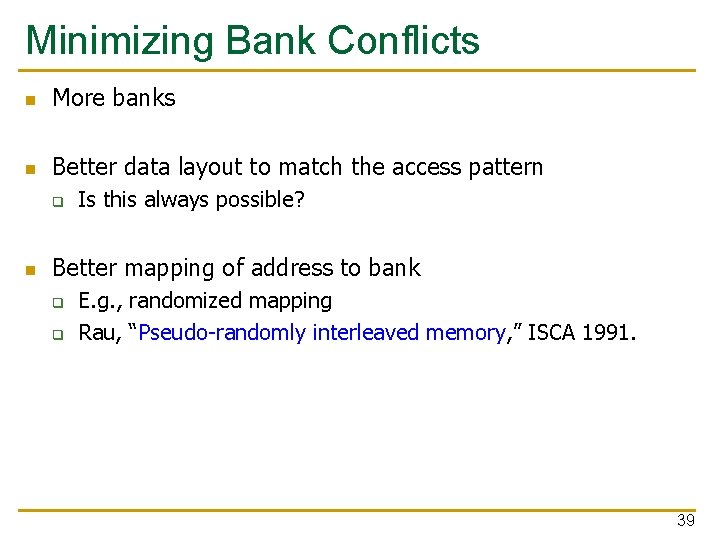

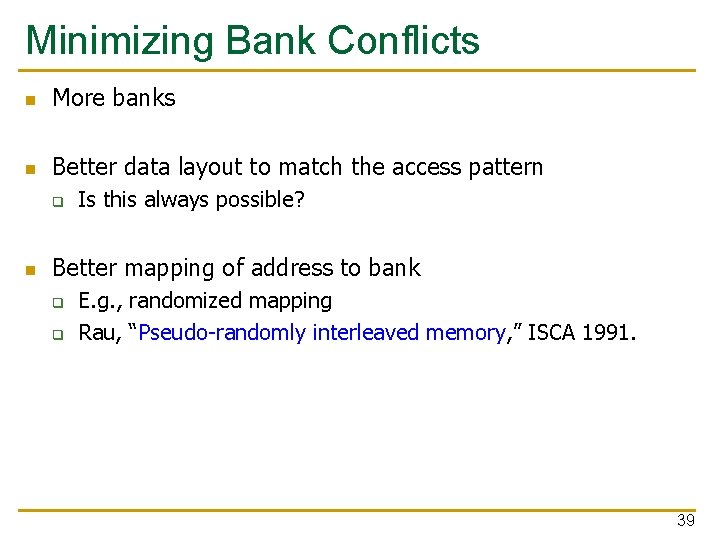

Array vs. Vector Processors, Revisited n Array vs. vector processor distinction is a “purist’s” distinction n Most “modern” SIMD processors are a combination of both q q They exploit data parallelism in both time and space GPUs are a prime example we will cover in a bit more detail 40

Remember: Array vs. Vector Processors ARRAY PROCESSOR VECTOR PROCESSOR Instruction Stream LD ADD MUL ST Same op @ same time VR A[3: 0] VR VR, 1 VR VR, 2 A[3: 0] VR Different ops @ time LD 0 LD 1 LD 2 LD 3 LD 0 AD 1 AD 2 AD 3 LD 1 AD 0 MU 1 MU 2 MU 3 LD 2 AD 1 MU 0 ST 1 ST 2 LD 3 AD 2 MU 1 ST 0 ST 3 Different ops @ same space AD 3 MU 2 ST 1 MU 3 ST 2 Same op @ space ST 3 Time Space 41

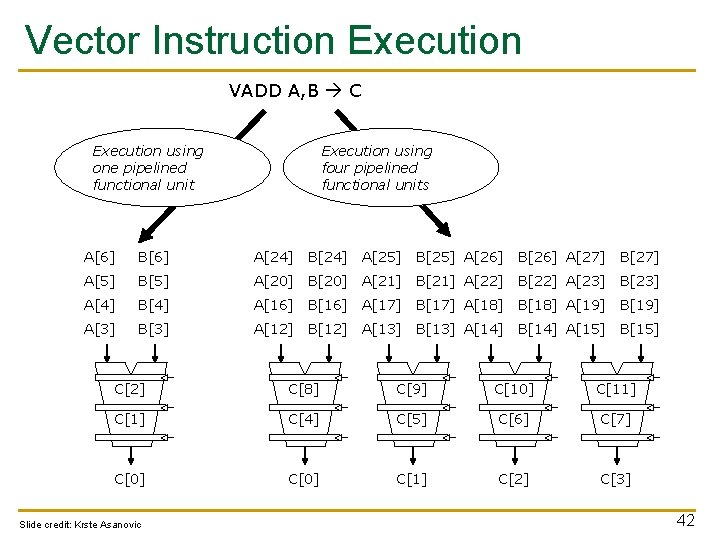

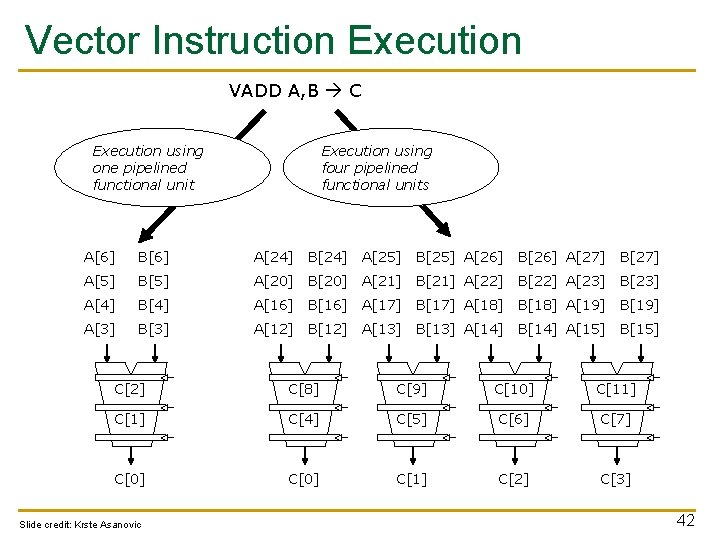

Vector Instruction Execution VADD A, B C Execution using one pipelined functional unit Execution using four pipelined functional units A[6] B[6] A[24] B[24] A[25] B[25] A[26] B[26] A[27] B[27] A[5] B[5] A[20] B[20] A[21] B[21] A[22] B[22] A[23] B[23] A[4] B[4] A[16] B[16] A[17] B[17] A[18] B[18] A[19] B[19] A[3] B[3] A[12] B[12] A[13] B[13] A[14] B[14] A[15] B[15] C[2] C[8] C[9] C[10] C[11] C[4] C[5] C[6] C[7] C[0] C[1] C[2] C[3] Slide credit: Krste Asanovic 42

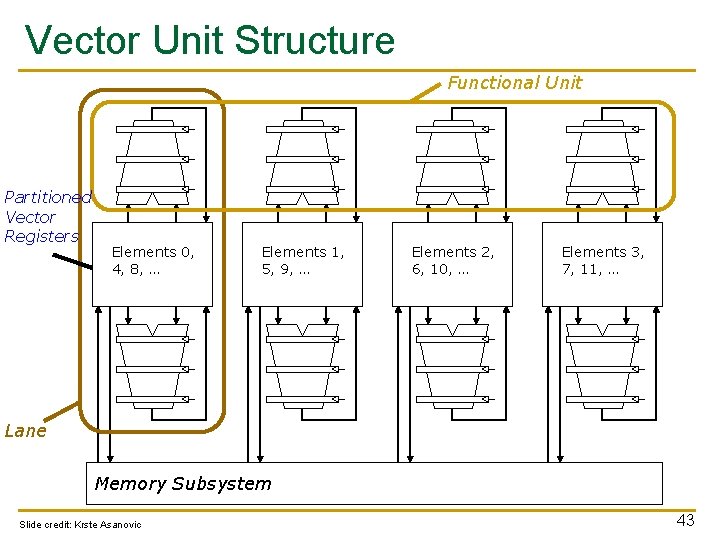

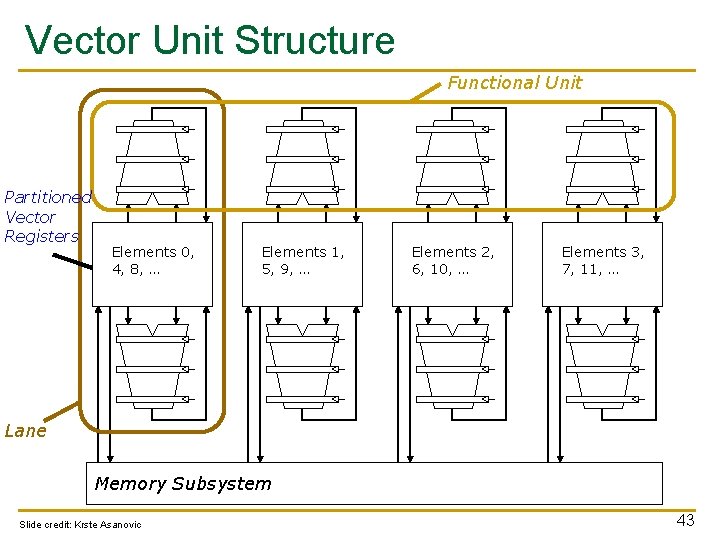

Vector Unit Structure Functional Unit Partitioned Vector Registers Elements 0, 4, 8, … Elements 1, 5, 9, … Elements 2, 6, 10, … Elements 3, 7, 11, … Lane Memory Subsystem Slide credit: Krste Asanovic 43

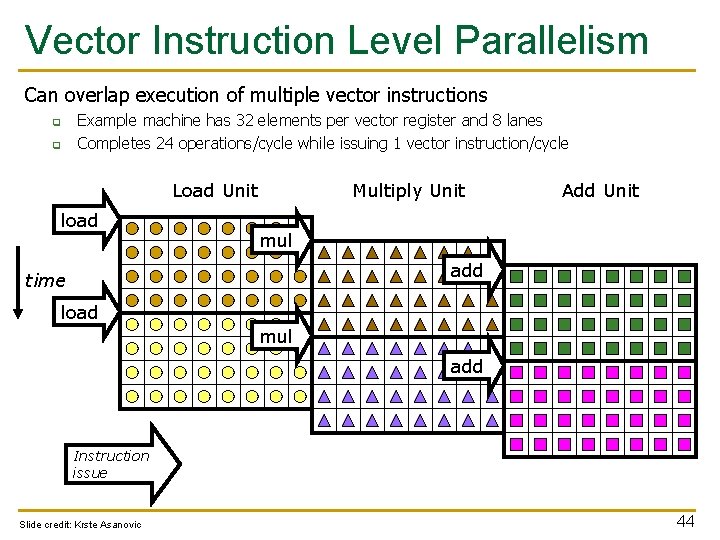

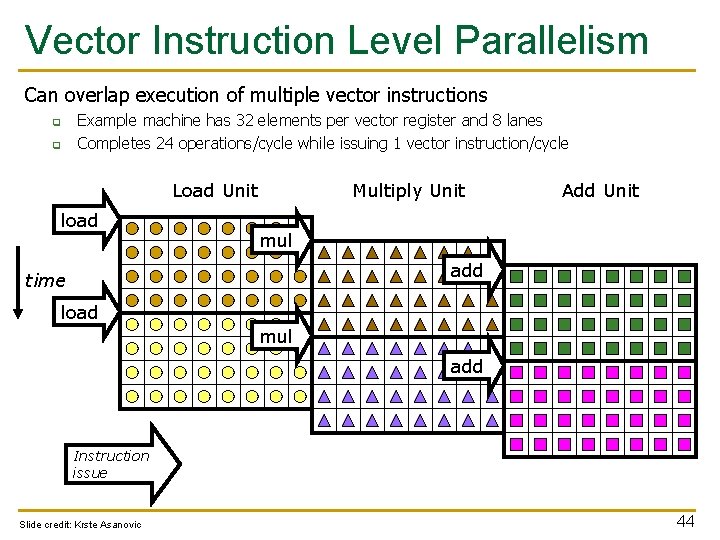

Vector Instruction Level Parallelism Can overlap execution of multiple vector instructions q q Example machine has 32 elements per vector register and 8 lanes Completes 24 operations/cycle while issuing 1 vector instruction/cycle Load Unit load Multiply Unit Add Unit mul add time load mul add Instruction issue Slide credit: Krste Asanovic 44

Design of Digital Circuits Lecture 20: SIMD Processors Prof. Onur Mutlu ETH Zurich Spring 2017 11 May 2017

We did not cover the following slides in lecture. These are for your preparation for the next lecture.

![Automatic Code Vectorization for i0 i N i Ci Ai Bi Automatic Code Vectorization for (i=0; i < N; i++) C[i] = A[i] + B[i];](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-47.jpg)

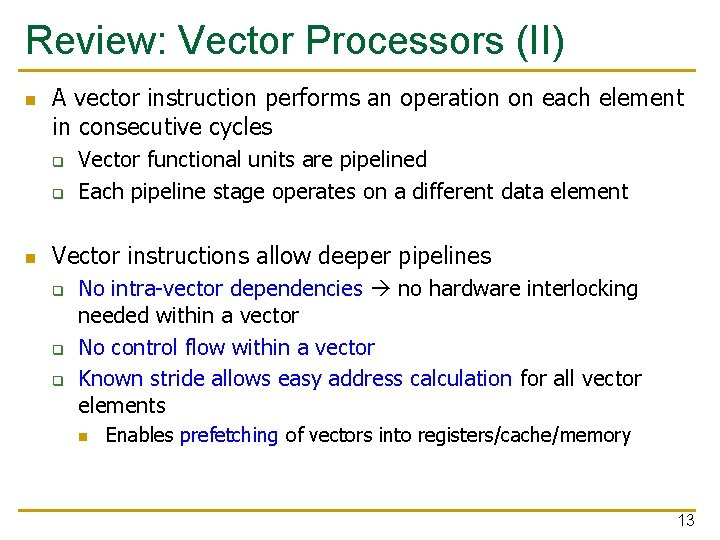

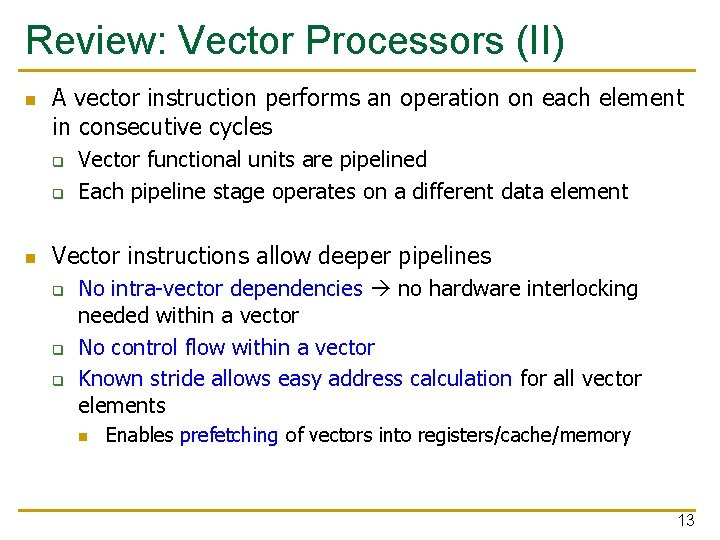

Automatic Code Vectorization for (i=0; i < N; i++) C[i] = A[i] + B[i]; Vectorized Code Scalar Sequential Code load Time Iter. 1 add store load Iter. 2 add store load Iter. 1 load add store Iter. 2 Vector Instruction Vectorization is a compile-time reordering of operation sequencing requires extensive loop dependence analysis Slide credit: Krste Asanovic 47

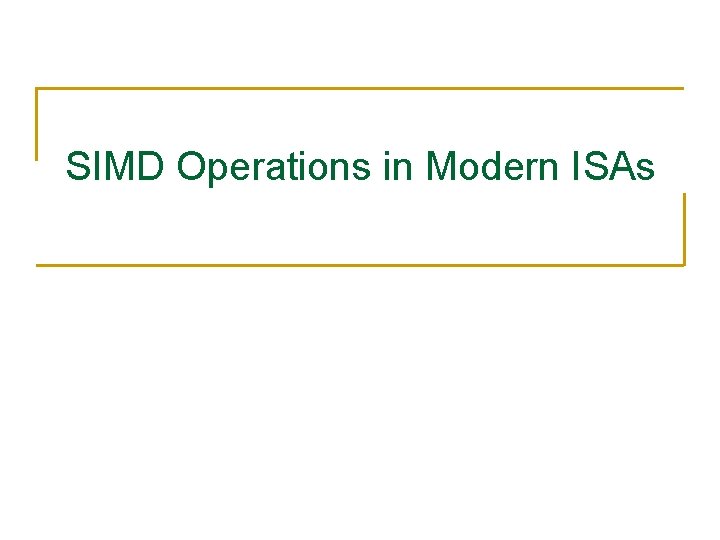

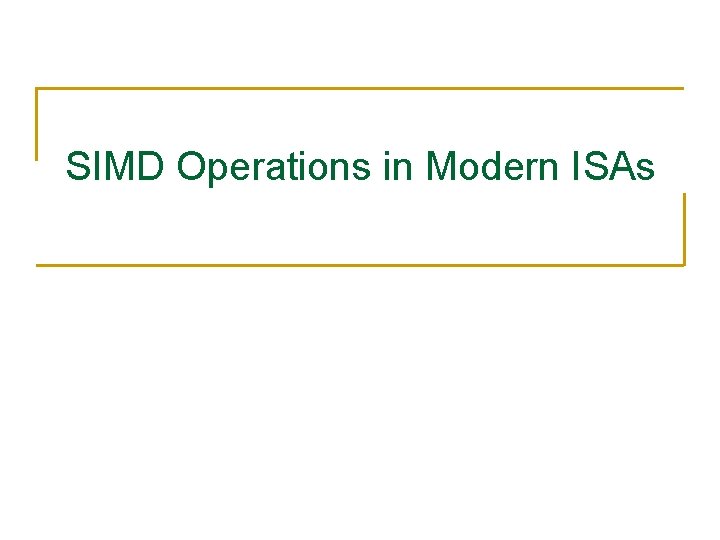

Vector/SIMD Processing Summary n Vector/SIMD machines are good at exploiting regular datalevel parallelism q q n Performance improvement limited by vectorizability of code q q q n Same operation performed on many data elements Improve performance, simplify design (no intra-vector dependencies) Scalar operations limit vector machine performance Remember Amdahl’s Law CRAY-1 was the fastest SCALAR machine at its time! Many existing ISAs include (vector-like) SIMD operations q Intel MMX/SSEn/AVX, Power. PC Alti. Vec, ARM Advanced SIMD 48

SIMD Operations in Modern ISAs

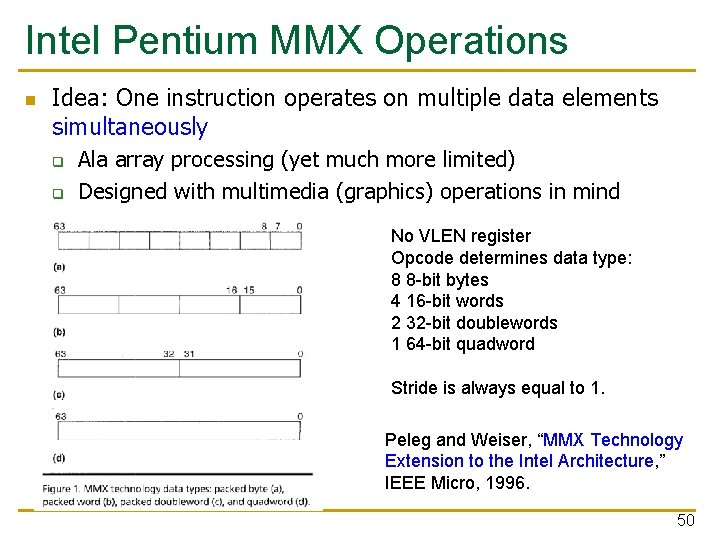

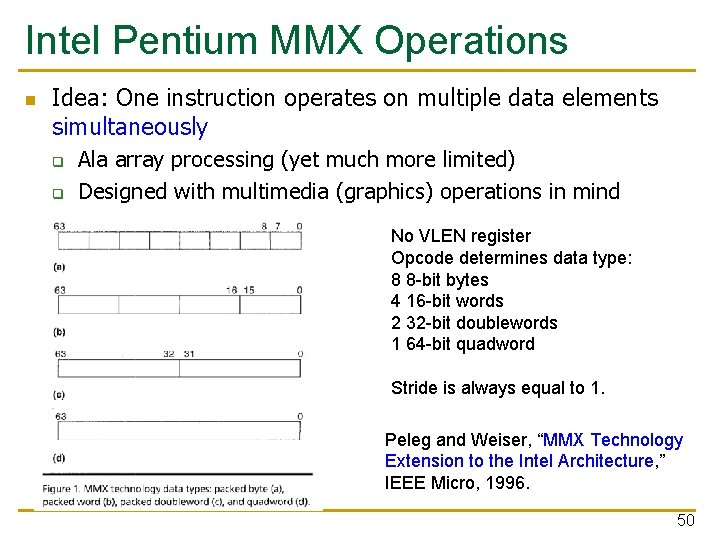

Intel Pentium MMX Operations n Idea: One instruction operates on multiple data elements simultaneously q q Ala array processing (yet much more limited) Designed with multimedia (graphics) operations in mind No VLEN register Opcode determines data type: 8 8 -bit bytes 4 16 -bit words 2 32 -bit doublewords 1 64 -bit quadword Stride is always equal to 1. Peleg and Weiser, “MMX Technology Extension to the Intel Architecture, ” IEEE Micro, 1996. 50

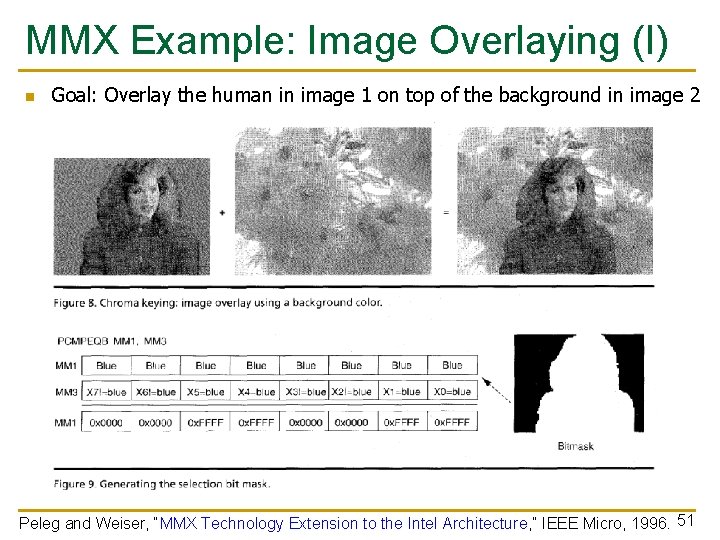

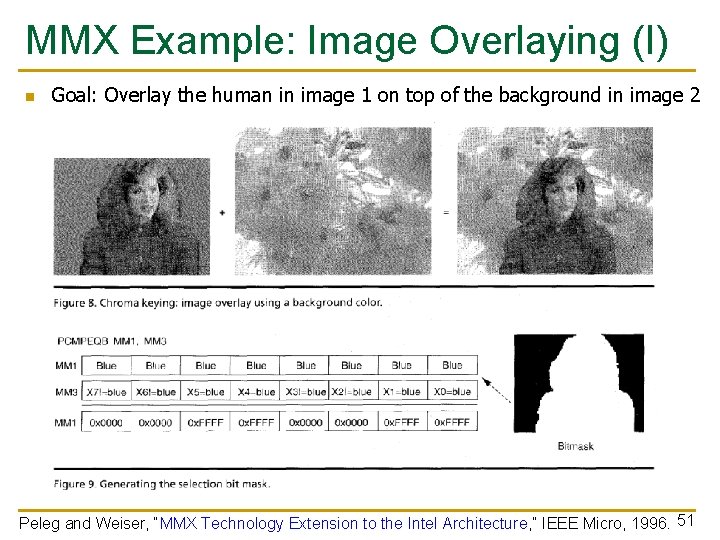

MMX Example: Image Overlaying (I) n Goal: Overlay the human in image 1 on top of the background in image 2 Peleg and Weiser, “MMX Technology Extension to the Intel Architecture, ” IEEE Micro, 1996. 51

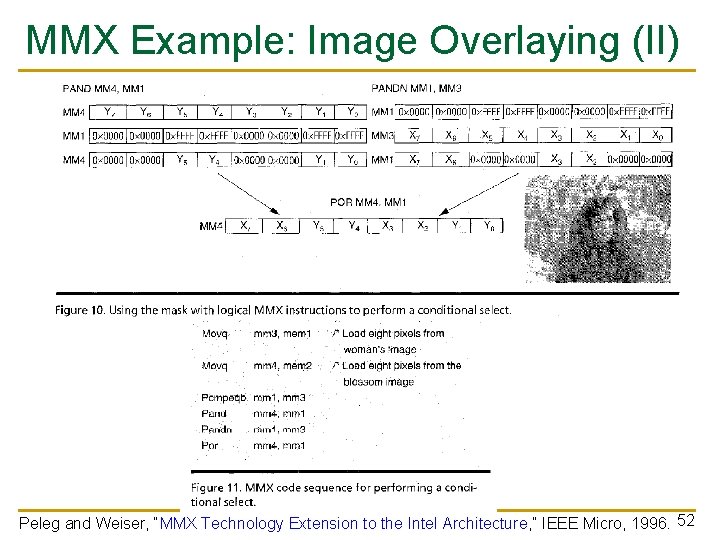

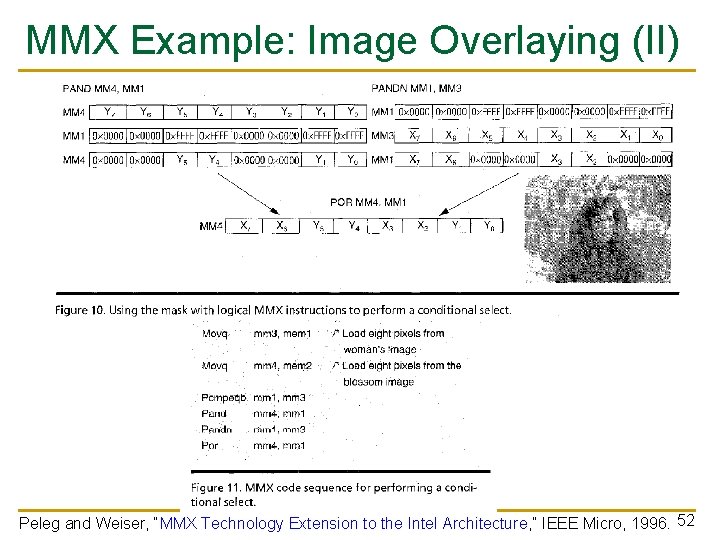

MMX Example: Image Overlaying (II) Peleg and Weiser, “MMX Technology Extension to the Intel Architecture, ” IEEE Micro, 1996. 52

GPUs (Graphics Processing Units)�

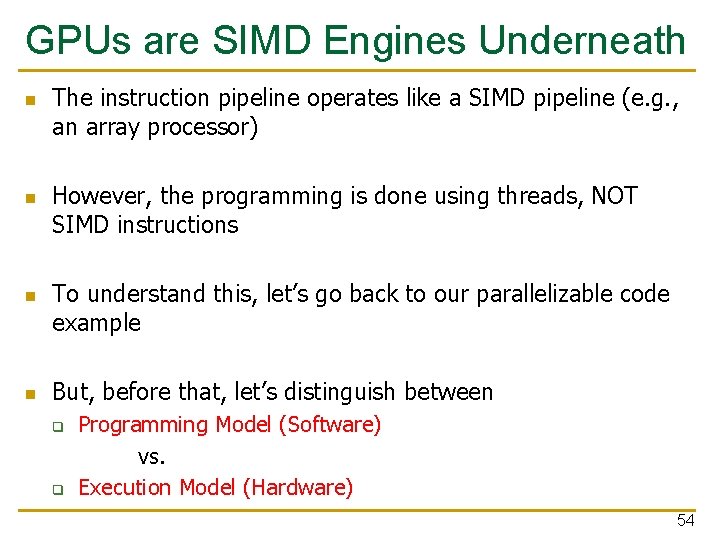

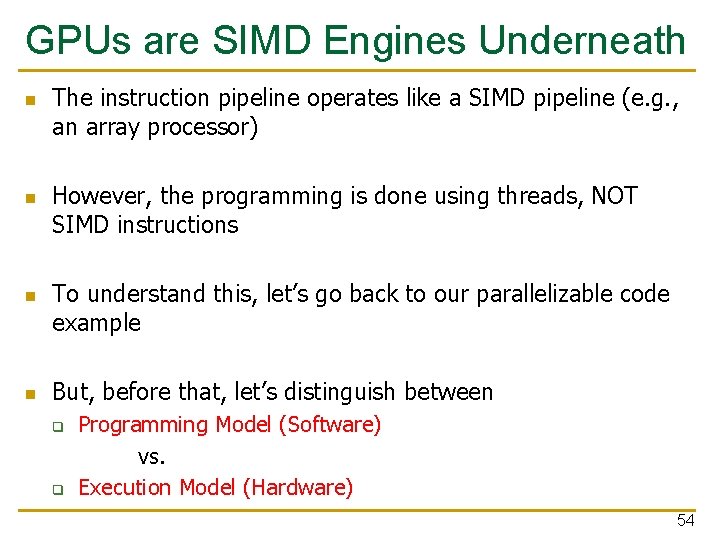

GPUs are SIMD Engines Underneath n n The instruction pipeline operates like a SIMD pipeline (e. g. , an array processor) However, the programming is done using threads, NOT SIMD instructions To understand this, let’s go back to our parallelizable code example But, before that, let’s distinguish between q q Programming Model (Software) vs. Execution Model (Hardware) 54

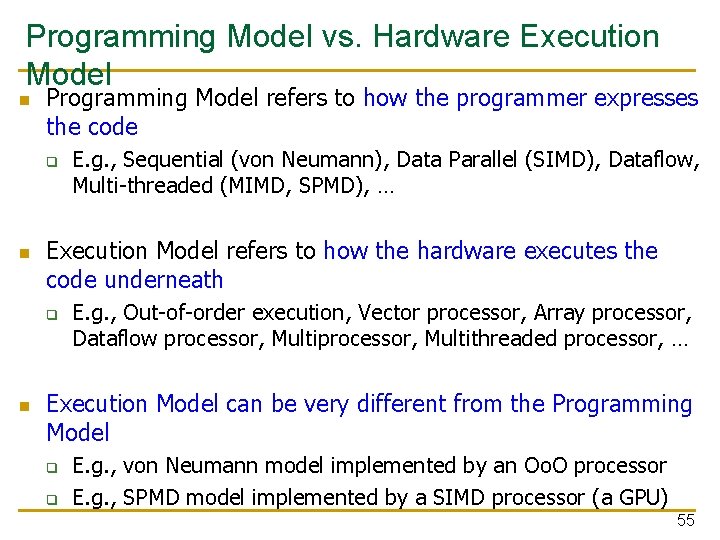

Programming Model vs. Hardware Execution Model n Programming Model refers to how the programmer expresses the code q n Execution Model refers to how the hardware executes the code underneath q n E. g. , Sequential (von Neumann), Data Parallel (SIMD), Dataflow, Multi-threaded (MIMD, SPMD), … E. g. , Out-of-order execution, Vector processor, Array processor, Dataflow processor, Multithreaded processor, … Execution Model can be very different from the Programming Model q q E. g. , von Neumann model implemented by an Oo. O processor E. g. , SPMD model implemented by a SIMD processor (a GPU) 55

![How Can You Exploit Parallelism Here for i0 i N i Ci How Can You Exploit Parallelism Here? for (i=0; i < N; i++) C[i] =](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-56.jpg)

How Can You Exploit Parallelism Here? for (i=0; i < N; i++) C[i] = A[i] + B[i]; Scalar Sequential Code load Iter. 1 add Let’s examine three programming options to exploit instruction-level parallelism present in this sequential code: store 1. Sequential (SISD) load Iter. 2 2. Data-Parallel (SIMD) add store 3. Multithreaded (MIMD/SPMD) 56

![for i0 i N i Ci Ai Bi Prog Model 1 for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 1:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-57.jpg)

for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 1: Sequential (SISD) Scalar Sequential Code n load Iter. 1 n n Can be executed on a: Pipelined processor Out-of-order execution processor add q store q load Iter. 2 add store q n Independent instructions executed when ready Different iterations are present in the instruction window and can execute in parallel in multiple functional units In other words, the loop is dynamically unrolled by the hardware Superscalar or VLIW processor q Can fetch and execute multiple instructions per cycle 57

![for i0 i N i Ci Ai Bi Prog Model 2 for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 2:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-58.jpg)

for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 2: Data Parallel (SIMD) Vector Instruction Scalar Sequential Code load load Iter. 1 load Vectorized Code VLD A V 1 VLD B V 2 add add VADD store VST load Iter. 2 1 add store load V 1 + V 2 V 3 C Iter. Realization: Each iteration is independent 2 Idea: Programmer or compiler generates a SIMD instruction to execute the same instruction from all iterations across different data Best executed by a SIMD processor (vector, array) 58

![for i0 i N i Ci Ai Bi Prog Model 3 for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-59.jpg)

for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3: Multithreaded Scalar Sequential Code load load Iter. 1 load add add store load Iter. 2 1 add store load Iter. Realization: Each iteration is independent 2 Idea: Programmer or compiler generates a thread to execute each iteration. Each thread does the same thing (but on different data) Can be executed on a MIMD machine 59

![for i0 i N i Ci Ai Bi Prog Model 3 for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3:](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-60.jpg)

for (i=0; i < N; i++) C[i] = A[i] + B[i]; Prog. Model 3: Multithreaded load Iter. 1 load add store Iter. Realization: Each iteration is independent 2 Idea: This Programmer compiler generates a thread particularormodel is also called: to execute each iteration. Each thread does the SPMD: Single Multiple Data same thing (but on Program different data) be on machine Can be executed on a a SIMT SIMD machine Can be executed on a MIMD machine Single Instruction Multiple Thread 60

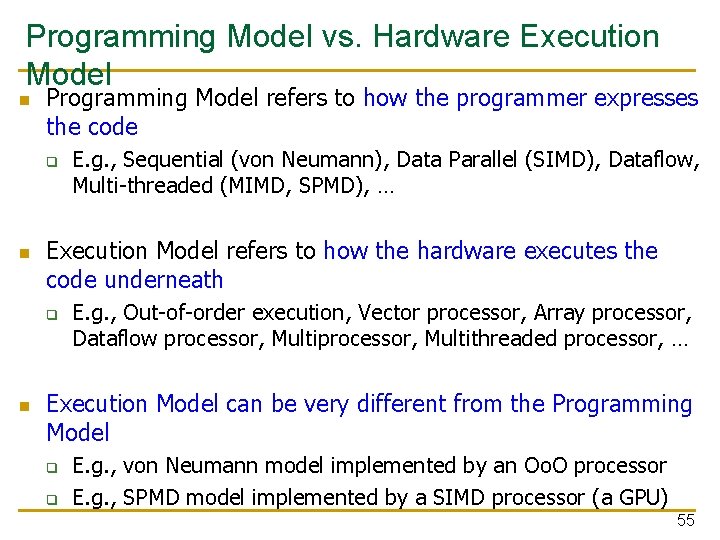

A GPU is a SIMD (SIMT) Machine n Except it is not programmed using SIMD instructions n It is programmed using threads (SPMD programming model) q q n Each thread executes the same code but operates a different piece of data Each thread has its own context (i. e. , can be treated/restarted/executed independently) A set of threads executing the same instruction are dynamically grouped into a warp (wavefront) by the hardware q A warp is essentially a SIMD operation formed by hardware! 61

SPMD on SIMT Machine load Warp 0 at PC X load Iter. 1 for (i=0; i < N; i++) C[i] = A[i] + B[i]; load Warp 0 at PC X+1 add Warp 0 at PC X+2 store Warp 0 at PC X+3 Iter. 2 Warp: A set of threads that execute Realization: Each iteration is independent the same instruction (i. e. , at the same PC) Idea: This Programmer compiler generates a thread particularormodel is also called: to execute each iteration. Each thread does the SPMD: Multiple Data same thing Single (but on Program different data) A GPU executes the SIMT model: Can be executed on a SIMD machine Can be executed onitausing MIMD machine Single Instruction Multiple Thread 62

Graphics Processing Units SIMD not Exposed to Programmer (SIMT)

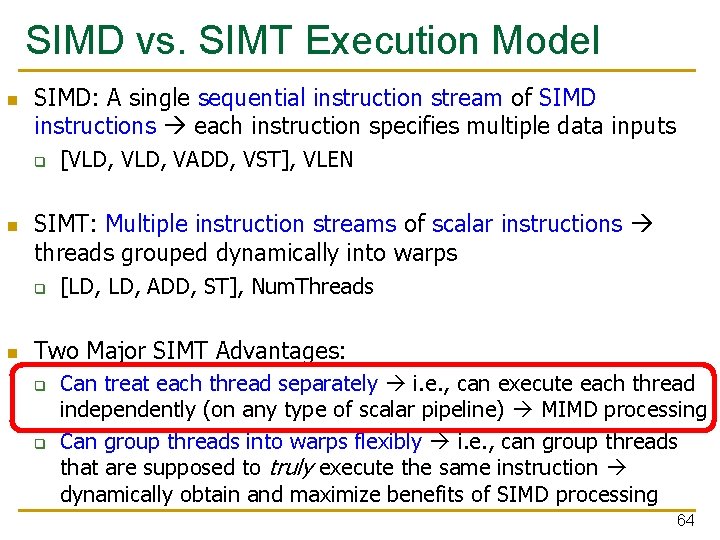

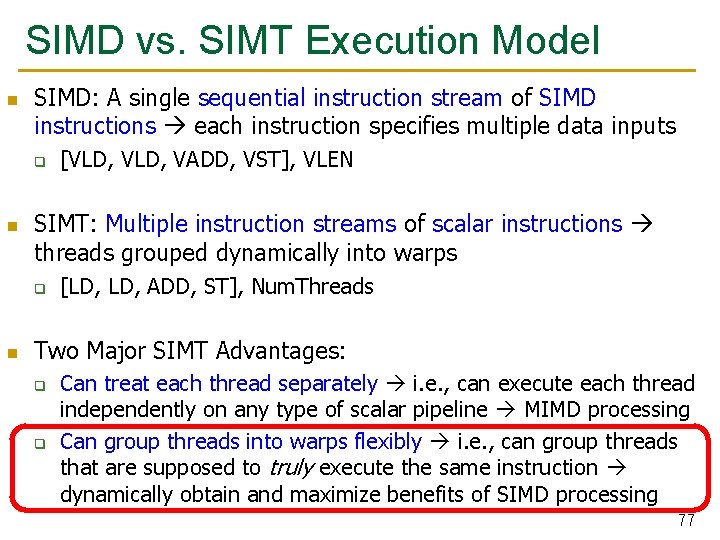

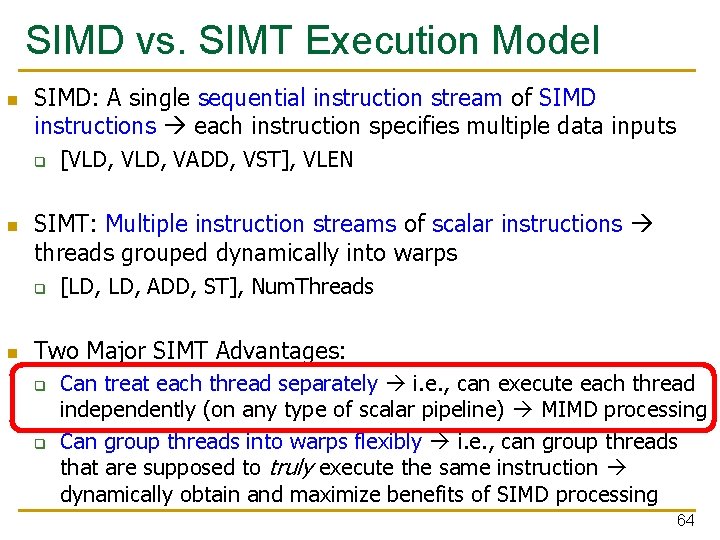

SIMD vs. SIMT Execution Model n SIMD: A single sequential instruction stream of SIMD instructions each instruction specifies multiple data inputs q n SIMT: Multiple instruction streams of scalar instructions threads grouped dynamically into warps q n [VLD, VADD, VST], VLEN [LD, ADD, ST], Num. Threads Two Major SIMT Advantages: q q Can treat each thread separately i. e. , can execute each thread independently (on any type of scalar pipeline) MIMD processing Can group threads into warps flexibly i. e. , can group threads that are supposed to truly execute the same instruction dynamically obtain and maximize benefits of SIMD processing 64

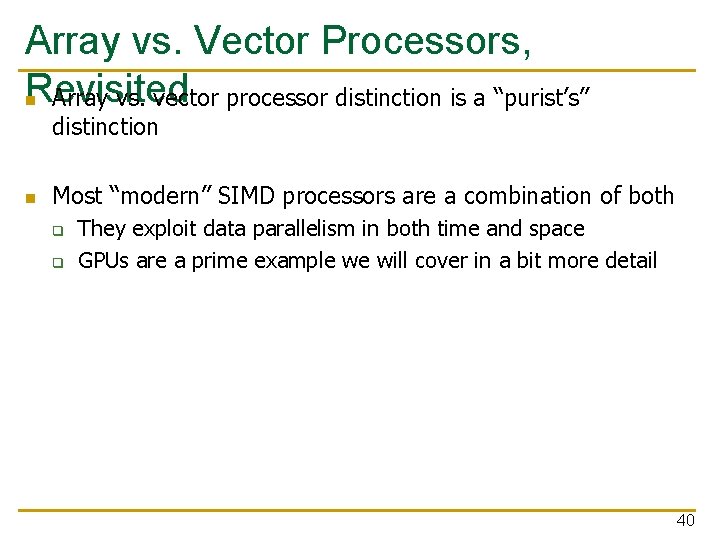

![Multithreading of Warps n n n for i0 i N i Ci Multithreading of Warps n n n for (i=0; i < N; i++) C[i] =](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-65.jpg)

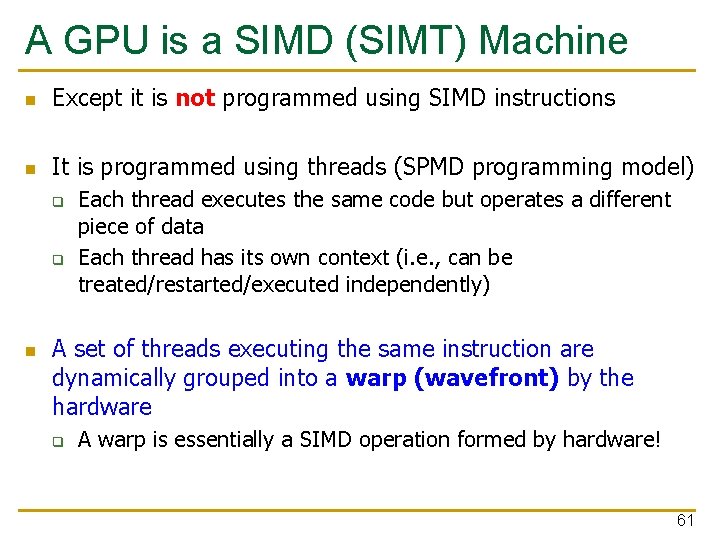

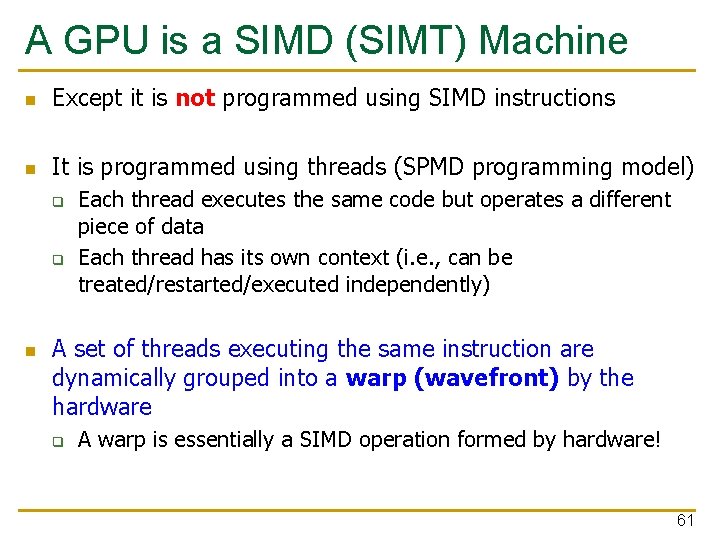

Multithreading of Warps n n n for (i=0; i < N; i++) C[i] = A[i] + B[i]; Assume a warp consists of 32 threads If you have 32 K iterations 1 K warps Warps can be interleaved on the same pipeline Fine grained multithreading of warps load add store Iter. 1 33 20*32 + 1 0 at PC X Warp 1 Warp 20 at PC X+2 Iter. 2 34 20*32 +2 65

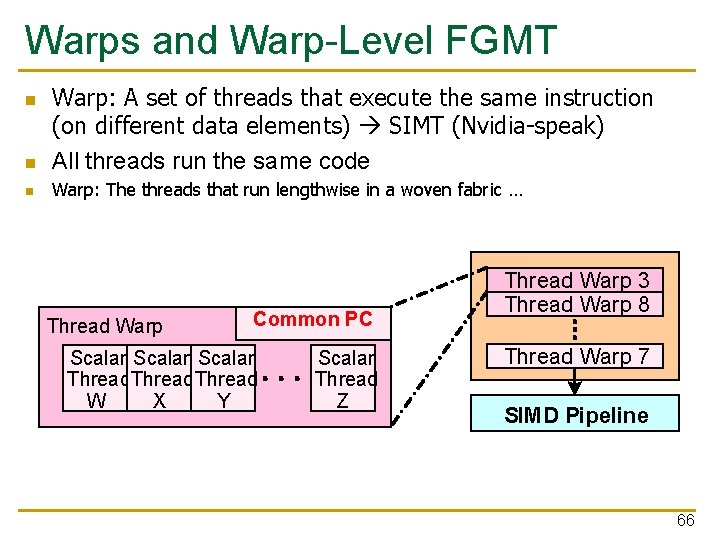

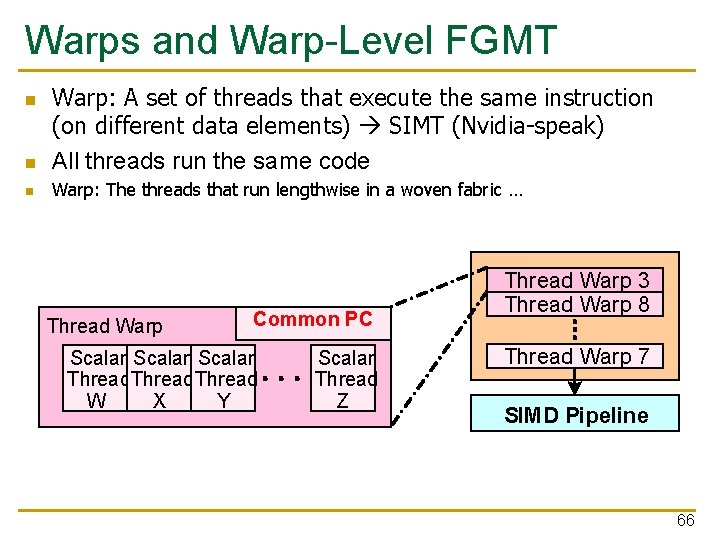

Warps and Warp-Level FGMT n Warp: A set of threads that execute the same instruction (on different data elements) SIMT (Nvidia-speak) All threads run the same code n Warp: The threads that run lengthwise in a woven fabric … n Thread Warp Common PC Scalar Thread W X Y Scalar Thread Z Thread Warp 3 Thread Warp 8 Thread Warp 7 SIMD Pipeline 66

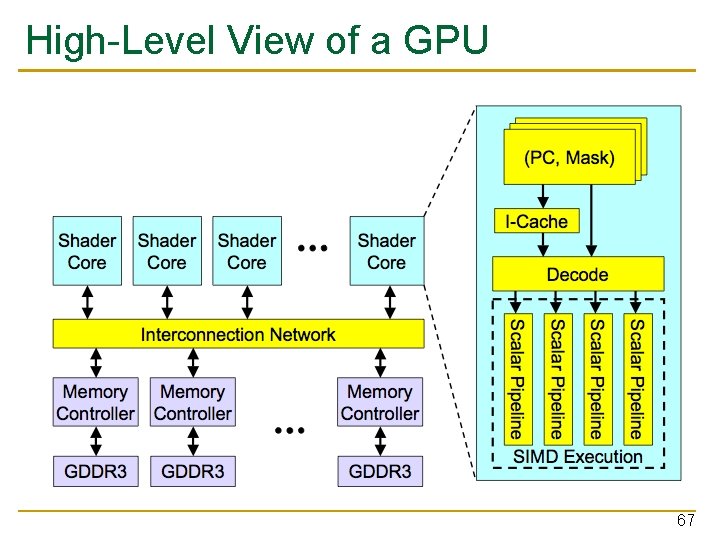

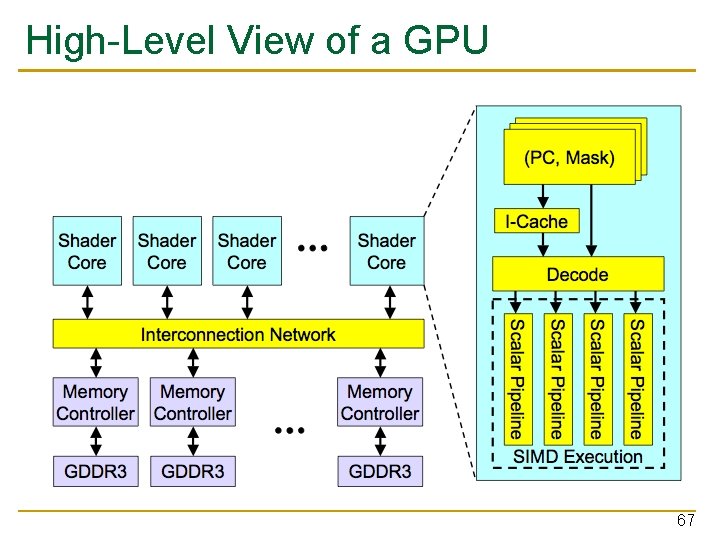

High-Level View of a GPU 67

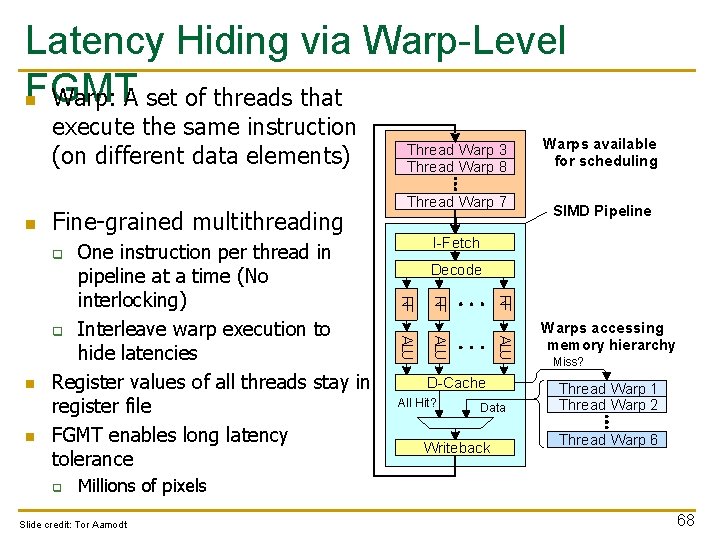

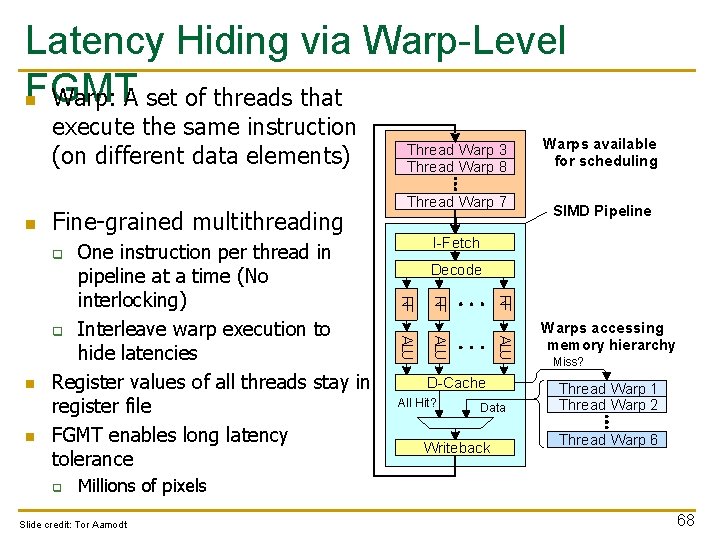

Latency Hiding via Warp-Level FGMT n Warp: A set of threads that execute the same instruction (on different data elements) n Fine-grained multithreading Thread Warp 7 RF ALU q ALU n SIMD Pipeline Decode RF n Warps available for scheduling I-Fetch q RF One instruction per thread in pipeline at a time (No interlocking) q Interleave warp execution to hide latencies Register values of all threads stay in register file FGMT enables long latency tolerance Thread Warp 3 Thread Warp 8 D-Cache All Hit? Data Writeback Warps accessing memory hierarchy Miss? Thread Warp 1 Thread Warp 2 Thread Warp 6 Millions of pixels Slide credit: Tor Aamodt 68

![Warp Execution Recall the Slide 32 thread warp executing ADD Atid Btid Ctid Execution Warp Execution (Recall the Slide) 32 -thread warp executing ADD A[tid], B[tid] C[tid] Execution](https://slidetodoc.com/presentation_image_h2/68ff4a6ea23b5b1fa33709c2eb142c22/image-69.jpg)

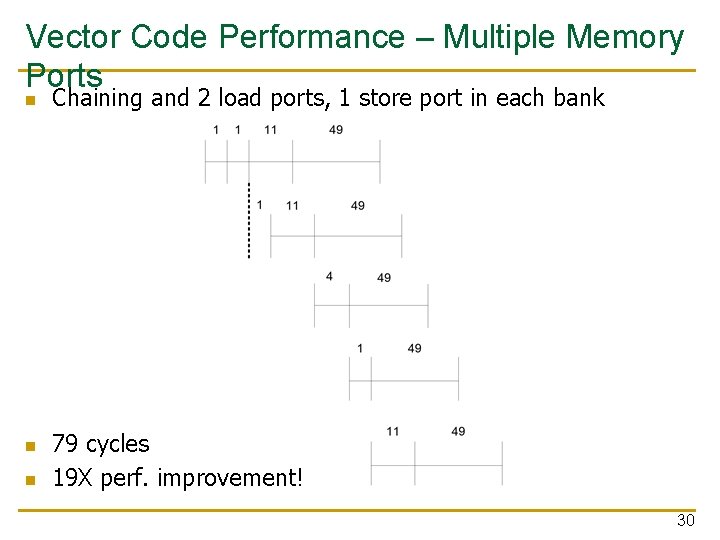

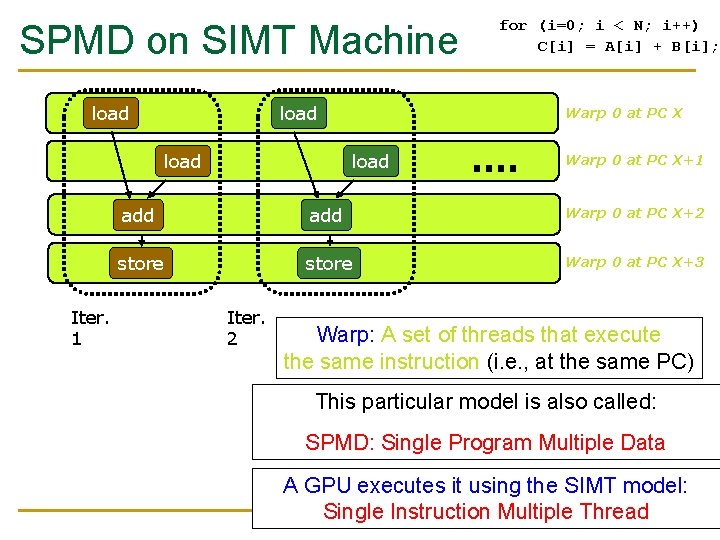

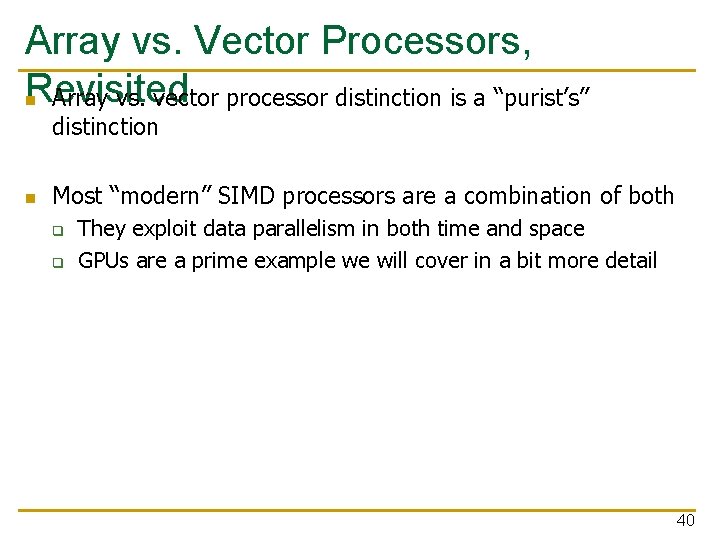

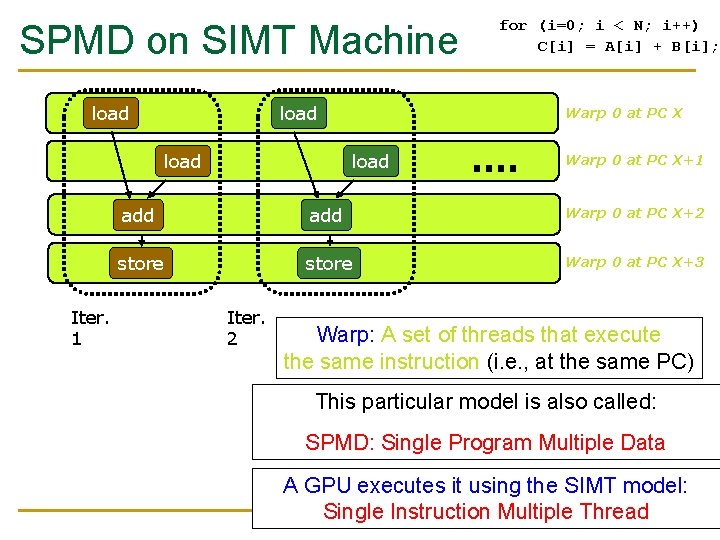

Warp Execution (Recall the Slide) 32 -thread warp executing ADD A[tid], B[tid] C[tid] Execution using one pipelined functional unit Execution using four pipelined functional units A[6] B[6] A[24] B[24] A[25] B[25] A[26] B[26] A[27] B[27] A[5] B[5] A[20] B[20] A[21] B[21] A[22] B[22] A[23] B[23] A[4] B[4] A[16] B[16] A[17] B[17] A[18] B[18] A[19] B[19] A[3] B[3] A[12] B[12] A[13] B[13] A[14] B[14] A[15] B[15] C[2] C[8] C[9] C[10] C[11] C[4] C[5] C[6] C[7] C[0] C[1] C[2] C[3] Slide credit: Krste Asanovic 69

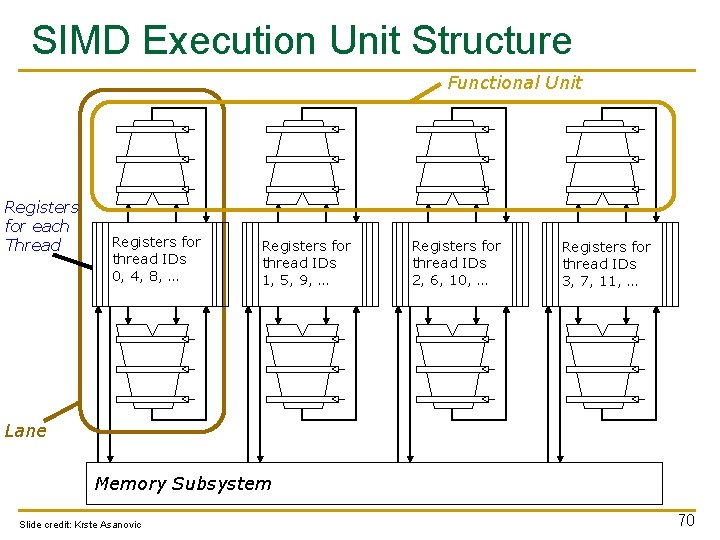

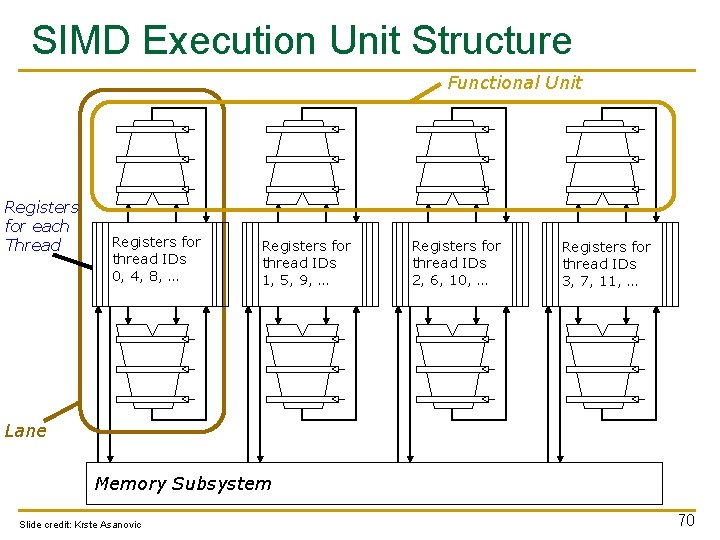

SIMD Execution Unit Structure Functional Unit Registers for each Thread Registers for thread IDs 0, 4, 8, … Registers for thread IDs 1, 5, 9, … Registers for thread IDs 2, 6, 10, … Registers for thread IDs 3, 7, 11, … Lane Memory Subsystem Slide credit: Krste Asanovic 70

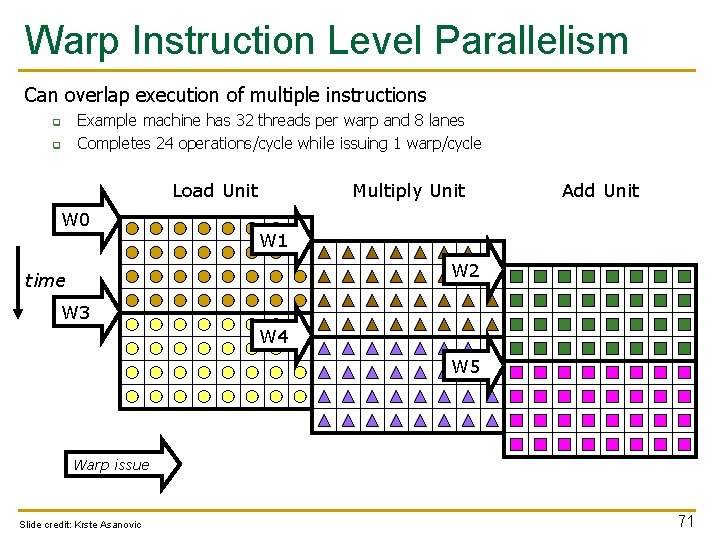

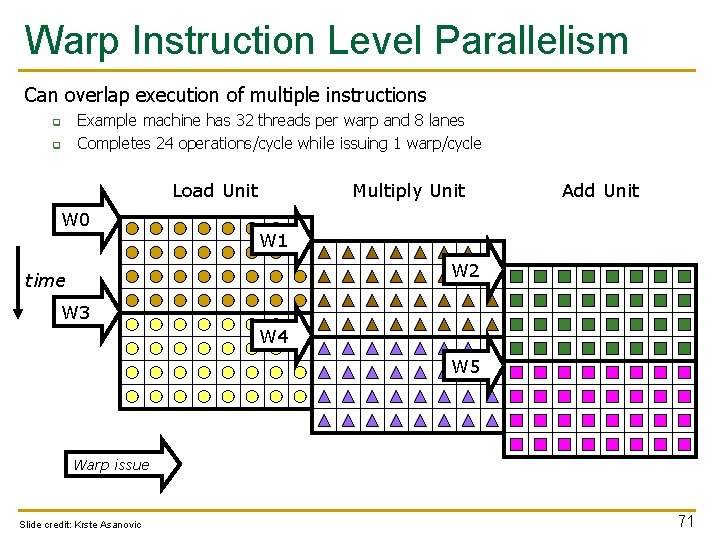

Warp Instruction Level Parallelism Can overlap execution of multiple instructions q q Example machine has 32 threads per warp and 8 lanes Completes 24 operations/cycle while issuing 1 warp/cycle Load Unit W 0 Multiply Unit Add Unit W 1 W 2 time W 3 W 4 W 5 Warp issue Slide credit: Krste Asanovic 71

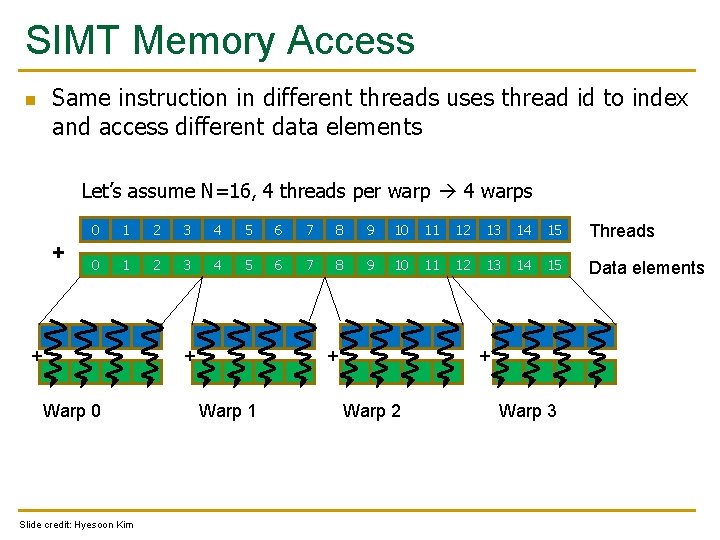

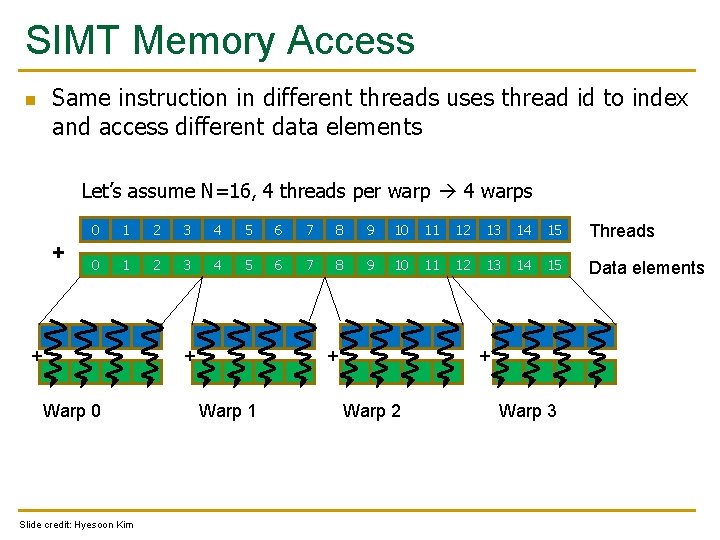

SIMT Memory Access Same instruction in different threads uses thread id to index and access different data elements n Let’s assume N=16, 4 threads per warp 4 warps + 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Threads 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Data elements + Warp 0 Slide credit: Hyesoon Kim + + Warp 1 + Warp 2 Warp 3

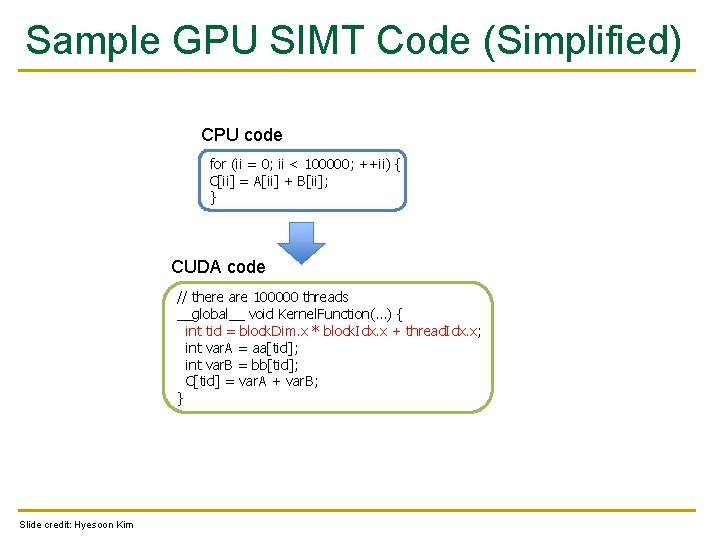

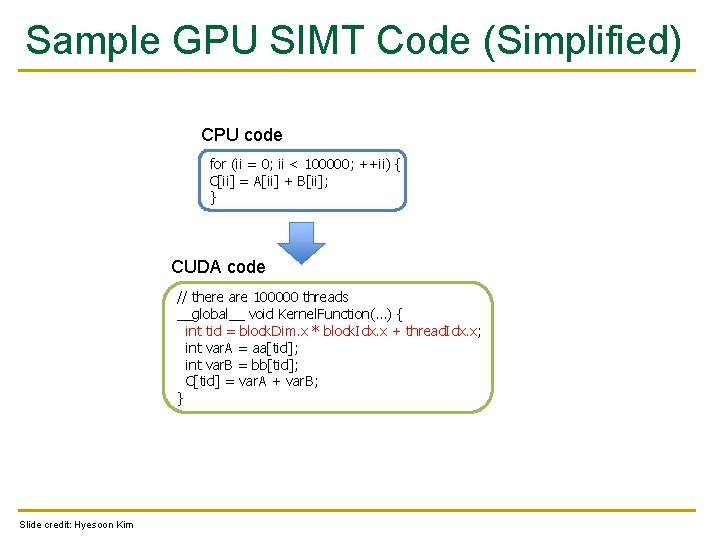

Sample GPU SIMT Code (Simplified) CPU code for (ii = 0; ii < 100000; ++ii) { C[ii] = A[ii] + B[ii]; } CUDA code // there are 100000 threads __global__ void Kernel. Function(…) { int tid = block. Dim. x * block. Idx. x + thread. Idx. x; int var. A = aa[tid]; int var. B = bb[tid]; C[tid] = var. A + var. B; } Slide credit: Hyesoon Kim

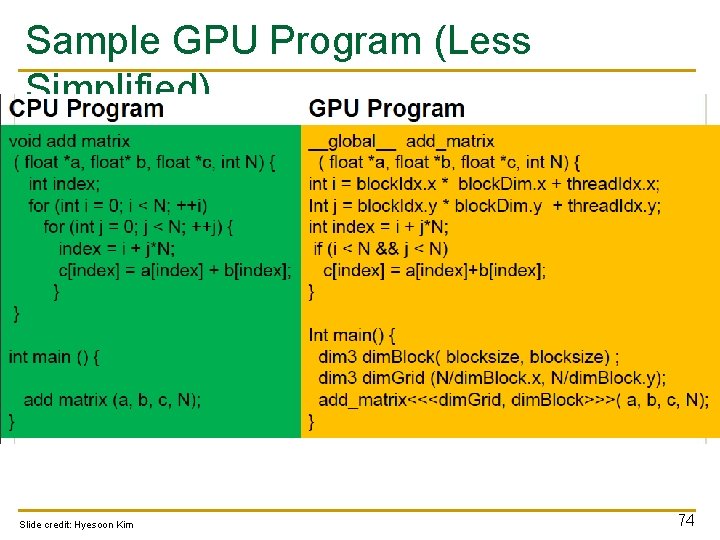

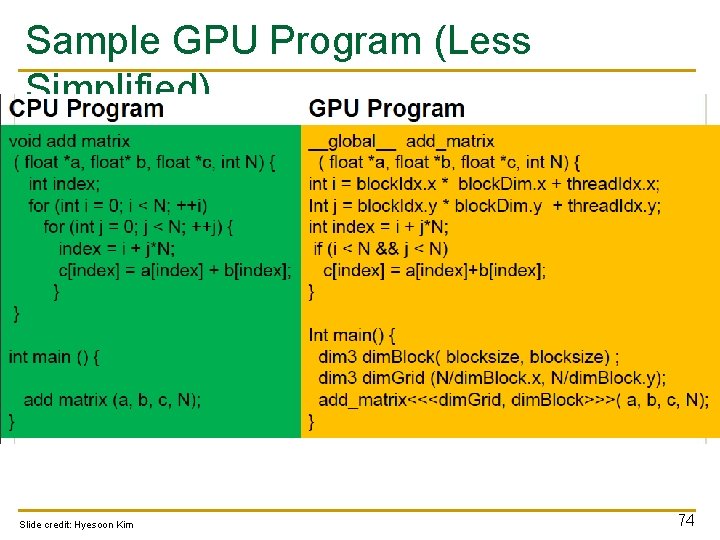

Sample GPU Program (Less Simplified) Slide credit: Hyesoon Kim 74

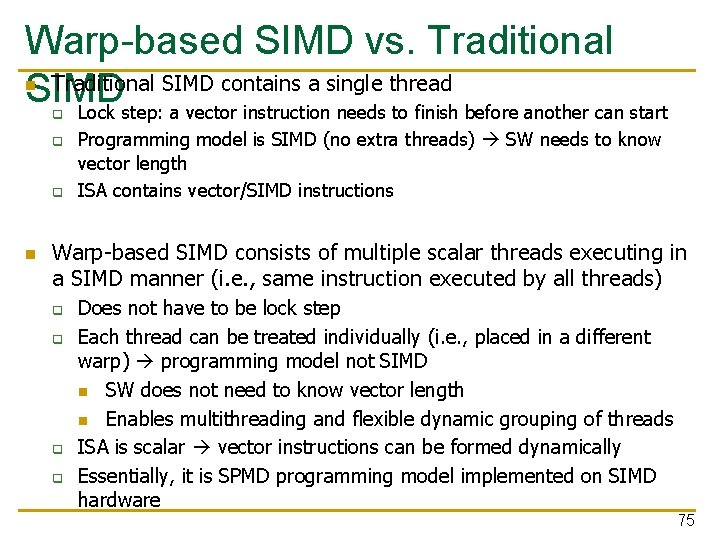

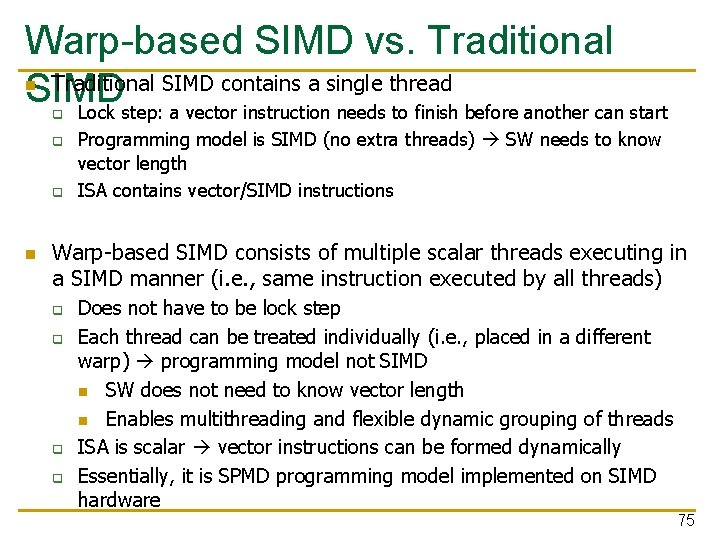

Warp-based SIMD vs. Traditional SIMD contains a single thread SIMD Lock step: a vector instruction needs to finish before another can start n q q q n Programming model is SIMD (no extra threads) SW needs to know vector length ISA contains vector/SIMD instructions Warp-based SIMD consists of multiple scalar threads executing in a SIMD manner (i. e. , same instruction executed by all threads) q q Does not have to be lock step Each thread can be treated individually (i. e. , placed in a different warp) programming model not SIMD n SW does not need to know vector length n Enables multithreading and flexible dynamic grouping of threads ISA is scalar vector instructions can be formed dynamically Essentially, it is SPMD programming model implemented on SIMD hardware 75

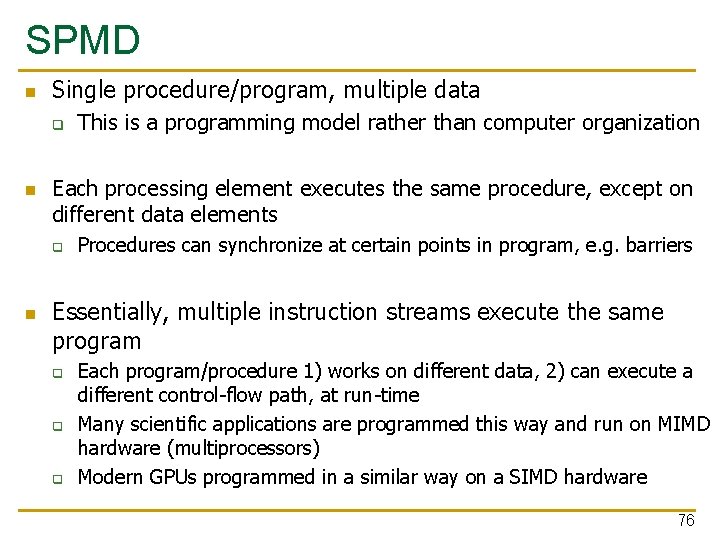

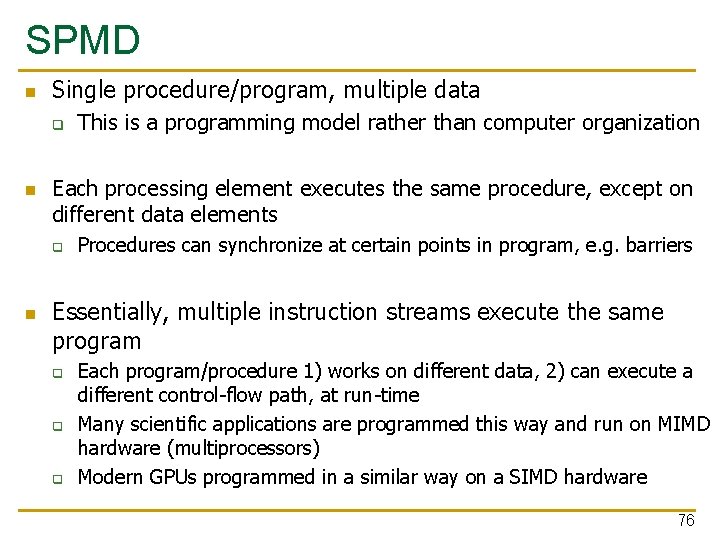

SPMD n Single procedure/program, multiple data q n Each processing element executes the same procedure, except on different data elements q n This is a programming model rather than computer organization Procedures can synchronize at certain points in program, e. g. barriers Essentially, multiple instruction streams execute the same program q q q Each program/procedure 1) works on different data, 2) can execute a different control-flow path, at run-time Many scientific applications are programmed this way and run on MIMD hardware (multiprocessors) Modern GPUs programmed in a similar way on a SIMD hardware 76

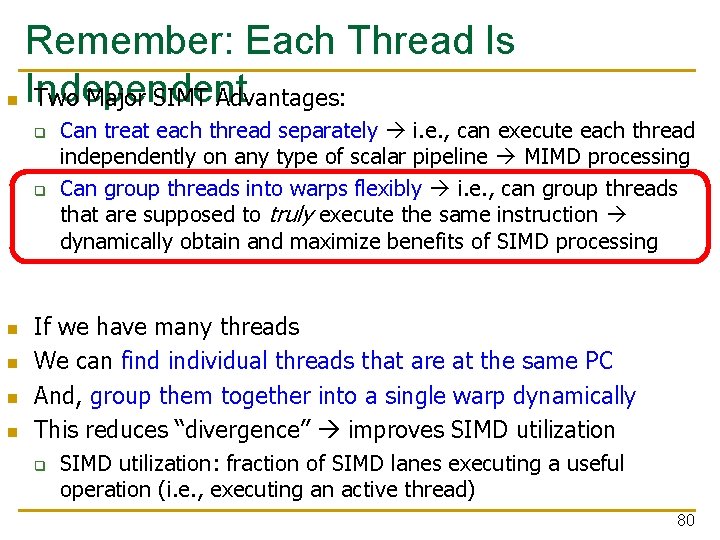

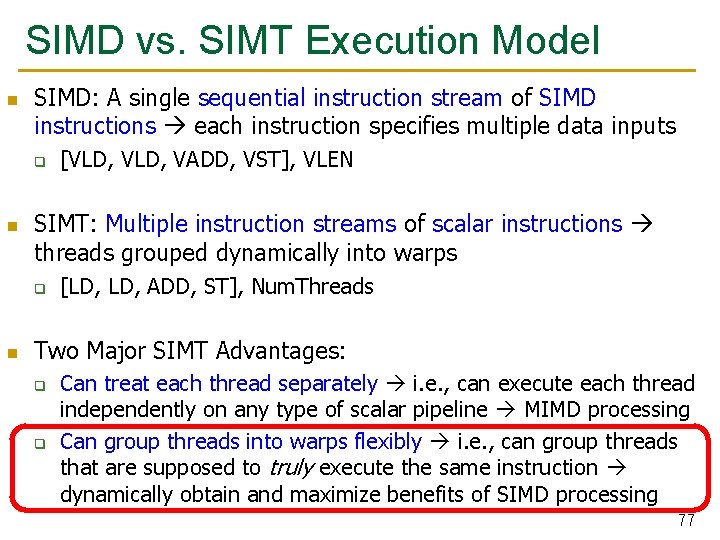

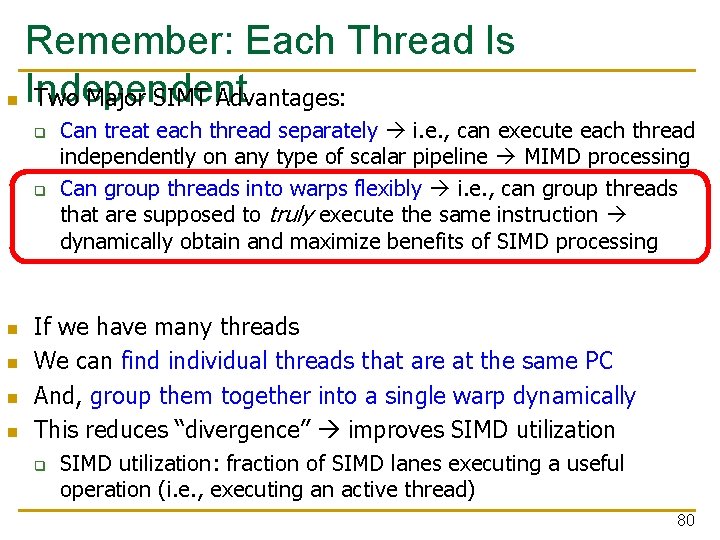

SIMD vs. SIMT Execution Model n SIMD: A single sequential instruction stream of SIMD instructions each instruction specifies multiple data inputs q n SIMT: Multiple instruction streams of scalar instructions threads grouped dynamically into warps q n [VLD, VADD, VST], VLEN [LD, ADD, ST], Num. Threads Two Major SIMT Advantages: q q Can treat each thread separately i. e. , can execute each thread independently on any type of scalar pipeline MIMD processing Can group threads into warps flexibly i. e. , can group threads that are supposed to truly execute the same instruction dynamically obtain and maximize benefits of SIMD processing 77

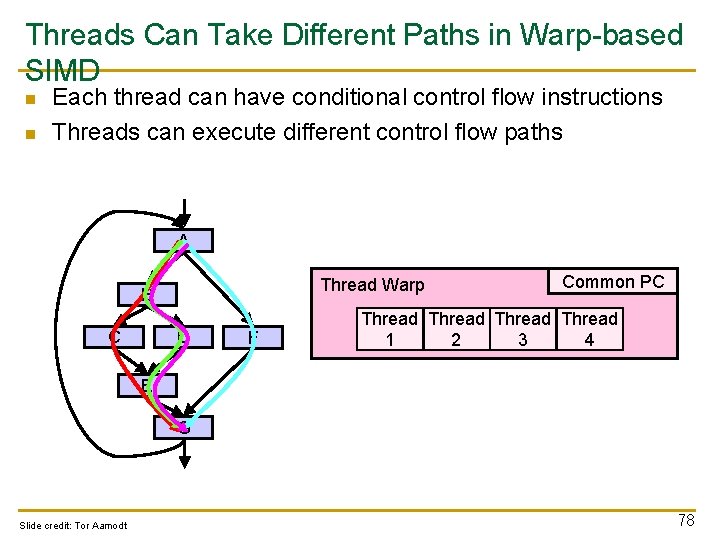

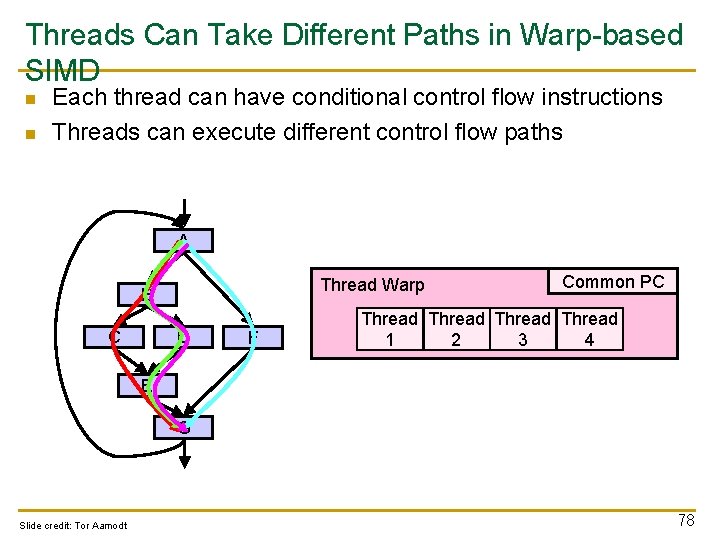

Threads Can Take Different Paths in Warp-based SIMD n n Each thread can have conditional control flow instructions Threads can execute different control flow paths A Thread Warp B C D F Common PC Thread 1 2 3 4 E G Slide credit: Tor Aamodt 78

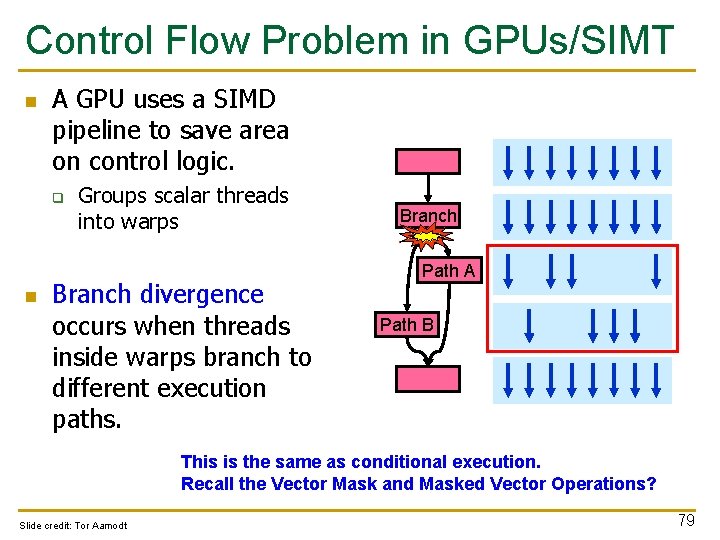

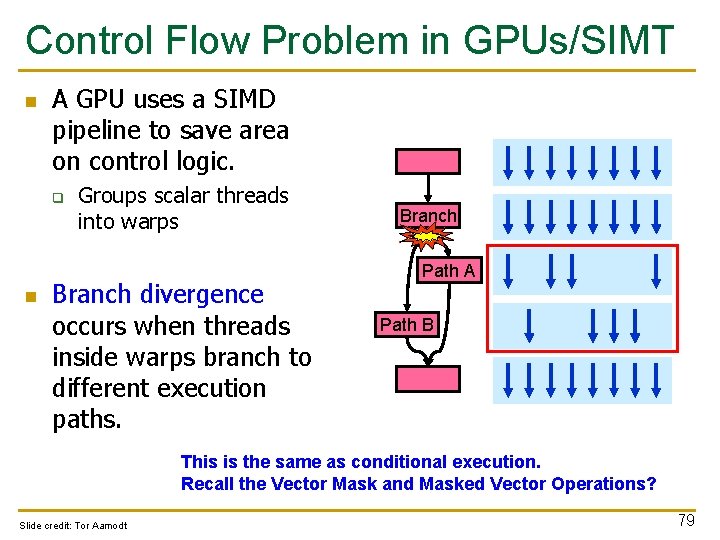

Control Flow Problem in GPUs/SIMT n A GPU uses a SIMD pipeline to save area on control logic. q n Groups scalar threads into warps Branch divergence occurs when threads inside warps branch to different execution paths. Branch Path A Path B This is the same as conditional execution. Recall the Vector Mask and Masked Vector Operations? Slide credit: Tor Aamodt 79

Remember: Each Thread Is n Independent Two Major SIMT Advantages: q q n n Can treat each thread separately i. e. , can execute each thread independently on any type of scalar pipeline MIMD processing Can group threads into warps flexibly i. e. , can group threads that are supposed to truly execute the same instruction dynamically obtain and maximize benefits of SIMD processing If we have many threads We can find individual threads that are at the same PC And, group them together into a single warp dynamically This reduces “divergence” improves SIMD utilization q SIMD utilization: fraction of SIMD lanes executing a useful operation (i. e. , executing an active thread) 80

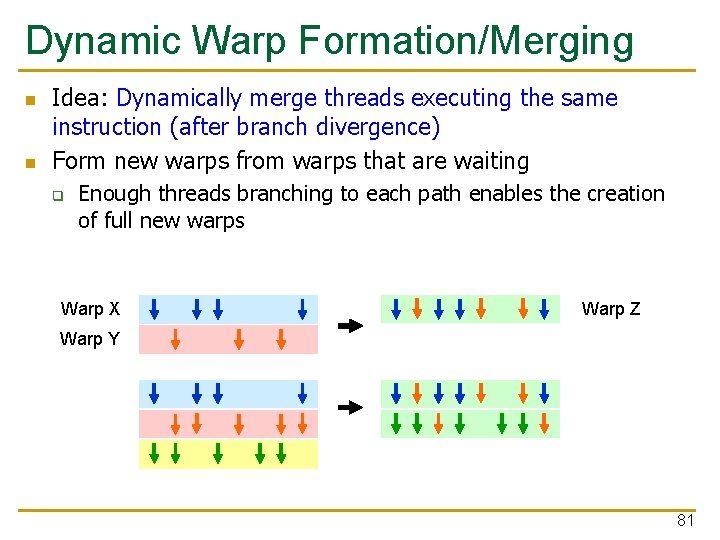

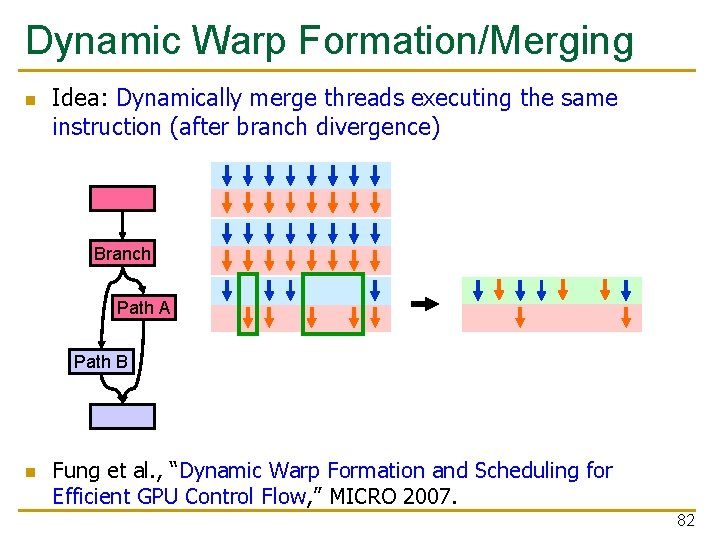

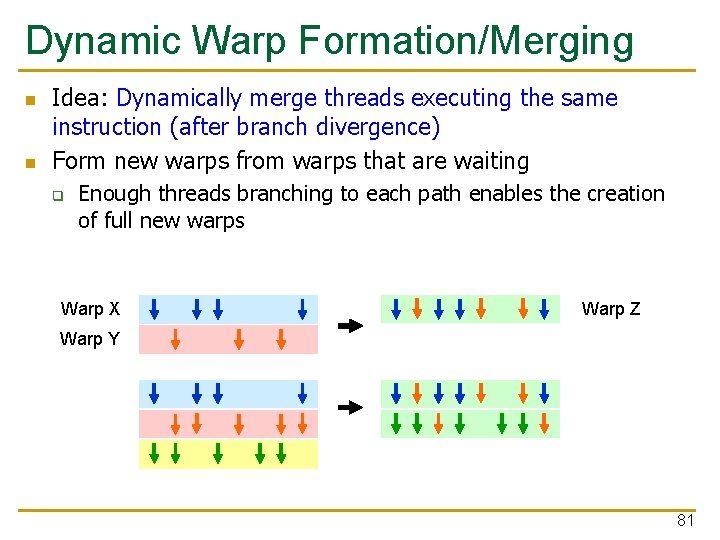

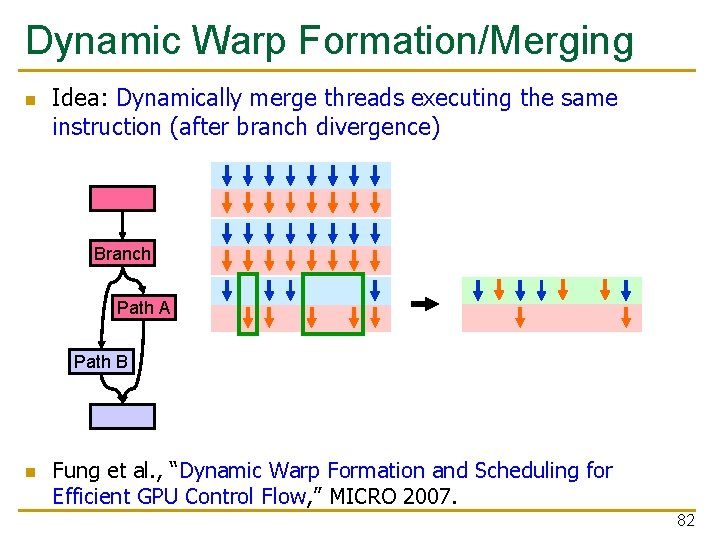

Dynamic Warp Formation/Merging n n Idea: Dynamically merge threads executing the same instruction (after branch divergence) Form new warps from warps that are waiting q Enough threads branching to each path enables the creation of full new warps Warp X Warp Z Warp Y 81

Dynamic Warp Formation/Merging n Idea: Dynamically merge threads executing the same instruction (after branch divergence) Branch Path A Path B n Fung et al. , “Dynamic Warp Formation and Scheduling for Efficient GPU Control Flow, ” MICRO 2007. 82

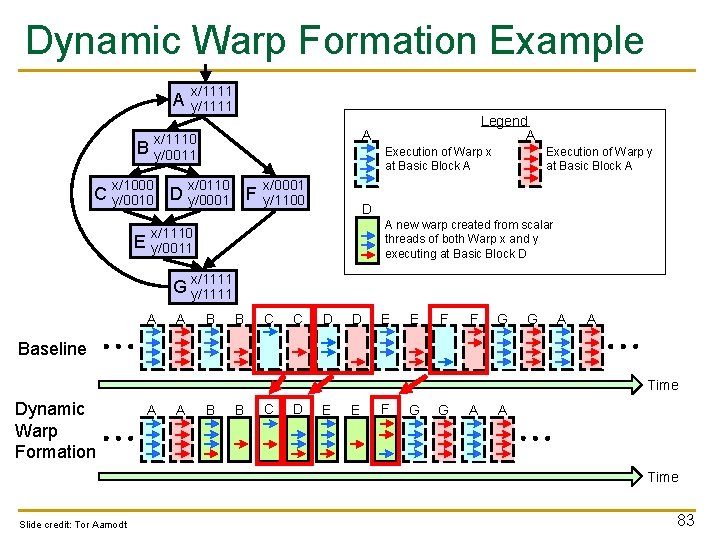

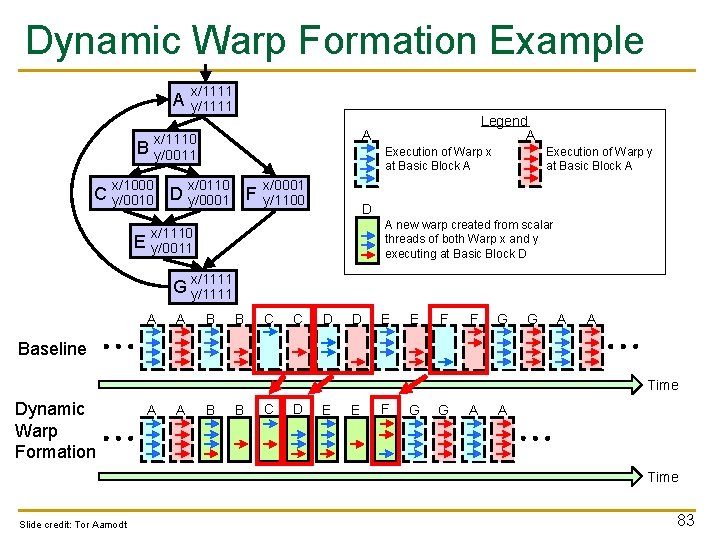

Dynamic Warp Formation Example A x/1111 y/1111 A x/1110 y/0011 B x/1000 Execution of Warp x at Basic Block A x/0110 C y/0010 D y/0001 F E Legend A x/0001 y/1100 Execution of Warp y at Basic Block A D A new warp created from scalar threads of both Warp x and y executing at Basic Block D x/1110 y/0011 x/1111 G y/1111 A A B B C C D D E E F F G G A A Baseline Time Dynamic Warp Formation A A B B C D E E F G G A A Time Slide credit: Tor Aamodt 83

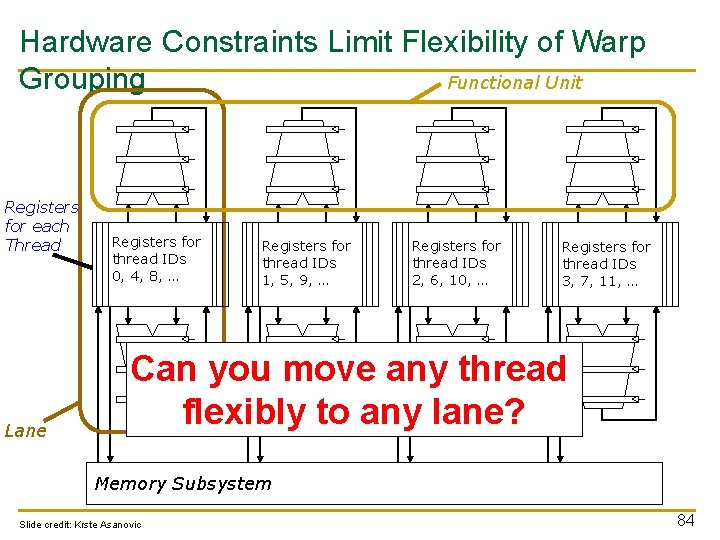

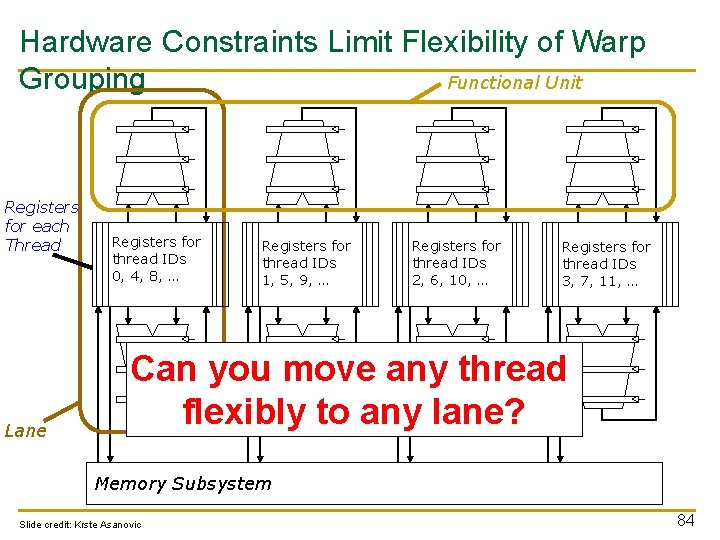

Hardware Constraints Limit Flexibility of Warp Functional Unit Grouping Registers for each Thread Lane Registers for thread IDs 0, 4, 8, … Registers for thread IDs 1, 5, 9, … Registers for thread IDs 2, 6, 10, … Registers for thread IDs 3, 7, 11, … Can you move any thread flexibly to any lane? Memory Subsystem Slide credit: Krste Asanovic 84

An Example GPU

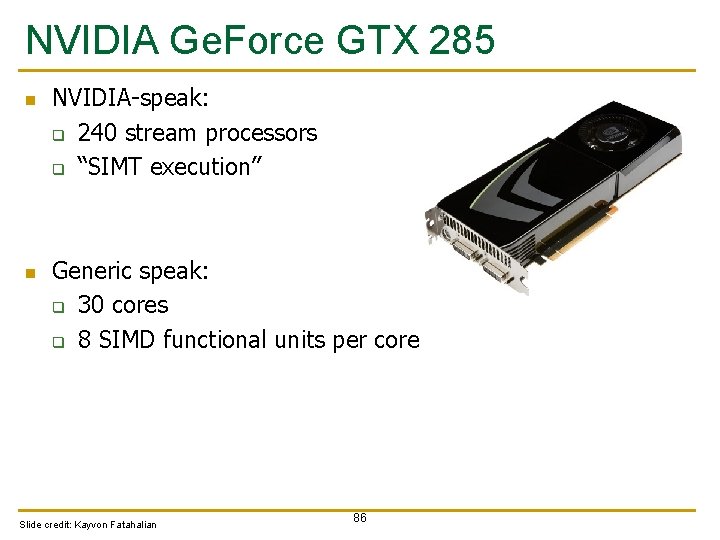

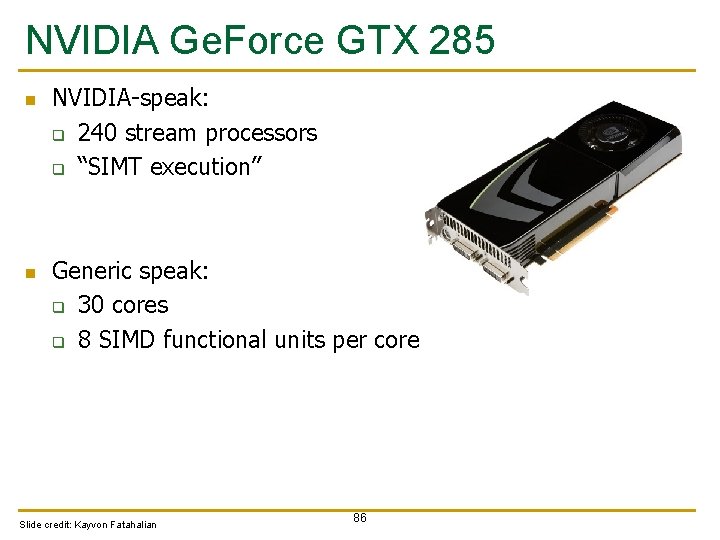

NVIDIA Ge. Force GTX 285 n n NVIDIA-speak: q 240 stream processors q “SIMT execution” Generic speak: q 30 cores q 8 SIMD functional units per core Slide credit: Kayvon Fatahalian 86

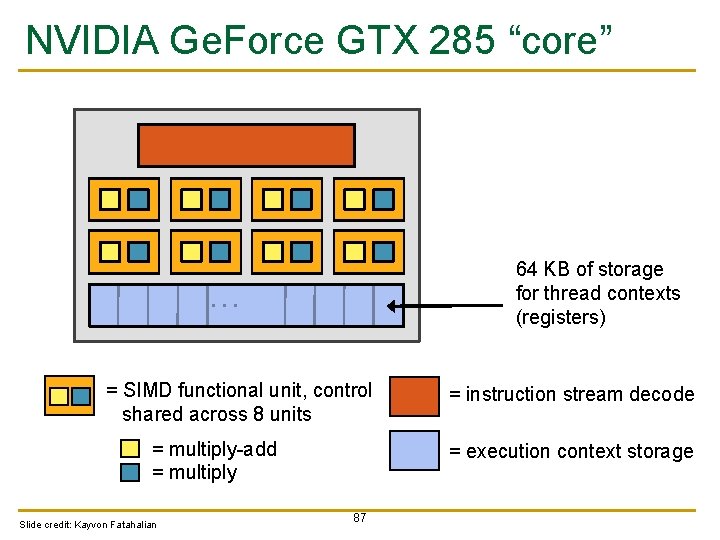

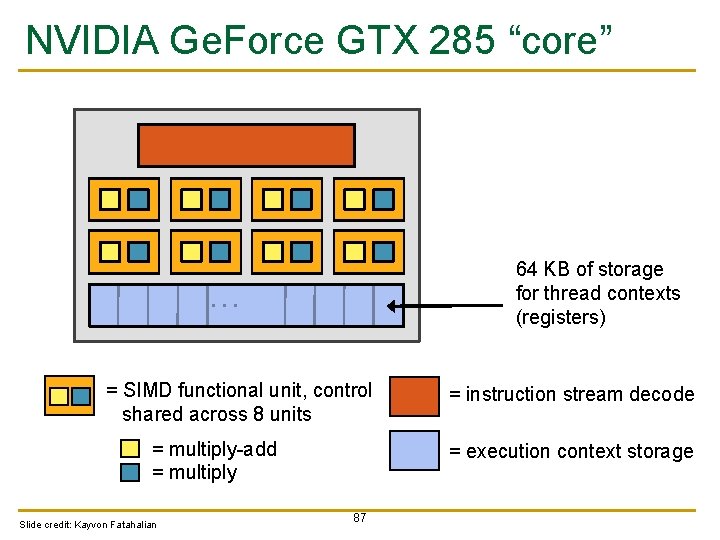

NVIDIA Ge. Force GTX 285 “core” 64 KB of storage for thread contexts (registers) … = SIMD functional unit, control shared across 8 units = multiply-add = multiply Slide credit: Kayvon Fatahalian = instruction stream decode = execution context storage 87

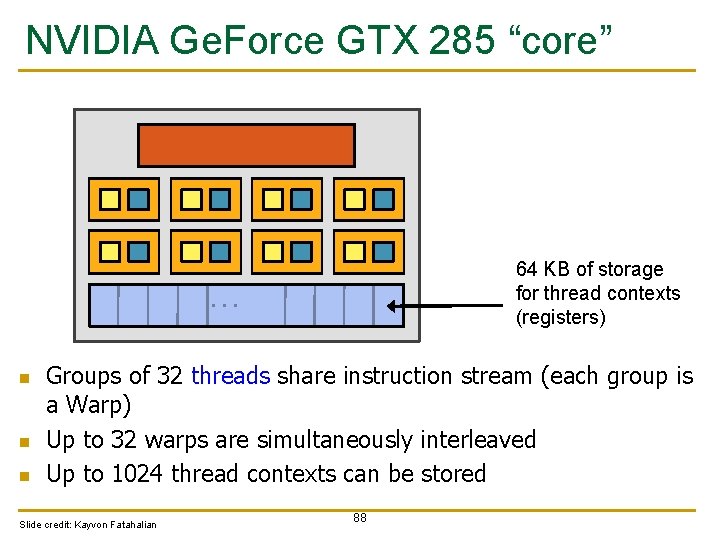

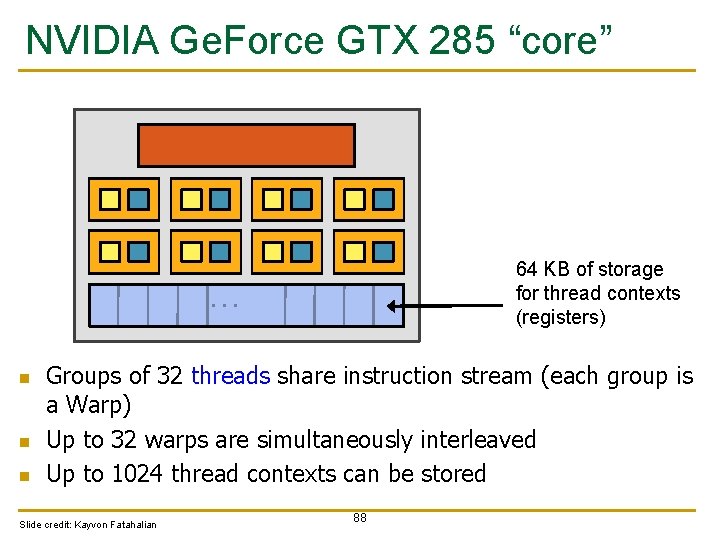

NVIDIA Ge. Force GTX 285 “core” 64 KB of storage for thread contexts (registers) … n n n Groups of 32 threads share instruction stream (each group is a Warp) Up to 32 warps are simultaneously interleaved Up to 1024 thread contexts can be stored Slide credit: Kayvon Fatahalian 88

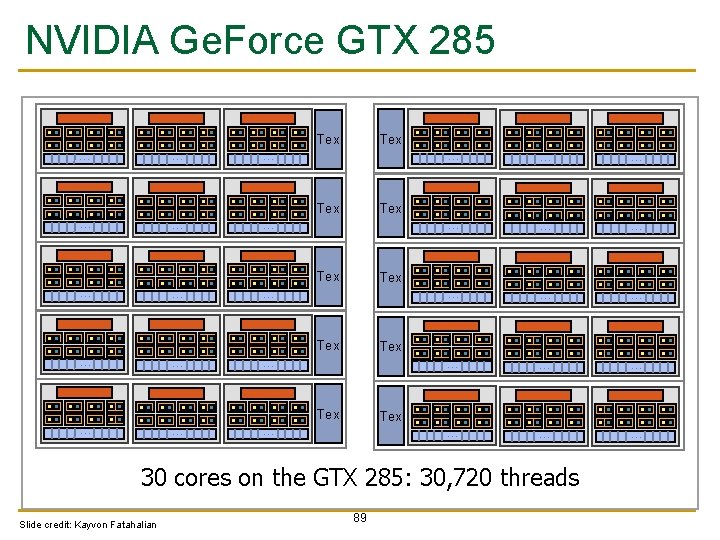

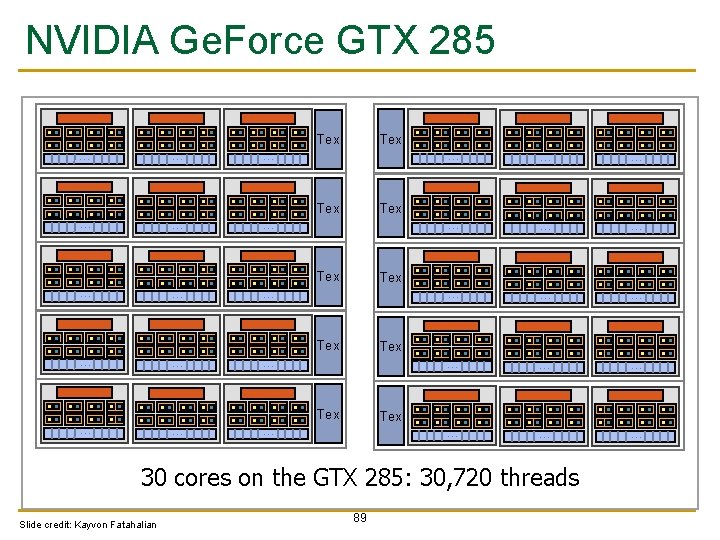

NVIDIA Ge. Force GTX 285 Tex … … … … … … … Tex … … Tex … 30 cores on the GTX 285: 30, 720 threads Slide credit: Kayvon Fatahalian 89