Verilog Digital System Design Z Navabi Mc GrawHill

Verilog Digital System Design Z. Navabi, Mc. Graw-Hill, 2005 Chapter 2 Register Transfer Level Design with Verilog Prepared by: Homa Alemzadeh January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 1

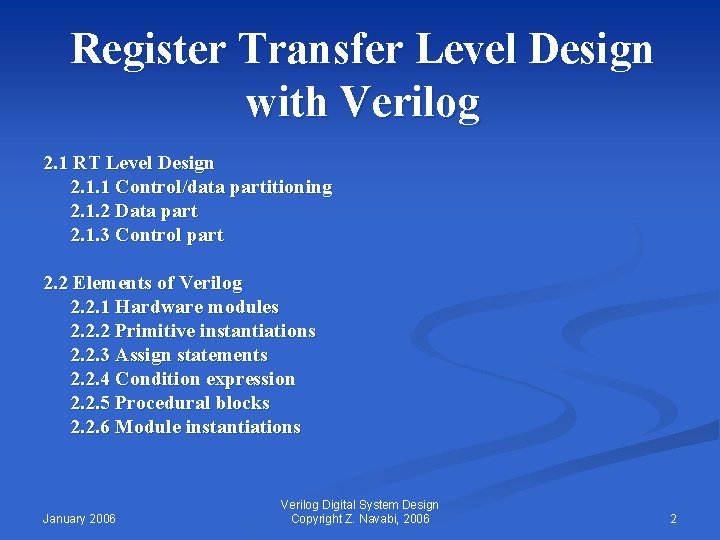

Register Transfer Level Design with Verilog 2. 1 RT Level Design 2. 1. 1 Control/data partitioning 2. 1. 2 Data part 2. 1. 3 Control part 2. 2 Elements of Verilog 2. 2. 1 Hardware modules 2. 2. 2 Primitive instantiations 2. 2. 3 Assign statements 2. 2. 4 Condition expression 2. 2. 5 Procedural blocks 2. 2. 6 Module instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 2

Register Transfer Level Design with Verilog 2. 3 Component Description in Verilog 2. 3. 1 Data components 2. 3. 2 Controllers 2. 4 Testbenches 2. 4. 1 A simple tester 2. 4. 2 Tasks and functions 2. 5 Summary January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 3

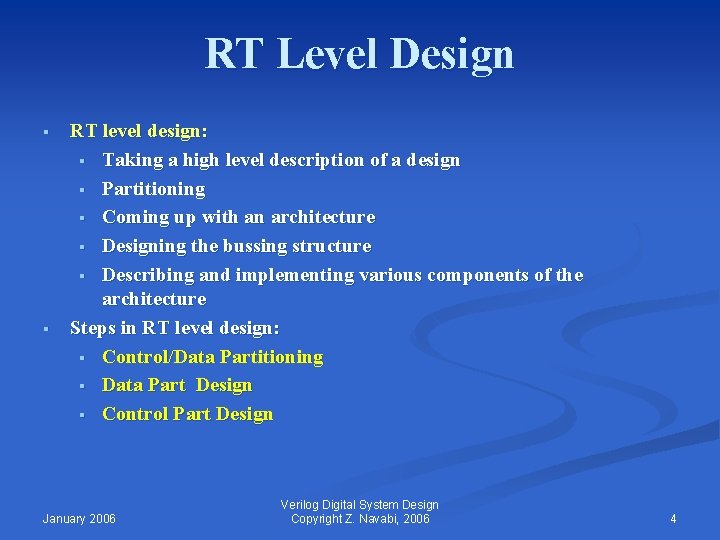

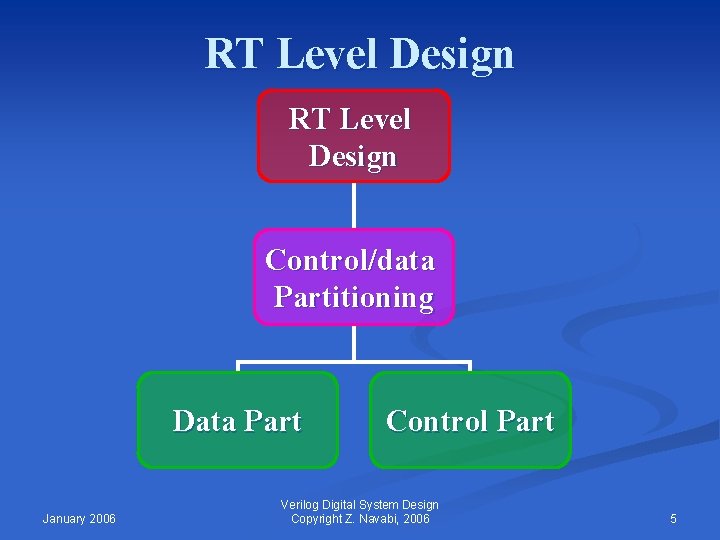

RT Level Design § § RT level design: § Taking a high level description of a design § Partitioning § Coming up with an architecture § Designing the bussing structure § Describing and implementing various components of the architecture Steps in RT level design: § Control/Data Partitioning § Data Part Design § Control Part Design January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 4

RT Level Design Control/data Partitioning Data Part January 2006 Control Part Verilog Digital System Design Copyright Z. Navabi, 2006 5

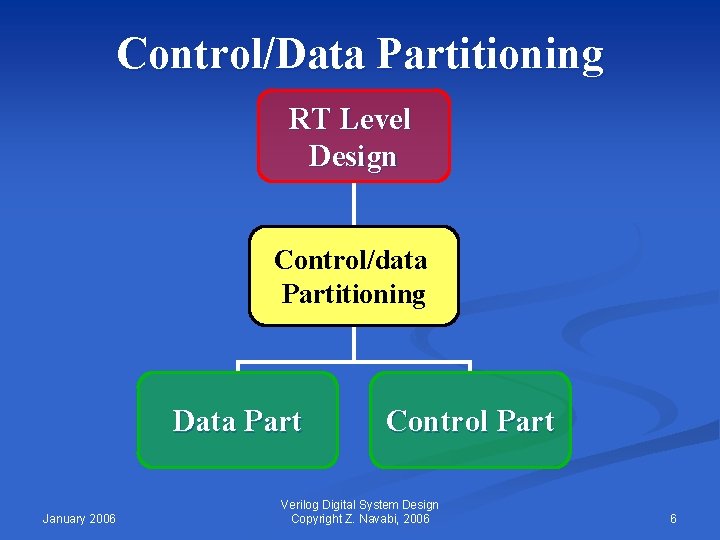

Control/Data Partitioning RT Level Design Control/data Partitioning Data Part January 2006 Control Part Verilog Digital System Design Copyright Z. Navabi, 2006 6

Control/Data Partitioning January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 7

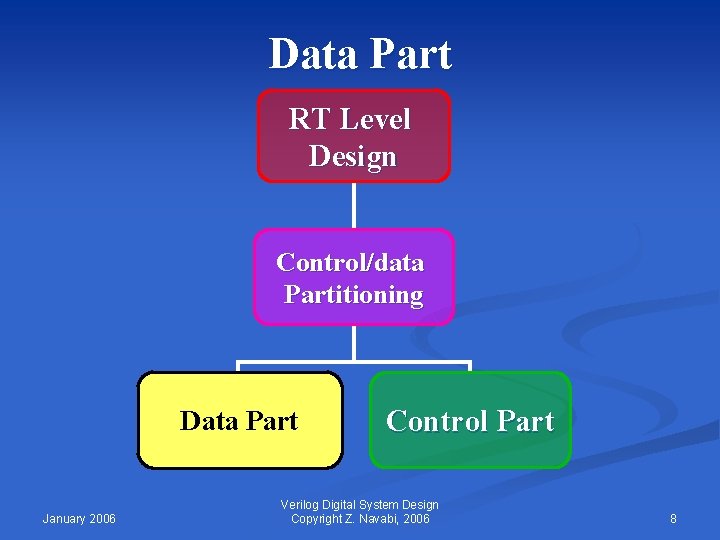

Data Part RT Level Design Control/data Partitioning Data Part Data January 2006 Control Part Verilog Digital System Design Copyright Z. Navabi, 2006 8

Data Part January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 9

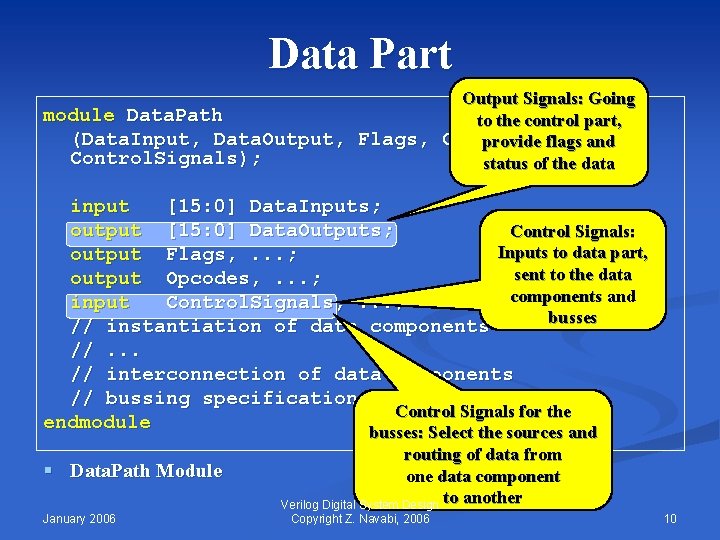

Data Part Output Signals: Going module Data. Path to the control part, (Data. Input, Data. Output, Flags, Opcodes, provide flags and Control. Signals); status of the data input [15: 0] Data. Inputs; output [15: 0] Data. Outputs; Control Signals: Inputs to data part, output Flags, . . . ; sent to the data output Opcodes, . . . ; components and input Control. Signals, . . . ; busses // instantiation of data components //. . . // interconnection of data components // bussing specification Control Signals for the endmodule busses: Select the sources and § Data. Path Module January 2006 busses: Select the sources and routing of data from one data component Verilog Digital System Design to another Copyright Z. Navabi, 2006 10

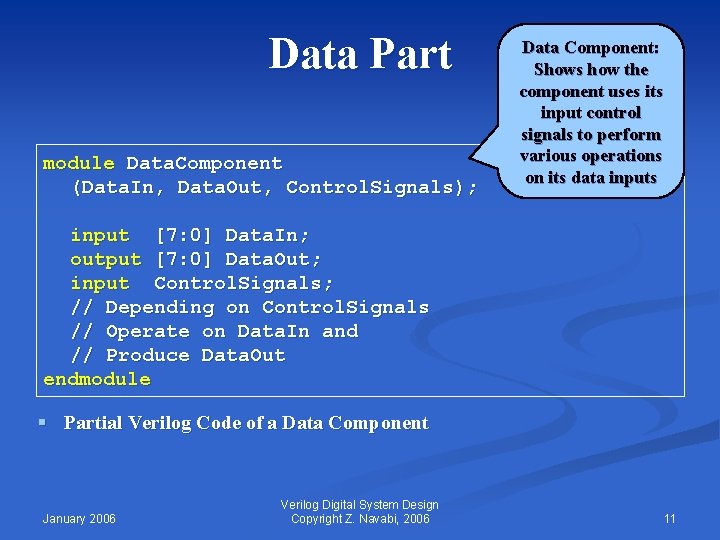

Data Part module Data. Component (Data. In, Data. Out, Control. Signals); Data Component: Shows how the component uses its input control signals to perform various operations on its data inputs input [7: 0] Data. In; output [7: 0] Data. Out; input Control. Signals; // Depending on Control. Signals // Operate on Data. In and // Produce Data. Out endmodule § Partial Verilog Code of a Data Component January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 11

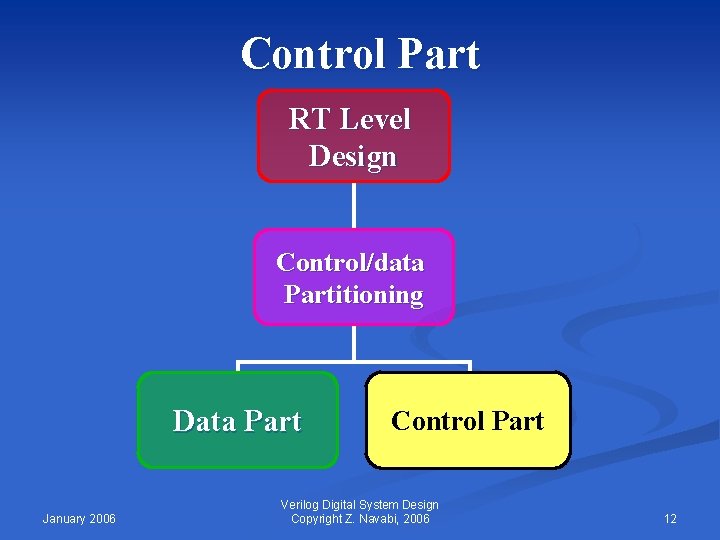

Control Part RT Level Design Control/data Partitioning Data Part January 2006 Control Part Verilog Digital System Design Copyright Z. Navabi, 2006 12

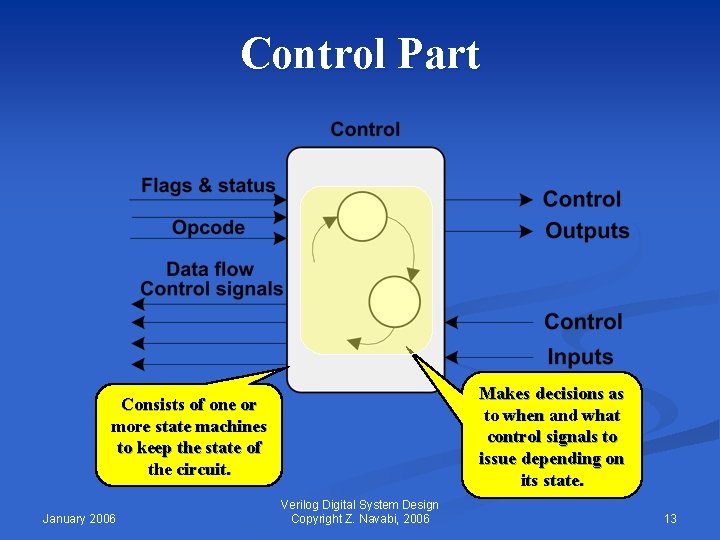

Control Part Makes decisions as to when and what control signals to issue depending on its state. Consists of one or more state machines to keep the state of the circuit. January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 13

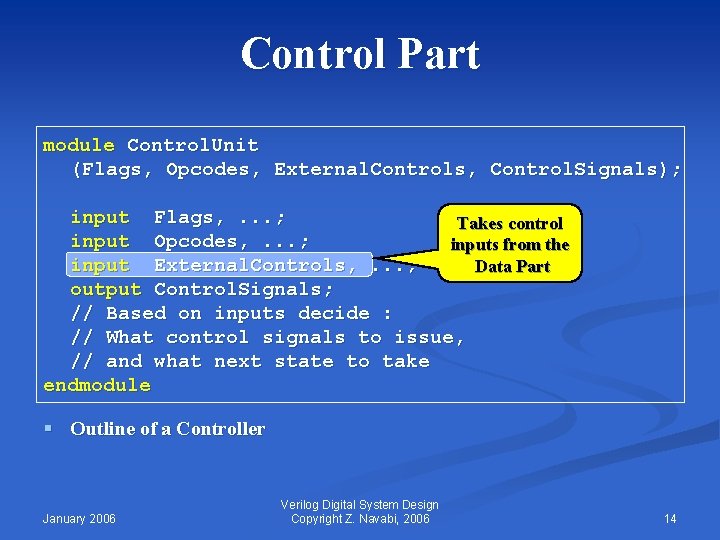

Control Part module Control. Unit (Flags, Opcodes, External. Controls, Control. Signals); input Flags, . . . ; Takes control input Opcodes, . . . ; inputs from the input External. Controls, . . . ; Data Part output Control. Signals; // Based on inputs decide : // What control signals to issue, // and what next state to take endmodule § Outline of a Controller January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 14

Elements of Verilog § We discuss basic constructs of Verilog language for describing a hardware module. January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 15

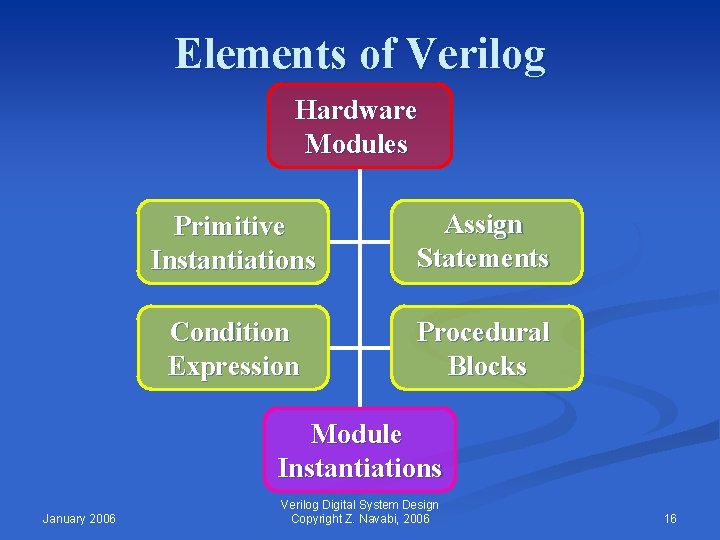

Elements of Verilog Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 16

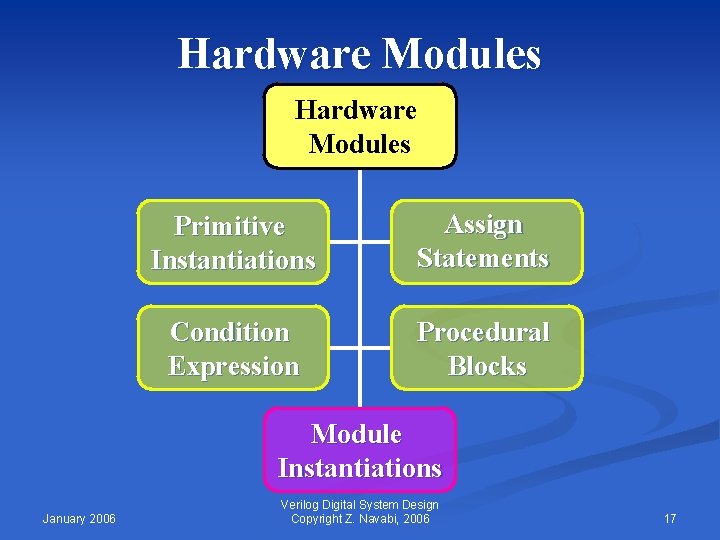

Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 17

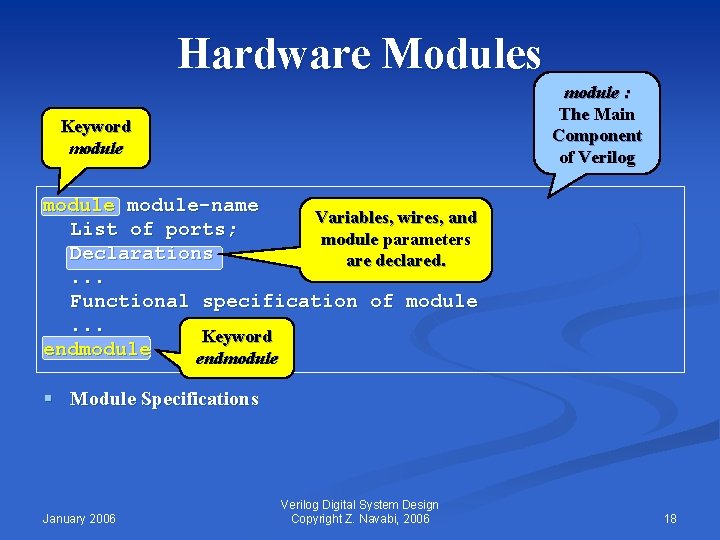

Hardware Modules module : The Main Component of Verilog Keyword module-name Variables, wires, and List of ports; module parameters Declarations are declared. . Functional specification of module. . . Keyword endmodule § Module Specifications January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 18

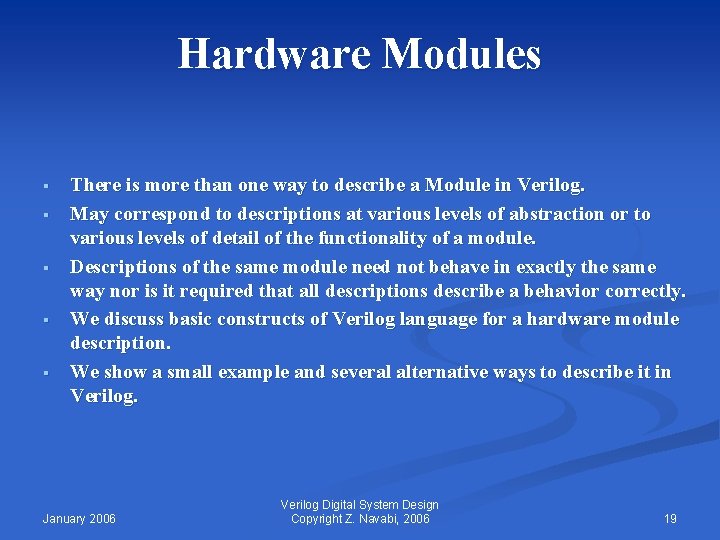

Hardware Modules § § § There is more than one way to describe a Module in Verilog. May correspond to descriptions at various levels of abstraction or to various levels of detail of the functionality of a module. Descriptions of the same module need not behave in exactly the same way nor is it required that all descriptions describe a behavior correctly. We discuss basic constructs of Verilog language for a hardware module description. We show a small example and several alternative ways to describe it in Verilog. January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 19

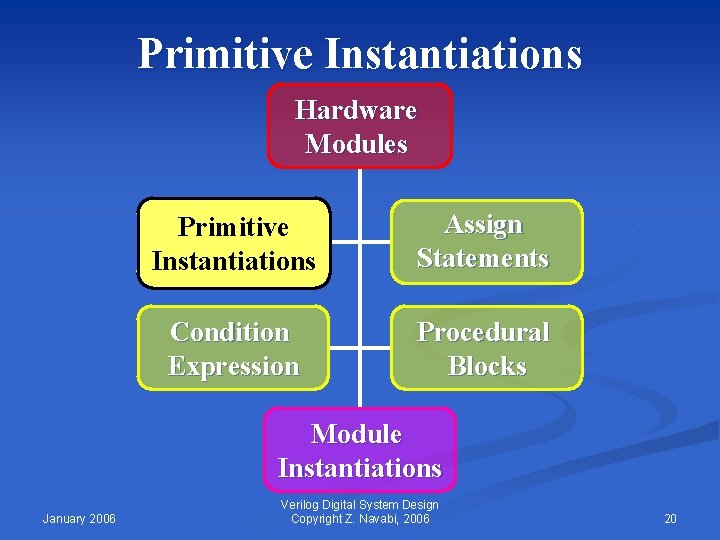

Primitive Instantiations Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 20

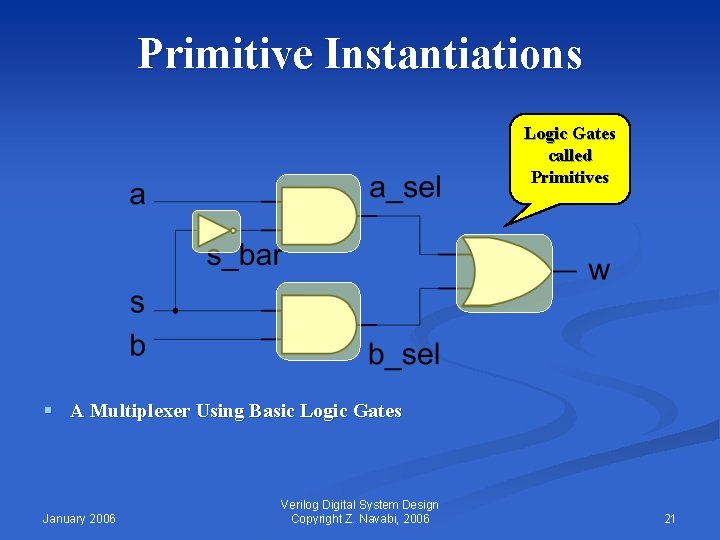

Primitive Instantiations Logic Gates called Primitives § A Multiplexer Using Basic Logic Gates January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 21

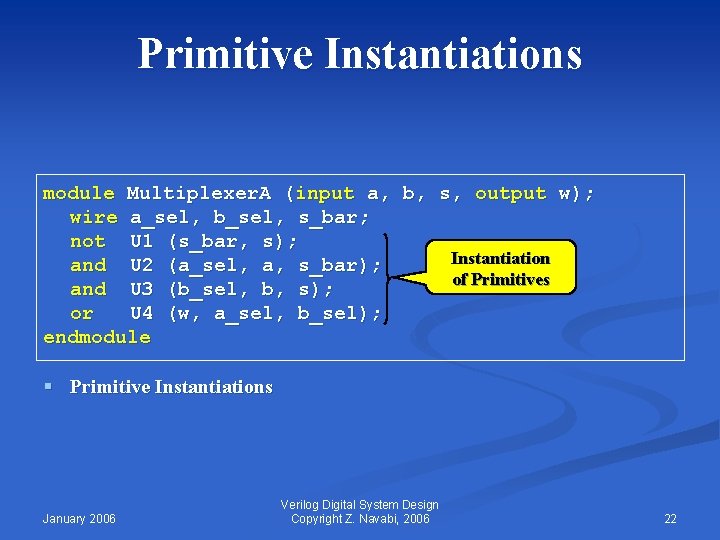

Primitive Instantiations module Multiplexer. A (input a, b, s, output w); wire a_sel, b_sel, s_bar; not U 1 (s_bar, s); Instantiation and U 2 (a_sel, a, s_bar); of Primitives and U 3 (b_sel, b, s); or U 4 (w, a_sel, b_sel); endmodule § Primitive Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 22

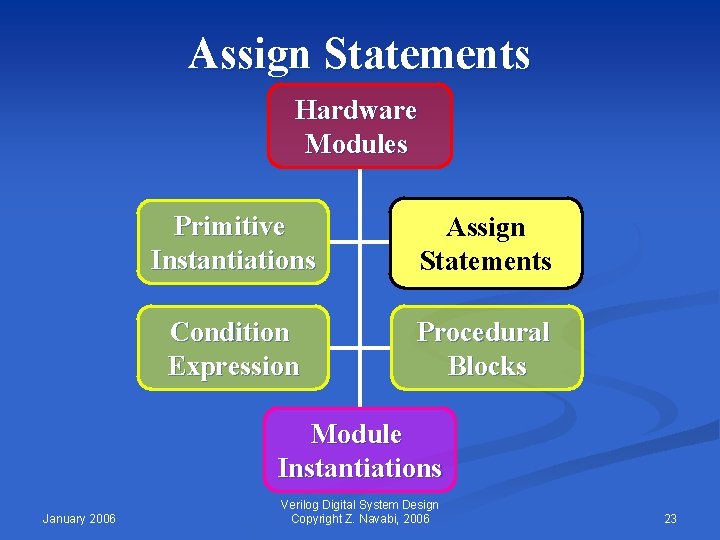

Assign Statements Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 23

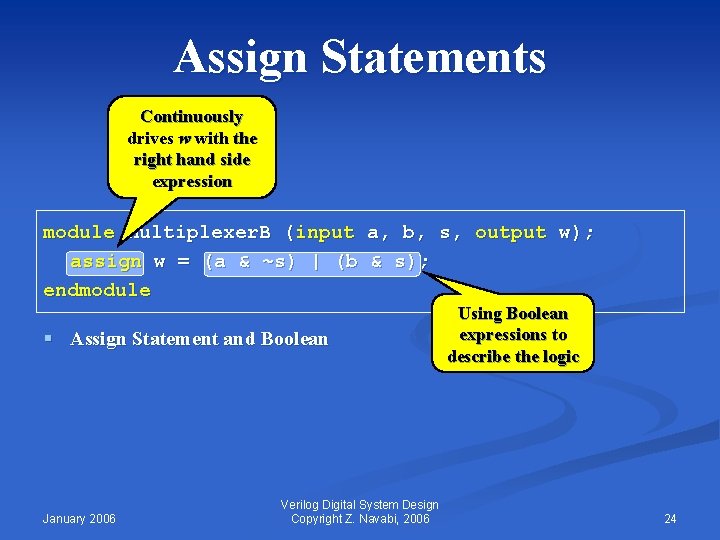

Assign Statements Continuously drives w with the right hand side expression module Multiplexer. B (input a, b, s, output w); assign w = (a & ~s) | (b & s); endmodule § Assign Statement and Boolean January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 Using Boolean expressions to describe the logic 24

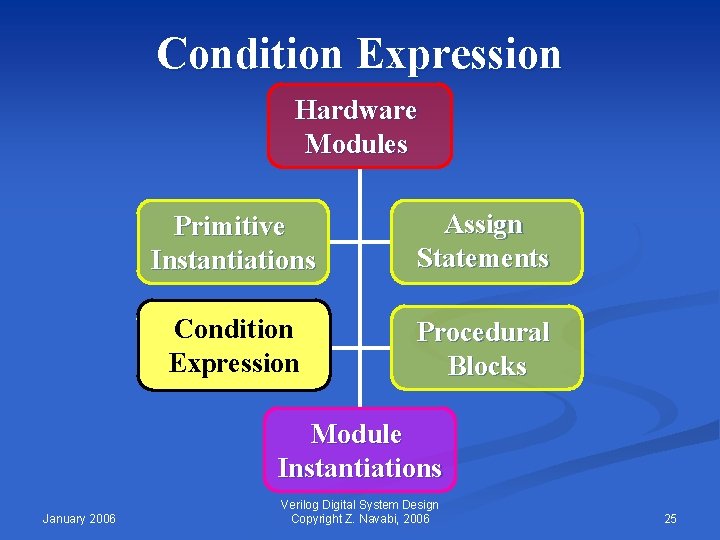

Condition Expression Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 25

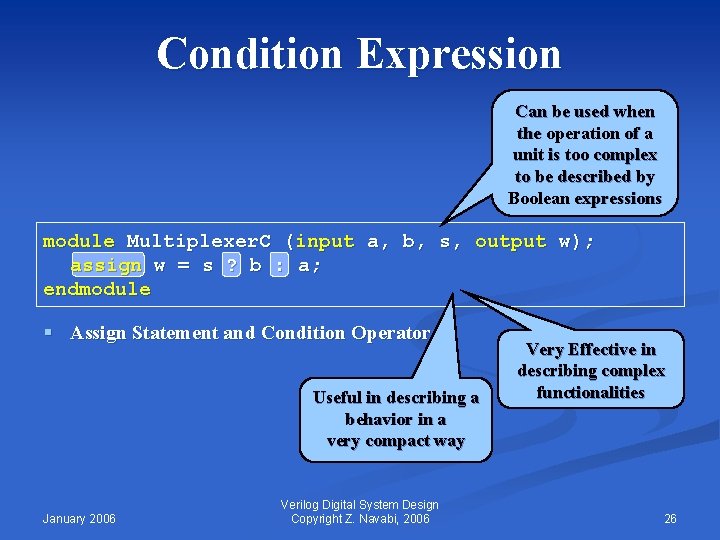

Condition Expression Can be used when the operation of a unit is too complex to be described by Boolean expressions module Multiplexer. C (input a, b, s, output w); assign w = s ? b : a; endmodule § Assign Statement and Condition Operator Useful in describing a behavior in a very compact way January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 Very Effective in describing complex functionalities 26

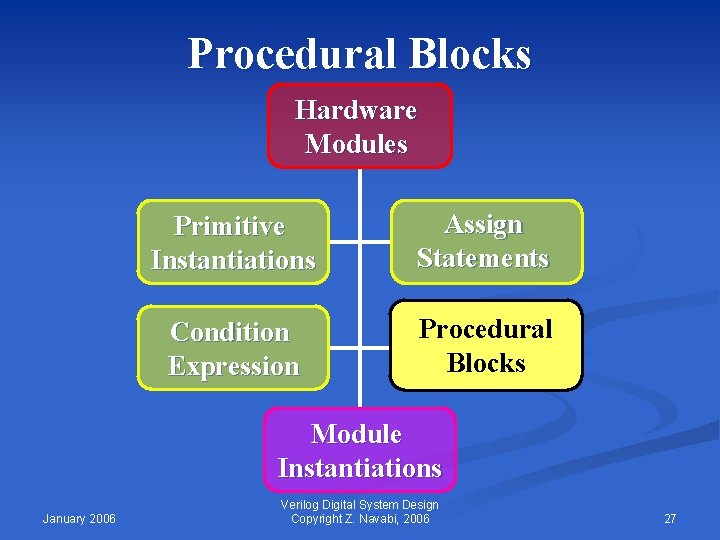

Procedural Blocks Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 27

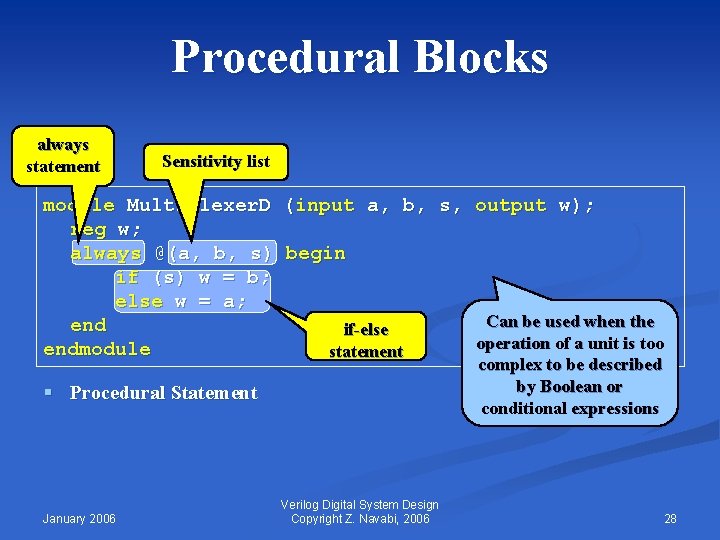

Procedural Blocks always statement Sensitivity list module Multiplexer. D (input a, b, s, output w); reg w; always @(a, b, s) begin if (s) w = b; else w = a; Can be used when the end if-else operation of a unit is too endmodule statement complex to be described by Boolean or conditional expressions § Procedural Statement January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 28

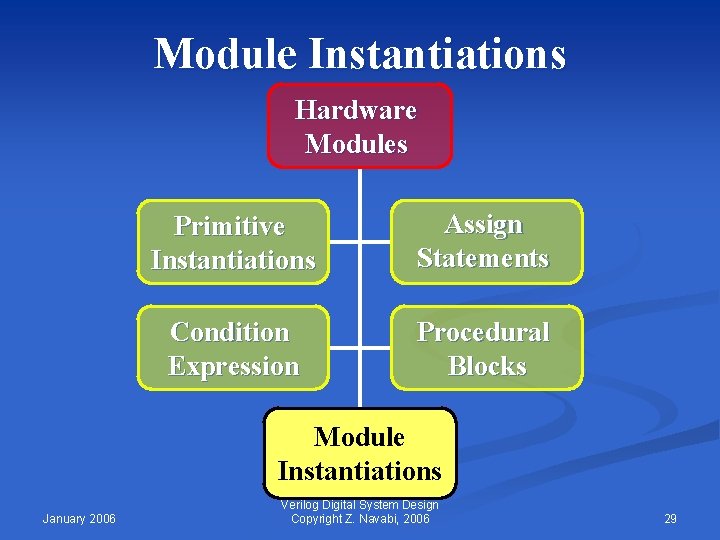

Module Instantiations Hardware Modules Primitive Instantiations Assign Statements Condition Expression Procedural Blocks Module Instantiations January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 29

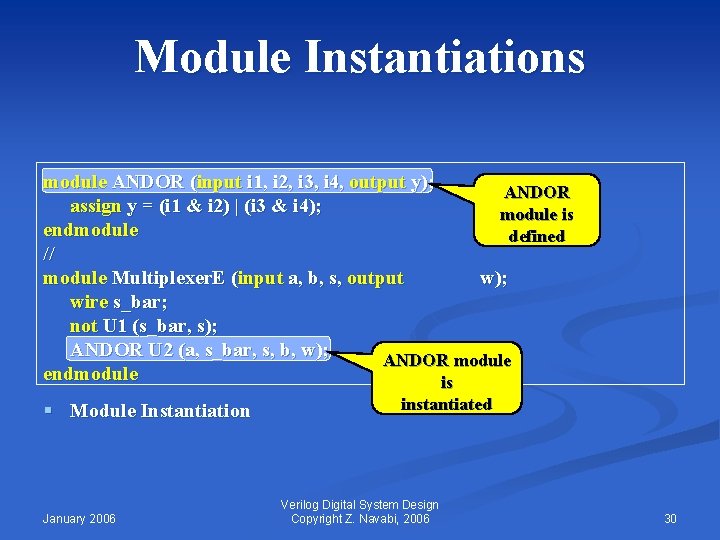

Module Instantiations module ANDOR (input i 1, i 2, i 3, i 4, output y); ANDOR assign y = (i 1 & i 2) | (i 3 & i 4); module is endmodule defined // module Multiplexer. E (input a, b, s, output w); wire s_bar; not U 1 (s_bar, s); ANDOR U 2 (a, s_bar, s, b, w); ANDOR module endmodule is § Module Instantiation January 2006 instantiated Verilog Digital System Design Copyright Z. Navabi, 2006 30

Module Instantiations § Multiplexer Using ANDOR January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 31

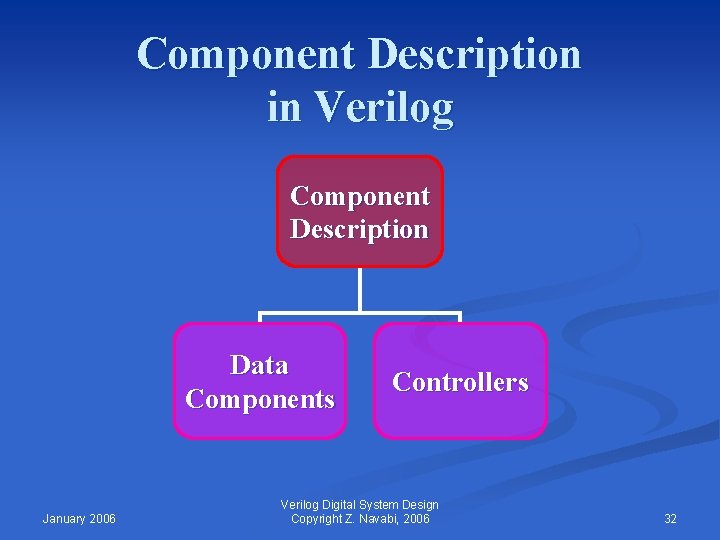

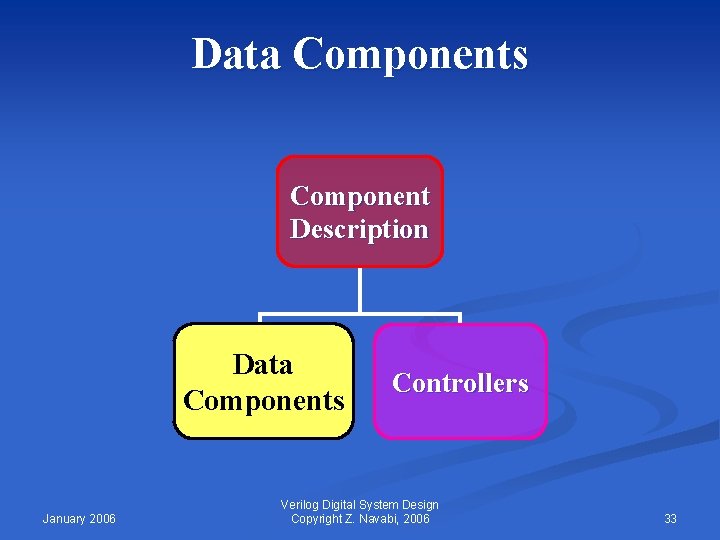

Component Description in Verilog Component Description Data Components January 2006 Controllers Verilog Digital System Design Copyright Z. Navabi, 2006 32

Data Components Component Description Data Components January 2006 Controllers Verilog Digital System Design Copyright Z. Navabi, 2006 33

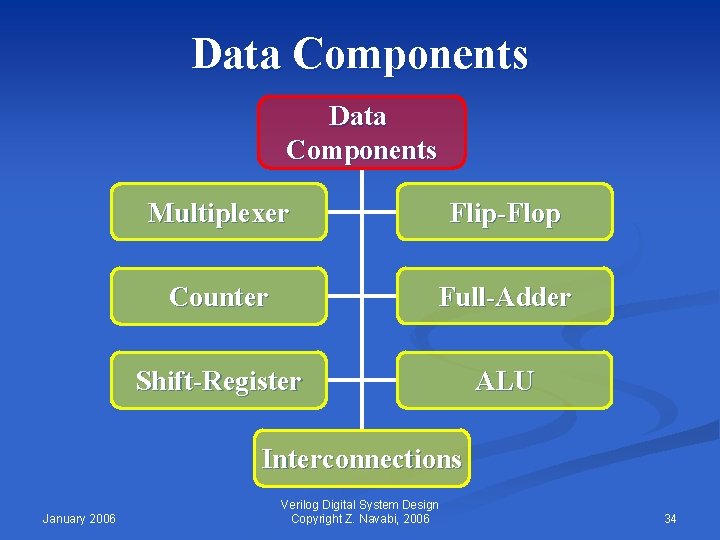

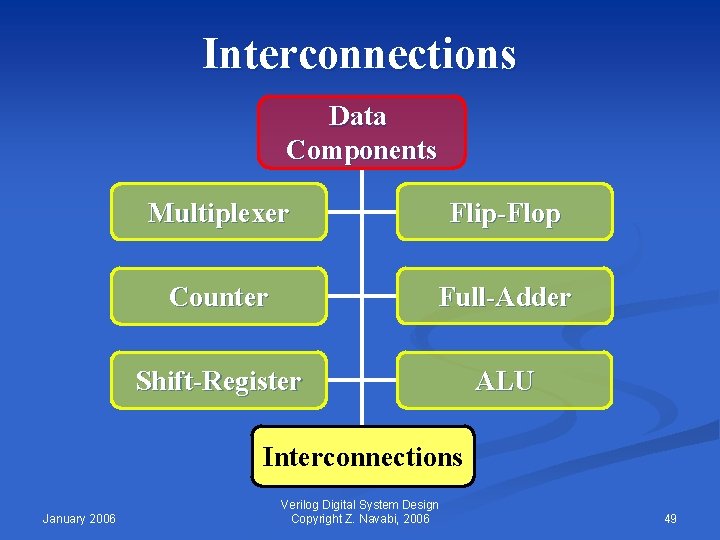

Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 34

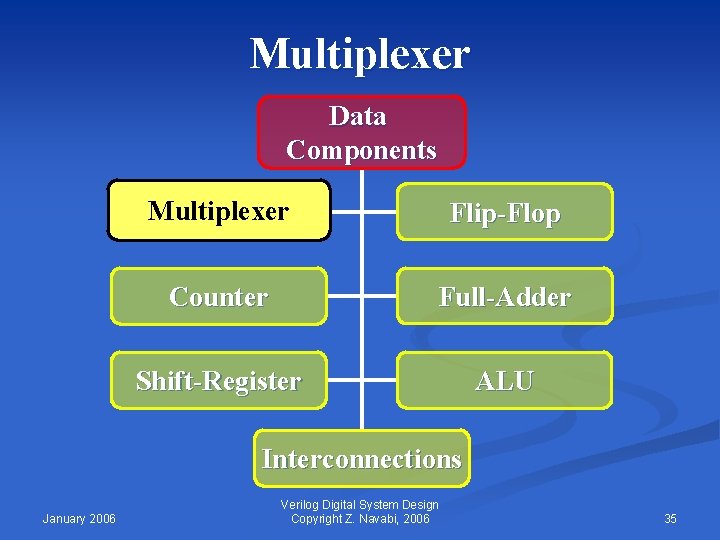

Multiplexer Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 35

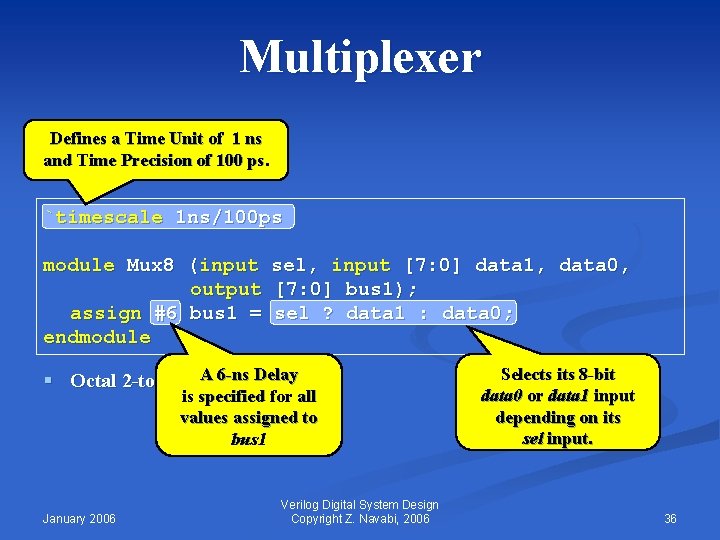

Multiplexer Defines a Time Unit of 1 ns and Time Precision of 100 ps. `timescale 1 ns/100 ps module Mux 8 (input sel, input [7: 0] data 1, data 0, output [7: 0] bus 1); assign #6 bus 1 = sel ? data 1 : data 0; endmodule A 6 -ns Delay § Octal 2 -to-1 MUX is specified for all values assigned to bus 1 January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 Selects its 8 -bit data 0 or data 1 input depending on its sel input. 36

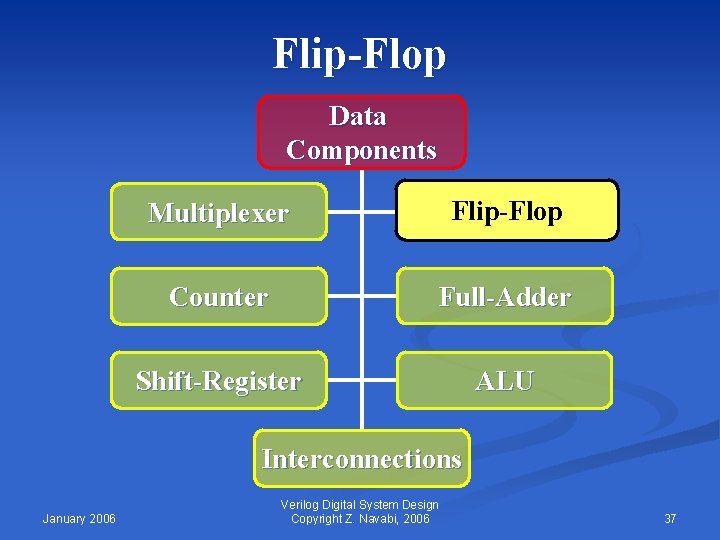

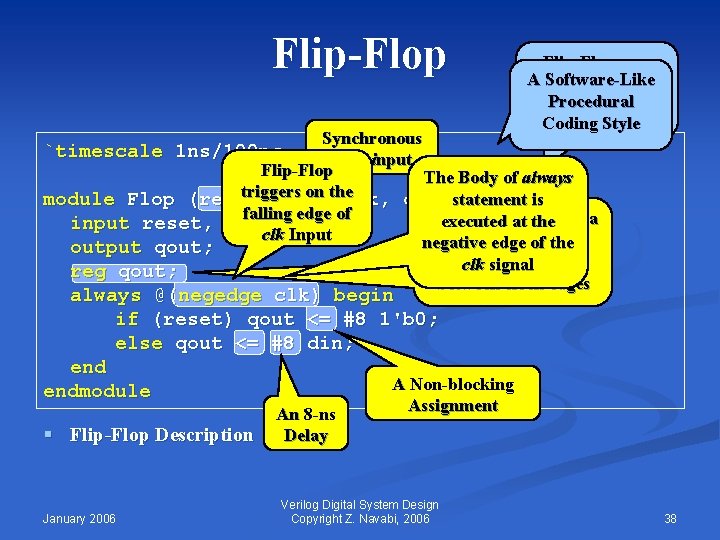

Flip-Flop Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 37

Flip-Flops are Aused Software-Like in data part for. Procedural flags and data Coding Style storage Synchronous `timescale 1 ns/100 ps reset input Flip-Flop The Body of always triggers on the module Flop (reset, din, clk, qout); statement is falling edge of Aexecuted Signal declared at the as a input reset, din, clk; clk Input reg to be capable negative edge of theof output qout; holding its values clk signal reg qout; between clock edges always @(negedge clk) begin if (reset) qout <= #8 1'b 0; else qout <= #8 din; end A Non-blocking endmodule § Flip-Flop Description January 2006 An 8 -ns Delay Assignment Verilog Digital System Design Copyright Z. Navabi, 2006 38

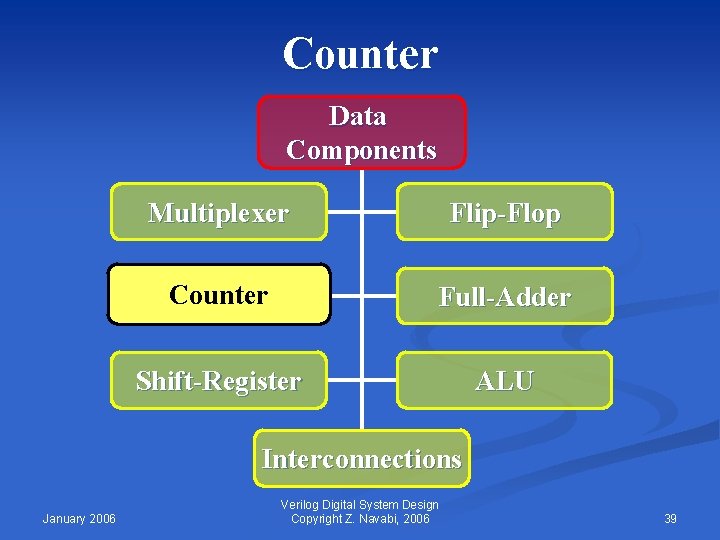

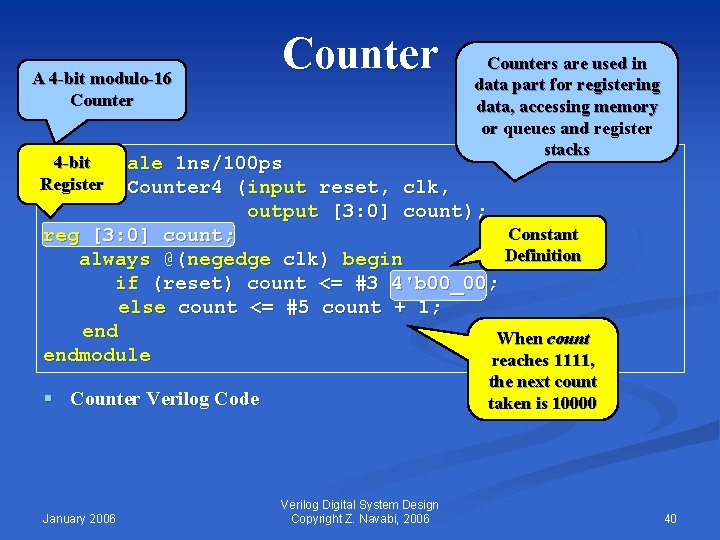

Counter Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 39

A 4 -bit modulo-16 Counters are used in data part for registering data, accessing memory or queues and register stacks 4 -bit `timescale 1 ns/100 ps Register module Counter 4 (input reset, clk, output [3: 0] count); Constant reg [3: 0] count; Definition always @(negedge clk) begin if (reset) count <= #3 4'b 00_00; else count <= #5 count + 1; end When count endmodule reaches 1111, the next count taken is 10000 § Counter Verilog Code January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 40

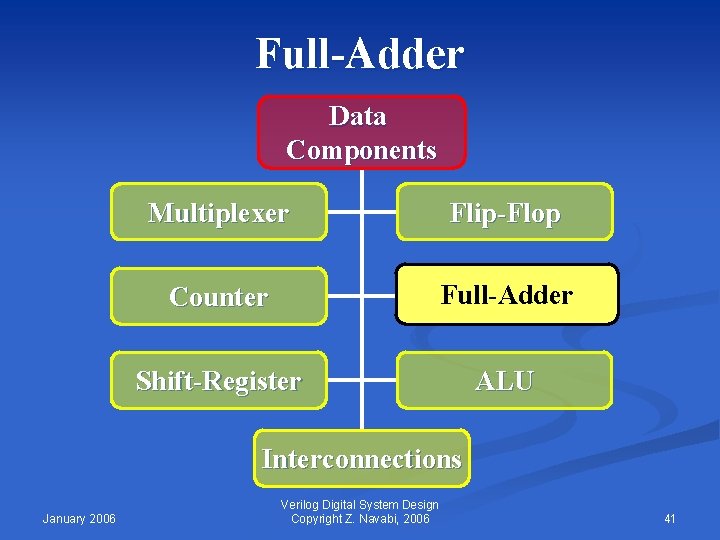

Full-Adder Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 41

Full-Adders are used in data part for building Carry-Chain adders A combinational circuit All Changes Occur after 5 ns `timescale 1 ns/100 ps module fulladder (input a, b, cin, output sum, cout); assign #5 sum = a ^ b ^ cin; assign #3 cout = (a & b)|(a & cin)|(b & cin); endmodule All Changes Occur after 3 ns § One Full-Adder delay for Verilog Code every output: t. PLH and t. PHL January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 42

Shift-Register Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 43

![Shift-Register 2 Mode inputs m[1: 0] form a `timescale 2 -bit number 1 ns/100 Shift-Register 2 Mode inputs m[1: 0] form a `timescale 2 -bit number 1 ns/100](http://slidetodoc.com/presentation_image/117d9335e101f831fd098da68bb118a6/image-44.jpg)

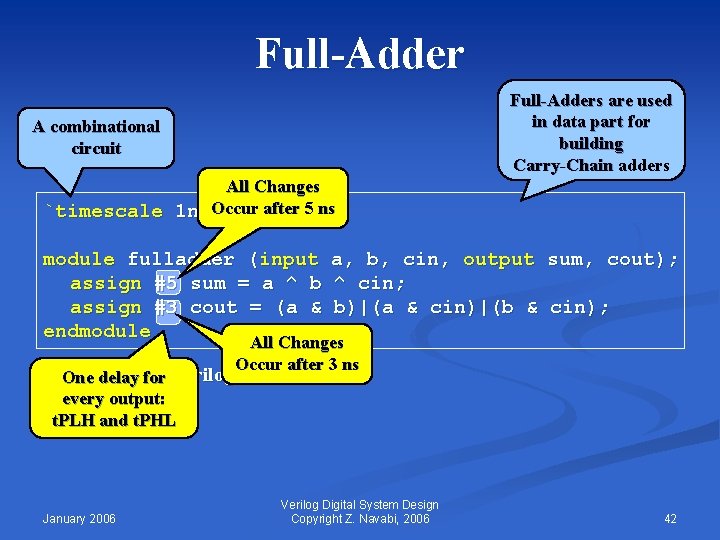

Shift-Register 2 Mode inputs m[1: 0] form a `timescale 2 -bit number 1 ns/100 ps An 8 -bit Universal Shift Register module Shift. Register 8 (input sl, sr, clk, input [7: 0] Par. In, Case Statement input [1: 0] m, output [7: 0] Par. Out); With 4 reg case-alternatives and default Value always @(negedge clk) begin case (m) m=0 : Does Nothing 0: Par. Out <= Par. Out; 1: Par. Out <= {sl, Par. Out [7: 1]}; 2: Par. Out <= {Par. Out [6: 0], sr}; m=1, 2: Shifts Right 3: Par. Out <= Par. In; and Left default: Par. Out <= 8'b. X; endcase m=3 : Loads its Parallel end input into the register endmodule January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 44

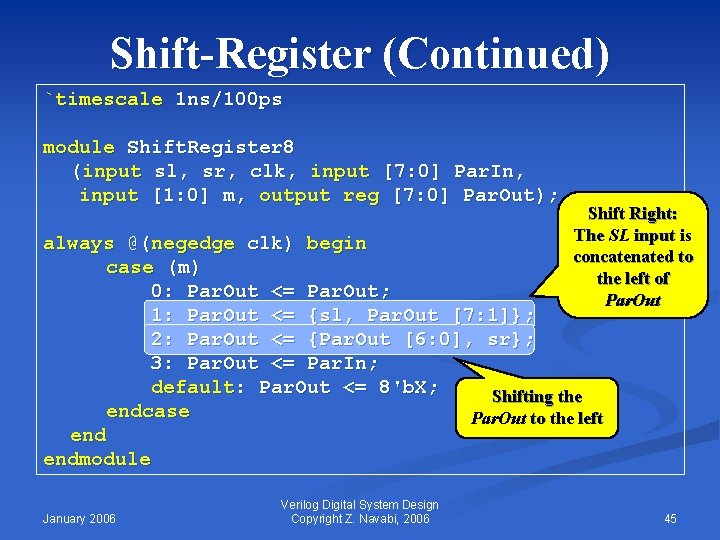

Shift-Register (Continued) `timescale 1 ns/100 ps module Shift. Register 8 (input sl, sr, clk, input [7: 0] Par. In, input [1: 0] m, output reg [7: 0] Par. Out); Shift Right: The SL input is concatenated to the left of Par. Out always @(negedge clk) begin case (m) 0: Par. Out <= Par. Out; 1: Par. Out <= {sl, Par. Out [7: 1]}; 2: Par. Out <= {Par. Out [6: 0], sr}; 3: Par. Out <= Par. In; default: Par. Out <= 8'b. X; Shifting the endcase Par. Out to the left endmodule January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 45

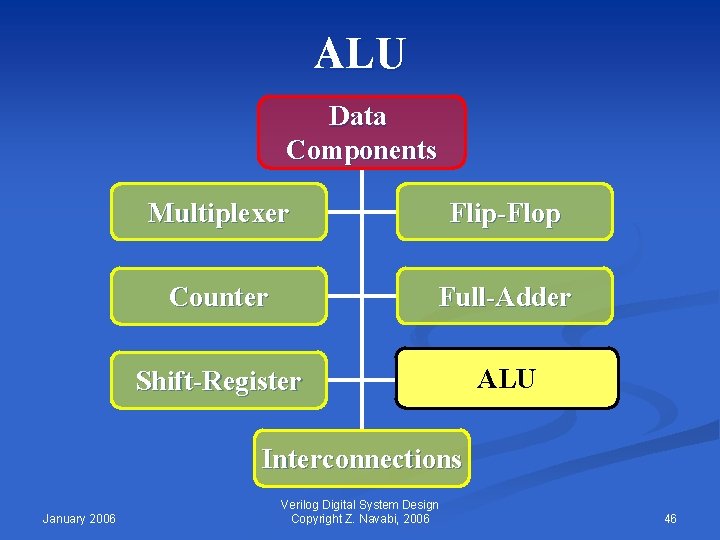

ALU Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 46

![ALU `timescale 1 ns/100 ps module ALU 8 (input [7: 0] left, right, 2 ALU `timescale 1 ns/100 ps module ALU 8 (input [7: 0] left, right, 2](http://slidetodoc.com/presentation_image/117d9335e101f831fd098da68bb118a6/image-47.jpg)

ALU `timescale 1 ns/100 ps module ALU 8 (input [7: 0] left, right, 2 -bit mode Input to select one of its 4 input [1: 0] mode, functions output reg [7: 0] ALUout); always @(left, right, mode) begin case (mode) 0: ALUout = left + right; 1: ALUout = left - right; Add Subtract 2: ALUout = left & right; AND 3: ALUout = left | right; OR default: ALUout = 8'b. X; endcase endmodule § An 8 -bit ALU January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 47

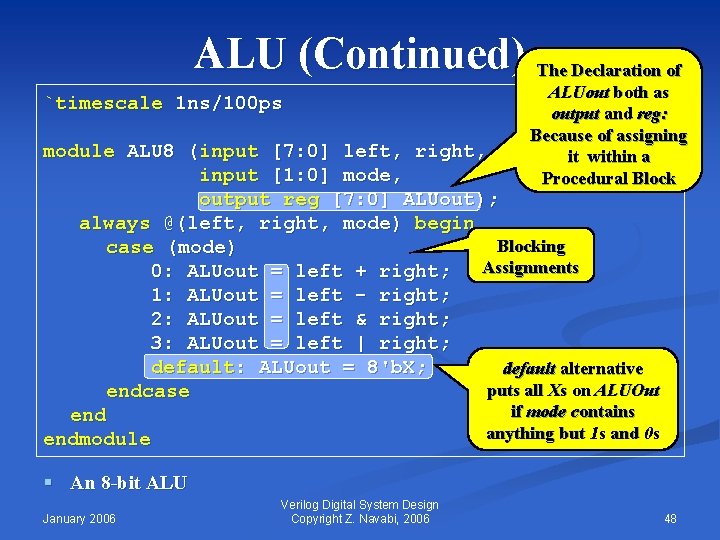

ALU (Continued) The Declaration of `timescale 1 ns/100 ps ALUout both as output and reg: Because of assigning it within a Procedural Block module ALU 8 (input [7: 0] left, right, input [1: 0] mode, output reg [7: 0] ALUout); always @(left, right, mode) begin Blocking case (mode) Assignments 0: ALUout = left + right; 1: ALUout = left - right; 2: ALUout = left & right; 3: ALUout = left | right; default: ALUout = 8'b. X; default alternative puts all Xs on ALUOut endcase if mode contains end anything but 1 s and 0 s endmodule § An 8 -bit ALU January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 48

Interconnections Data Components Multiplexer Flip-Flop Counter Full-Adder Shift-Register ALU Interconnections January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 49

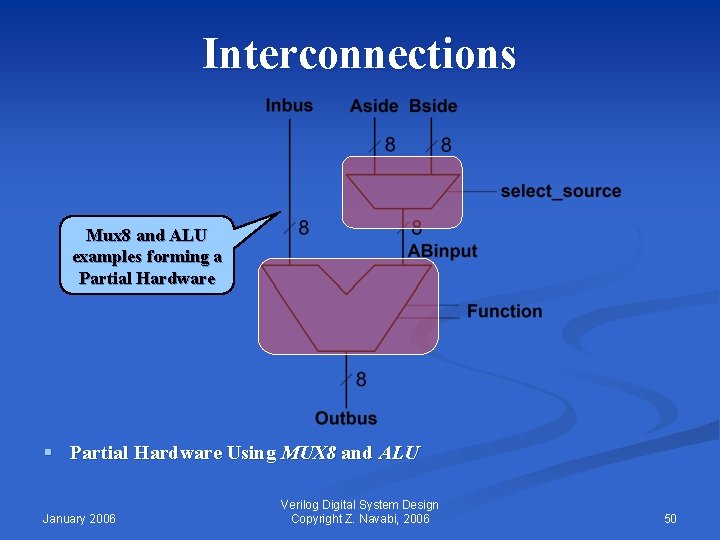

Interconnections Mux 8 and ALU examples forming a Partial Hardware § Partial Hardware Using MUX 8 and ALU January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 50

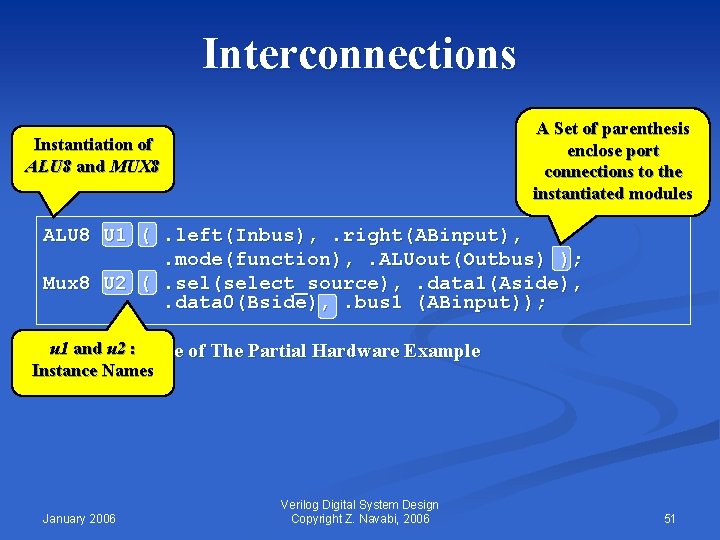

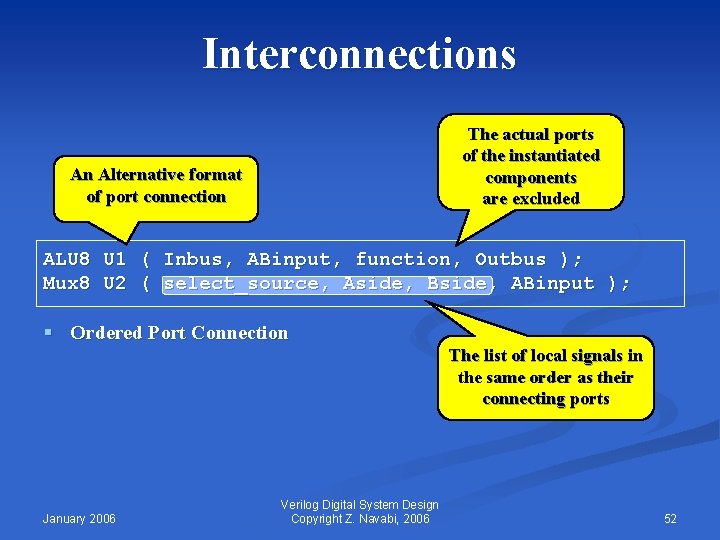

Interconnections A Set of parenthesis enclose port connections to the instantiated modules Instantiation of ALU 8 and MUX 8 ALU 8 U 1 (. left(Inbus), . right(ABinput), . mode(function), . ALUout(Outbus) ); Mux 8 U 2 (. sel(select_source), . data 1(Aside), . data 0(Bside), . bus 1 (ABinput)); and u 2 : Code of The Partial Hardware Example §u 1 Verilog Instance Names January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 51

Interconnections The actual ports of the instantiated components are excluded An Alternative format of port connection ALU 8 U 1 ( Inbus, ABinput, function, Outbus ); Mux 8 U 2 ( select_source, Aside, Bside, ABinput ); § Ordered Port Connection The list of local signals in the same order as their connecting ports January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 52

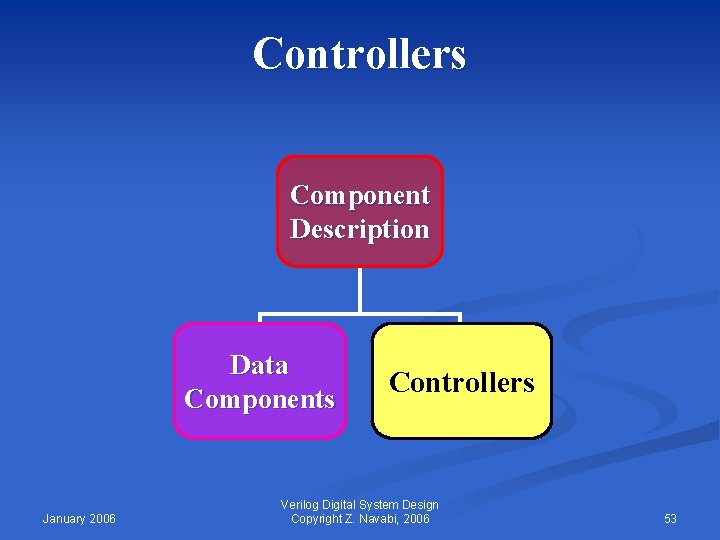

Controllers Component Description Data Components January 2006 Controllers Verilog Digital System Design Copyright Z. Navabi, 2006 53

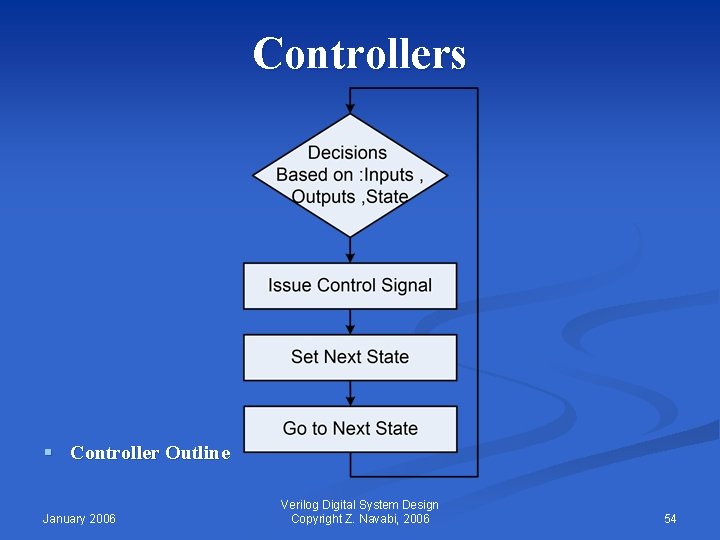

Controllers § Controller Outline January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 54

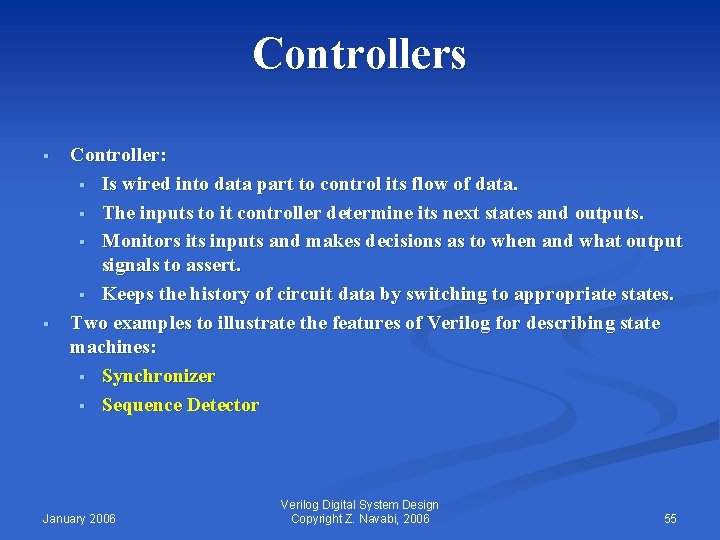

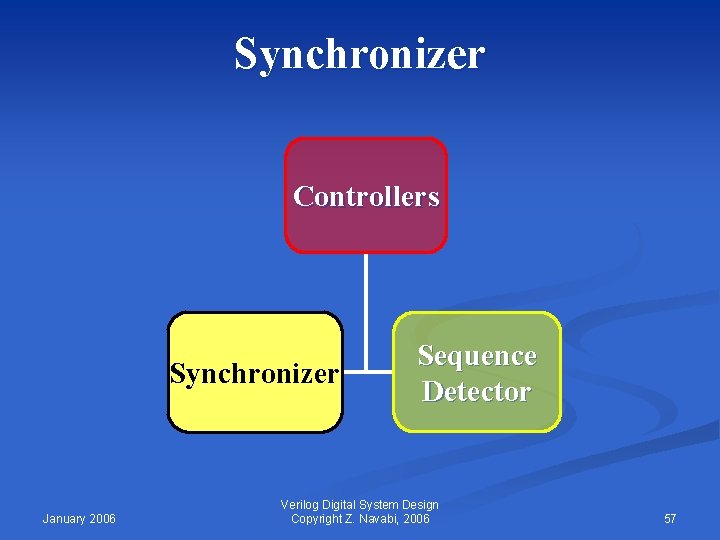

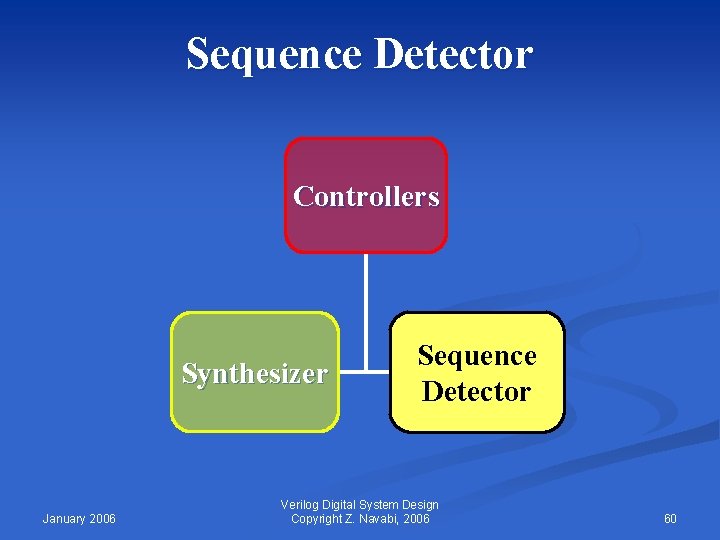

Controllers § § Controller: § Is wired into data part to control its flow of data. § The inputs to it controller determine its next states and outputs. § Monitors its inputs and makes decisions as to when and what output signals to assert. § Keeps the history of circuit data by switching to appropriate states. Two examples to illustrate the features of Verilog for describing state machines: § Synchronizer § Sequence Detector January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 55

Controllers Synchronizer January 2006 Sequence Detector Verilog Digital System Design Copyright Z. Navabi, 2006 56

Synchronizer Controllers Synthesizer Synchronizer January 2006 Sequence Detector Verilog Digital System Design Copyright Z. Navabi, 2006 57

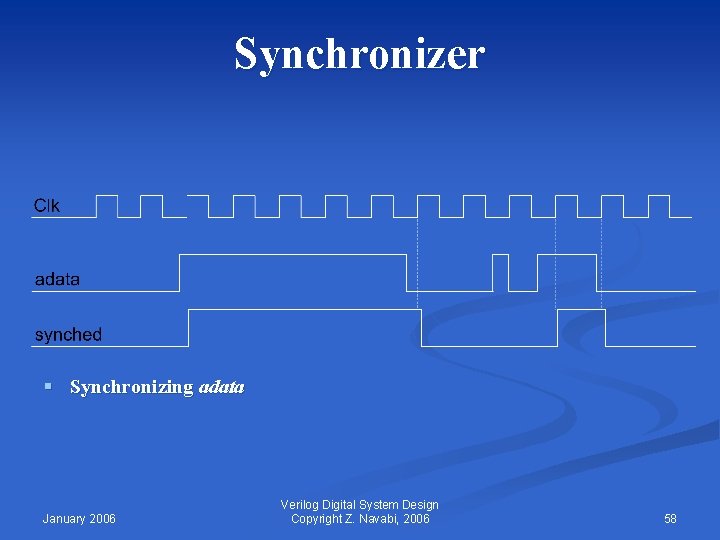

Synchronizer § Synchronizing adata January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 58

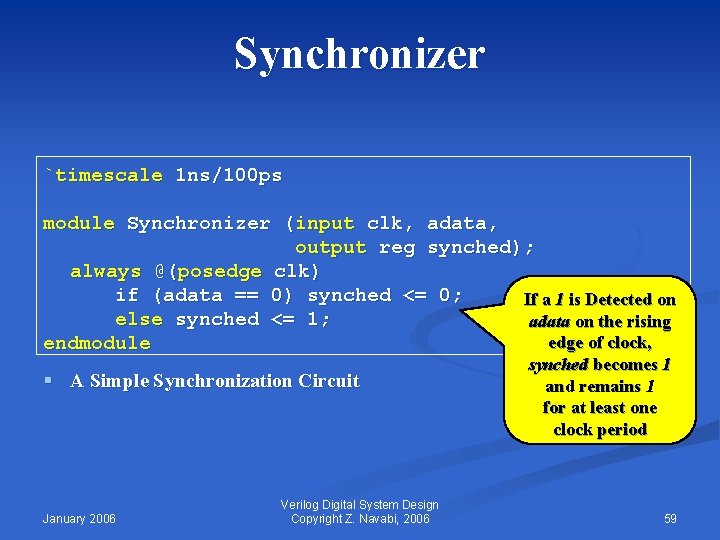

Synchronizer `timescale 1 ns/100 ps module Synchronizer (input clk, adata, output reg synched); always @(posedge clk) if (adata == 0) synched <= 0; If a 1 is Detected on else synched <= 1; adata on the rising edge of clock, endmodule § A Simple Synchronization Circuit January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 synched becomes 1 and remains 1 for at least one clock period 59

Sequence Detector Controllers Synthesizer January 2006 Sequence Detector Verilog Digital System Design Copyright Z. Navabi, 2006 60

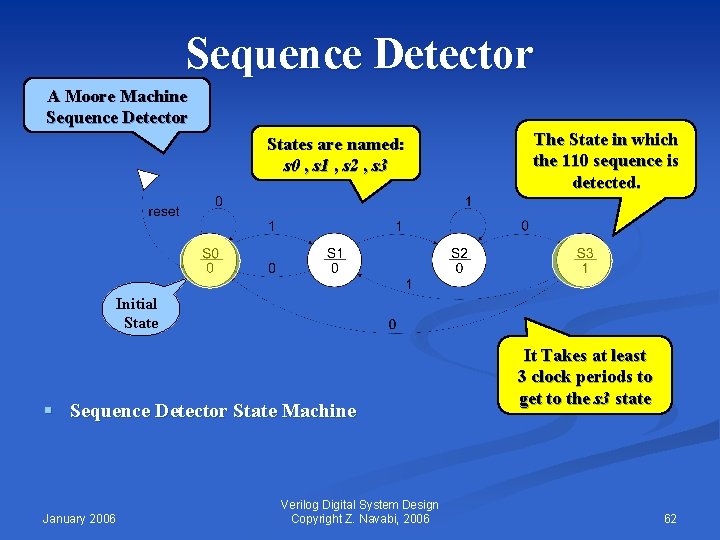

Sequence Detector When the sequence is detected, the w Output becomes 1 and stays 1 for a complete clock cycle Searches on it’s a input for the 110 Sequence § State Machine Description January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 61

Sequence Detector A Moore Machine Sequence Detector States are named: s 0 , s 1 , s 2 , s 3 The State in which the 110 sequence is detected. Initial State § Sequence Detector State Machine January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 It Takes at least 3 clock periods to get to the s 3 state 62

![Sequence Detector module Detector 110 (input a, clk, reset, output w); parameter [1: 0] Sequence Detector module Detector 110 (input a, clk, reset, output w); parameter [1: 0]](http://slidetodoc.com/presentation_image/117d9335e101f831fd098da68bb118a6/image-63.jpg)

Sequence Detector module Detector 110 (input a, clk, reset, output w); parameter [1: 0] s 0=2'b 00, s 1=2'b 01, s 2=2'b 10, s 3=2'b 11; reg [1: 0] current; always @(posedge clk) begin if (reset) current = s 0; else case (current) s 0: if (a) current <= s 1: if (a) current <= s 2: if (a) current <= s 3: if (a) current <= endcase end s 1; s 2; s 1; else current <= <= s 0; s 3; s 0; assign w = (current == s 3) ? 1 : 0; endmodule § Verilog Code for 110 Detector January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 63

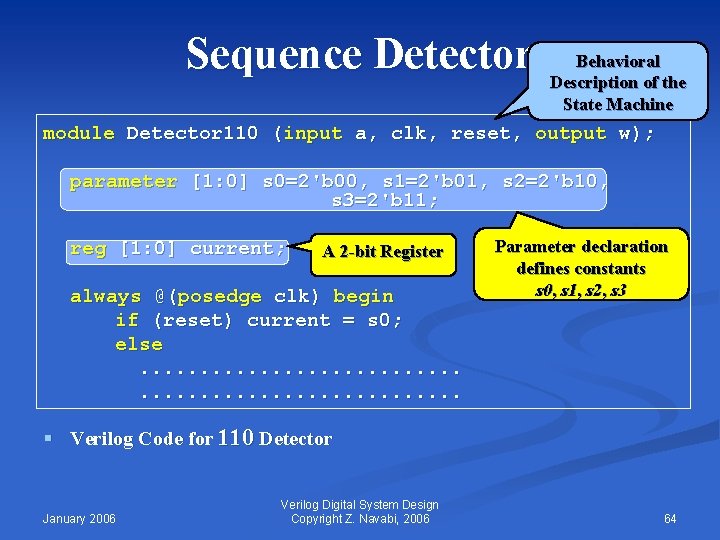

Sequence Detector Behavioral Description of the State Machine module Detector 110 (input a, clk, reset, output w); parameter [1: 0] s 0=2'b 00, s 1=2'b 01, s 2=2'b 10, s 3=2'b 11; reg [1: 0] current; A 2 -bit Register always @(posedge clk) begin if (reset) current = s 0; else. . . . Parameter declaration defines constants s 0, s 1, s 2, s 3 § Verilog Code for 110 Detector January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 64

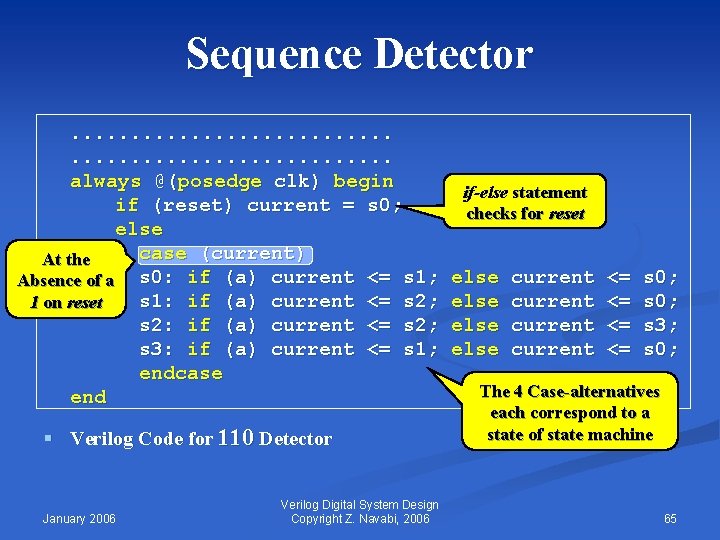

Sequence Detector. . . . always @(posedge clk) begin if (reset) current = s 0; else case (current) At the Absence of a s 0: if (a) current <= s 1; s 1: if (a) current <= s 2; 1 on reset s 2: if (a) current <= s 2; s 3: if (a) current <= s 1; endcase end § Verilog Code for 110 Detector January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 if-else statement checks for reset else current <= <= s 0; s 3; s 0; The 4 Case-alternatives each correspond to a state of state machine 65

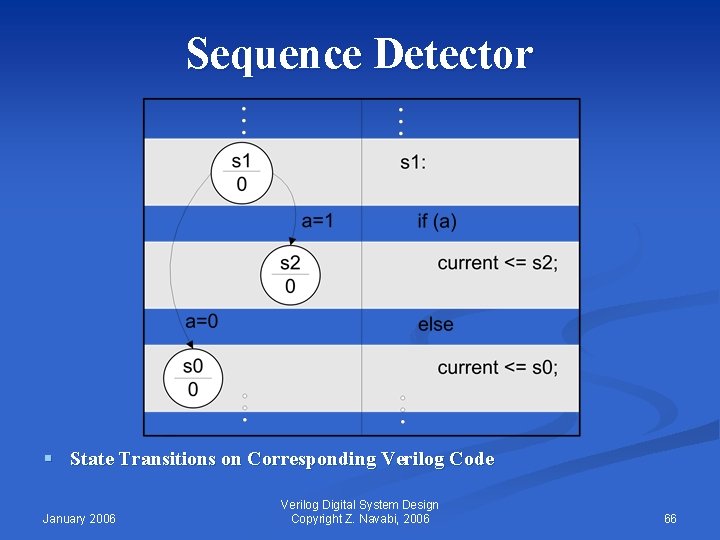

Sequence Detector § State Transitions on Corresponding Verilog Code January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 66

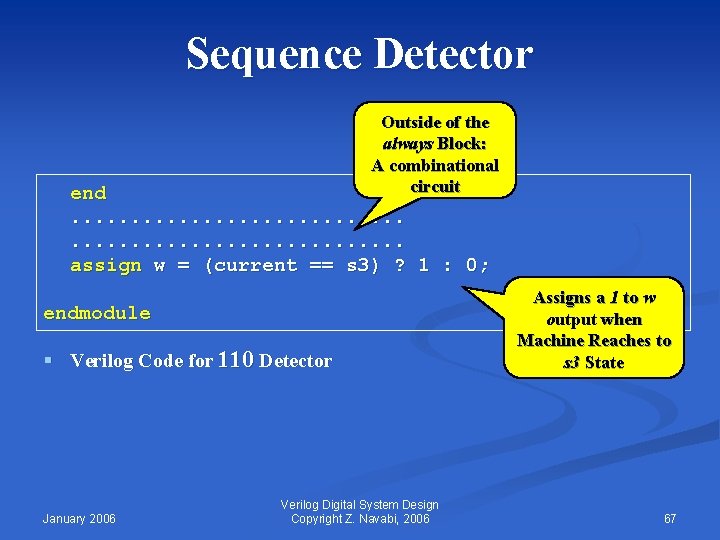

Sequence Detector Outside of the always Block: A combinational circuit end. . . . assign w = (current == s 3) ? 1 : 0; endmodule § Verilog Code for 110 Detector January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 Assigns a 1 to w output when Machine Reaches to s 3 State 67

Testbenches A Simple Tester January 2006 Tasks And Functions Verilog Digital System Design Copyright Z. Navabi, 2006 68

A Simple Tester Testbenches A Simple Tester January 2006 Tasks And Functions Verilog Digital System Design Copyright Z. Navabi, 2006 69

A Simple Tester `timescale 1 ns/100 ps module Detector 110 Tester; reg aa, clock, rst; wire ww; Detector 110 UUT (aa, clock, rst, ww); initial begin aa = 0; clock = 0; rst = 1; end initial repeat (44) #7 clock = ~clock; initial repeat (15) #23 aa = ~aa; initial begin #31 rst = 1; #23 rst = 0; end always @(ww) if (ww == 1) $display ("A 1 was detected on w at time = %t", $time); endmodule § Testbench for Detector 110 January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 70

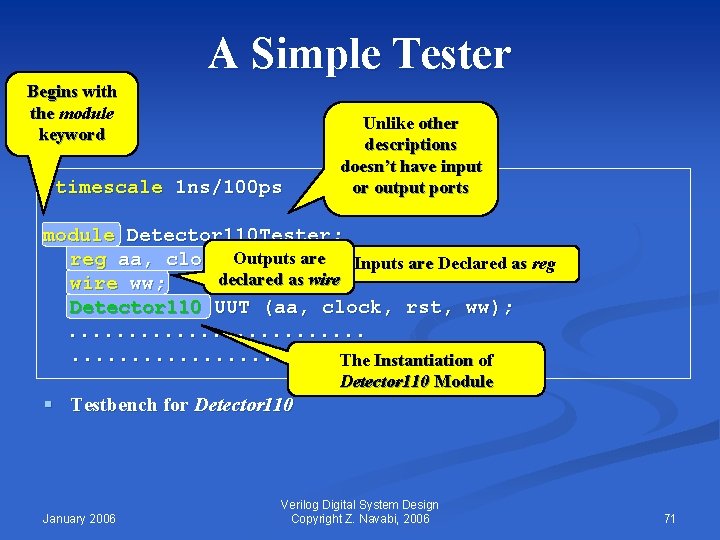

A Simple Tester Begins with the module keyword `timescale 1 ns/100 ps Unlike other descriptions doesn’t have input or output ports module Detector 110 Tester; reg aa, clock, Outputs rst; are Inputs are Declared as reg declared as wire ww; Detector 110 UUT (aa, clock, rst, ww); . . . The Instantiation of Detector 110 Module § Testbench for Detector 110 January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 71

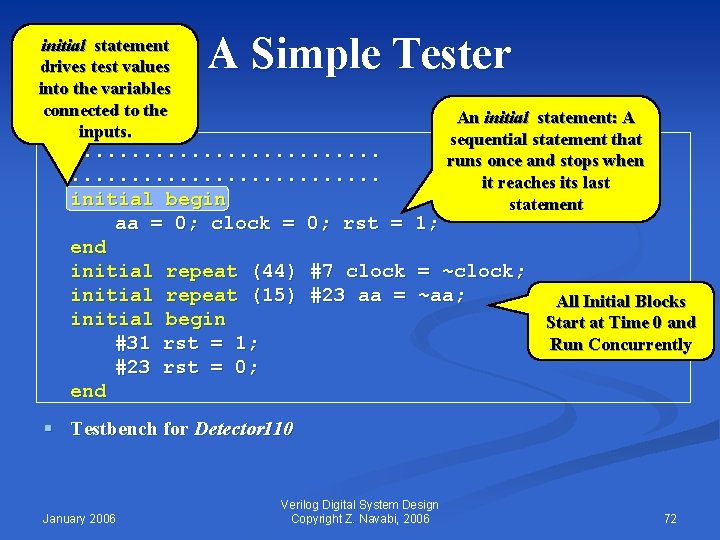

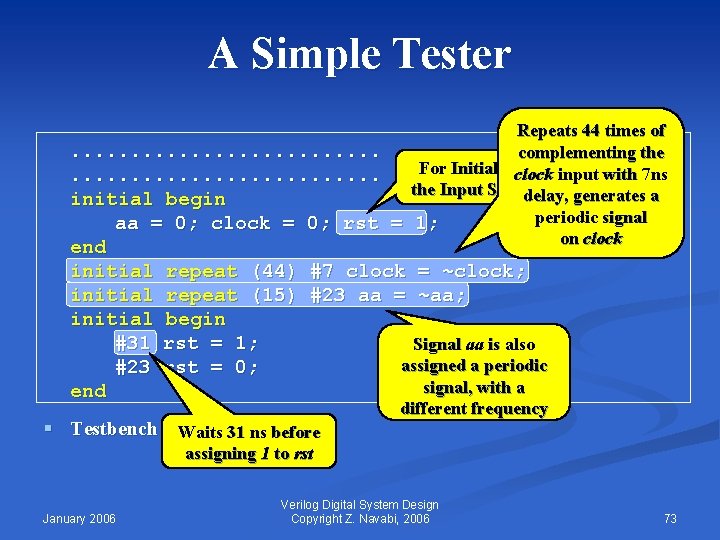

initial statement drives test values into the variables connected to the inputs. A Simple Tester An initial statement: A sequential statement that runs once and stops when it reaches its last statement . . . initial begin aa = 0; clock = 0; rst = 1; end initial repeat (44) #7 clock = ~clock; initial repeat (15) #23 aa = ~aa; All Initial Blocks initial begin Start at Time 0 and #31 rst = 1; Run Concurrently #23 rst = 0; end § Testbench for Detector 110 January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 72

A Simple Tester Repeats 44 times of. . . complementing the For Initializing clock input with 7 ns. . . the Input Signals delay, generates a initial begin periodic signal aa = 0; clock = 0; rst = 1; on clock end initial #31 #23 end repeat (44) #7 clock = ~clock; repeat (15) #23 aa = ~aa; begin rst = 1; Signal aa is also assigned a periodic rst = 0; § Testbench for Detector 110 Waits 31 ns before signal, with a different frequency assigning 1 to rst January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 73

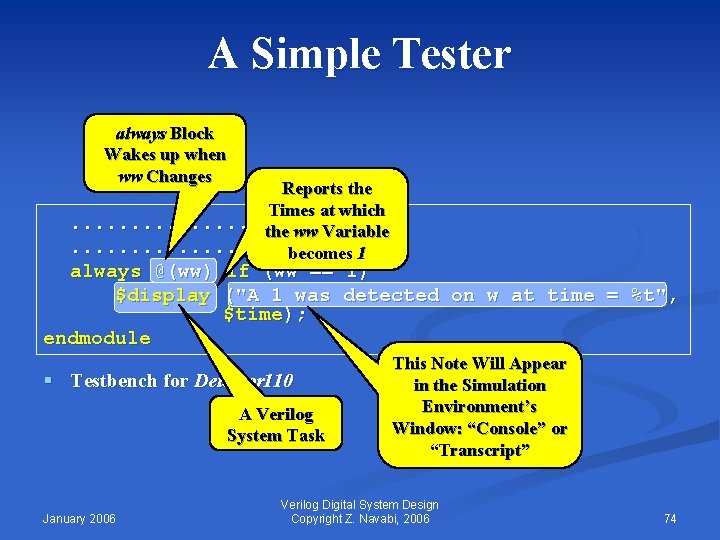

A Simple Tester always Block Wakes up when ww Changes Reports the Times at which. . . the ww Variable. . . becomes 1 always @(ww) if (ww == 1) $display ("A 1 was detected on w at time = %t", $time); endmodule § Testbench for Detector 110 A Verilog System Task January 2006 This Note Will Appear in the Simulation Environment’s Window: “Console” or “Transcript” Verilog Digital System Design Copyright Z. Navabi, 2006 74

Tasks And Functions Testbenches A Simple Tester January 2006 Tasks And Functions Verilog Digital System Design Copyright Z. Navabi, 2006 75

Tasks And Functions § § § Verilog Tasks and Functions: § System tasks for Input, Output, Display, and Timing Checks § User defined tasks and functions Tasks: § Can represent a sub module within a Verilog module § Begins with a task keyword § Its body can only consist of sequential statements like if-else and case Functions: § Can be used for corresponding to hardware entities § May be used for writing structured codes § Applications: Representation of Boolean functions, data and code conversion, and input and output formatting January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 76

Summary § This chapter presented: § An overview of Verilog and how this language is used for design and test of RT level description § Components of an RT level design § Small examples to illustrate such components and at the same time Verilog coding of hardware modules § The descriptions in this part were all synthesizable and had a one-to -one hardware correspondence. § How testbenches could be developed in Verilog and new constructs of it in this part January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 77

- Slides: 77