Digital Integrated Circuits A Design Perspective Jan M

![Standard Cell — Example [Brodersen 92] © Digital Integrated Circuits 2 nd Design Methodologie Standard Cell — Example [Brodersen 92] © Digital Integrated Circuits 2 nd Design Methodologie](https://slidetodoc.com/presentation_image_h/1911bf96ef70d2c64bf8711b7fd62407/image-6.jpg)

- Slides: 51

Digital Integrated Circuits A Design Perspective Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic Design Methodologies December 2002+ © Digital Integrated Circuits 2 nd Design Methodologie

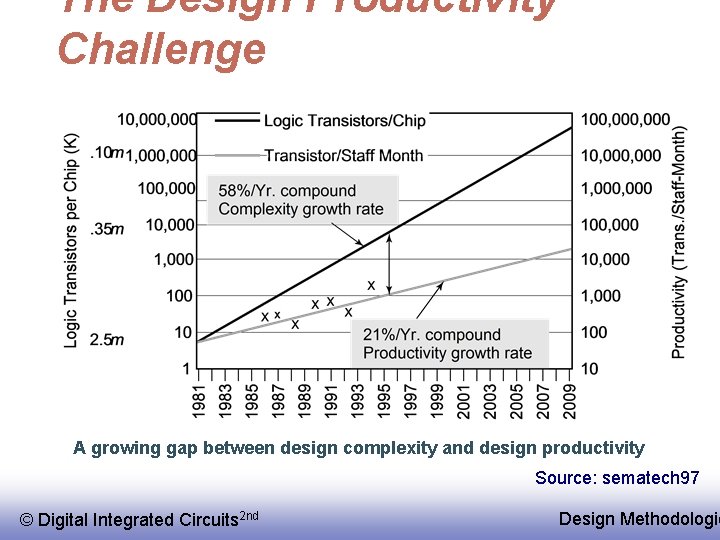

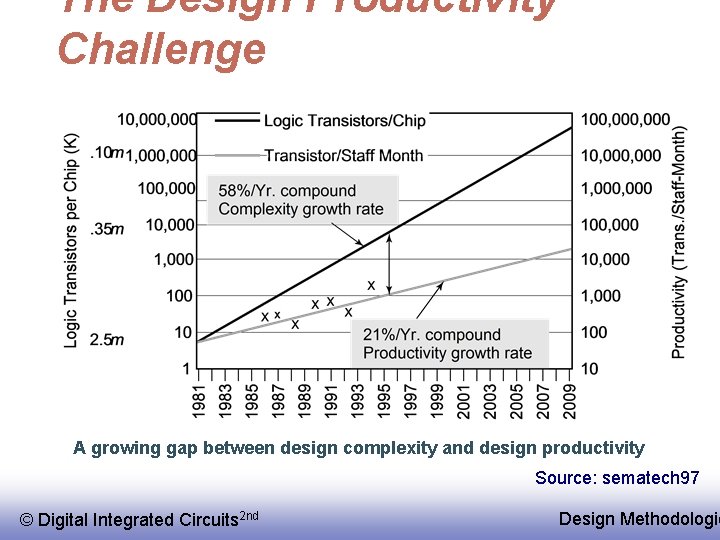

The Design Productivity Challenge A growing gap between design complexity and design productivity Source: sematech 97 © Digital Integrated Circuits 2 nd Design Methodologie

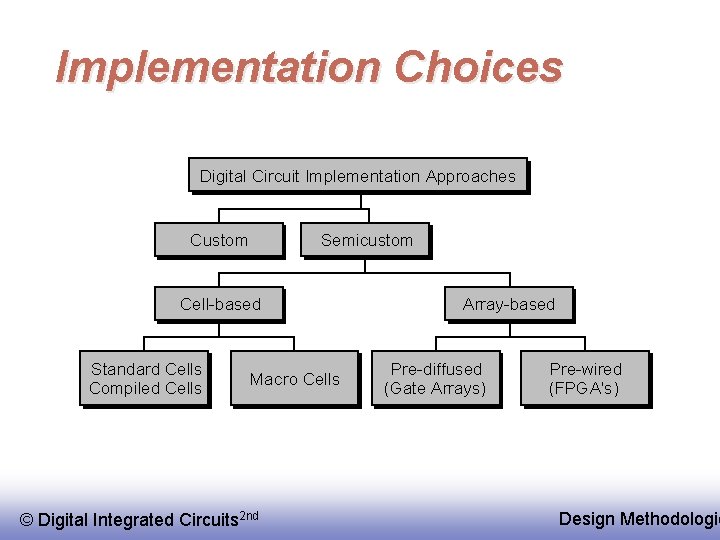

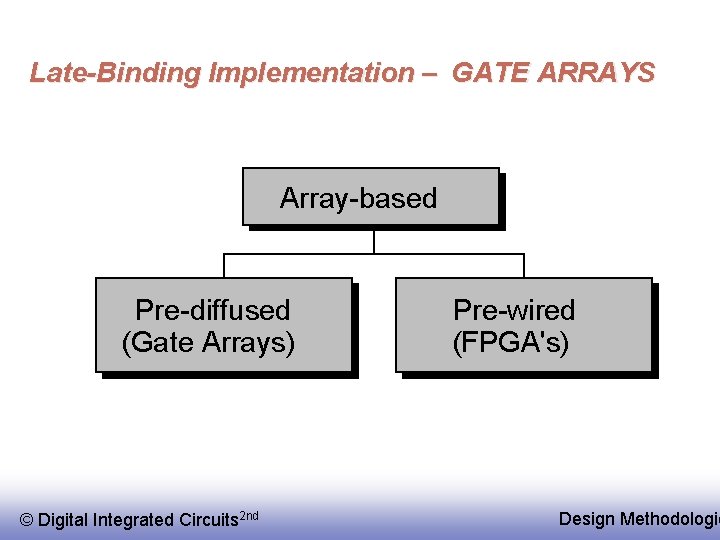

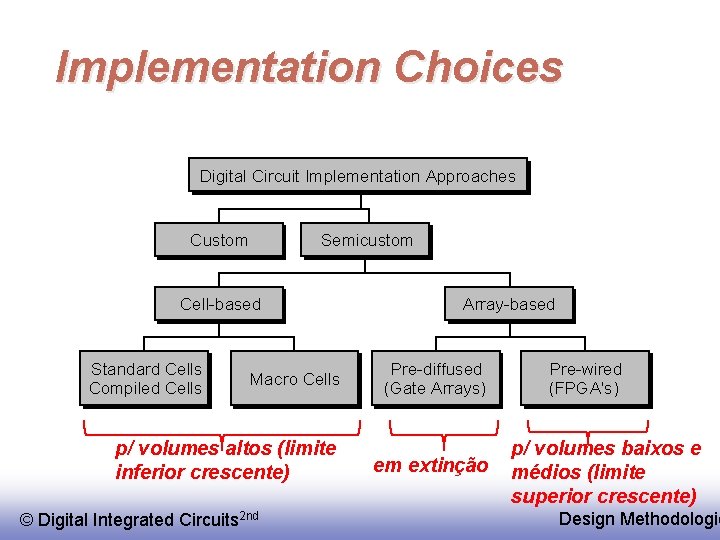

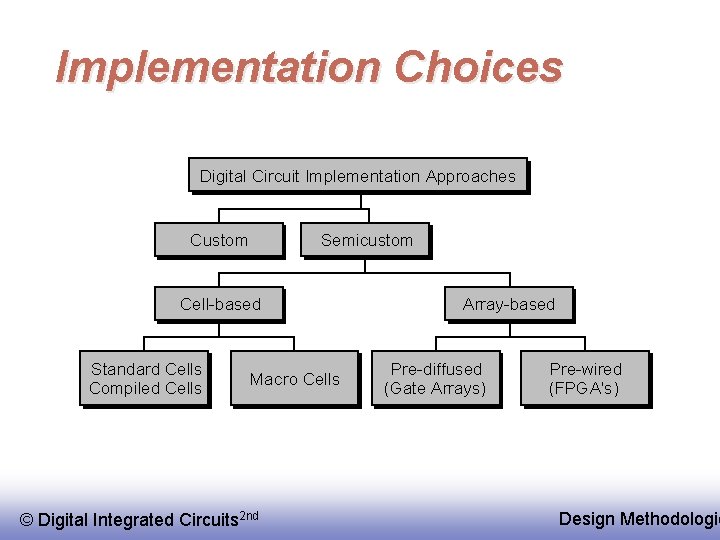

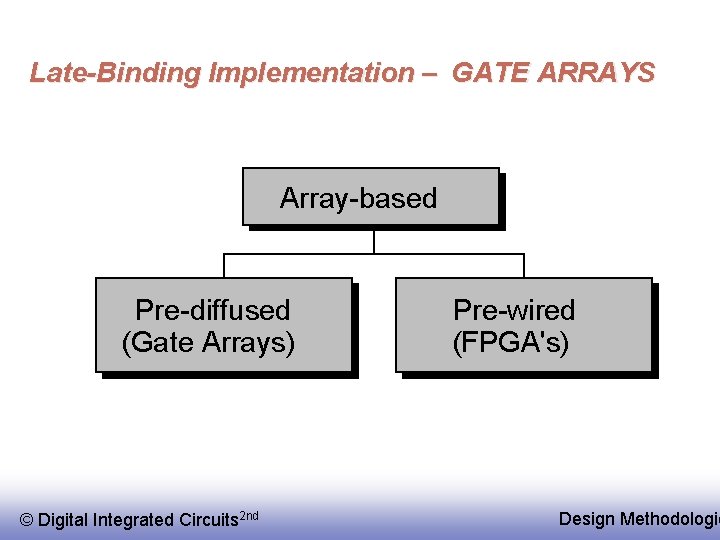

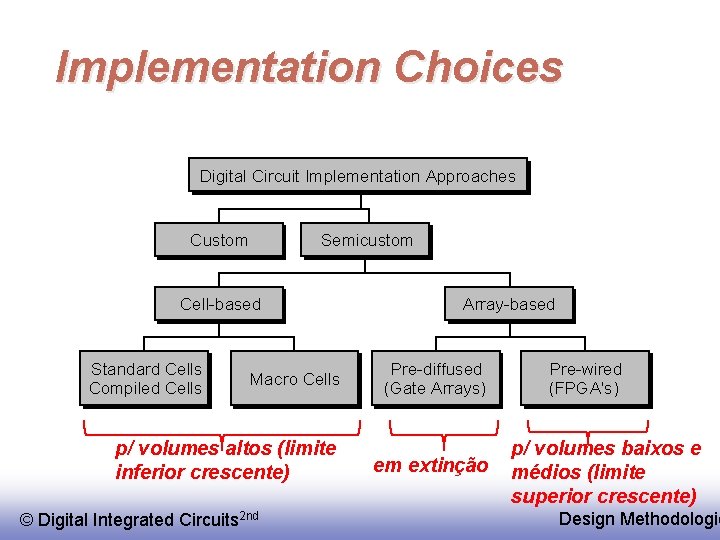

Implementation Choices Digital Circuit Implementation Approaches Custom Semicustom Cell-based Standard Cells Compiled Cells Macro Cells © Digital Integrated Circuits 2 nd Array-based Pre-diffused (Gate Arrays) Pre-wired (FPGA's) Design Methodologie

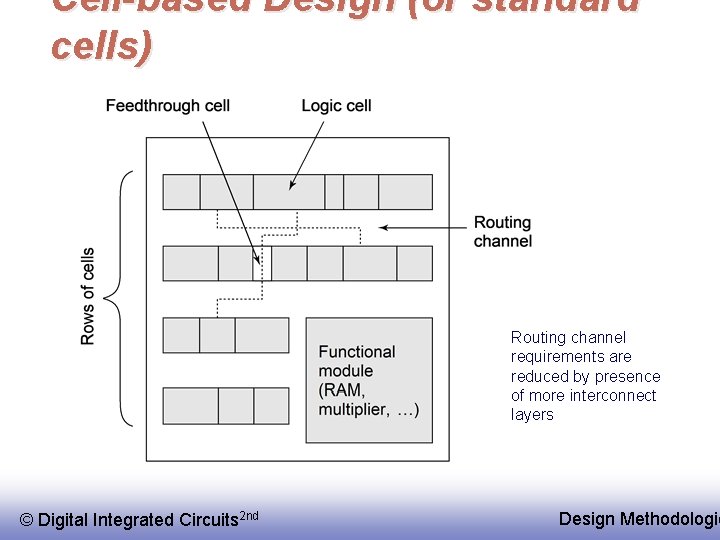

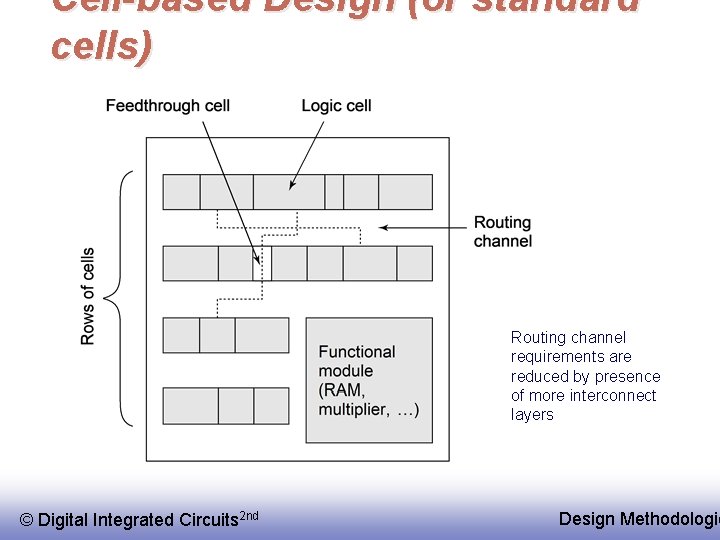

Cell-based Design (or standard cells) Routing channel requirements are reduced by presence of more interconnect layers © Digital Integrated Circuits 2 nd Design Methodologie

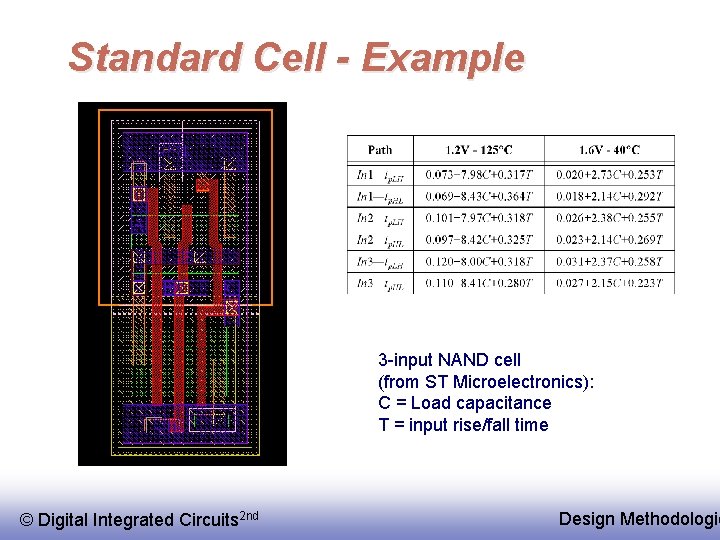

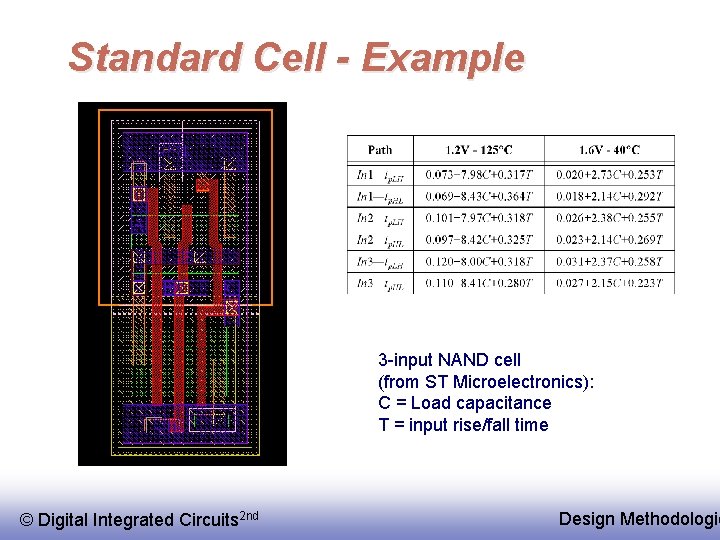

Standard Cell - Example 3 -input NAND cell (from ST Microelectronics): C = Load capacitance T = input rise/fall time © Digital Integrated Circuits 2 nd Design Methodologie

![Standard Cell Example Brodersen 92 Digital Integrated Circuits 2 nd Design Methodologie Standard Cell — Example [Brodersen 92] © Digital Integrated Circuits 2 nd Design Methodologie](https://slidetodoc.com/presentation_image_h/1911bf96ef70d2c64bf8711b7fd62407/image-6.jpg)

Standard Cell — Example [Brodersen 92] © Digital Integrated Circuits 2 nd Design Methodologie

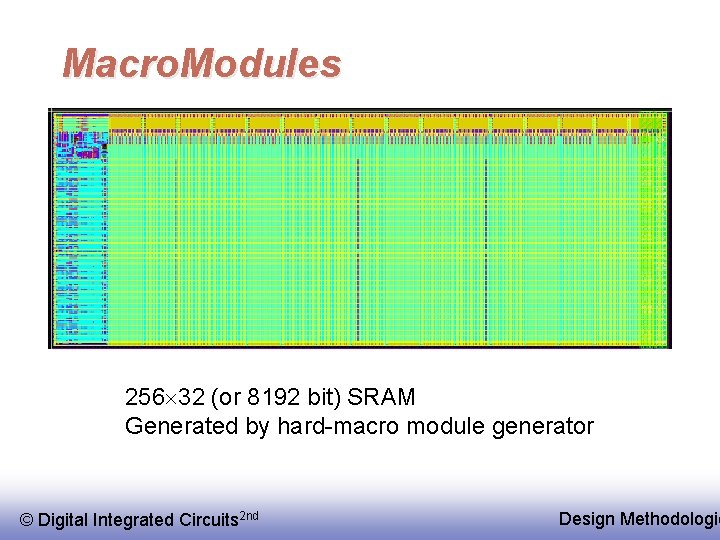

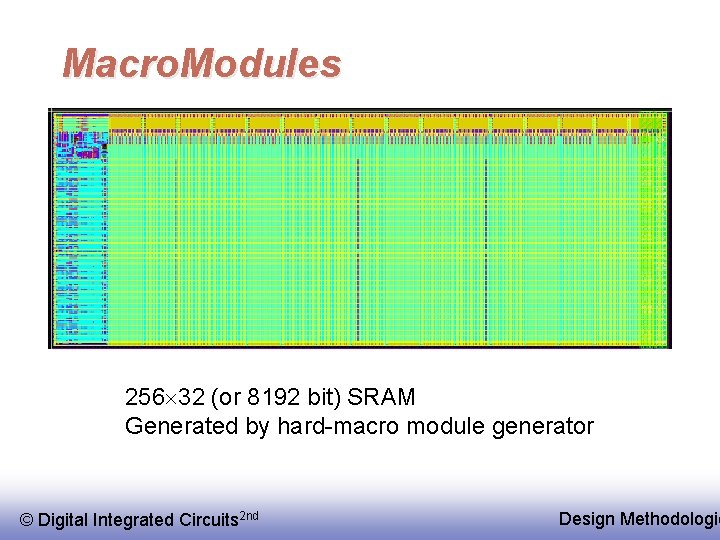

Macro. Modules 256 32 (or 8192 bit) SRAM Generated by hard-macro module generator © Digital Integrated Circuits 2 nd Design Methodologie

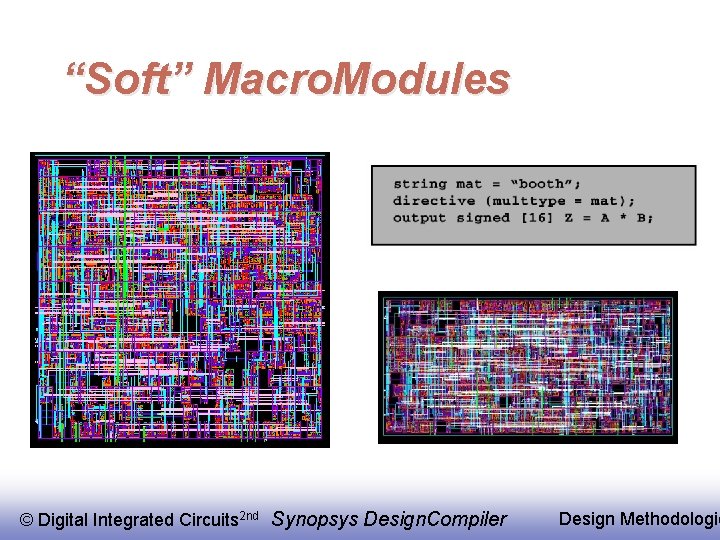

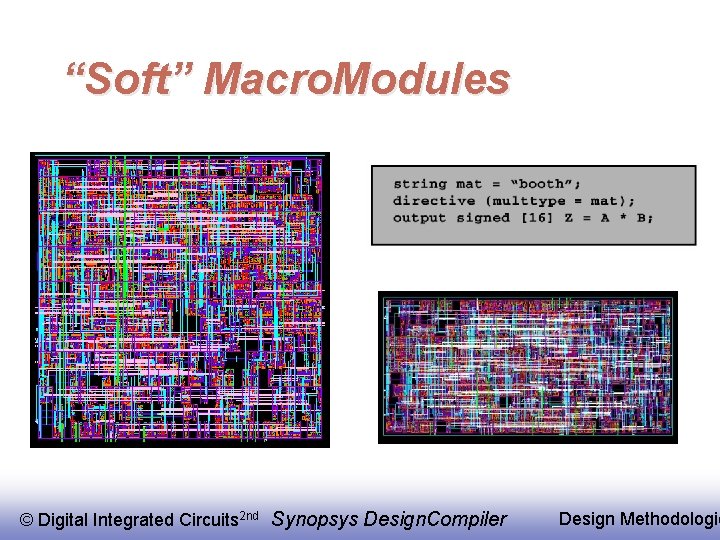

“Soft” Macro. Modules © Digital Integrated Circuits 2 nd Synopsys Design. Compiler Design Methodologie

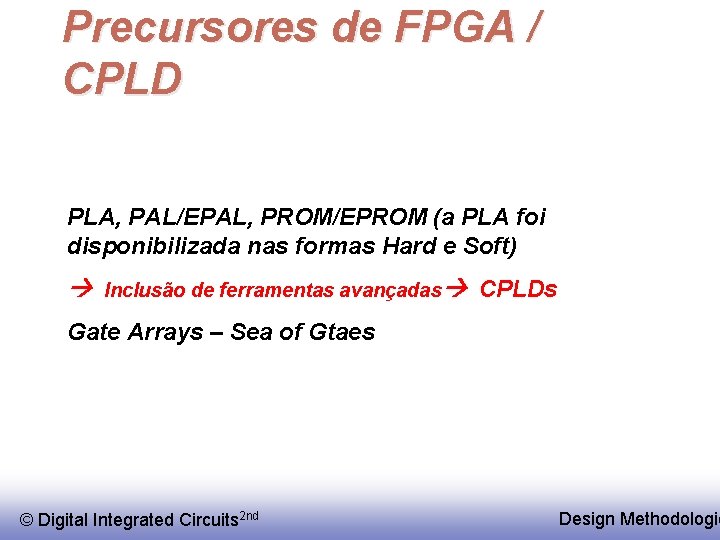

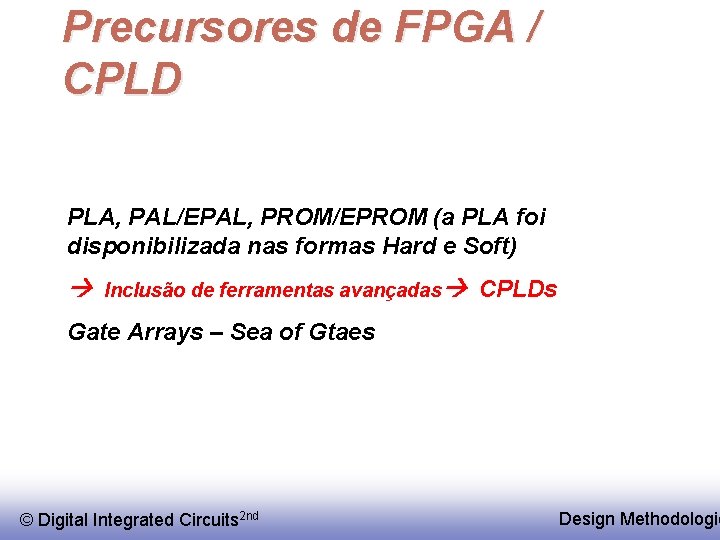

Precursores de FPGA / CPLD PLA, PAL/EPAL, PROM/EPROM (a PLA foi disponibilizada nas formas Hard e Soft) Gate Arrays – Sea of Gtaes © Digital Integrated Circuits 2 nd Design Methodologie

Precursores de FPGA / CPLD PLA, PAL/EPAL, PROM/EPROM (a PLA foi disponibilizada nas formas Hard e Soft) Inclusão de ferramentas avançadas CPLDs Gate Arrays – Sea of Gtaes © Digital Integrated Circuits 2 nd Design Methodologie

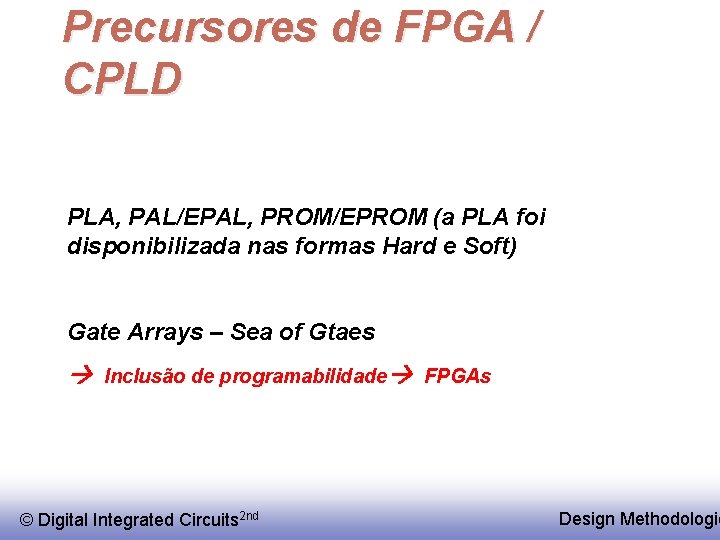

Precursores de FPGA / CPLD PLA, PAL/EPAL, PROM/EPROM (a PLA foi disponibilizada nas formas Hard e Soft) Gate Arrays – Sea of Gtaes Inclusão de programabilidade FPGAs © Digital Integrated Circuits 2 nd Design Methodologie

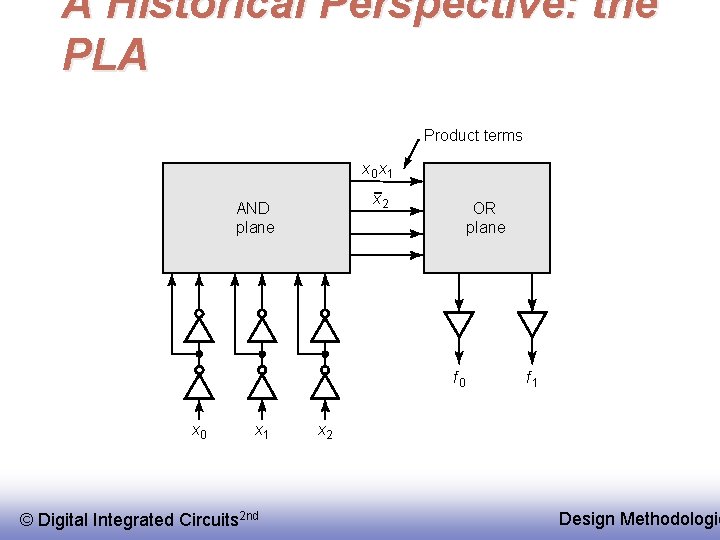

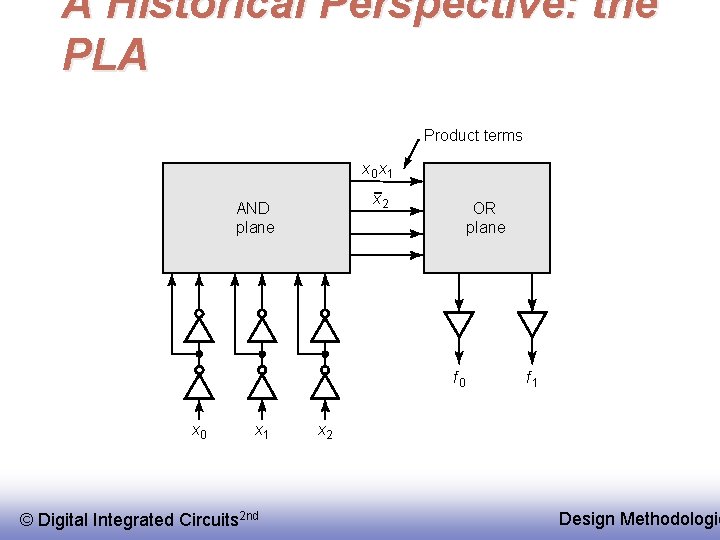

A Historical Perspective: the PLA Product terms x 0 x 1 x 2 AND plane OR plane f 0 x 1 © Digital Integrated Circuits 2 nd f 1 x 2 Design Methodologie

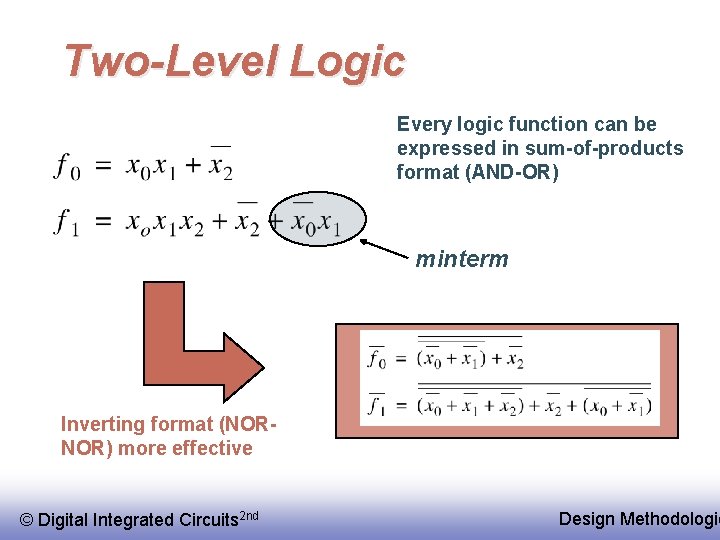

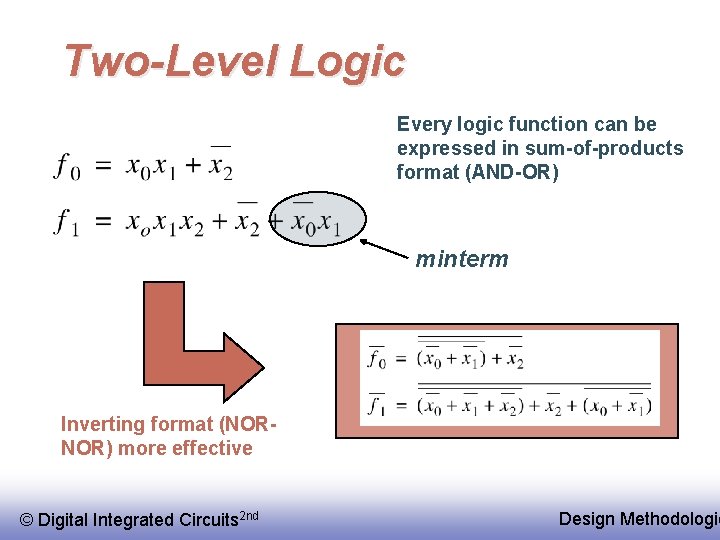

Two-Level Logic Every logic function can be expressed in sum-of-products format (AND-OR) minterm Inverting format (NORNOR) more effective © Digital Integrated Circuits 2 nd Design Methodologie

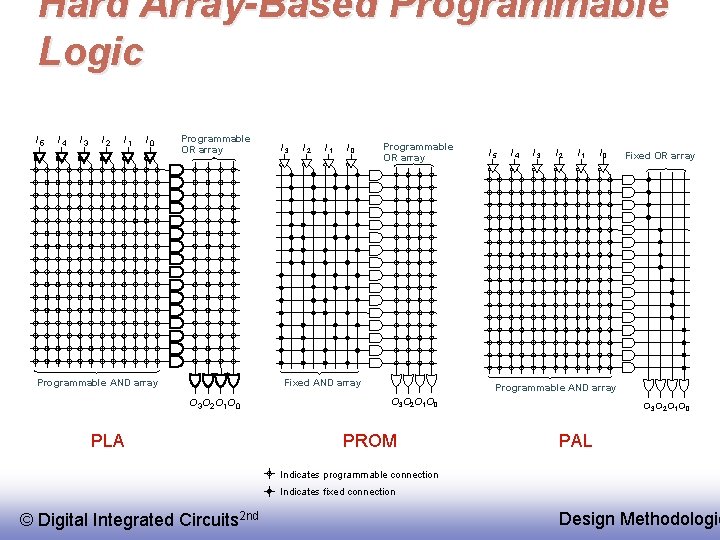

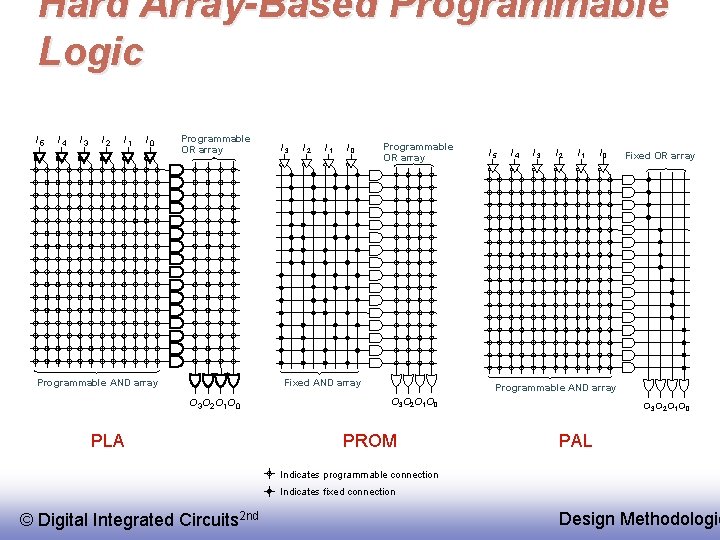

Hard Array-Based Programmable Logic I 5 I 4 I 3 I 2 I 1 I 0 Programmable OR array Programmable AND array I 3 I 2 I 1 I 0 Programmable OR array Fixed AND array O 3 O 2 O 1 O 0 PLA I 5 I 4 I 3 I 2 I 1 I 0 Fixed OR array Programmable AND array O 3 O 2 O 1 O 0 PROM O 3 O 2 O 1 O 0 PAL Indicates programmable connection Indicates fixed connection © Digital Integrated Circuits 2 nd Design Methodologie

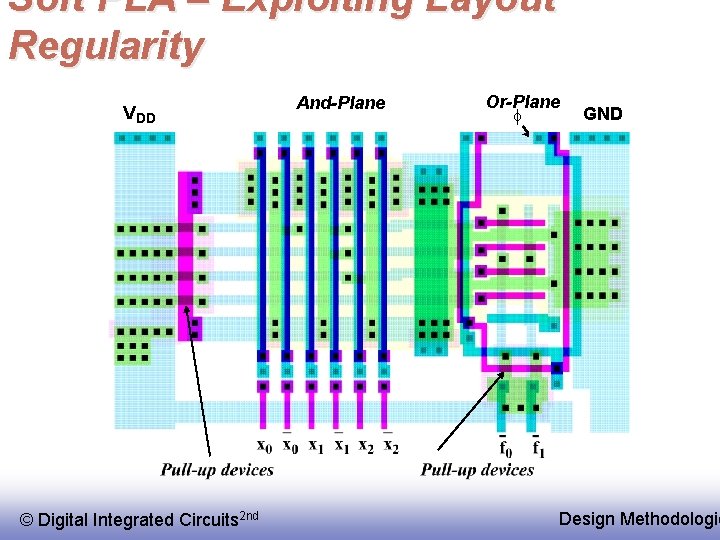

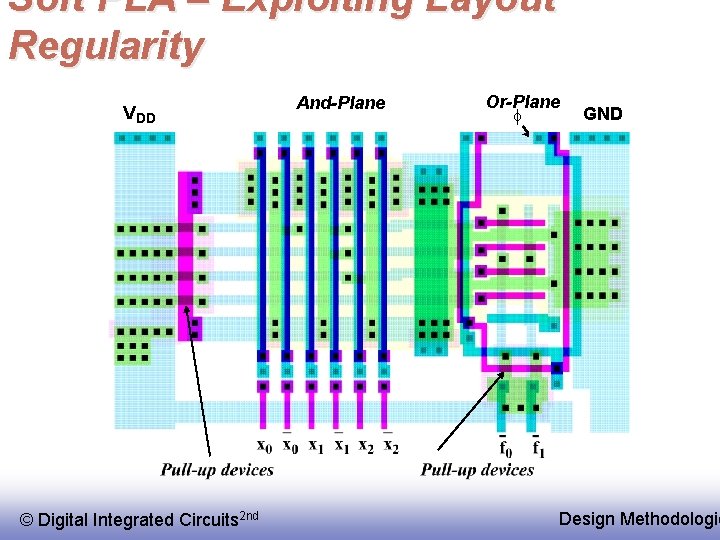

Soft PLA – Exploiting Layout Regularity V DD © Digital Integrated Circuits 2 nd And-Plane Or-Plane f GND Design Methodologie

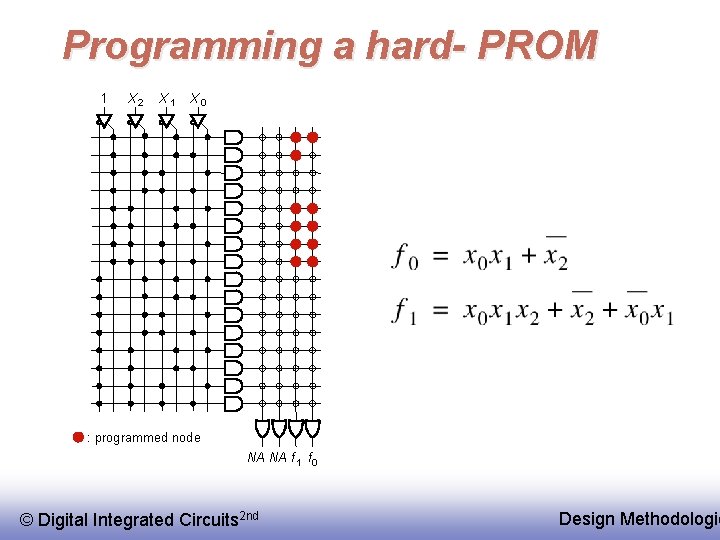

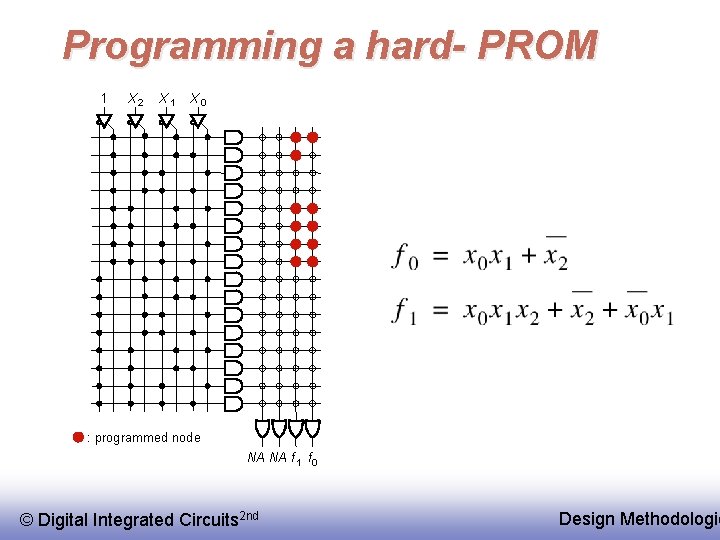

Programming a hard- PROM 1 X 2 X 1 X 0 : programmed node NA NA f 1 f 0 © Digital Integrated Circuits 2 nd Design Methodologie

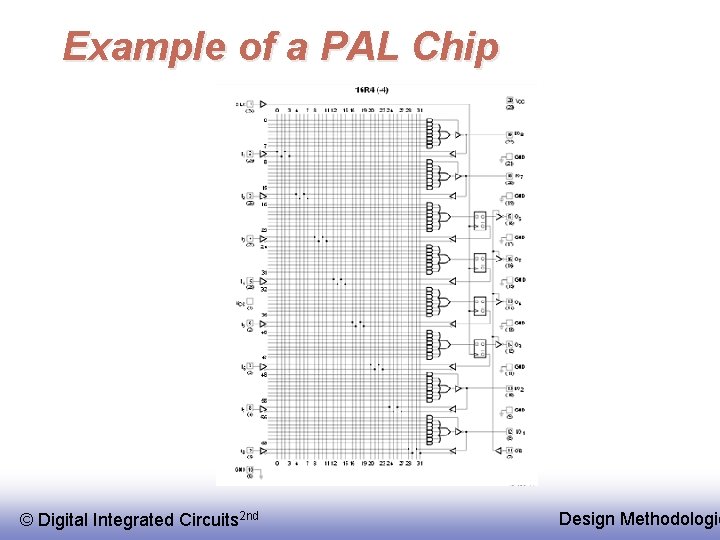

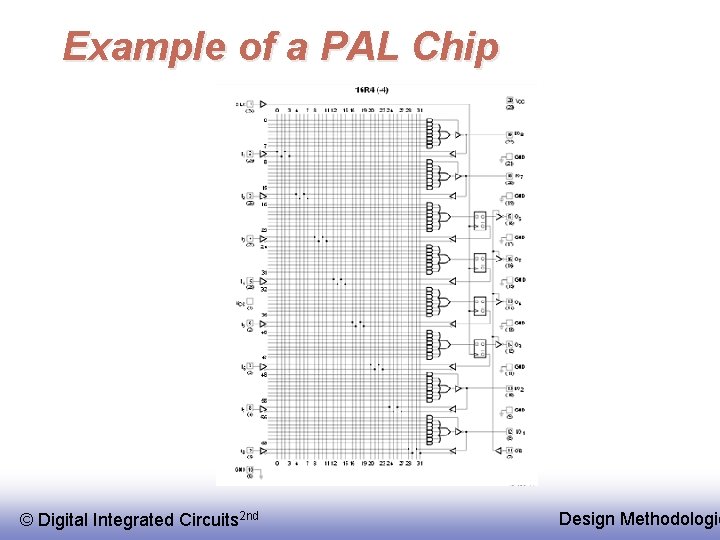

Example of a PAL Chip © Digital Integrated Circuits 2 nd Design Methodologie

Precursores de FPGA / CPLD PLA, PAL/EPAL, PROM/EPROM (a PLA foi disponibilizada nas formas Hard e Soft) Inclusão de ferramentas avançadas CPLDs Gate Arrays – Sea of Gtaes © Digital Integrated Circuits 2 nd Design Methodologie

Late-Binding Implementation – GATE ARRAYS Array-based Pre-diffused (Gate Arrays) © Digital Integrated Circuits 2 nd Pre-wired (FPGA's) Design Methodologie

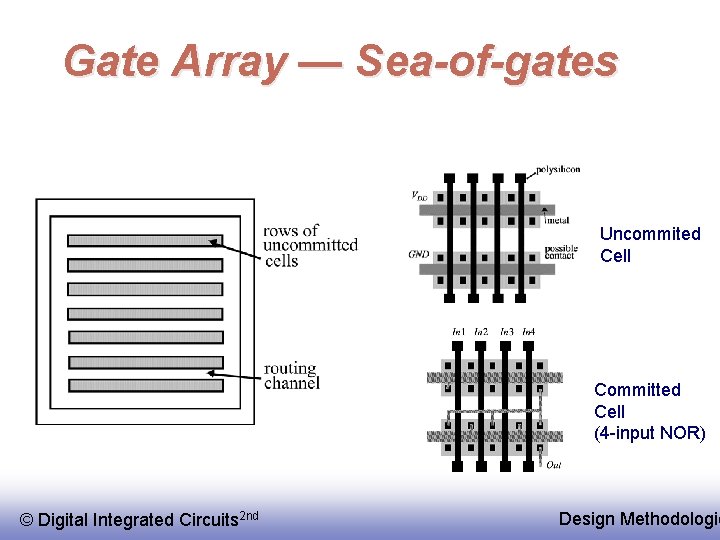

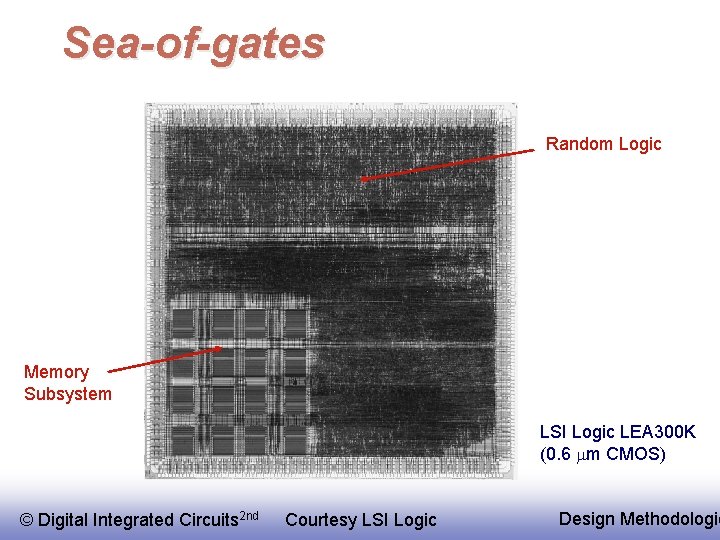

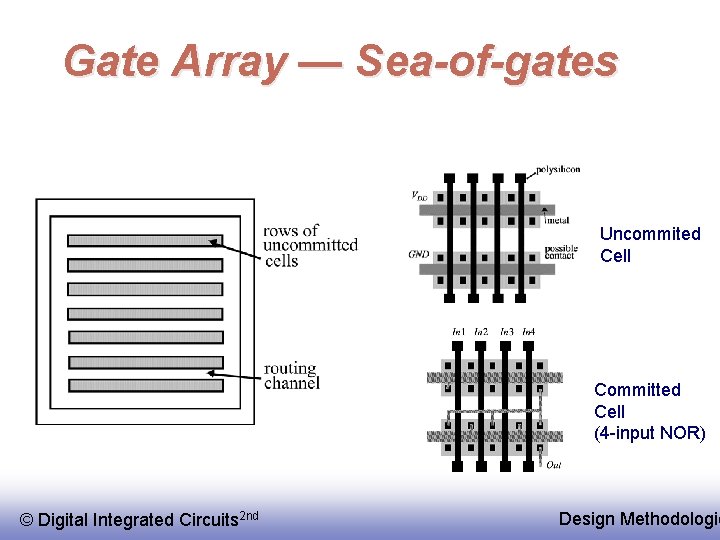

Gate Array — Sea-of-gates Uncommited Cell Committed Cell (4 -input NOR) © Digital Integrated Circuits 2 nd Design Methodologie

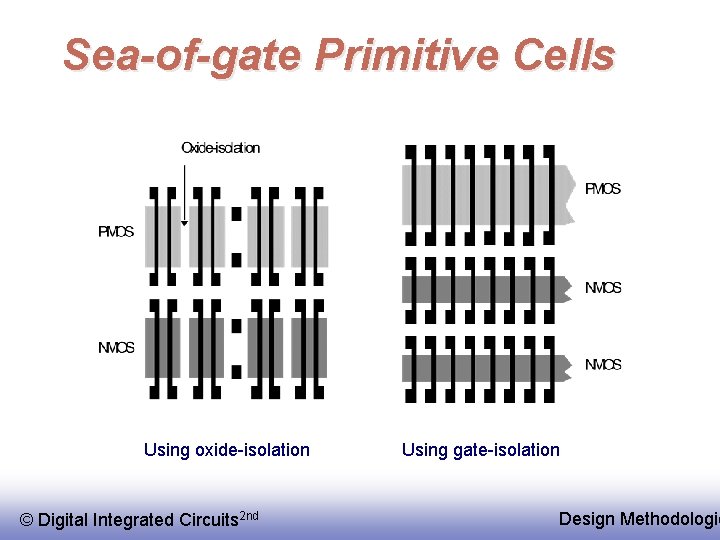

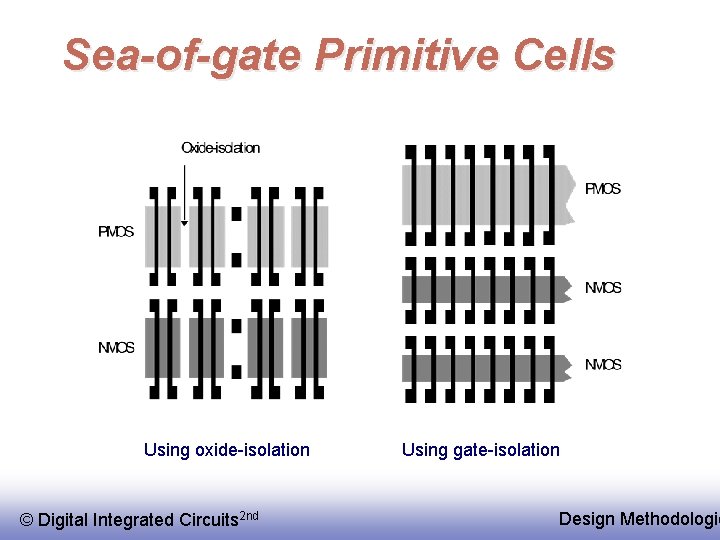

Sea-of-gate Primitive Cells Using oxide-isolation © Digital Integrated Circuits 2 nd Using gate-isolation Design Methodologie

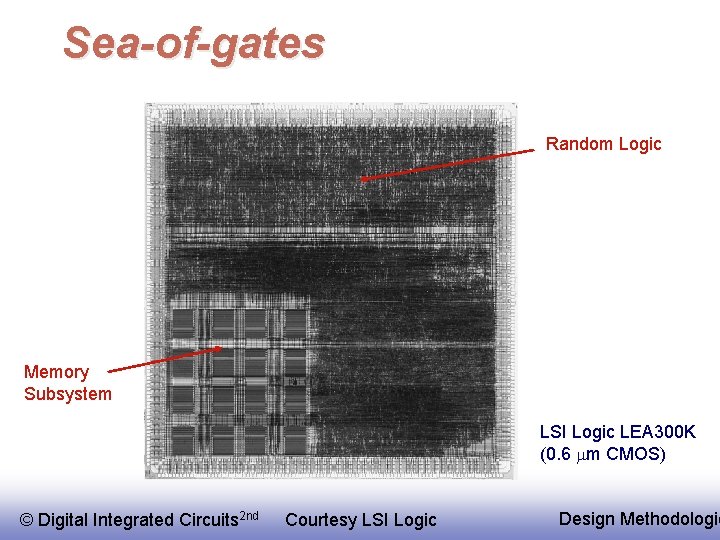

Sea-of-gates Random Logic Memory Subsystem LSI Logic LEA 300 K (0. 6 mm CMOS) © Digital Integrated Circuits 2 nd Courtesy LSI Logic Design Methodologie

O QUE FALTA SER FABRICADO? q CAMADAS DE METALIZAÇÃO E DE CONTATOS q NO CICLO DE PRODUÇÃO, A TAREFA DE FABRICAÇÃO FICA MAIS CURTA (RÁPIDA) E MUITO MAIS BARATA. q HÁ PERDA DE DESEMPENHO © Digital Integrated Circuits 2 nd Design Methodologie

Precursores de FPGA / CPLD PLA, PAL/EPAL, PROM/EPROM (a PLA foi disponibilizada nas formas Hard e Soft) Gate Arrays – Sea of Gtaes Inclusão de programabilidade FPGAs © Digital Integrated Circuits 2 nd Design Methodologie

O QUE FALTA SER FABRICADO? q NADA! q NO CICLO DE PRODUÇÃO, A FABRICAÇÃO OCORREU ANTES DO PROJETO. q O CUSTO DE PRODUÇÃO FICA MINIMIZADO. q HÁ PERDA DE DESEMPENHO © Digital Integrated Circuits 2 nd Design Methodologie

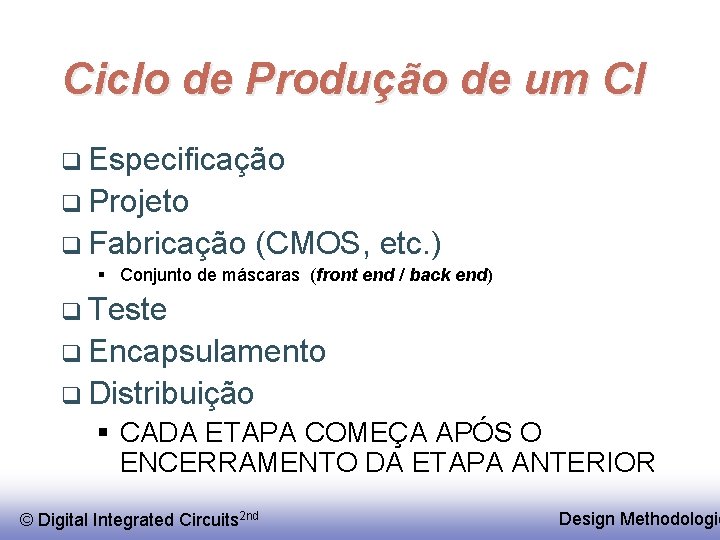

Ciclo de Produção de um CI q Especificação q Projeto q Fabricação (CMOS, etc. ) § Conjunto de máscaras (front end / back end) q Teste q Encapsulamento q Distribuição § CADA ETAPA COMEÇA APÓS O ENCERRAMENTO DA ETAPA ANTERIOR © Digital Integrated Circuits 2 nd Design Methodologie

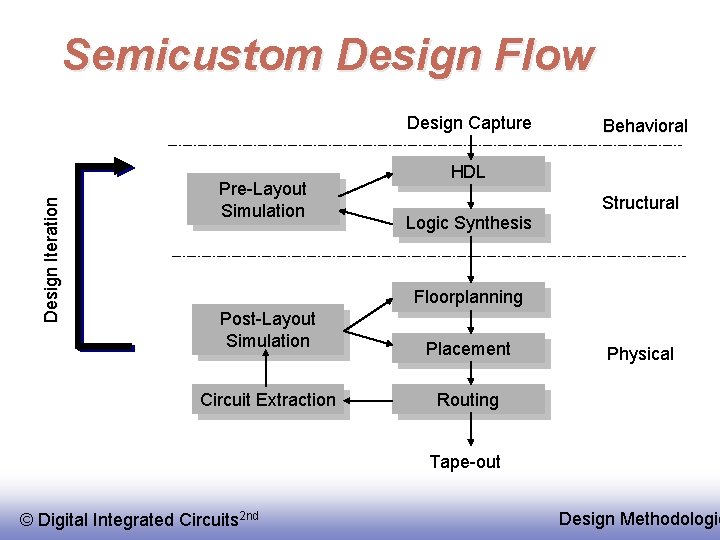

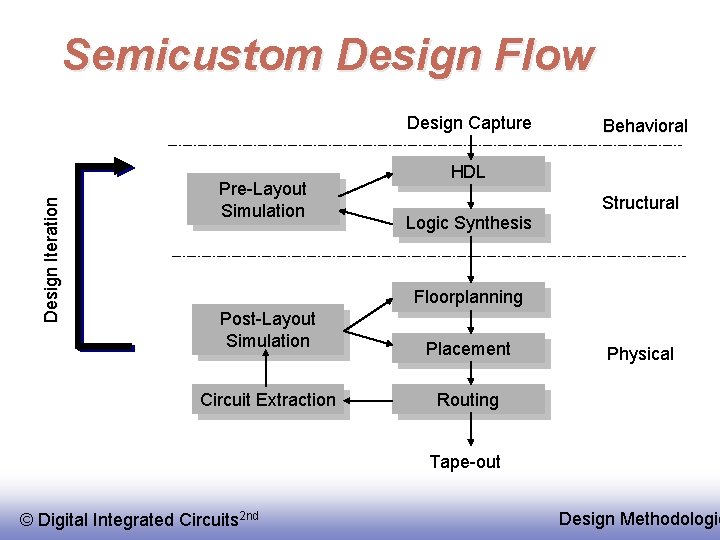

Semicustom Design Flow Design Iteration Design Capture Pre-Layout Simulation Behavioral HDL Logic Synthesis Structural Floorplanning Post-Layout Simulation Placement Circuit Extraction Routing Physical Tape-out © Digital Integrated Circuits 2 nd Design Methodologie

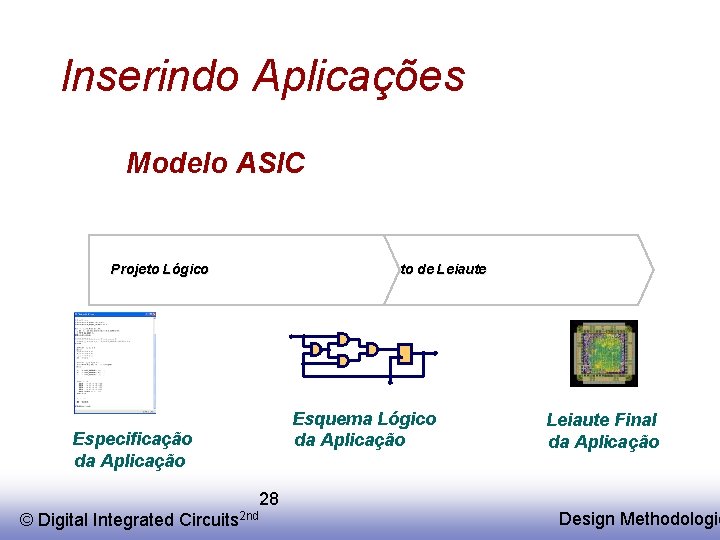

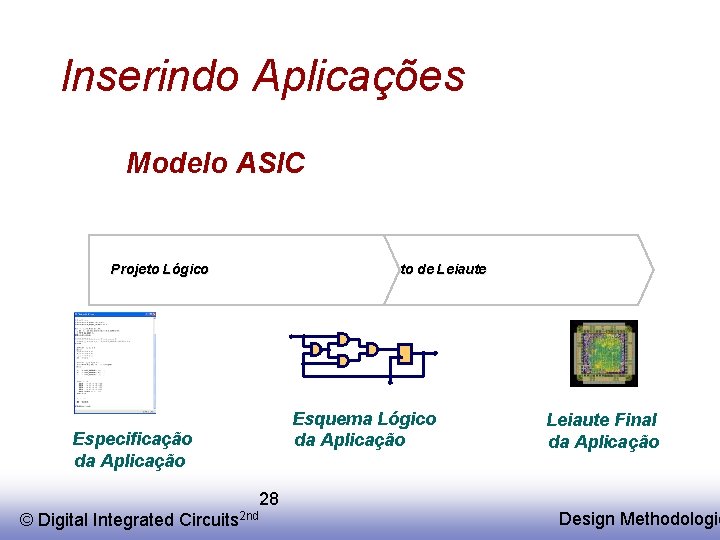

Inserindo Aplicações Modelo ASIC Projeto Lógico Projeto de Leiaute Esquema Lógico da Aplicação Especificação da Aplicação 28 © Digital Integrated Circuits 2 nd Leiaute Final da Aplicação Design Methodologie

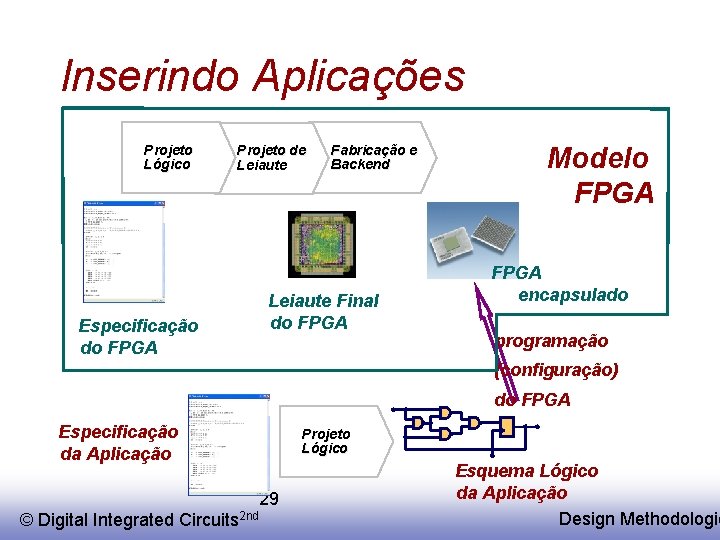

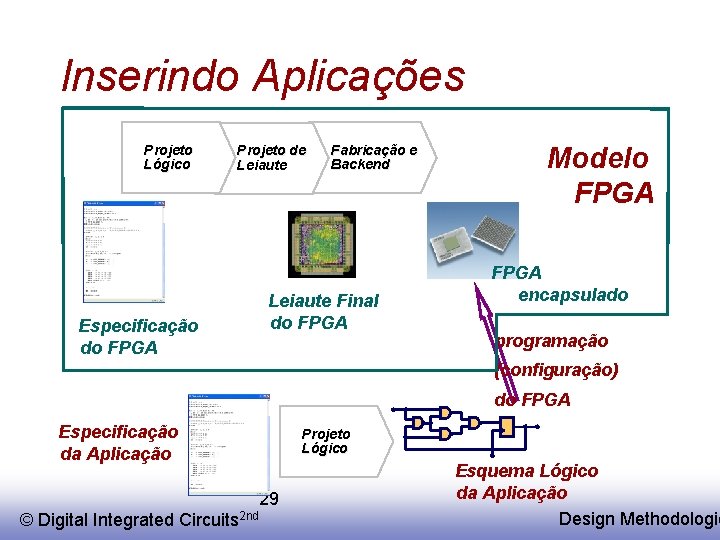

Inserindo Aplicações Projeto Lógico Projeto de Leiaute Especificação do FPGA Fabricação e Backend Leiaute Final do FPGA Modelo FPGA encapsulado programação (configuração) do FPGA Especificação da Aplicação Projeto Lógico 29 © Digital Integrated Circuits 2 nd Esquema Lógico da Aplicação Design Methodologie

Implementation Choices Digital Circuit Implementation Approaches Custom Semicustom Cell-based Standard Cells Compiled Cells Macro Cells p/ volumes altos (limite inferior crescente) © Digital Integrated Circuits 2 nd Array-based Pre-diffused (Gate Arrays) em extinção Pre-wired (FPGA's) p/ volumes baixos e médios (limite superior crescente) Design Methodologie

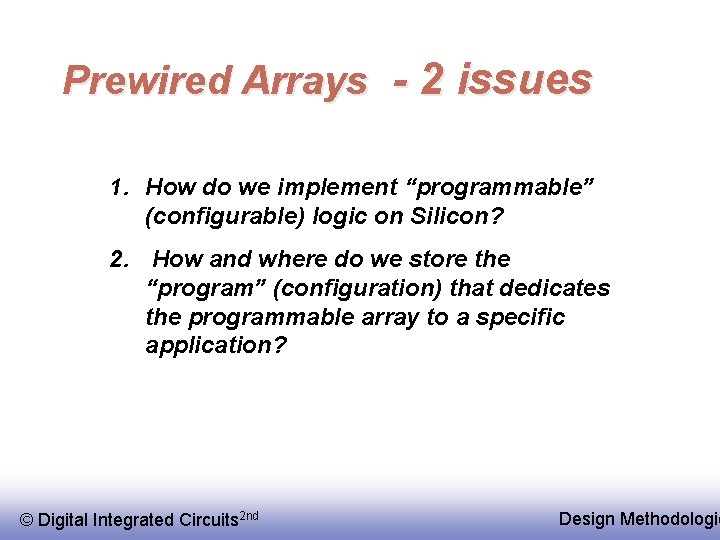

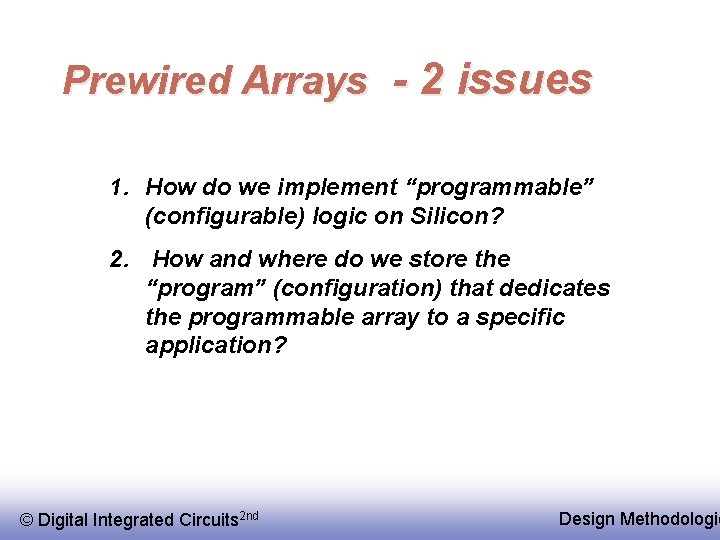

Prewired Arrays - 2 issues 1. How do we implement “programmable” (configurable) logic on Silicon? 2. How and where do we store the “program” (configuration) that dedicates the programmable array to a specific application? © Digital Integrated Circuits 2 nd Design Methodologie

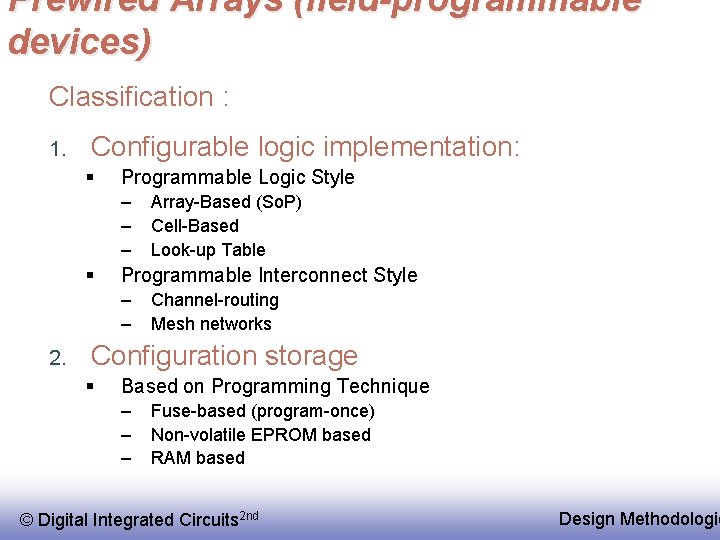

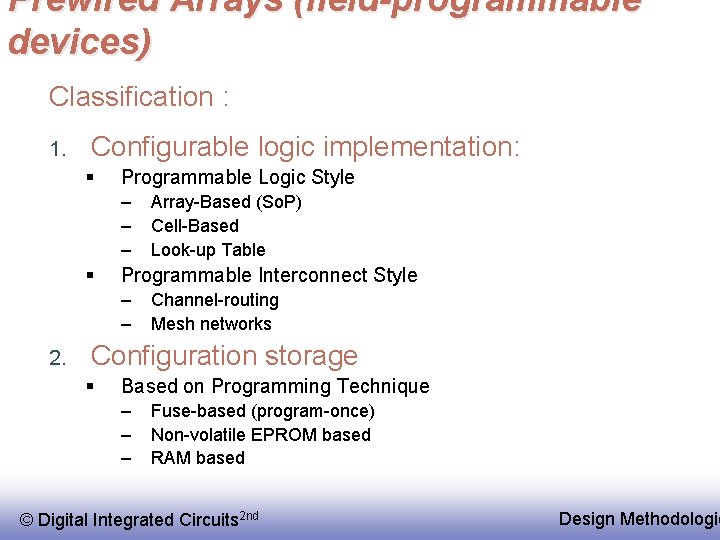

Prewired Arrays (field-programmable devices) Classification : 1. Configurable logic implementation: § Programmable Logic Style – – – § Programmable Interconnect Style – – 2. Array-Based (So. P) Cell-Based Look-up Table Channel-routing Mesh networks Configuration storage § Based on Programming Technique – – – Fuse-based (program-once) Non-volatile EPROM based RAM based © Digital Integrated Circuits 2 nd Design Methodologie

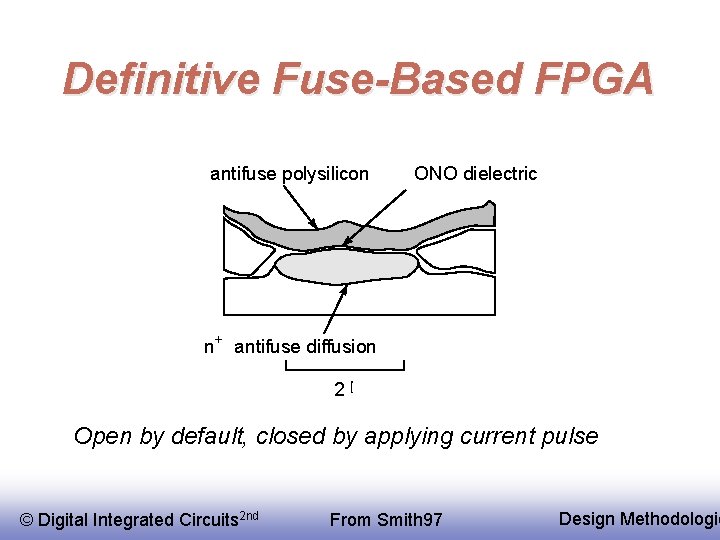

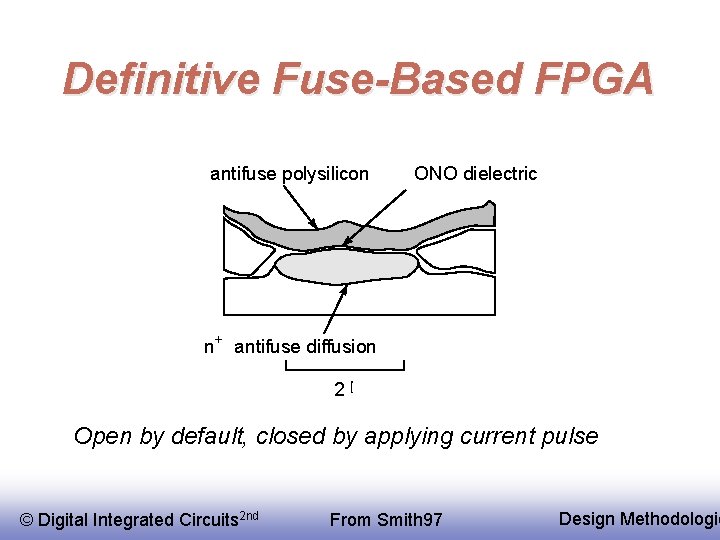

Definitive Fuse-Based FPGA antifuse polysilicon ONO dielectric n+ antifuse diffusion 2 l Open by default, closed by applying current pulse © Digital Integrated Circuits 2 nd From Smith 97 Design Methodologie

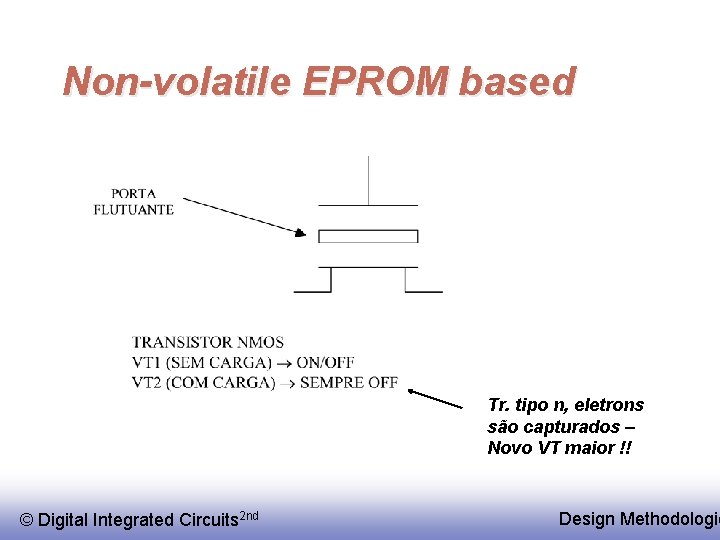

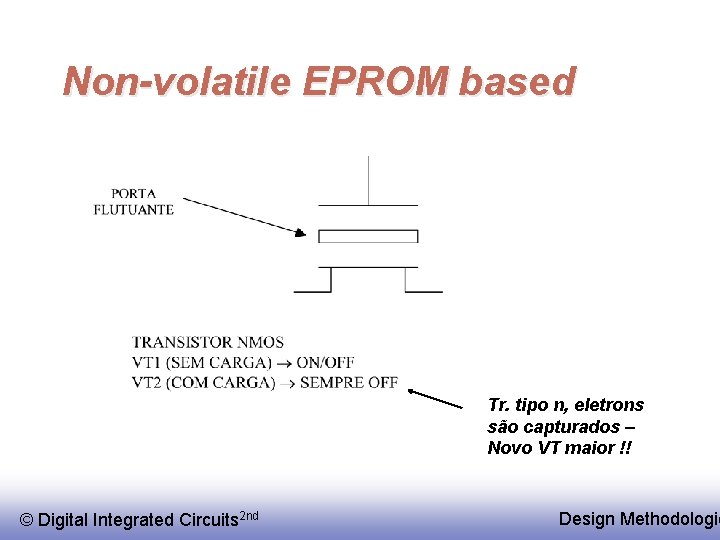

Non-volatile EPROM based Tr. tipo n, eletrons são capturados – Novo VT maior !! © Digital Integrated Circuits 2 nd Design Methodologie

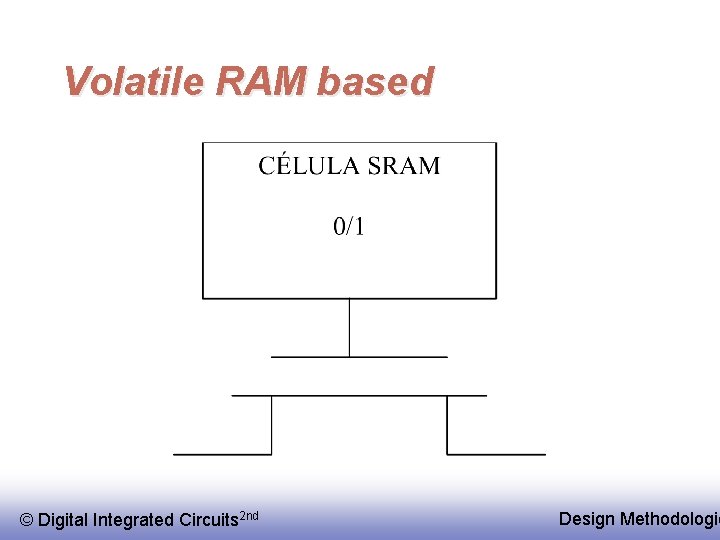

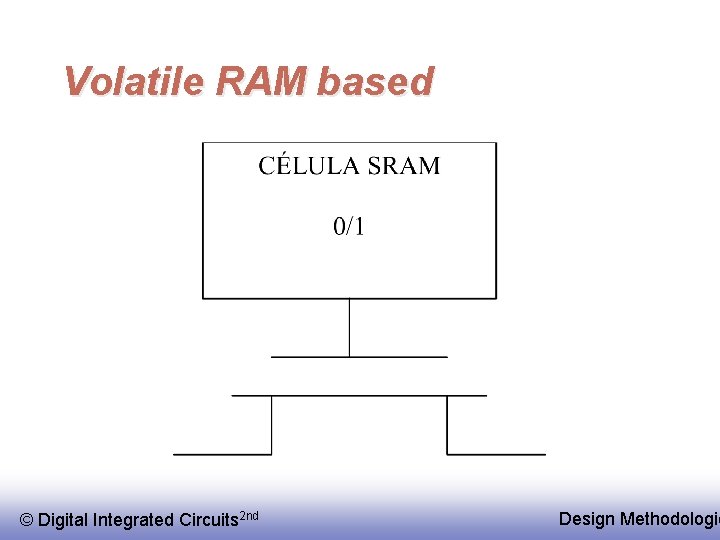

Volatile RAM based © Digital Integrated Circuits 2 nd Design Methodologie

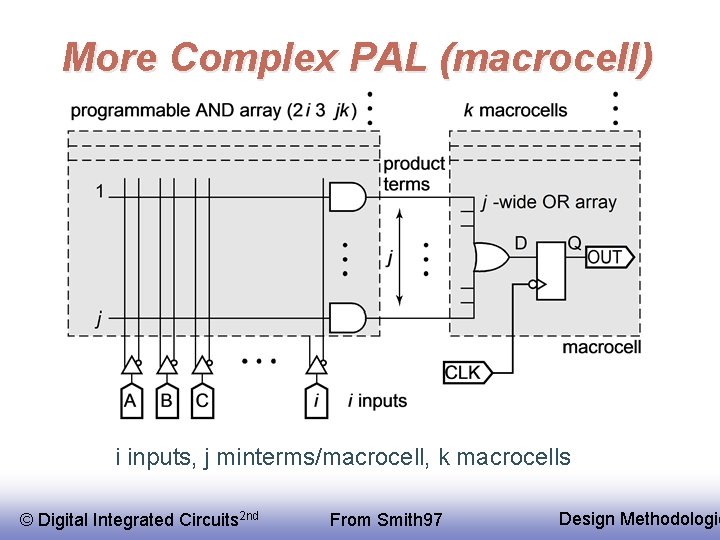

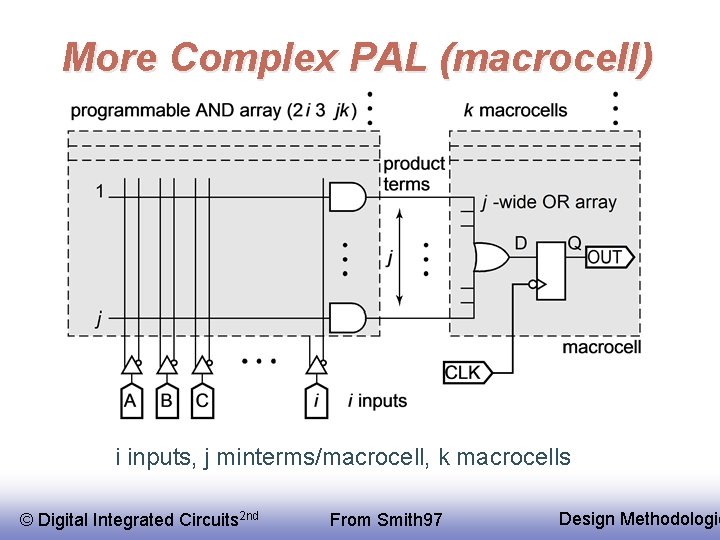

More Complex PAL (macrocell) i inputs, j minterms/macrocell, k macrocells © Digital Integrated Circuits 2 nd From Smith 97 Design Methodologie

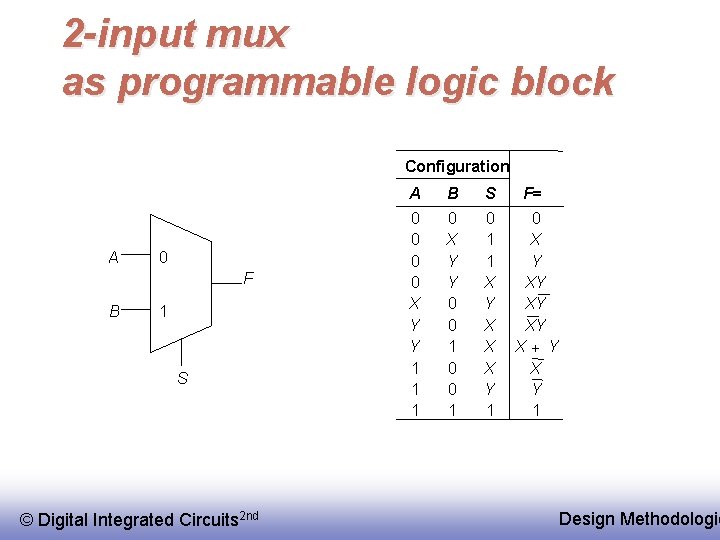

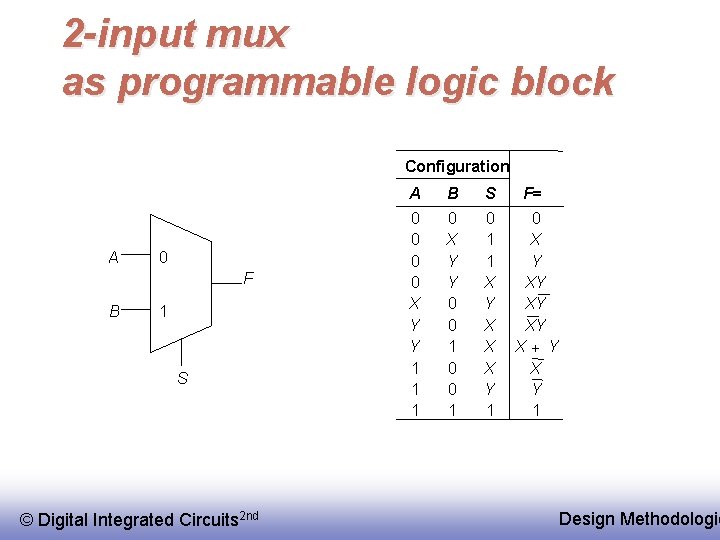

2 -input mux as programmable logic block Configuration A 0 F B 1 S © Digital Integrated Circuits 2 nd A B S F= 0 0 X Y Y 1 1 1 0 X Y Y 0 0 1 0 1 1 X Y X X X Y 1 0 X Y XY X+ Y X Y 1 Design Methodologie

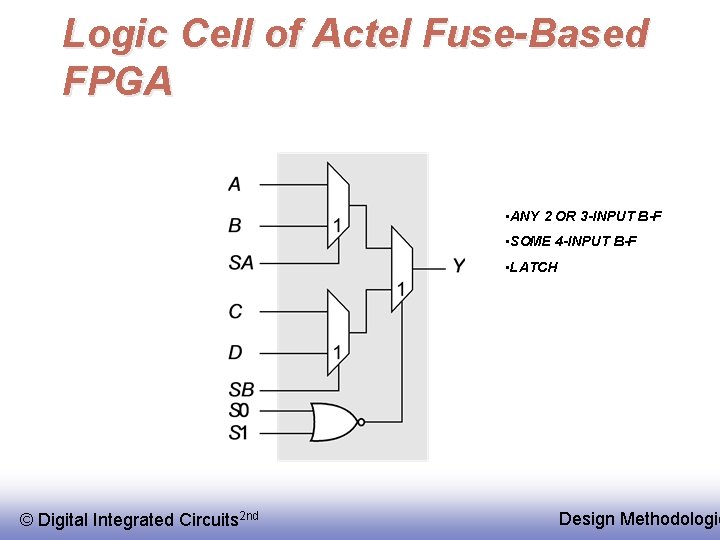

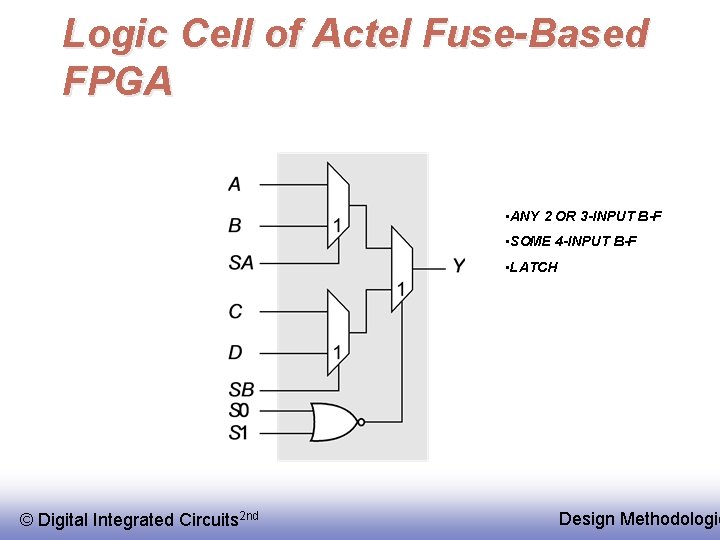

Logic Cell of Actel Fuse-Based FPGA • ANY 2 OR 3 -INPUT B-F • SOME 4 -INPUT B-F • LATCH © Digital Integrated Circuits 2 nd Design Methodologie

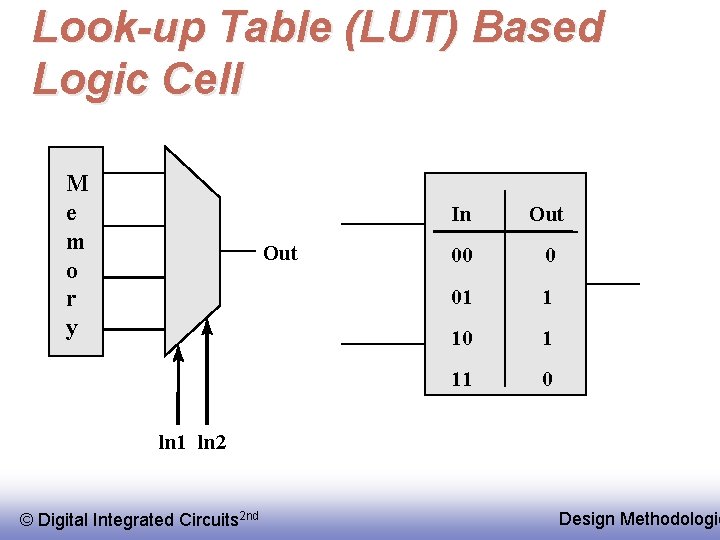

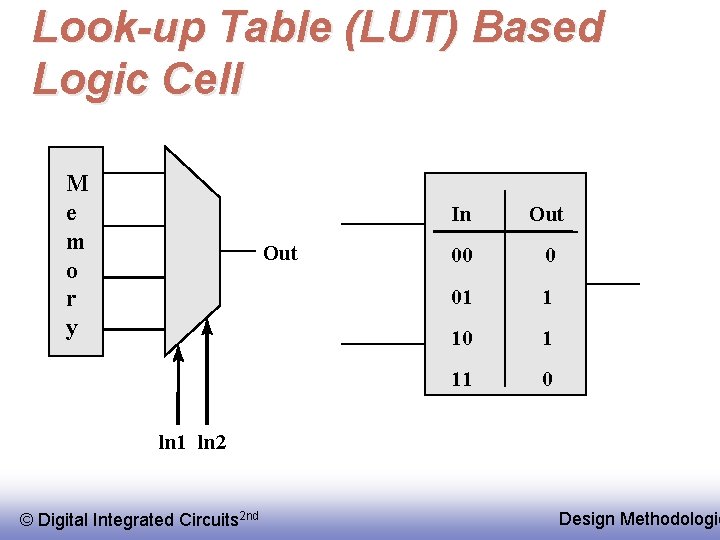

Look-up Table (LUT) Based Logic Cell M e m o r y Out In Out 00 0 01 1 10 1 11 0 ln 1 ln 2 © Digital Integrated Circuits 2 nd Design Methodologie

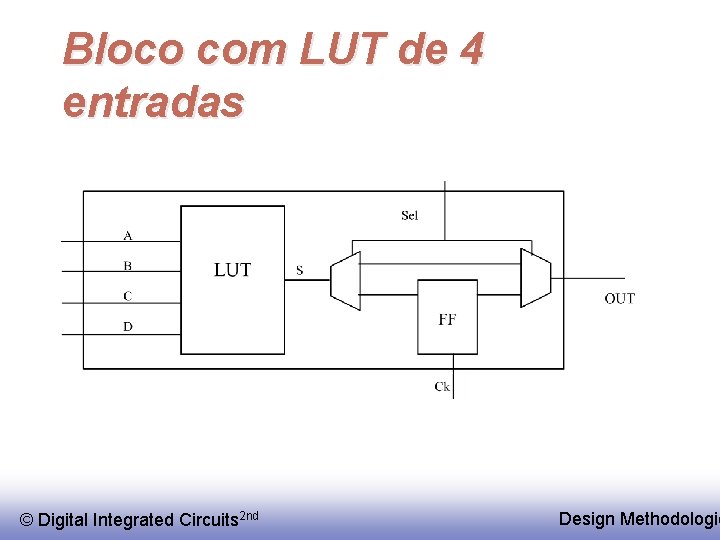

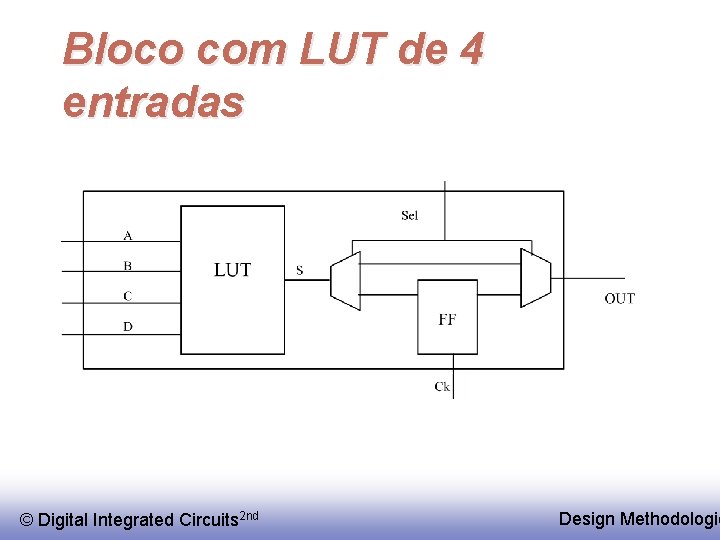

Bloco com LUT de 4 entradas © Digital Integrated Circuits 2 nd Design Methodologie

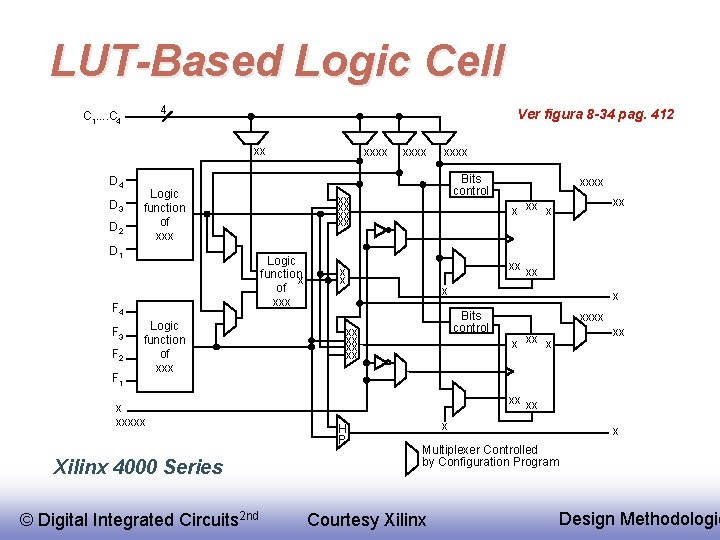

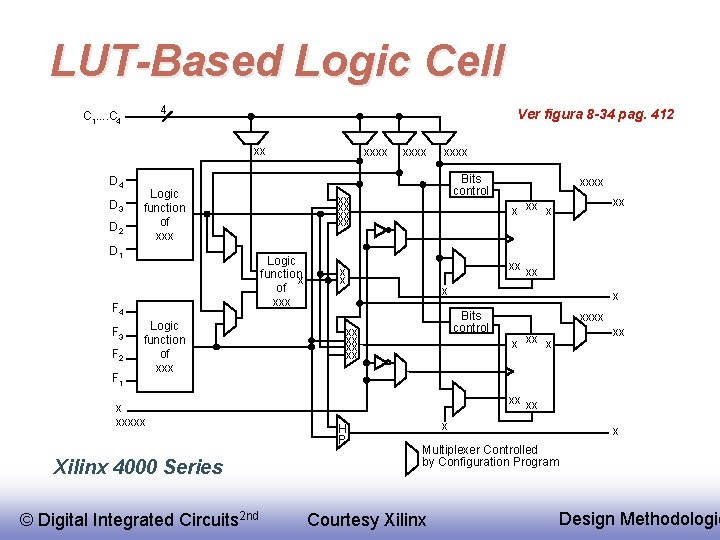

LUT-Based Logic Cell 4 C 1. . C 4 Ver figura 8 -34 pag. 412 xx D 4 D 3 D 2 Logic function of xxx D 1 F 3 F 2 F 1 Logic function of xxx x xxxxx Xilinx 4000 Series © Digital Integrated Circuits 2 nd xxxx Bits control xx xx Logic functionx of xxx F 4 xxxx xx x x Bits control xx xx xxxx xx xx H P x x Multiplexer Controlled by Configuration Program Courtesy Xilinx Design Methodologie

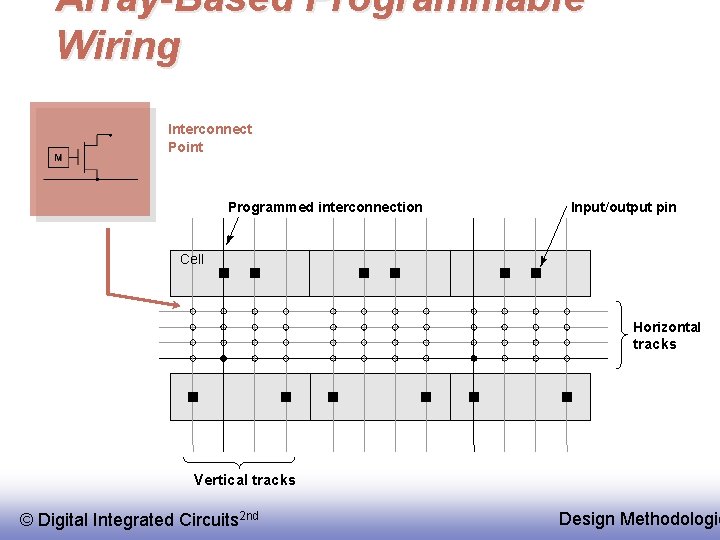

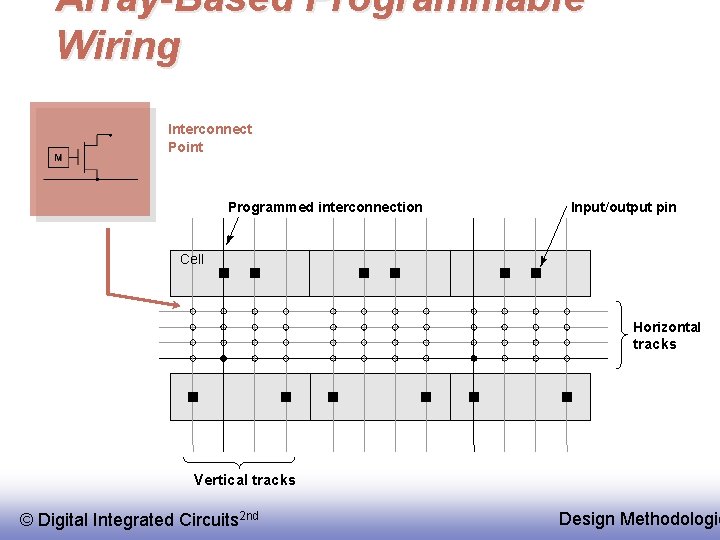

Array-Based Programmable Wiring Interconnect Point Programmed interconnection Input/output pin Cell Horizontal tracks Vertical tracks © Digital Integrated Circuits 2 nd Design Methodologie

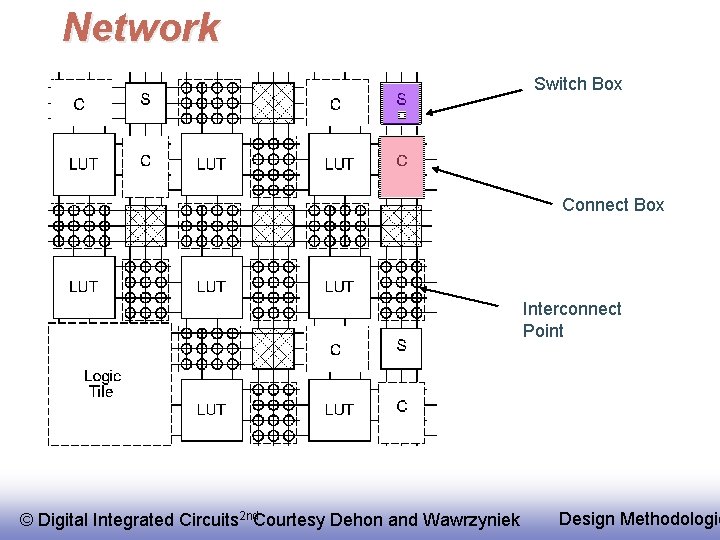

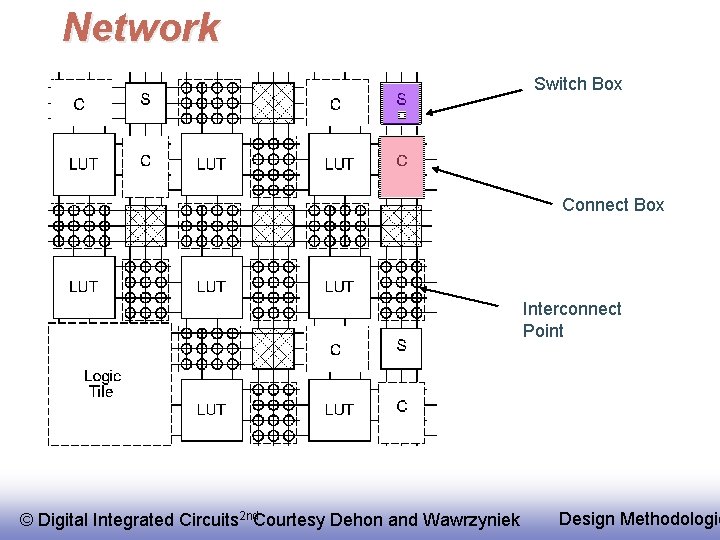

Network Switch Box Connect Box Interconnect Point © Digital Integrated Circuits 2 nd. Courtesy Dehon and Wawrzyniek Design Methodologie

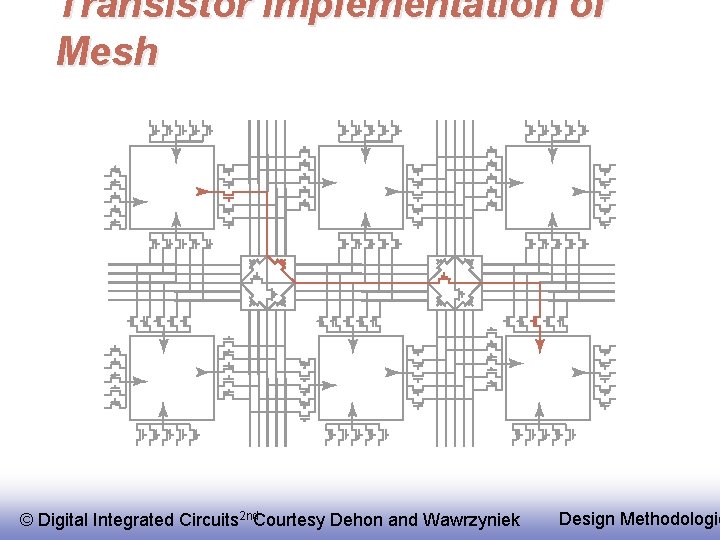

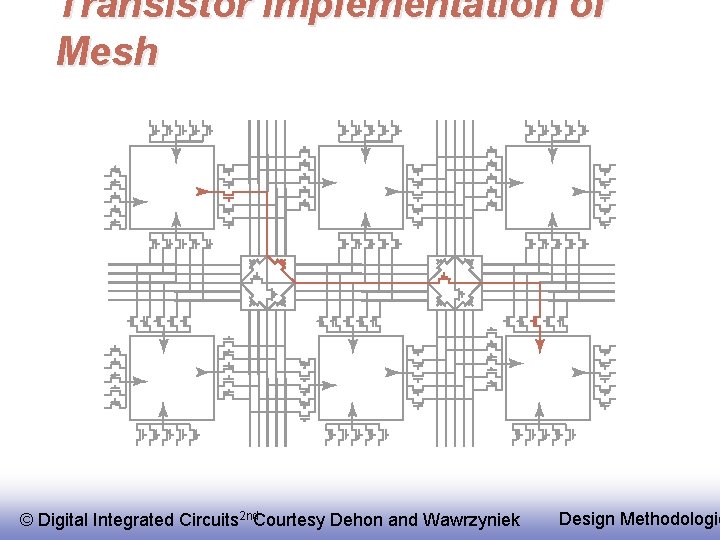

Transistor Implementation of Mesh © Digital Integrated Circuits 2 nd. Courtesy Dehon and Wawrzyniek Design Methodologie

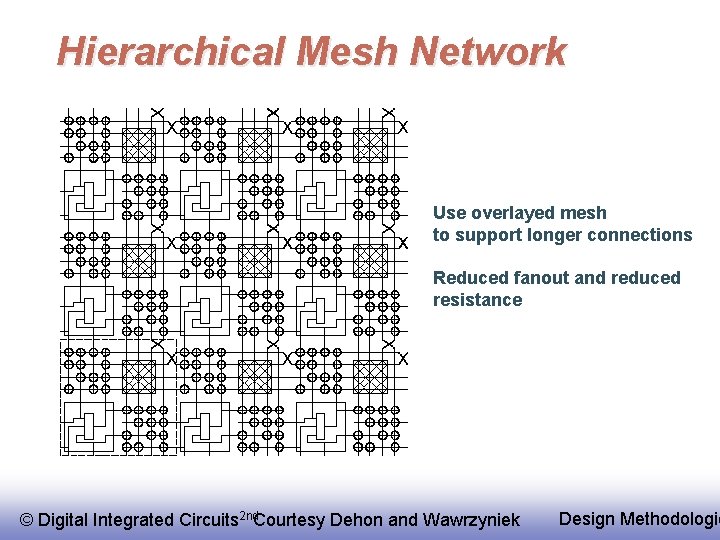

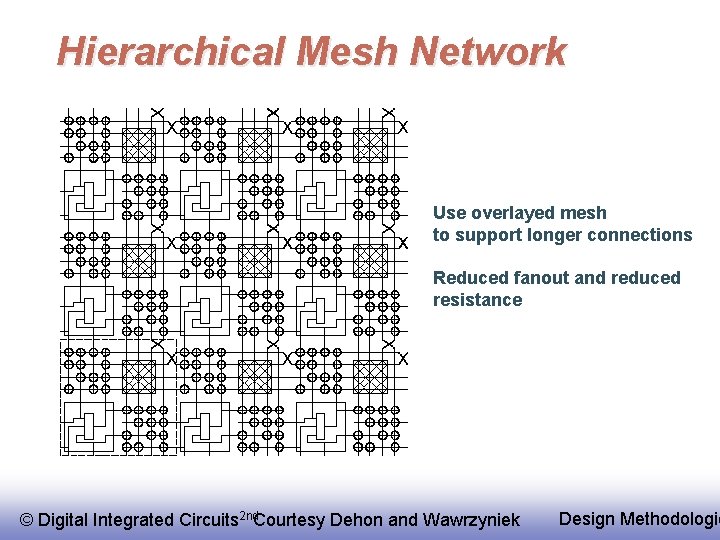

Hierarchical Mesh Network Use overlayed mesh to support longer connections Reduced fanout and reduced resistance © Digital Integrated Circuits 2 nd. Courtesy Dehon and Wawrzyniek Design Methodologie

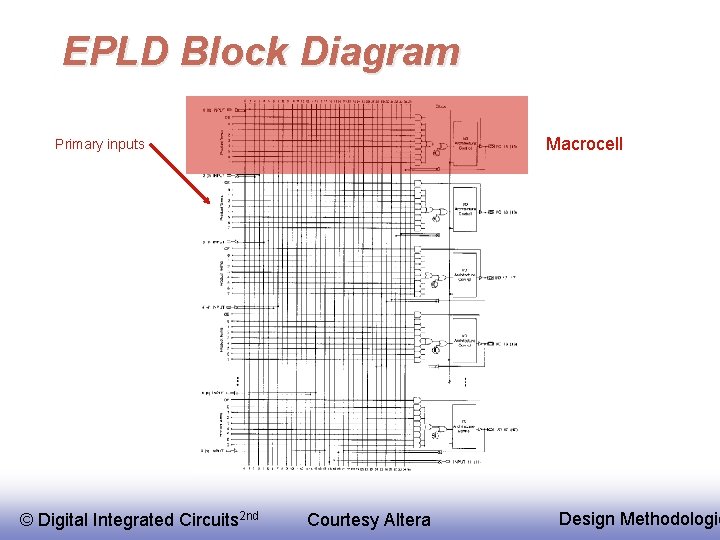

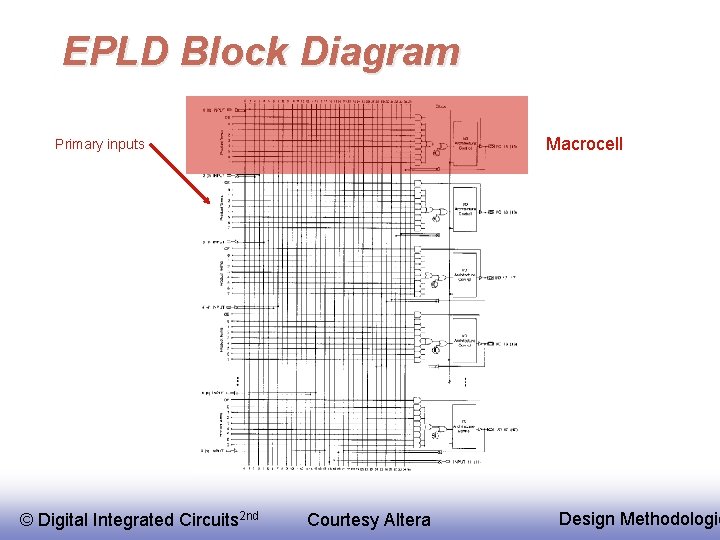

EPLD Block Diagram Macrocell Primary inputs © Digital Integrated Circuits 2 nd Courtesy Altera Design Methodologie

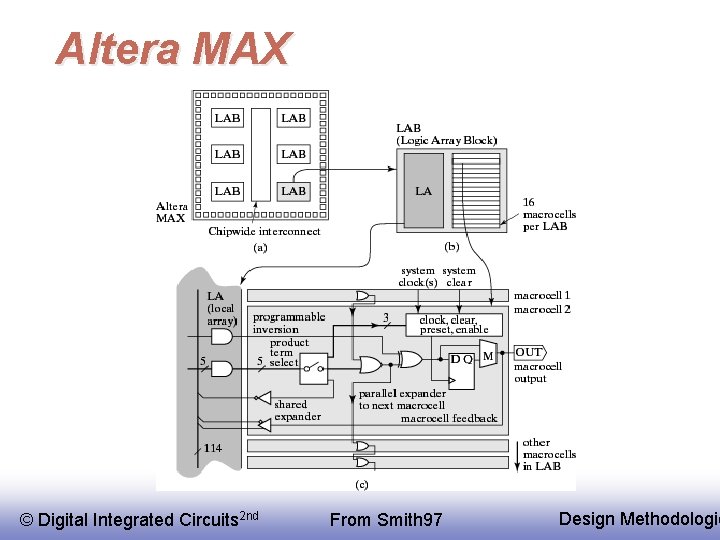

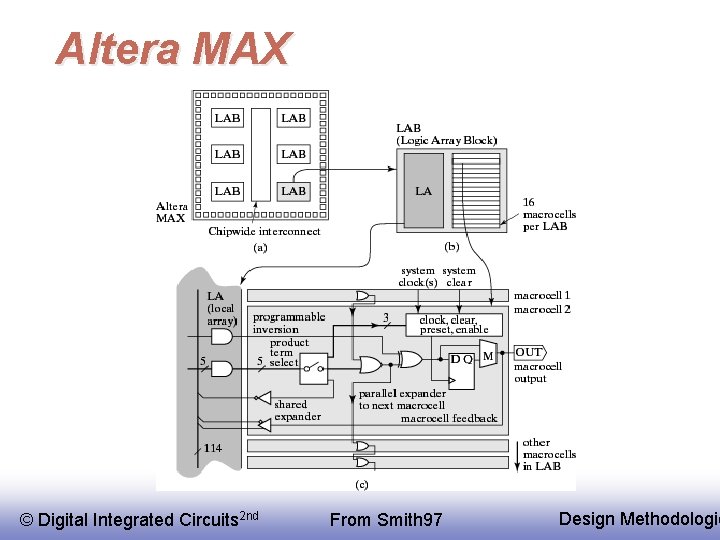

Altera MAX © Digital Integrated Circuits 2 nd From Smith 97 Design Methodologie

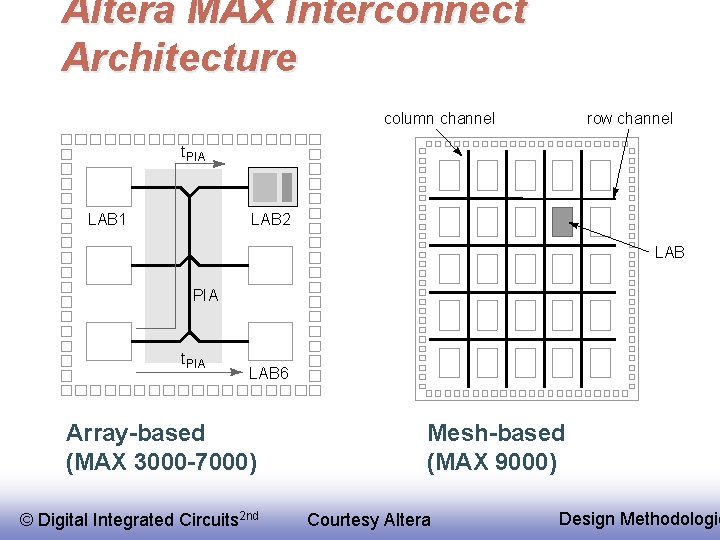

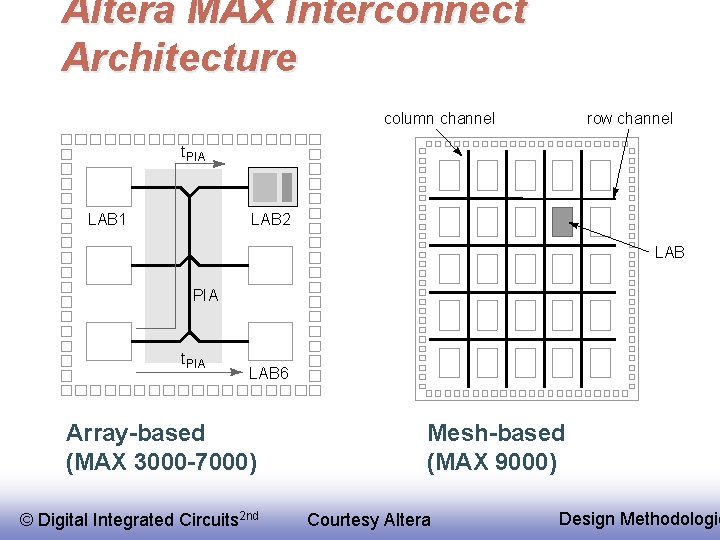

Altera MAX Interconnect Architecture column channel row channel t PIA LAB 1 LAB 2 LAB PIA t PIA LAB 6 Array-based (MAX 3000 -7000) © Digital Integrated Circuits 2 nd Mesh-based (MAX 9000) Courtesy Altera Design Methodologie

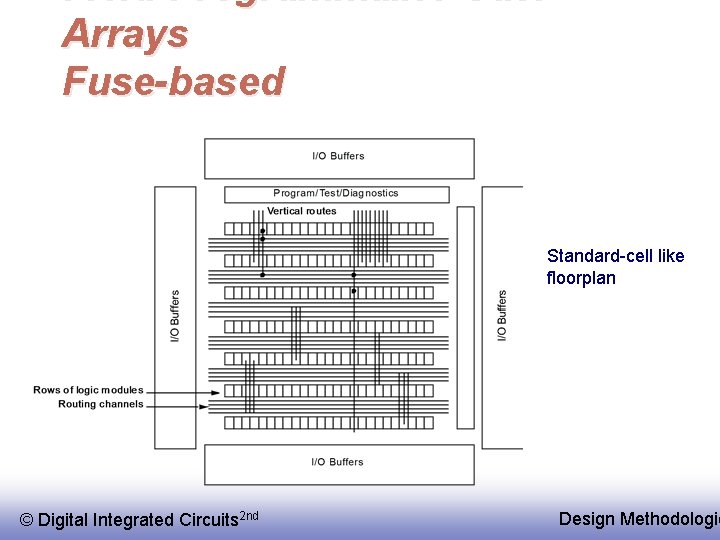

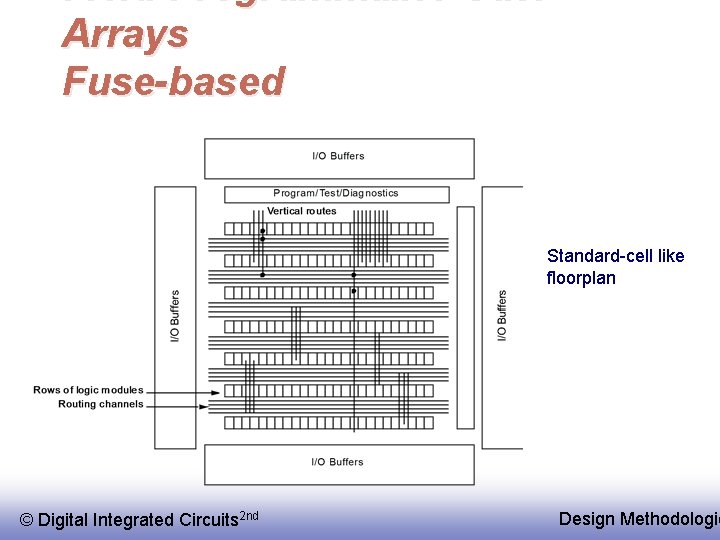

Field-Programmable Gate Arrays Fuse-based Standard-cell like floorplan © Digital Integrated Circuits 2 nd Design Methodologie

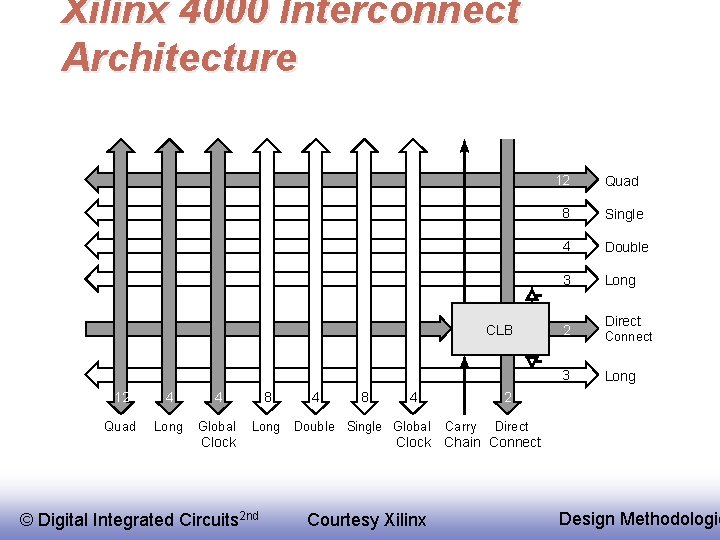

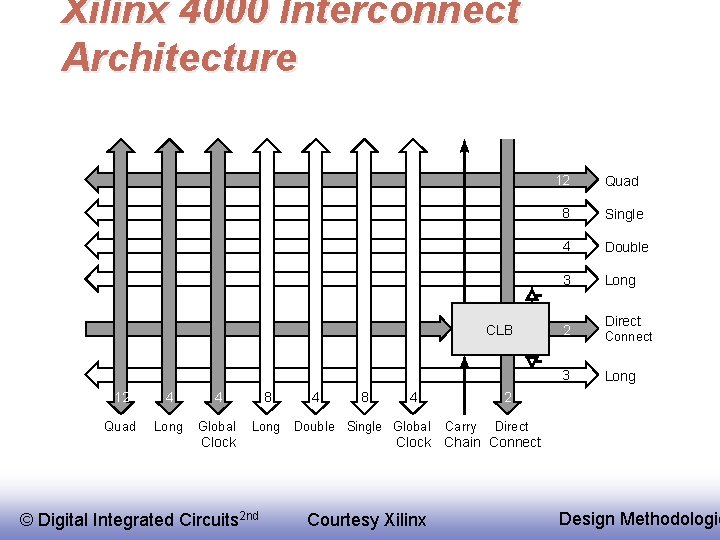

Xilinx 4000 Interconnect Architecture CLB 12 Quad 8 Single 4 Double 3 Long 2 3 12 4 4 8 Quad Long Global Long Clock © Digital Integrated Circuits 2 nd 4 8 4 Double Single Global Direct Connect Long 2 Carry Direct Clock Chain Connect Courtesy Xilinx Design Methodologie

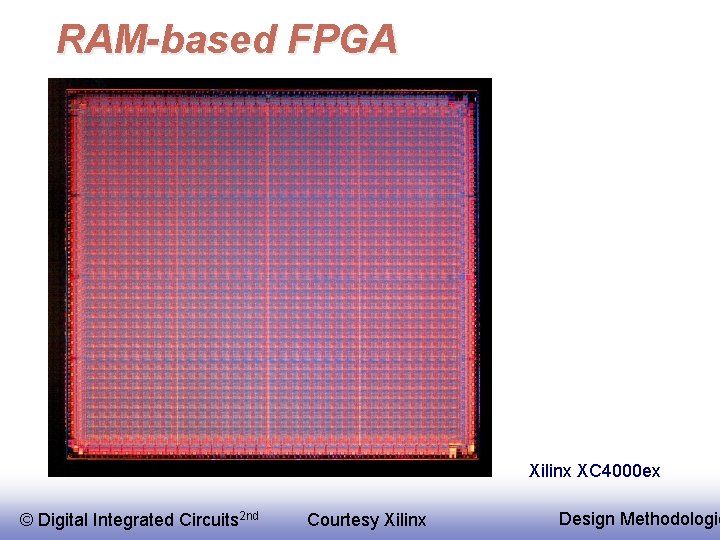

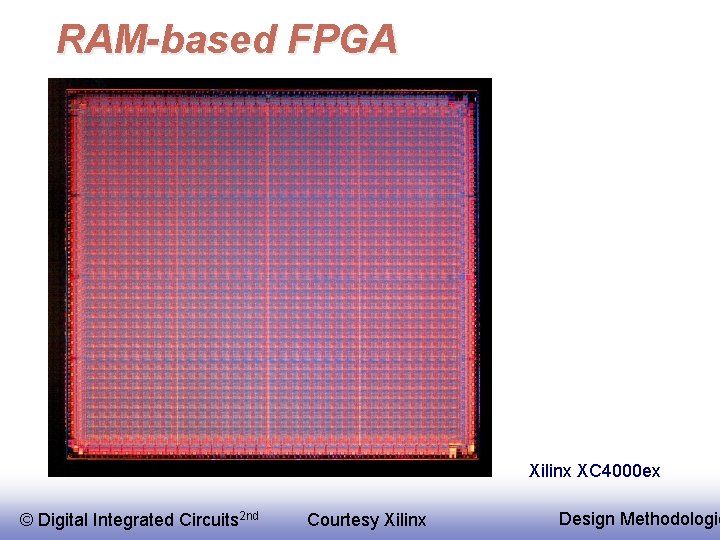

RAM-based FPGA Xilinx XC 4000 ex © Digital Integrated Circuits 2 nd Courtesy Xilinx Design Methodologie