Review Basic Digital Logic Systems Digital Design Review

Review Basic Digital Logic Systems Digital Design Review 1

Outline 1. 2. 3. 4. Number Systems / Binary Encoding Boolean Algebra Combinational Circuits Sequential Circuits Digital Design Review 2

1. Number Systems Digital Design Review 3

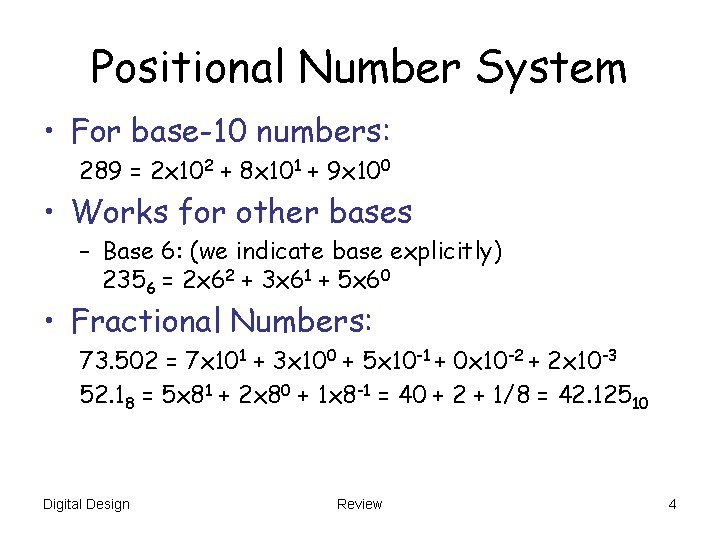

Positional Number System • For base-10 numbers: 289 = 2 x 102 + 8 x 101 + 9 x 100 • Works for other bases – Base 6: (we indicate base explicitly) 2356 = 2 x 62 + 3 x 61 + 5 x 60 • Fractional Numbers: 73. 502 = 7 x 101 + 3 x 100 + 5 x 10 -1 + 0 x 10 -2 + 2 x 10 -3 52. 18 = 5 x 81 + 2 x 80 + 1 x 8 -1 = 40 + 2 + 1/8 = 42. 12510 Digital Design Review 4

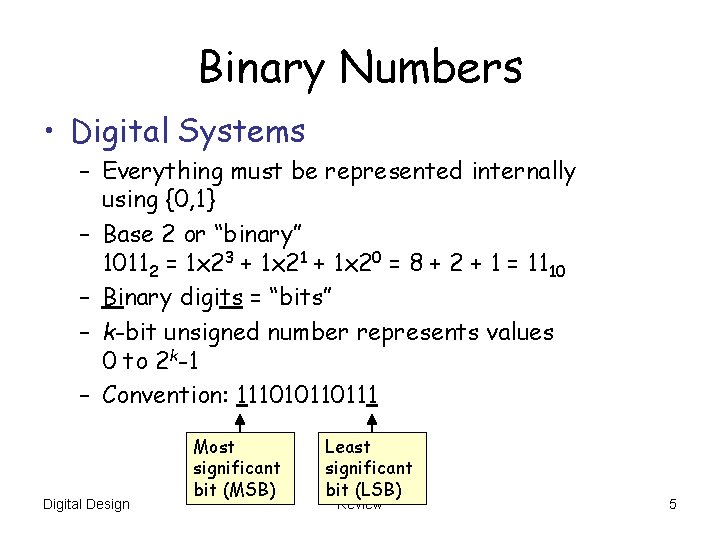

Binary Numbers • Digital Systems – Everything must be represented internally using {0, 1} – Base 2 or “binary” 10112 = 1 x 23 + 1 x 21 + 1 x 20 = 8 + 2 + 1 = 1110 – Binary digits = “bits” – k-bit unsigned number represents values 0 to 2 k-1 – Convention: 111010110111 Digital Design Most significant bit (MSB) Least significant bit (LSB) Review 5

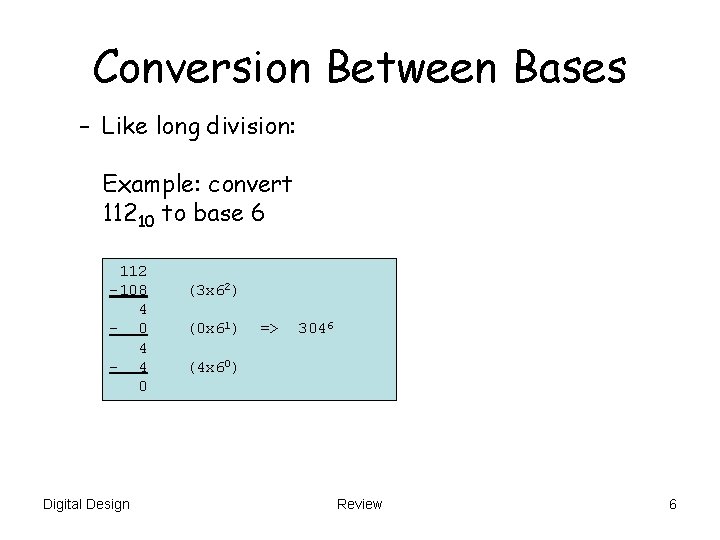

Conversion Between Bases – Like long division: Example: convert 11210 to base 6 112 -108 4 - 0 4 - 4 0 Digital Design (3 x 62) (0 x 61) => 3046 (4 x 60) Review 6

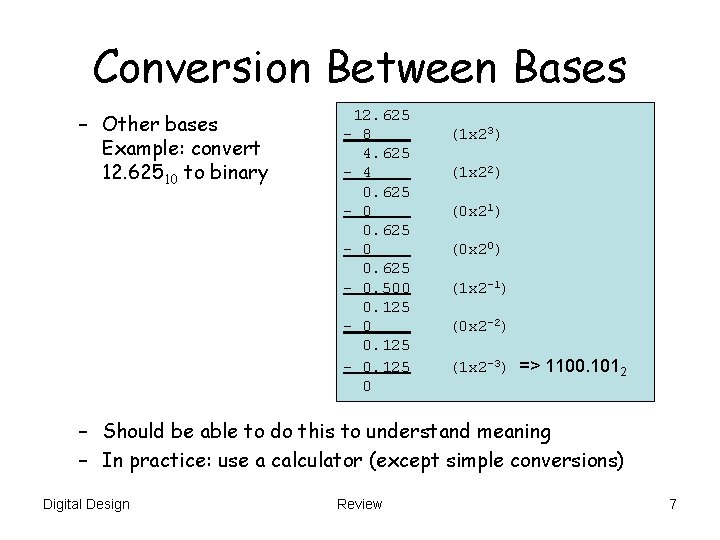

Conversion Between Bases – Other bases Example: convert 12. 62510 to binary 12. 625 - 8 4. 625 - 4 0. 625 - 0. 500 0. 125 - 0. 125 0 (1 x 23) (1 x 22) (0 x 21) (0 x 20) (1 x 2 -1) (0 x 2 -2) (1 x 2 -3) => 1100. 1012 – Should be able to do this to understand meaning – In practice: use a calculator (except simple conversions) Digital Design Review 7

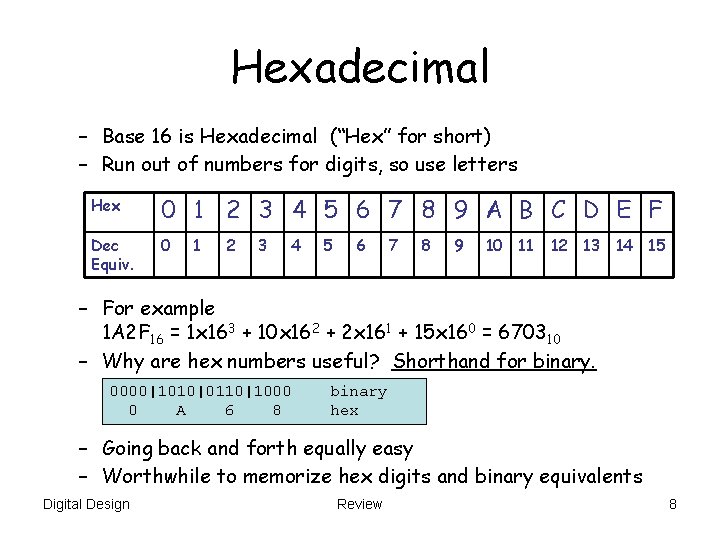

Hexadecimal – Base 16 is Hexadecimal (“Hex” for short) – Run out of numbers for digits, so use letters Hex 0 1 2 3 4 5 6 7 8 9 A B C D E F Dec Equiv. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 – For example 1 A 2 F 16 = 1 x 163 + 10 x 162 + 2 x 161 + 15 x 160 = 670310 – Why are hex numbers useful? Shorthand for binary. 0000|1010|0110|1000 0 A 6 8 binary hex – Going back and forth equally easy – Worthwhile to memorize hex digits and binary equivalents Digital Design Review 8

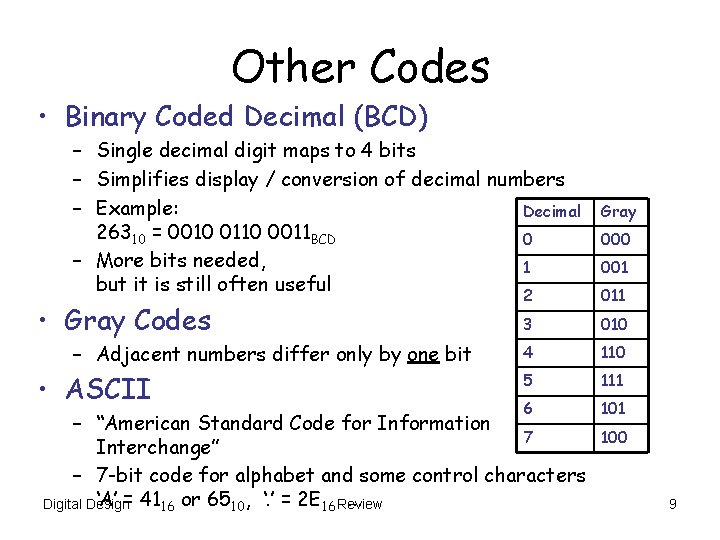

Other Codes • Binary Coded Decimal (BCD) – Single decimal digit maps to 4 bits – Simplifies display / conversion of decimal numbers – Example: Decimal 26310 = 0010 0110 0011 BCD 0 – More bits needed, 1 but it is still often useful 2 • Gray Codes – Adjacent numbers differ only by one bit • ASCII Gray 000 001 011 3 010 4 110 5 111 6 101 – “American Standard Code for Information 7 Interchange” – 7 -bit code for alphabet and some control characters ‘A’ = 4116 or 6510, ‘. ’ = 2 E 16 Review. . . Digital Design 100 9

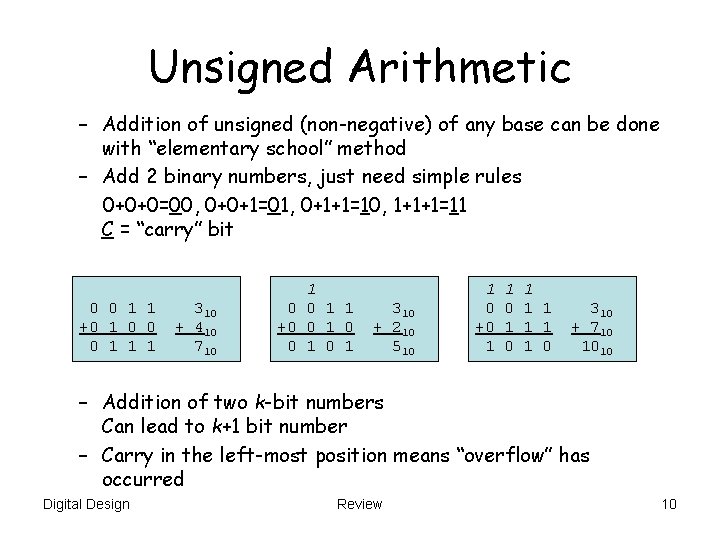

Unsigned Arithmetic – Addition of unsigned (non-negative) of any base can be done with “elementary school” method – Add 2 binary numbers, just need simple rules 0+0+0=00, 0+0+1=01, 0+1+1=10, 1+1+1=11 C = “carry” bit 0 0 1 1 +0 1 0 0 0 1 1 1 310 + 410 710 1 0 0 1 1 +0 0 1 0 1 310 + 210 510 1 0 +0 1 1 1 0 310 + 710 1010 – Addition of two k-bit numbers Can lead to k+1 bit number – Carry in the left-most position means “overflow” has occurred Digital Design Review 10

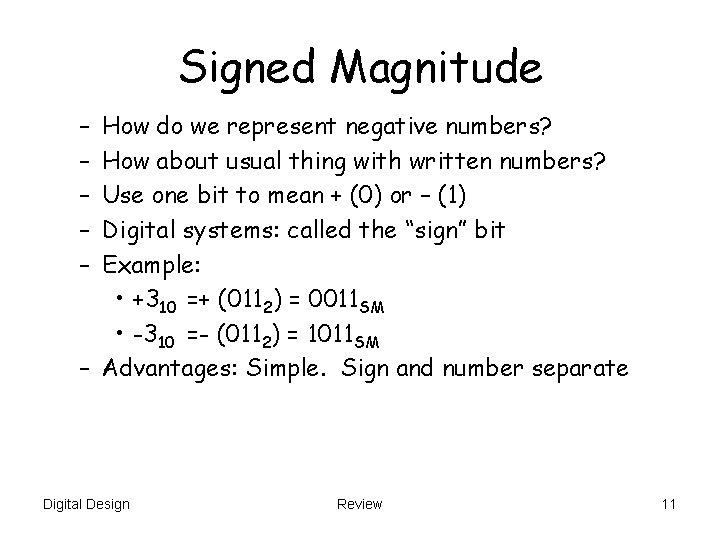

Signed Magnitude – – – How do we represent negative numbers? How about usual thing with written numbers? Use one bit to mean + (0) or – (1) Digital systems: called the “sign” bit Example: • +310 =+ (0112) = 0011 SM • -310 =- (0112) = 1011 SM – Advantages: Simple. Sign and number separate Digital Design Review 11

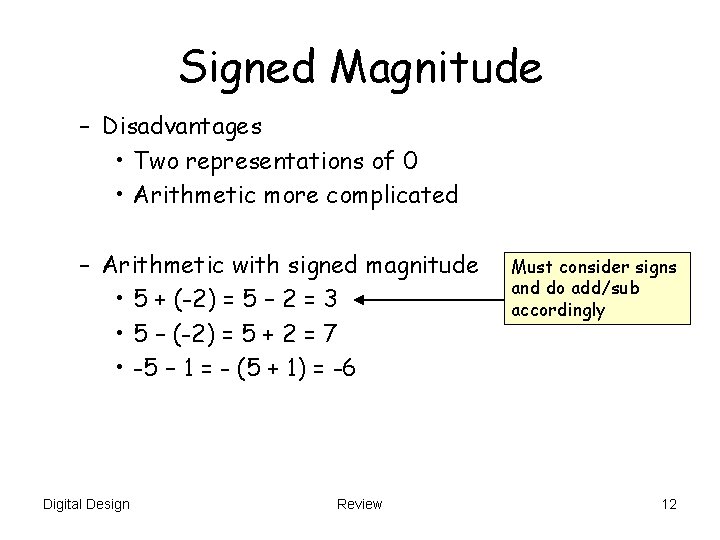

Signed Magnitude – Disadvantages • Two representations of 0 • Arithmetic more complicated – Arithmetic with signed magnitude • 5 + (-2) = 5 – 2 = 3 • 5 – (-2) = 5 + 2 = 7 • -5 – 1 = - (5 + 1) = -6 Digital Design Review Must consider signs and do add/sub accordingly 12

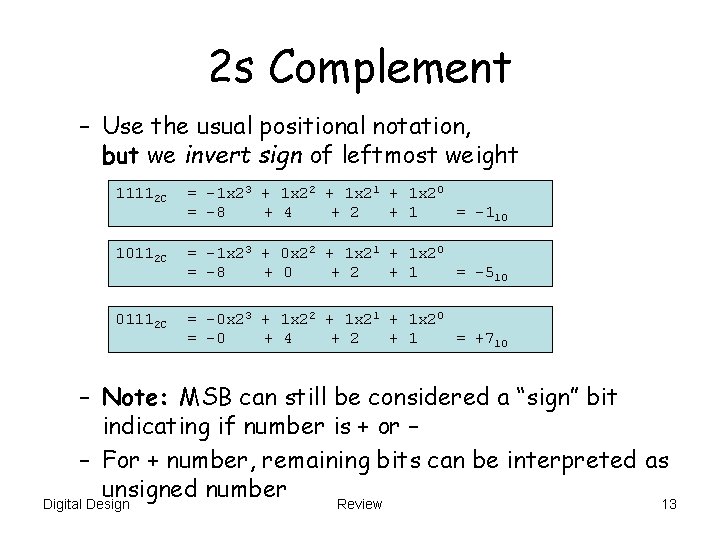

2 s Complement – Use the usual positional notation, but we invert sign of leftmost weight 11112 C = -1 x 23 + 1 x 22 + 1 x 21 + 1 x 20 = -8 + 4 + 2 + 1 = -110 10112 C = -1 x 23 + 0 x 22 + 1 x 21 + 1 x 20 = -8 + 0 + 2 + 1 = -510 01112 C = -0 x 23 + 1 x 22 + 1 x 21 + 1 x 20 = -0 + 4 + 2 + 1 = +710 – Note: MSB can still be considered a “sign” bit indicating if number is + or – – For + number, remaining bits can be interpreted as unsigned number Digital Design Review 13

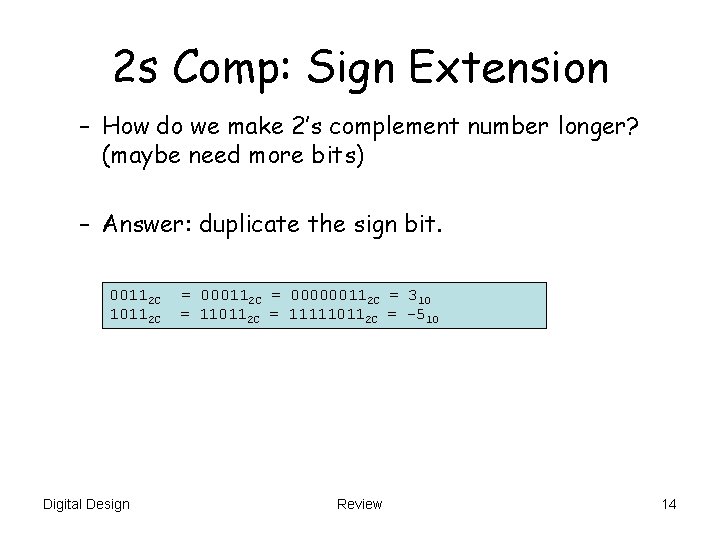

2 s Comp: Sign Extension – How do we make 2’s complement number longer? (maybe need more bits) – Answer: duplicate the sign bit. 00112 C 10112 C Digital Design = 000112 C = 000000112 C = 310 = 110112 C = 111110112 C = -510 Review 14

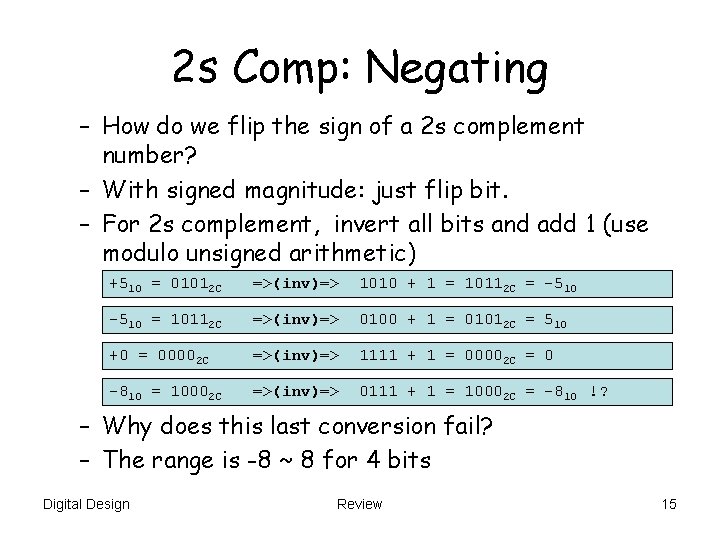

2 s Comp: Negating – How do we flip the sign of a 2 s complement number? – With signed magnitude: just flip bit. – For 2 s complement, invert all bits and add 1 (use modulo unsigned arithmetic) +510 = 01012 C =>(inv)=> 1010 + 1 = 10112 C = -510 = 10112 C =>(inv)=> 0100 + 1 = 01012 C = 510 +0 = 00002 C =>(inv)=> 1111 + 1 = 00002 C = 0 -810 = 10002 C =>(inv)=> 0111 + 1 = 10002 C = -810 !? – Why does this last conversion fail? – The range is -8 ~ 8 for 4 bits Digital Design Review 15

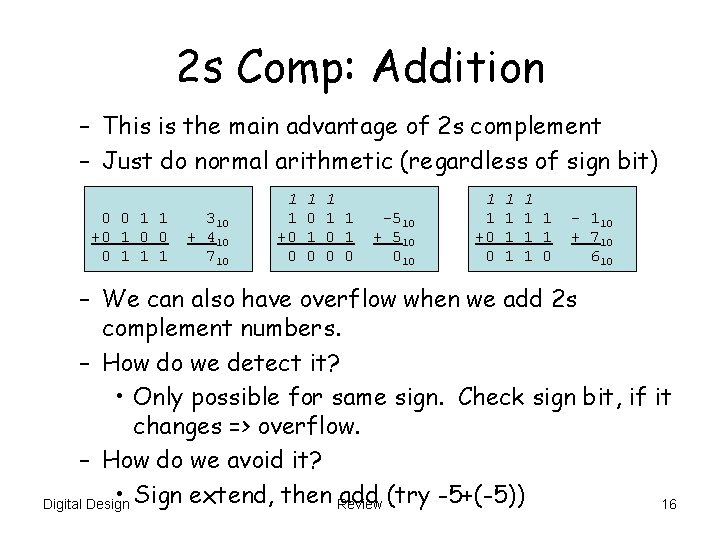

2 s Comp: Addition – This is the main advantage of 2 s complement – Just do normal arithmetic (regardless of sign bit) 0 0 1 1 +0 1 0 0 0 1 1 1 310 + 410 710 1 1 +0 0 1 0 1 1 1 0 0 -510 + 510 010 1 1 +0 0 1 1 1 1 1 0 - 110 + 710 610 – We can also have overflow when we add 2 s complement numbers. – How do we detect it? • Only possible for same sign. Check sign bit, if it changes => overflow. – How do we avoid it? • Sign extend, then Review add (try -5+(-5)) Digital Design 16

2. Boolean Algebra Digital Design Review 17

Boolean Algebra – Named after George Boole in 19 th century – Map: TRUE 1, FALSE 0 – Operators: AND a·b or just ab OR a+b NOT a’ or a – De. Morgan’s (DM) Rules • (AB)’ = A’ + B’ • (A+B)’ = A’B’ Easily proven using a truth table. . . Digital Design Review 18

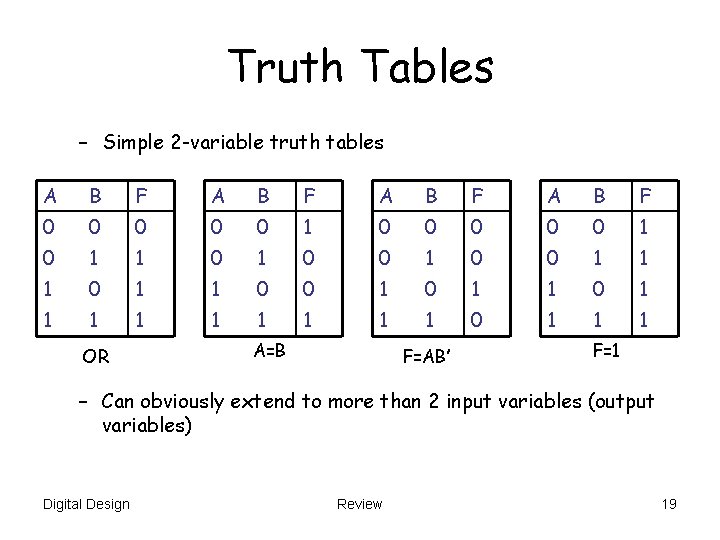

Truth Tables – Simple 2 -variable truth tables A B F 0 0 0 0 0 1 0 1 1 0 0 1 1 1 0 0 1 1 1 1 1 0 1 1 1 OR A=B F=AB’ F=1 – Can obviously extend to more than 2 input variables (output variables) Digital Design Review 19

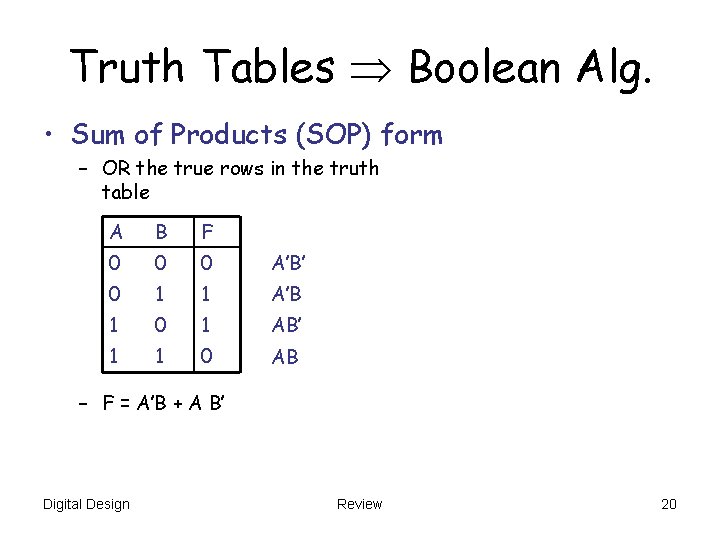

Truth Tables Boolean Alg. • Sum of Products (SOP) form – OR the true rows in the truth table A B F 0 0 0 A’B’ 0 1 1 A’B 1 0 1 AB’ 1 1 0 AB – F = A’B + A B’ Digital Design Review 20

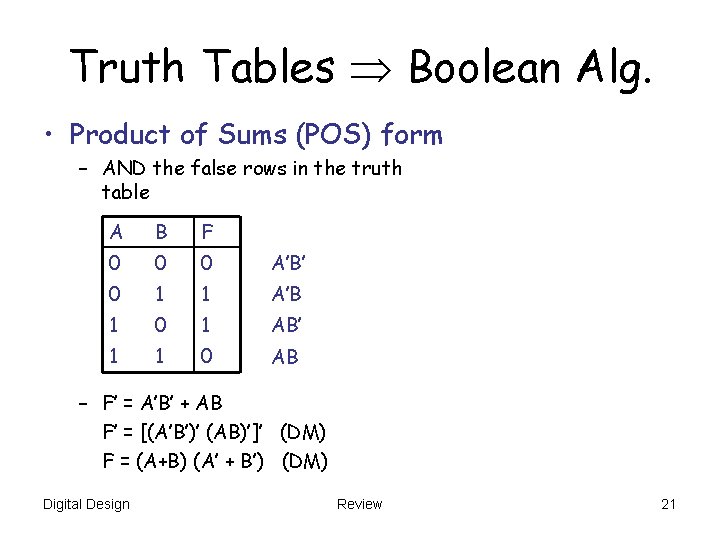

Truth Tables Boolean Alg. • Product of Sums (POS) form – AND the false rows in the truth table A B F 0 0 0 A’B’ 0 1 1 A’B 1 0 1 AB’ 1 1 0 AB – F’ = A’B’ + AB F’ = [(A’B’)’ (AB)’]’ (DM) F = (A+B) (A’ + B’) (DM) Digital Design Review 21

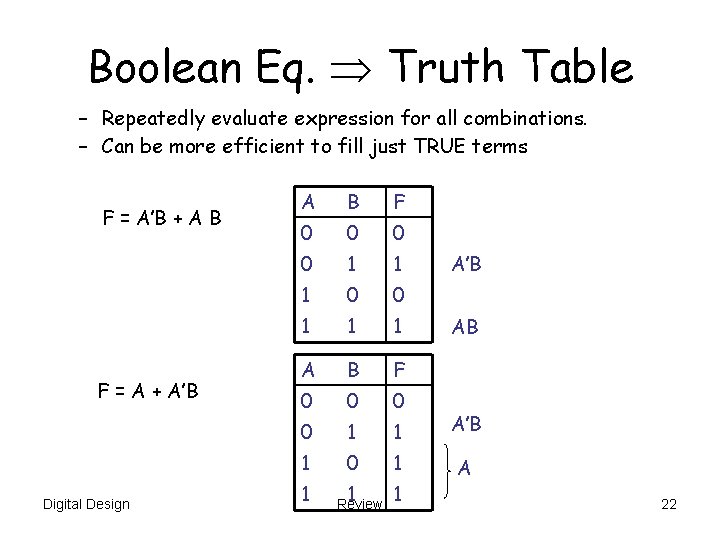

Boolean Eq. Truth Table – Repeatedly evaluate expression for all combinations. – Can be more efficient to fill just TRUE terms F = A’B + A B F = A + A’B Digital Design A B F 0 0 1 1 1 A B F 0 0 1 1 A’B 1 0 1 1 1 A 1 Review A’B AB 22

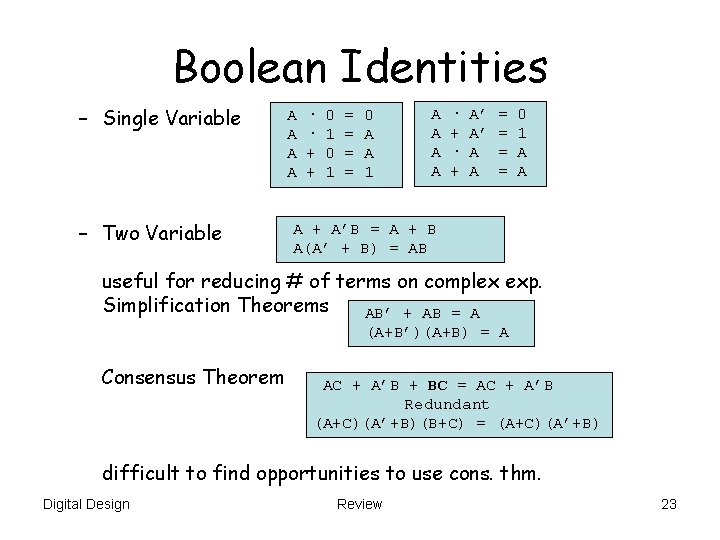

Boolean Identities – Single Variable – Two Variable A A · · + + 0 1 = = 0 A A 1 A A · + A’ A’ A A = = 0 1 A A A + A’B = A + B A(A’ + B) = AB useful for reducing # of terms on complex exp. Simplification Theorems AB’ + AB = A (A+B’)(A+B) = A Consensus Theorem AC + A’B + BC = AC + A’B Redundant (A+C)(A’+B)(B+C) = (A+C)(A’+B) difficult to find opportunities to use cons. thm. Digital Design Review 23

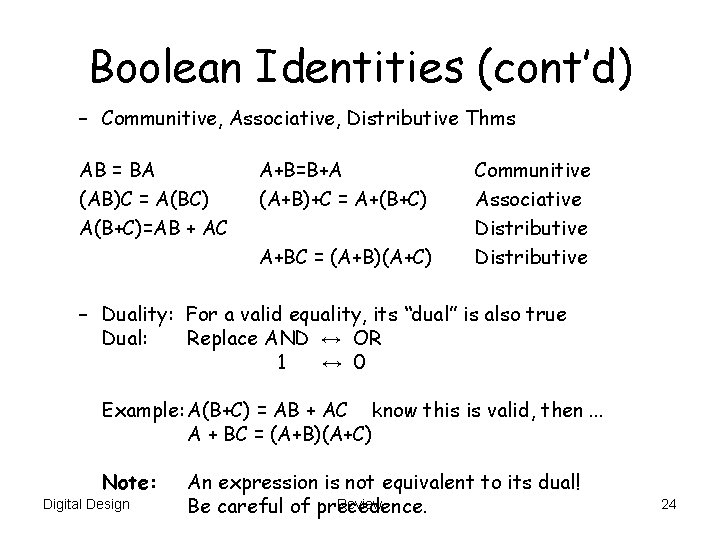

Boolean Identities (cont’d) – Communitive, Associative, Distributive Thms AB = BA (AB)C = A(BC) A(B+C)=AB + AC A+B=B+A (A+B)+C = A+(B+C) A+BC = (A+B)(A+C) Communitive Associative Distributive – Duality: For a valid equality, its “dual” is also true Dual: Replace AND ↔ OR 1 ↔ 0 Example: A(B+C) = AB + AC know this is valid, then. . . A + BC = (A+B)(A+C) Note: Digital Design An expression is not equivalent to its dual! Review Be careful of precedence. 24

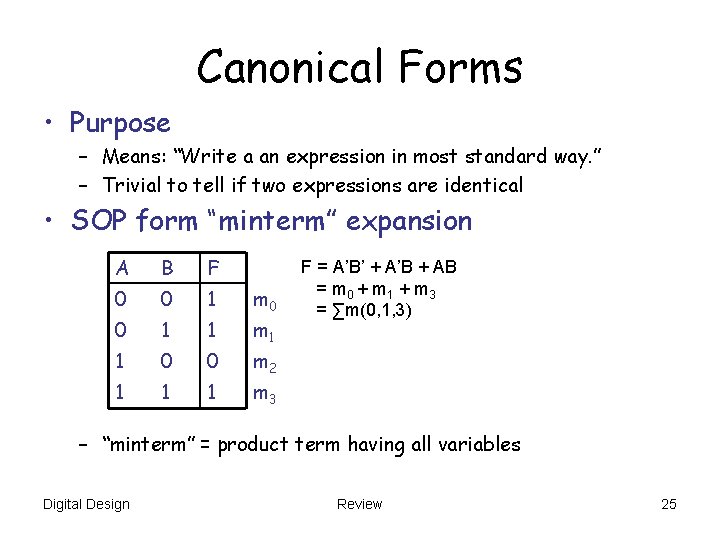

Canonical Forms • Purpose – Means: “Write a an expression in most standard way. ” – Trivial to tell if two expressions are identical • SOP form “minterm” expansion A B F 0 0 1 m 0 0 1 1 m 1 1 0 0 m 2 1 1 1 m 3 F = A’B’ + A’B + AB = m 0 + m 1 + m 3 = ∑m(0, 1, 3) – “minterm” = product term having all variables Digital Design Review 25

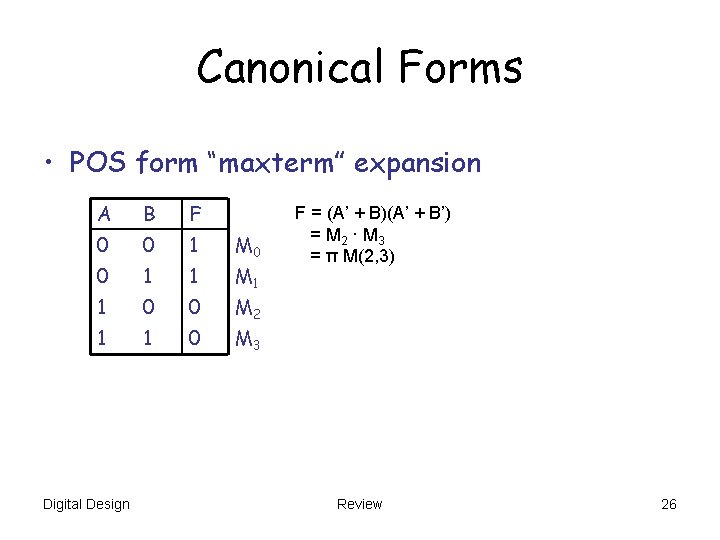

Canonical Forms • POS form “maxterm” expansion A B F 0 0 1 M 0 0 1 1 M 1 1 0 0 M 2 1 1 0 M 3 Digital Design F = (A’ + B)(A’ + B’) = M 2 · M 3 = π M(2, 3) Review 26

Proving Boolean Expressions • Methods – – Truth table Minterm/maxterm expansion (same terms? ) Manipulate one side to = other (identities) Manipulate both sides with identical operations Digital Design Review 27

Boolean Minimization – Make expression as “simple” as possible (low number of terms) • AB’ = AB = A(B’ +B) = A· 1 = A – Less complicated expression Fewer gates, less area, runs faster – Attempt to find minimal cost solution – What is minimal representation? Depends on technology and contraints. Digital Design Review 28

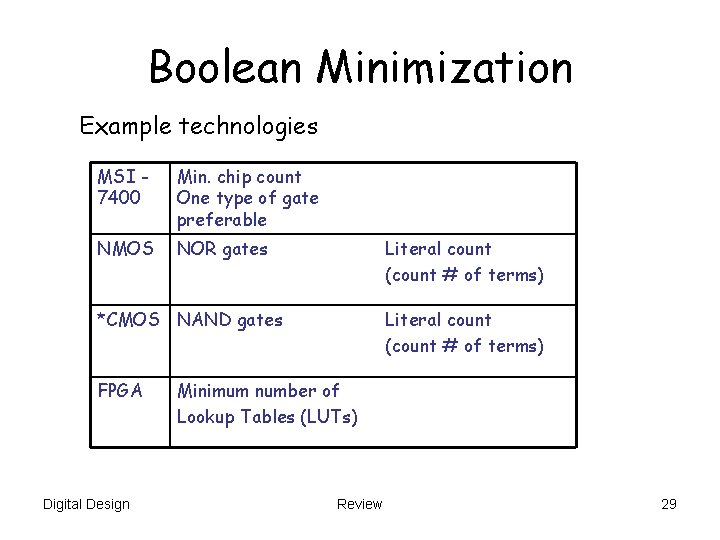

Boolean Minimization Example technologies MSI 7400 Min. chip count One type of gate preferable NMOS NOR gates Literal count (count # of terms) *CMOS NAND gates FPGA Digital Design Literal count (count # of terms) Minimum number of Lookup Tables (LUTs) Review 29

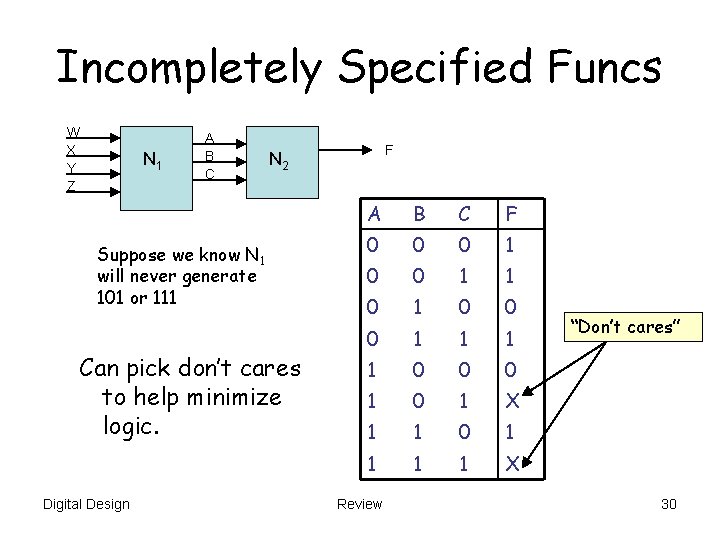

Incompletely Specified Funcs W X Y Z N 1 A B C Suppose we know N 1 will never generate 101 or 111 Can pick don’t cares to help minimize logic. Digital Design F N 2 A B C F 0 0 0 1 1 0 0 0 1 X 1 1 0 1 1 X Review “Don’t cares” 30

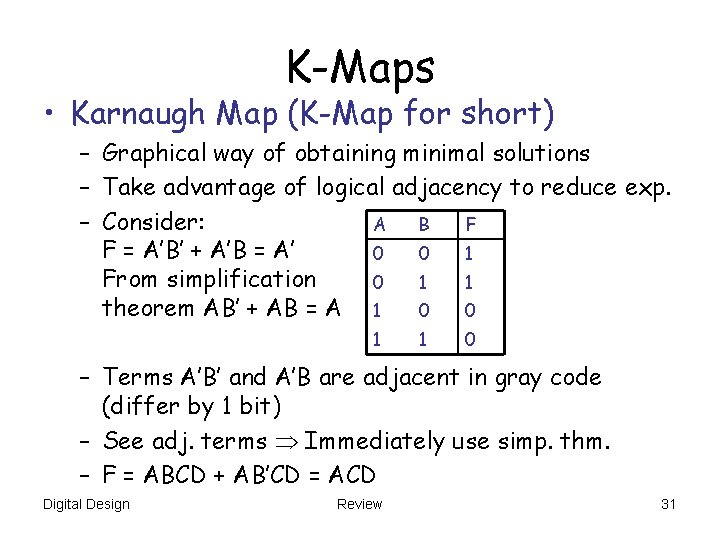

K-Maps • Karnaugh Map (K-Map for short) – Graphical way of obtaining minimal solutions – Take advantage of logical adjacency to reduce exp. – Consider: A B F F = A’B’ + A’B = A’ 0 0 1 From simplification 0 1 1 theorem AB’ + AB = A 1 0 0 1 1 0 – Terms A’B’ and A’B are adjacent in gray code (differ by 1 bit) – See adj. terms Immediately use simp. thm. – F = ABCD + AB’CD = ACD Digital Design Review 31

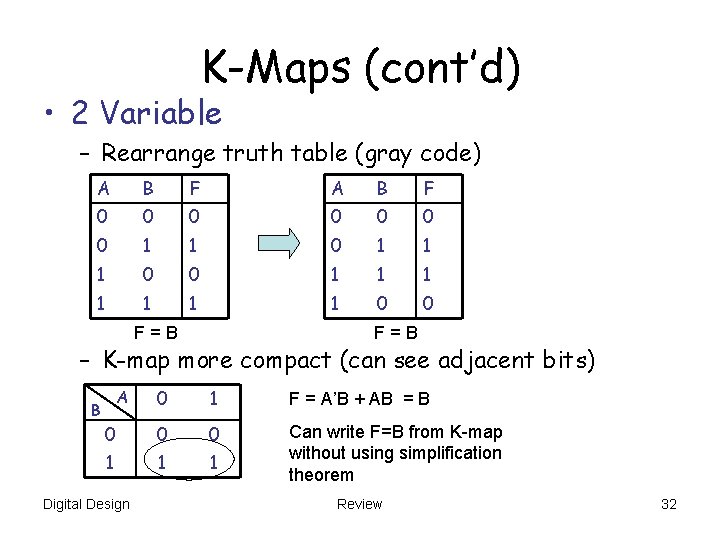

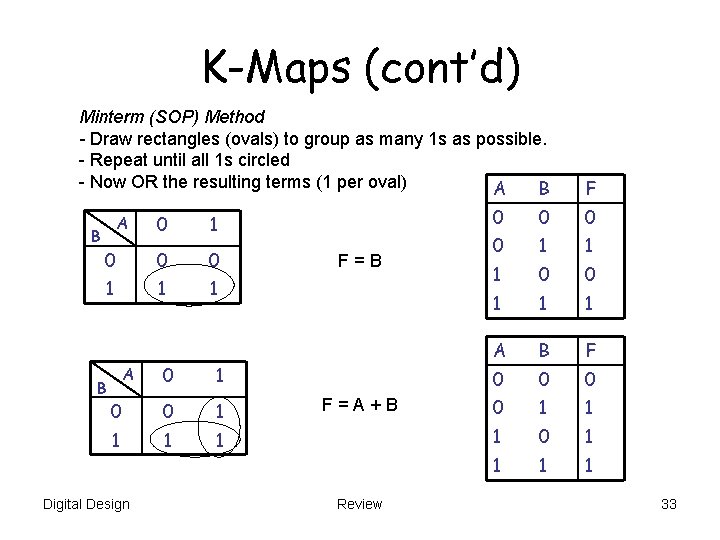

K-Maps (cont’d) • 2 Variable – Rearrange truth table (gray code) A B F 0 0 0 0 1 1 1 1 0 0 F=B – K-map more compact (can see adjacent bits) B 0 1 F = A’B + AB = B 0 0 0 1 1 1 Can write F=B from K-map without using simplification theorem A Digital Design Review 32

K-Maps (cont’d) Minterm (SOP) Method - Draw rectangles (ovals) to group as many 1 s as possible. - Repeat until all 1 s circled - Now OR the resulting terms (1 per oval) A B B 0 1 0 0 0 1 1 1 A B 0 1 0 0 1 1 A Digital Design F=B F=A+B Review F 0 0 1 1 1 A B F 0 0 1 1 1 0 1 1 33

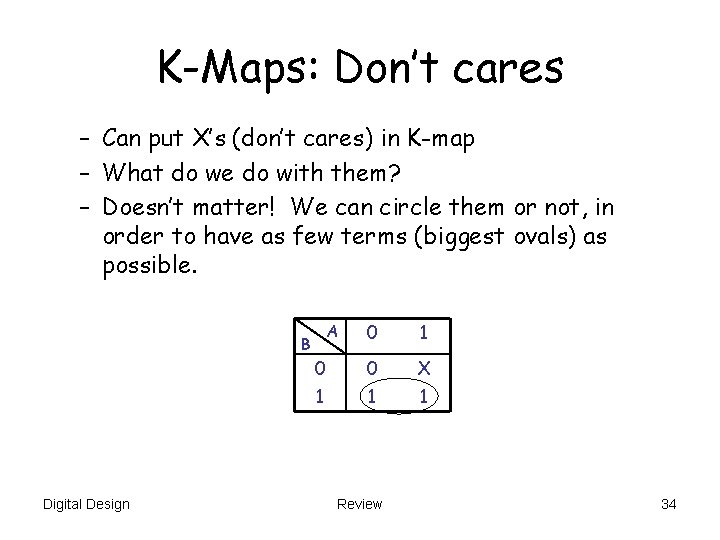

K-Maps: Don’t cares – Can put X’s (don’t cares) in K-map – What do we do with them? – Doesn’t matter! We can circle them or not, in order to have as few terms (biggest ovals) as possible. B Digital Design 0 1 0 0 X 1 1 1 A Review 34

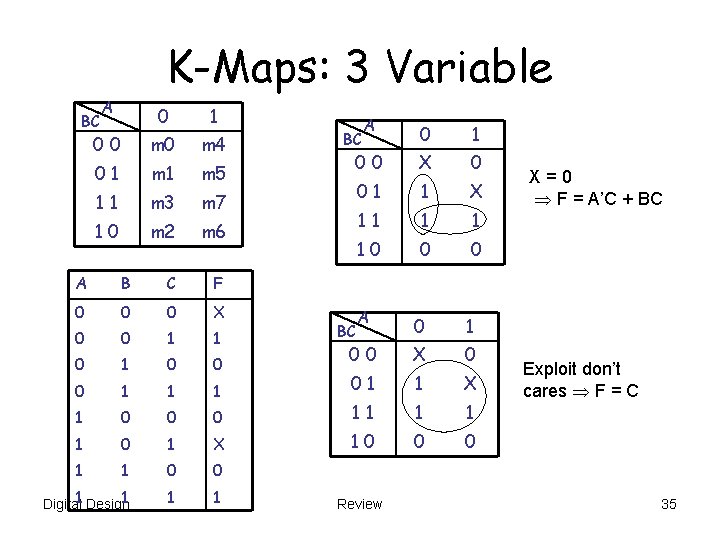

K-Maps: 3 Variable A 0 1 00 m 4 01 m 5 11 m 3 m 7 10 m 2 m 6 BC A B C F 0 0 0 X 0 0 1 1 0 0 1 A 0 1 00 X 0 01 1 X 11 1 1 10 0 0 BC A 0 1 00 X 0 01 1 X 0 11 1 X 10 0 0 1 Digital 1 Design 1 1 BC Review X=0 F = A’C + BC Exploit don’t cares F = C 35

3. Combinational Circuits Digital Design Review 36

Combinational Logic • Definition – – Outputs depend only on inputs No “memory” or “state” Can have propagation delay But, eventually output determined by simple Boolean algebra Digital Design Review 37

Gates • Logic Gates (or just “gates”) – Basic building block in digital systems • Goal – Review different types of gates – Understand how to connect to get desired (arbitrary) Boolean expression – Define performance (delay) Digital Design Review 38

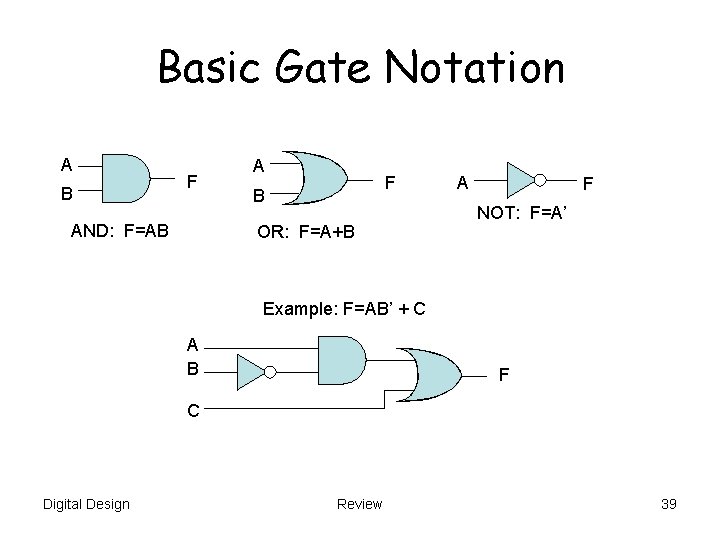

Basic Gate Notation A B F AND: F=AB A F B OR: F=A+B A F NOT: F=A’ Example: F=AB’ + C A B F C Digital Design Review 39

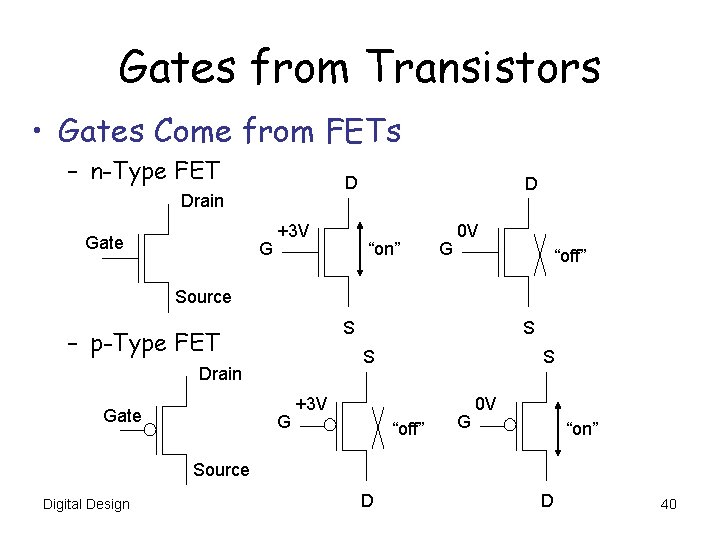

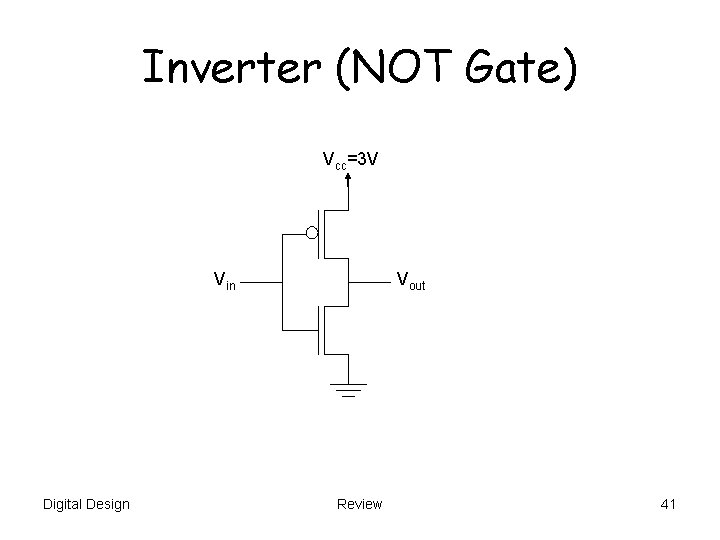

Gates from Transistors • Gates Come from FETs – n-Type FET D Drain Gate G +3 V D “on” G 0 V “off” Source S – p-Type FET S Drain Gate S G S +3 V “off” G 0 V “on” Source Digital Design D D 40

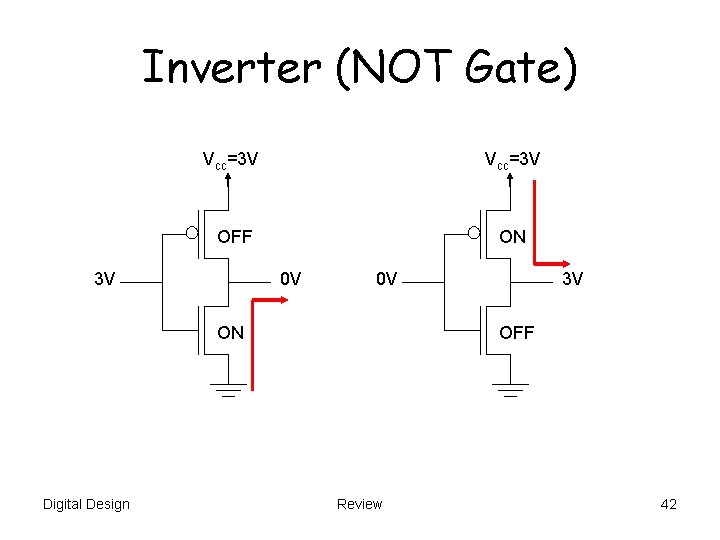

Inverter (NOT Gate) Vcc=3 V Vin Digital Design Vout Review 41

Inverter (NOT Gate) Vcc=3 V OFF ON 3 V 0 V 0 V ON Digital Design 3 V OFF Review 42

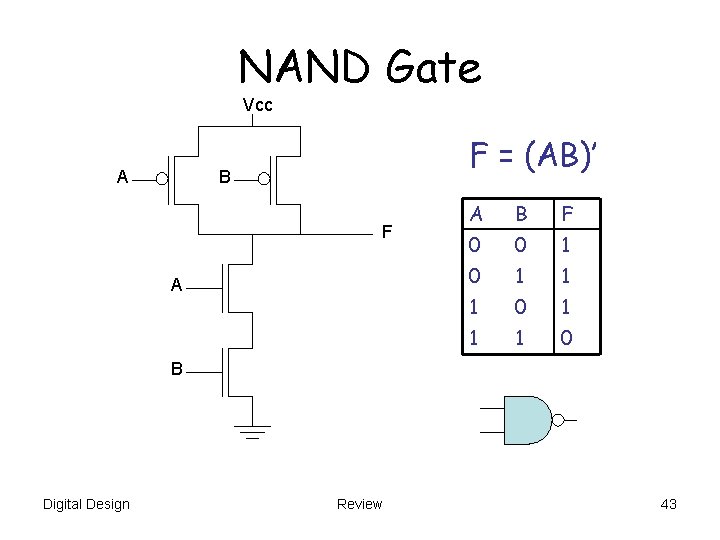

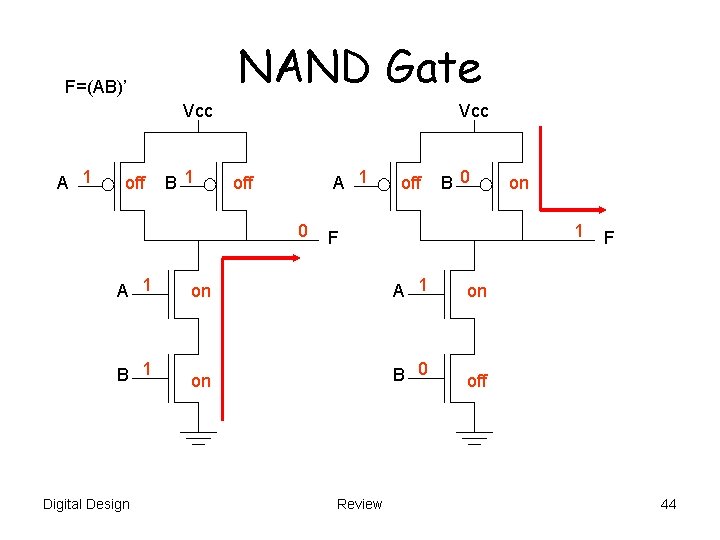

NAND Gate Vcc A F = (AB)’ B F A A B F 0 0 1 1 1 0 B Digital Design Review 43

NAND Gate F=(AB)’ Vcc A 1 off B 1 Vcc A 1 off 0 off B 0 1 F A 1 on B 0 off Digital Design Review on F 44

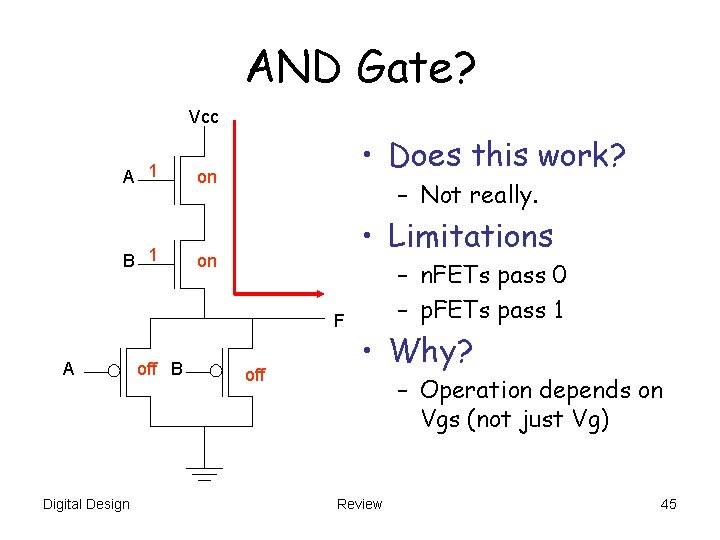

AND Gate? Vcc A 1 B 1 • Does this work? on – Not really. • Limitations on F A Digital Design off B off – n. FETs pass 0 – p. FETs pass 1 • Why? – Operation depends on Vgs (not just Vg) Review 45

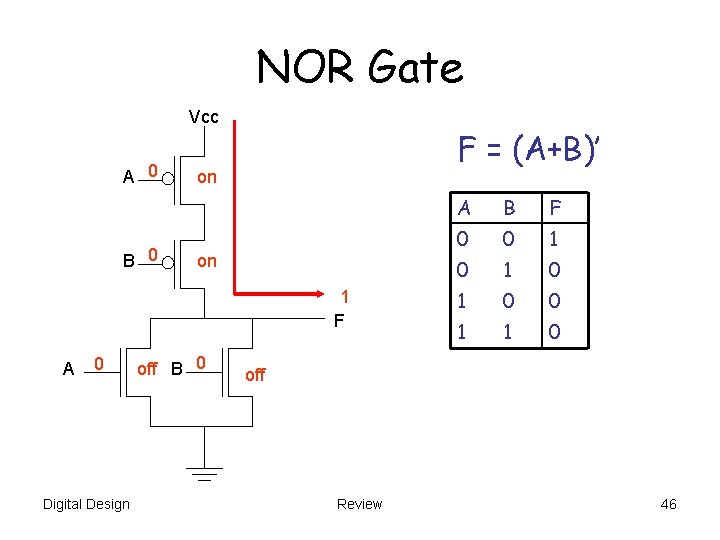

NOR Gate Vcc A 0 B 0 F = (A+B)’ on on 1 F A 0 Digital Design off B 0 A B F 0 0 1 0 1 0 0 1 1 0 off Review 46

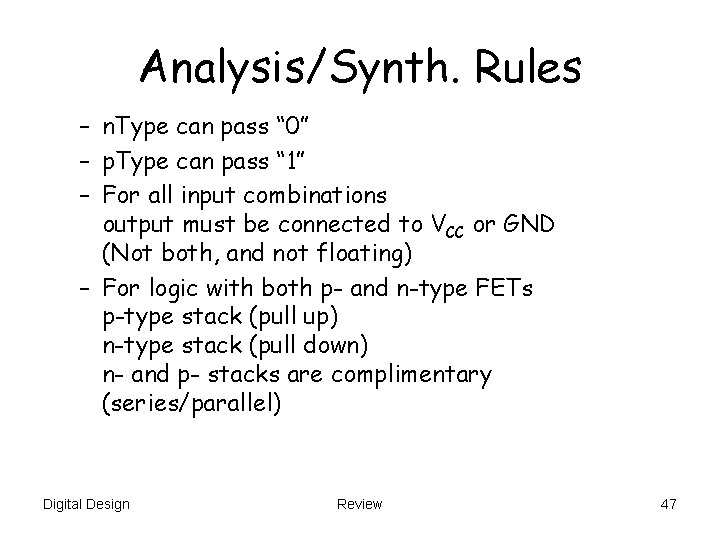

Analysis/Synth. Rules – n. Type can pass “ 0” – p. Type can pass “ 1” – For all input combinations output must be connected to VCC or GND (Not both, and not floating) – For logic with both p- and n-type FETs p-type stack (pull up) n-type stack (pull down) n- and p- stacks are complimentary (series/parallel) Digital Design Review 47

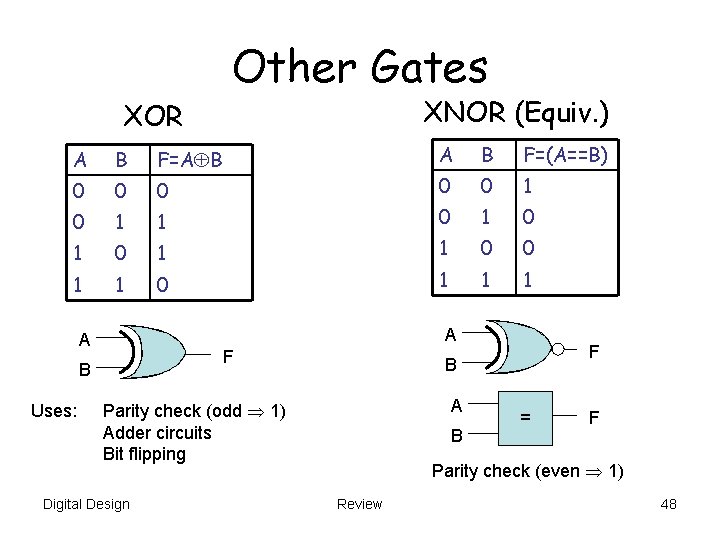

Other Gates XNOR (Equiv. ) XOR A B F=A B 0 0 1 1 1 0 B F=(A==B) 0 0 1 0 1 0 0 1 1 1 A A F B Uses: A A Parity check (odd 1) Adder circuits Bit flipping Digital Design F B B = F Parity check (even 1) Review 48

Functionally Complete Logic • Definition – Set of gates that can be used to realize all logic functions • Minimal set – Just one gate – NAND – NOR Digital Design Review 49

Multi-Input Gates • Extend gates by adding inputs 4 -input NAND – Problem? – Larger propagation delay due to series connected FETs. – Increase speed with higher current (larger area) – Gate width tradeoff: area, speed, power Digital Design Review 50

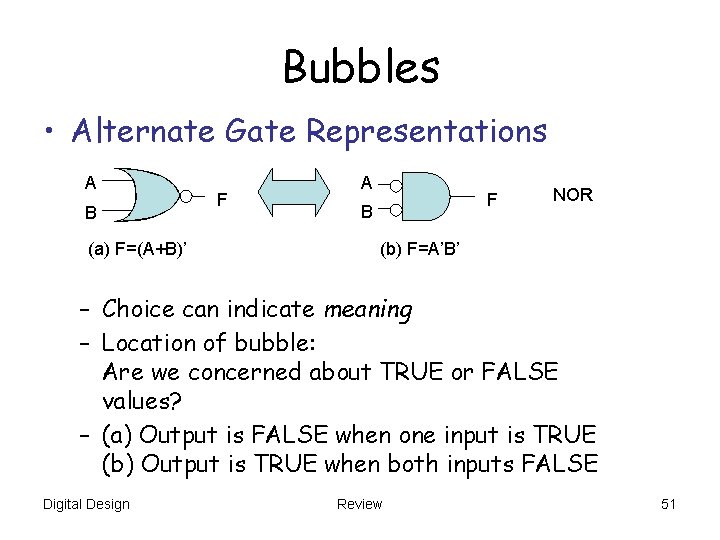

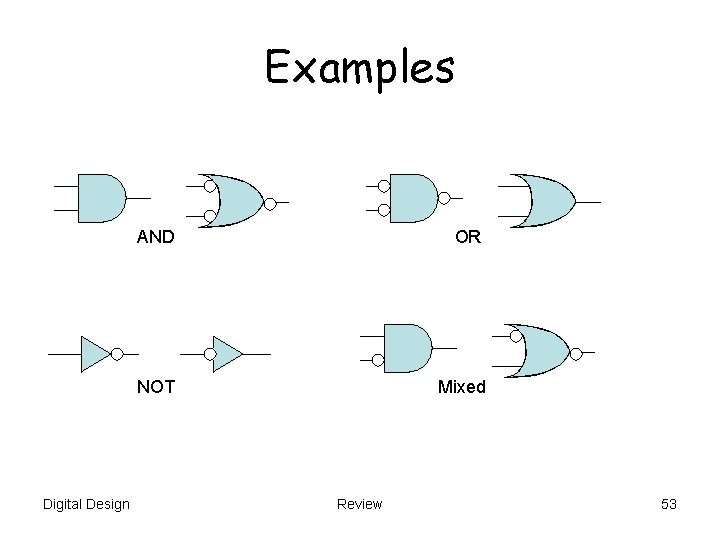

Bubbles • Alternate Gate Representations A B (a) F=(A+B)’ F A F B NOR (b) F=A’B’ – Choice can indicate meaning – Location of bubble: Are we concerned about TRUE or FALSE values? – (a) Output is FALSE when one input is TRUE (b) Output is TRUE when both inputs FALSE Digital Design Review 51

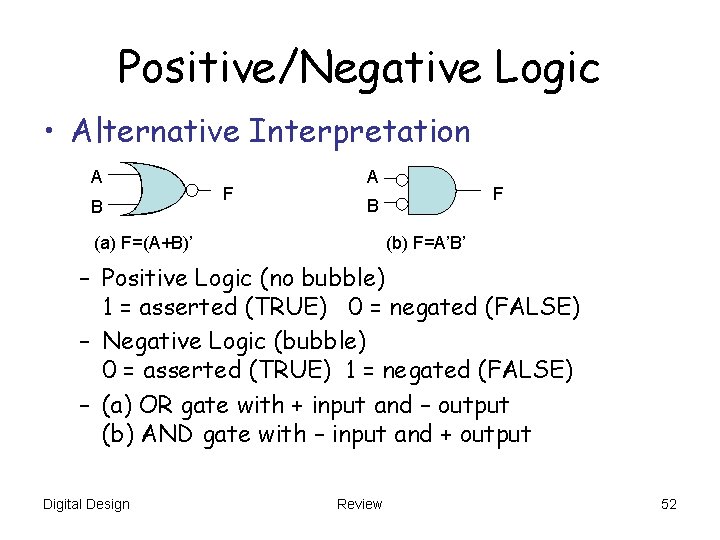

Positive/Negative Logic • Alternative Interpretation A B F A F B (a) F=(A+B)’ (b) F=A’B’ – Positive Logic (no bubble) 1 = asserted (TRUE) 0 = negated (FALSE) – Negative Logic (bubble) 0 = asserted (TRUE) 1 = negated (FALSE) – (a) OR gate with + input and – output (b) AND gate with – input and + output Digital Design Review 52

Examples Digital Design AND OR NOT Mixed Review 53

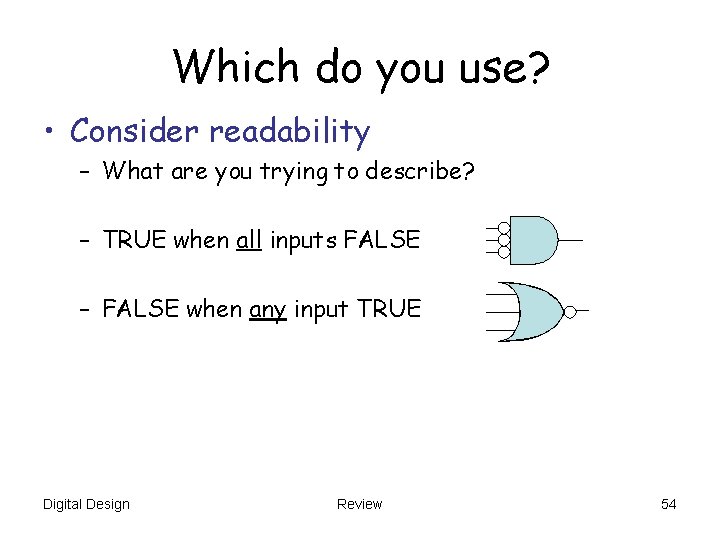

Which do you use? • Consider readability – What are you trying to describe? – TRUE when all inputs FALSE – FALSE when any input TRUE Digital Design Review 54

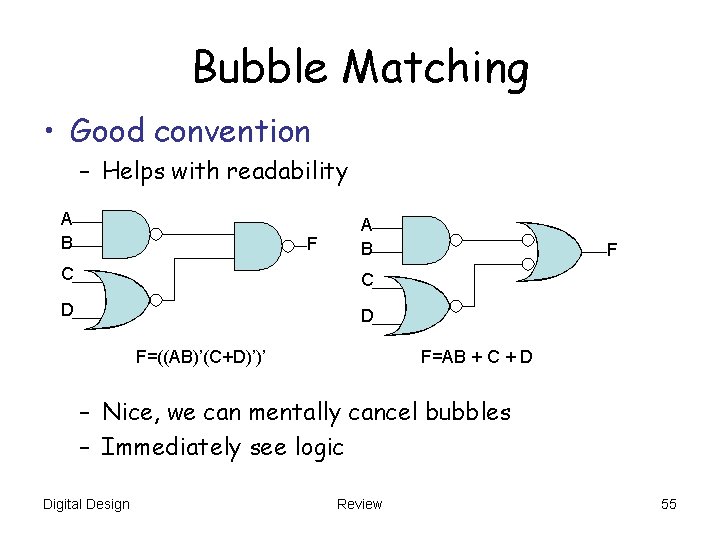

Bubble Matching • Good convention – Helps with readability A B F A B C C D D F=((AB)’(C+D)’)’ F F=AB + C + D – Nice, we can mentally cancel bubbles – Immediately see logic Digital Design Review 55

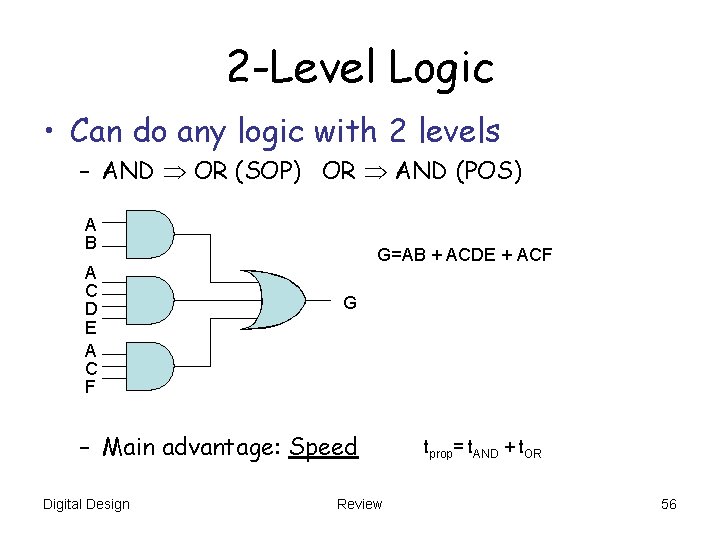

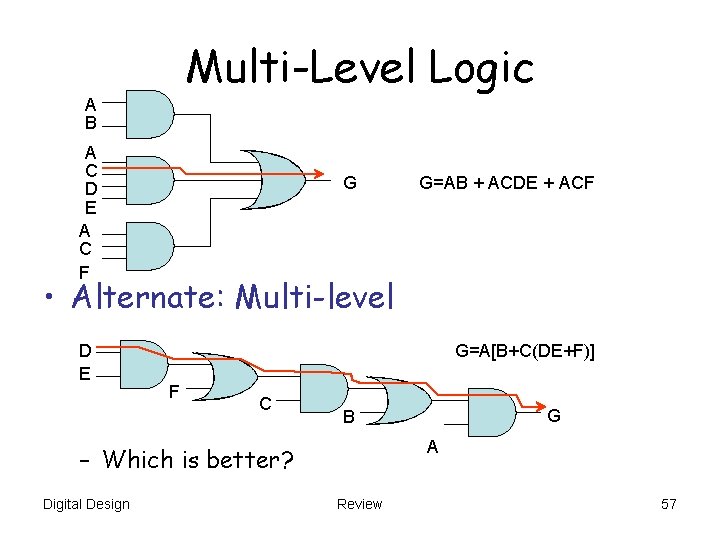

2 -Level Logic • Can do any logic with 2 levels – AND OR (SOP) OR AND (POS) A B A C D E A C F G=AB + ACDE + ACF G – Main advantage: Speed Digital Design Review tprop= t. AND + t. OR 56

Multi-Level Logic A B A C D E A C F G G=AB + ACDE + ACF • Alternate: Multi-level D E G=A[B+C(DE+F)] F C A – Which is better? Digital Design G B Review 57

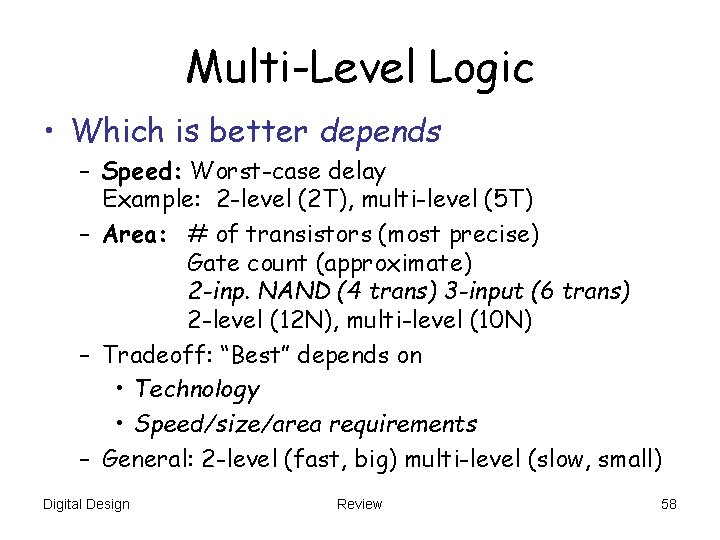

Multi-Level Logic • Which is better depends – Speed: Worst-case delay Example: 2 -level (2 T), multi-level (5 T) – Area: # of transistors (most precise) Gate count (approximate) 2 -inp. NAND (4 trans) 3 -input (6 trans) 2 -level (12 N), multi-level (10 N) – Tradeoff: “Best” depends on • Technology • Speed/size/area requirements – General: 2 -level (fast, big) multi-level (slow, small) Digital Design Review 58

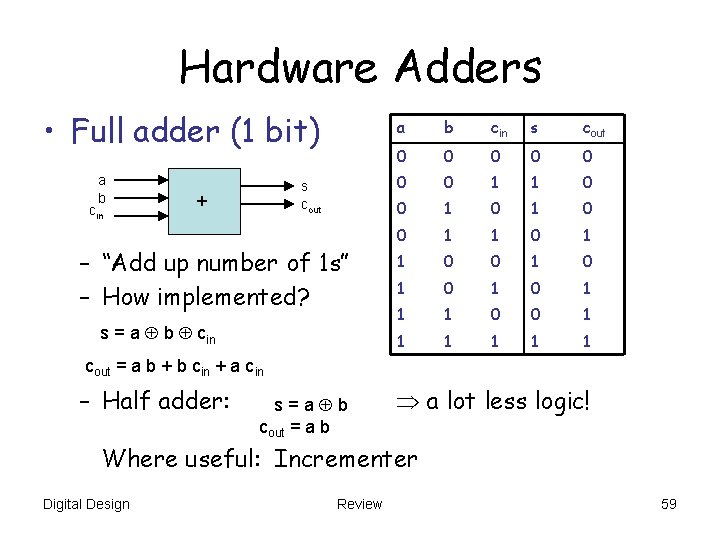

Hardware Adders • Full adder (1 bit) a b cin s cout + – “Add up number of 1 s” – How implemented? s = a b cin a b cin s cout 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1 cout = a b + b cin + a cin – Half adder: s=a b cout = a b a lot less logic! Where useful: Incrementer Digital Design Review 59

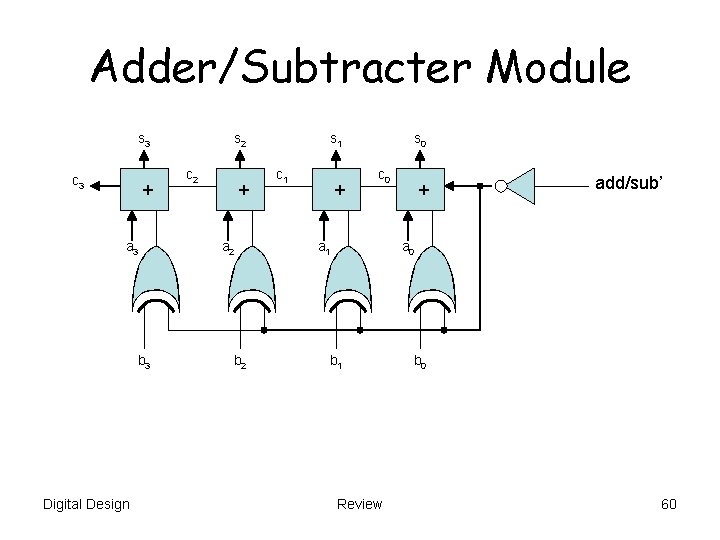

Adder/Subtracter Module s 3 c 3 + a 3 b 3 Digital Design s 2 c 2 + a 2 b 2 s 1 c 1 + s 0 c 0 a 1 + add/sub’ a 0 b 1 Review b 0 60

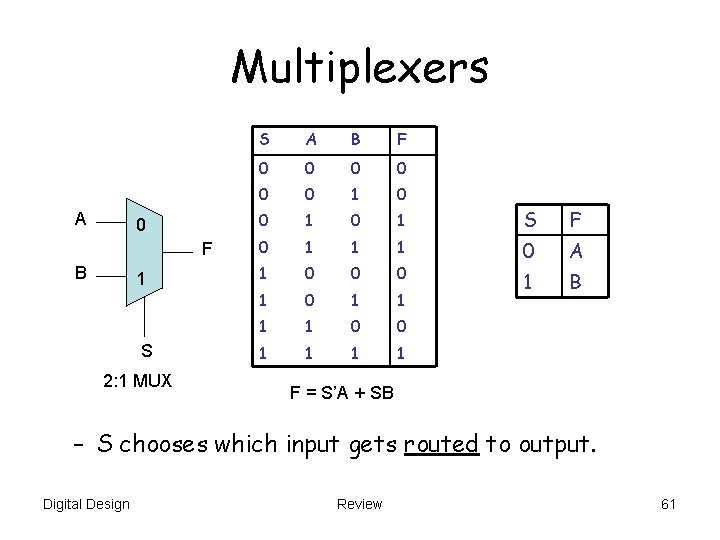

Multiplexers A 0 F B 1 S 2: 1 MUX S A B F 0 0 0 1 S F 0 1 1 0 0 A 1 0 1 1 1 B 1 1 0 0 1 1 F = S’A + SB – S chooses which input gets routed to output. Digital Design Review 61

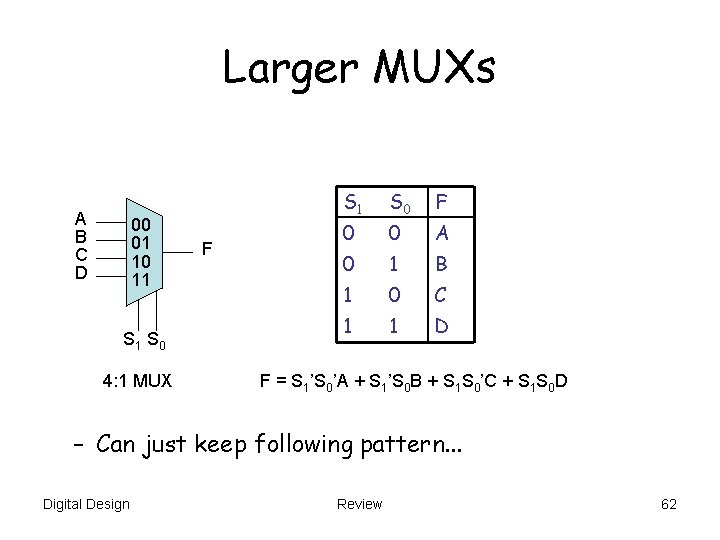

Larger MUXs A B C D 00 01 10 11 S 0 4: 1 MUX F S 1 S 0 F 0 0 A 0 1 B 1 0 C 1 1 D F = S 1’S 0’A + S 1’S 0 B + S 1 S 0’C + S 1 S 0 D – Can just keep following pattern. . . Digital Design Review 62

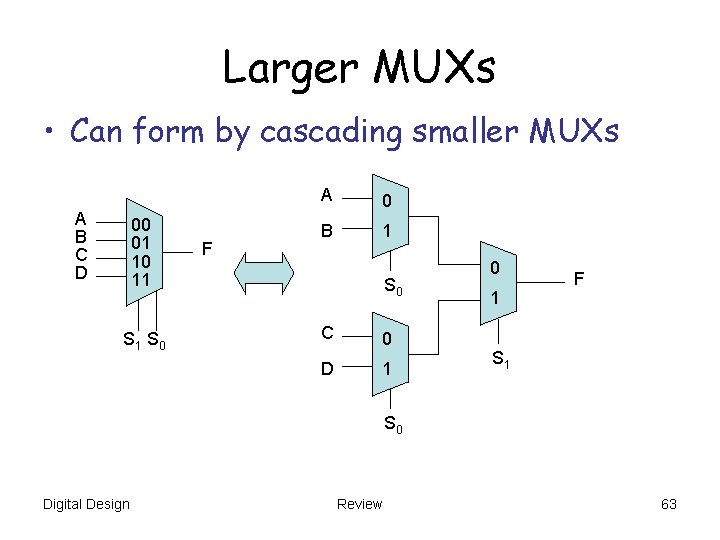

Larger MUXs • Can form by cascading smaller MUXs A B C D 00 01 10 11 S 0 F A 0 B 1 S 0 C 0 D 1 0 1 F S 1 S 0 Digital Design Review 63

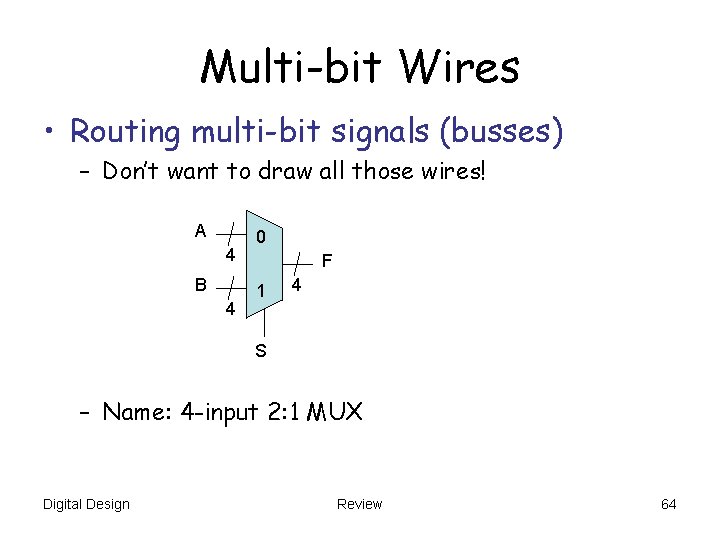

Multi-bit Wires • Routing multi-bit signals (busses) – Don’t want to draw all those wires! A 4 B 4 0 F 1 4 S – Name: 4 -input 2: 1 MUX Digital Design Review 64

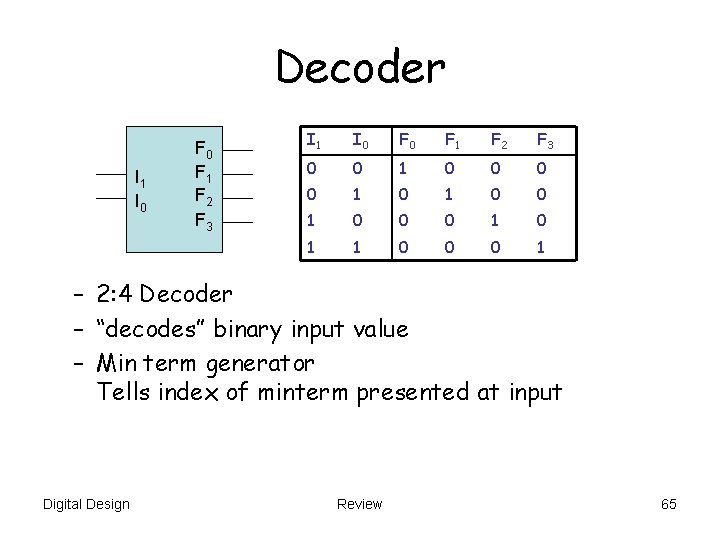

Decoder I 1 I 0 F 0 F 1 F 2 F 3 0 0 1 0 0 1 0 0 0 1 – 2: 4 Decoder – “decodes” binary input value – Min term generator Tells index of minterm presented at input Digital Design Review 65

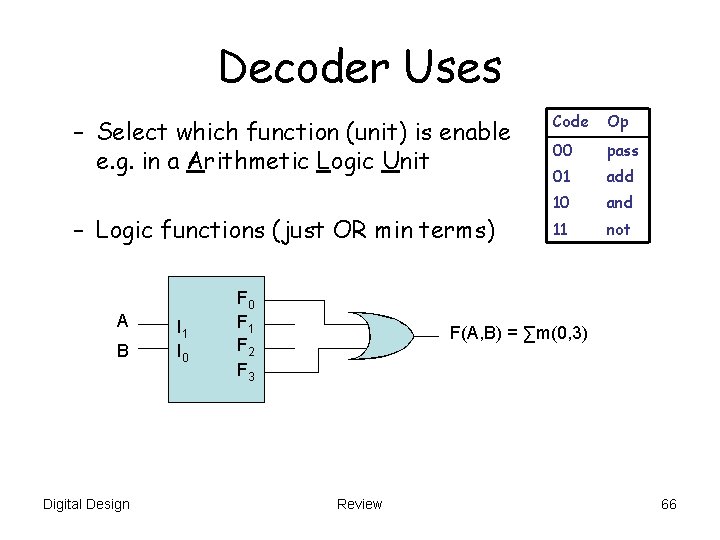

Decoder Uses – Select which function (unit) is enable e. g. in a Arithmetic Logic Unit – Logic functions (just OR min terms) A B Digital Design I 1 I 0 F 1 F 2 F 3 Code Op 00 pass 01 add 10 and 11 not F(A, B) = ∑m(0, 3) Review 66

Using MUXs, Decoders • Making everything out of low-level gates – Highest degree of control over design – But may be difficult to read • Higher level MUXs, Decoders – Easier to read, understand function – Simpler to maintain design – Most CAD tools good at optimizing mapping of MUXs/Decoders to gates for given target technology Digital Design Review 67

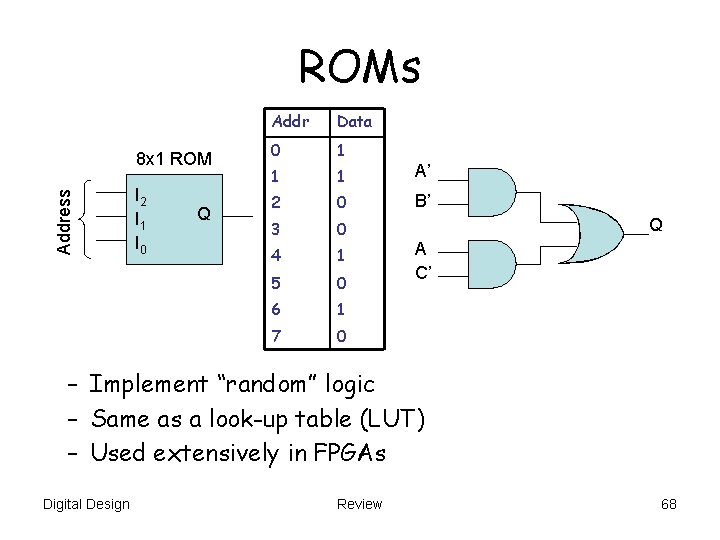

ROMs Address 8 x 1 ROM I 2 I 1 I 0 Q Addr Data 0 1 1 1 A’ 2 0 B’ 3 0 4 1 5 0 6 1 7 0 Q A C’ – Implement “random” logic – Same as a look-up table (LUT) – Used extensively in FPGAs Digital Design Review 68

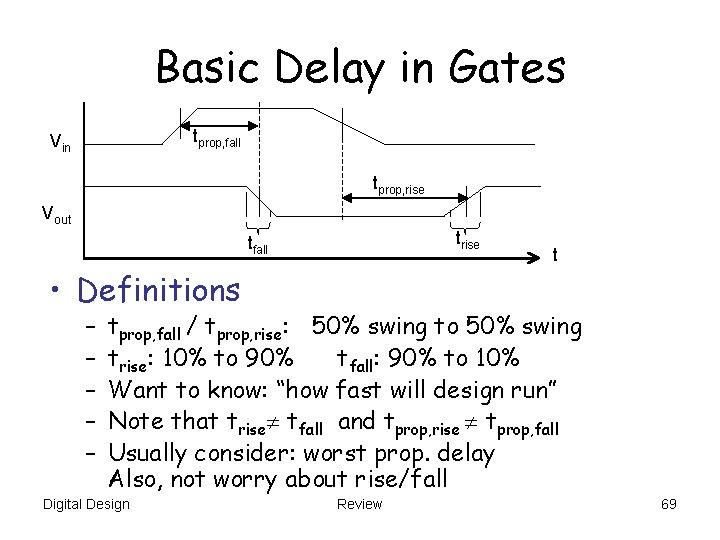

Basic Delay in Gates tprop, fall Vin tprop, rise Vout trise tfall t • Definitions – – – tprop, fall / tprop, rise: 50% swing to 50% swing trise: 10% to 90% tfall: 90% to 10% Want to know: “how fast will design run” Note that trise tfall and tprop, rise tprop, fall Usually consider: worst prop. delay Also, not worry about rise/fall Digital Design Review 69

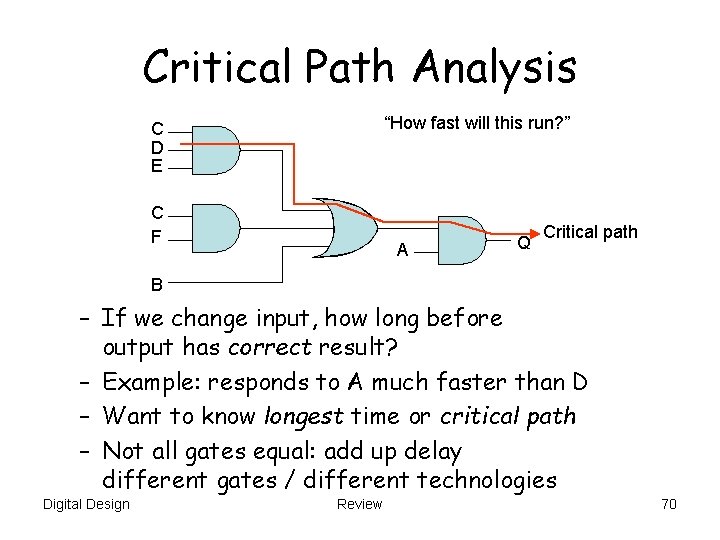

Critical Path Analysis “How fast will this run? ” C D E C F A Q Critical path B – If we change input, how long before output has correct result? – Example: responds to A much faster than D – Want to know longest time or critical path – Not all gates equal: add up delay different gates / different technologies Digital Design Review 70

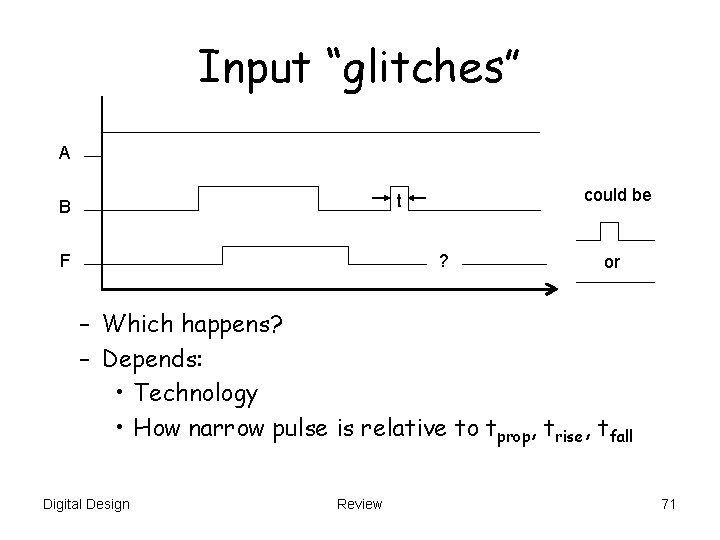

Input “glitches” A could be t B F ? or – Which happens? – Depends: • Technology • How narrow pulse is relative to tprop, trise, tfall Digital Design Review 71

Glitches (Transients) • Consider: B C A F – What is the output? – For static inputs: F=AA’=0 – Single rising A edge on A B C F – Pulse generator? – Point: Inputs to comb. logic change Transient period outputs fluctuate before final stable value Digital Design Review 72

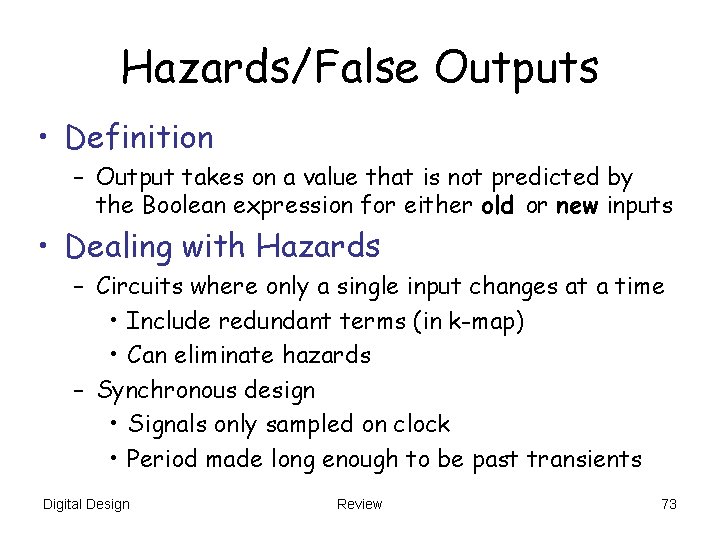

Hazards/False Outputs • Definition – Output takes on a value that is not predicted by the Boolean expression for either old or new inputs • Dealing with Hazards – Circuits where only a single input changes at a time • Include redundant terms (in k-map) • Can eliminate hazards – Synchronous design • Signals only sampled on clock • Period made long enough to be past transients Digital Design Review 73

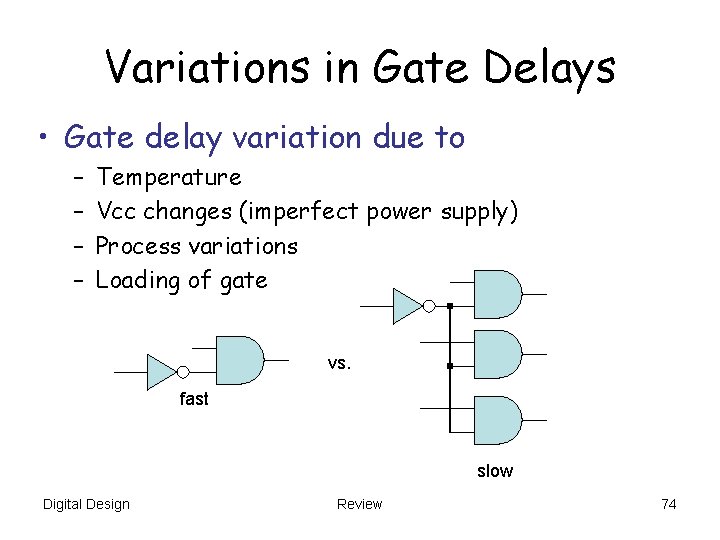

Variations in Gate Delays • Gate delay variation due to – – Temperature Vcc changes (imperfect power supply) Process variations Loading of gate vs. fast slow Digital Design Review 74

4. Sequential Circuits Digital Design Review 75

Complex Algorithms • Require – – Series of operations to be performed Order, timing important Storage for intermediate results Means we have memory • Digital Memory Elements – Latches – Flip-flops – SRAM, DRAM Digital Design Review 76

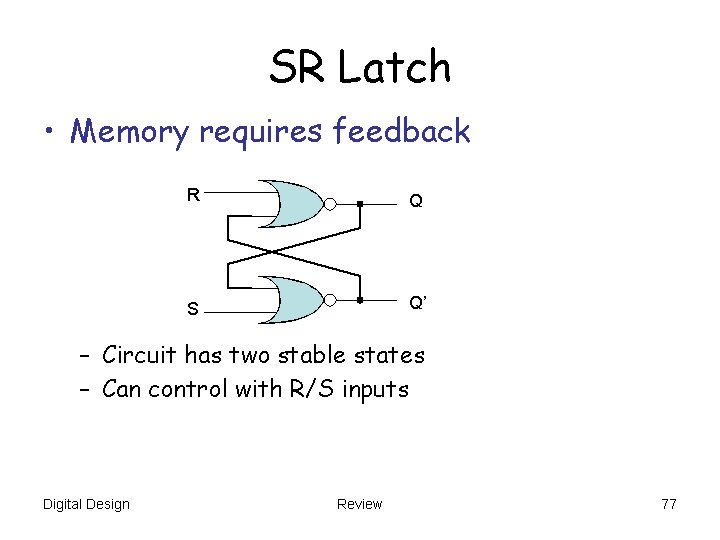

SR Latch • Memory requires feedback R Q S Q’ – Circuit has two stable states – Can control with R/S inputs Digital Design Review 77

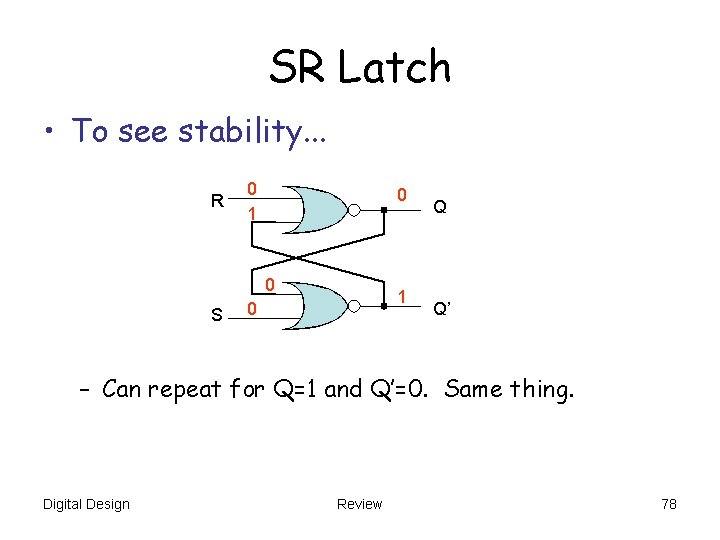

SR Latch • To see stability. . . R 0 1 0 0 S 1 0 Q Q’ – Can repeat for Q=1 and Q’=0. Same thing. Digital Design Review 78

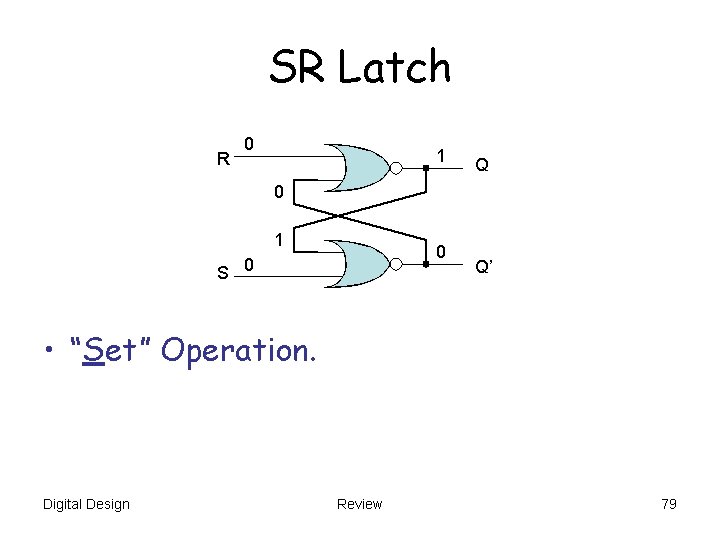

SR Latch R 0 0 1 Q 1 0 0 1 1 0 1 S 0 Q’ • “Set” Operation. Digital Design Review 79

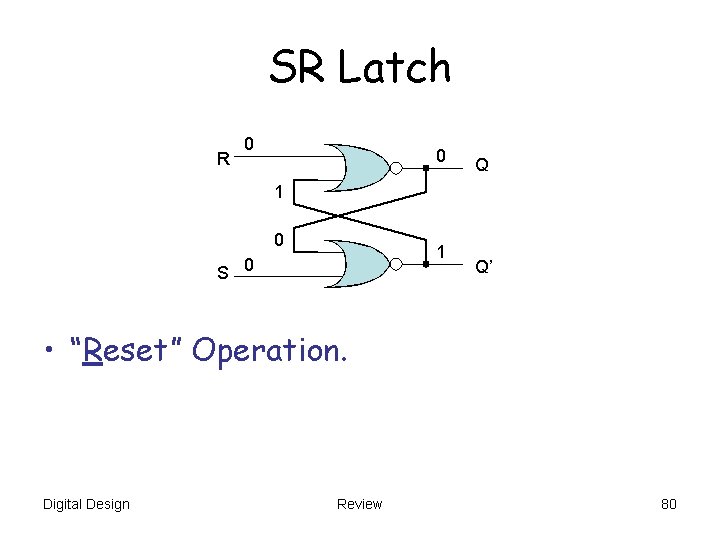

SR Latch R 1 0 Q 0 1 1 0 0 1 S 0 Q’ • “Reset” Operation. Digital Design Review 80

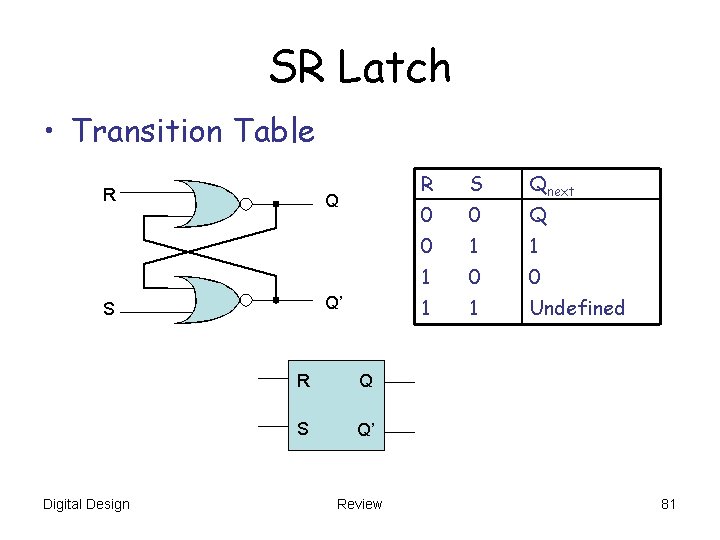

SR Latch • Transition Table R Q Q’ S Digital Design R Q S Q’ Review R S Qnext 0 0 Q 0 1 1 1 0 0 1 1 Undefined 81

SR Latch Summary • Features – Provides 1 bit of memory – Control by temporarily raising S or R • Problems? – Output can change at any time when S/R change Think about glitches! – Inconvenient to have two inputs to control How do we store just the bit on a line? Digital Design Review 82

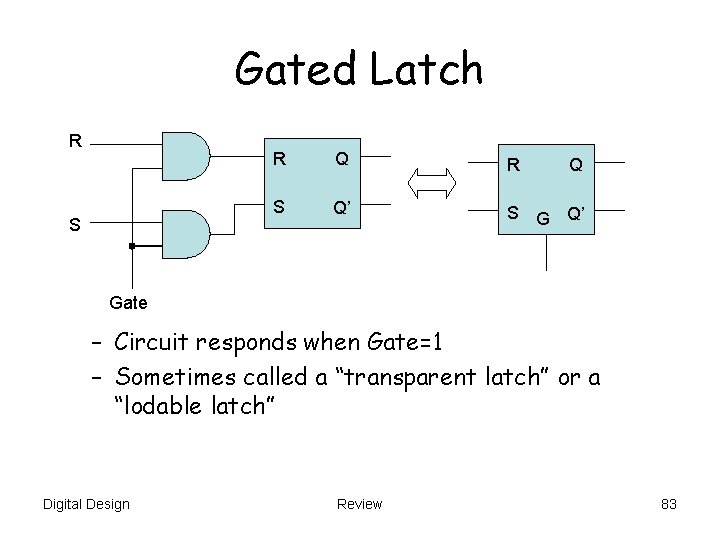

Gated Latch R S R Q R S Q’ S G Q’ Q Gate – Circuit responds when Gate=1 – Sometimes called a “transparent latch” or a “lodable latch” Digital Design Review 83

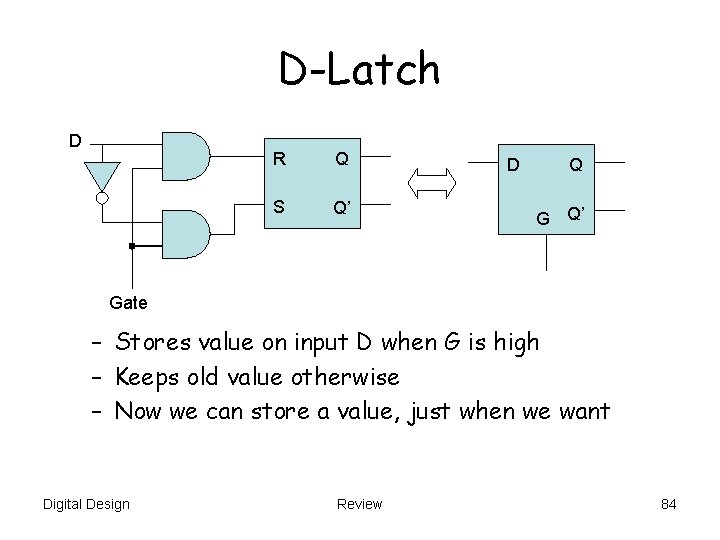

D-Latch D R Q S Q’ D Q G Q’ Gate – Stores value on input D when G is high – Keeps old value otherwise – Now we can store a value, just when we want Digital Design Review 84

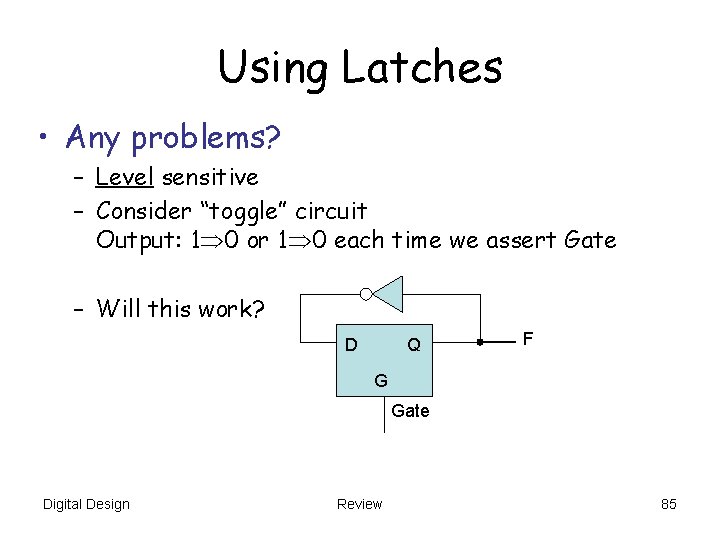

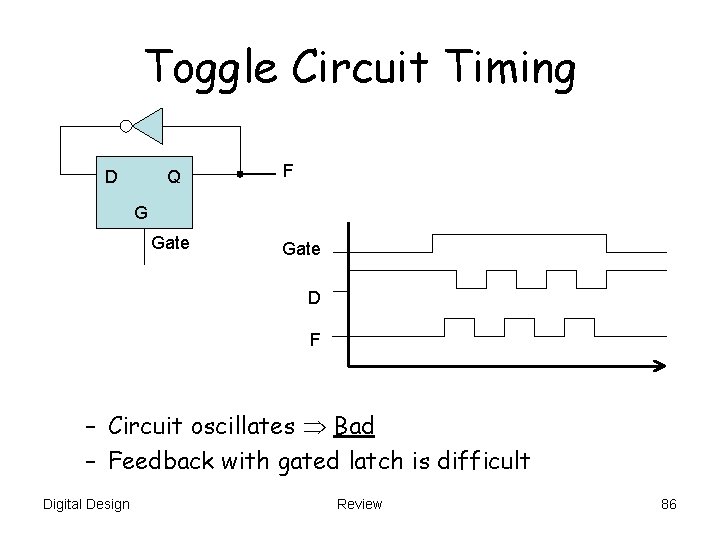

Using Latches • Any problems? – Level sensitive – Consider “toggle” circuit Output: 1 0 or 1 0 each time we assert Gate – Will this work? D Q F G Gate Digital Design Review 85

Toggle Circuit Timing D Q F G Gate D F – Circuit oscillates Bad – Feedback with gated latch is difficult Digital Design Review 86

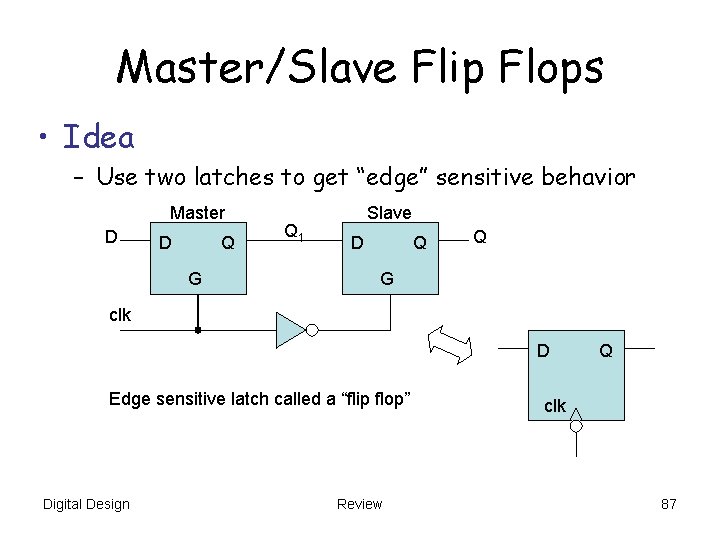

Master/Slave Flip Flops • Idea – Use two latches to get “edge” sensitive behavior Master D D Q G Q 1 Slave D Q Q G clk D Edge sensitive latch called a “flip flop” Digital Design Review Q clk 87

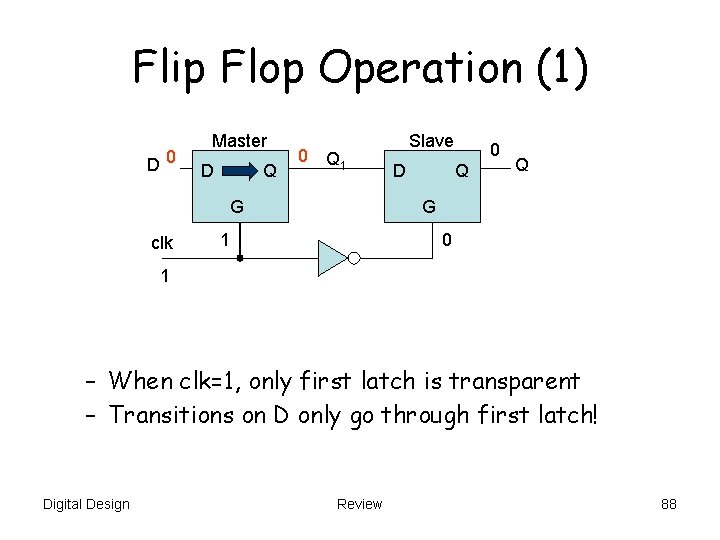

Flip Flop Operation (1) 0 1 D Master D Q 1 0 G clk Slave D 0 Q Q G 1 0 1 – When clk=1, only first latch is transparent – Transitions on D only go through first latch! Digital Design Review 88

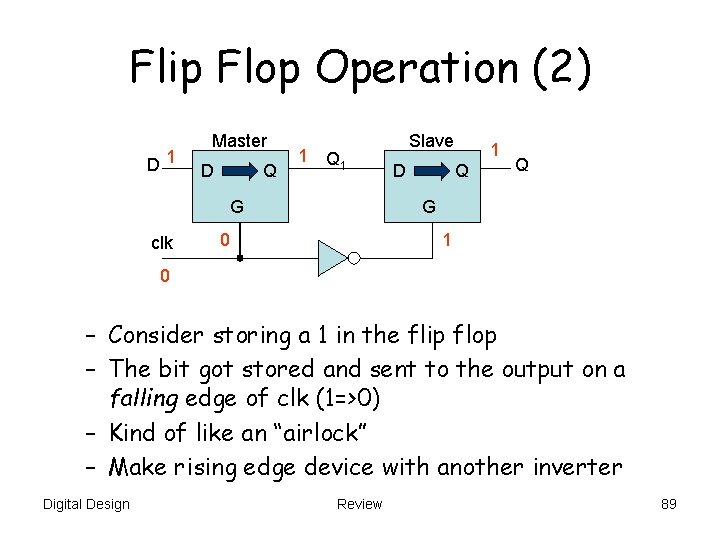

Flip Flop Operation (2) 0 D 1 Master D Q 0 Q 1 1 G clk Slave D 0 1 Q Q G 0 1 1 0 – Consider storing a 1 in the flip flop – The bit got stored and sent to the output on a falling edge of clk (1=>0) – Kind of like an “airlock” – Make rising edge device with another inverter Digital Design Review 89

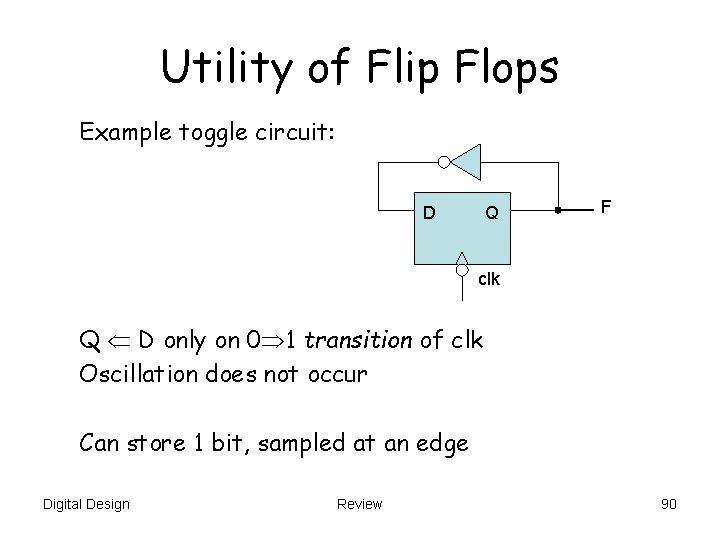

Utility of Flip Flops Example toggle circuit: D Q F clk Q D only on 0 1 transition of clk Oscillation does not occur Can store 1 bit, sampled at an edge Digital Design Review 90

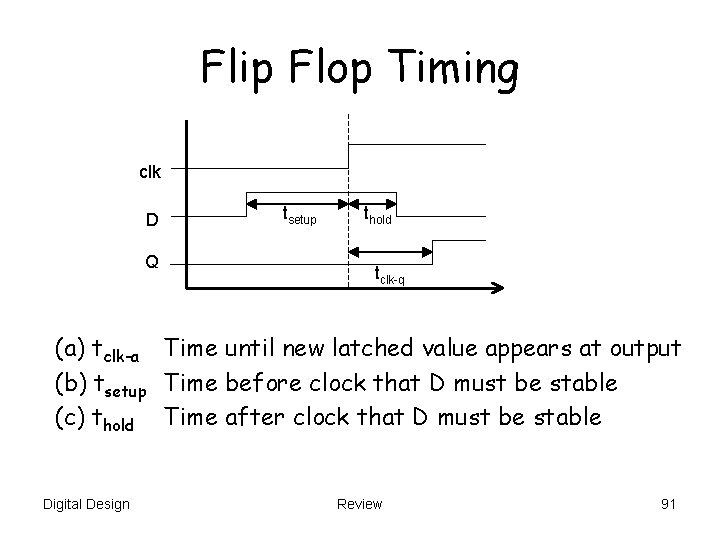

Flip Flop Timing clk D Q tsetup thold tclk-q (a) tclk-a Time until new latched value appears at output (b) tsetup Time before clock that D must be stable (c) thold Time after clock that D must be stable Digital Design Review 91

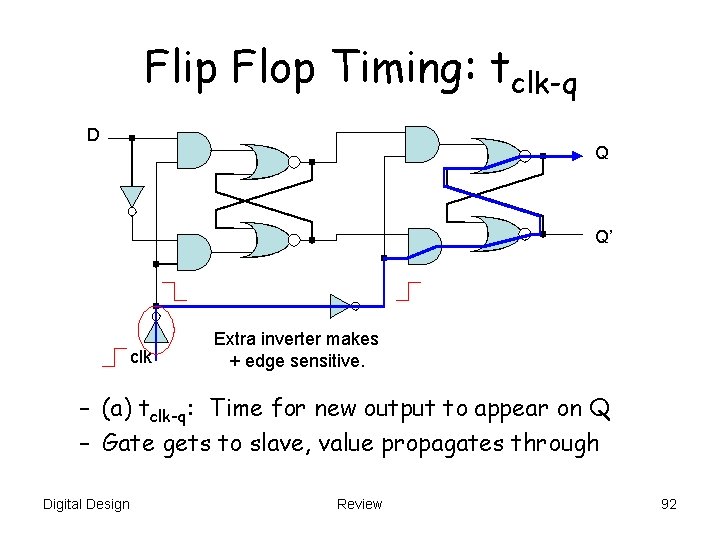

Flip Flop Timing: tclk-q D Q Q’ clk Extra inverter makes + edge sensitive. – (a) tclk-q : Time for new output to appear on Q – Gate gets to slave, value propagates through Digital Design Review 92

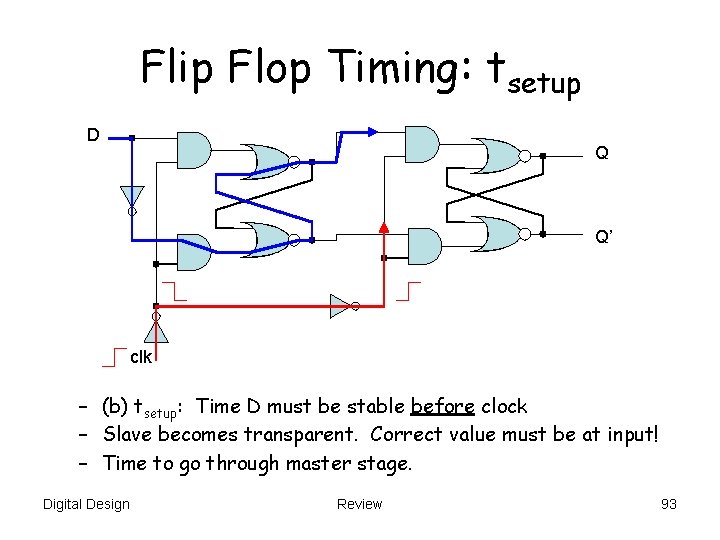

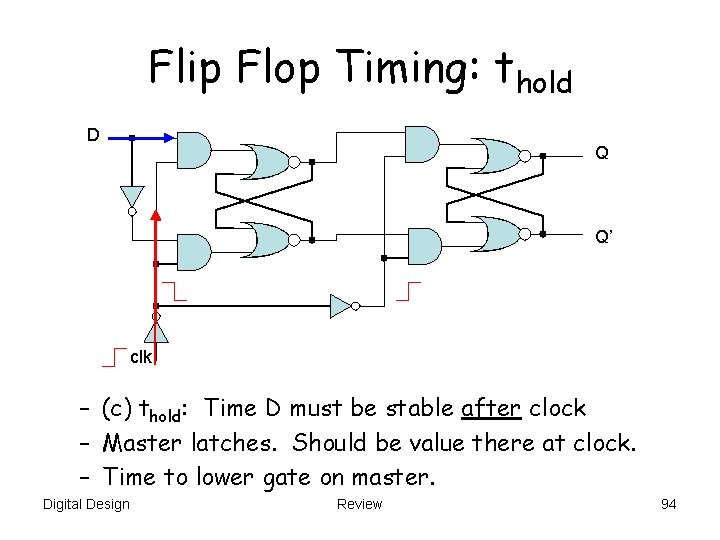

Flip Flop Timing: tsetup D Q Q’ clk – (b) tsetup: Time D must be stable before clock – Slave becomes transparent. Correct value must be at input! – Time to go through master stage. Digital Design Review 93

Flip Flop Timing: thold D Q Q’ clk – (c) thold: Time D must be stable after clock – Master latches. Should be value there at clock. – Time to lower gate on master. Digital Design Review 94

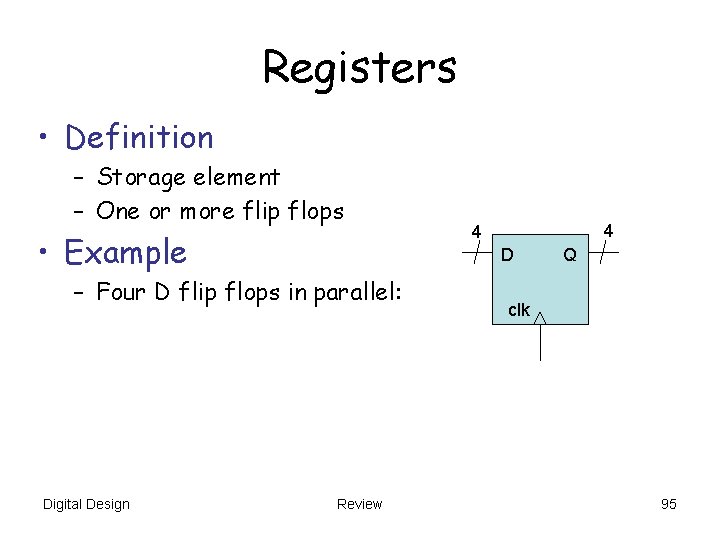

Registers • Definition – Storage element – One or more flip flops • Example D – Four D flip flops in parallel: Digital Design 4 4 Review Q clk 95

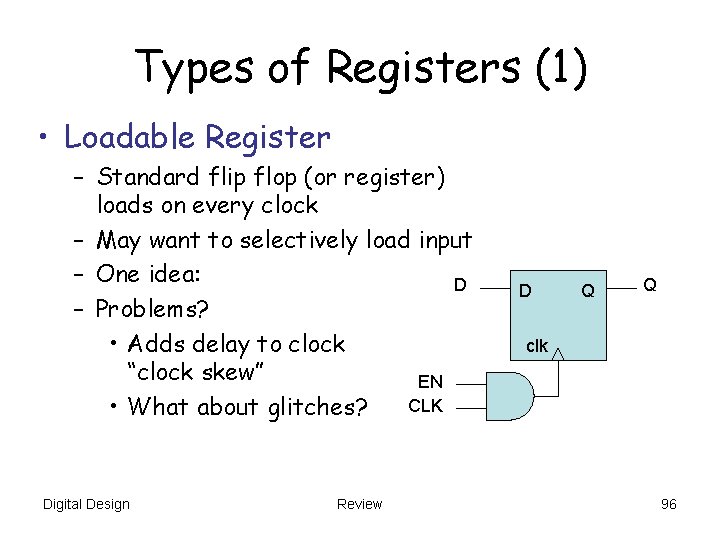

Types of Registers (1) • Loadable Register – Standard flip flop (or register) loads on every clock – May want to selectively load input – One idea: D – Problems? • Adds delay to clock “clock skew” EN CLK • What about glitches? Digital Design Review D Q Q clk 96

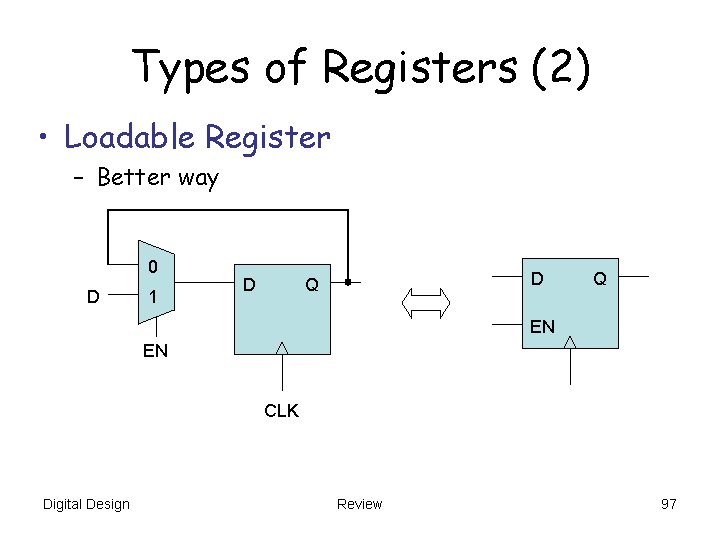

Types of Registers (2) • Loadable Register – Better way 0 D 1 D D Q Q EN EN CLK Digital Design Review 97

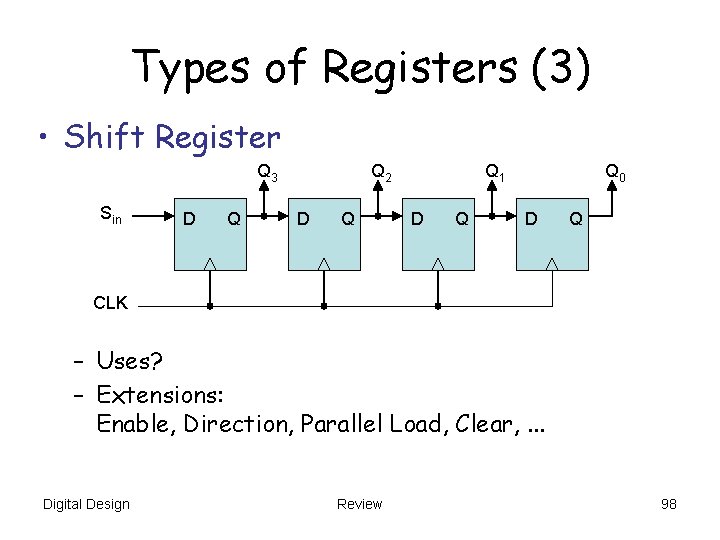

Types of Registers (3) • Shift Register Q 3 Sin D Q Q 2 D Q Q 1 D Q Q 0 D Q CLK – Uses? – Extensions: Enable, Direction, Parallel Load, Clear, . . . Digital Design Review 98

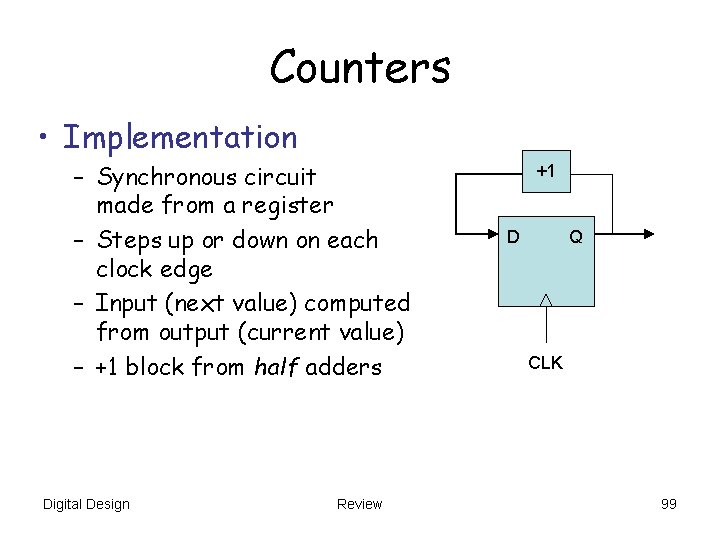

Counters • Implementation – Synchronous circuit made from a register – Steps up or down on each clock edge – Input (next value) computed from output (current value) – +1 block from half adders Digital Design Review +1 D Q CLK 99

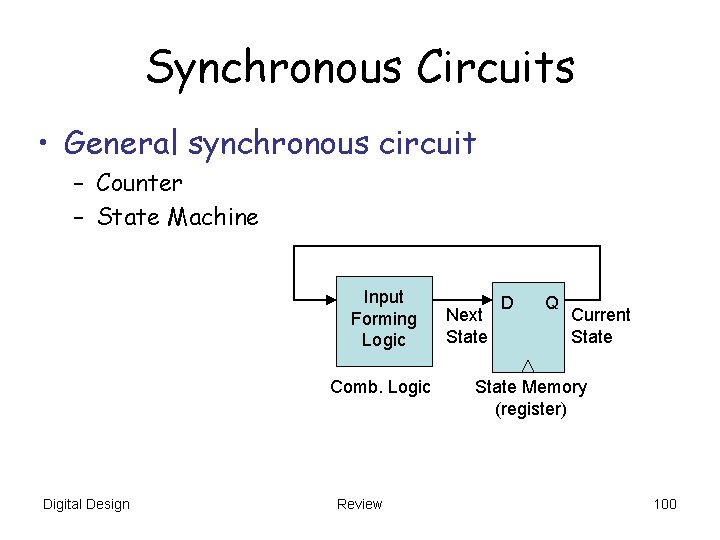

Synchronous Circuits • General synchronous circuit – Counter – State Machine Input Forming Logic Comb. Logic Digital Design Review Next State D Q Current State Memory (register) 100

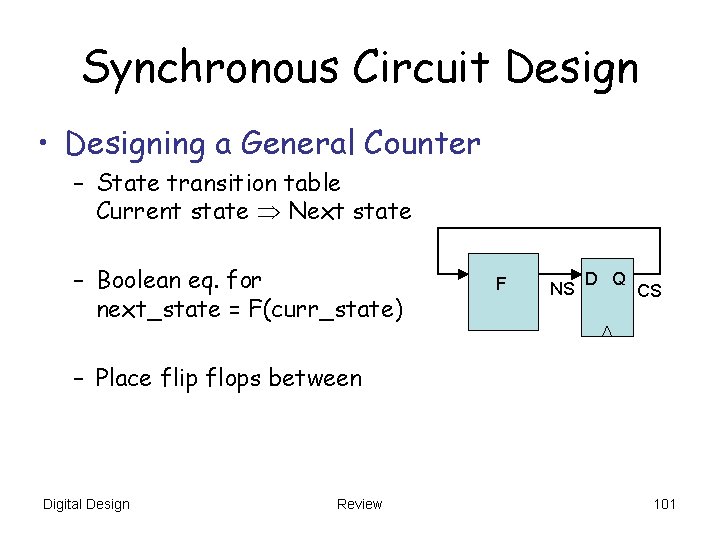

Synchronous Circuit Design • Designing a General Counter – State transition table Current state Next state – Boolean eq. for next_state = F(curr_state) F NS D Q CS – Place flip flops between Digital Design Review 101

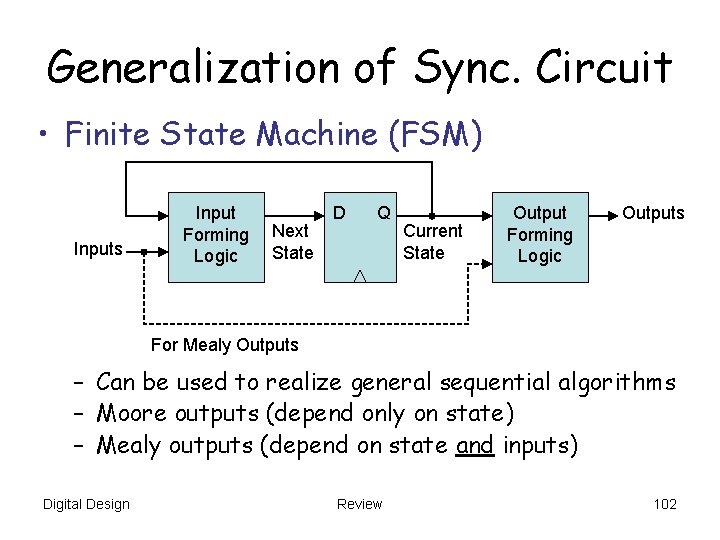

Generalization of Sync. Circuit • Finite State Machine (FSM) Inputs Input Forming Logic Next State D Q Current State Output Forming Logic Outputs For Mealy Outputs – Can be used to realize general sequential algorithms – Moore outputs (depend only on state) – Mealy outputs (depend on state and inputs) Digital Design Review 102

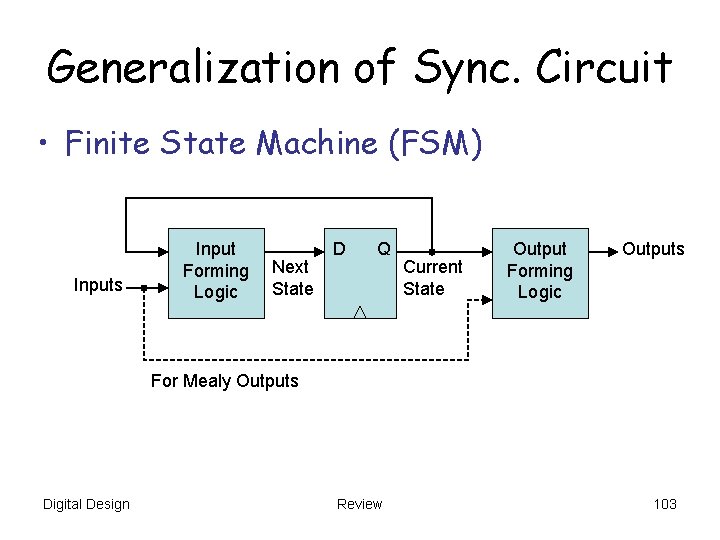

Generalization of Sync. Circuit • Finite State Machine (FSM) Inputs Input Forming Logic Next State D Q Current State Output Forming Logic Outputs For Mealy Outputs Digital Design Review 103

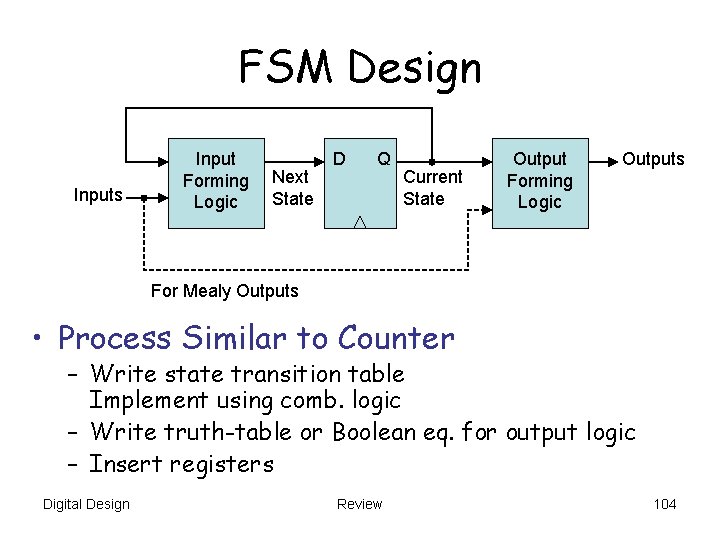

FSM Design Inputs Input Forming Logic Next State D Q Current State Output Forming Logic Outputs For Mealy Outputs • Process Similar to Counter – Write state transition table Implement using comb. logic – Write truth-table or Boolean eq. for output logic – Insert registers Digital Design Review 104

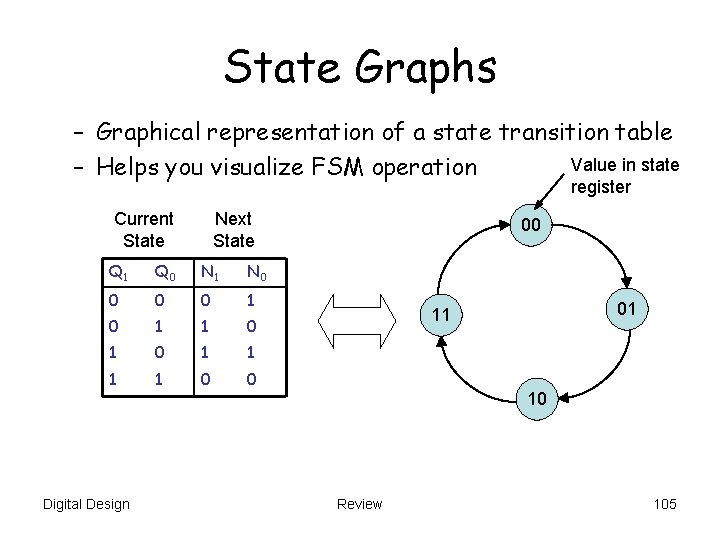

State Graphs – Graphical representation of a state transition table Value in state – Helps you visualize FSM operation register Current State Next State Q 1 Q 0 N 1 N 0 0 1 0 1 0 1 1 0 0 Digital Design 00 01 11 10 Review 105

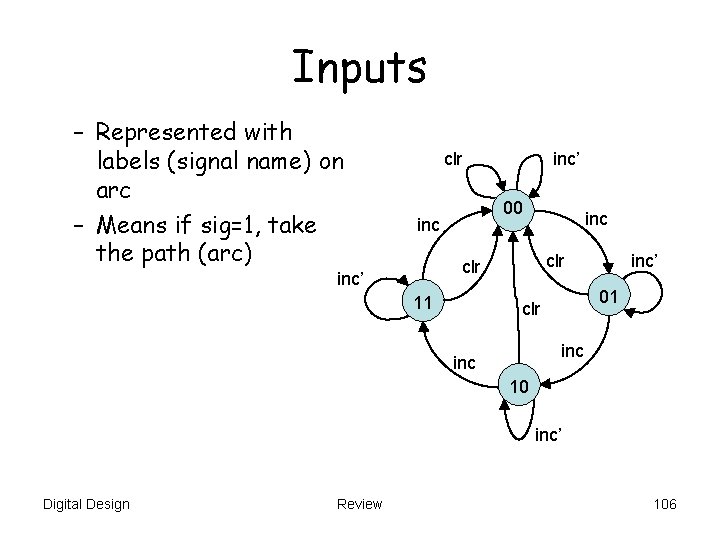

Inputs – Represented with labels (signal name) on arc – Means if sig=1, take the path (arc) clr inc’ 00 inc clr inc’ 11 inc’ 01 clr inc 10 inc’ Digital Design Review 106

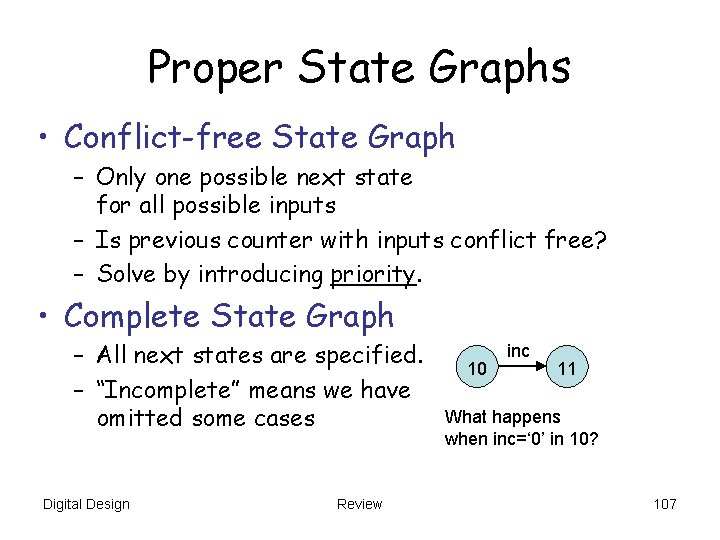

Proper State Graphs • Conflict-free State Graph – Only one possible next state for all possible inputs – Is previous counter with inputs conflict free? – Solve by introducing priority. • Complete State Graph – All next states are specified. – “Incomplete” means we have omitted some cases Digital Design Review 10 inc 11 What happens when inc=‘ 0’ in 10? 107

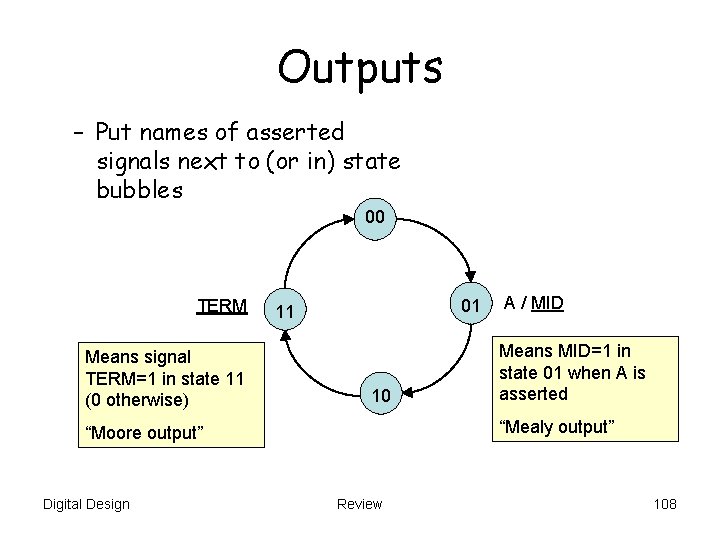

Outputs – Put names of asserted signals next to (or in) state bubbles 00 TERM Means signal TERM=1 in state 11 (0 otherwise) 01 11 10 Means MID=1 in state 01 when A is asserted “Mealy output” “Moore output” Digital Design A / MID Review 108

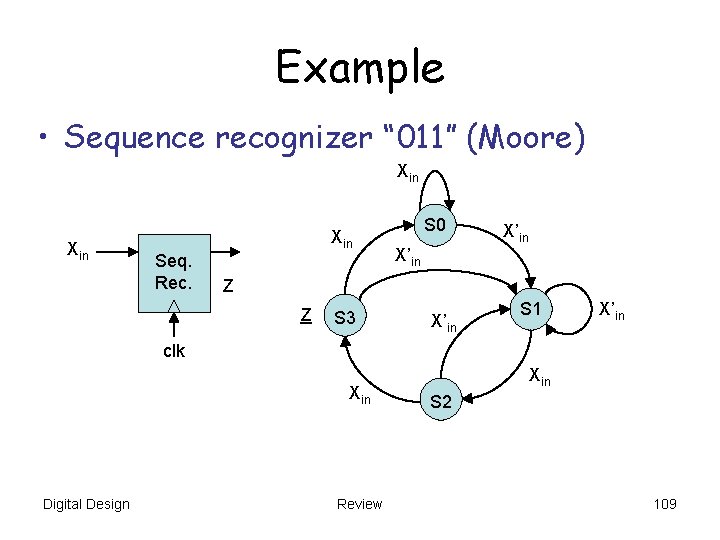

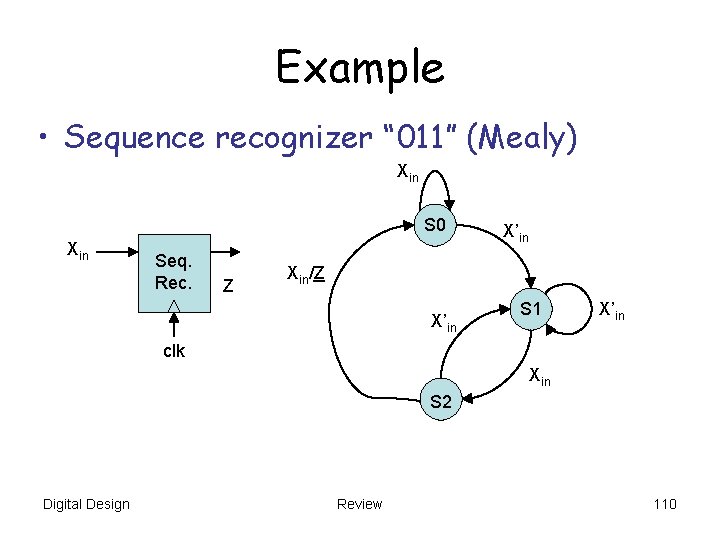

Example • Sequence recognizer “ 011” (Moore) Xin Xin Seq. Rec. S 0 X’in Z Z S 3 X’in S 1 X’in clk Xin Digital Design Review Xin S 2 109

Example • Sequence recognizer “ 011” (Mealy) Xin S 0 Xin Seq. Rec. Z X’in Xin/Z X’in S 1 X’in clk Xin S 2 Digital Design Review 110

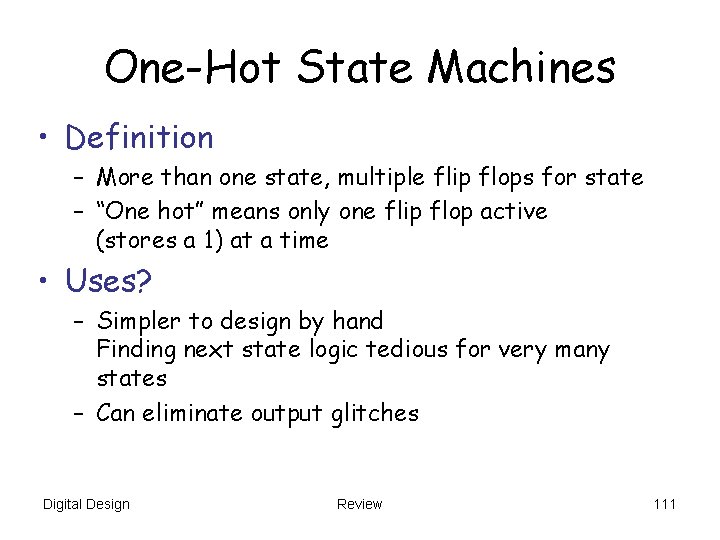

One-Hot State Machines • Definition – More than one state, multiple flip flops for state – “One hot” means only one flip flop active (stores a 1) at a time • Uses? – Simpler to design by hand Finding next state logic tedious for very many states – Can eliminate output glitches Digital Design Review 111

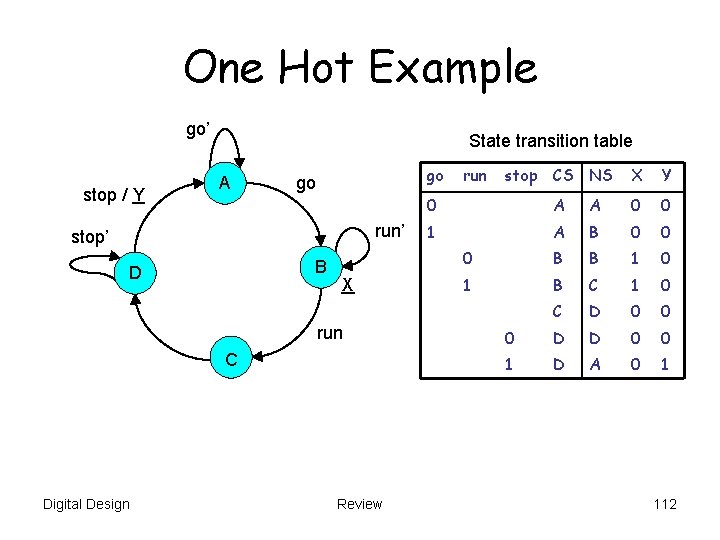

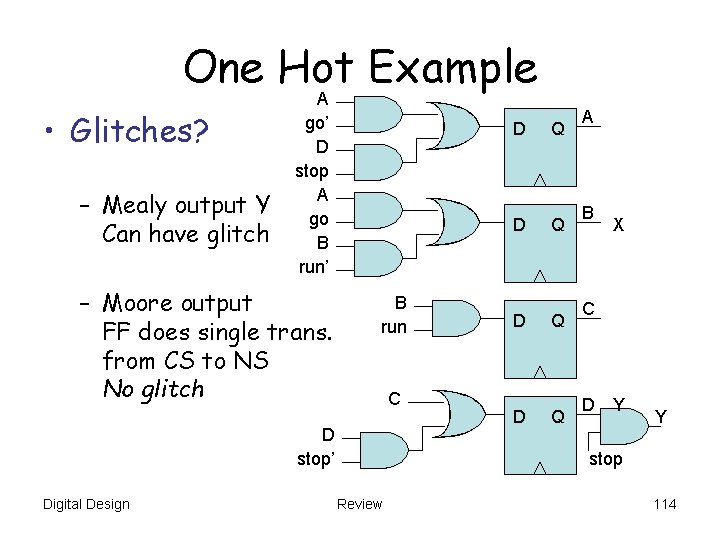

One Hot Example go’ stop / Y State transition table A go go run’ stop’ B D X run C Digital Design Review run stop CS NS X Y 0 A A 0 0 1 A B 0 0 0 B B 1 0 1 B C 1 0 C D 0 0 0 D D 0 0 1 D A 0 1 112

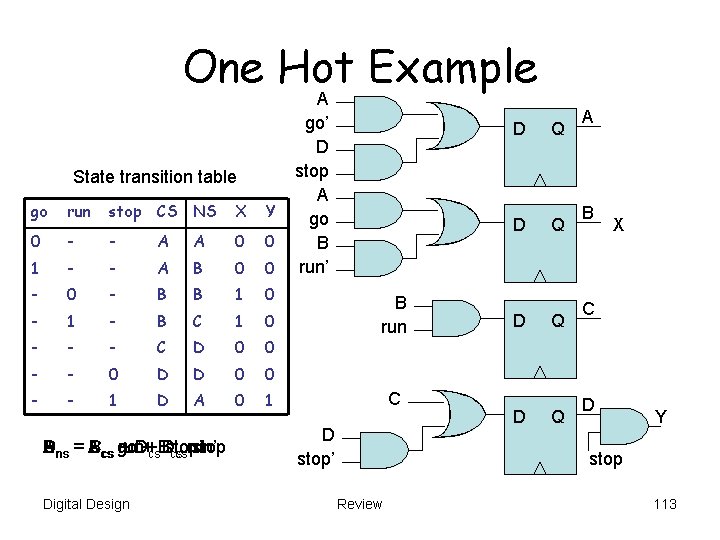

One Hot Example State transition table go run stop CS NS X Y 0 - - A A 0 0 1 - - A B 0 0 - B B 1 0 - 1 - B C 1 0 - - - C D 0 0 - - 0 D D 0 0 - - 1 D A 0 1 Ans = A B C D Bcs C go’ run + D++cs. BD stop’ stop cs go cs csrun’ Digital Design A go’ D stop A go B run’ B run C D stop’ D Q D Q A B X C D Y stop Review 113

One Hot Example • Glitches? – Mealy output Y Can have glitch A go’ D stop A go B run’ – Moore output FF does single trans. from CS to NS No glitch B run C D stop’ Digital Design D Q D Q A B X C D Y Y stop Review 114

Summary 1. 2. 3. 4. Number Systems / Binary Encoding Boolean Algebra Combinational Circuits Sequential Circuits Fundamental concepts and terms we need for the rest of the course. Digital Design Review 115

- Slides: 115