Chapter 5 Basic Computer Organization and Design http

Chapter 5 Basic Computer Organization and Design 충남대학교 컴퓨터전공 http: //sslab. cnu. ac. kr 이철훈 1

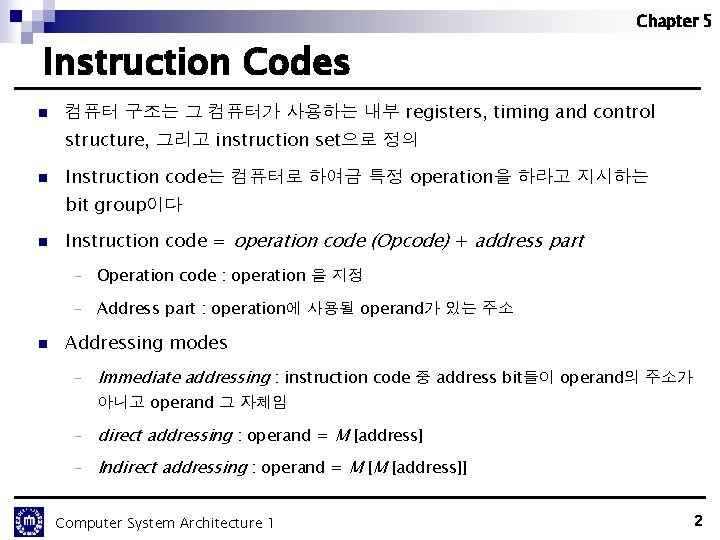

Chapter 5 Instruction Codes n 컴퓨터 구조는 그 컴퓨터가 사용하는 내부 registers, timing and control structure, 그리고 instruction set으로 정의 n Instruction code는 컴퓨터로 하여금 특정 operation을 하라고 지시하는 bit group이다 n n Instruction code = operation code (Opcode) + address part - Operation code : operation 을 지정 - Address part : operation에 사용될 operand가 있는 주소 Addressing modes - Immediate addressing : instruction code 중 address bit들이 operand의 주소가 아니고 operand 그 자체임 - direct addressing : operand = M [address] - Indirect addressing : operand = M [M [address]] Computer System Architecture 1 2

Chapter 5 Instruction Codes Fig. 5 -2 Demonstration of direct and indirect address Computer System Architecture 1 3

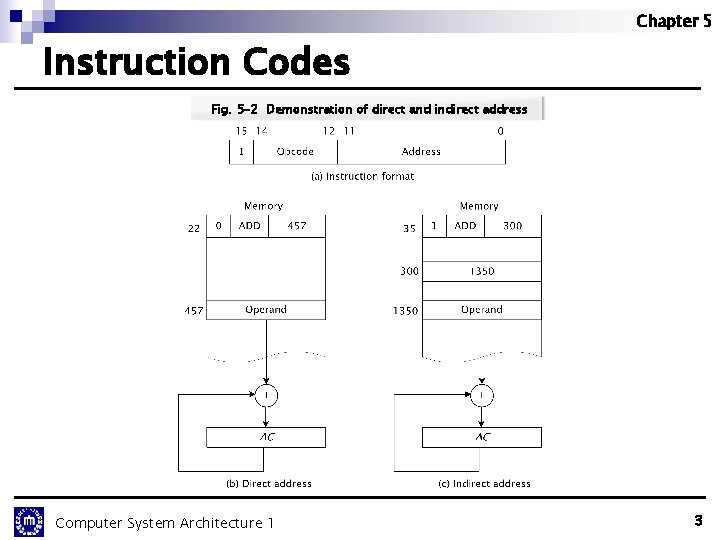

Chapter 5 Computer Registers n Basic computer registers and memory Fig. 5 -3 Basic computer registers and memory Computer System Architecture 1 4

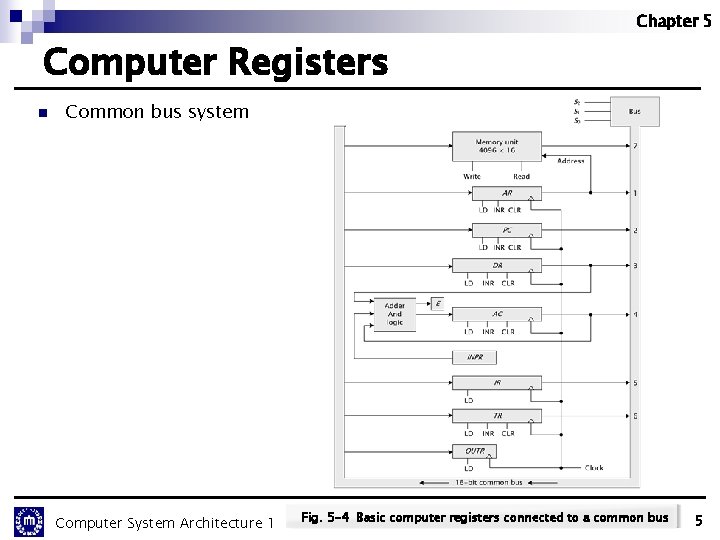

Chapter 5 Computer Registers n Common bus system Computer System Architecture 1 Fig. 5 -4 Basic computer registers connected to a common bus 5

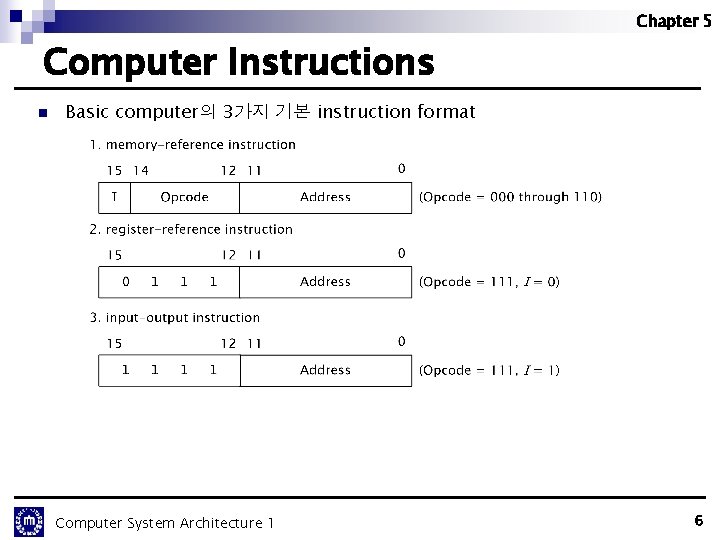

Chapter 5 Computer Instructions n Basic computer의 3가지 기본 instruction format Computer System Architecture 1 6

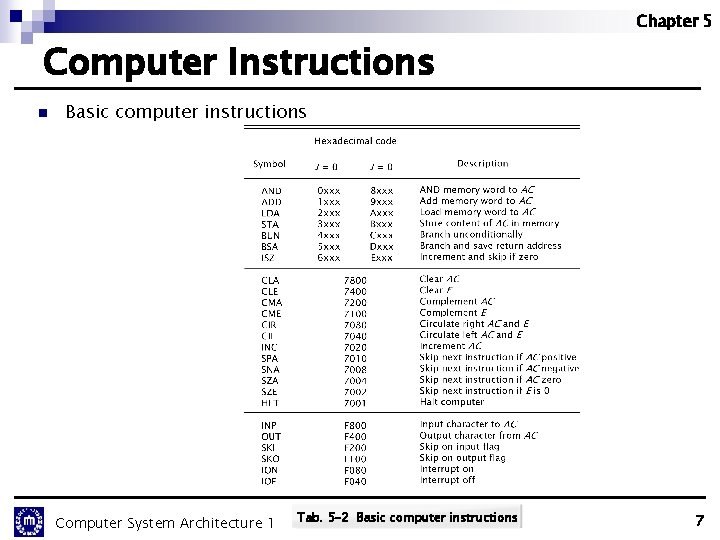

Chapter 5 Computer Instructions n Basic computer instructions Computer System Architecture 1 Tab. 5 -2 Basic computer instructions 7

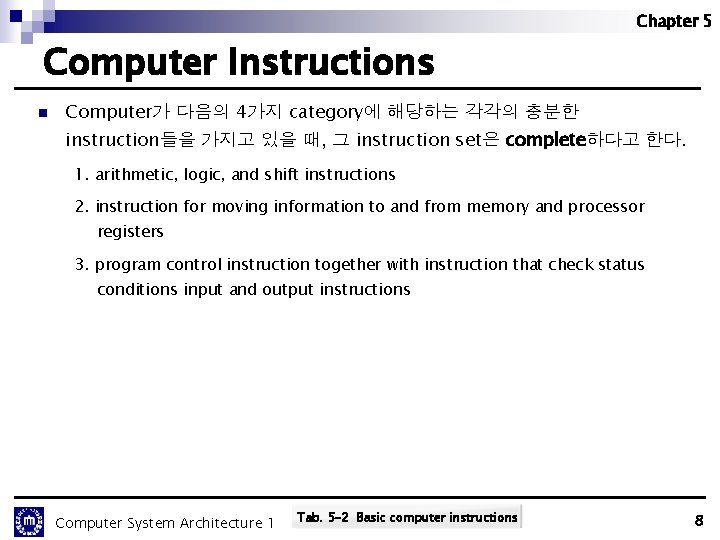

Chapter 5 Computer Instructions n Computer가 다음의 4가지 category에 해당하는 각각의 충분한 instruction들을 가지고 있을 때, 그 instruction set은 complete하다고 한다. 1. arithmetic, logic, and shift instructions 2. instruction for moving information to and from memory and processor registers 3. program control instruction together with instruction that check status conditions input and output instructions Computer System Architecture 1 Tab. 5 -2 Basic computer instructions 8

Chapter 5 Timing and Control n Basic computer의 모든 register에 대한 timing은 master clock generator가 제공하는 clock pulse에 의해 control된다. n Register 내용은 control signal에 의해 enable되어 있을 경우에만 clock pulse에 의해 바뀐다. n Control signal은 control unit에 의해 generate된다. n Control unit - Hardwired control : control logic이 gate, flip-flop, decoder, 또는 다른 logic circuit으로 구성된다 - Microprogrammed control : control 정보가 control memory에 저장 - Hardwired control은 속도가 빠른 대신 수정이 어렵다. Computer System Architecture 1 Tab. 5 -2 Basic computer instructions 9

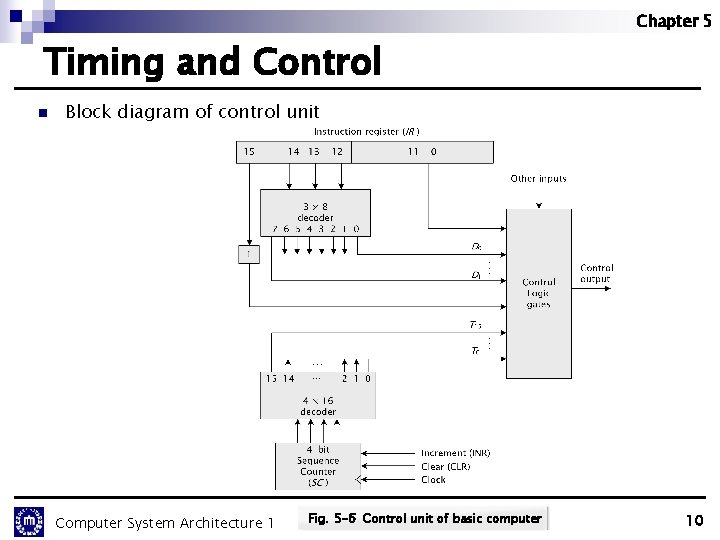

Chapter 5 Timing and Control n Block diagram of control unit Computer System Architecture 1 Fig. 5 -6 Control unit of basic computer 10

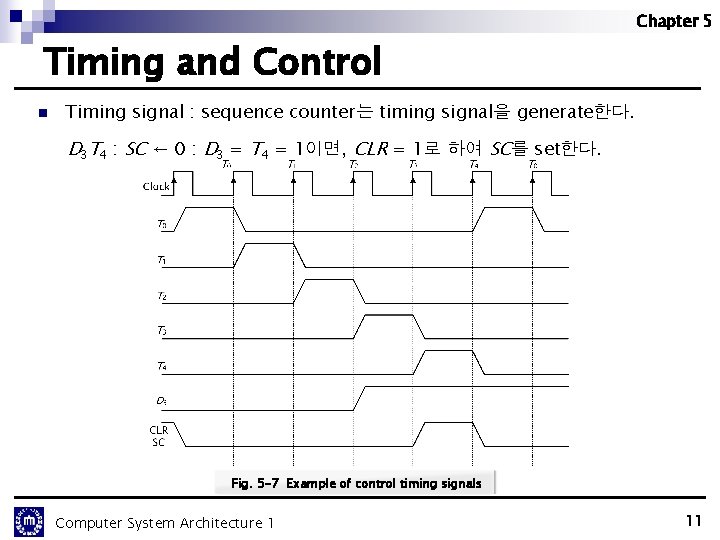

Chapter 5 Timing and Control n Timing signal : sequence counter는 timing signal을 generate한다. D 3 T 4 : SC ← 0 : D 3 = T 4 = 1이면, CLR = 1로 하여 SC를 set한다. Fig. 5 -7 Example of control timing signals Computer System Architecture 1 11

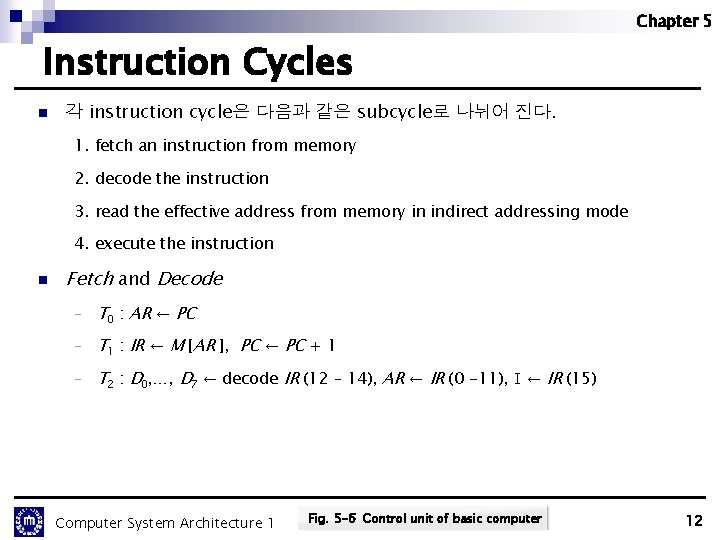

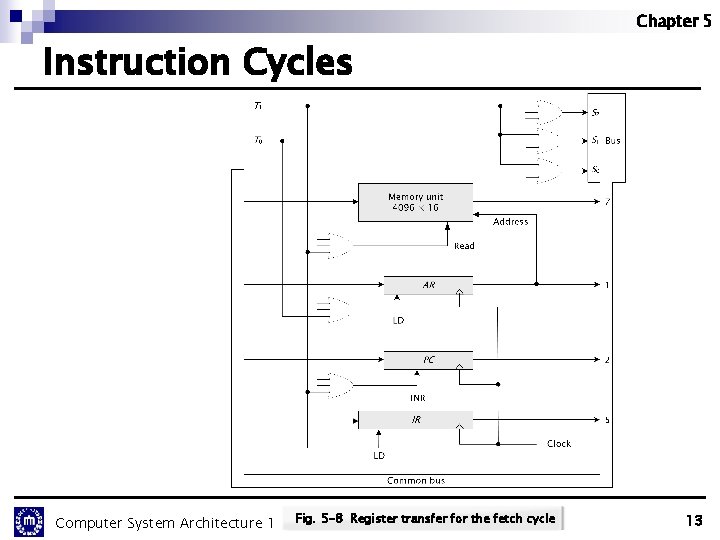

Chapter 5 Instruction Cycles n 각 instruction cycle은 다음과 같은 subcycle로 나뉘어 진다. 1. fetch an instruction from memory 2. decode the instruction 3. read the effective address from memory in indirect addressing mode 4. execute the instruction n Fetch and Decode - T 0 : AR ← PC - T 1 : IR ← M [AR ], PC ← PC + 1 - T 2 : D 0, …, D 7 ← decode IR (12 – 14), AR ← IR (0 -11), I ← IR (15) Computer System Architecture 1 Fig. 5 -6 Control unit of basic computer 12

Chapter 5 Instruction Cycles Computer System Architecture 1 Fig. 5 -8 Register transfer for the fetch cycle 13

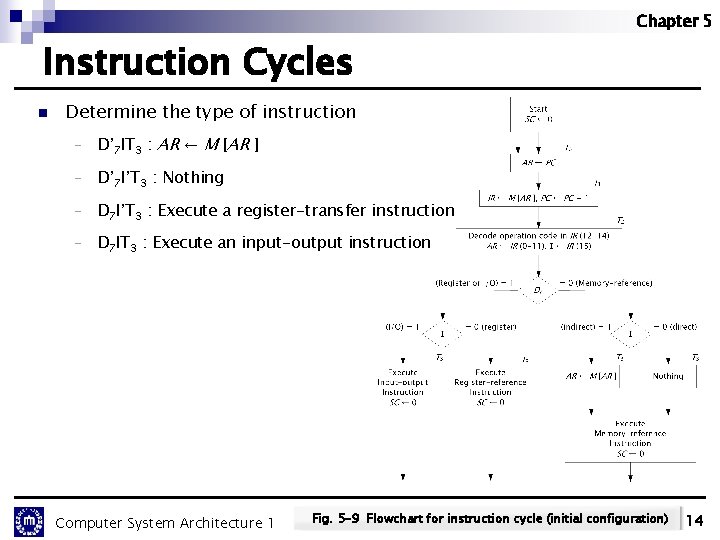

Chapter 5 Instruction Cycles n Determine the type of instruction - D’ 7 IT 3 : AR ← M [AR ] - D’ 7 I’T 3 : Nothing - D 7 I’T 3 : Execute a register-transfer instruction - D 7 IT 3 : Execute an input-output instruction Computer System Architecture 1 Fig. 5 -9 Flowchart for instruction cycle (initial configuration) 14

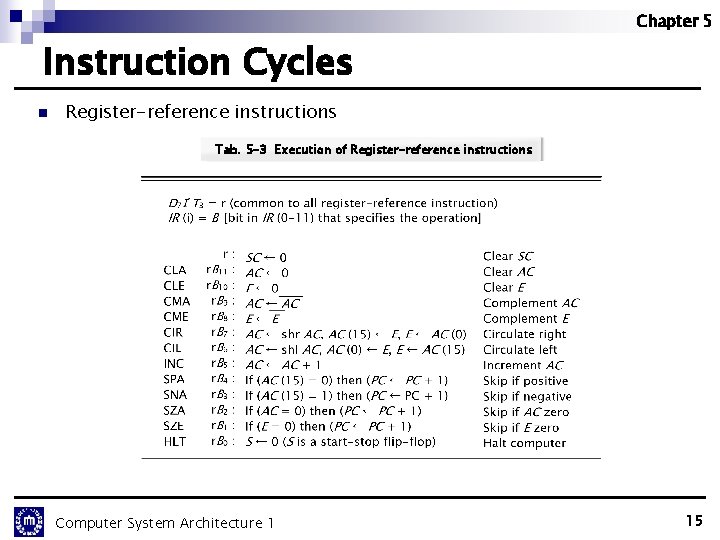

Chapter 5 Instruction Cycles n Register-reference instructions Tab. 5 -3 Execution of Register-reference instructions Computer System Architecture 1 15

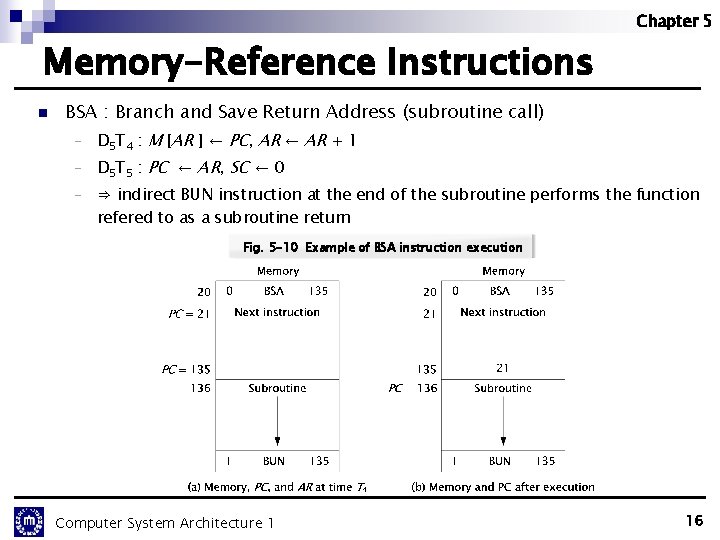

Chapter 5 Memory-Reference Instructions n BSA : Branch and Save Return Address (subroutine call) - D 5 T 4 : M [AR ] ← PC, AR ← AR + 1 D 5 T 5 : PC ← AR, SC ← 0 ⇒ indirect BUN instruction at the end of the subroutine performs the function refered to as a subroutine return Fig. 5 -10 Example of BSA instruction execution Computer System Architecture 1 16

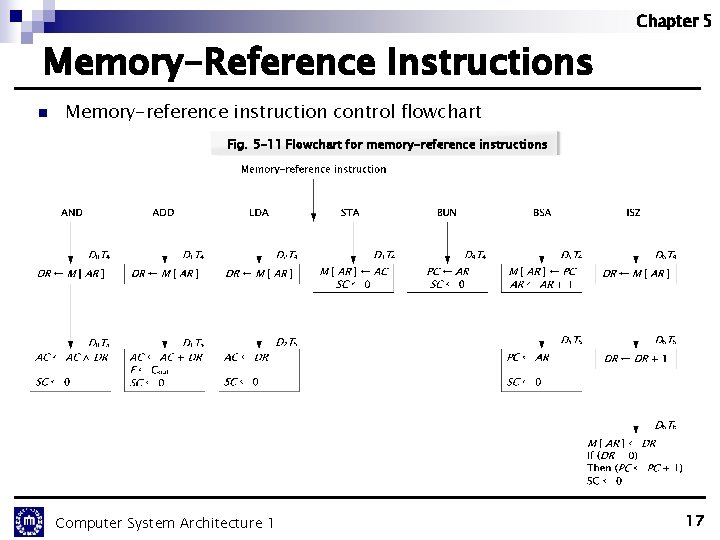

Chapter 5 Memory-Reference Instructions n Memory-reference instruction control flowchart Fig. 5 -11 Flowchart for memory-reference instructions Computer System Architecture 1 17

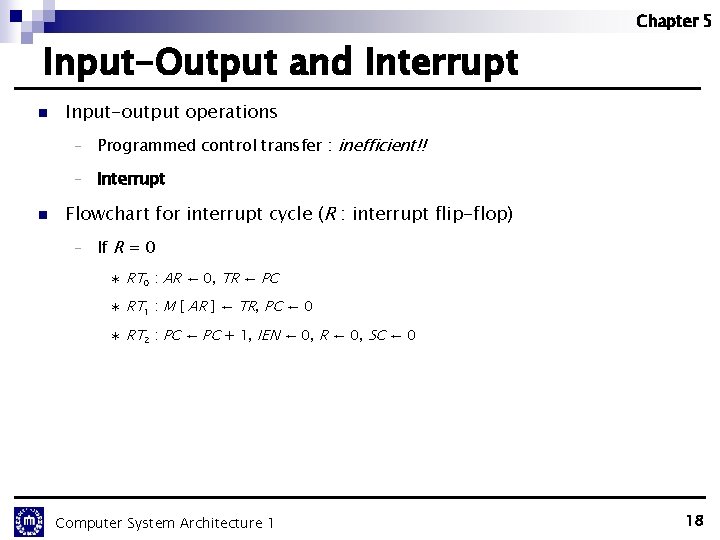

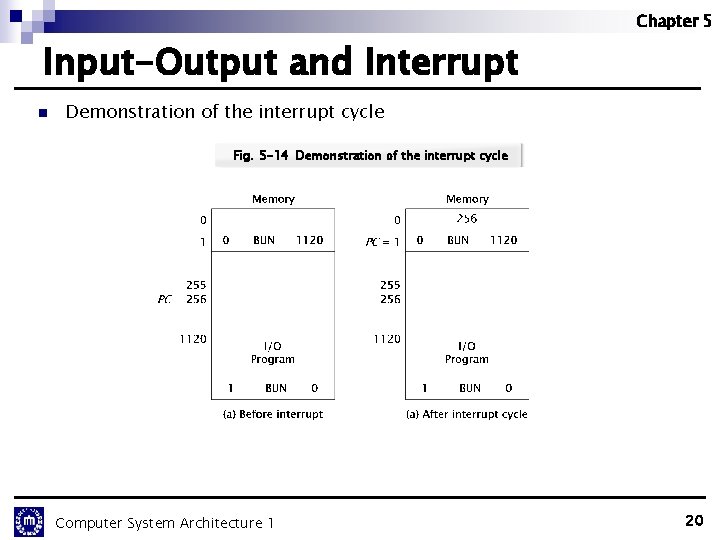

Chapter 5 Input-Output and Interrupt n n Input-output operations - Programmed control transfer : inefficient!! - Interrupt Flowchart for interrupt cycle (R : interrupt flip-flop) - If R = 0 ∗ RT 0 : AR ← 0, TR ← PC ∗ RT 1 : M [ AR ] ← TR, PC ← 0 ∗ RT 2 : PC ← PC + 1, IEN ← 0, R ← 0, SC ← 0 Computer System Architecture 1 18

Chapter 5 Input-Output and Interrupt Fig. 5 -13 Flowchart for interrupt cycle Computer System Architecture 1 19

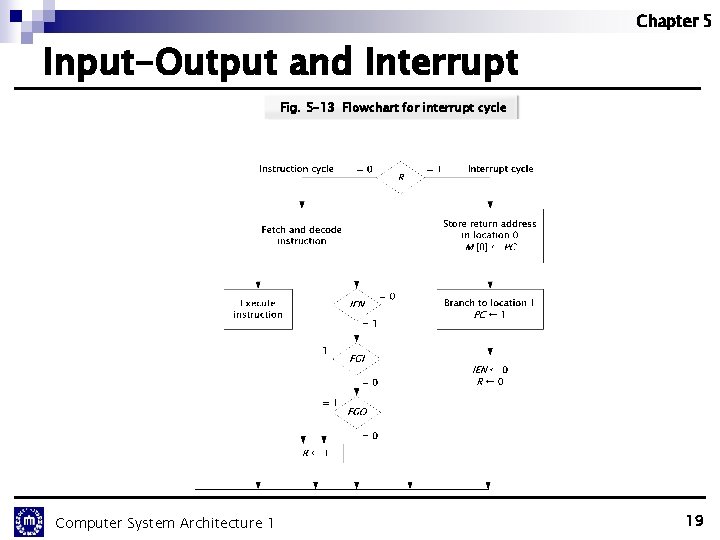

Chapter 5 Input-Output and Interrupt n Demonstration of the interrupt cycle Fig. 5 -14 Demonstration of the interrupt cycle Computer System Architecture 1 20

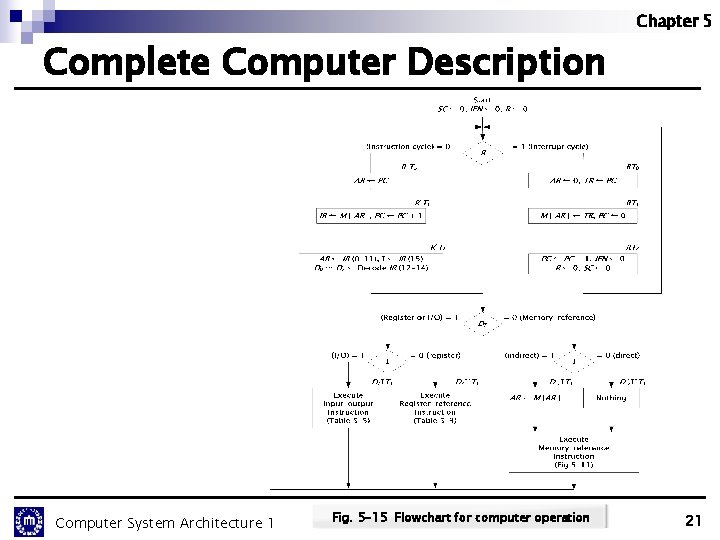

Chapter 5 Complete Computer Description Computer System Architecture 1 Fig. 5 -15 Flowchart for computer operation 21

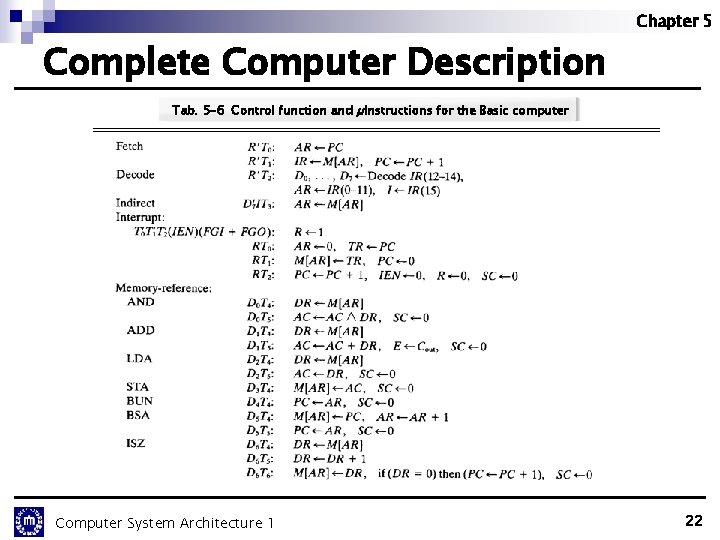

Chapter 5 Complete Computer Description Tab. 5 -6 Control function and µInstructions for the Basic computer Computer System Architecture 1 22

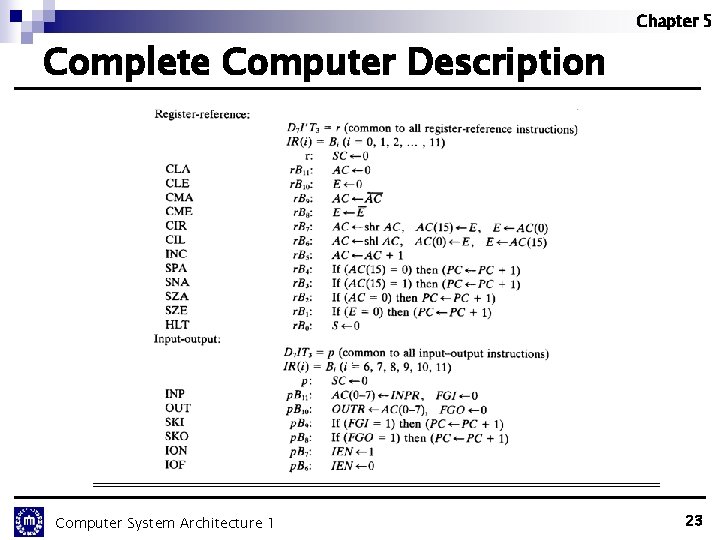

Chapter 5 Complete Computer Description Computer System Architecture 1 23

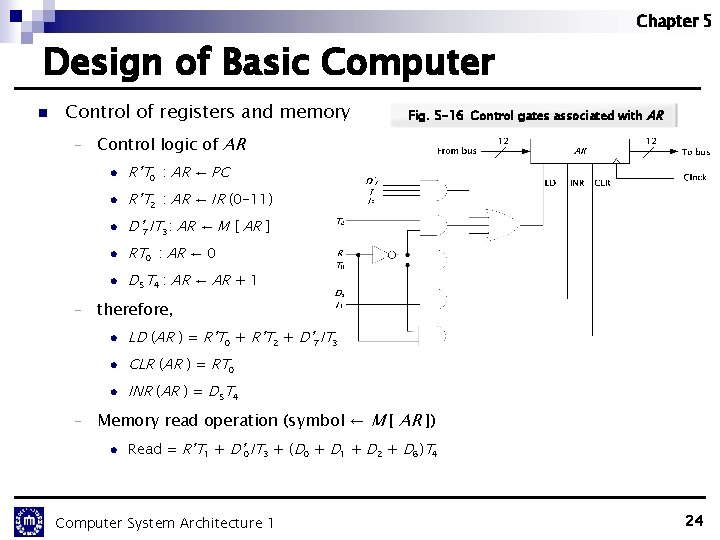

Chapter 5 Design of Basic Computer n Control of registers and memory - - - Fig. 5 -16 Control gates associated with AR Control logic of AR l R’T 0 : AR ← PC l R’T 2 : AR ← IR (0 -11) l D’ 7 IT 3: AR ← M [ AR ] l RT 0 : AR ← 0 l D 5 T 4 : AR ← AR + 1 therefore, l LD (AR ) = R’T 0 + R’T 2 + D’ 7 IT 3 l CLR (AR ) = RT 0 l INR (AR ) = D 5 T 4 Memory read operation (symbol ← M [ AR ]) l Read = R’T 1 + D’ 0 IT 3 + (D 0 + D 1 + D 2 + D 6)T 4 Computer System Architecture 1 24

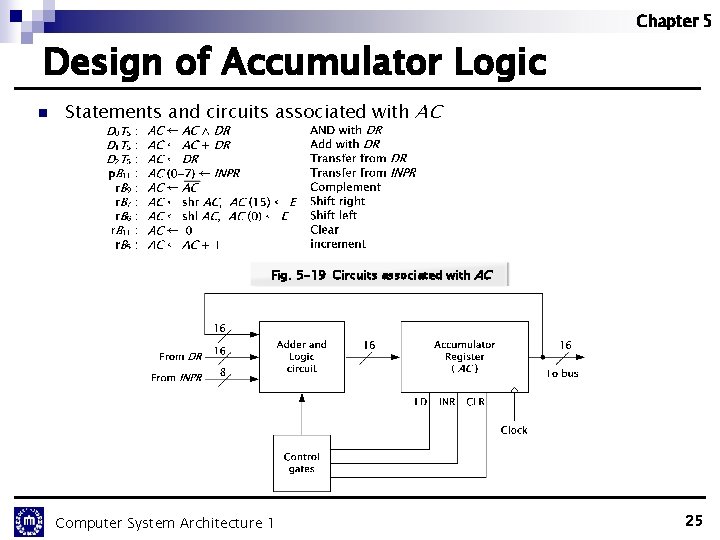

Chapter 5 Design of Accumulator Logic n Statements and circuits associated with AC Fig. 5 -19 Circuits associated with AC Computer System Architecture 1 25

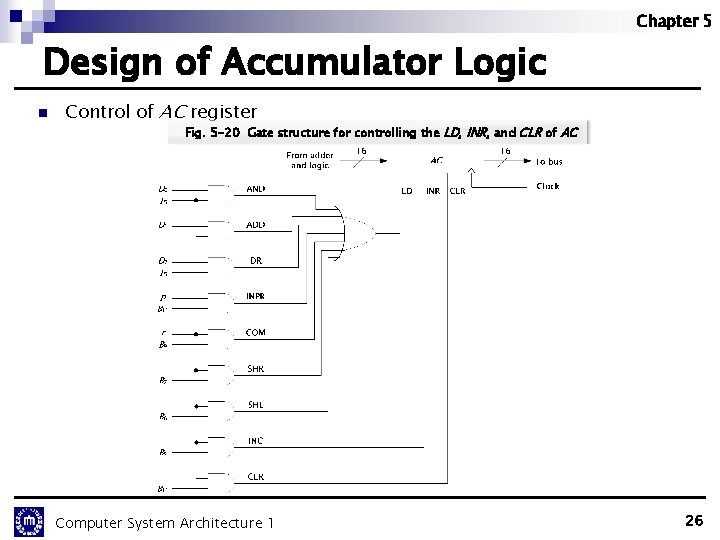

Chapter 5 Design of Accumulator Logic n Control of AC register Fig. 5 -20 Gate structure for controlling the LD, INR, and CLR of AC Computer System Architecture 1 26

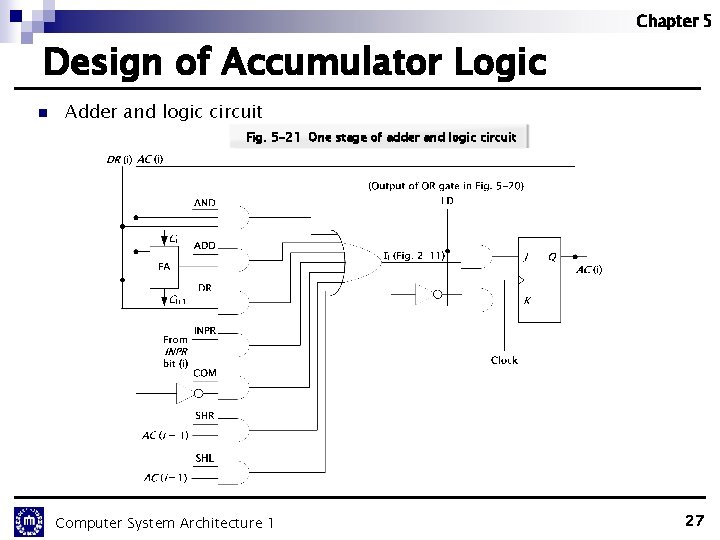

Chapter 5 Design of Accumulator Logic n Adder and logic circuit Fig. 5 -21 One stage of adder and logic circuit Computer System Architecture 1 27

- Slides: 27