Review of Digital Logic Design Concepts Basic Digital

Review of Digital Logic Design Concepts

Basic Digital Logic Gates

Digital (Positive) Logic • Logic Level High – 1 or ONE or HIGH or +Vdd or yes or ON or True • Logic Level Low – 0 or ZERO or LOW or L or GND or no or OFF or False 1 0

Definitions • Assert – A control signal is asserted when the action control by the signal is being done. – Ex: Assume a control signal labeled en • en is asserted when en is high • Active low signal – A signal that is asserted when it is a logic level low. • Active high signal – A signal that is asserted when it is a logic level high.

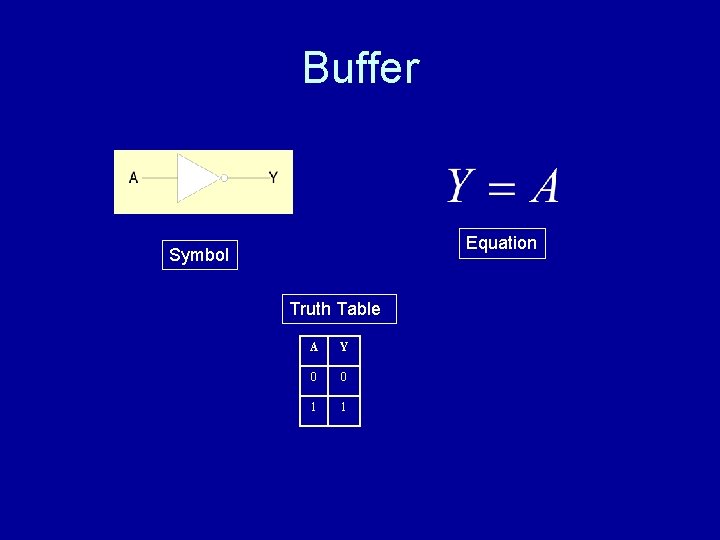

Buffer Equation Symbol Truth Table A Y 0 0 1 1

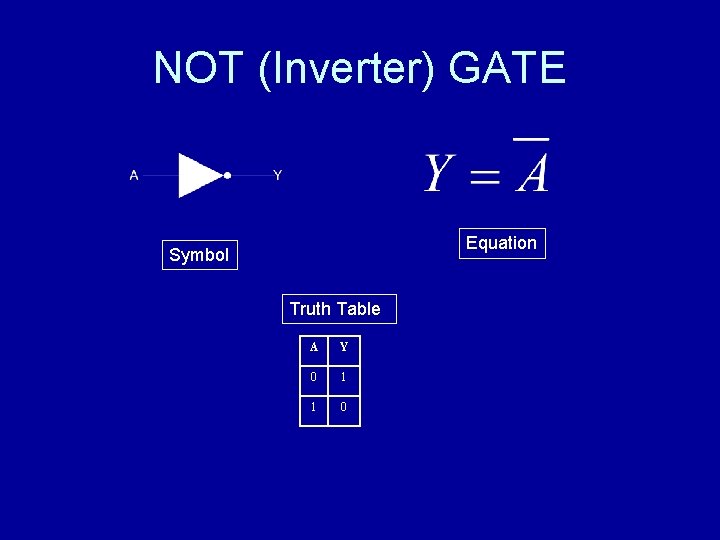

NOT (Inverter) GATE Equation Symbol Truth Table A Y 0 1 1 0

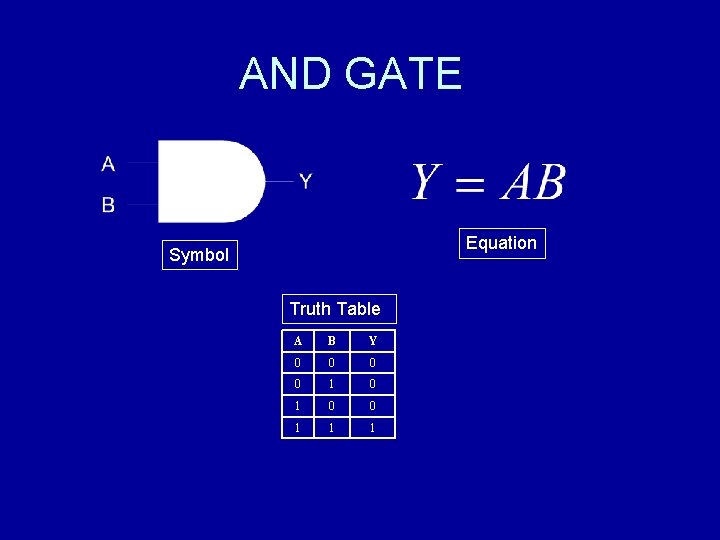

AND GATE Equation Symbol Truth Table A B Y 0 0 1 1 1

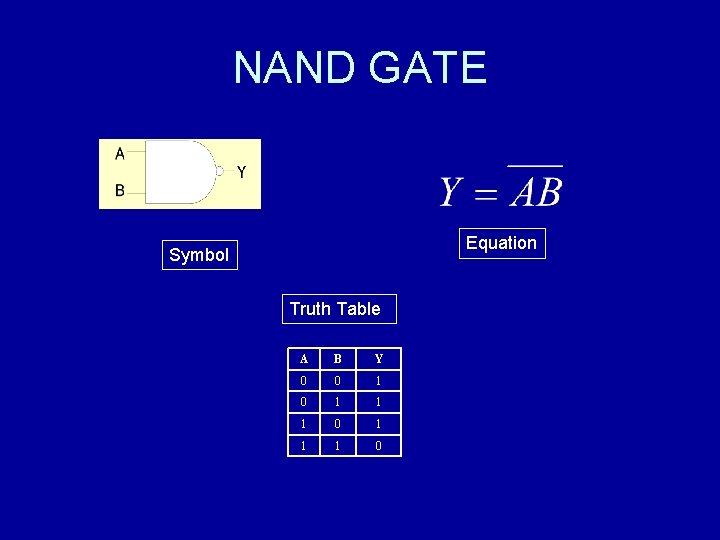

NAND GATE Equation Symbol Truth Table A B Y 0 0 1 1 1 0

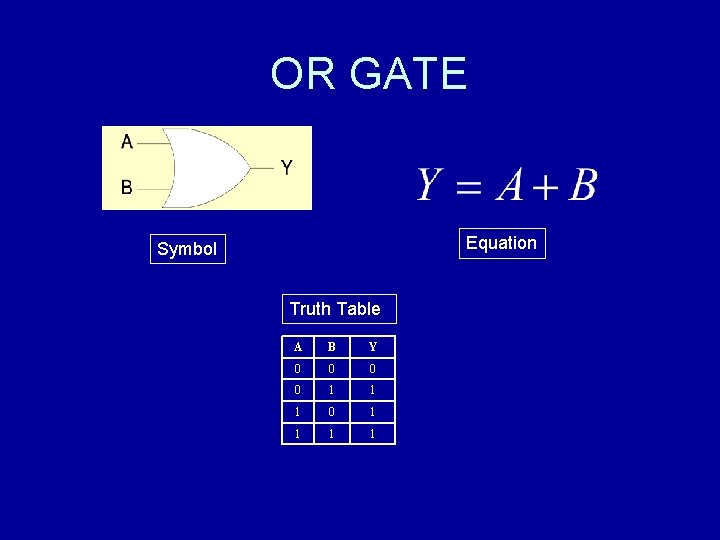

OR GATE Equation Symbol Truth Table A B Y 0 0 1 1 1 0 1 1

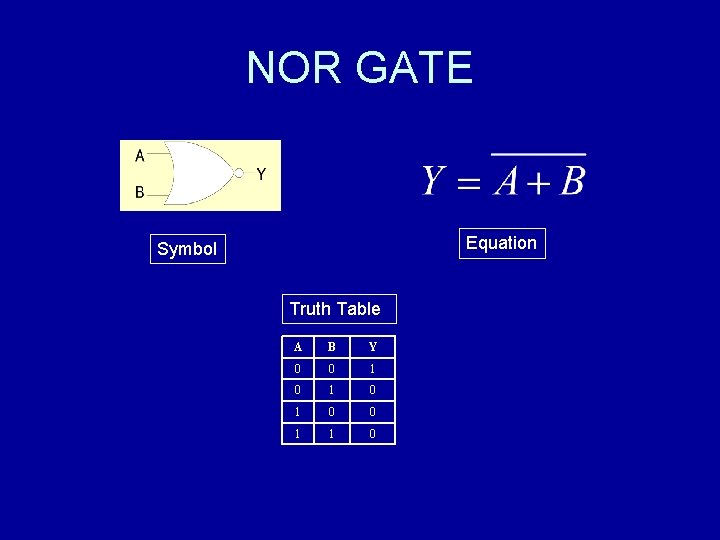

NOR GATE Equation Symbol Truth Table A B Y 0 0 1 0 1 0 0 1 1 0

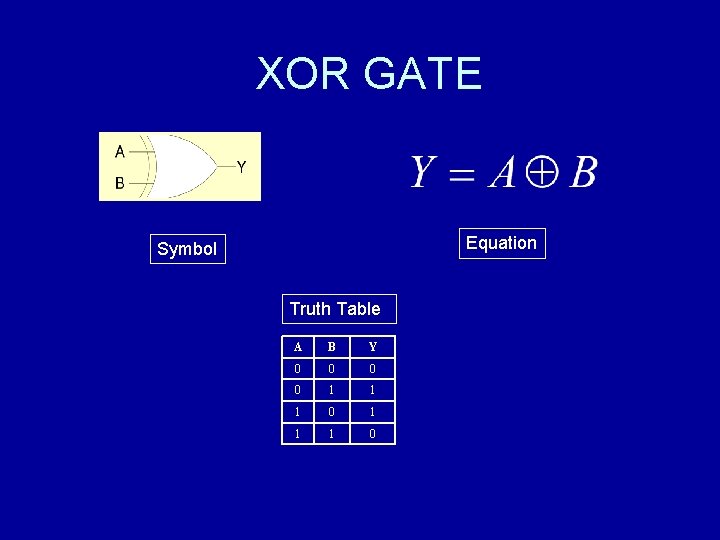

XOR GATE Equation Symbol Truth Table A B Y 0 0 1 1 1 0

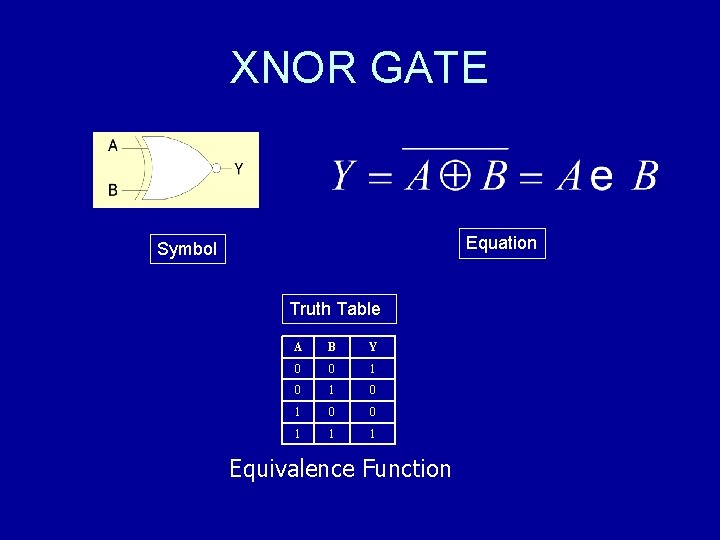

XNOR GATE Equation Symbol Truth Table A B Y 0 0 1 0 1 0 0 1 1 1 Equivalence Function

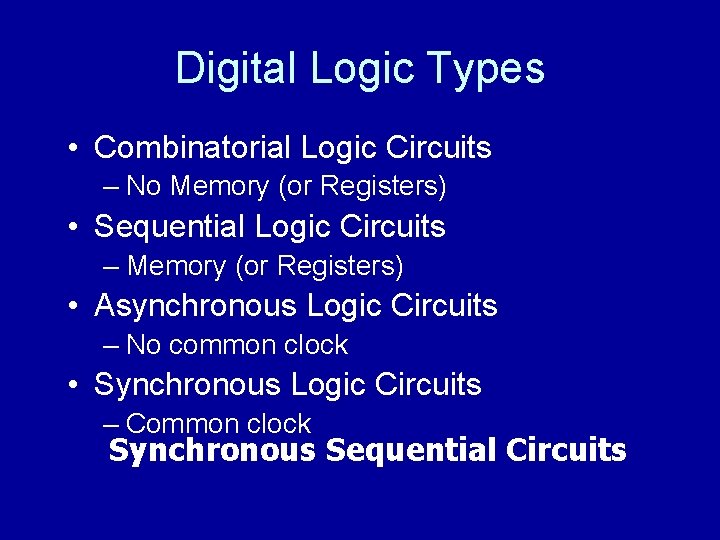

Digital Logic Types • Combinatorial Logic Circuits – No Memory (or Registers) • Sequential Logic Circuits – Memory (or Registers) • Asynchronous Logic Circuits – No common clock • Synchronous Logic Circuits – Common clock Synchronous Sequential Circuits

Memory Storage Registers Latches and Flip-Flops

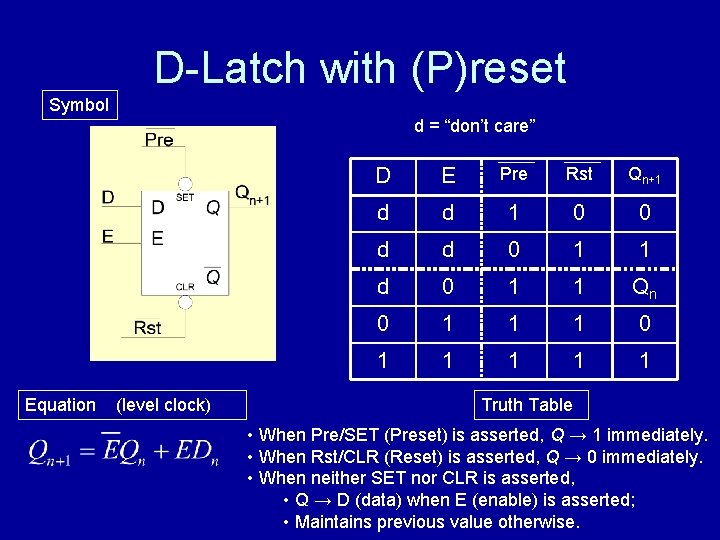

D-Latch with (P)reset Symbol d = “don’t care” Equation (level clock) D E Pre Rst Qn+1 d d 1 0 0 d d 0 1 1 Qn 0 1 1 1 1 1 Truth Table • When Pre/SET (Preset) is asserted, Q → 1 immediately. • When Rst/CLR (Reset) is asserted, Q → 0 immediately. • When neither SET nor CLR is asserted, • Q → D (data) when E (enable) is asserted; • Maintains previous value otherwise.

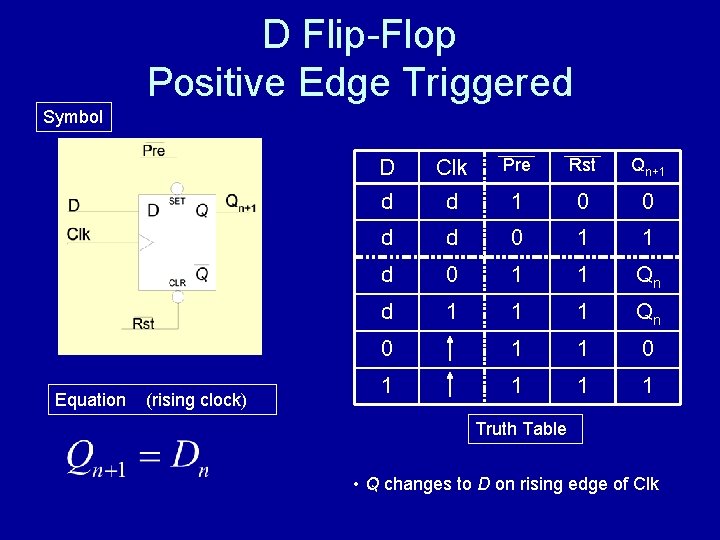

D Flip-Flop Positive Edge Triggered Symbol Equation (rising clock) D Clk Pre Rst Qn+1 d d 1 0 0 d d 0 1 1 Qn d 1 1 1 Qn 0 1 1 1 1 Truth Table • Q changes to D on rising edge of Clk

Finite State Machines

Finite State Machines (FSMs) • Three basic types 1. Moore FSM 2. Mealy FSM 3. Mealy-Moore FSM

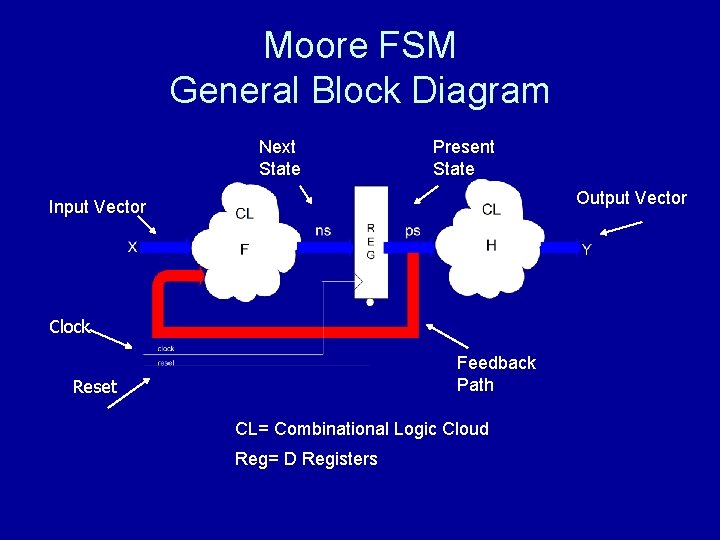

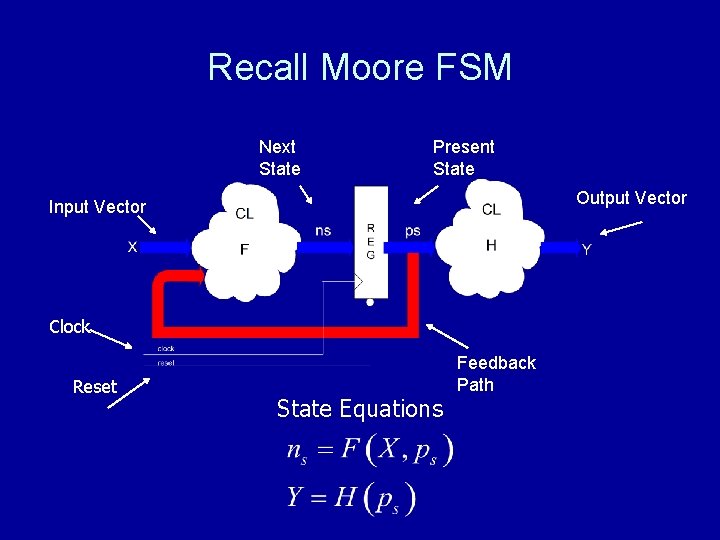

Moore FSM General Block Diagram Next State Present State Output Vector Input Vector Clock Feedback Path Reset CL= Combinational Logic Cloud Reg= D Registers

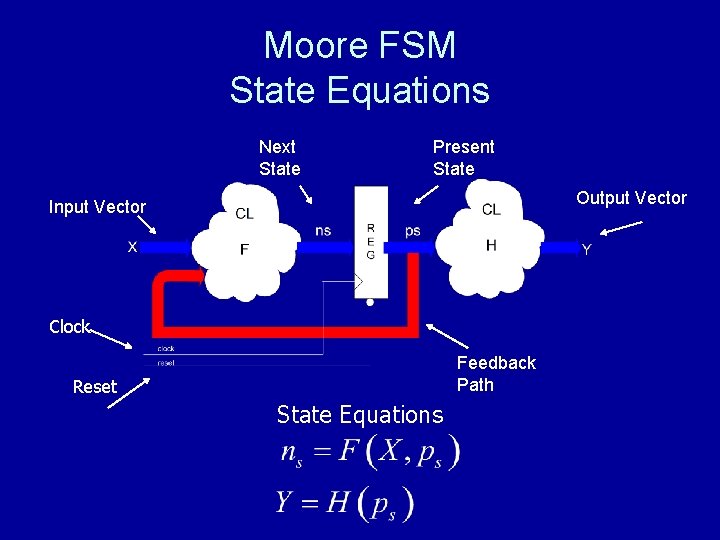

Moore FSM State Equations Next State Present State Output Vector Input Vector Clock Feedback Path Reset State Equations

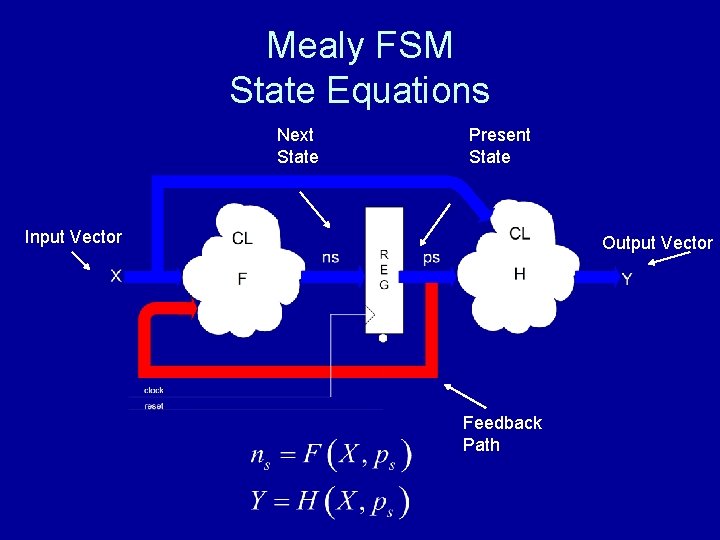

Mealy FSM State Equations Next State Present State Input Vector Output Vector Feedback Path

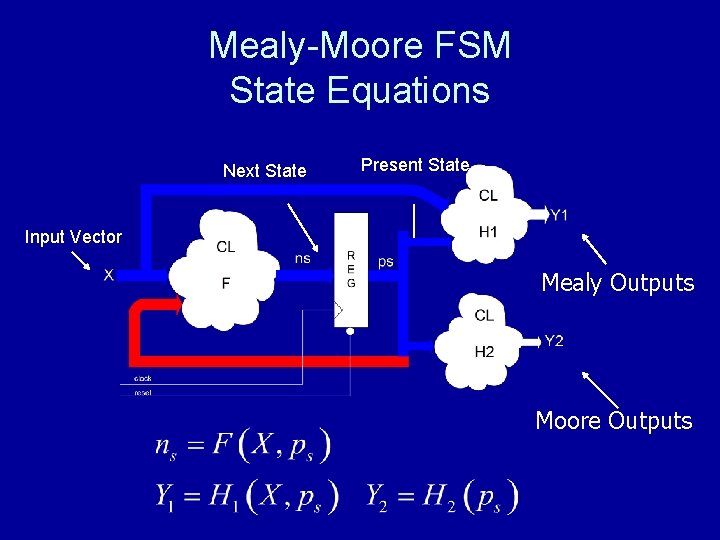

Mealy-Moore FSM State Equations Next State Present State Input Vector Mealy Outputs Moore Outputs

State Diagrams

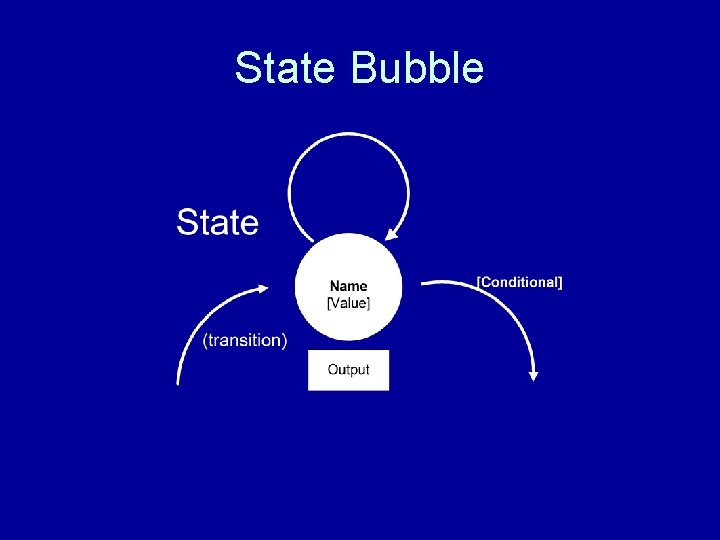

State Bubble

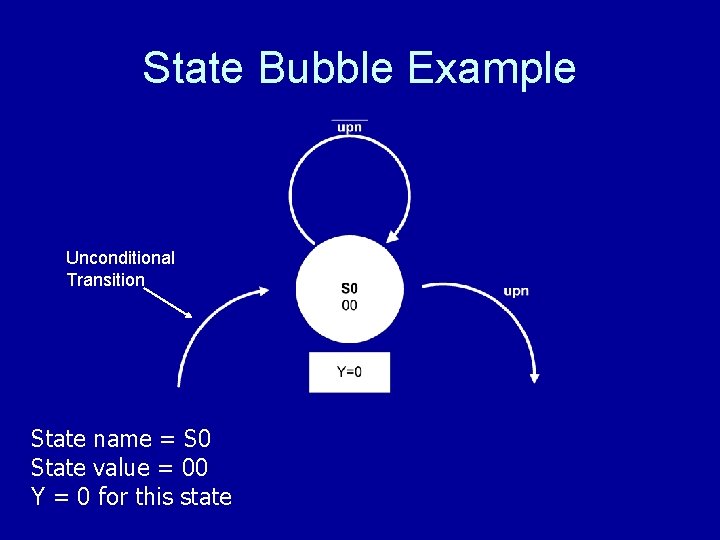

State Bubble Example Unconditional Transition State name = S 0 State value = 00 Y = 0 for this state

FSM Example

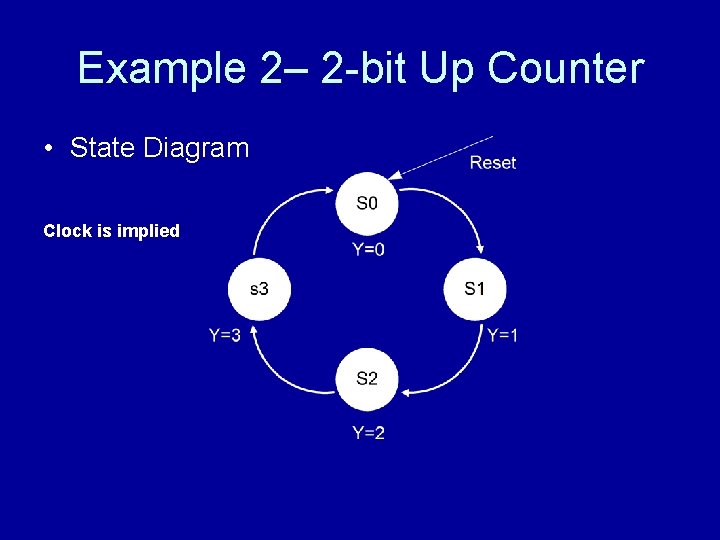

Example 2– 2 -bit Up Counter • State Diagram Clock is implied

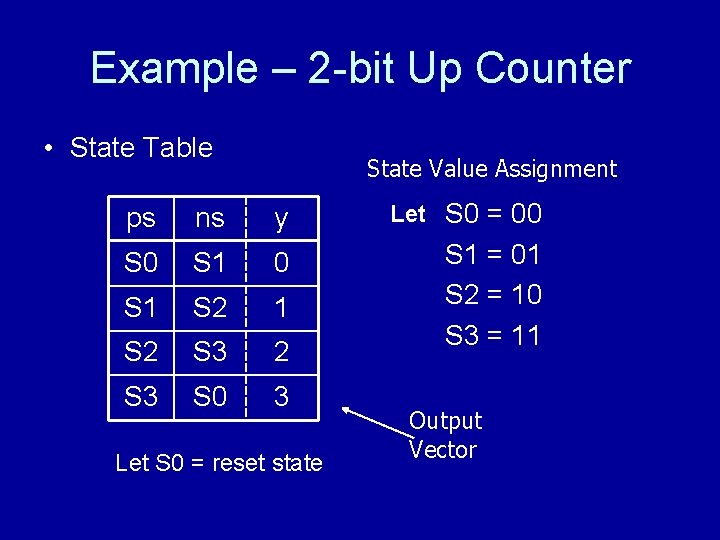

Example – 2 -bit Up Counter • State Table State Value Assignment ps ns y Let S 0 = 00 S 1 S 2 S 3 2 S 1 = 01 S 2 = 10 S 3 = 11 S 3 S 0 3 Let S 0 = reset state Output Vector

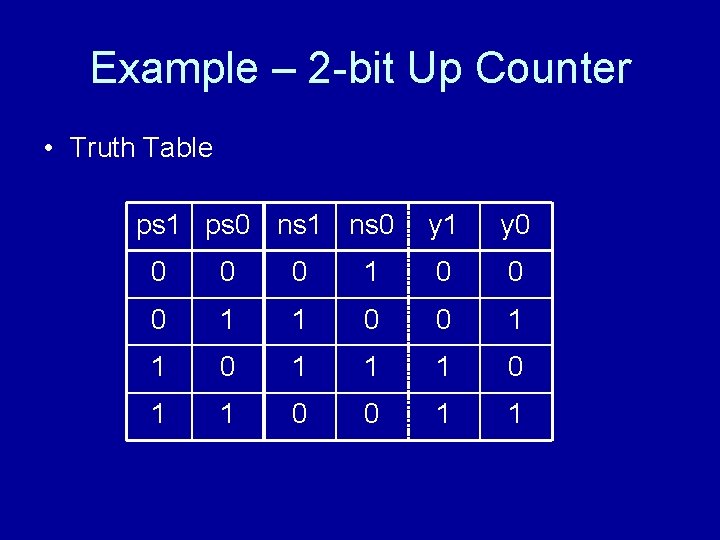

Example – 2 -bit Up Counter • Truth Table ps 1 ps 0 ns 1 ns 0 y 1 y 0 0 1 0 0 0 1 1 1 0 0 1 1

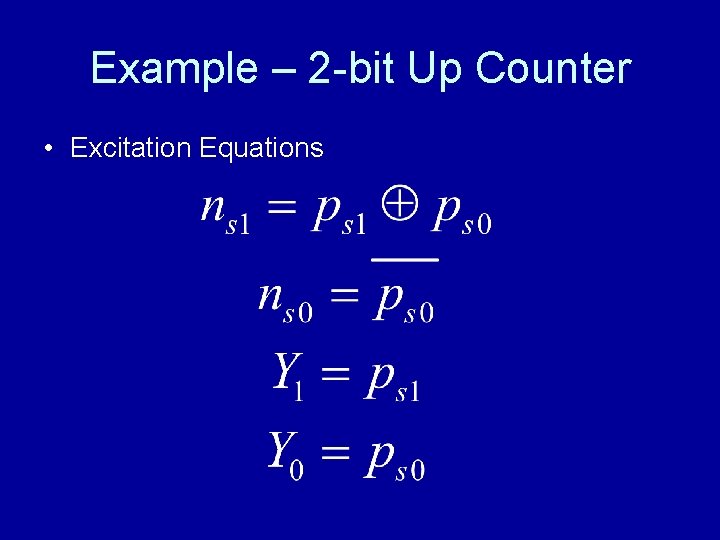

Example – 2 -bit Up Counter • Excitation Equations

Recall Moore FSM Next State Present State Output Vector Input Vector Clock Reset State Equations Feedback Path

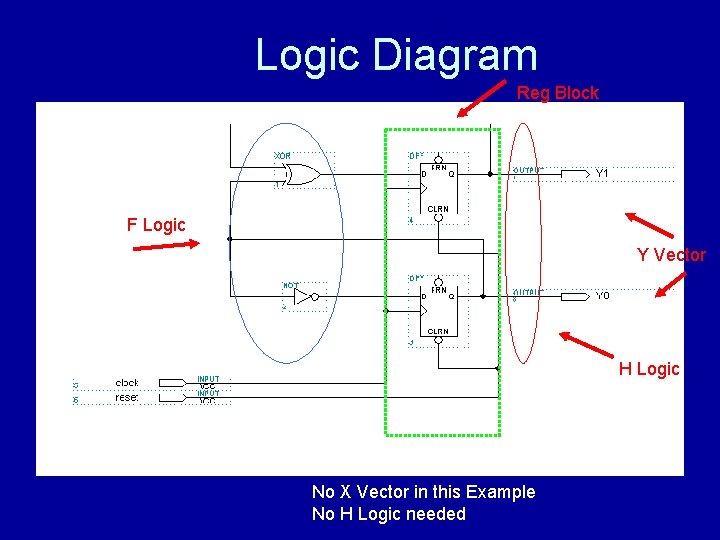

Logic Diagram Reg Block F Logic Y Vector H Logic No X Vector in this Example No H Logic needed

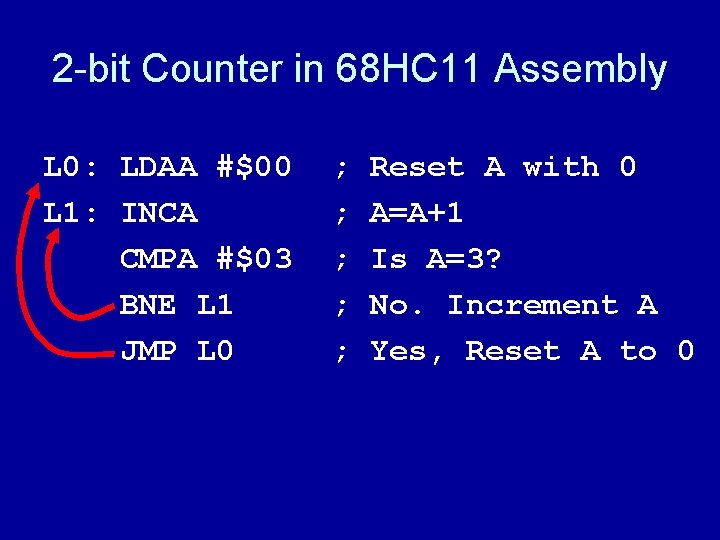

2 -bit Counter in 68 HC 11 Assembly L 0: LDAA #$00 L 1: INCA CMPA #$03 BNE L 1 JMP L 0 ; ; ; Reset A with 0 A=A+1 Is A=3? No. Increment A Yes, Reset A to 0

- Slides: 33