CMOS FIRSTORDER SIGMADELTA MODULATOR ACEs I II III

- Slides: 30

CMOS FIRST-ORDER SIGMA-DELTA MODULATOR 팀명 : ACEs

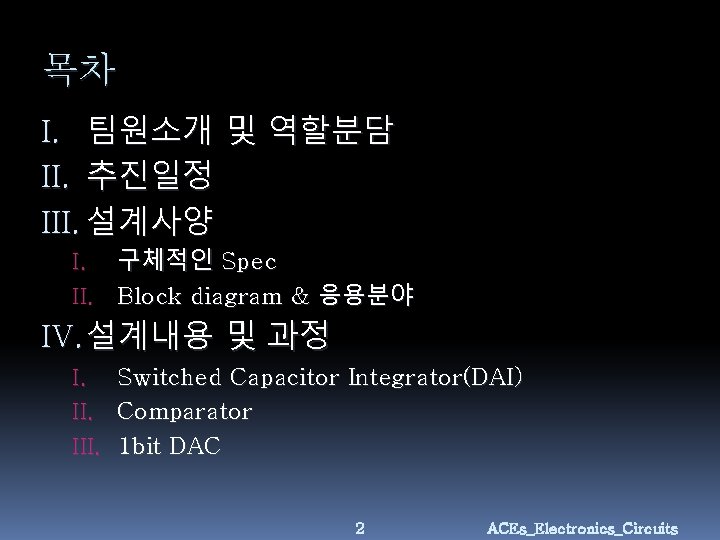

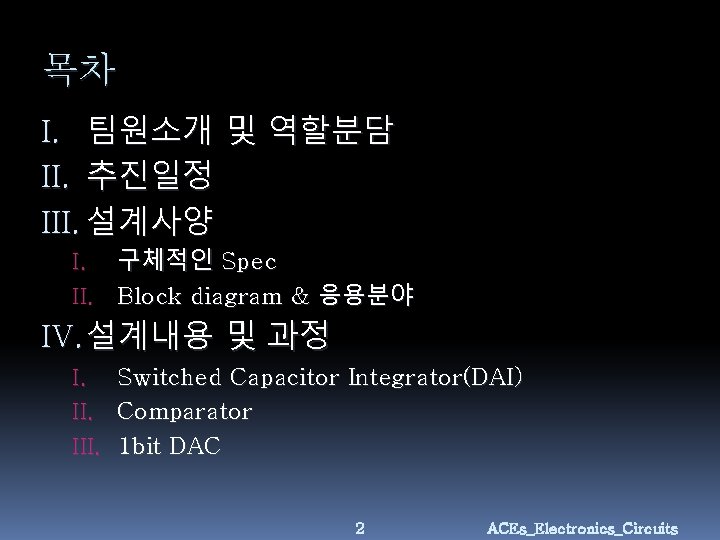

목차 I. 팀원소개 및 역할분담 II. 추진일정 III. 설계사양 구체적인 Spec II. Block diagram & 응용분야 I. IV. 설계내용 및 과정 Switched Capacitor Integrator(DAI) II. Comparator III. 1 bit DAC I. 2 ACEs_Electronics_Circuits

목차 V. 설계결과 VI. 결론 및 고찰 VII. 참고문헌 3 ACEs_Electronics_Circuits

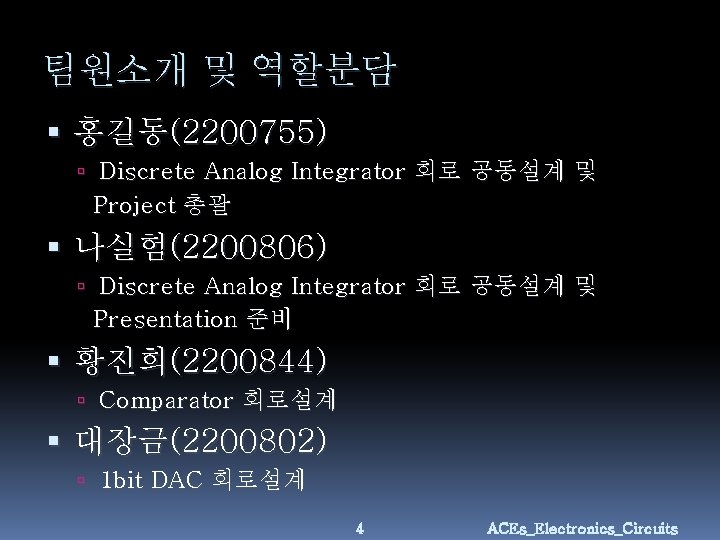

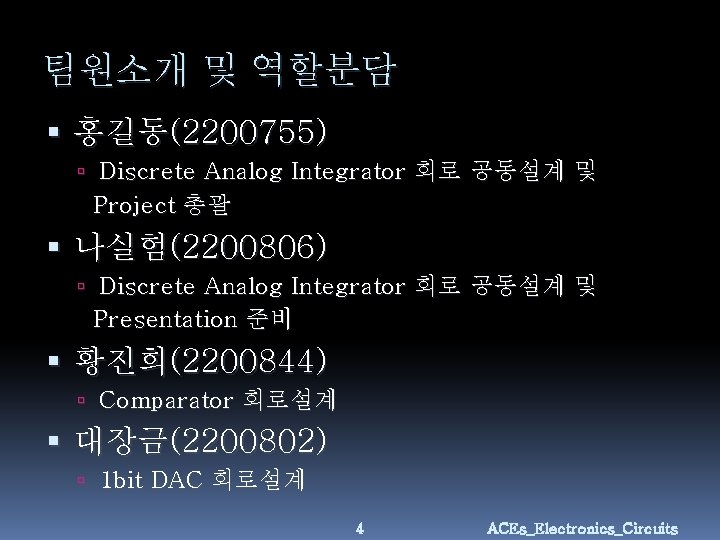

팀원소개 및 역할분담 홍길동(2200755) Discrete Analog Integrator 회로 공동설계 및 Project 총괄 나실험(2200806) Discrete Analog Integrator 회로 공동설계 및 Presentation 준비 황진희(2200844) Comparator 회로설계 대장금(2200802) 1 bit DAC 회로설계 4 ACEs_Electronics_Circuits

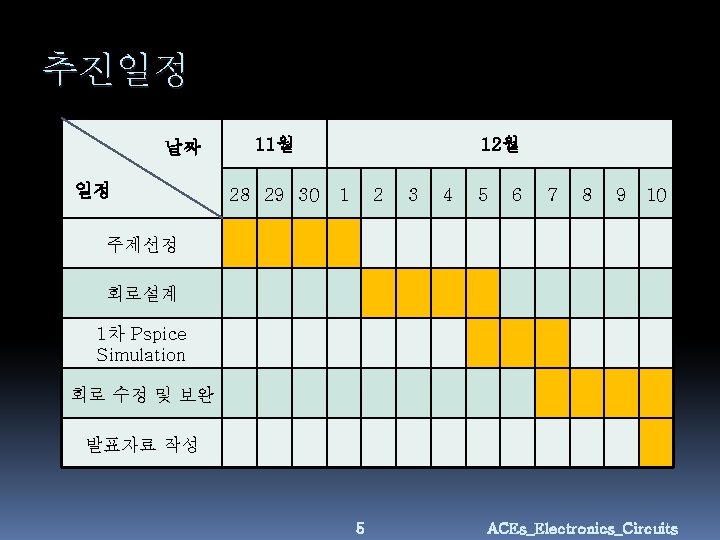

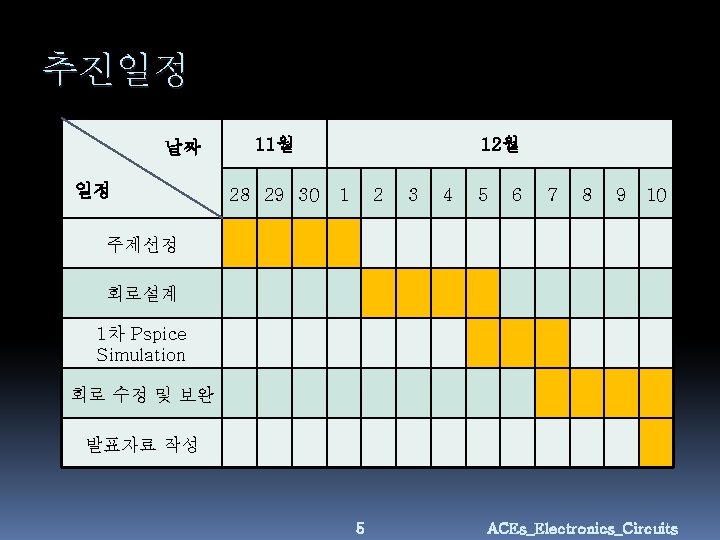

추진일정 날짜 일정 11월 28 29 30 12월 1 2 3 4 5 6 7 8 9 10 주제선정 회로설계 1차 Pspice Simulation 회로 수정 및 보완 발표자료 작성 5 ACEs_Electronics_Circuits

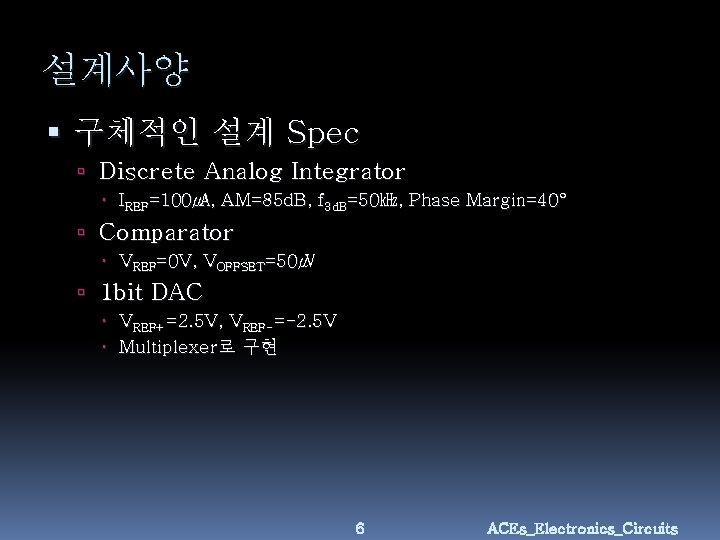

설계사양 구체적인 설계 Spec Discrete Analog Integrator IREF=100㎂, AM=85 d. B, f 3 d. B=50㎑, Phase Margin=40° Comparator VREF=0 V, VOFFSET=50㎶ 1 bit DAC VREF+=2. 5 V, VREF-=-2. 5 V Multiplexer로 구현 6 ACEs_Electronics_Circuits

설계사양 Block diagram Analog Input ∑ Switched Capacitor Integrator Analog-to-Digital Converter(Comparator) 1 bit Digital Output 1 bit Digital-to-Analog Converter 7 ACEs_Electronics_Circuits

응용분야 ADC(DSP, RFID 등) 오디오용 DAC 광대역 유무선 송수신기(GSM, WCDMA 등) 8 ACEs_Electronics_Circuits

Analog-to-Digital Converter Flash ADC Pipeline ADC Successive Approximation ADC Sigma-Delta ADC 9 ACEs_Electronics_Circuits

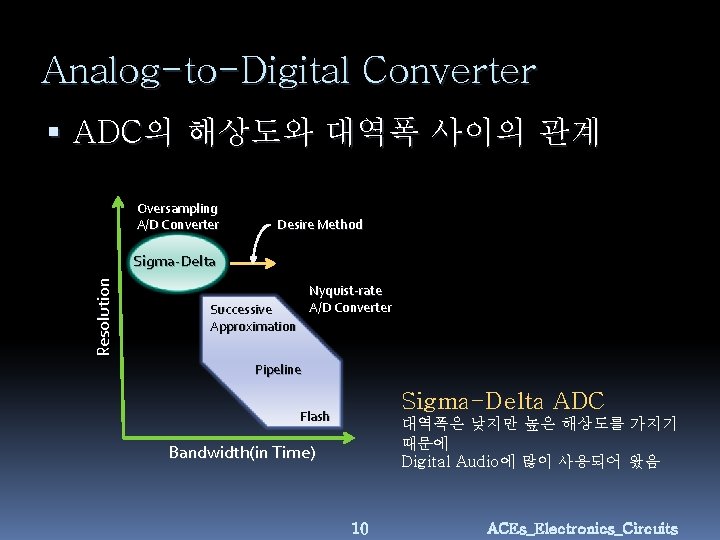

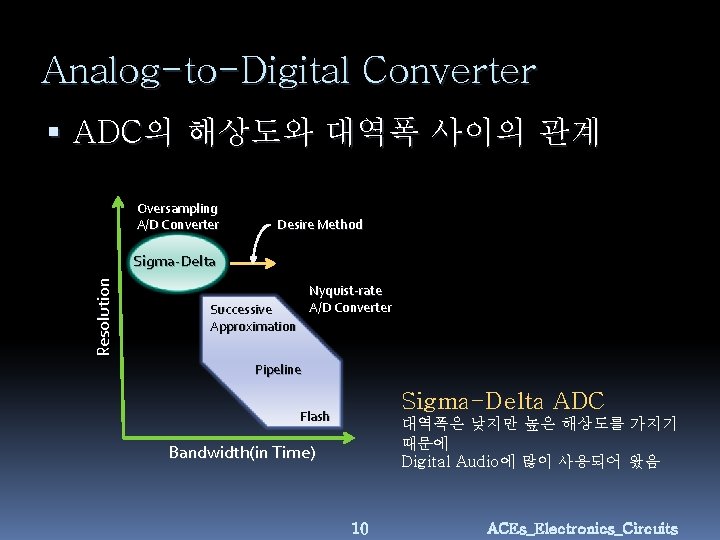

Analog-to-Digital Converter ADC의 해상도와 대역폭 사이의 관계 Oversampling A/D Converter Desire Method R e s ol u ti on Sigma-Delta Nyquist-rate A/D Converter Successive Approximation Pipeline Sigma-Delta ADC Flash 대역폭은 낮지만 높은 해상도를 가지기 때문에 Digital Audio에 많이 사용되어 왔음 Bandwidth(in Time) 10 ACEs_Electronics_Circuits

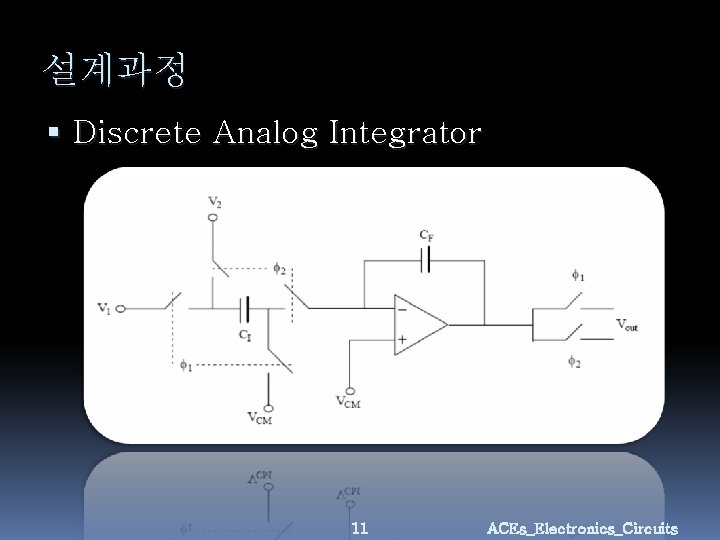

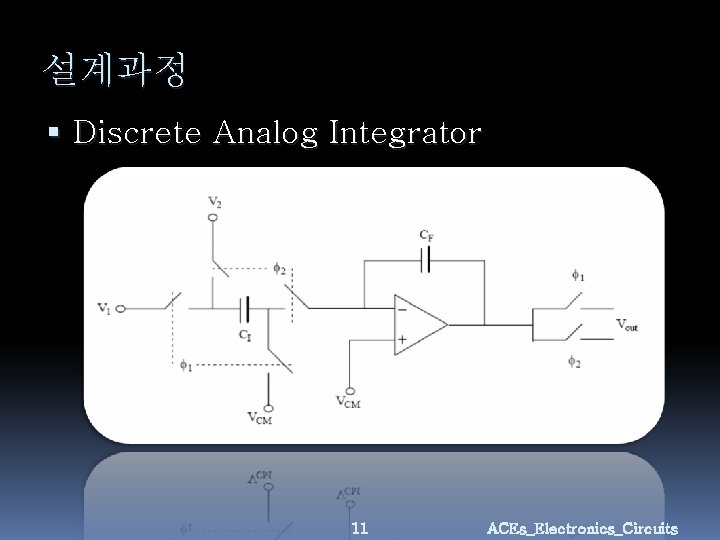

설계과정 Discrete Analog Integrator 11 ACEs_Electronics_Circuits

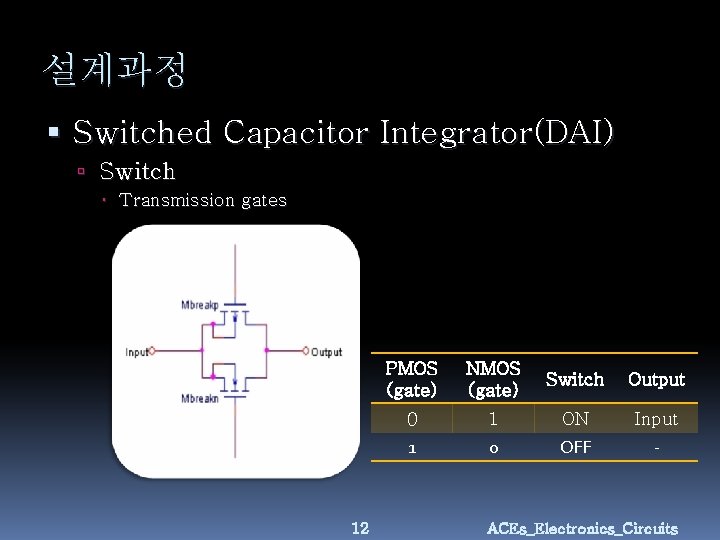

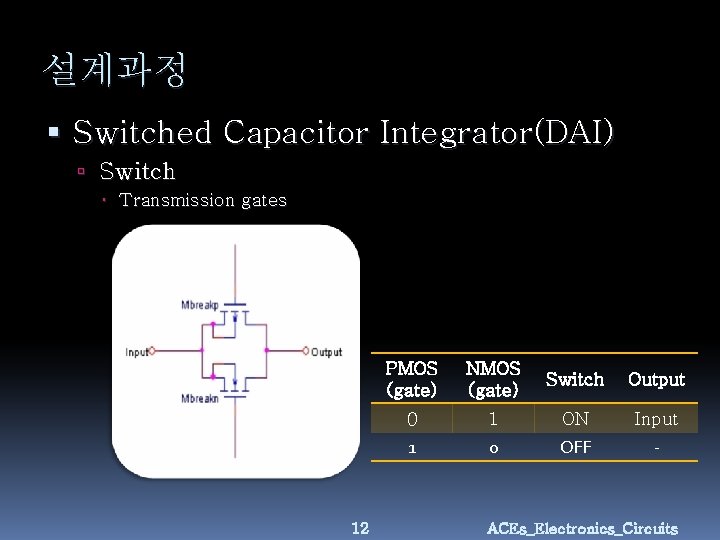

설계과정 Switched Capacitor Integrator(DAI) Switch Transmission gates 12 PMOS (gate) NMOS (gate) Switch Output 0 1 ON Input 1 0 OFF - ACEs_Electronics_Circuits

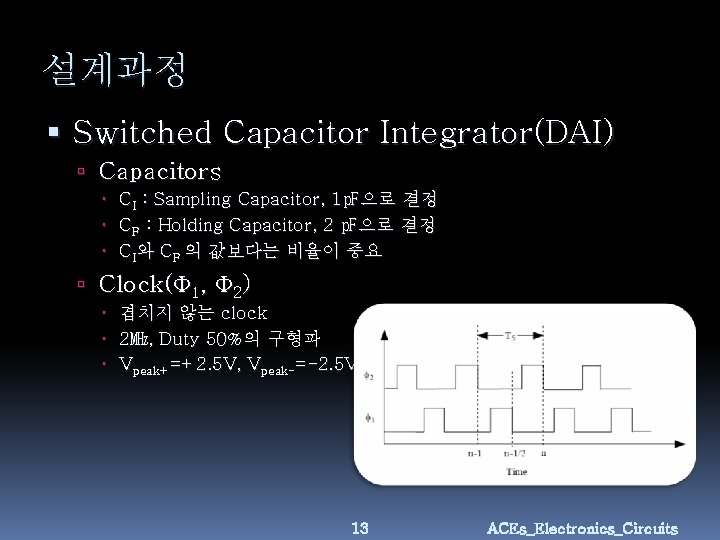

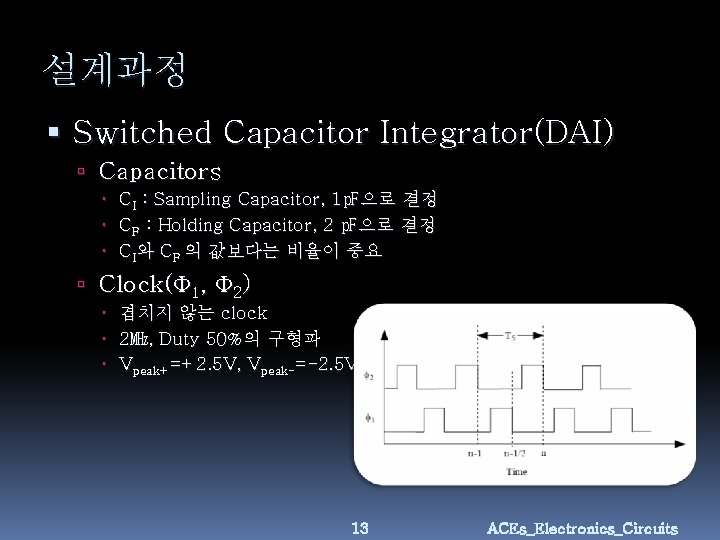

설계과정 Switched Capacitor Integrator(DAI) Capacitors CI : Sampling Capacitor, 1㎊으로 결정 CF : Holding Capacitor, 2 ㎊으로 결정 CI와 CF 의 값보다는 비율이 중요 Clock(Ф 1, Ф 2) 겹치지 않는 clock 2㎒, Duty 50%의 구형파 Vpeak+=+2. 5 V, Vpeak-=-2. 5 V 13 ACEs_Electronics_Circuits

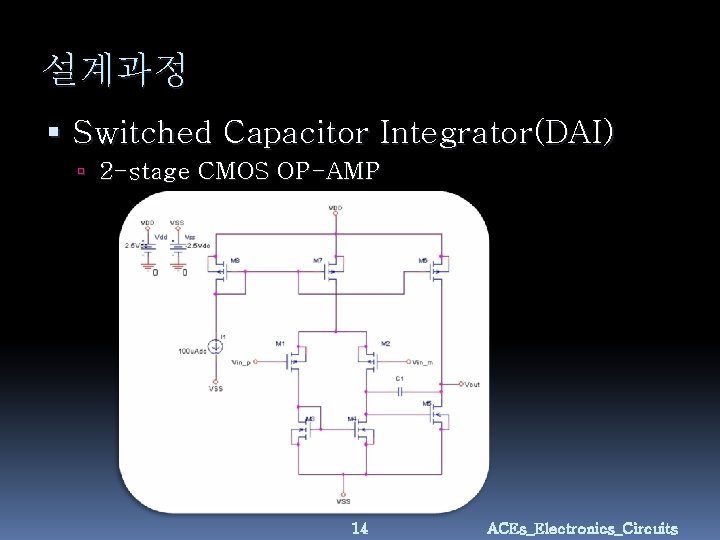

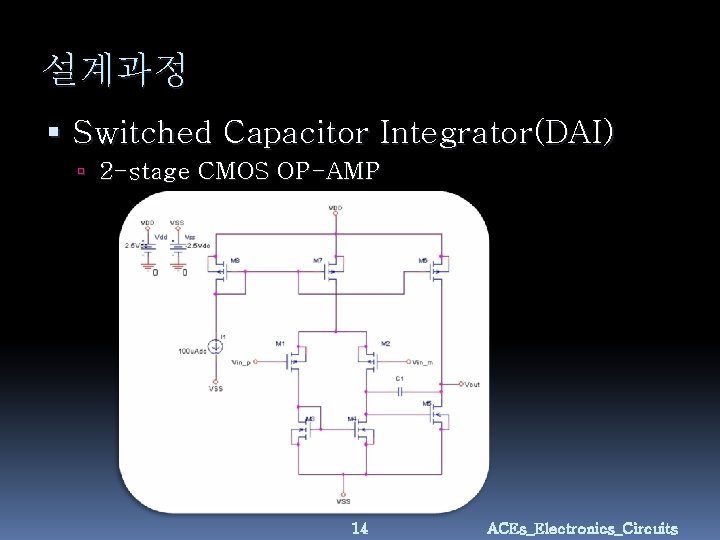

설계과정 Switched Capacitor Integrator(DAI) 2 -stage CMOS OP-AMP 14 ACEs_Electronics_Circuits

설계과정 Switched Capacitor Integrator(DAI) 2 -stage CMOS OP-AMP(0. 5㎛공정) NMOS LEVEL=1, VTO=0. 7 V, KP=190㎂/V 2, TOX=9㎚, COX=3. 8 f. F/㎛ 2 LAMBDA=0. 1, GAMMA=0, CGDO=500 ㎊/m, CGSO=500㎊/m PMOS LEVEL=1, VTO=-0. 8 V, KP=68㎂/V 2, TOX=9㎚, COX=3. 8 f. F/㎛ 2 LAMBDA=0. 2, GAMMA=0, CGDO=500 ㎊/m, CGSO=500㎊/m VDD=+2. 5 V, VSS=-2. 5 V IREF=100㎂ Compensation Capacitor(C 1)=1㎊ 15 ACEs_Electronics_Circuits

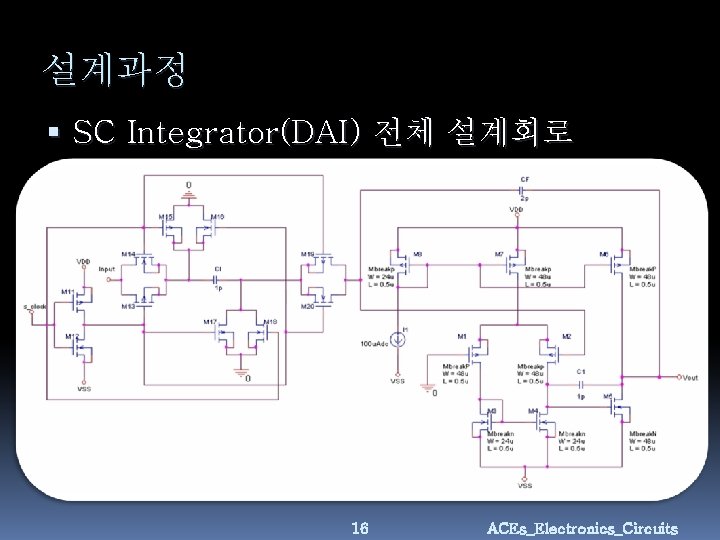

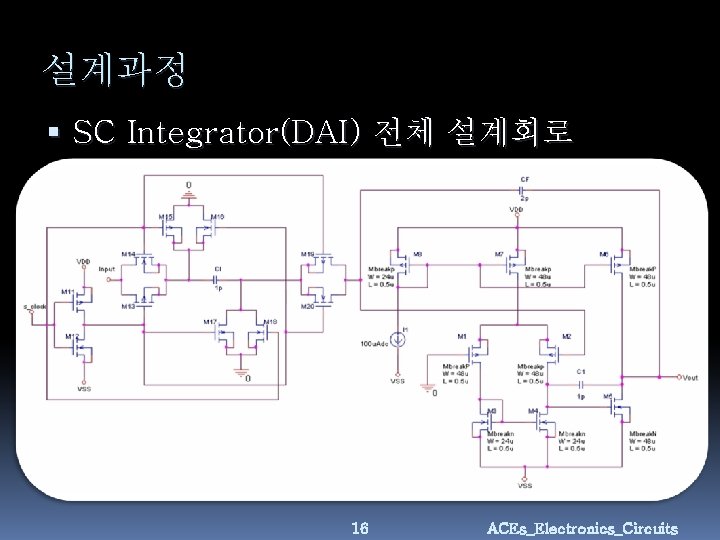

설계과정 SC Integrator(DAI) 전체 설계회로 16 ACEs_Electronics_Circuits

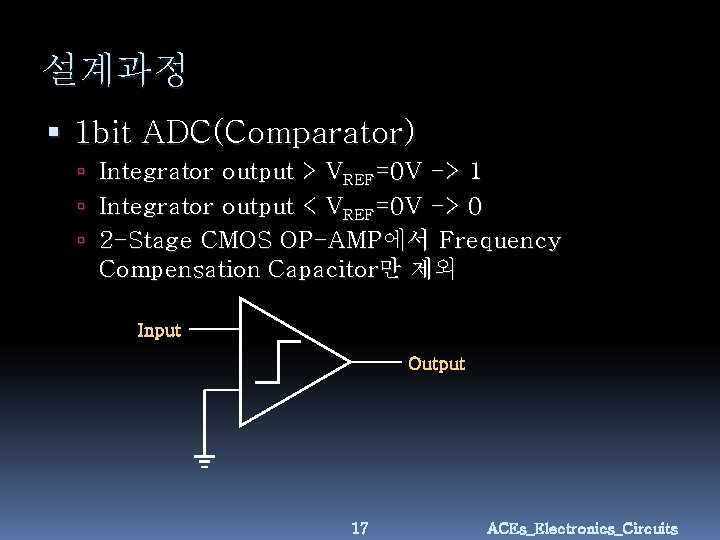

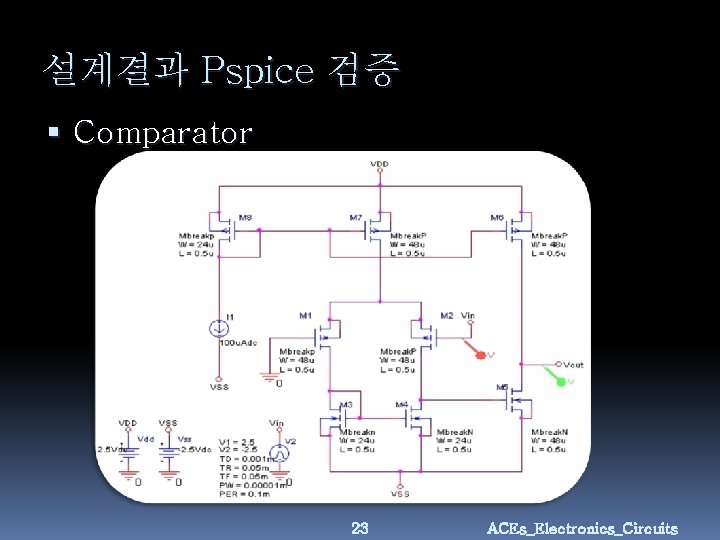

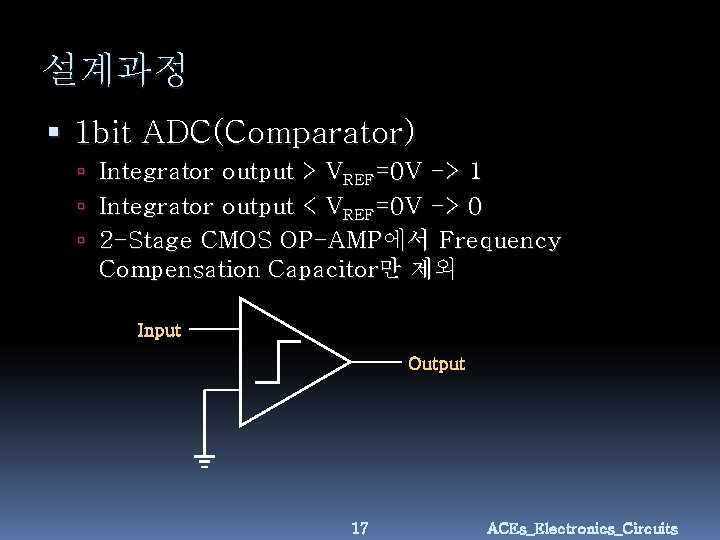

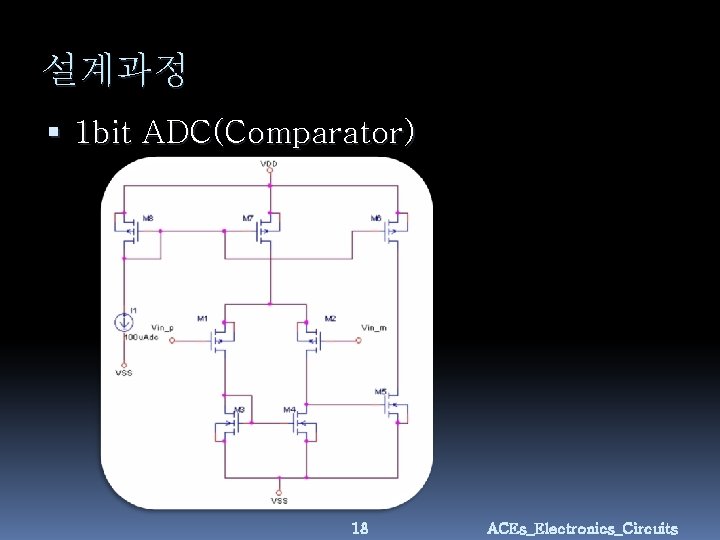

설계과정 1 bit ADC(Comparator) Integrator output > VREF=0 V -> 1 Integrator output < VREF=0 V -> 0 2 -Stage CMOS OP-AMP에서 Frequency Compensation Capacitor만 제외 Input Output 17 ACEs_Electronics_Circuits

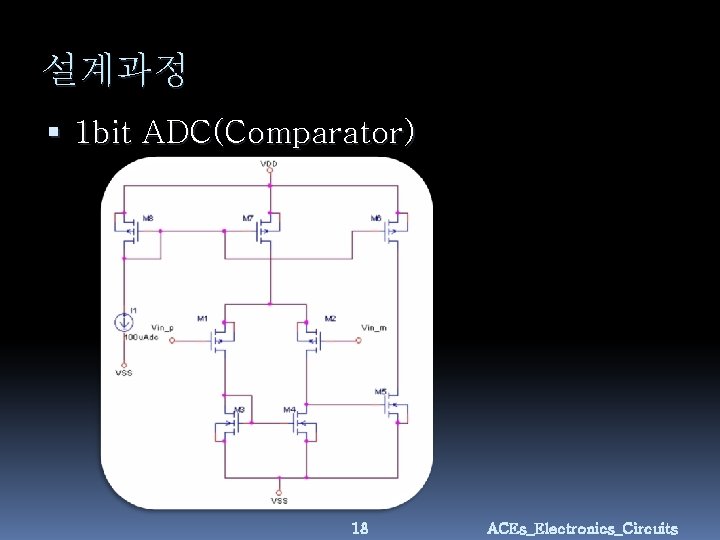

설계과정 1 bit ADC(Comparator) 18 ACEs_Electronics_Circuits

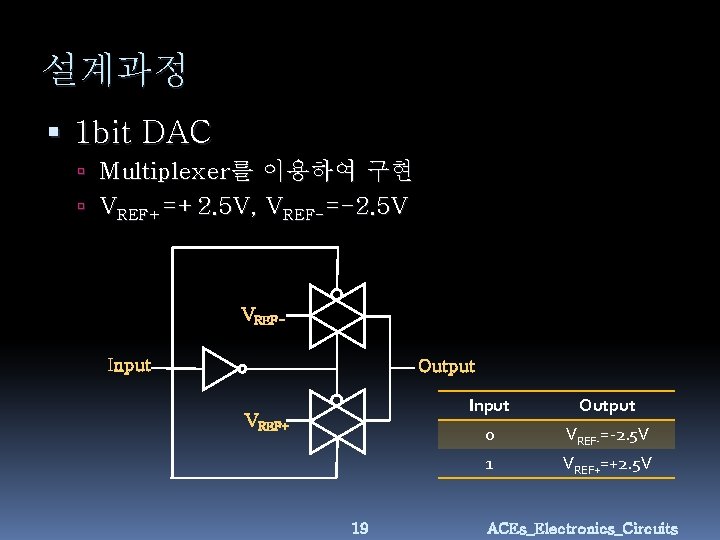

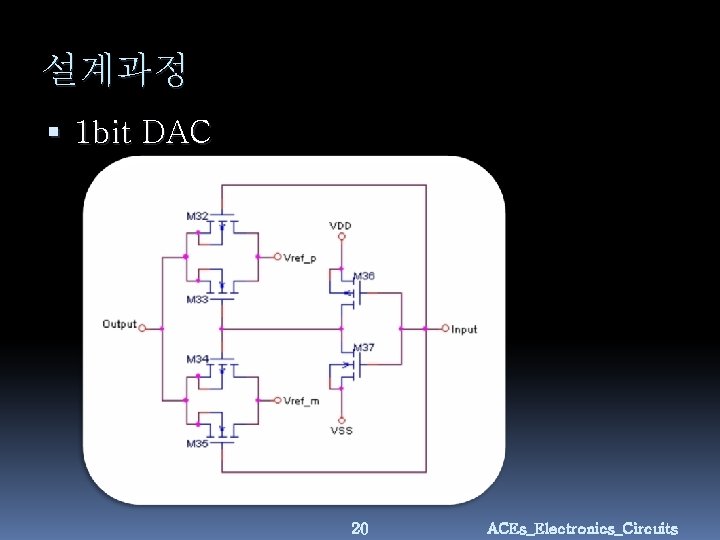

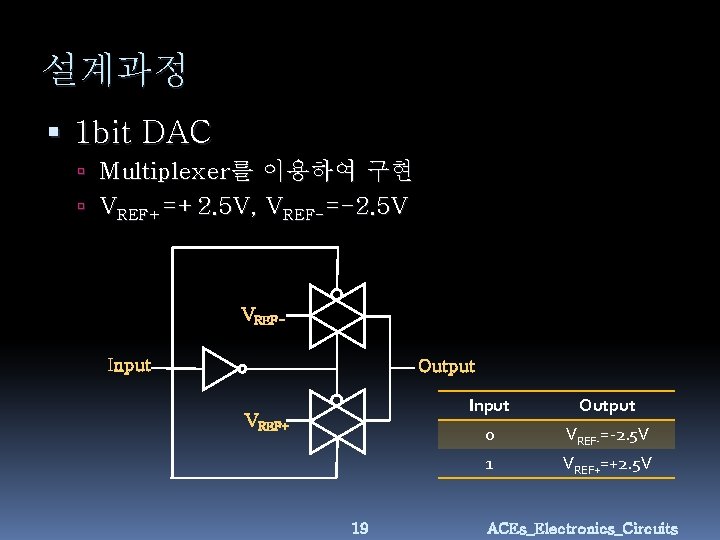

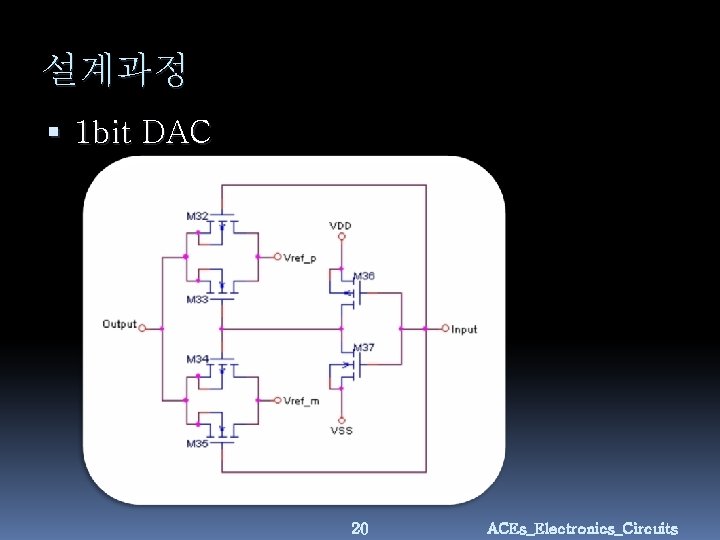

설계과정 1 bit DAC Multiplexer를 이용하여 구현 VREF+=+2. 5 V, VREF-=-2. 5 V VREFInput Output VREF+ 19 Input Output 0 VREF-=-2. 5 V 1 VREF+=+2. 5 V ACEs_Electronics_Circuits

설계과정 1 bit DAC 20 ACEs_Electronics_Circuits

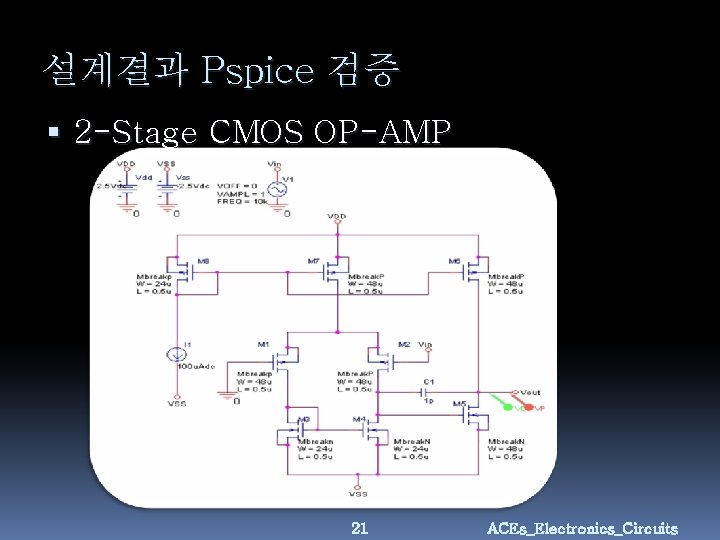

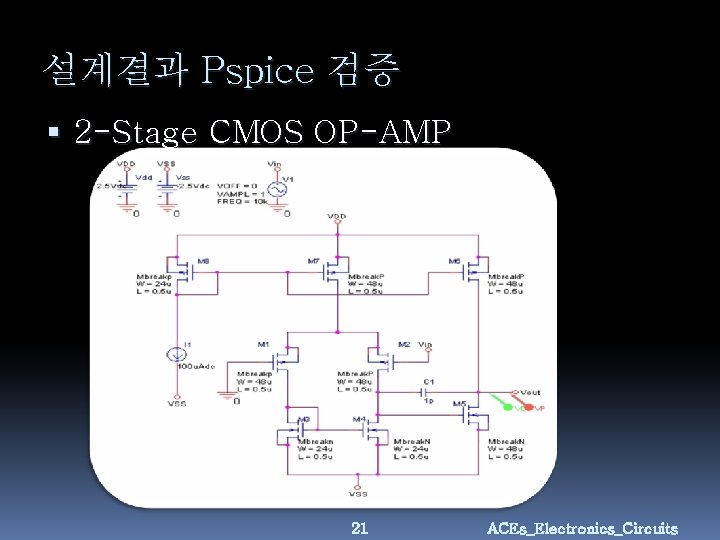

설계결과 Pspice 검증 2 -Stage CMOS OP-AMP 21 ACEs_Electronics_Circuits

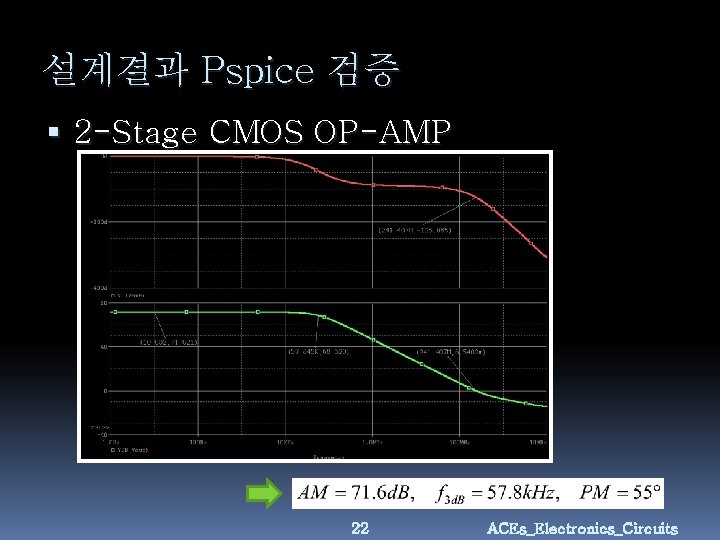

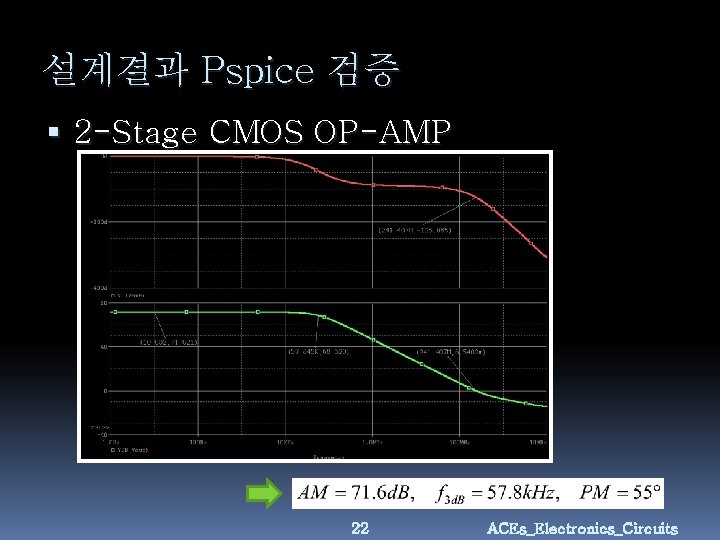

설계결과 Pspice 검증 2 -Stage CMOS OP-AMP 22 ACEs_Electronics_Circuits

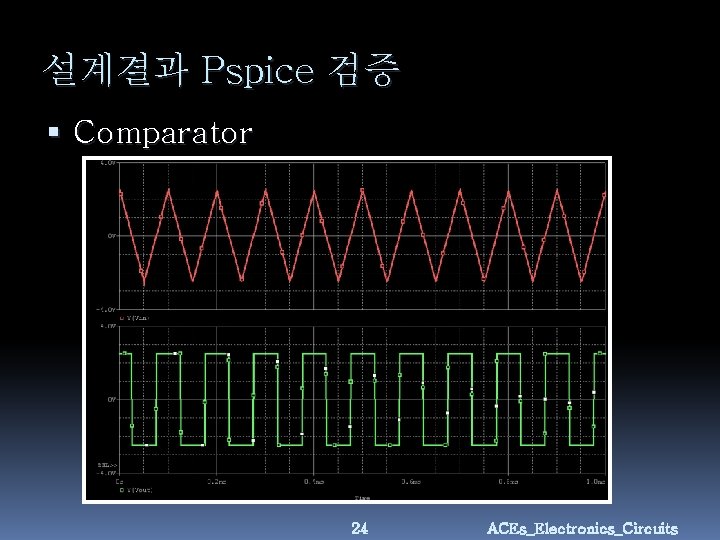

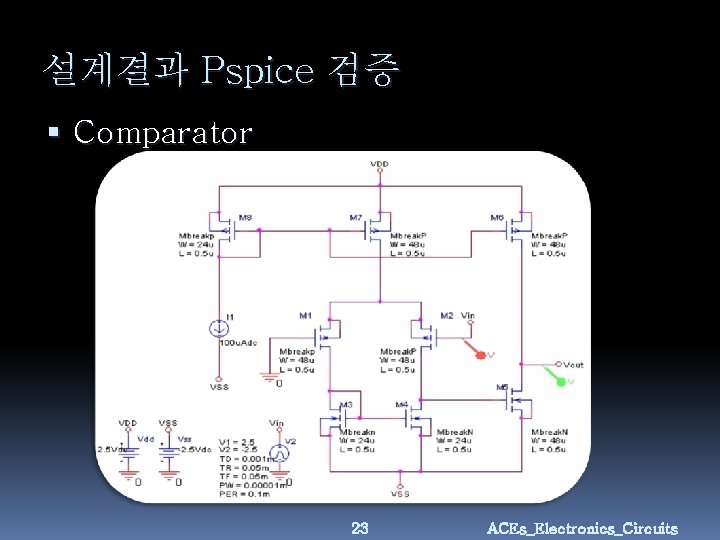

설계결과 Pspice 검증 Comparator 23 ACEs_Electronics_Circuits

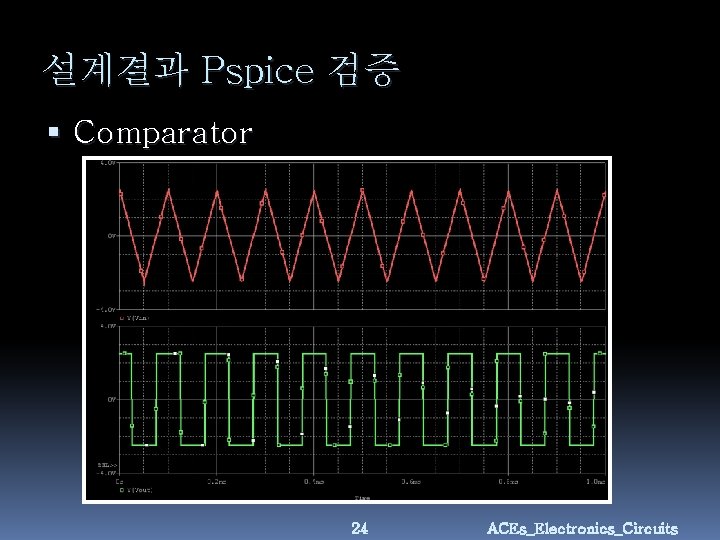

설계결과 Pspice 검증 Comparator 24 ACEs_Electronics_Circuits

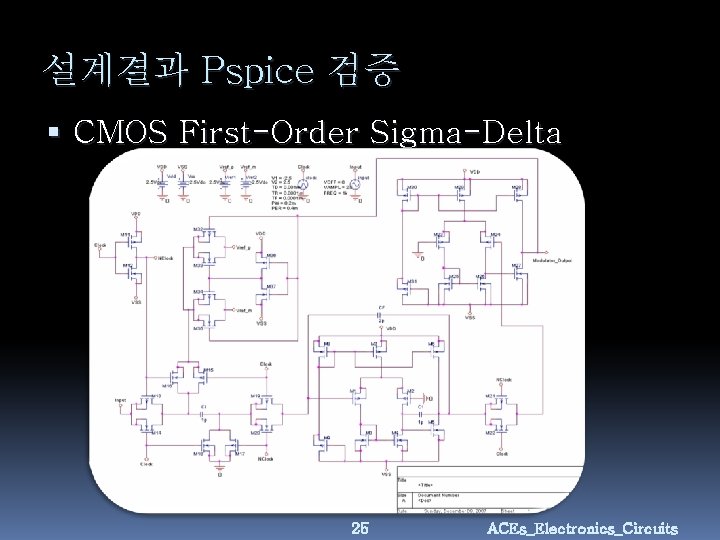

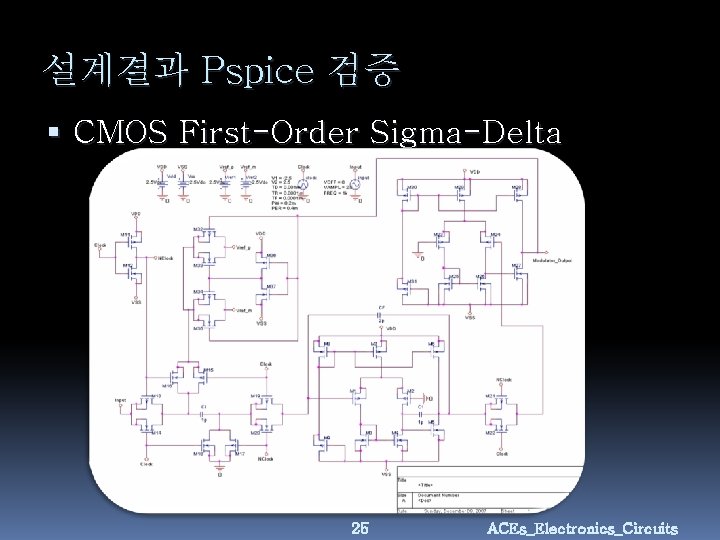

설계결과 Pspice 검증 CMOS First-Order Sigma-Delta 25 ACEs_Electronics_Circuits

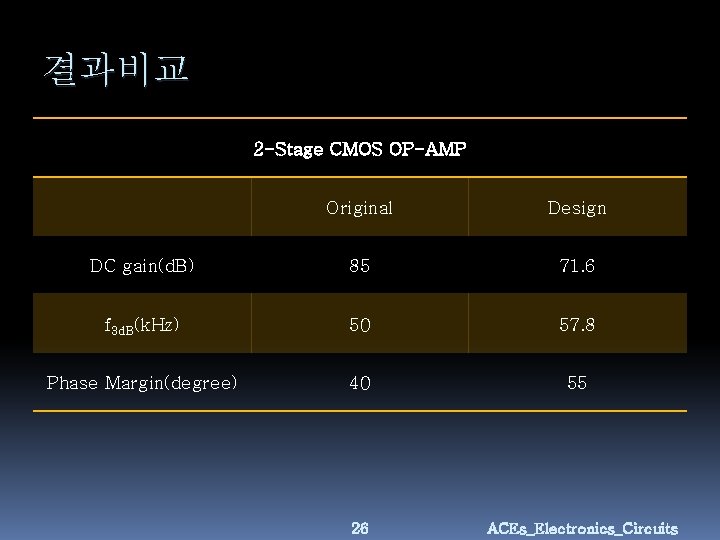

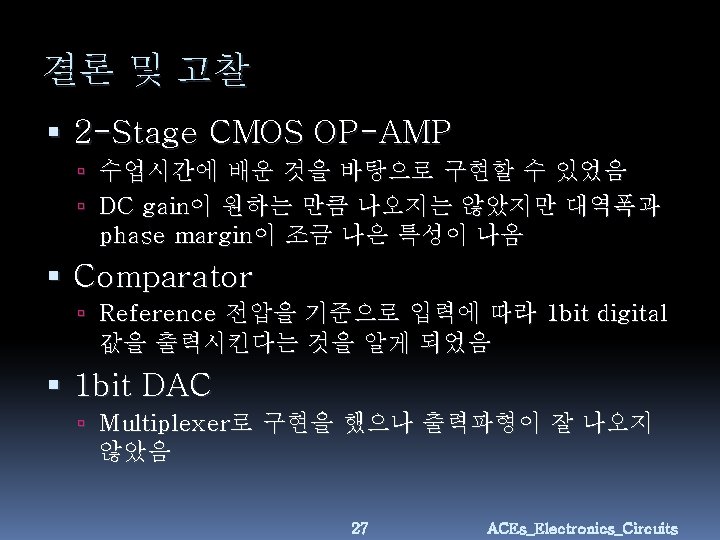

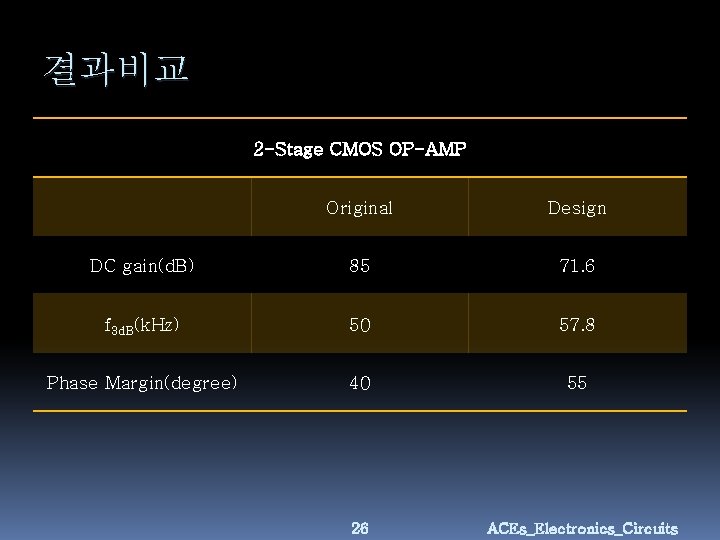

결과비교 2 -Stage CMOS OP-AMP Original Design DC gain(d. B) 85 71. 6 f 3 d. B(k. Hz) 50 57. 8 Phase Margin(degree) 40 55 26 ACEs_Electronics_Circuits

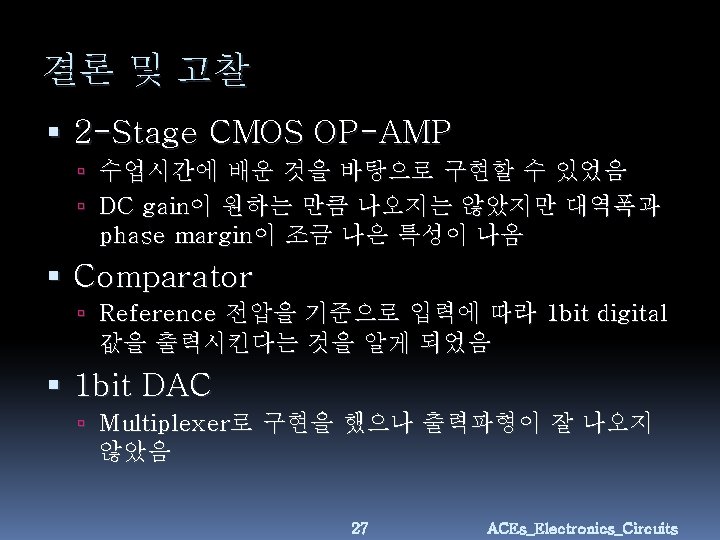

참고문헌 Jawaharlal Nehru Technological University(Anand K. Chamakura) IDDQ Testing of a CMOS first order sigma-delta Modulator of an 8 -bit oversampling ADC IEEE PRESS(James C. Candy) Oversampling delta-sigma data converters Bachelor of technology, Nagarjuna University(Syam Prasad SBS Kommana) First order sigma-delta modulator of an oversampling ADC design in CMOS using floating gate MOSFETs 29 ACEs_Electronics_Circuits

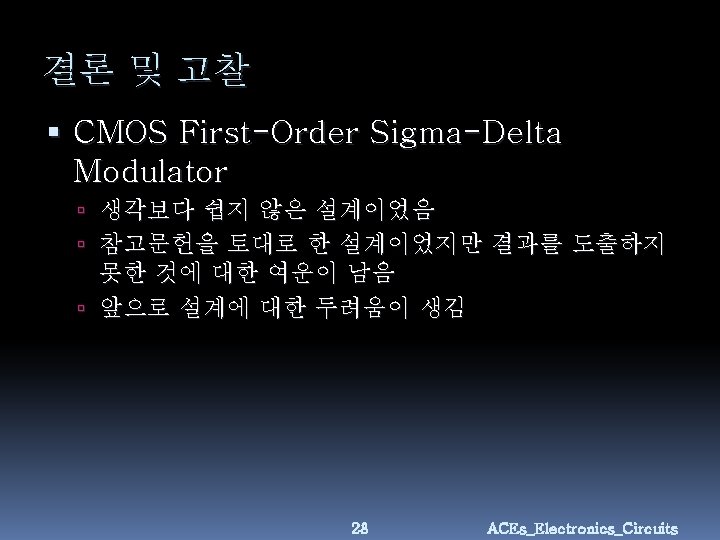

THE END Thanks ACEs_Electronics_Circuits