Hardware Description Language Logic Design using Verilog TsungChu

- Slides: 13

Hardware Description Language -- Logic Design using Verilog Tsung-Chu Huang Dept. of Electronic Eng. National Changhua University of Ed. Email: tch@cc. ncue. edu. tw 2015/11/26 HDL T. -C. Huang / NCUE Fall 2015 1

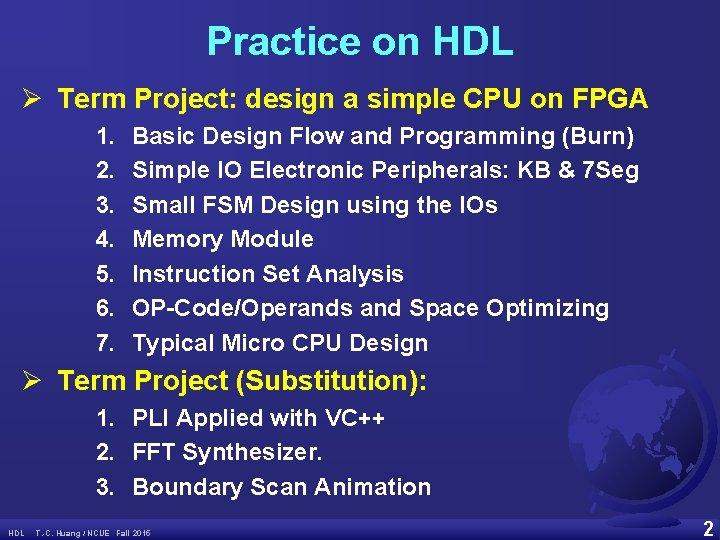

Practice on HDL Ø Term Project: design a simple CPU on FPGA 1. 2. 3. 4. 5. 6. 7. Basic Design Flow and Programming (Burn) Simple IO Electronic Peripherals: KB & 7 Seg Small FSM Design using the IOs Memory Module Instruction Set Analysis OP-Code/Operands and Space Optimizing Typical Micro CPU Design Ø Term Project (Substitution): 1. PLI Applied with VC++ 2. FFT Synthesizer. 3. Boundary Scan Animation HDL T. -C. Huang / NCUE Fall 2015 2

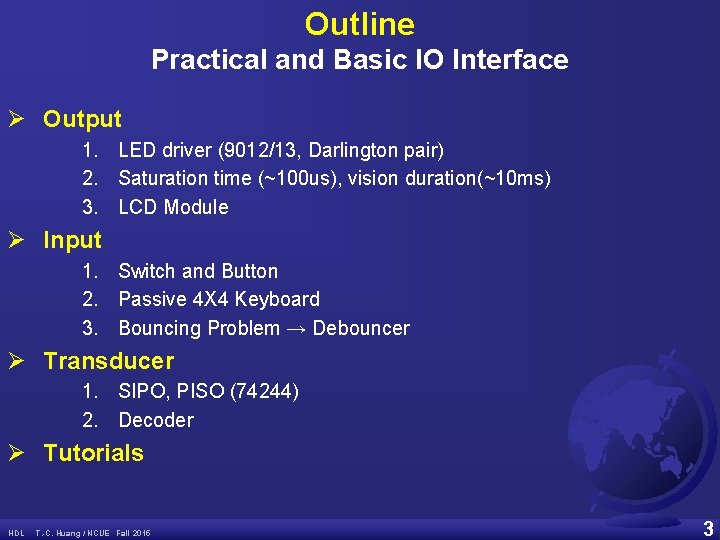

Outline Practical and Basic IO Interface Ø Output 1. LED driver (9012/13, Darlington pair) 2. Saturation time (~100 us), vision duration(~10 ms) 3. LCD Module Ø Input 1. Switch and Button 2. Passive 4 X 4 Keyboard 3. Bouncing Problem → Debouncer Ø Transducer 1. SIPO, PISO (74244) 2. Decoder Ø Tutorials HDL T. -C. Huang / NCUE Fall 2015 3

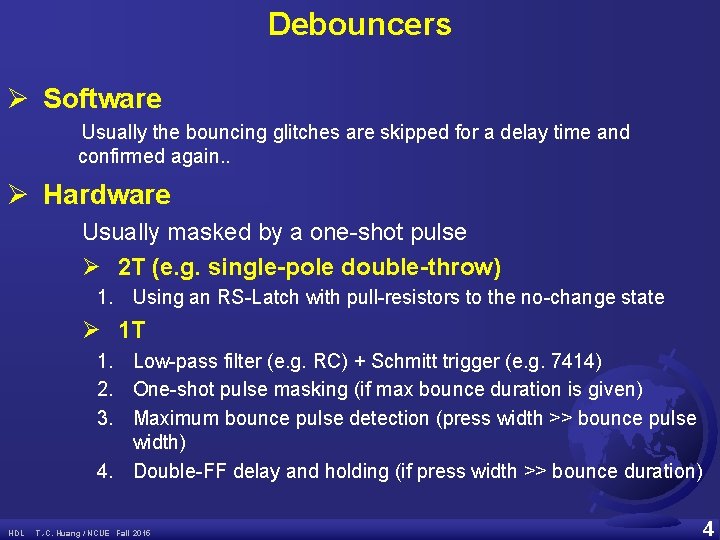

Debouncers Ø Software Usually the bouncing glitches are skipped for a delay time and confirmed again. . Ø Hardware Usually masked by a one-shot pulse Ø 2 T (e. g. single-pole double-throw) 1. Using an RS-Latch with pull-resistors to the no-change state Ø 1 T 1. Low-pass filter (e. g. RC) + Schmitt trigger (e. g. 7414) 2. One-shot pulse masking (if max bounce duration is given) 3. Maximum bounce pulse detection (press width >> bounce pulse width) 4. Double-FF delay and holding (if press width >> bounce duration) HDL T. -C. Huang / NCUE Fall 2015 4

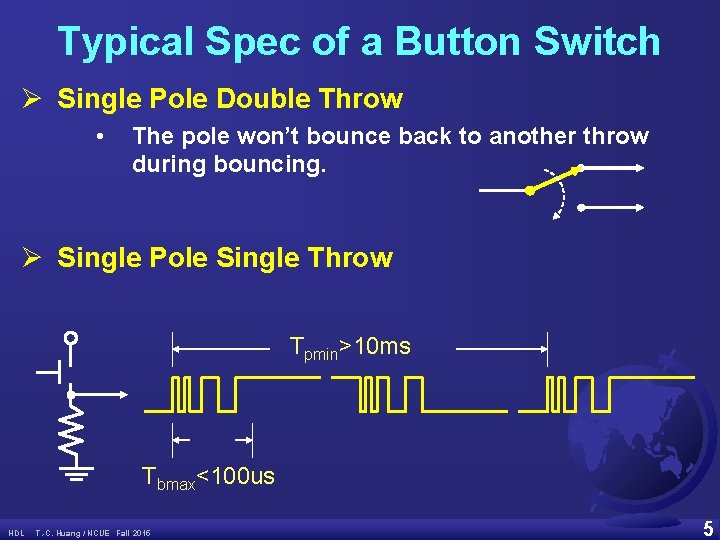

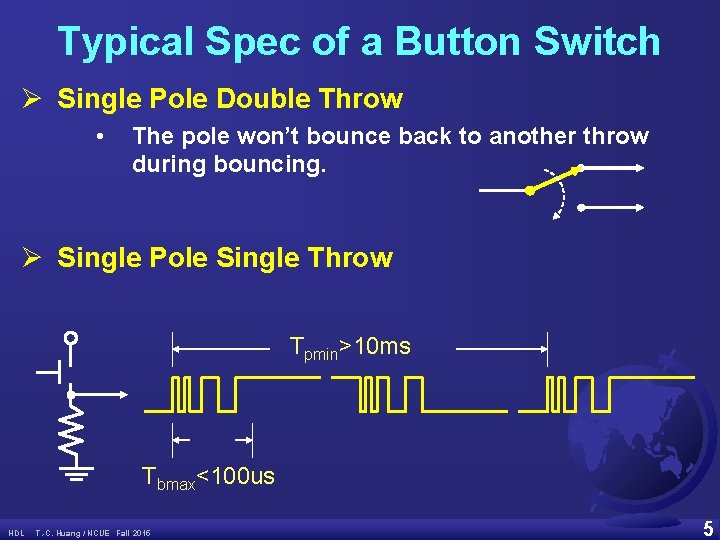

Typical Spec of a Button Switch Ø Single Pole Double Throw • The pole won’t bounce back to another throw during bouncing. Ø Single Pole Single Throw Tpmin>10 ms Tbmax<100 us HDL T. -C. Huang / NCUE Fall 2015 5

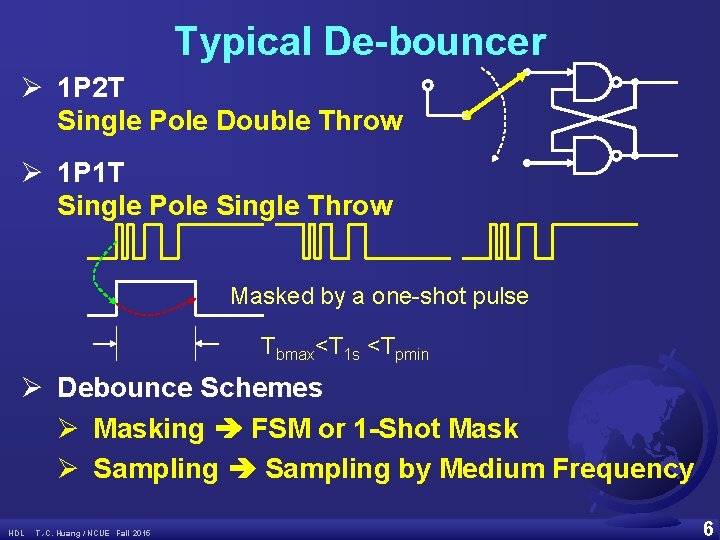

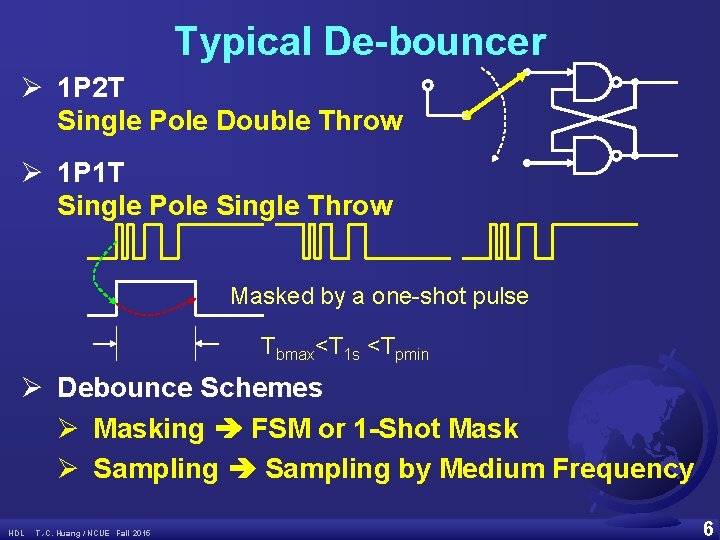

Typical De-bouncer Ø 1 P 2 T Single Pole Double Throw Ø 1 P 1 T Single Pole Single Throw Masked by a one-shot pulse Tbmax<T 1 s <Tpmin Ø Debounce Schemes Ø Masking FSM or 1 -Shot Mask Ø Sampling by Medium Frequency HDL T. -C. Huang / NCUE Fall 2015 6

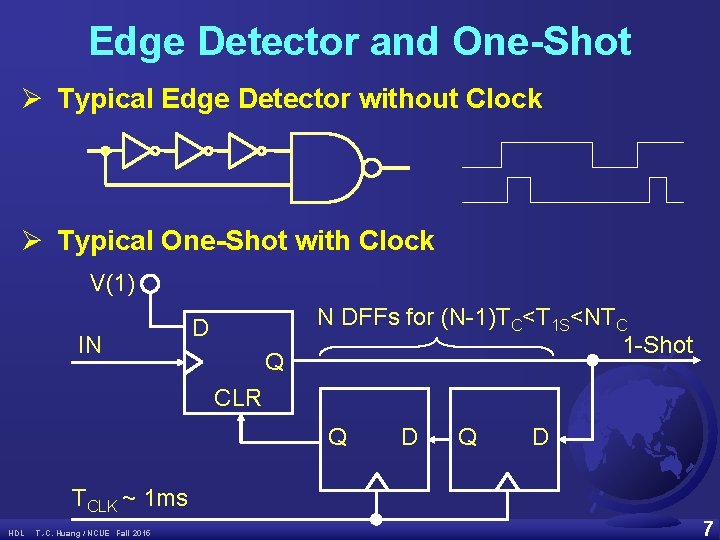

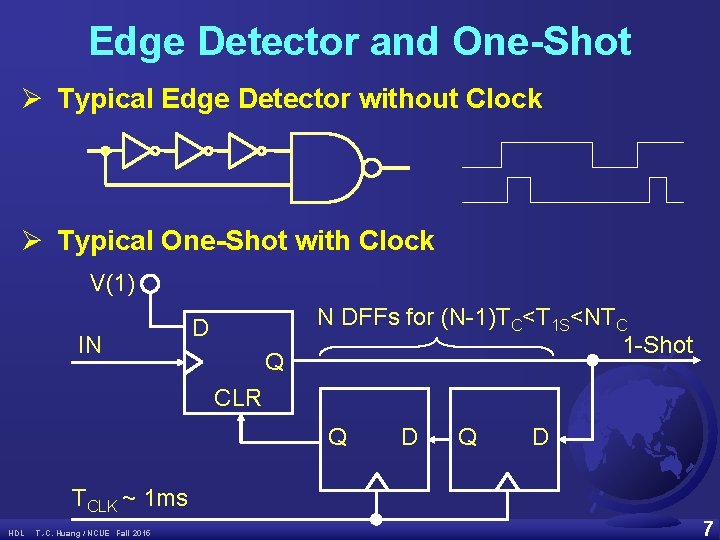

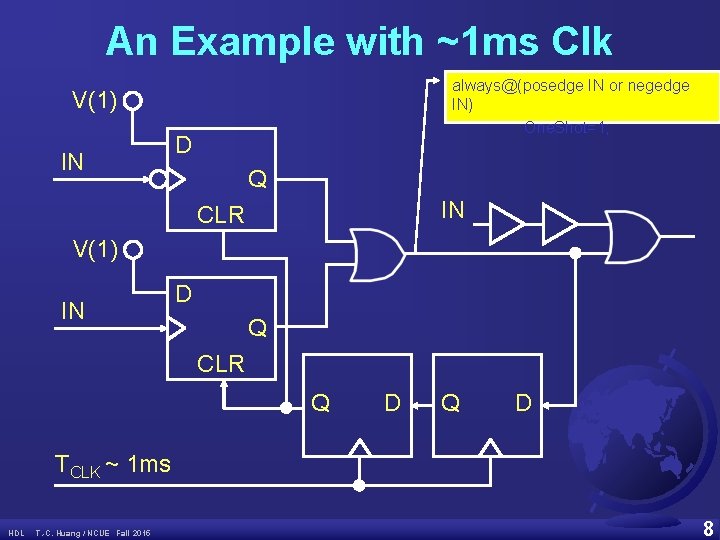

Edge Detector and One-Shot Ø Typical Edge Detector without Clock Ø Typical One-Shot with Clock V(1) IN D Q N DFFs for (N-1)TC<T 1 S<NTC 1 -Shot CLR Q D TCLK ~ 1 ms HDL T. -C. Huang / NCUE Fall 2015 7

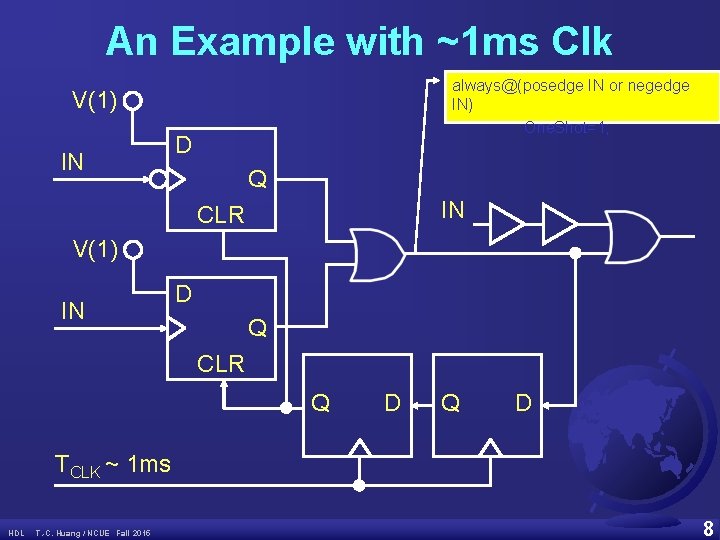

An Example with ~1 ms Clk always@(posedge IN or negedge IN) One. Shot=1; V(1) IN D Q IN CLR V(1) IN D Q CLR Q D TCLK ~ 1 ms HDL T. -C. Huang / NCUE Fall 2015 8

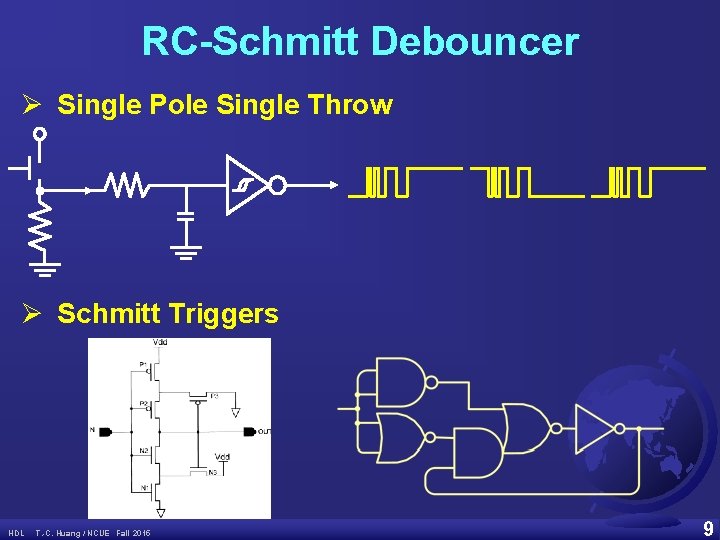

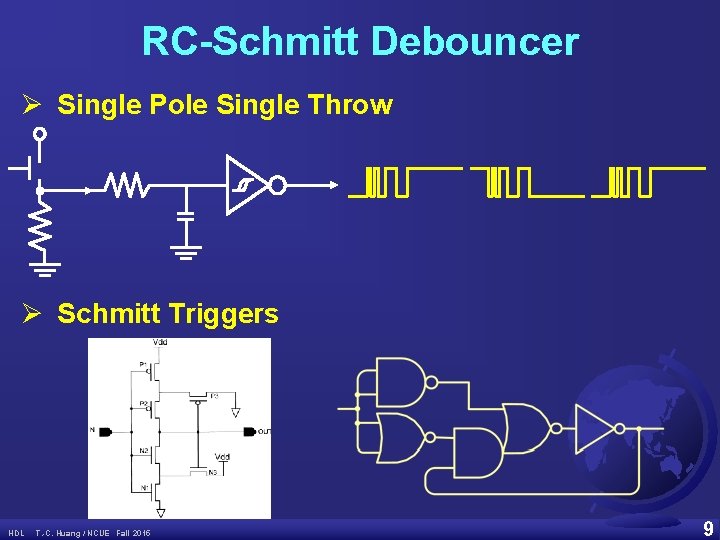

RC-Schmitt Debouncer Ø Single Pole Single Throw Ø Schmitt Triggers HDL T. -C. Huang / NCUE Fall 2015 9

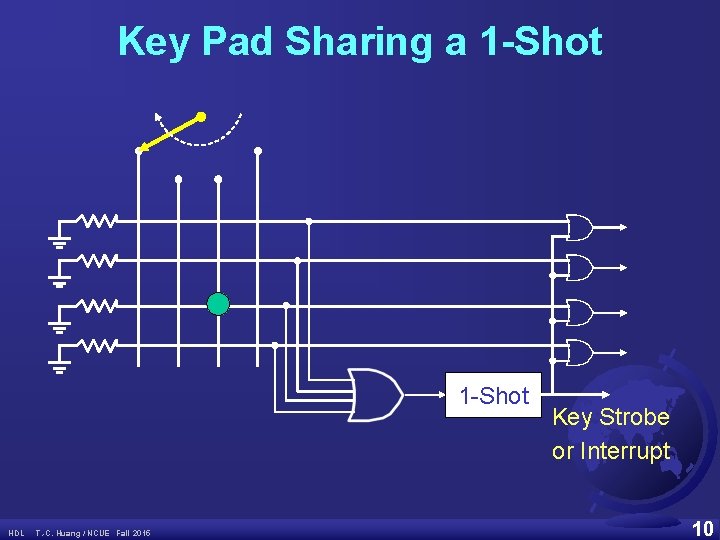

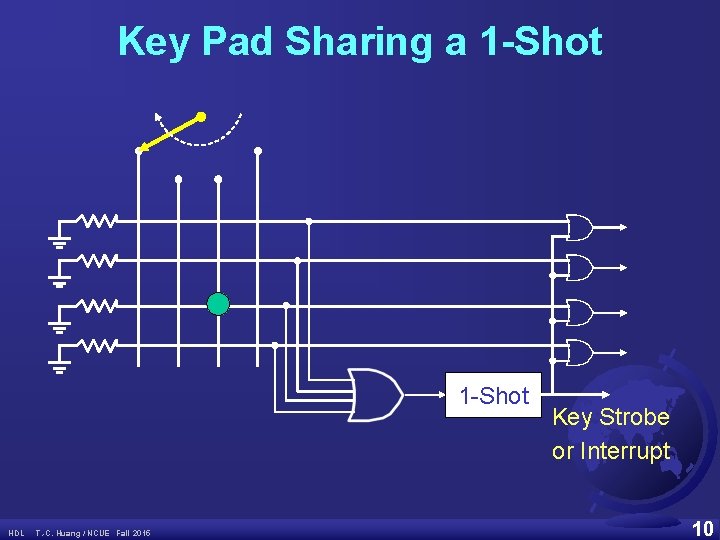

Key Pad Sharing a 1 -Shot HDL T. -C. Huang / NCUE Fall 2015 Key Strobe or Interrupt 10

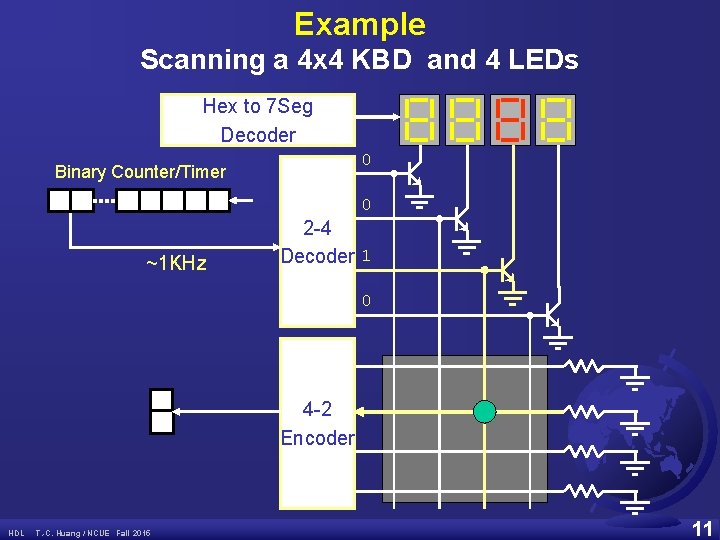

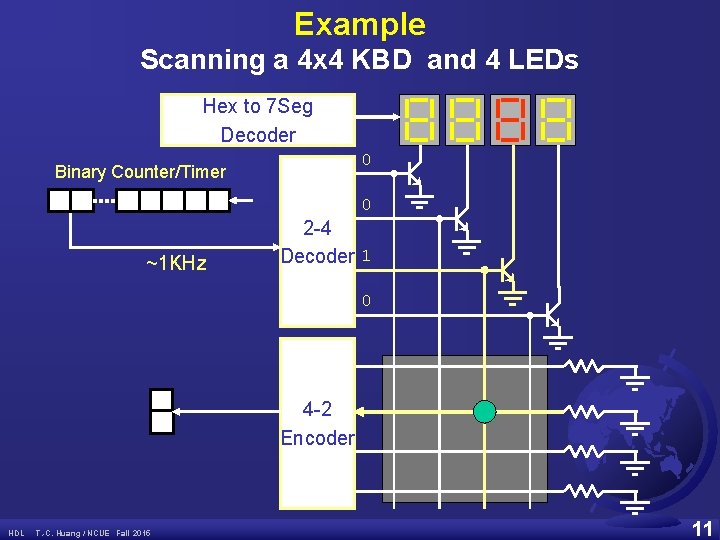

Example Scanning a 4 x 4 KBD and 4 LEDs Hex to 7 Seg Decoder 0 Binary Counter/Timer 0 ~1 KHz 2 -4 Decoder 1 0 4 -2 Encoder HDL T. -C. Huang / NCUE Fall 2015 11

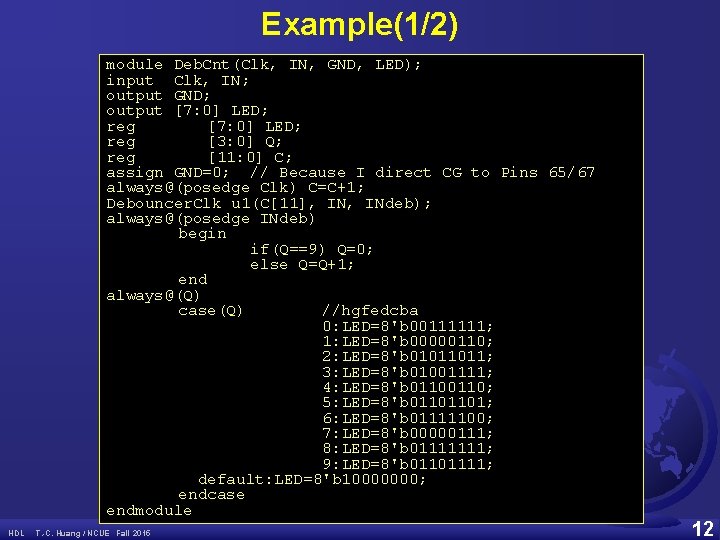

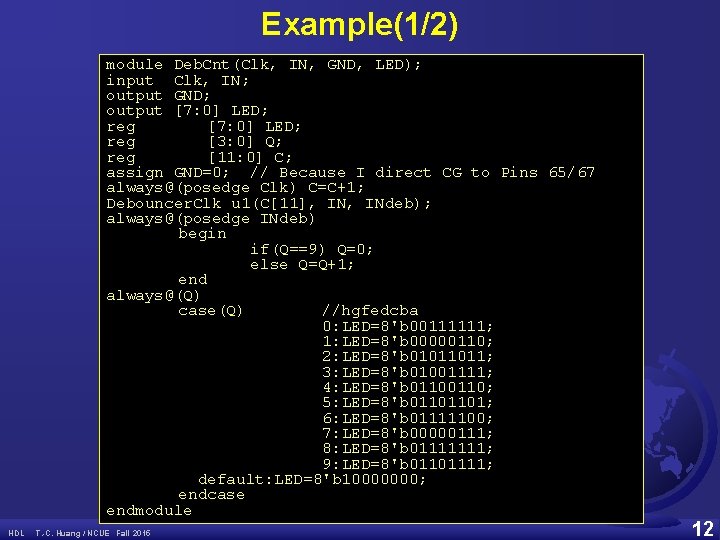

Example(1/2) module Deb. Cnt(Clk, IN, GND, LED); input Clk, IN; output GND; output [7: 0] LED; reg [3: 0] Q; reg [11: 0] C; assign GND=0; // Because I direct CG to Pins 65/67 always@(posedge Clk) C=C+1; Debouncer. Clk u 1(C[11], INdeb); always@(posedge INdeb) begin if(Q==9) Q=0; else Q=Q+1; end always@(Q) case(Q) //hgfedcba 0: LED=8'b 00111111; 1: LED=8'b 00000110; 2: LED=8'b 01011011; 3: LED=8'b 01001111; 4: LED=8'b 0110; 5: LED=8'b 01101101; 6: LED=8'b 01111100; 7: LED=8'b 00000111; 8: LED=8'b 01111111; 9: LED=8'b 01101111; default: LED=8'b 10000000; endcase endmodule HDL T. -C. Huang / NCUE Fall 2015 12

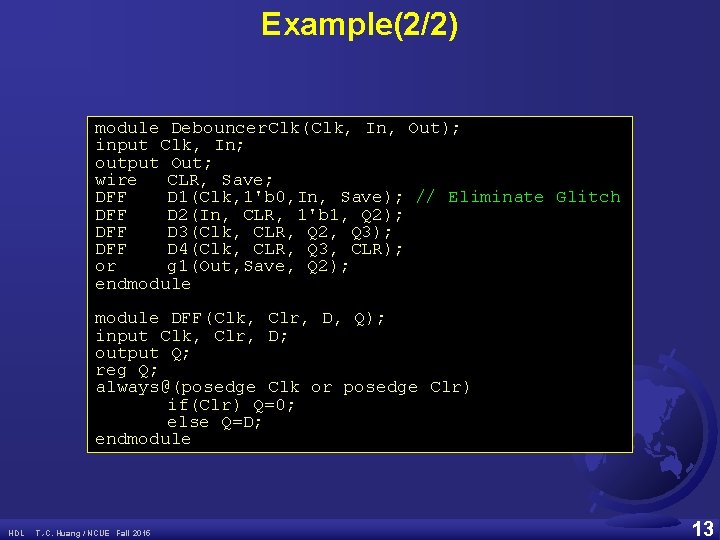

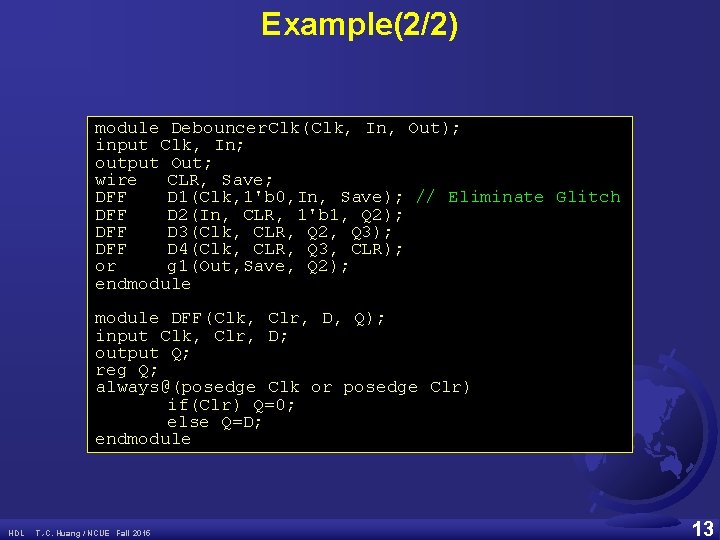

Example(2/2) module Debouncer. Clk(Clk, In, Out); input Clk, In; output Out; wire CLR, Save; DFF D 1(Clk, 1'b 0, In, Save); // Eliminate Glitch DFF D 2(In, CLR, 1'b 1, Q 2); DFF D 3(Clk, CLR, Q 2, Q 3); DFF D 4(Clk, CLR, Q 3, CLR); or g 1(Out, Save, Q 2); endmodule DFF(Clk, Clr, D, Q); input Clk, Clr, D; output Q; reg Q; always@(posedge Clk or posedge Clr) if(Clr) Q=0; else Q=D; endmodule HDL T. -C. Huang / NCUE Fall 2015 13