COE 405 Introduction to Digital Design Methodology Dr

- Slides: 25

COE 405 Introduction to Digital Design Methodology Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

Outline n Digital System Design n Design Space and Evaluation Space n Digital System Complexity n Design Domains and Levels of Abstractions n Synthesis Process 1 -2

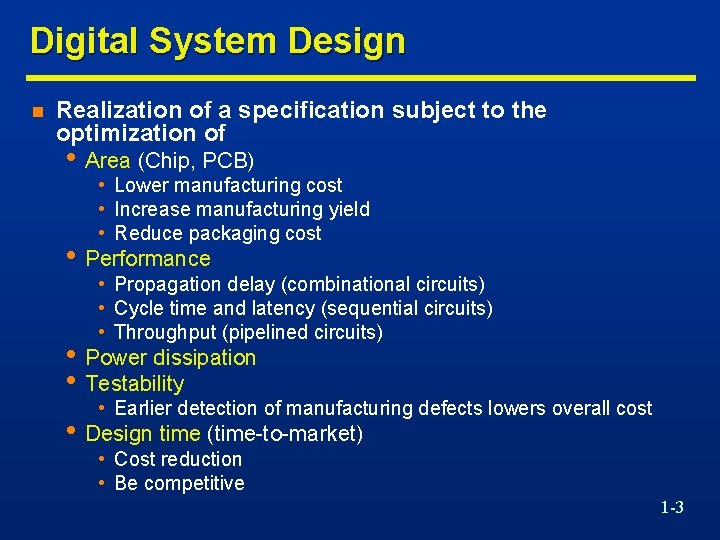

Digital System Design n Realization of a specification subject to the optimization of • Area (Chip, PCB) • Lower manufacturing cost • Increase manufacturing yield • Reduce packaging cost • Performance • Propagation delay (combinational circuits) • Cycle time and latency (sequential circuits) • Throughput (pipelined circuits) • Power dissipation • Testability • Earlier detection of manufacturing defects lowers overall cost • Design time (time-to-market) • Cost reduction • Be competitive 1 -3

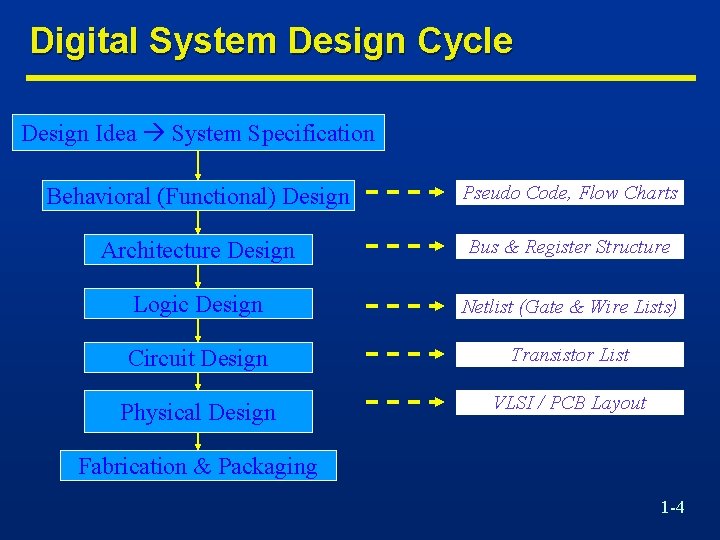

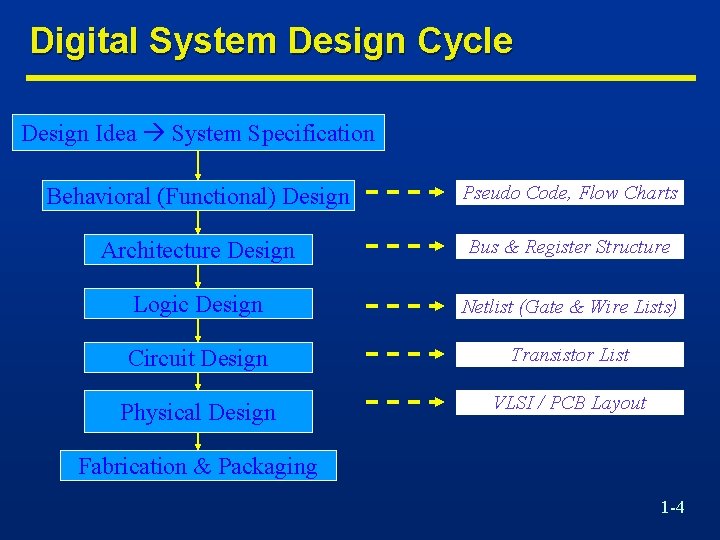

Digital System Design Cycle Design Idea System Specification Behavioral (Functional) Design Pseudo Code, Flow Charts Architecture Design Bus & Register Structure Logic Design Netlist (Gate & Wire Lists) Circuit Design Transistor List Physical Design VLSI / PCB Layout Fabrication & Packaging 1 -4

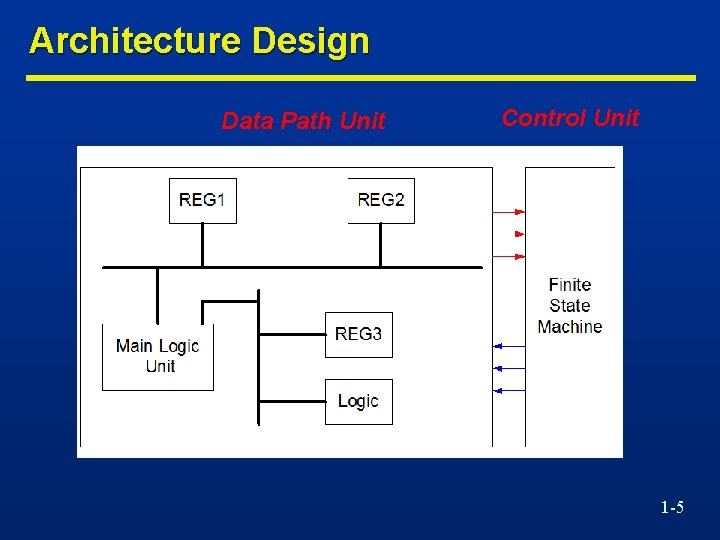

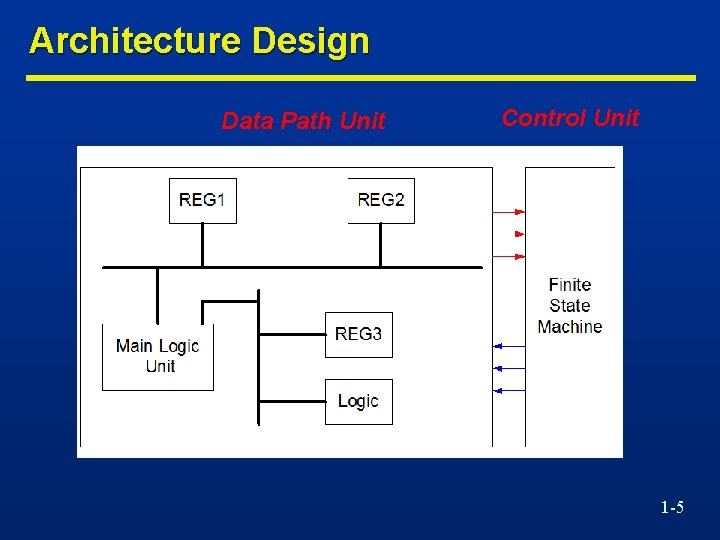

Architecture Design Data Path Unit Control Unit 1 -5

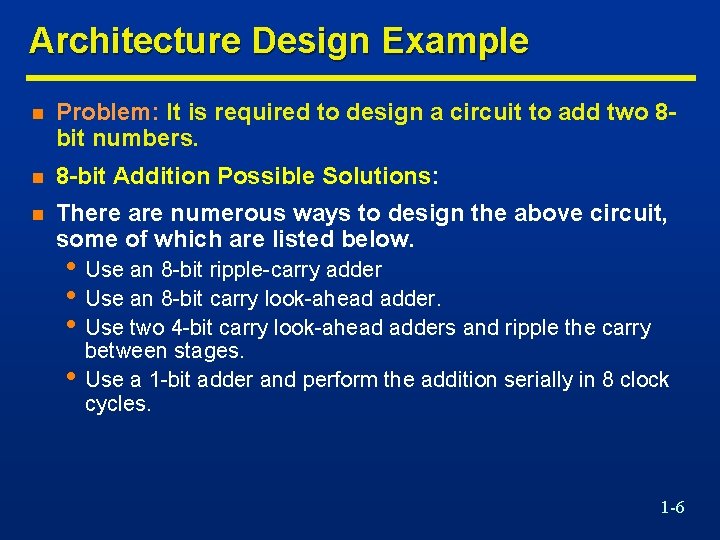

Architecture Design Example n Problem: It is required to design a circuit to add two 8 bit numbers. n 8 -bit Addition Possible Solutions: n There are numerous ways to design the above circuit, some of which are listed below. • Use an 8 -bit ripple-carry adder • Use an 8 -bit carry look-ahead adder. • Use two 4 -bit carry look-ahead adders and ripple the carry • between stages. Use a 1 -bit adder and perform the addition serially in 8 clock cycles. 1 -6

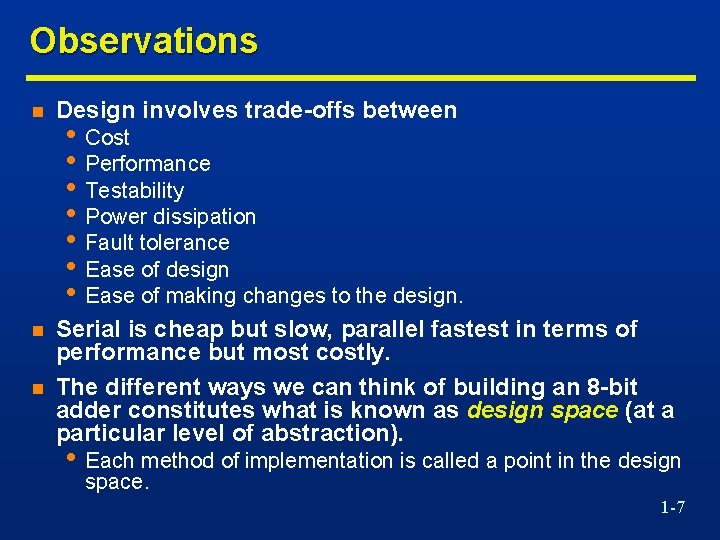

Observations n Design involves trade-offs between n Serial is cheap but slow, parallel fastest in terms of performance but most costly. The different ways we can think of building an 8 -bit adder constitutes what is known as design space (at a particular level of abstraction). n • Cost • Performance • Testability • Power dissipation • Fault tolerance • Ease of design • Ease of making changes to the design. • Each method of implementation is called a point in the design space. 1 -7

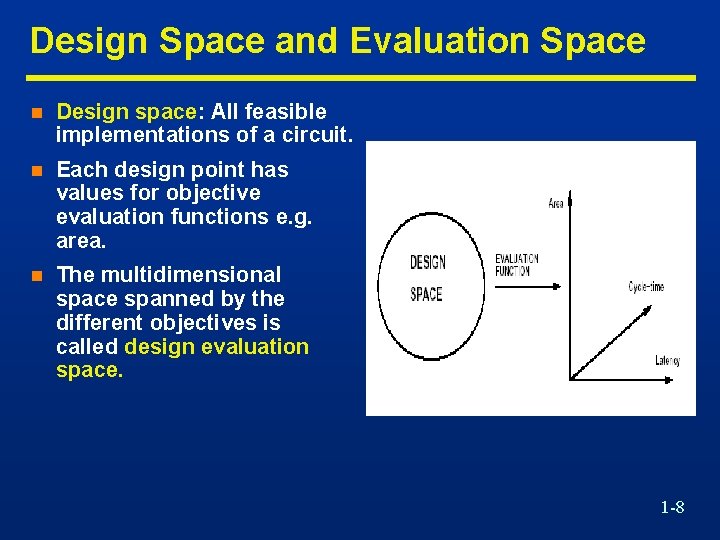

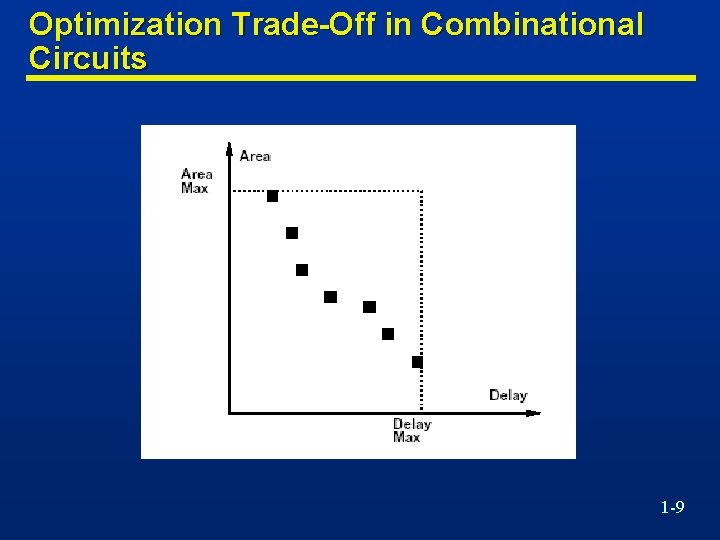

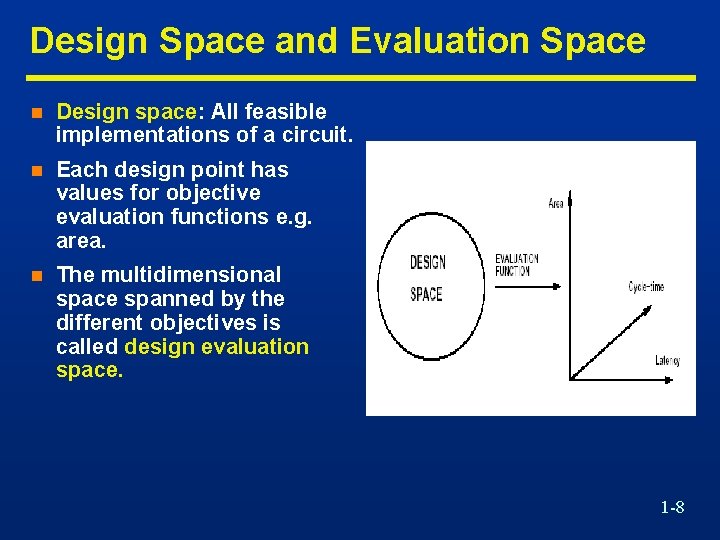

Design Space and Evaluation Space n Design space: All feasible implementations of a circuit. n Each design point has values for objective evaluation functions e. g. area. n The multidimensional space spanned by the different objectives is called design evaluation space. 1 -8

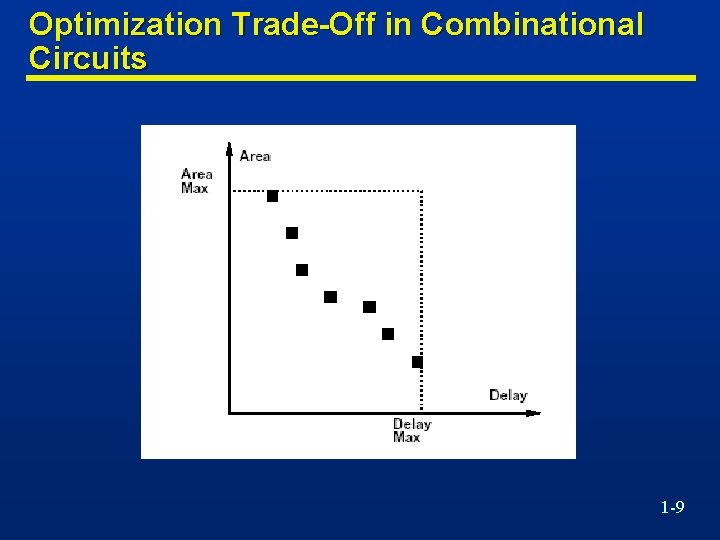

Optimization Trade-Off in Combinational Circuits 1 -9

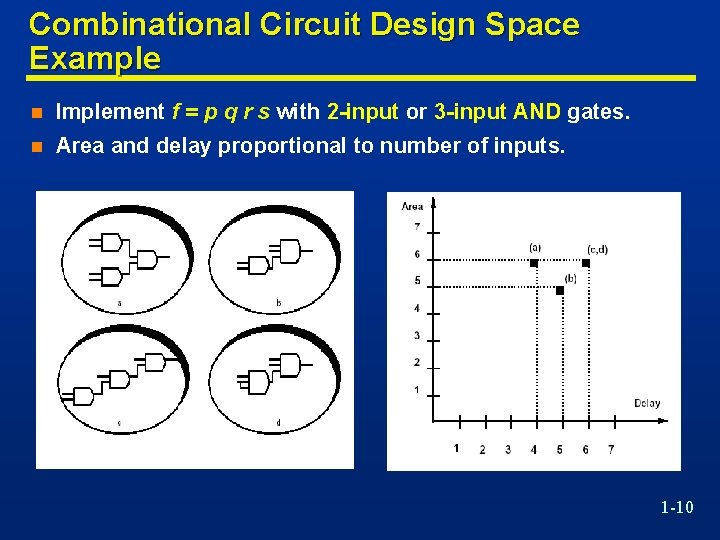

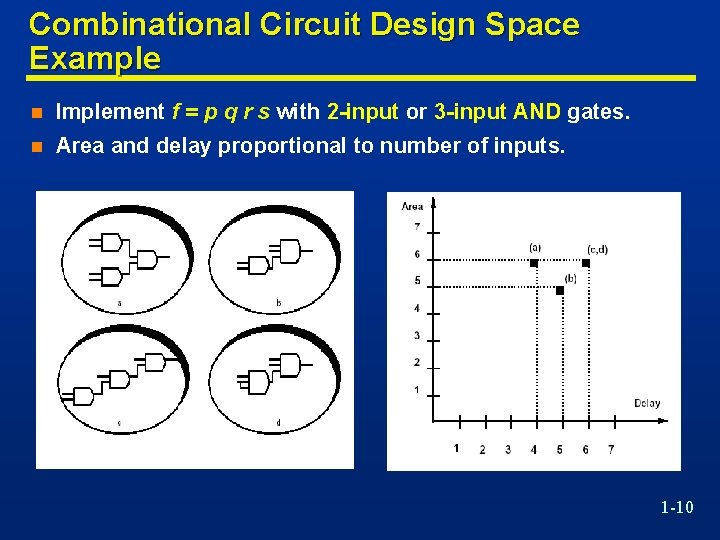

Combinational Circuit Design Space Example n Implement f = p q r s with 2 -input or 3 -input AND gates. n Area and delay proportional to number of inputs. 1 -10

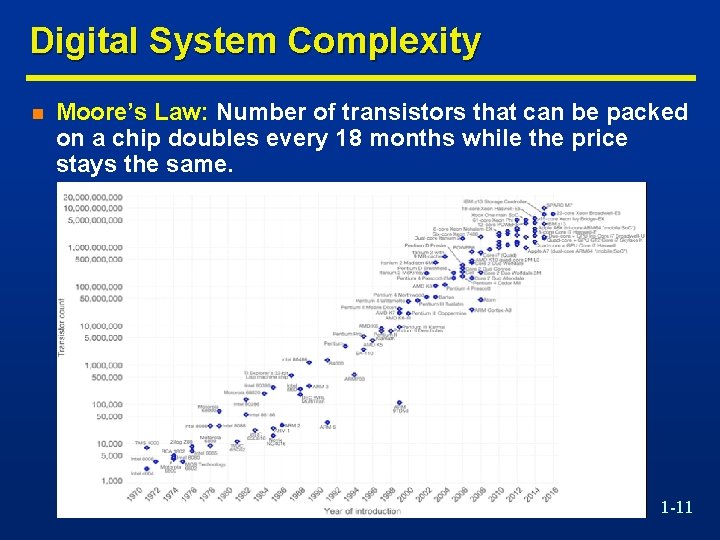

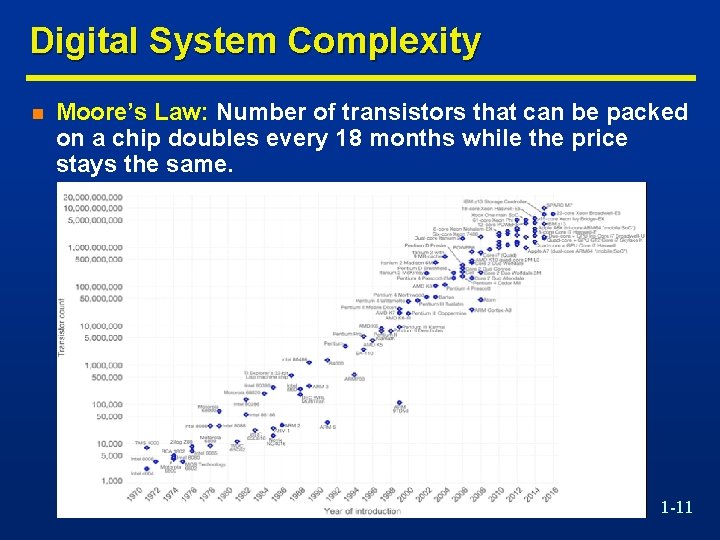

Digital System Complexity n Moore’s Law: Number of transistors that can be packed on a chip doubles every 18 months while the price stays the same. 1 -11

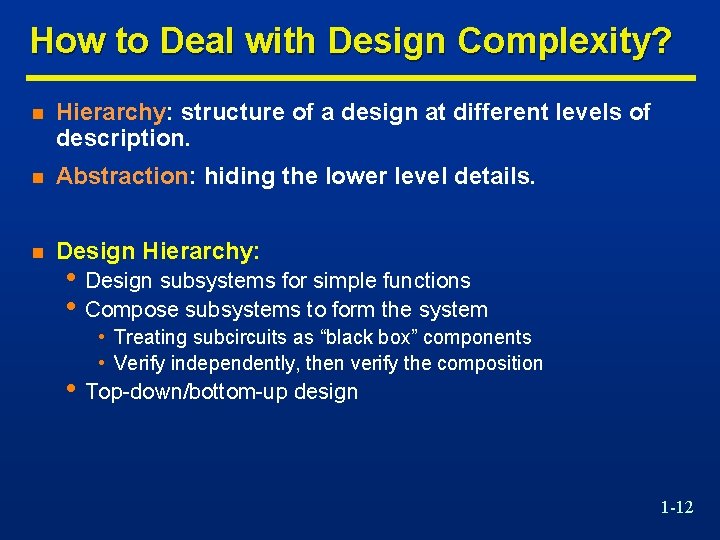

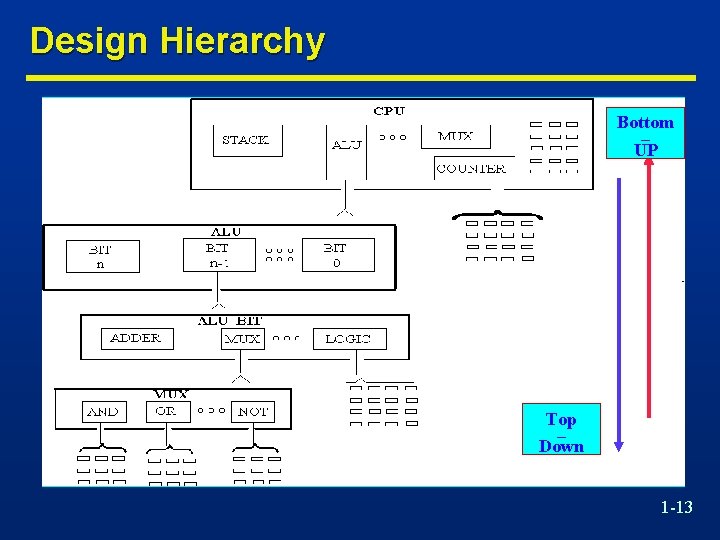

How to Deal with Design Complexity? n Hierarchy: structure of a design at different levels of description. n Abstraction: hiding the lower level details. n Design Hierarchy: • Design subsystems for simple functions • Compose subsystems to form the system • Treating subcircuits as “black box” components • Verify independently, then verify the composition • Top-down/bottom-up design 1 -12

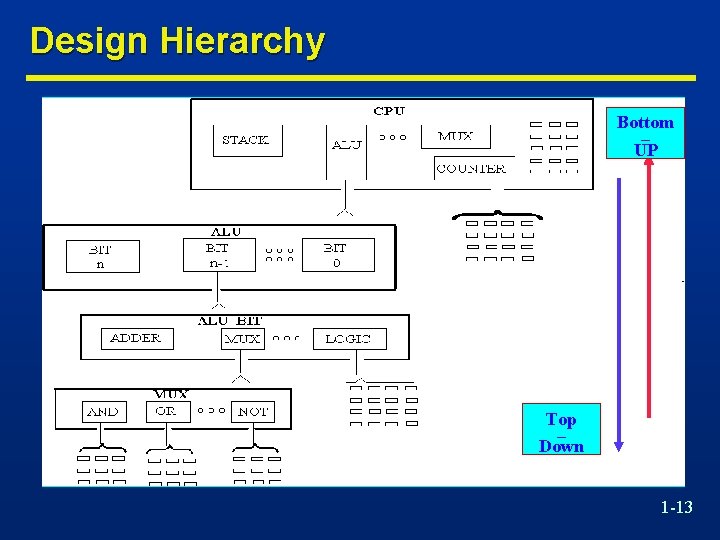

Design Hierarchy Bottom – UP Top – Down 1 -13

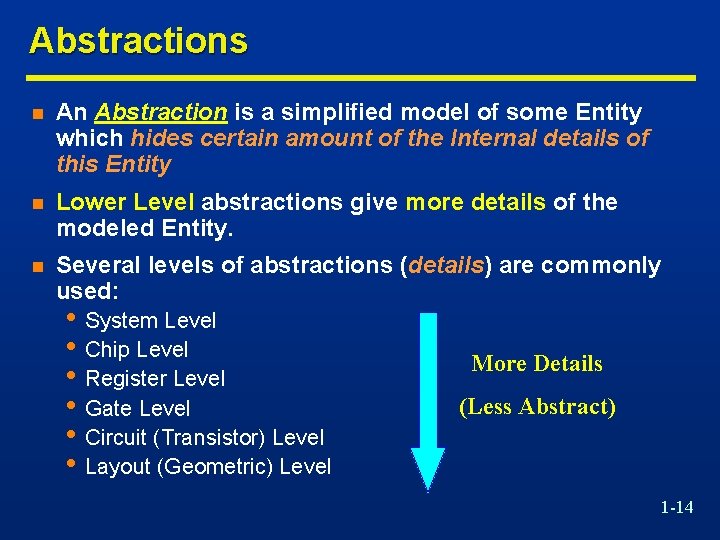

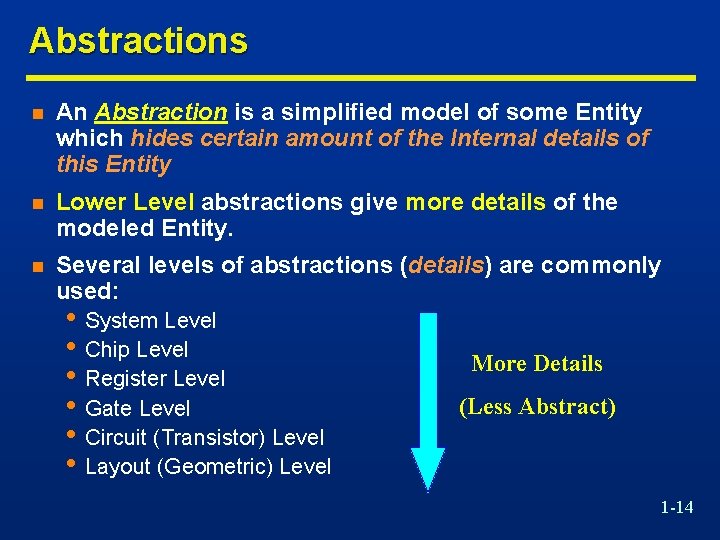

Abstractions n An Abstraction is a simplified model of some Entity which hides certain amount of the Internal details of this Entity n Lower Level abstractions give more details of the modeled Entity. n Several levels of abstractions (details) are commonly used: • System Level • Chip Level • Register Level • Gate Level • Circuit (Transistor) Level • Layout (Geometric) Level More Details (Less Abstract) 1 -14

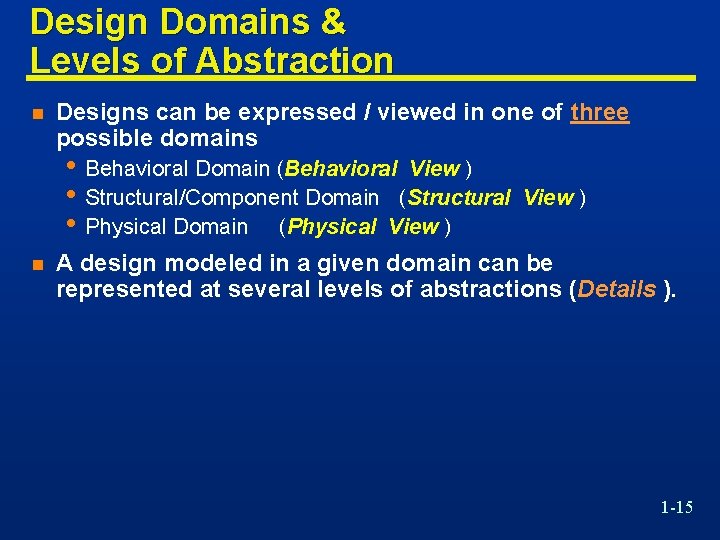

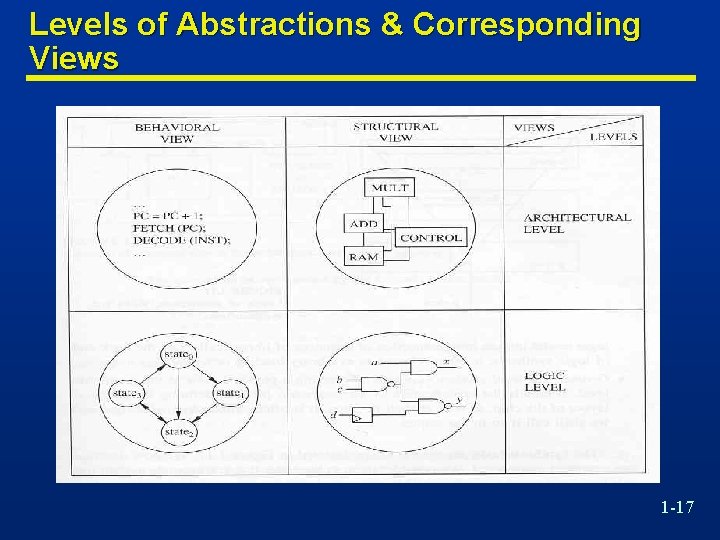

Design Domains & Levels of Abstraction n Designs can be expressed / viewed in one of three possible domains • Behavioral Domain (Behavioral View ) • Structural/Component Domain (Structural • Physical Domain (Physical View ) n View ) A design modeled in a given domain can be represented at several levels of abstractions (Details ). 1 -15

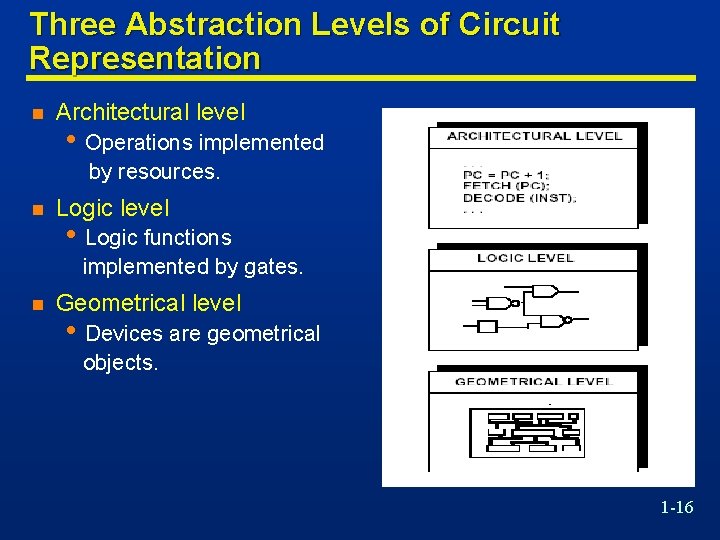

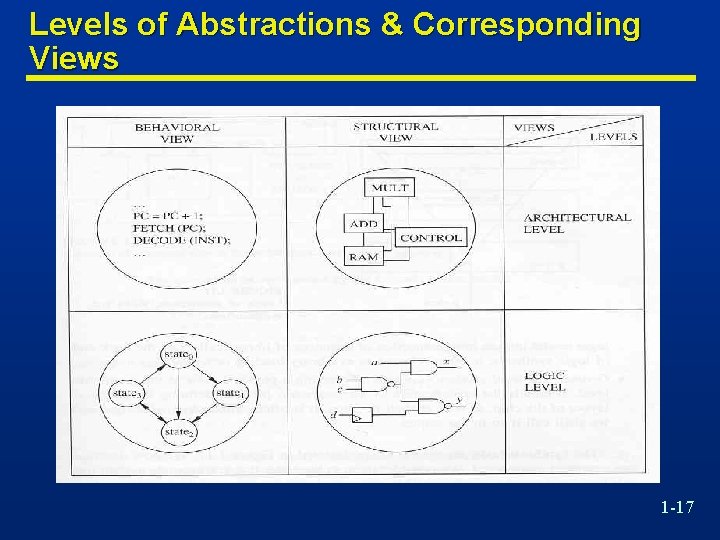

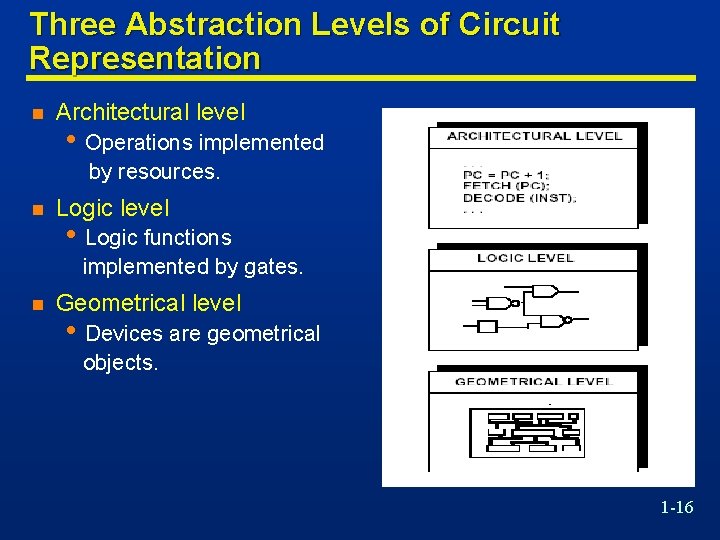

Three Abstraction Levels of Circuit Representation n Architectural level • Operations implemented by resources. n Logic level • Logic functions implemented by gates. n Geometrical level • Devices are geometrical objects. 1 -16

Levels of Abstractions & Corresponding Views 1 -17

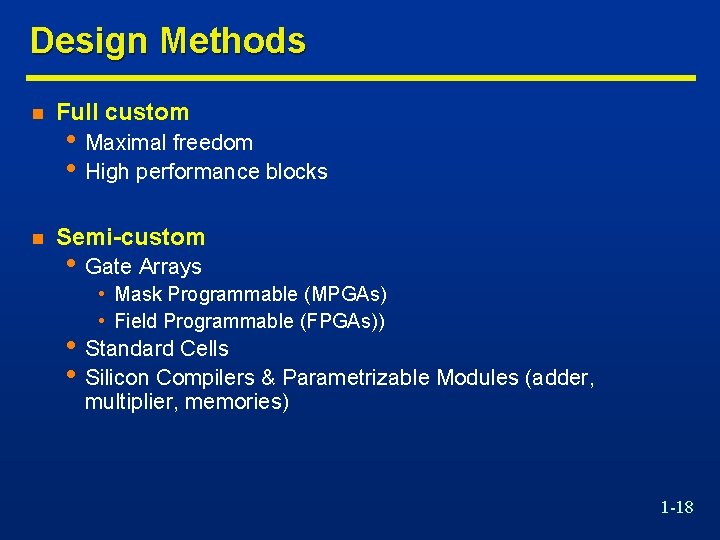

Design Methods n Full custom n Semi-custom • Maximal freedom • High performance blocks • Gate Arrays • Mask Programmable (MPGAs) • Field Programmable (FPGAs)) • Standard Cells • Silicon Compilers & Parametrizable Modules (adder, multiplier, memories) 1 -18

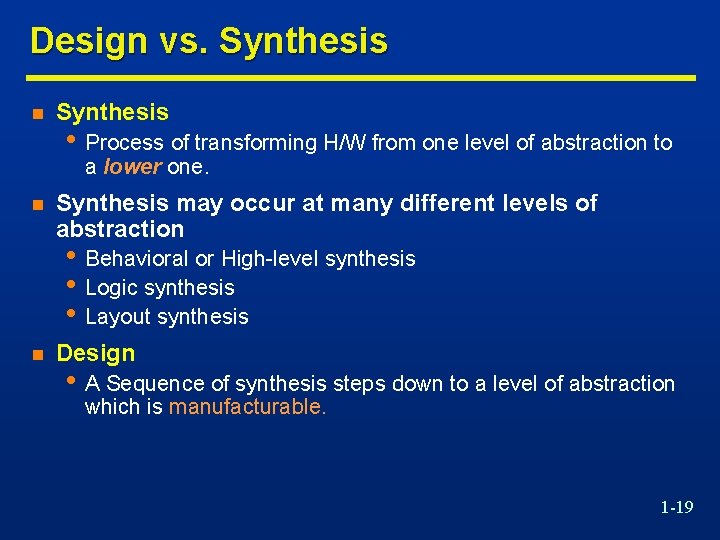

Design vs. Synthesis n Synthesis • Process of transforming H/W from one level of abstraction to a lower one. n Synthesis may occur at many different levels of abstraction • Behavioral or High-level synthesis • Logic synthesis • Layout synthesis n Design • A Sequence of synthesis steps down to a level of abstraction which is manufacturable. 1 -19

Synthesis Process 1 -20

Circuit Synthesis n Architectural-level synthesis • Determine the macroscopic structure • Interconnection of major building blocks. n Logic-level synthesis • Determine the microscopic structure • Interconnection of logic gates. n Geometrical-level synthesis (Physical design) • Placement and routing. • Determine positions and connections. 1 -21

Circuit Synthesis n We usually design using register-transfer-level (RTL) Verilog • Higher level of abstraction than gates n Synthesis tool translates to a circuit of gates that performs the same function n Specify to the tool n Post-synthesis verification • the target implementation fabric • constraints on timing, area, etc. • synthesized circuit meets constraints 1 -22

Physical Implementation n Implementation fabrics n Floor-planning: arranging the subsystems n Placement: arranging the gates within subsystems n Routing: joining the gates with wires n Physical verification • Application-specific ICs (ASICs) • Field-programmable gate arrays (FPGAs) • physical circuit still meets constraints • use better estimates of delays 1 -23

Hardware Description Languages n HDLs are used to describe the hardware for the purpose of modeling, simulation, testing, design, and documentation. • Modeling: behavior, flow of data, structure • Simulation: verification and test • Design: synthesis n Two widely-used HDLs today • VHDL: VHSIC (Very High Speed Integrated Circuit) • Hardware Description Language (IEEE standard) Verilog (from Cadence, IEEE standard) 1 -24

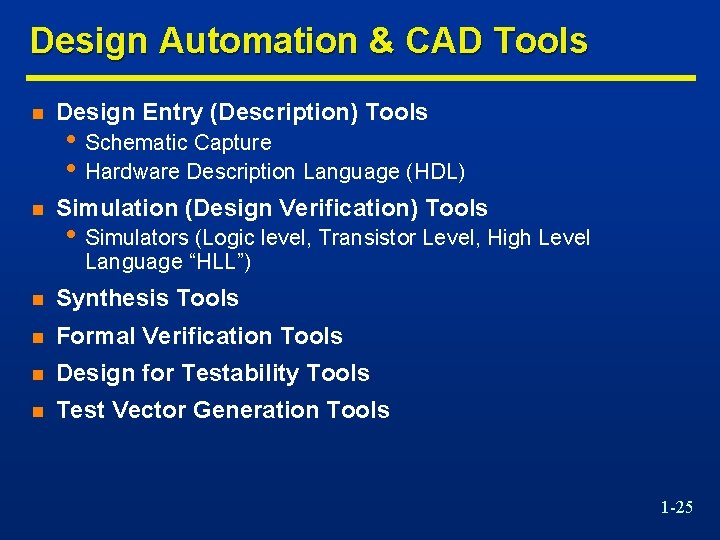

Design Automation & CAD Tools n Design Entry (Description) Tools n Simulation (Design Verification) Tools • Schematic Capture • Hardware Description Language (HDL) • Simulators (Logic level, Transistor Level, High Level Language “HLL”) n Synthesis Tools n Formal Verification Tools n Design for Testability Tools n Test Vector Generation Tools 1 -25