K thut s Chng 71 Gii thiu VHDL

![Architecture – Cú pháp đơn giản ARCHITECTURE architecture_name OF entity_name IS [ declarations ] Architecture – Cú pháp đơn giản ARCHITECTURE architecture_name OF entity_name IS [ declarations ]](https://slidetodoc.com/presentation_image_h2/52fcc2caa59f083c135cbdd2659d6607/image-48.jpg)

- Slides: 90

Kỹ thuật số Chương 7_1: Giới thiệu VHDL Biên soạn: Tống Văn On Bộ môn: Kỹ thuật Điện tử Khoa: Điện & Điện tử Trường: Đại học Bách khoa TP Hồ Chí Minh Năm học 2011 - 2012 ài liệu gốc: Introduction to VHDL, Department of Electrical and Computer Engineering George Mason University, Fall 2007).

Nội dung bài giảng • Lịch sử VHDL. • Các luồng thiết kế của VHDL. • VHDL để tổng hợp. 2

Lịch sử tóm tắt của VHDL ECE 545 – Introduction to VHDL 3

VHDL • VHDL là ngôn ngữ dùng để mô tả phần cứng của mạch số được sử dụng trong công nghiệp trên toàn cầu. • VHDL là từ cấu tạo bằng những chữ đầu của VHSIC (Very High Speed Integrated Circuit) Hardware Description Language. 4

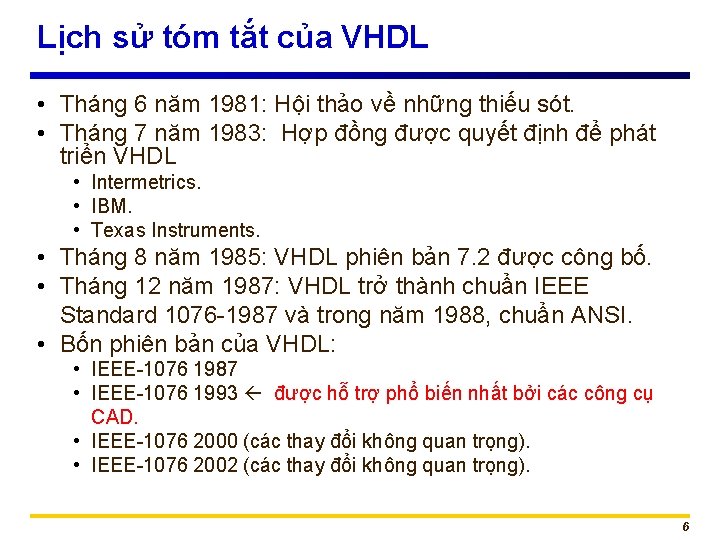

Sự hình thành VHDL • Trình độ phát triển của khoa học kỹ thuật vào khoảng những năm 1980: • Nhiều phương pháp nhập thiết kế và ngôn ngữ mô tả phần cứng được sử dụng. • Các thiết kế giữa những công cụ CAD từ những nhà cung cấp khác nhau không có tính di chuyển hoặc tính di chuyển bị giới hạn. • Mục đích: thu ngắn thời gian từ khái niệm thiết kế đến thực hiện từ 18 tháng xuống còn 6 tháng. 5

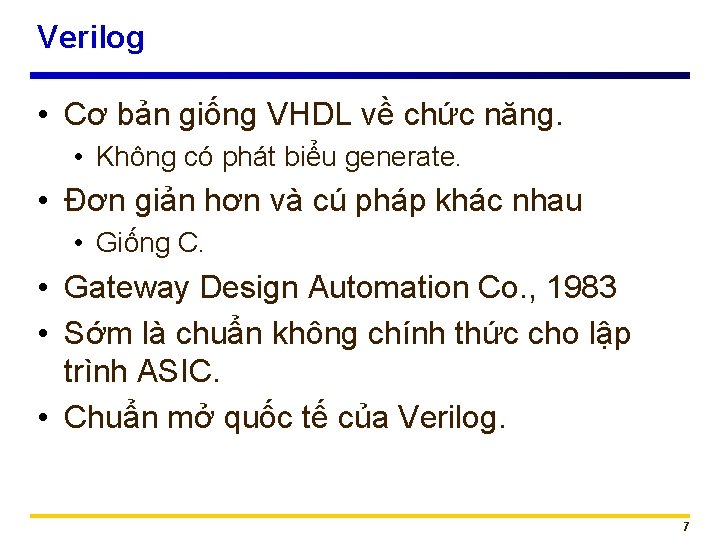

Lịch sử tóm tắt của VHDL • Tháng 6 năm 1981: Hội thảo về những thiếu sót. • Tháng 7 năm 1983: Hợp đồng được quyết định để phát triển VHDL • Intermetrics. • IBM. • Texas Instruments. • Tháng 8 năm 1985: VHDL phiên bản 7. 2 được công bố. • Tháng 12 năm 1987: VHDL trở thành chuẩn IEEE Standard 1076 -1987 và trong năm 1988, chuẩn ANSI. • Bốn phiên bản của VHDL: • IEEE-1076 1987 • IEEE-1076 1993 được hỗ trợ phổ biến nhất bởi các công cụ CAD. • IEEE-1076 2000 (các thay đổi không quan trọng). • IEEE-1076 2002 (các thay đổi không quan trọng). 6

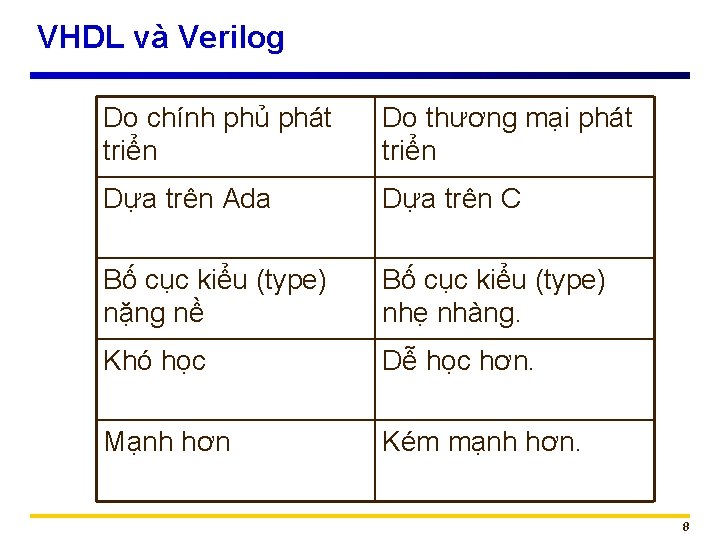

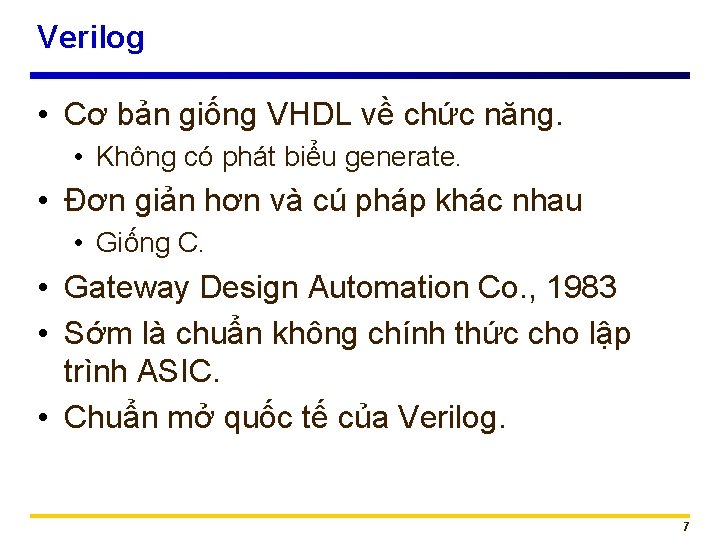

Verilog • Cơ bản giống VHDL về chức năng. • Không có phát biểu generate. • Đơn giản hơn và cú pháp khác nhau • Giống C. • Gateway Design Automation Co. , 1983 • Sớm là chuẩn không chính thức cho lập trình ASIC. • Chuẩn mở quốc tế của Verilog. 7

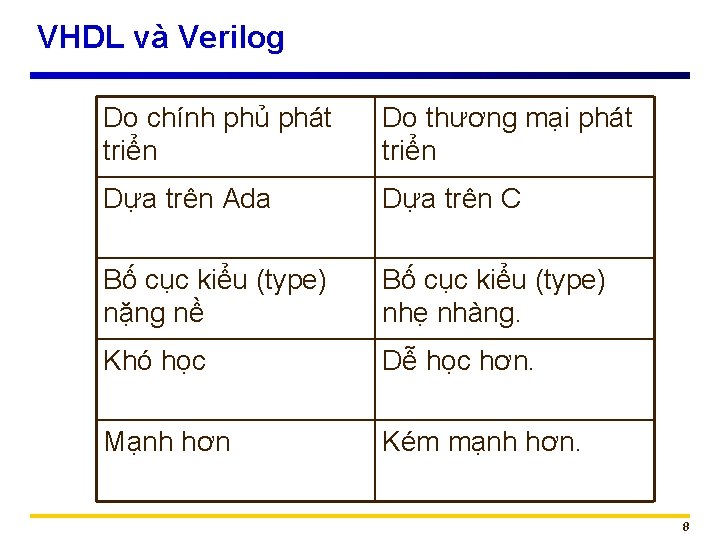

VHDL và Verilog Do chính phủ phát triển Do thương mại phát triển Dựa trên Ada Dựa trên C Bố cục kiểu (type) nặng nề Bố cục kiểu (type) nhẹ nhàng. Khó học Dễ học hơn. Mạnh hơn Kém mạnh hơn. 8

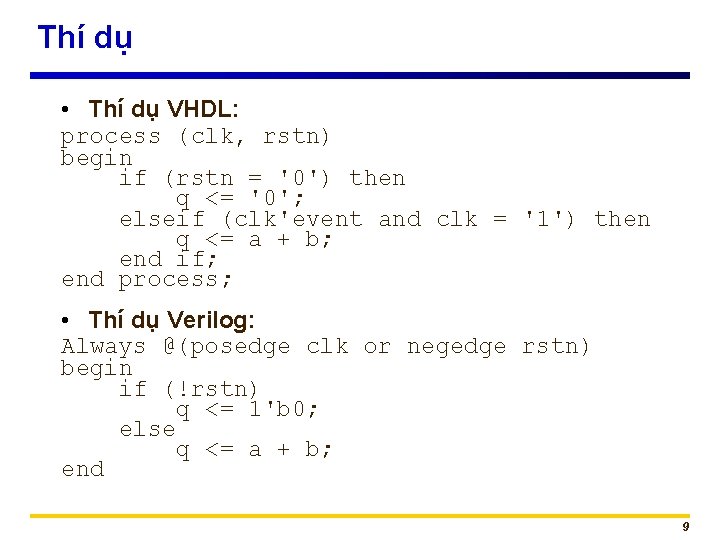

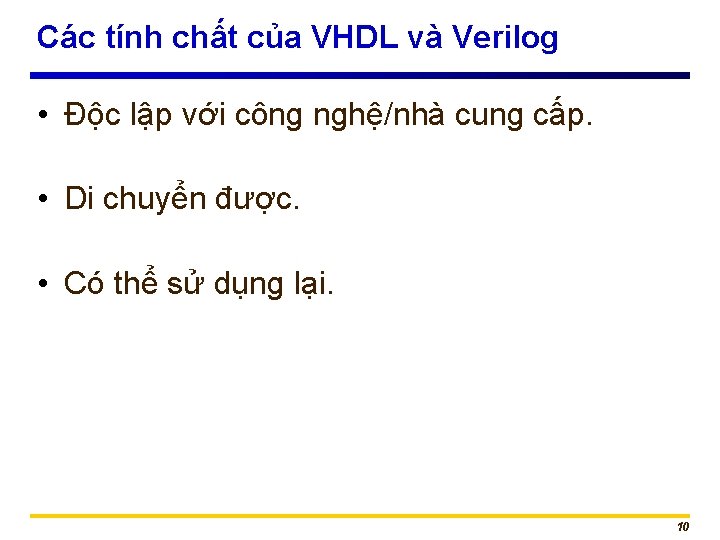

Thí dụ • Thí dụ VHDL: process (clk, rstn) begin if (rstn = '0') then q <= '0'; elseif (clk'event and clk = '1') then q <= a + b; end if; end process; • Thí dụ Verilog: Always @(posedge clk or negedge rstn) begin if (!rstn) q <= 1'b 0; else q <= a + b; end 9

Các tính chất của VHDL và Verilog • Độc lập với công nghệ/nhà cung cấp. • Di chuyển được. • Có thể sử dụng lại. 10

Các luồng thiết kế của VHDL

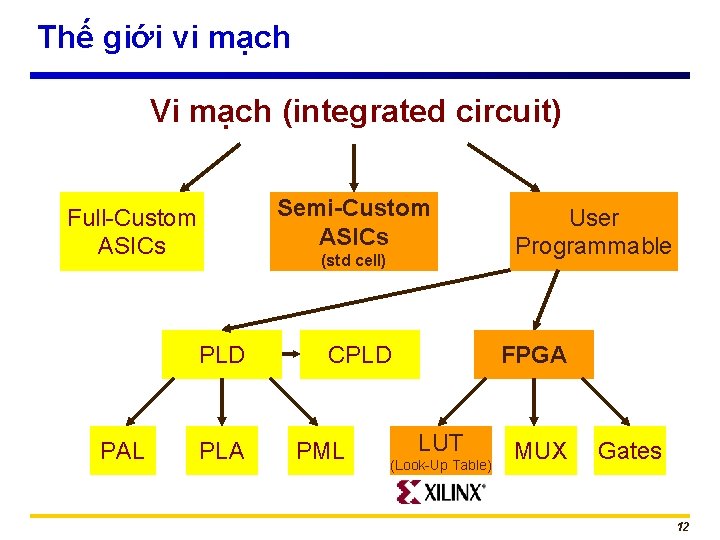

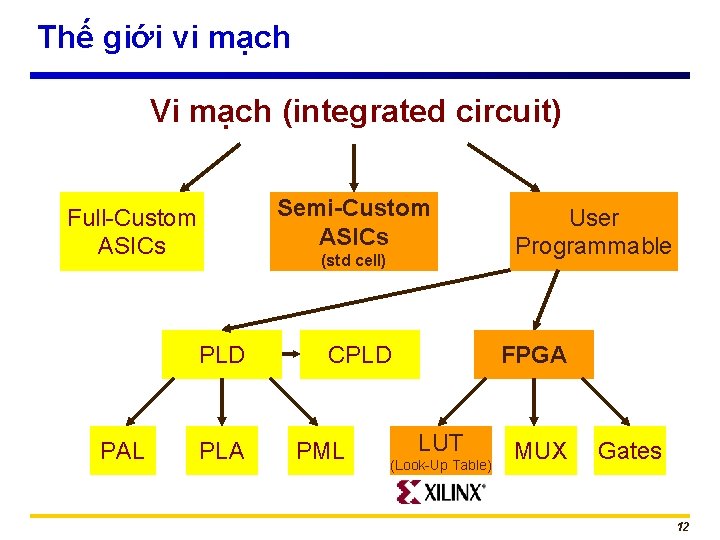

Thế giới vi mạch Vi mạch (integrated circuit) Semi-Custom ASICs Full-Custom ASICs (std cell) PLD PAL PLA CPLD PML User Programmable FPGA LUT (Look-Up Table) MUX Gates 12

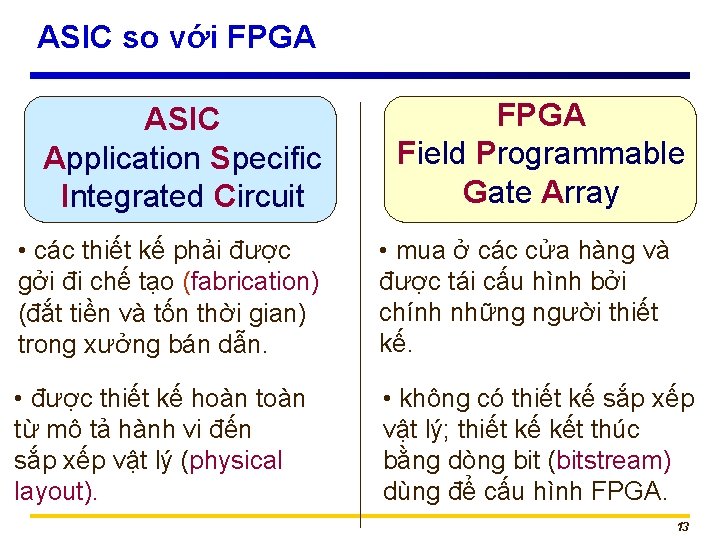

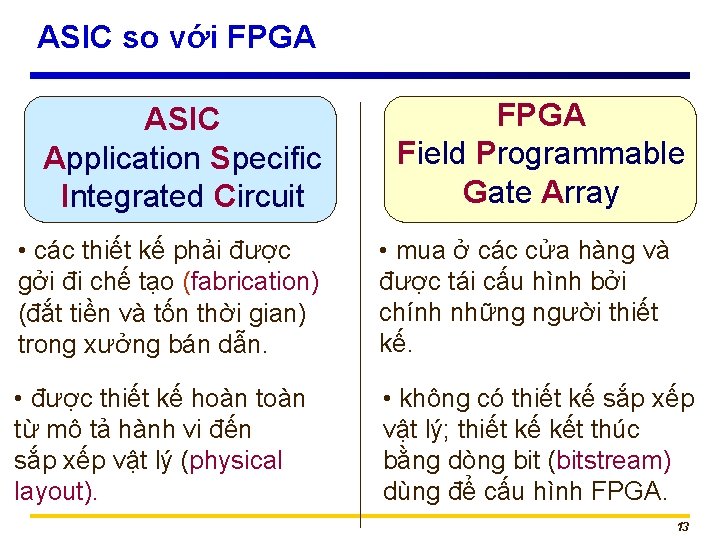

ASIC so với FPGA ASIC Application Specific Integrated Circuit FPGA Field Programmable Gate Array • các thiết kế phải được gởi đi chế tạo (fabrication) (đắt tiền và tốn thời gian) trong xưởng bán dẫn. • mua ở các cửa hàng và được tái cấu hình bởi chính những người thiết kế. • được thiết kế hoàn từ mô tả hành vi đến sắp xếp vật lý (physical layout). • không có thiết kế sắp xếp vật lý; thiết kế kết thúc bằng dòng bit (bitstream) dùng để cấu hình FPGA. 13

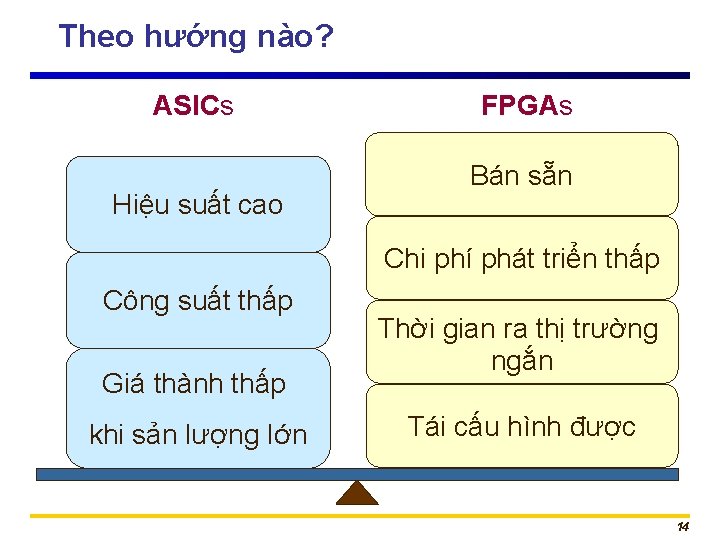

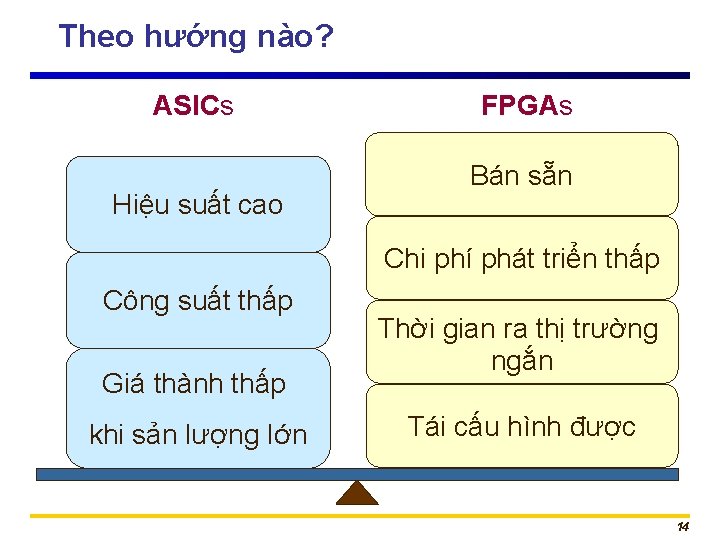

Theo hướng nào? ASICs Hiệu suất cao FPGAs Bán sẵn Chi phí phát triển thấp Công suất thấp Giá thành thấp khi sản lượng lớn Thời gian ra thị trường ngắn Tái cấu hình được 14

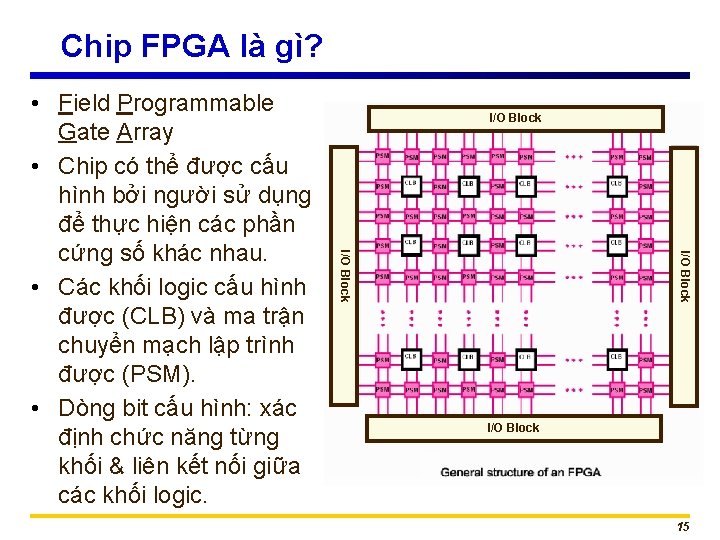

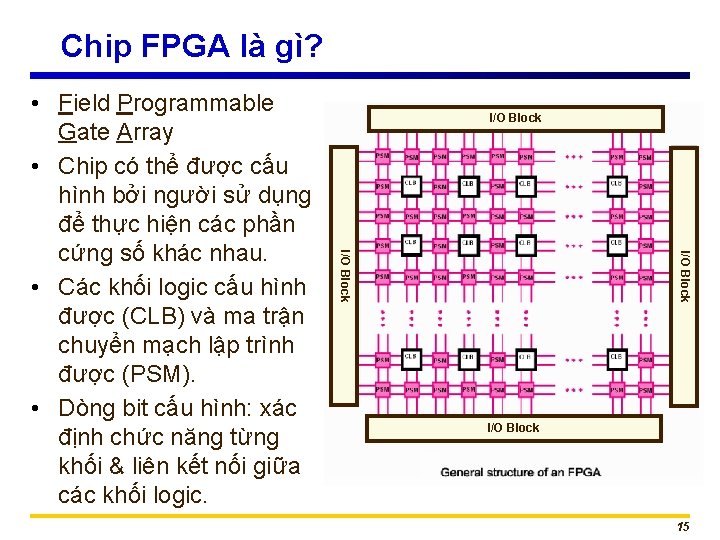

Chip FPGA là gì? I/O Block • Field Programmable Gate Array • Chip có thể được cấu hình bởi người sử dụng để thực hiện các phần cứng số khác nhau. • Các khối logic cấu hình được (CLB) và ma trận chuyển mạch lập trình được (PSM). • Dòng bit cấu hình: xác định chức năng từng khối & liên kết nối giữa các khối logic. I/O Block Source: [Brown 99] 15

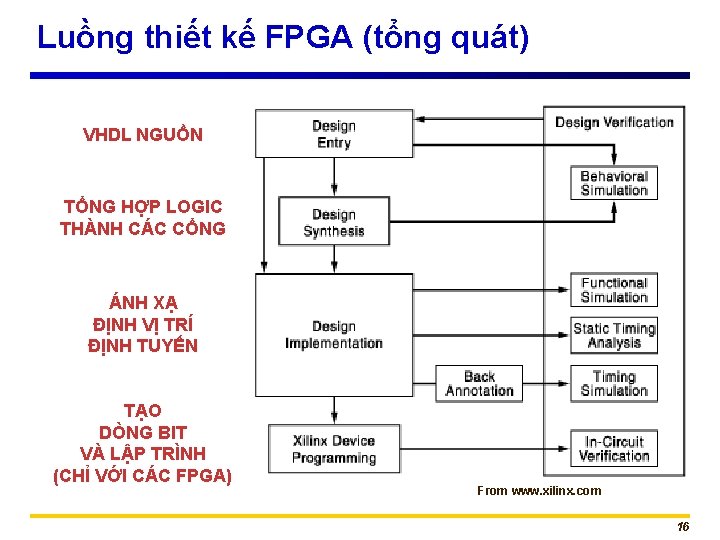

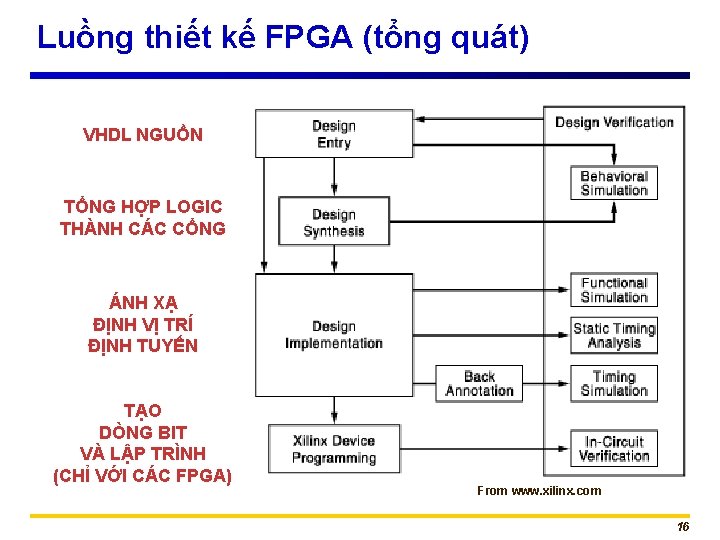

Luồng thiết kế FPGA (tổng quát) VHDL NGUỒN TỔNG HỢP LOGIC THÀNH CÁC CỔNG ÁNH XẠ ĐỊNH VỊ TRÍ ĐỊNH TUYẾN TẠO DÒNG BIT VÀ LẬP TRÌNH (CHỈ VỚI CÁC FPGA) From www. xilinx. com 16

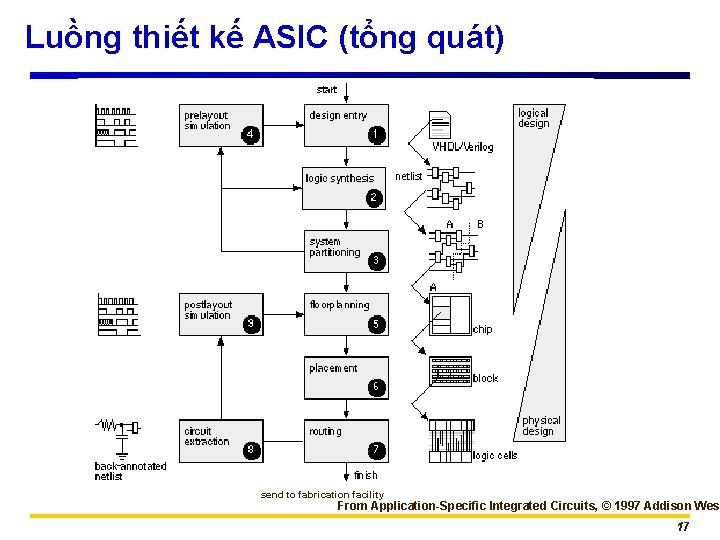

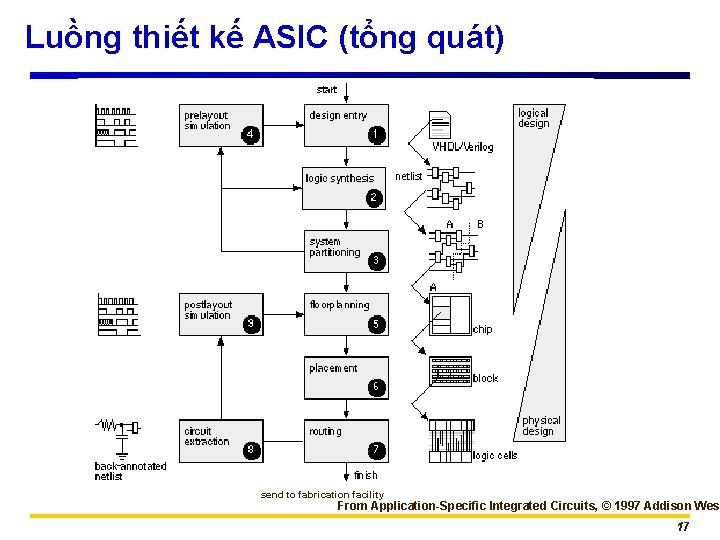

Luồng thiết kế ASIC (tổng quát) send to fabrication facility From Application-Specific Integrated Circuits, © 1997 Addison Wes 17

Luồng thiết kế của môn học này • Môn học này tập trung vào các luồng thiết kế FPGA. • Luồng thiết kế ASIC thuộc phạm vi của môn học khác. 18

VHDL để tổng hợp 19

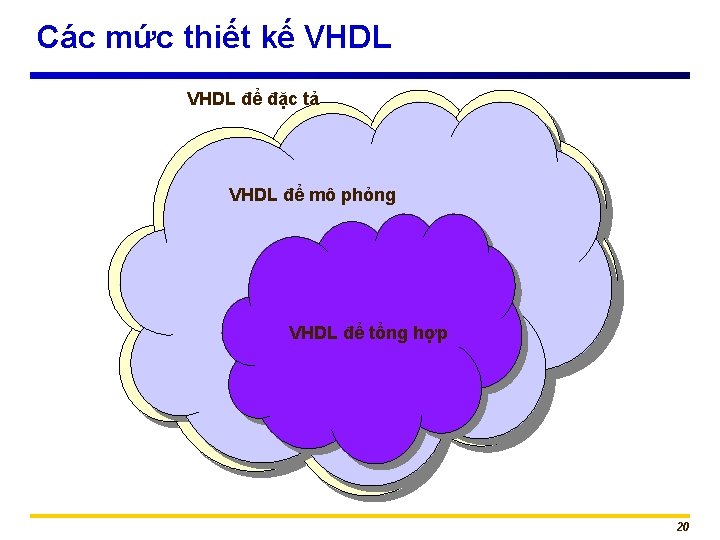

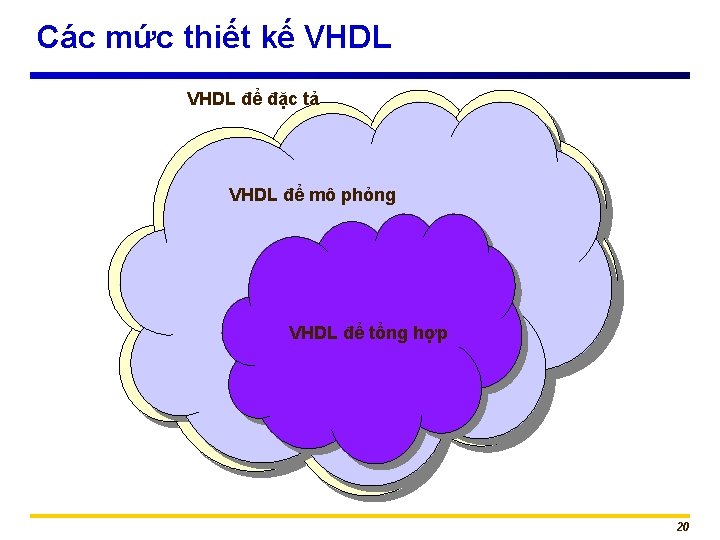

Các mức thiết kế VHDL để đặc tả VHDL để mô phỏng VHDL để tổng hợp 20

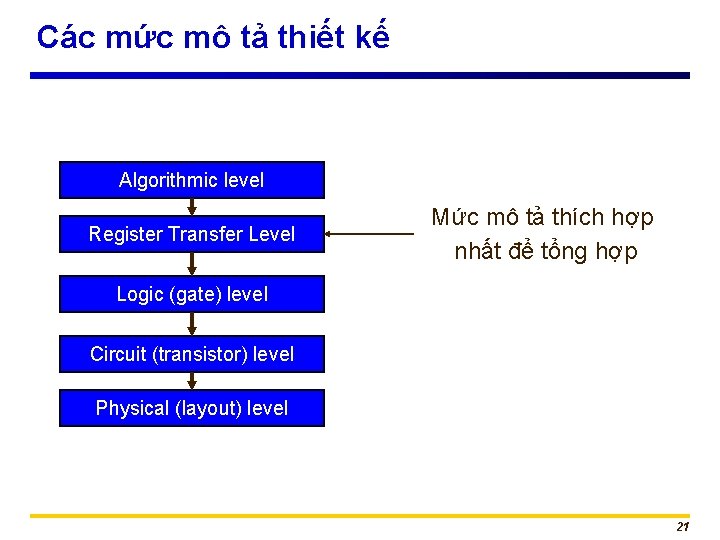

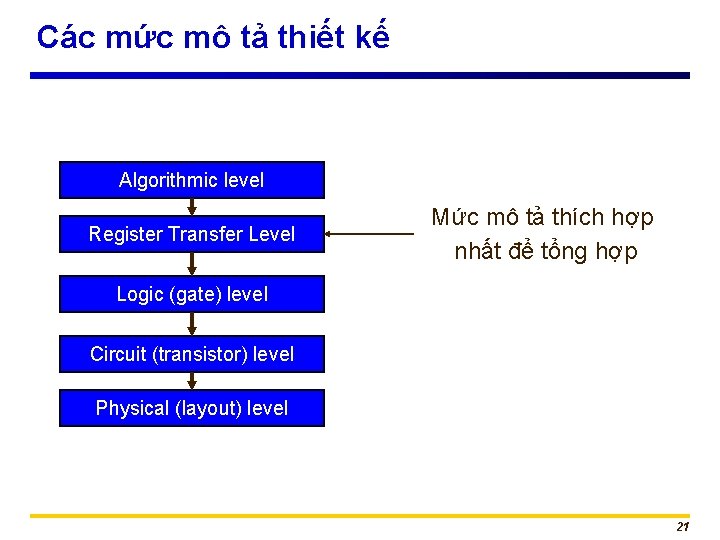

Các mức mô tả thiết kế Algorithmic level Register Transfer Level Mức mô tả thích hợp nhất để tổng hợp Logic (gate) level Circuit (transistor) level Physical (layout) level 21

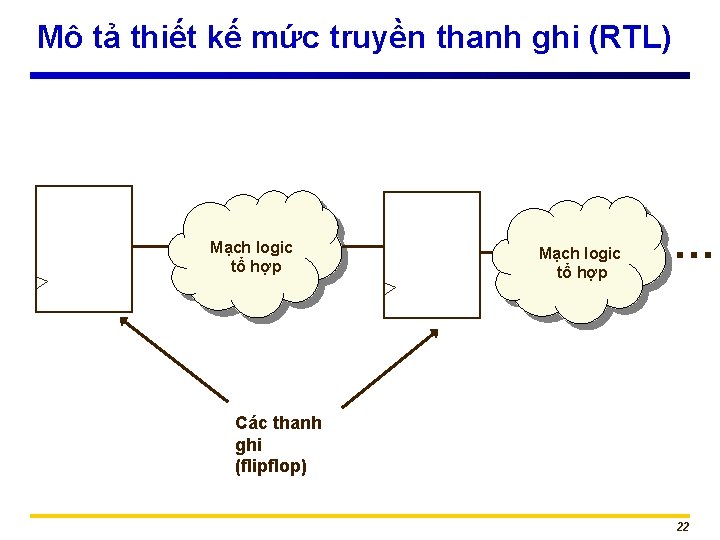

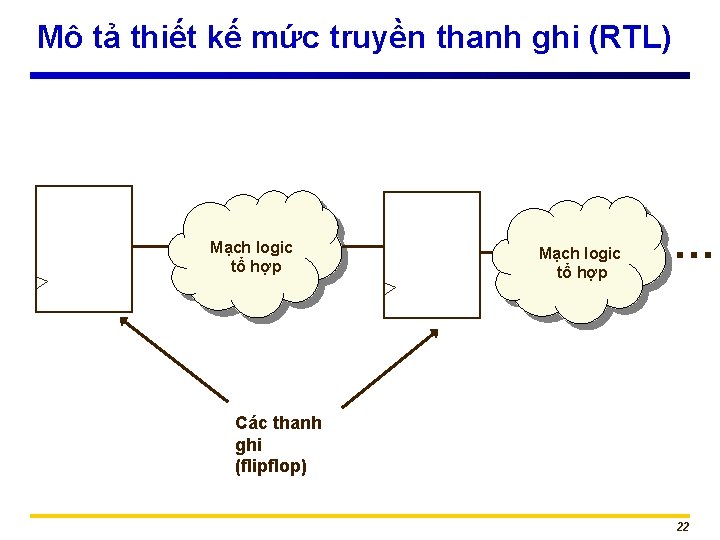

Mô tả thiết kế mức truyền thanh ghi (RTL) Mạch logic tổ hợp … Các thanh ghi (flipflop) 22

Các nguyên tắc cơ bản của VHDL 23

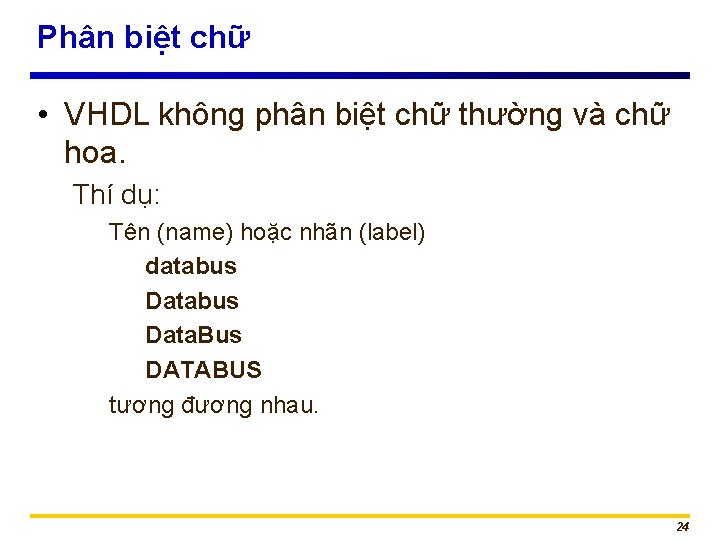

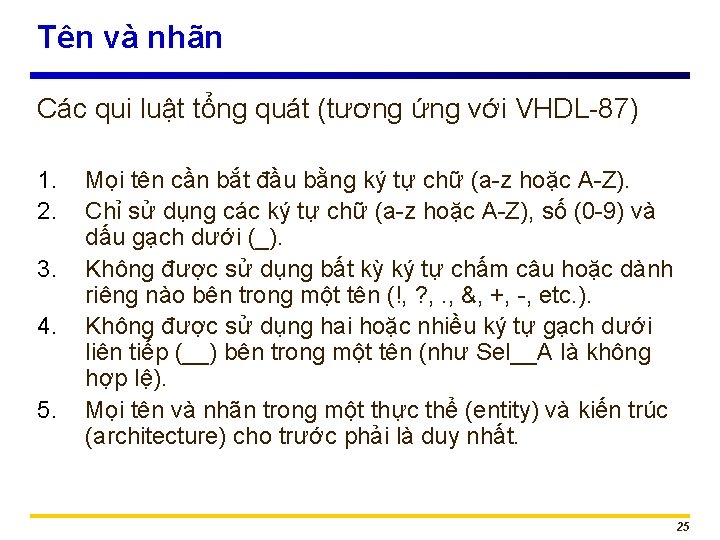

Phân biệt chữ • VHDL không phân biệt chữ thường và chữ hoa. Thí dụ: Tên (name) hoặc nhãn (label) databus Data. Bus DATABUS tương đương nhau. 24

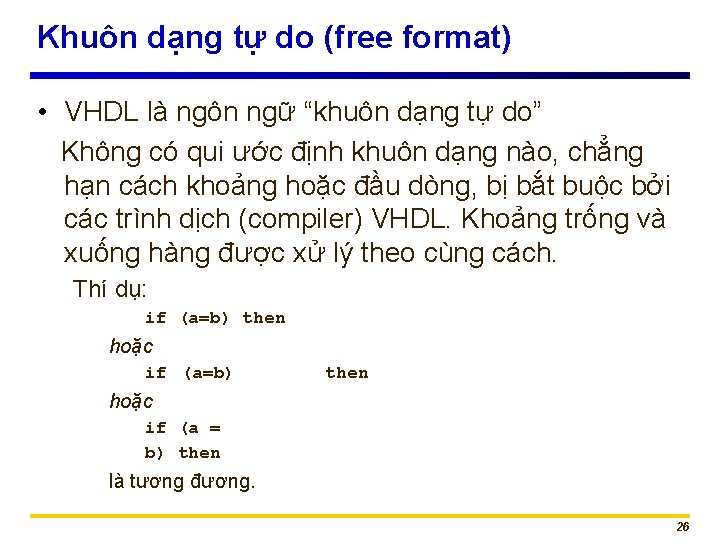

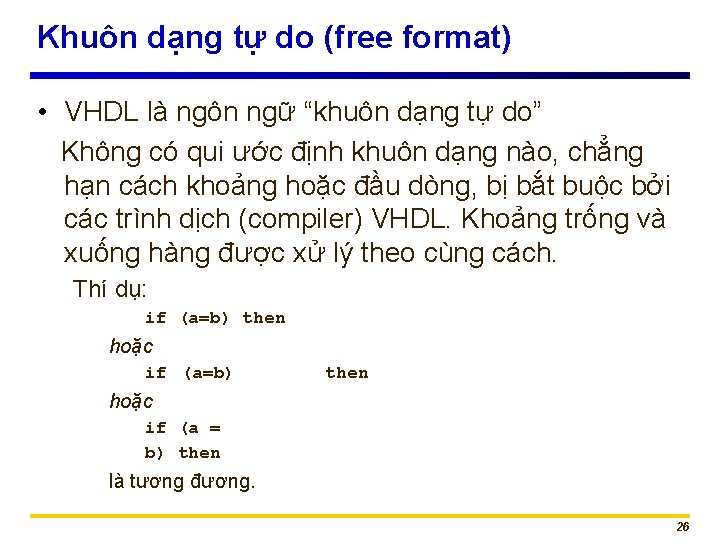

Tên và nhãn Các qui luật tổng quát (tương ứng với VHDL-87) 1. 2. 3. 4. 5. Mọi tên cần bắt đầu bằng ký tự chữ (a-z hoặc A-Z). Chỉ sử dụng các ký tự chữ (a-z hoặc A-Z), số (0 -9) và dấu gạch dưới (_). Không được sử dụng bất kỳ ký tự chấm câu hoặc dành riêng nào bên trong một tên (!, ? , . , &, +, -, etc. ). Không được sử dụng hai hoặc nhiều ký tự gạch dưới liên tiếp (__) bên trong một tên (như Sel__A là không hợp lệ). Mọi tên và nhãn trong một thực thể (entity) và kiến trúc (architecture) cho trước phải là duy nhất. 25

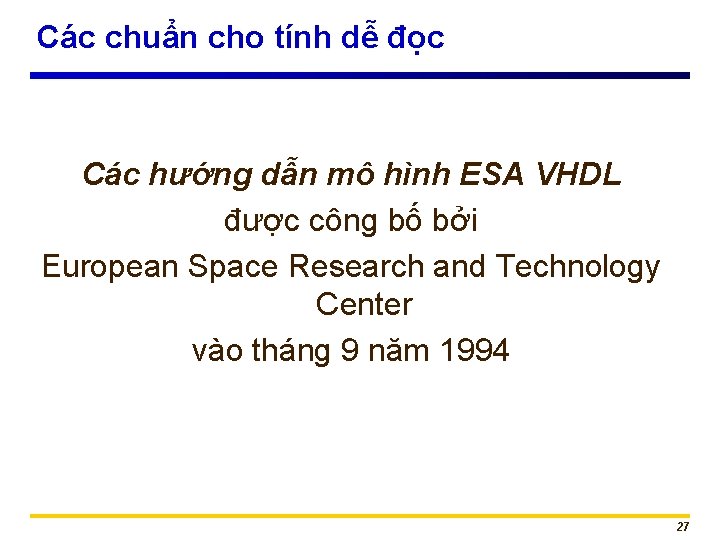

Khuôn dạng tự do (free format) • VHDL là ngôn ngữ “khuôn dạng tự do” Không có qui ước định khuôn dạng nào, chẳng hạn cách khoảng hoặc đầu dòng, bị bắt buộc bởi các trình dịch (compiler) VHDL. Khoảng trống và xuống hàng được xử lý theo cùng cách. Thí dụ: if (a=b) then hoặc if (a = b) then là tương đương. 26

Các chuẩn cho tính dễ đọc Các hướng dẫn mô hình ESA VHDL được công bố bởi European Space Research and Technology Center vào tháng 9 năm 1994 27

Các chuẩn cho tính dễ đọc Các hướng dẫn ESA bao trùm các vấn đề chọn lọc sau: • Kiểu viết nhất quán. • Các qui ước đặt tên nhất quán. • Đầu dòng nhất quán. • Kiểu chú thích nhất quán. • Các header của tập tin được khuyến khích. • Gán tên tập tin và các nội dung. • Số phát biểu (statement)/khai báo (declaration) mỗi hàng. • Thứ tự của các khai báo port và tín hiệu (signal). • Các cấu trúc (construct) cần tránh. 28

Chú thích (comment) • Các chú thích trong VHDL được chỉ ra bằng “hai dấu gạch ngang”, nghĩa là “--”. § Chỉ báo chú thích có thể đặt ở bất kỳ đâu trong dòng. § Đoạn văn bản bất kỳ theo sau trong cùng dòng được xử lý là một chú thích. § Ký tự xuống dòng sẽ kết thúc một chú thích. § Không có phương pháp cho việc chú thích một khối kéo dài trên hai dòng. Tí dụ: -- mạch con chính Data_in <= Data_bus; -- đọc dữ liệu từ FIFO đầu vào. 29

Chú thích • Giải thích chức năng của mô-đun cho những người thiết kế khác. • Có tính giải thích, không phải là phát biểu mô tả lại mã. • Đặt gần mã được mô tả • Đặt gần mã thực thi, không phải ở trong header. 30

Thực thể (entity) của thiết kế 31

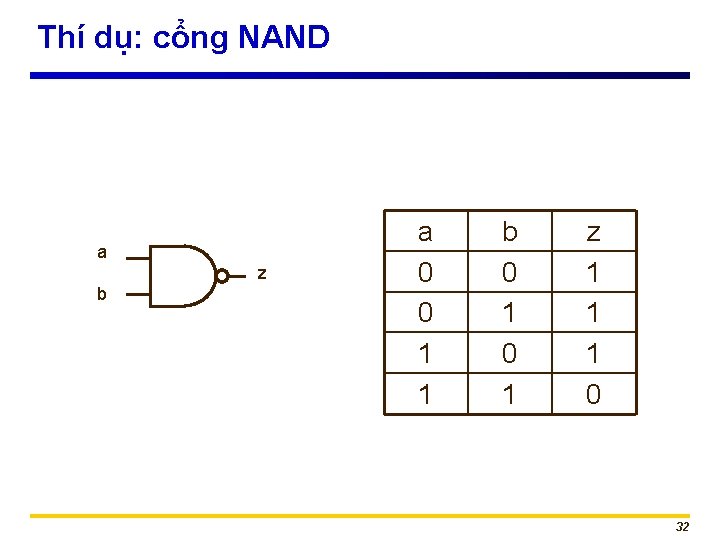

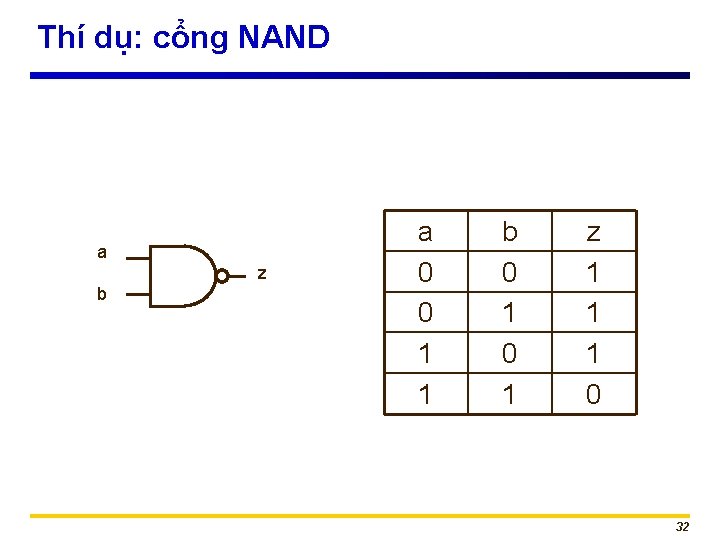

Thí dụ: cổng NAND a z b a 0 0 1 1 b 0 1 z 1 1 1 0 32

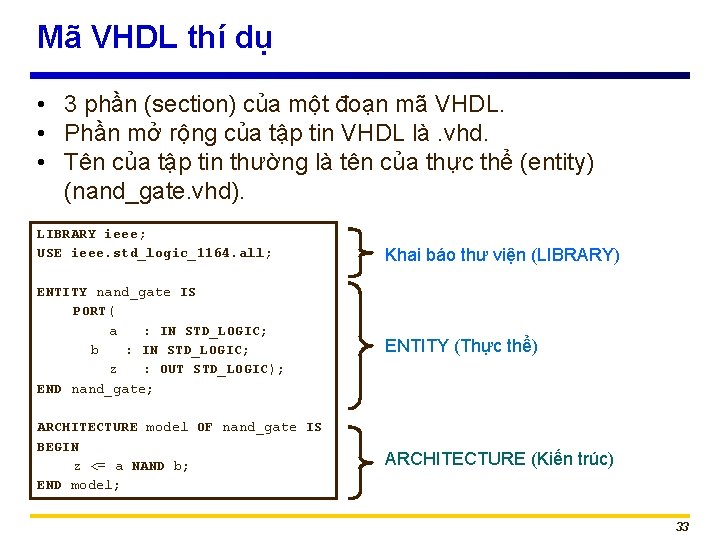

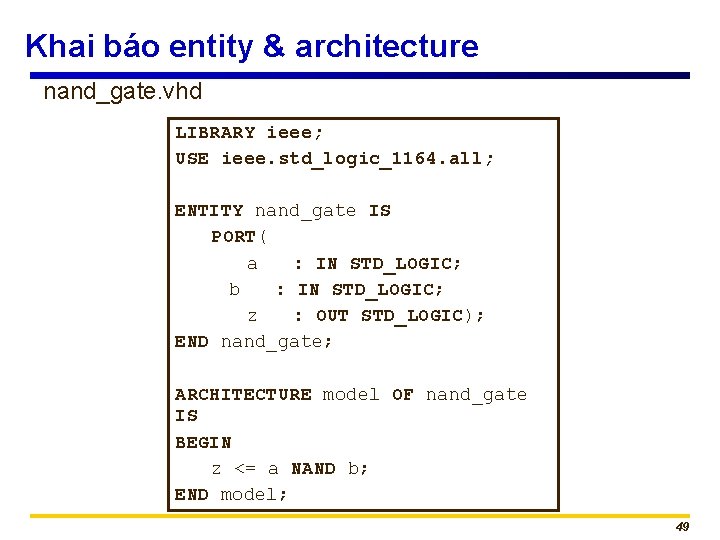

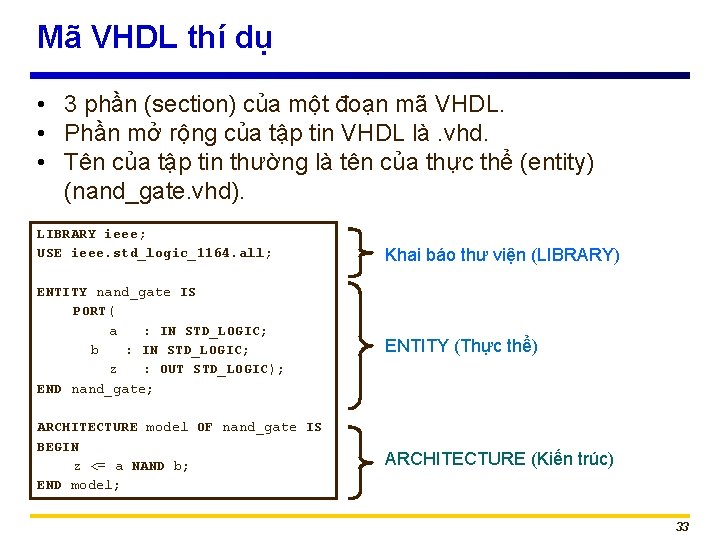

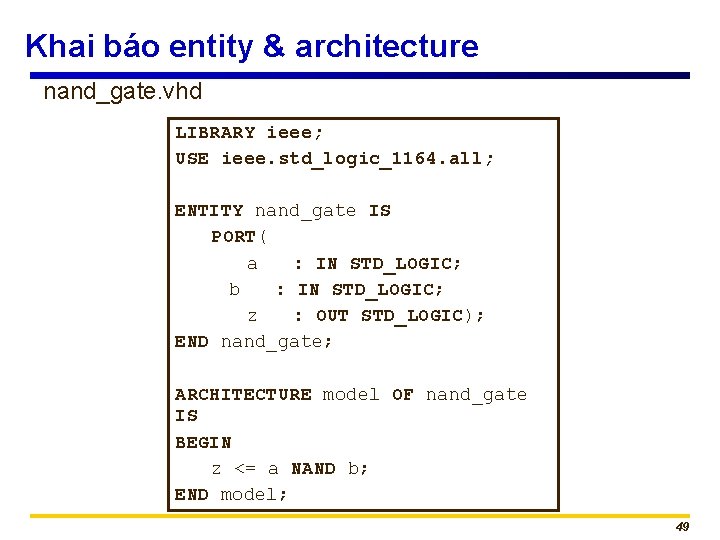

Mã VHDL thí dụ • 3 phần (section) của một đoạn mã VHDL. • Phần mở rộng của tập tin VHDL là. vhd. • Tên của tập tin thường là tên của thực thể (entity) (nand_gate. vhd). LIBRARY ieee; USE ieee. std_logic_1164. all; Khai báo thư viện (LIBRARY) ENTITY nand_gate IS PORT( a : IN STD_LOGIC; b : IN STD_LOGIC; z : OUT STD_LOGIC); END nand_gate; ENTITY (Thực thể) ARCHITECTURE model OF nand_gate IS BEGIN z <= a NAND b; END model; ARCHITECTURE (Kiến trúc) 33

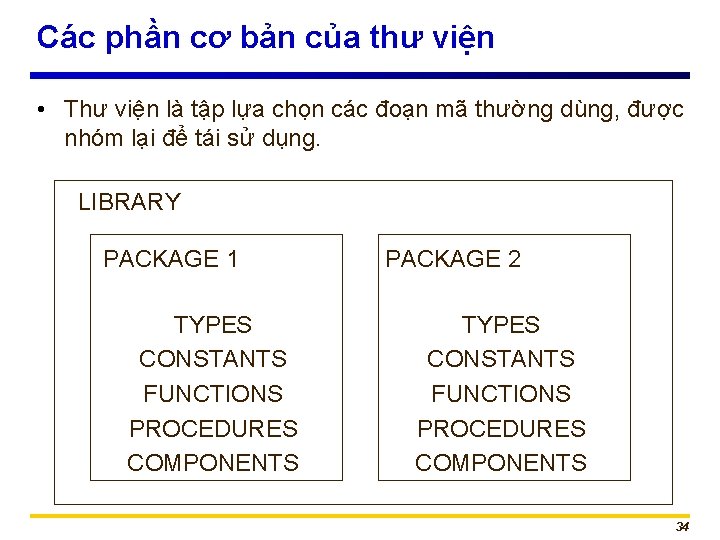

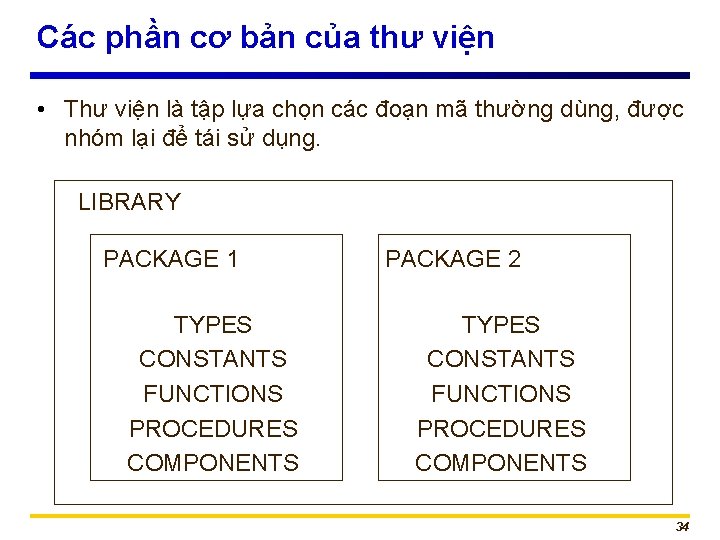

Các phần cơ bản của thư viện • Thư viện là tập lựa chọn các đoạn mã thường dùng, được nhóm lại để tái sử dụng. LIBRARY PACKAGE 1 TYPES CONSTANTS FUNCTIONS PROCEDURES COMPONENTS PACKAGE 2 TYPES CONSTANTS FUNCTIONS PROCEDURES COMPONENTS 34

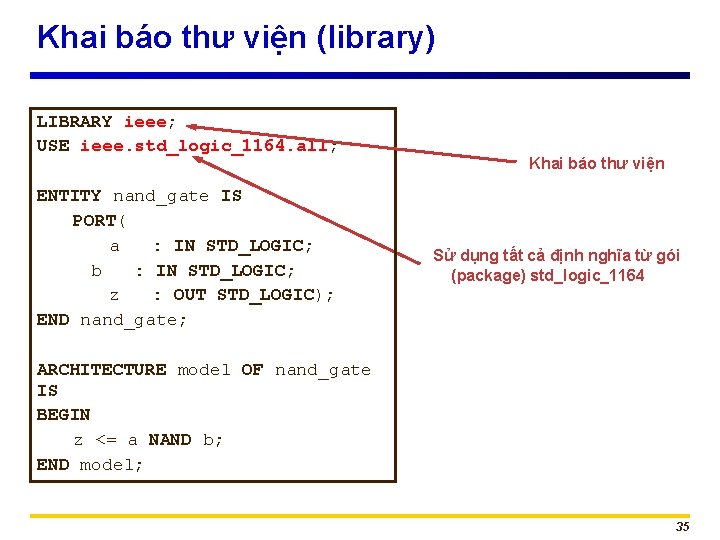

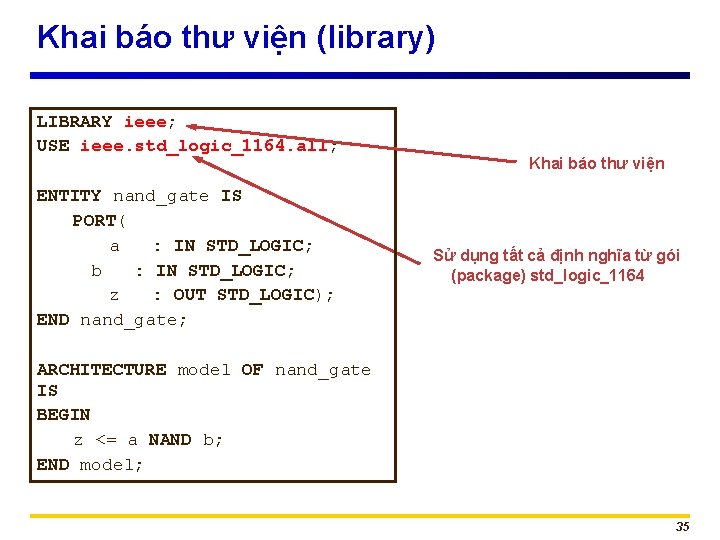

Khai báo thư viện (library) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY nand_gate IS PORT( a : IN STD_LOGIC; b : IN STD_LOGIC; z : OUT STD_LOGIC); END nand_gate; Khai báo thư viện Sử dụng tất cả định nghĩa từ gói (package) std_logic_1164 ARCHITECTURE model OF nand_gate IS BEGIN z <= a NAND b; END model; 35

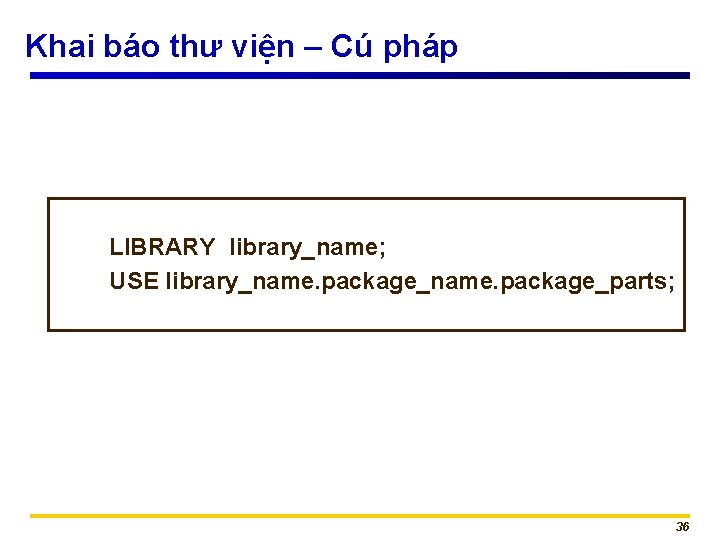

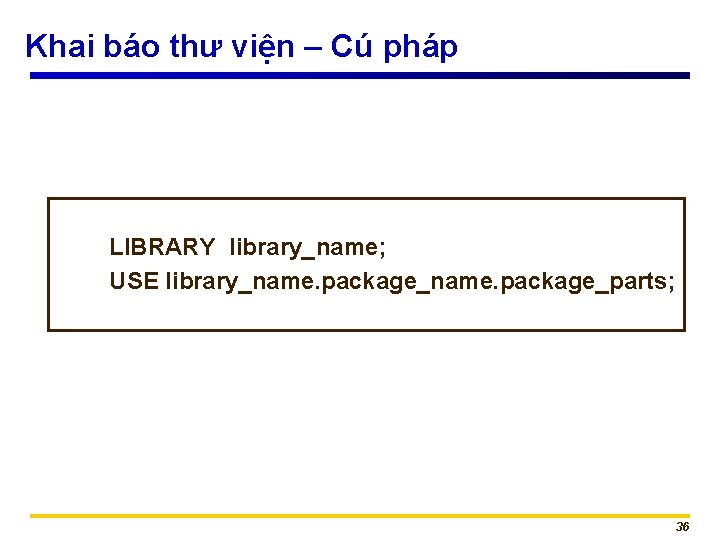

Khai báo thư viện – Cú pháp LIBRARY library_name; USE library_name. package_parts; 36

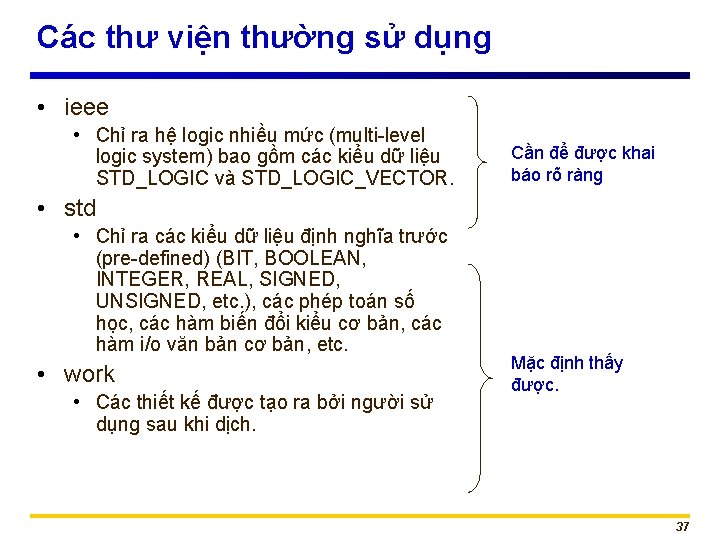

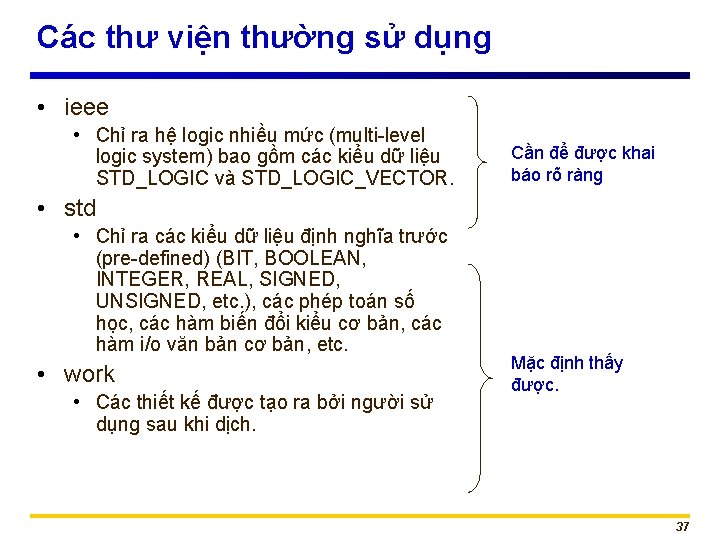

Các thư viện thường sử dụng • ieee • Chỉ ra hệ logic nhiều mức (multi-level logic system) bao gồm các kiểu dữ liệu STD_LOGIC và STD_LOGIC_VECTOR. Cần để được khai báo rõ ràng • std • Chỉ ra các kiểu dữ liệu định nghĩa trước (pre-defined) (BIT, BOOLEAN, INTEGER, REAL, SIGNED, UNSIGNED, etc. ), các phép toán số học, các hàm biến đổi kiểu cơ bản, các hàm i/o văn bản cơ bản, etc. • work • Các thiết kế được tạo ra bởi người sử dụng sau khi dịch. Mặc định thấy được. 37

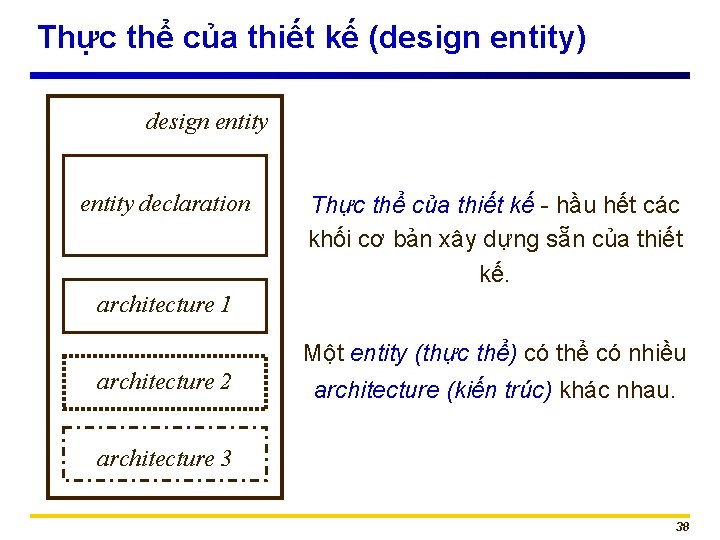

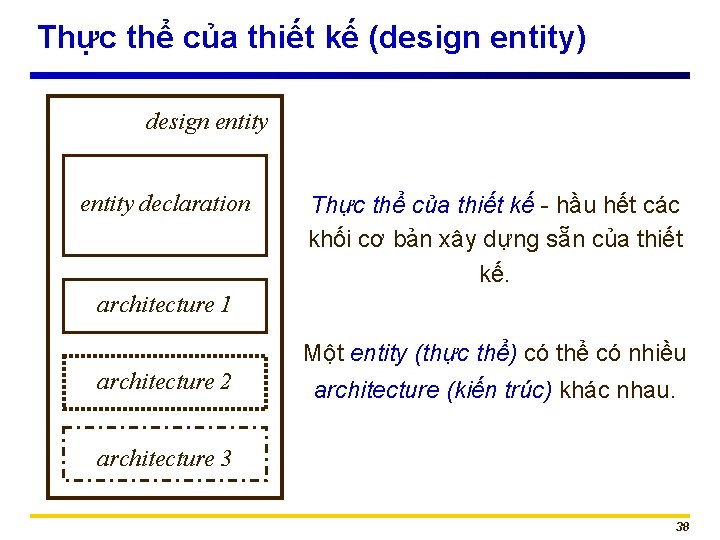

Thực thể của thiết kế (design entity) design entity declaration Thực thể của thiết kế - hầu hết các khối cơ bản xây dựng sẵn của thiết kế. architecture 1 Một entity (thực thể) có thể có nhiều architecture 2 architecture (kiến trúc) khác nhau. architecture 3 38

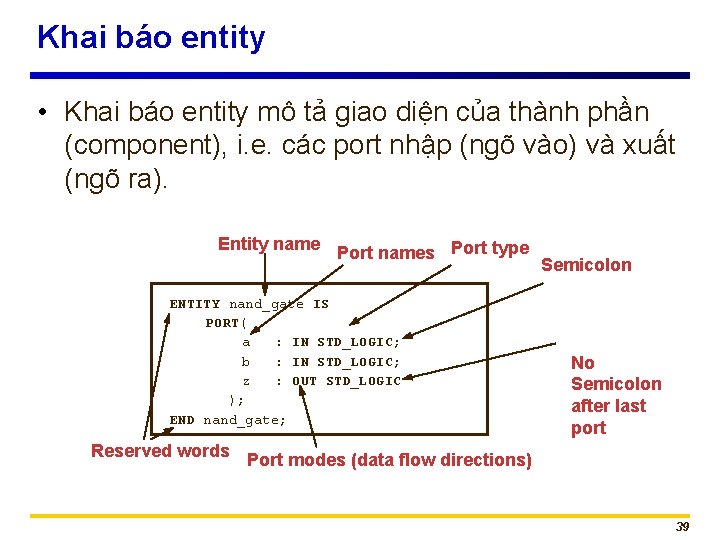

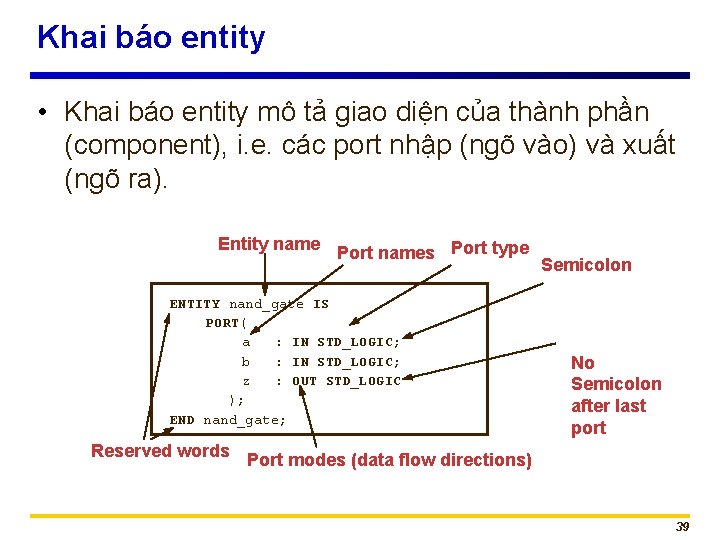

Khai báo entity • Khai báo entity mô tả giao diện của thành phần (component), i. e. các port nhập (ngõ vào) và xuất (ngõ ra). Entity name Port names Port type ENTITY nand_gate IS PORT( a : IN STD_LOGIC; b : IN STD_LOGIC; z : OUT STD_LOGIC ); END nand_gate; Semicolon No Semicolon after last port Reserved words Port modes (data flow directions) 39

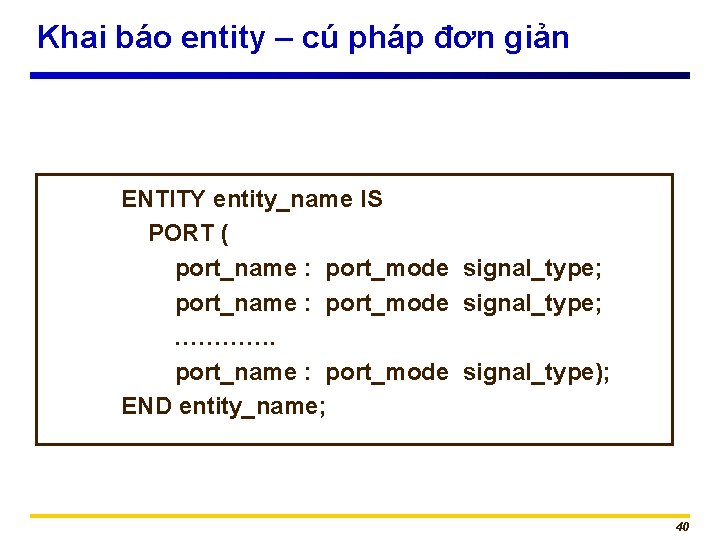

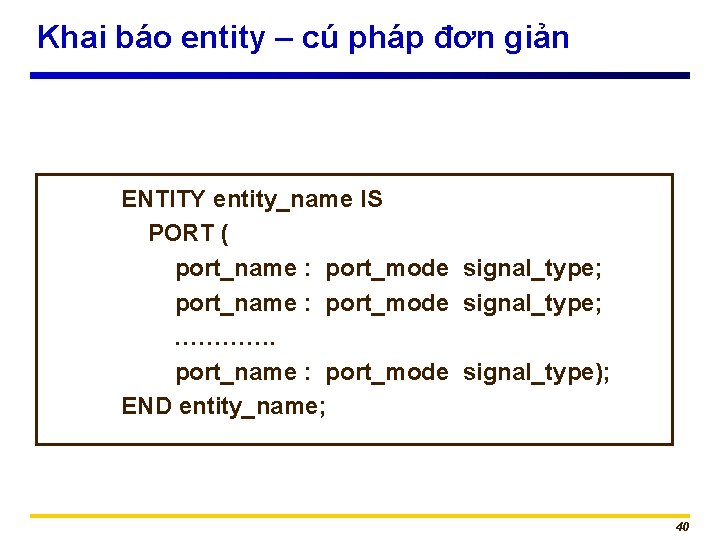

Khai báo entity – cú pháp đơn giản ENTITY entity_name IS PORT ( port_name : port_mode signal_type; …………. port_name : port_mode signal_type); END entity_name; 40

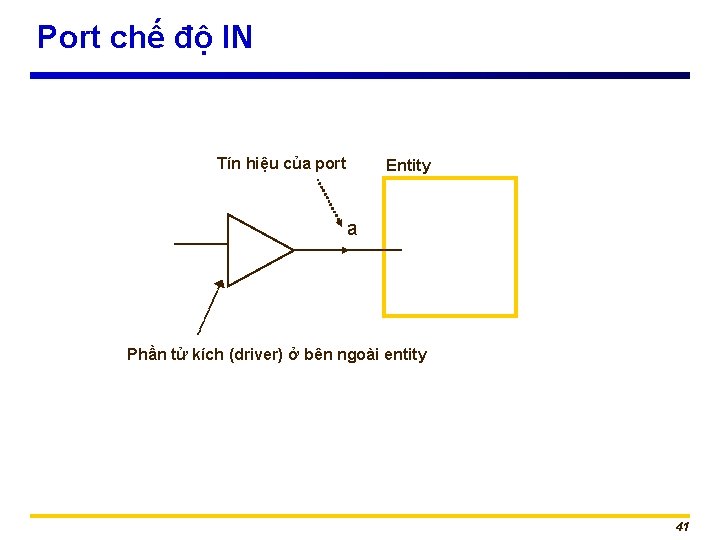

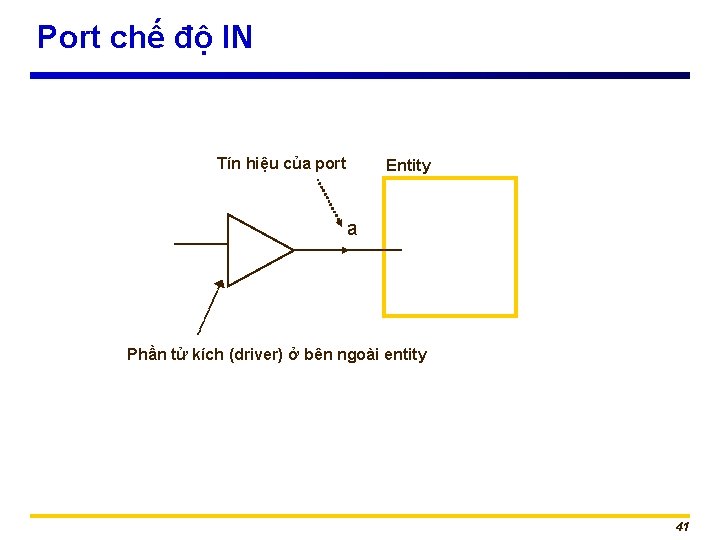

Port chế độ IN Tín hiệu của port Entity a Phần tử kích (driver) ở bên ngoài entity 41

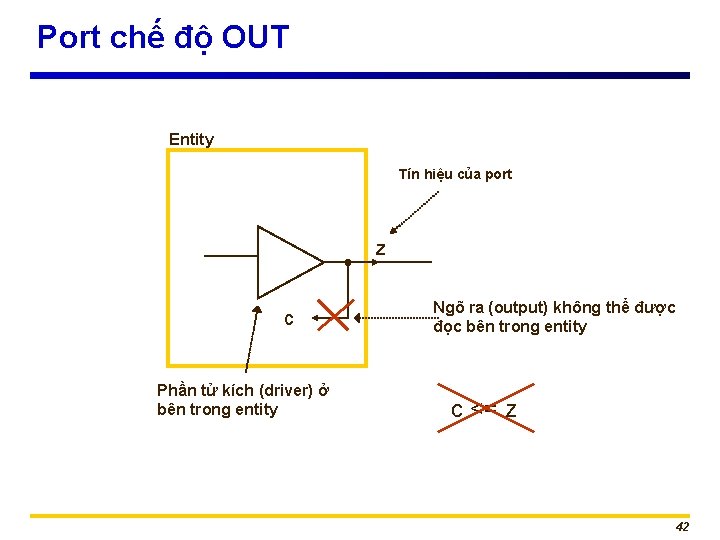

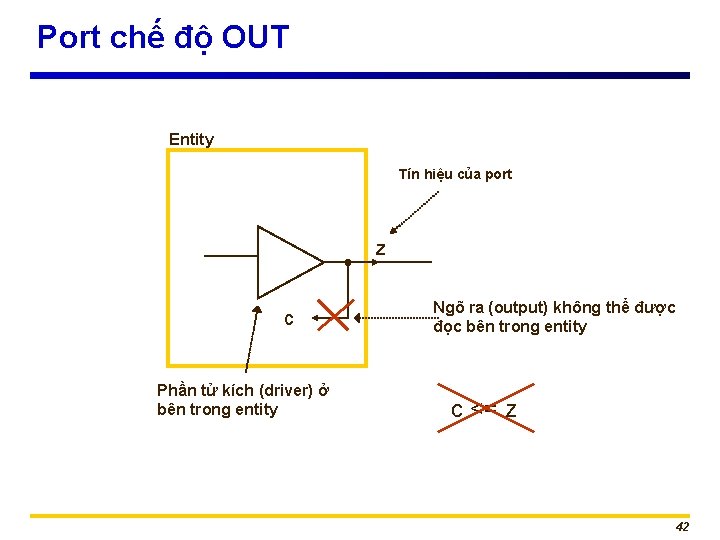

Port chế độ OUT Entity Tín hiệu của port z c Phần tử kích (driver) ở bên trong entity Ngõ ra (output) không thể được đọc bên trong entity c <= z 42

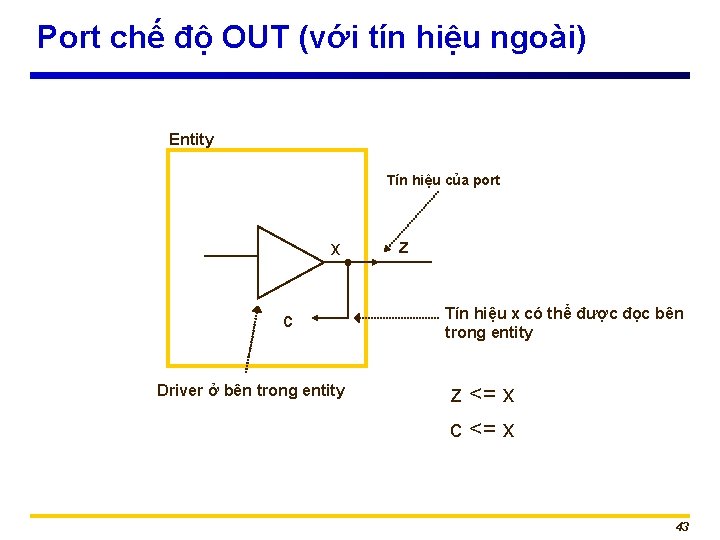

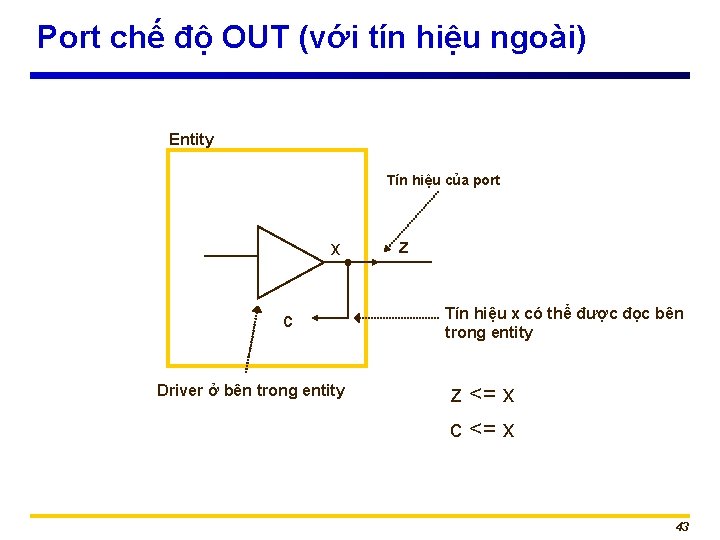

Port chế độ OUT (với tín hiệu ngoài) Entity Tín hiệu của port x c Driver ở bên trong entity z Tín hiệu x có thể được đọc bên trong entity z <= x c <= x 43

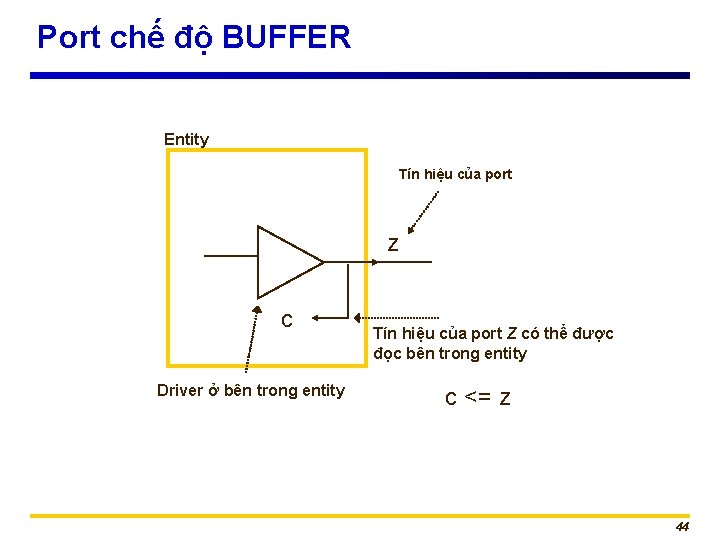

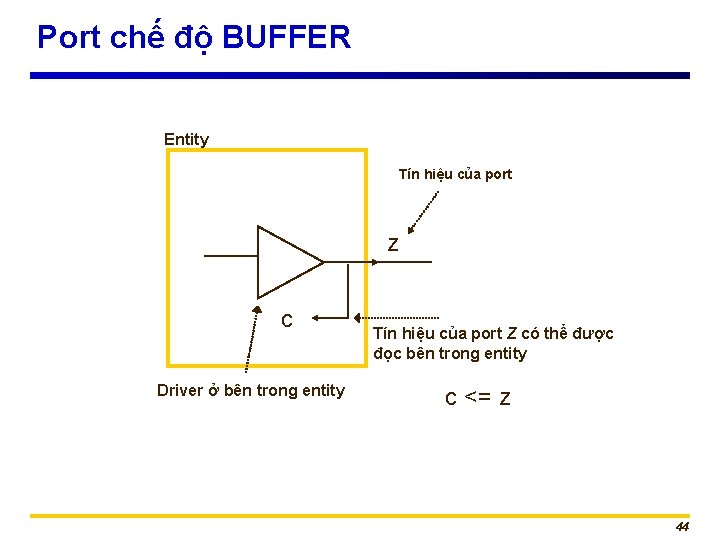

Port chế độ BUFFER Entity Tín hiệu của port z c Driver ở bên trong entity Tín hiệu của port Z có thể được đọc bên trong entity c <= z 44

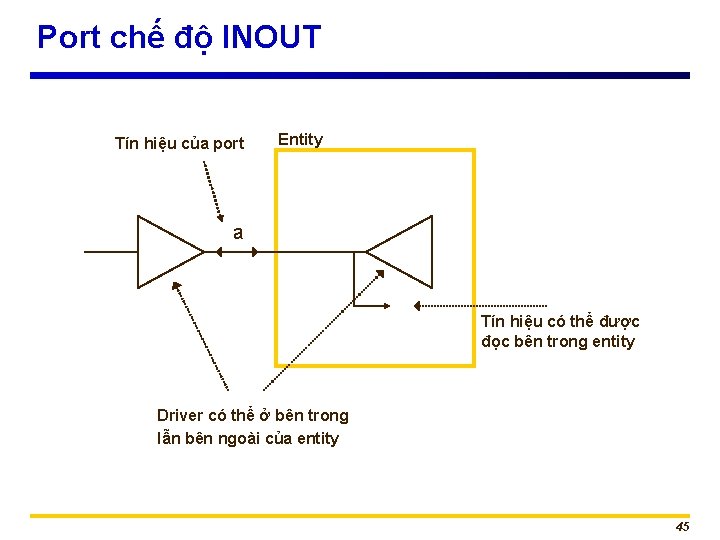

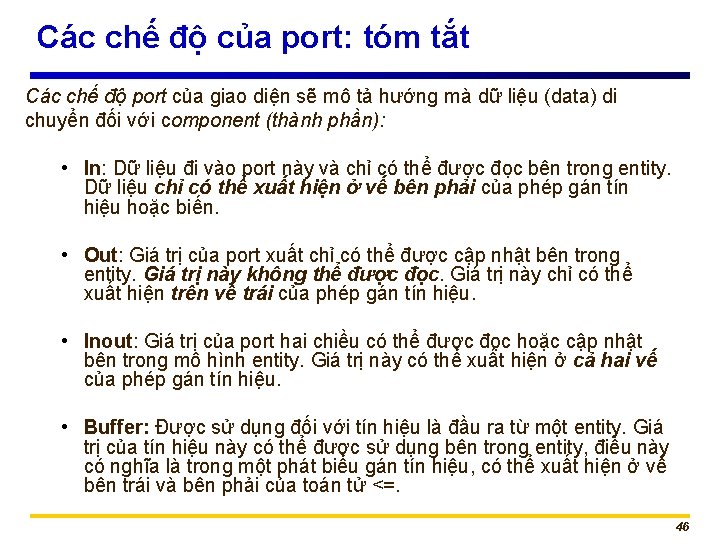

Port chế độ INOUT Tín hiệu của port Entity a Tín hiệu có thể được đọc bên trong entity Driver có thể ở bên trong lẫn bên ngoài của entity 45

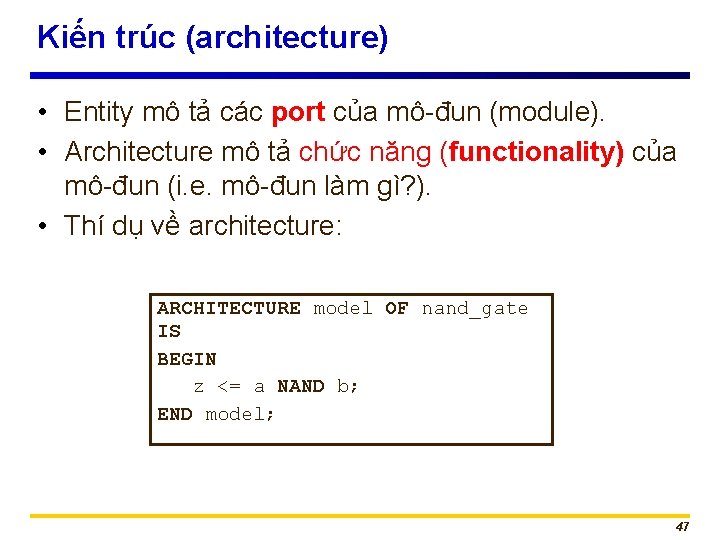

Các chế độ của port: tóm tắt Các chế độ port của giao diện sẽ mô tả hướng mà dữ liệu (data) di chuyển đối với component (thành phần): • In: Dữ liệu đi vào port này và chỉ có thể được đọc bên trong entity. Dữ liệu chỉ có thể xuất hiện ở vế bên phải của phép gán tín hiệu hoặc biến. • Out: Giá trị của port xuất chỉ có thể được cập nhật bên trong entity. Giá trị này không thể được đọc. Giá trị này chỉ có thể xuất hiện trên vế trái của phép gán tín hiệu. • Inout: Giá trị của port hai chiều có thể được đọc hoặc cập nhật bên trong mô hình entity. Giá trị này có thể xuất hiện ở cả hai vế của phép gán tín hiệu. • Buffer: Được sử dụng đối với tín hiệu là đầu ra từ một entity. Giá trị của tín hiệu này có thể được sử dụng bên trong entity, điều này có nghĩa là trong một phát biểu gán tín hiệu, có thể xuất hiện ở vế bên trái và bên phải của toán tử <=. 46

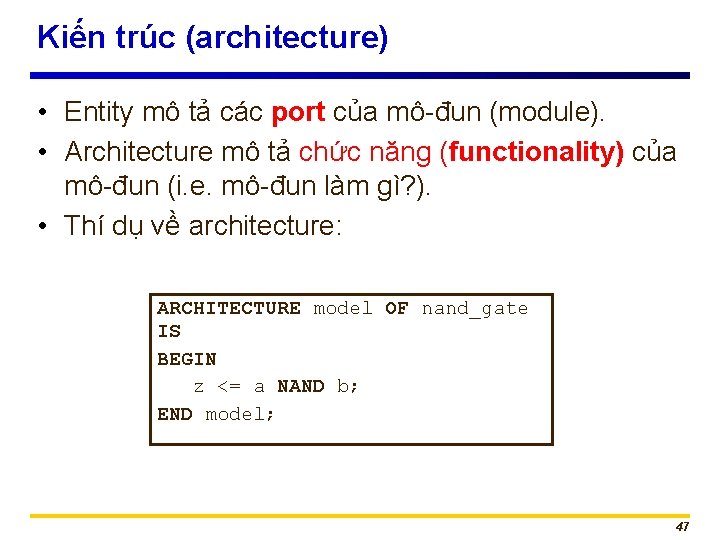

Kiến trúc (architecture) • Entity mô tả các port của mô-đun (module). • Architecture mô tả chức năng (functionality) của mô-đun (i. e. mô-đun làm gì? ). • Thí dụ về architecture: ARCHITECTURE model OF nand_gate IS BEGIN z <= a NAND b; END model; 47

![Architecture Cú pháp đơn giản ARCHITECTURE architecturename OF entityname IS declarations Architecture – Cú pháp đơn giản ARCHITECTURE architecture_name OF entity_name IS [ declarations ]](https://slidetodoc.com/presentation_image_h2/52fcc2caa59f083c135cbdd2659d6607/image-48.jpg)

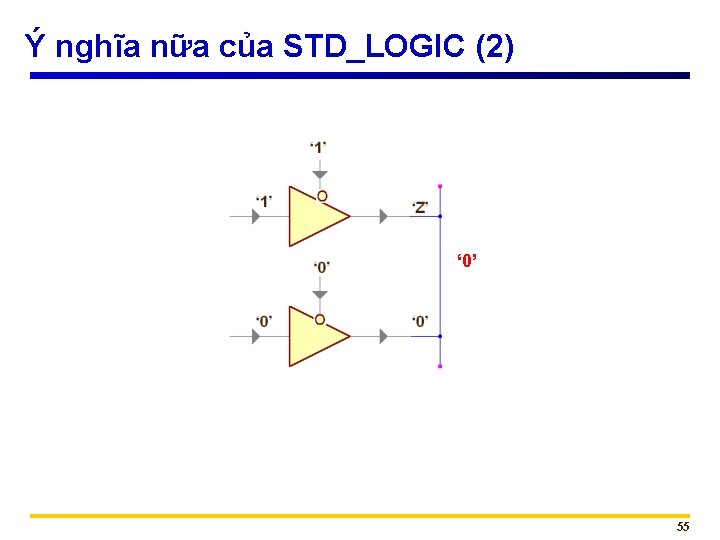

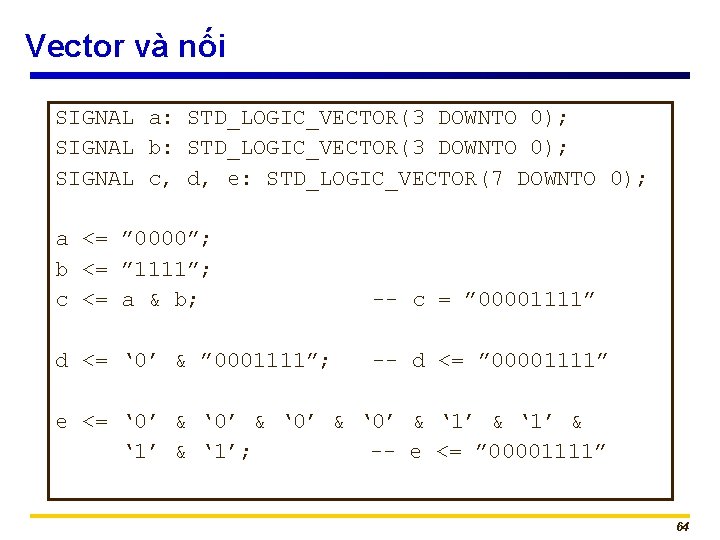

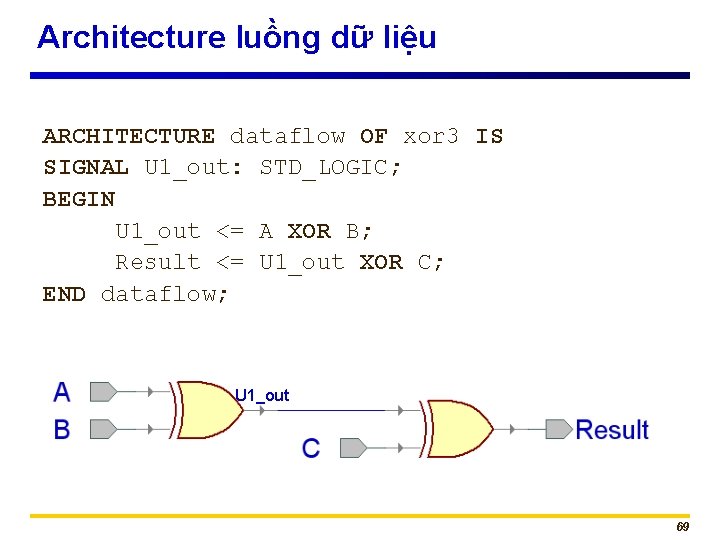

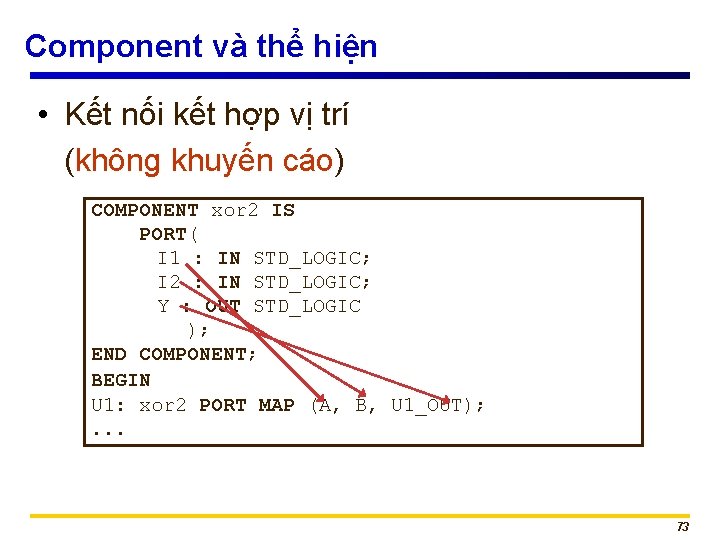

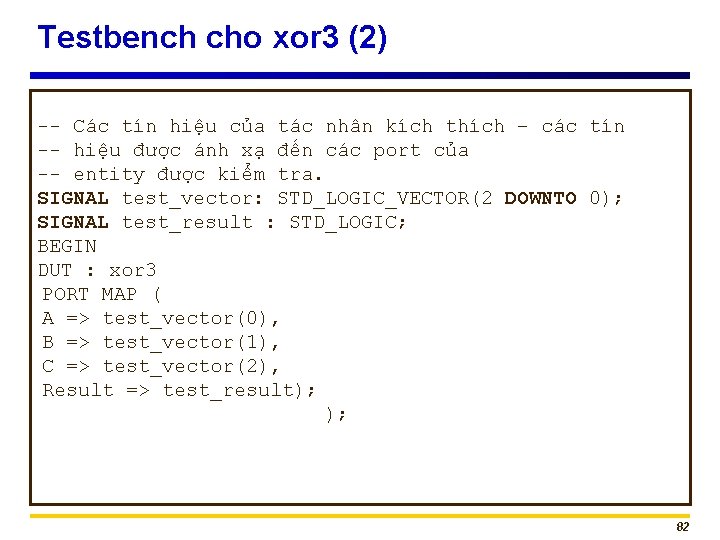

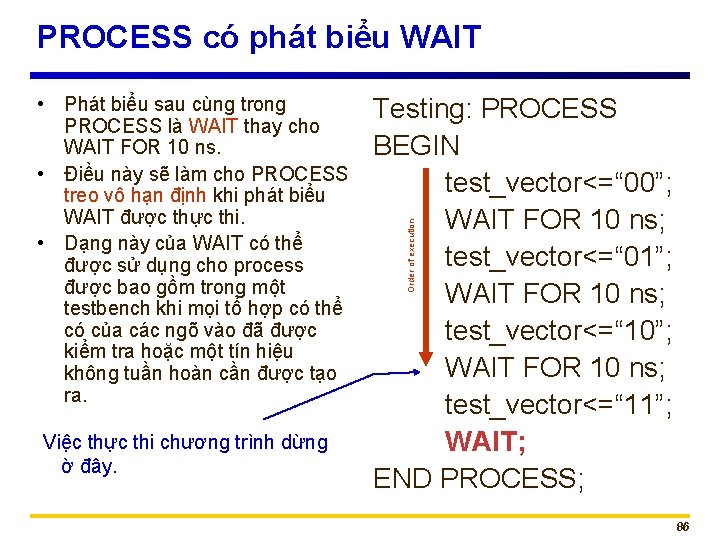

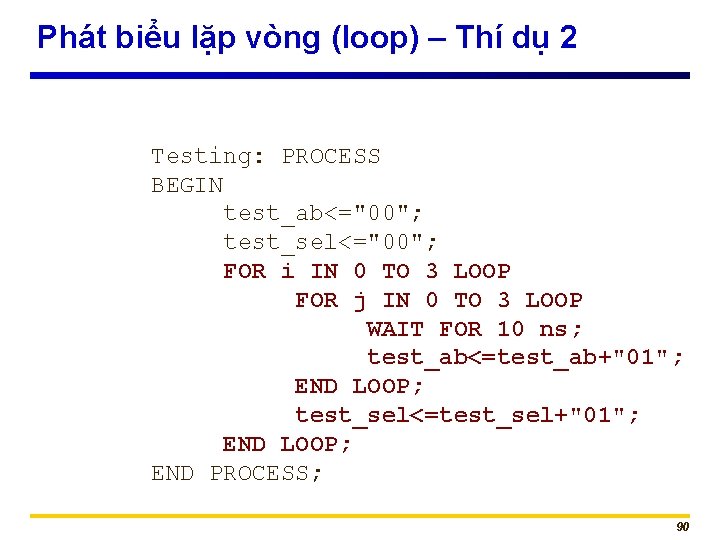

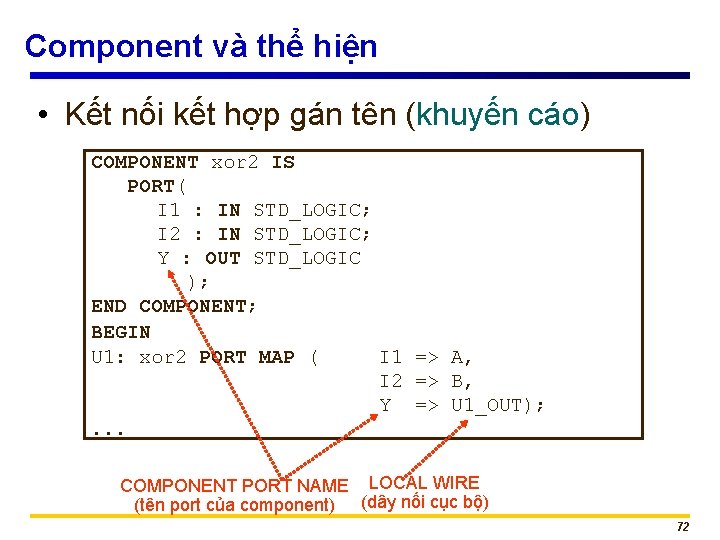

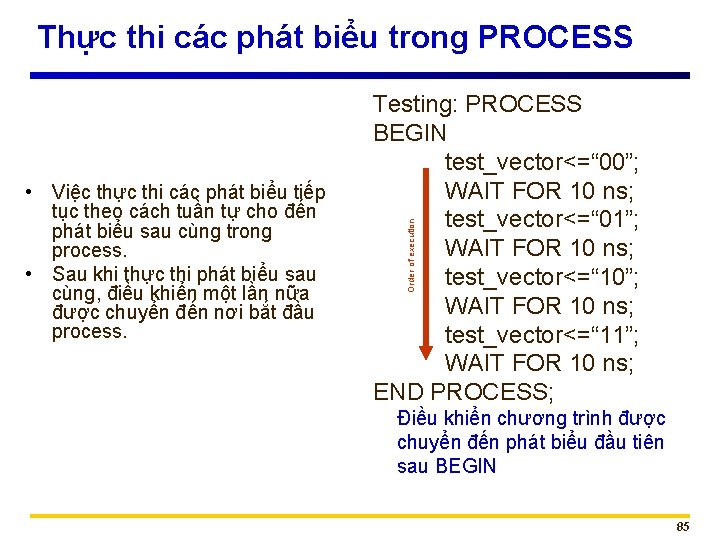

Architecture – Cú pháp đơn giản ARCHITECTURE architecture_name OF entity_name IS [ declarations ] BEGIN code END architecture_name; 48

Khai báo entity & architecture nand_gate. vhd LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY nand_gate IS PORT( a : IN STD_LOGIC; b : IN STD_LOGIC; z : OUT STD_LOGIC); END nand_gate; ARCHITECTURE model OF nand_gate IS BEGIN z <= a NAND b; END model; 49

STD_LOGIC 50

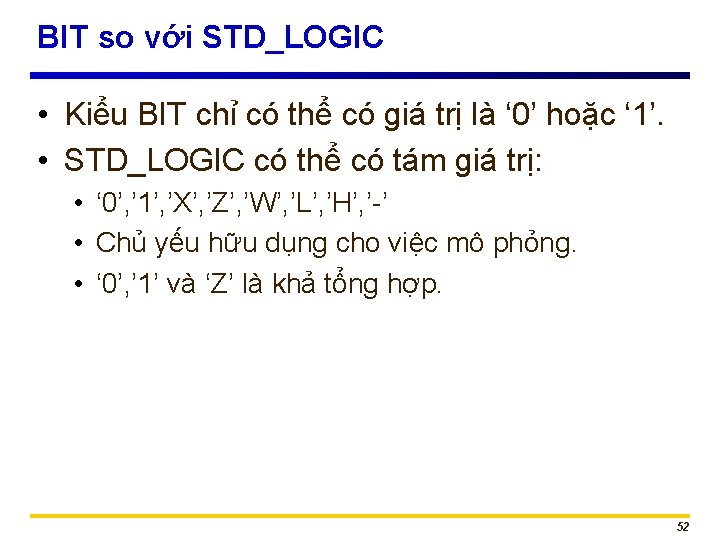

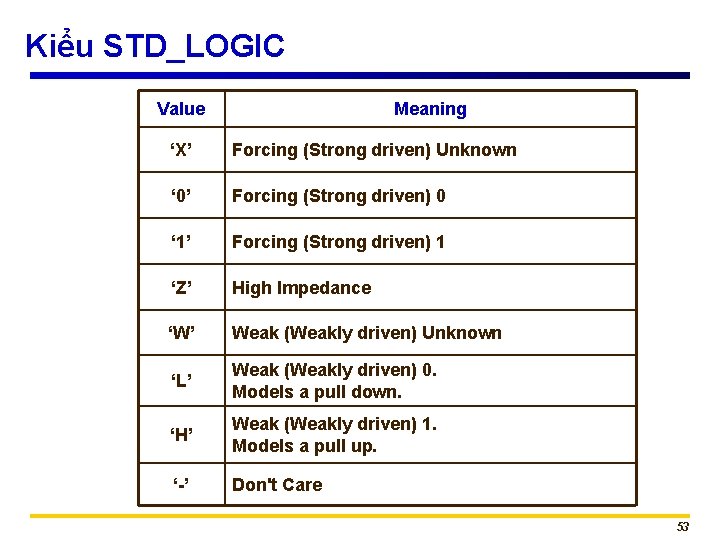

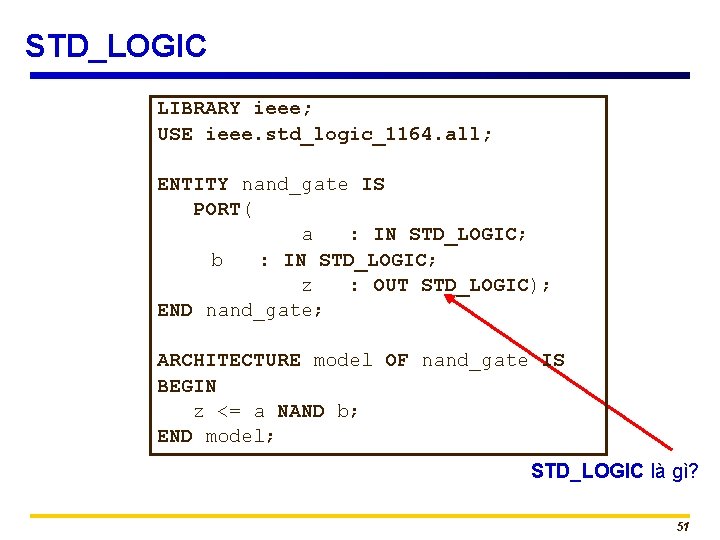

STD_LOGIC LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY nand_gate IS PORT( a : IN STD_LOGIC; b : IN STD_LOGIC; z : OUT STD_LOGIC); END nand_gate; ARCHITECTURE model OF nand_gate IS BEGIN z <= a NAND b; END model; STD_LOGIC là gì? 51

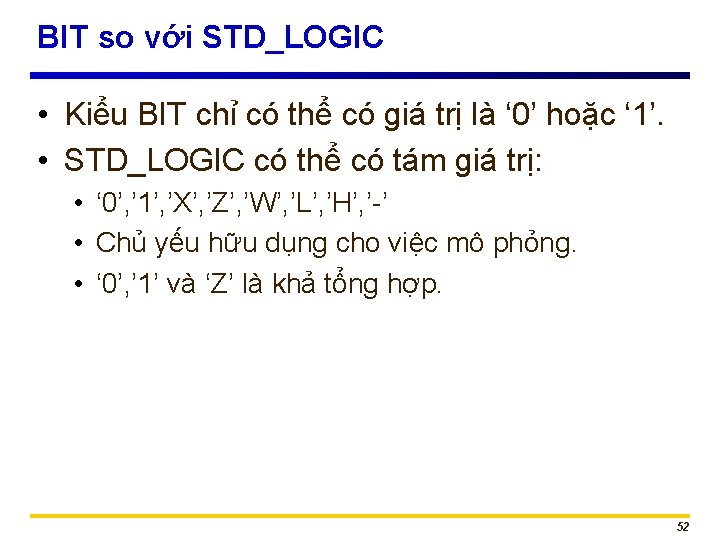

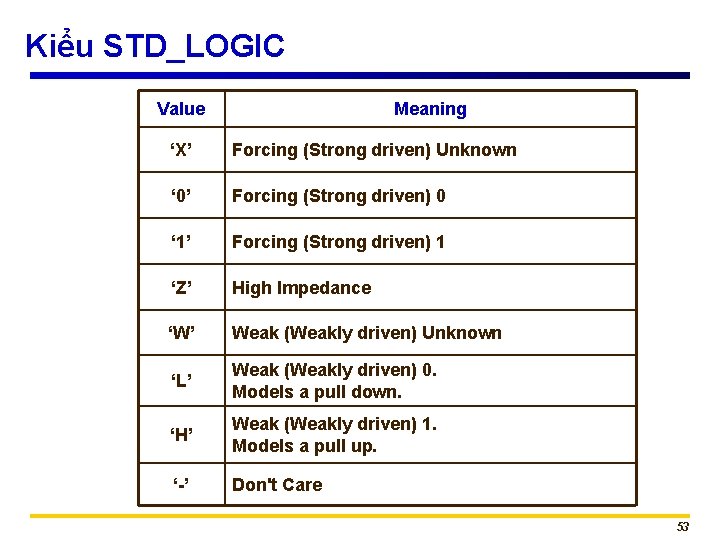

Kiểu STD_LOGIC Value Meaning ‘X’ Forcing (Strong driven) Unknown ‘ 0’ Forcing (Strong driven) 0 ‘ 1’ Forcing (Strong driven) 1 ‘Z’ High Impedance ‘W’ Weak (Weakly driven) Unknown ‘L’ Weak (Weakly driven) 0. Models a pull down. ‘H’ Weak (Weakly driven) 1. Models a pull up. ‘-’ Don't Care 53

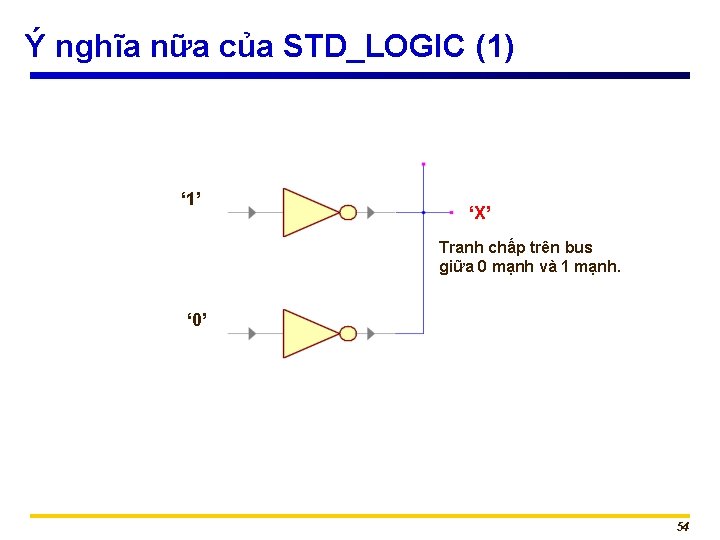

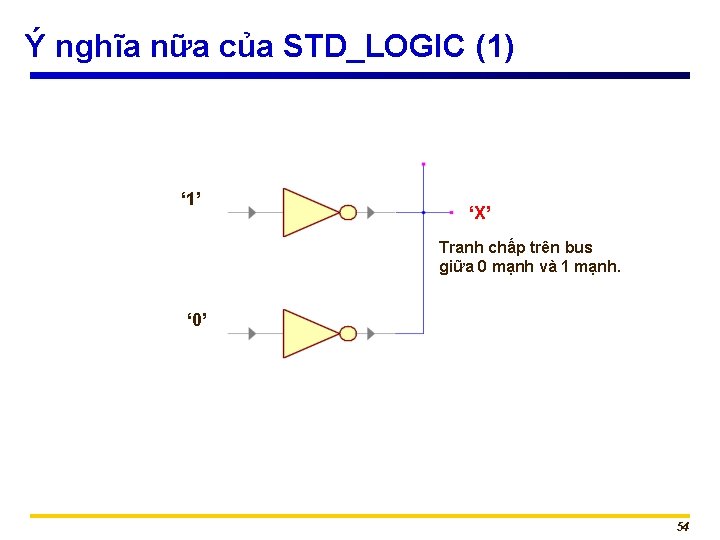

Ý nghĩa nữa của STD_LOGIC (1) ‘ 1’ ‘X’ Tranh chấp trên bus giữa 0 mạnh và 1 mạnh. ‘ 0’ 54

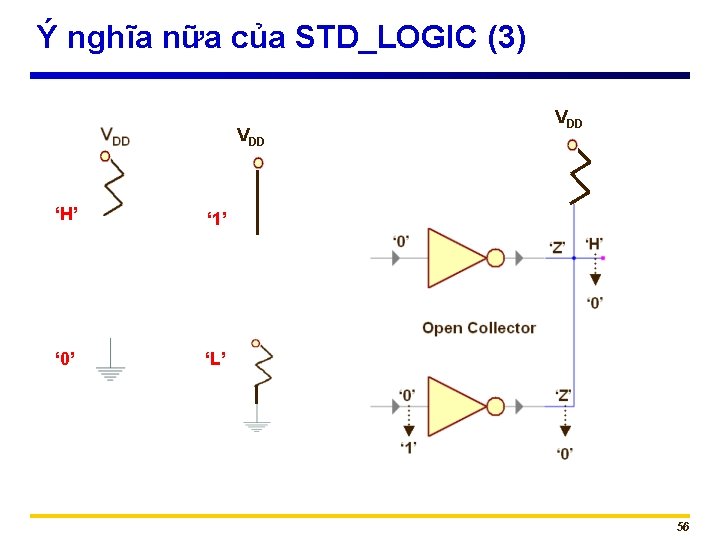

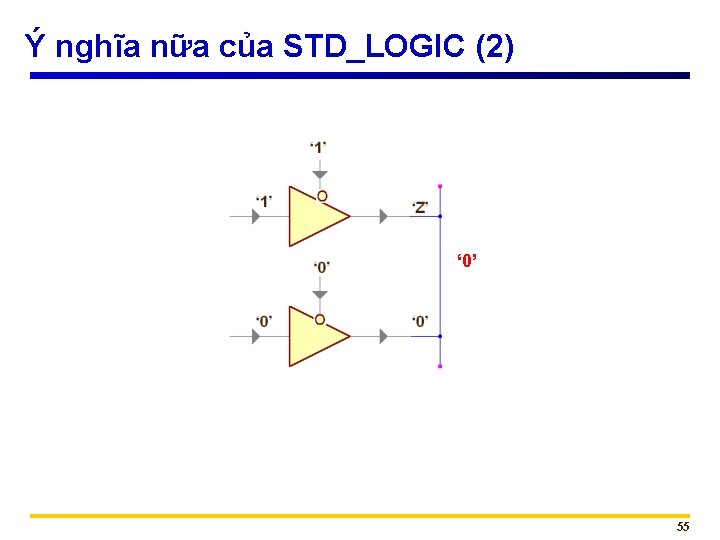

Ý nghĩa nữa của STD_LOGIC (2) ‘ 0’ 55

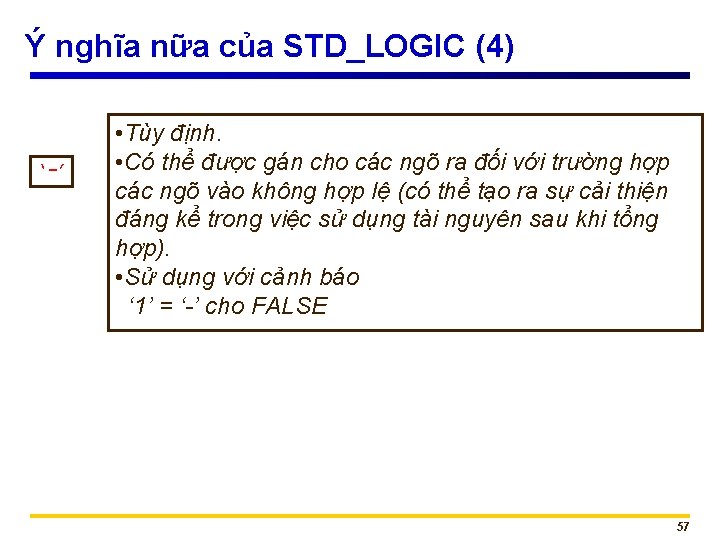

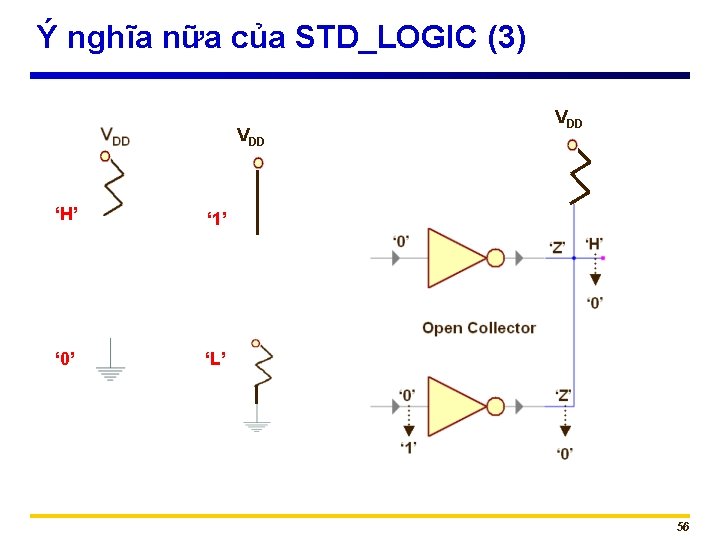

Ý nghĩa nữa của STD_LOGIC (3) VDD ‘H’ ‘ 1’ ‘ 0’ ‘L’ VDD 56

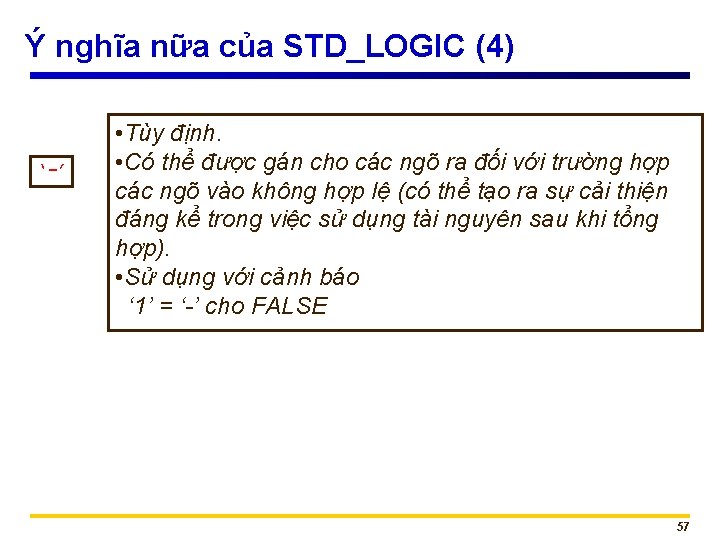

Ý nghĩa nữa của STD_LOGIC (4) ‘-’ • Tùy định. • Có thể được gán cho các ngõ ra đối với trường hợp các ngõ vào không hợp lệ (có thể tạo ra sự cải thiện đáng kể trong việc sử dụng tài nguyên sau khi tổng hợp). • Sử dụng với cảnh báo ‘ 1’ = ‘-’ cho FALSE 57

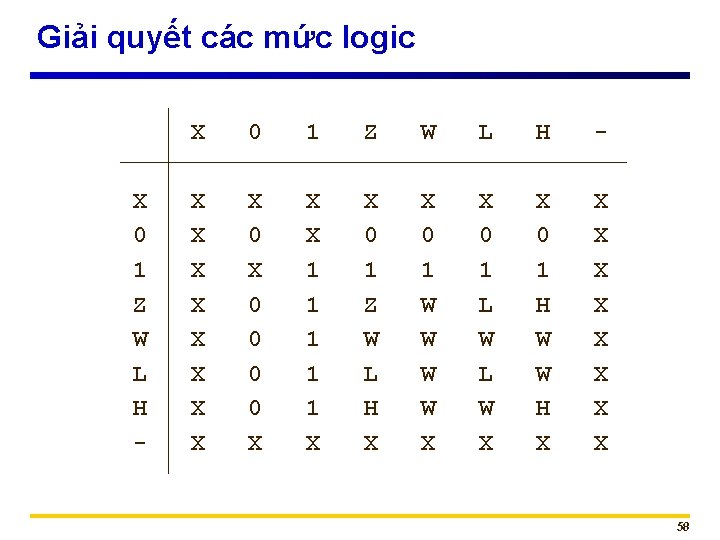

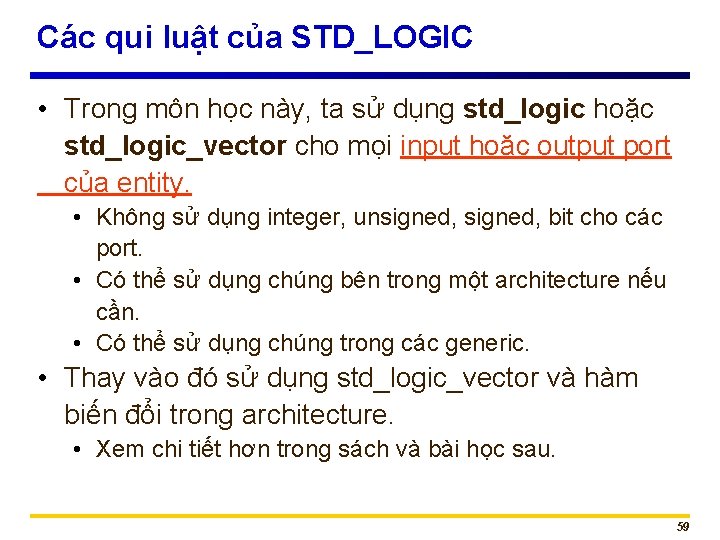

Giải quyết các mức logic X 0 1 Z W L H - X X X X X 0 0 0 0 X X X 1 1 1 X X 0 1 Z W L H X X 0 1 W W X X 0 1 L W X X 0 1 H W W H X X X X X 58

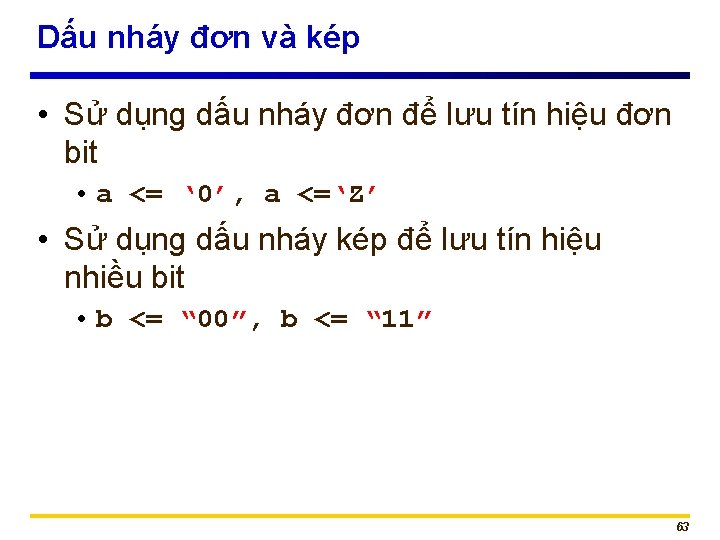

Các qui luật của STD_LOGIC • Trong môn học này, ta sử dụng std_logic hoặc std_logic_vector cho mọi input hoặc output port của entity. • Không sử dụng integer, unsigned, bit cho các port. • Có thể sử dụng chúng bên trong một architecture nếu cần. • Có thể sử dụng chúng trong các generic. • Thay vào đó sử dụng std_logic_vector và hàm biến đổi trong architecture. • Xem chi tiết hơn trong sách và bài học sau. 59

Mô hình dây nối và bus 60

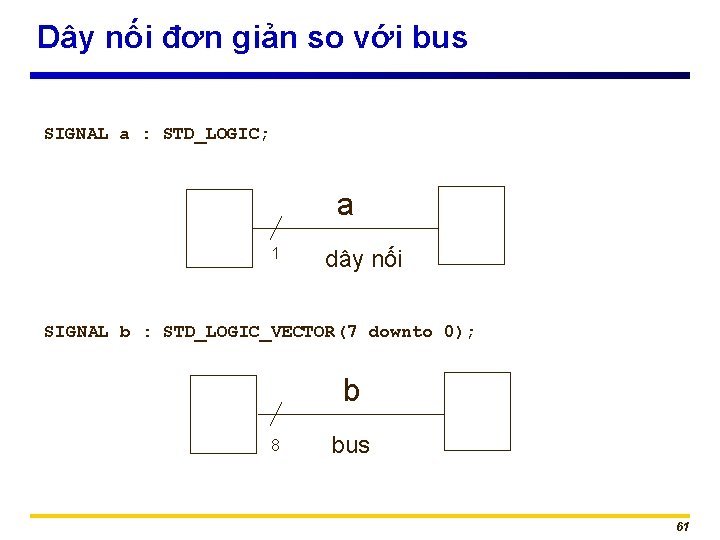

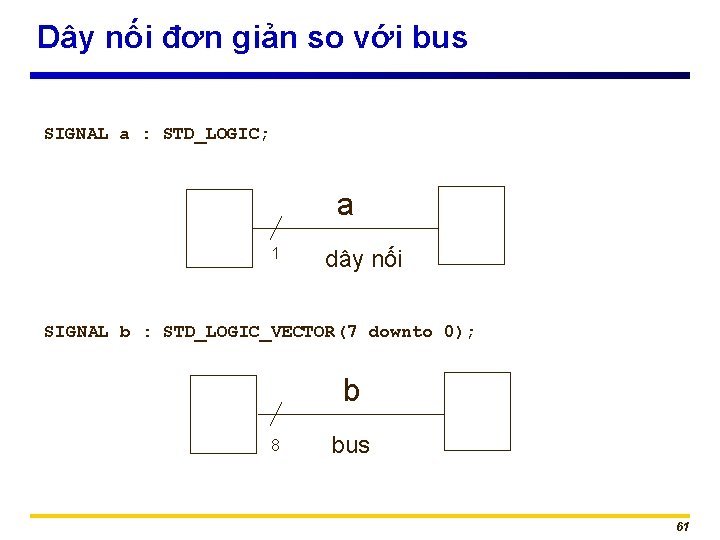

Dây nối đơn giản so với bus SIGNAL a : STD_LOGIC; a 1 dây nối SIGNAL b : STD_LOGIC_VECTOR(7 downto 0); b 8 bus 61

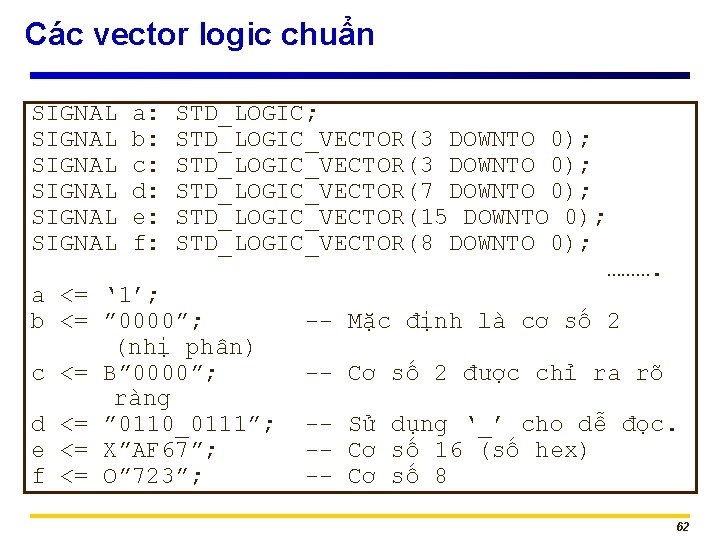

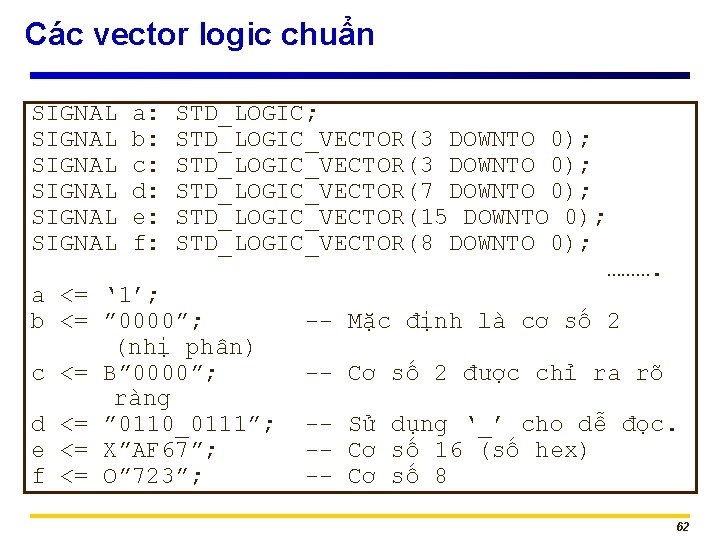

Các vector logic chuẩn SIGNAL SIGNAL a: b: c: d: e: f: STD_LOGIC; STD_LOGIC_VECTOR(3 DOWNTO 0); STD_LOGIC_VECTOR(7 DOWNTO 0); STD_LOGIC_VECTOR(15 DOWNTO 0); STD_LOGIC_VECTOR(8 DOWNTO 0); ………. a <= ‘ 1’; b <= ” 0000”; (nhị phân) c <= B” 0000”; ràng d <= ” 0110_0111”; e <= X”AF 67”; f <= O” 723”; -- Mặc định là cơ số 2 -- Cơ số 2 được chỉ ra rõ -- Sử dụng ‘_’ cho dễ đọc. -- Cơ số 16 (số hex) -- Cơ số 8 62

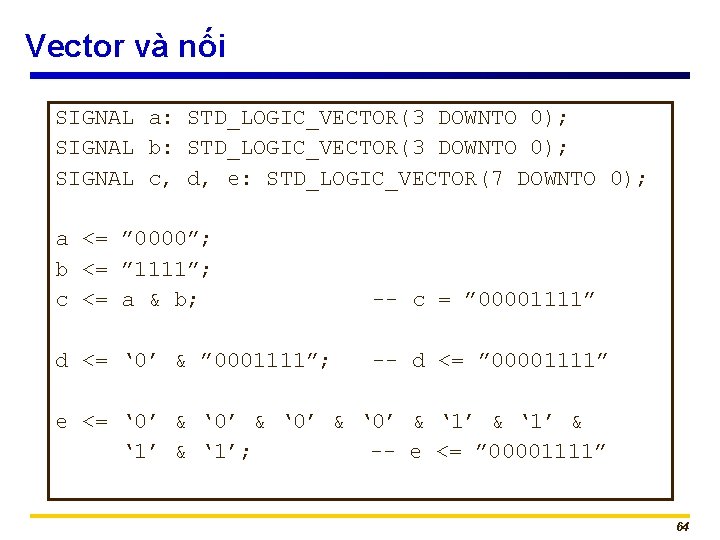

Vector và nối SIGNAL a: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL b: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL c, d, e: STD_LOGIC_VECTOR(7 DOWNTO 0); a <= ” 0000”; b <= ” 1111”; c <= a & b; -- c = ” 00001111” d <= ‘ 0’ & ” 0001111”; -- d <= ” 00001111” e <= ‘ 0’ & ‘ 1’ & ‘ 1’; -- e <= ” 00001111” 64

Các kiểu thiết kế của VHDL 65

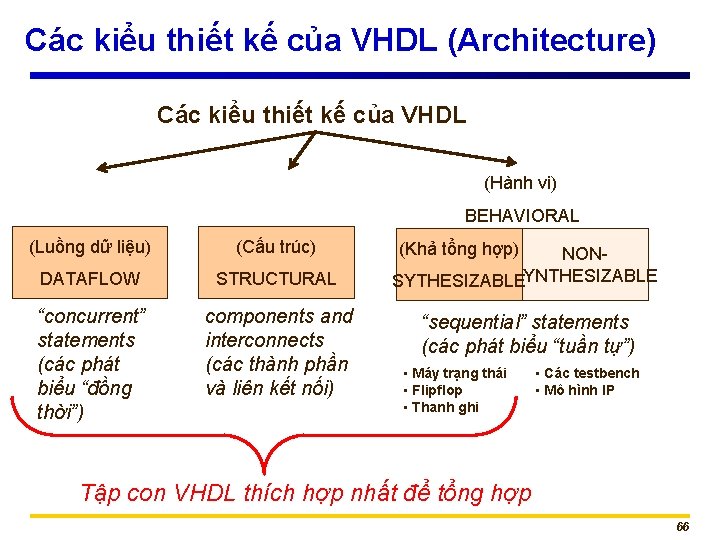

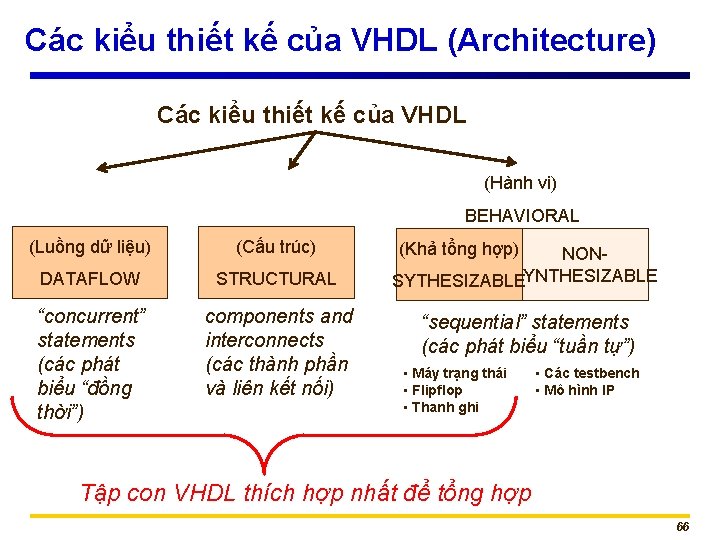

Các kiểu thiết kế của VHDL (Architecture) Các kiểu thiết kế của VHDL (Hành vi) BEHAVIORAL (Luồng dữ liệu) (Cấu trúc) DATAFLOW STRUCTURAL “concurrent” statements (các phát biểu “đồng thời”) components and interconnects (các thành phần và liên kết nối) (Khả tổng hợp) NONSYNTHESIZABLE SYTHESIZABLE “sequential” statements (các phát biểu “tuần tự”) • Máy trạng thái • Flipflop • Thanh ghi • Các testbench • Mô hình IP Tập con VHDL thích hợp nhất để tổng hợp 66

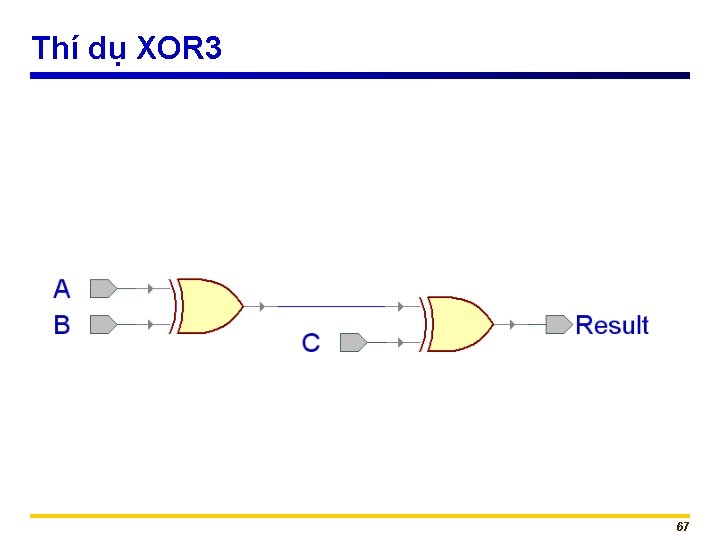

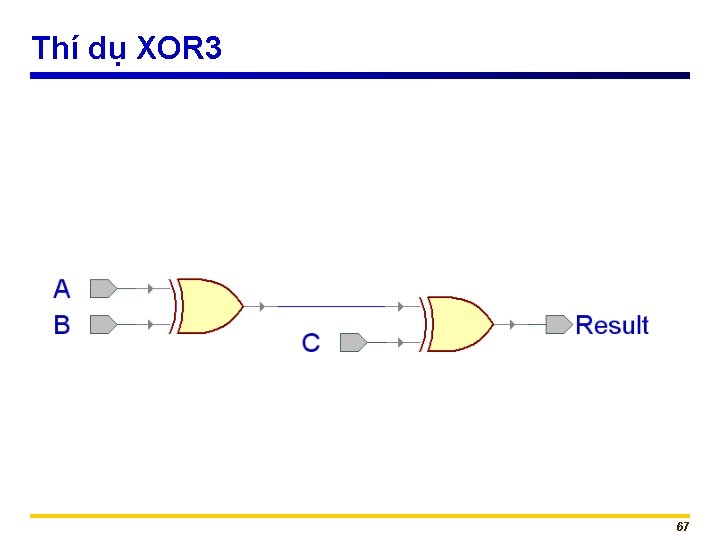

Thí dụ XOR 3 67

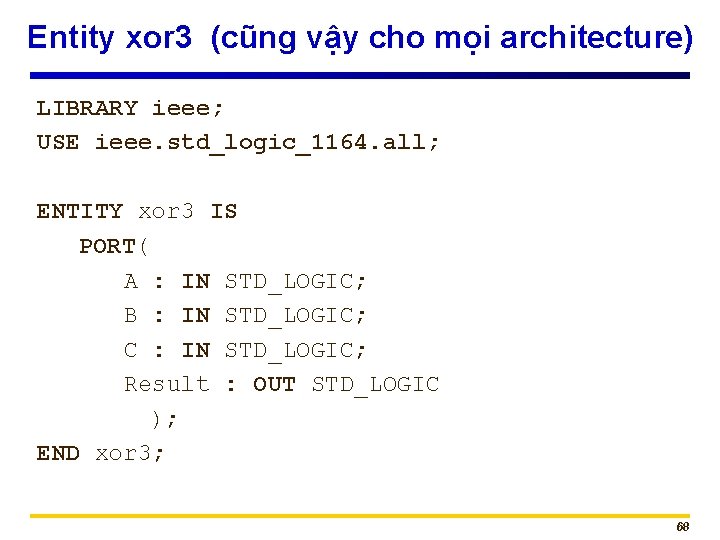

Entity xor 3 (cũng vậy cho mọi architecture) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY xor 3 IS PORT( A : IN STD_LOGIC; B : IN STD_LOGIC; C : IN STD_LOGIC; Result : OUT STD_LOGIC ); END xor 3; 68

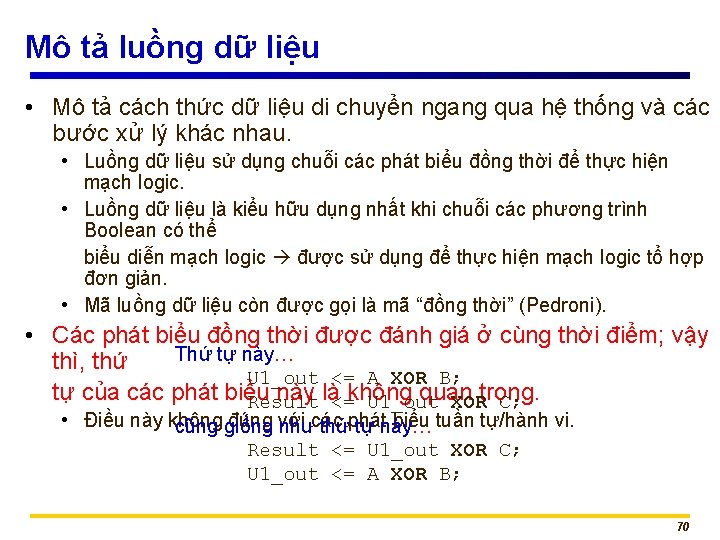

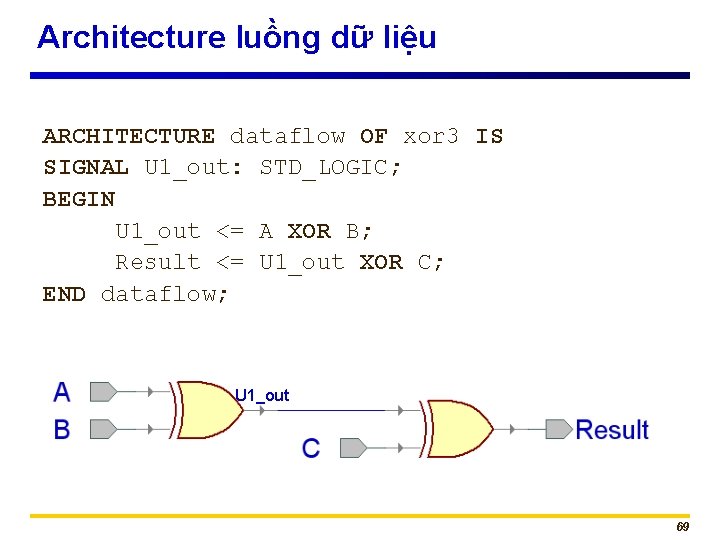

Architecture luồng dữ liệu ARCHITECTURE dataflow OF xor 3 IS SIGNAL U 1_out: STD_LOGIC; BEGIN U 1_out <= A XOR B; Result <= U 1_out XOR C; END dataflow; U 1_out 69

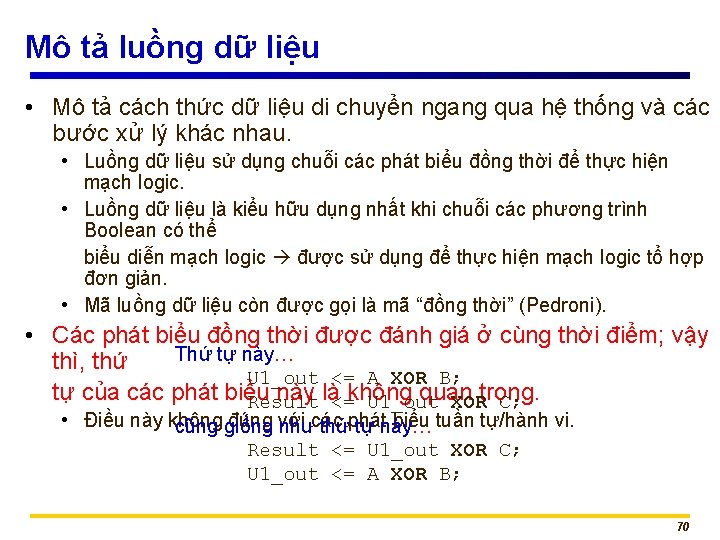

Mô tả luồng dữ liệu • Mô tả cách thức dữ liệu di chuyển ngang qua hệ thống và các bước xử lý khác nhau. • Luồng dữ liệu sử dụng chuỗi các phát biểu đồng thời để thực hiện mạch logic. • Luồng dữ liệu là kiểu hữu dụng nhất khi chuỗi các phương trình Boolean có thể biểu diễn mạch logic được sử dụng để thực hiện mạch logic tổ hợp đơn giản. • Mã luồng dữ liệu còn được gọi là mã “đồng thời” (Pedroni). • Các phát biểu đồng thời được đánh giá ở cùng thời điểm; vậy Thứ tự này… thì, thứ U 1_out <= A XOR B; tự của các phát biểu này là<=không quan Result U 1_out XORtrọng. C; • Điều này không đúng với biểu tuần tự/hành vi. cũng giống nhưcác thứphát tự này… Result <= U 1_out XOR C; U 1_out <= A XOR B; 70

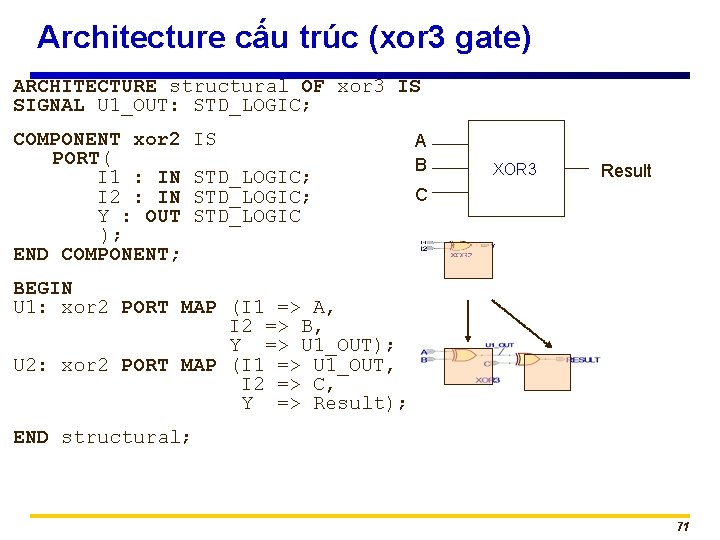

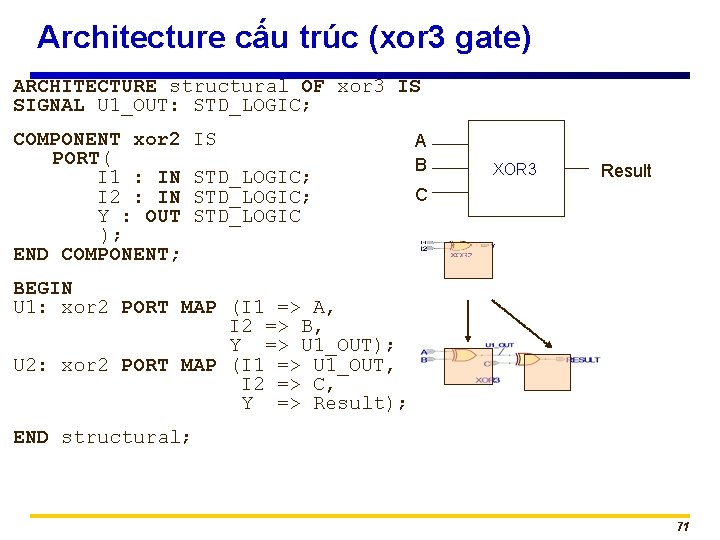

Architecture cấu trúc (xor 3 gate) ARCHITECTURE structural OF xor 3 IS SIGNAL U 1_OUT: STD_LOGIC; COMPONENT xor 2 PORT( I 1 : IN I 2 : IN Y : OUT ); END COMPONENT; IS STD_LOGIC; STD_LOGIC A B XOR 3 Result C BEGIN U 1: xor 2 PORT MAP (I 1 => A, I 2 => B, Y => U 1_OUT); U 2: xor 2 PORT MAP (I 1 => U 1_OUT, I 2 => C, Y => Result); END structural; 71

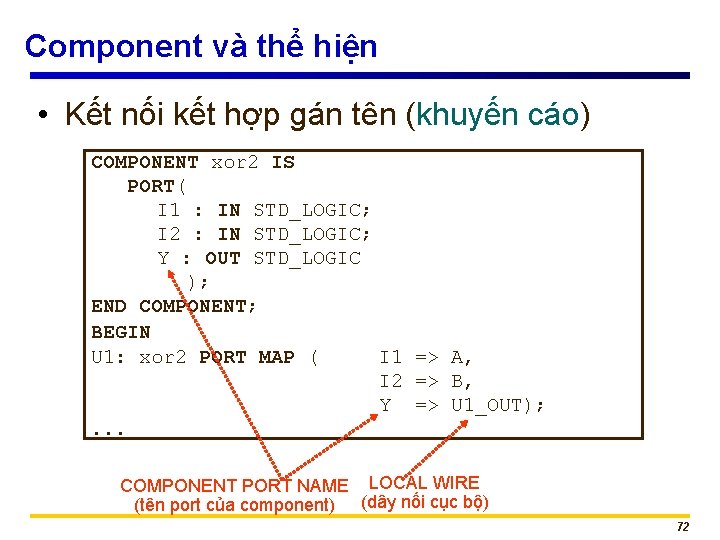

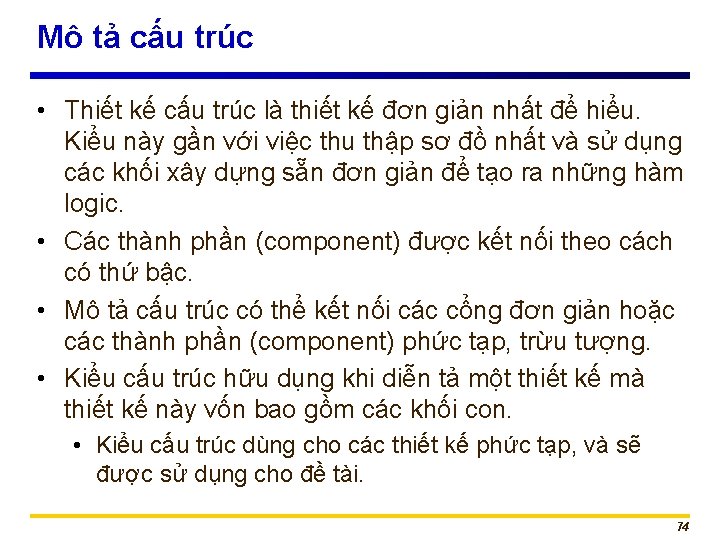

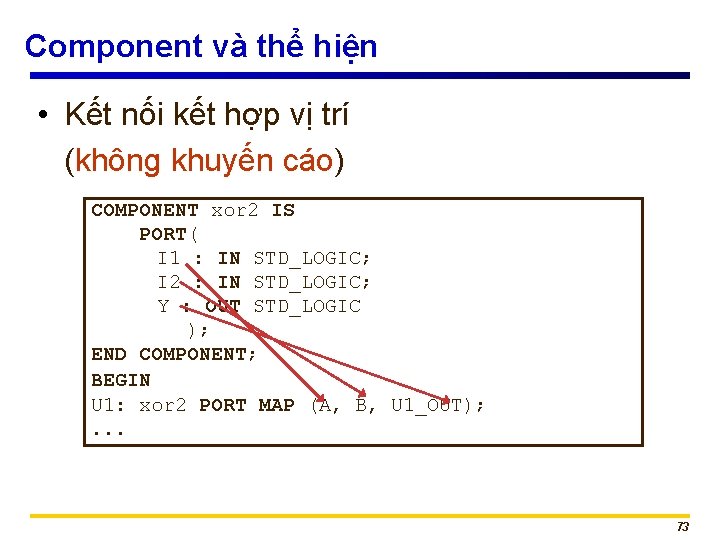

Component và thể hiện • Kết nối kết hợp gán tên (khuyến cáo) COMPONENT xor 2 IS PORT( I 1 : IN STD_LOGIC; I 2 : IN STD_LOGIC; Y : OUT STD_LOGIC ); END COMPONENT; BEGIN U 1: xor 2 PORT MAP ( I 1 => A, I 2 => B, Y => U 1_OUT); . . . COMPONENT PORT NAME LOCAL WIRE (tên port của component) (dây nối cục bộ) 72

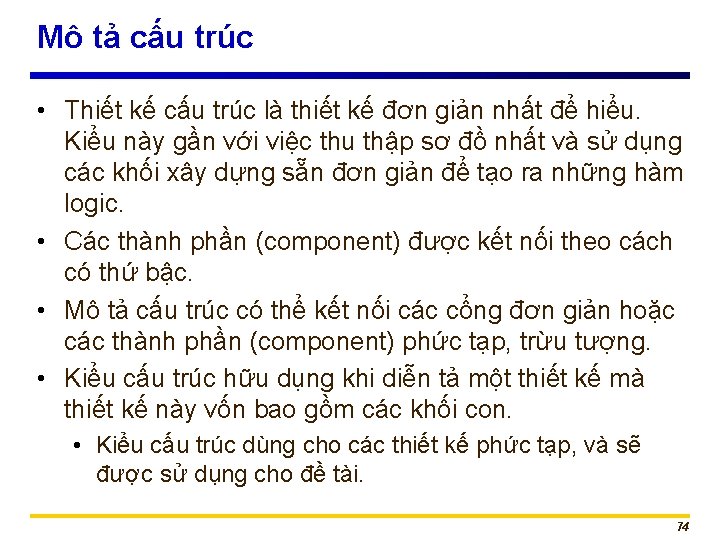

Component và thể hiện • Kết nối kết hợp vị trí (không khuyến cáo) COMPONENT xor 2 IS PORT( I 1 : IN STD_LOGIC; I 2 : IN STD_LOGIC; Y : OUT STD_LOGIC ); END COMPONENT; BEGIN U 1: xor 2 PORT MAP (A, B, U 1_OUT); . . . 73

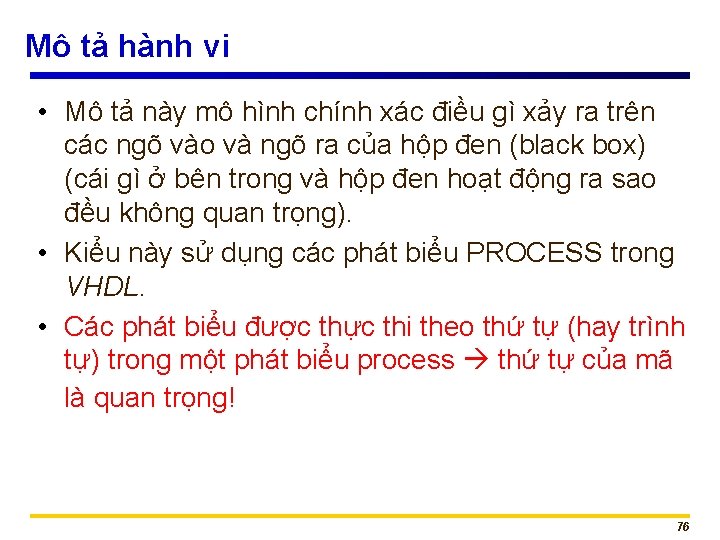

Mô tả cấu trúc • Thiết kế cấu trúc là thiết kế đơn giản nhất để hiểu. Kiểu này gần với việc thu thập sơ đồ nhất và sử dụng các khối xây dựng sẵn đơn giản để tạo ra những hàm logic. • Các thành phần (component) được kết nối theo cách có thứ bậc. • Mô tả cấu trúc có thể kết nối các cổng đơn giản hoặc các thành phần (component) phức tạp, trừu tượng. • Kiểu cấu trúc hữu dụng khi diễn tả một thiết kế mà thiết kế này vốn bao gồm các khối con. • Kiểu cấu trúc dùng cho các thiết kế phức tạp, và sẽ được sử dụng cho đề tài. 74

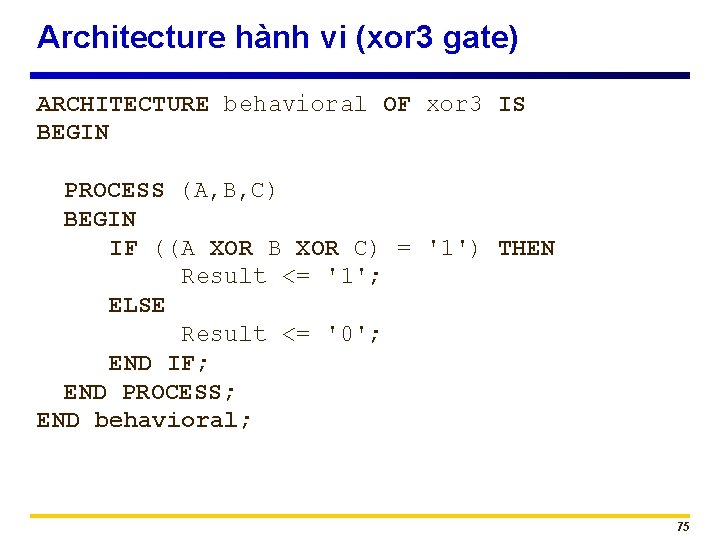

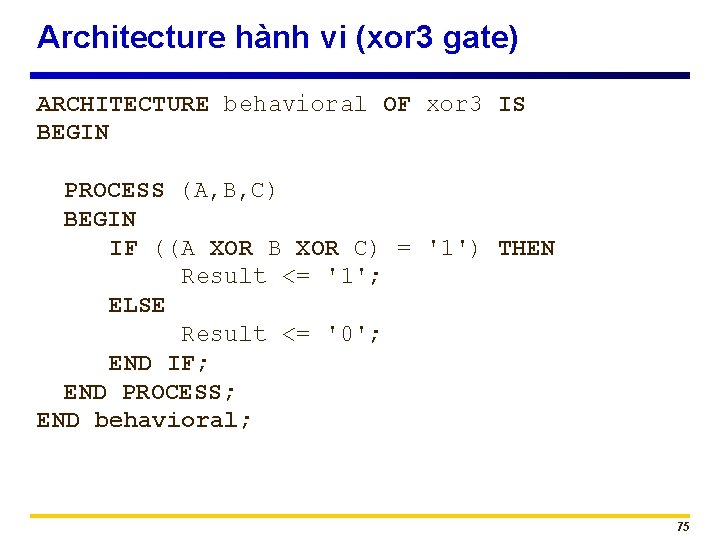

Architecture hành vi (xor 3 gate) ARCHITECTURE behavioral OF xor 3 IS BEGIN PROCESS (A, B, C) BEGIN IF ((A XOR B XOR C) = '1') THEN Result <= '1'; ELSE Result <= '0'; END IF; END PROCESS; END behavioral; 75

Mô tả hành vi • Mô tả này mô hình chính xác điều gì xảy ra trên các ngõ vào và ngõ ra của hộp đen (black box) (cái gì ở bên trong và hộp đen hoạt động ra sao đều không quan trọng). • Kiểu này sử dụng các phát biểu PROCESS trong VHDL. • Các phát biểu được thực thi theo thứ tự (hay trình tự) trong một phát biểu process thứ tự của mã là quan trọng! 76

Các testbench 77

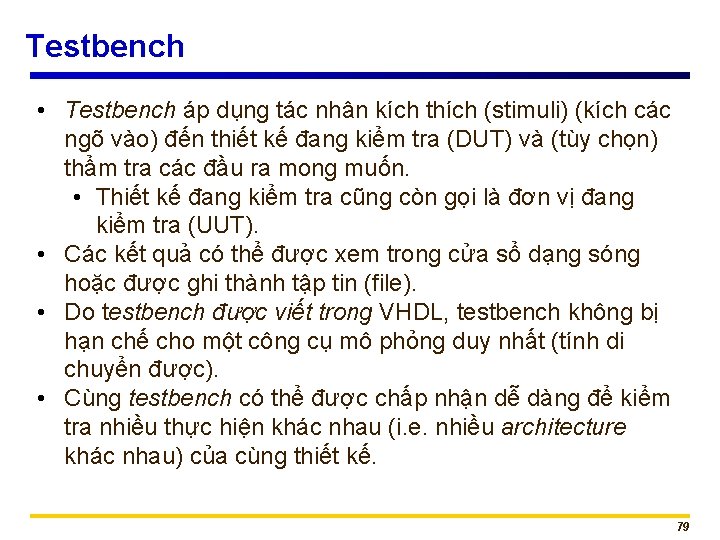

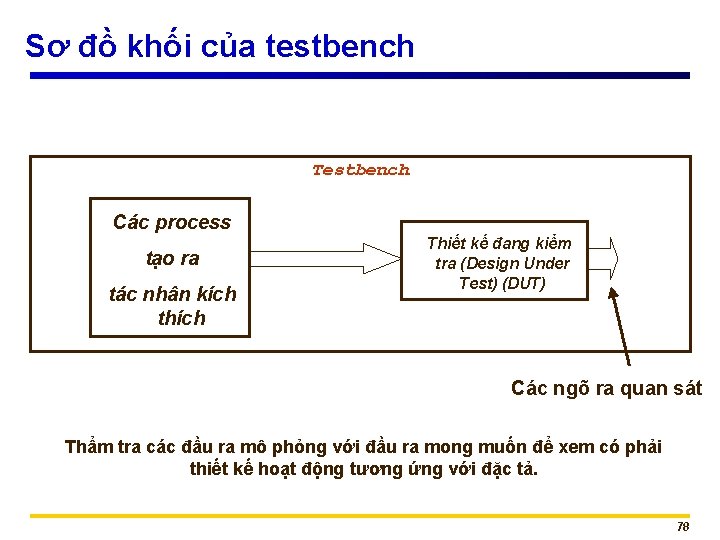

Sơ đồ khối của testbench Testbench Các process tạo ra tác nhân kích thích Thiết kế đang kiểm tra (Design Under Test) (DUT) Các ngõ ra quan sát Thẩm tra các đầu ra mô phỏng với đầu ra mong muốn để xem có phải thiết kế hoạt động tương ứng với đặc tả. 78

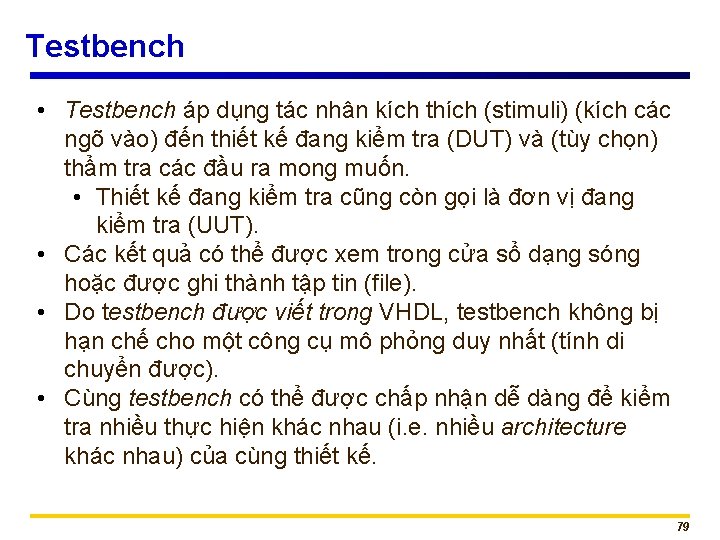

Testbench • Testbench áp dụng tác nhân kích thích (stimuli) (kích các ngõ vào) đến thiết kế đang kiểm tra (DUT) và (tùy chọn) thẩm tra các đầu ra mong muốn. • Thiết kế đang kiểm tra cũng còn gọi là đơn vị đang kiểm tra (UUT). • Các kết quả có thể được xem trong cửa sổ dạng sóng hoặc được ghi thành tập tin (file). • Do testbench được viết trong VHDL, testbench không bị hạn chế cho một công cụ mô phỏng duy nhất (tính di chuyển được). • Cùng testbench có thể được chấp nhận dễ dàng để kiểm tra nhiều thực hiện khác nhau (i. e. nhiều architecture khác nhau) của cùng thiết kế. 79

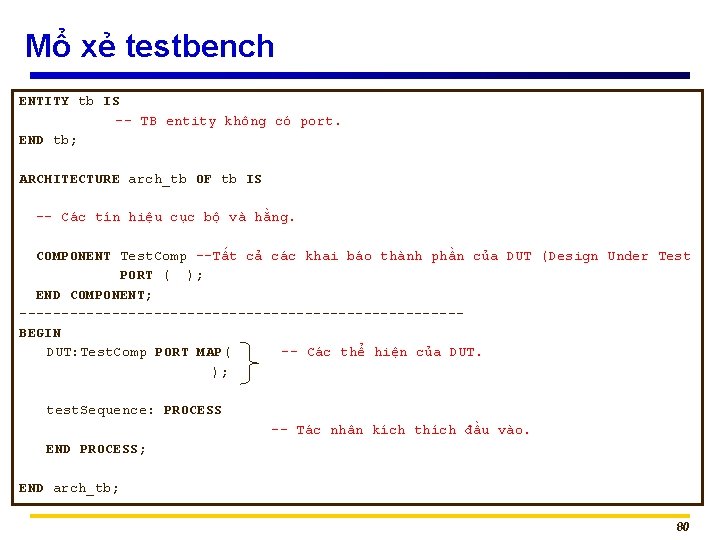

Mổ xẻ testbench ENTITY tb IS -- TB entity không có port. END tb; ARCHITECTURE arch_tb OF tb IS -- Các tín hiệu cục bộ và hằng. COMPONENT Test. Comp –-Tất cả các khai báo thành phần của DUT (Design Under Test PORT ( ); END COMPONENT; --------------------------BEGIN DUT: Test. Comp PORT MAP( -- Các thể hiện của DUT. ); test. Sequence: PROCESS -- Tác nhân kích thích đầu vào. END PROCESS; END arch_tb; 80

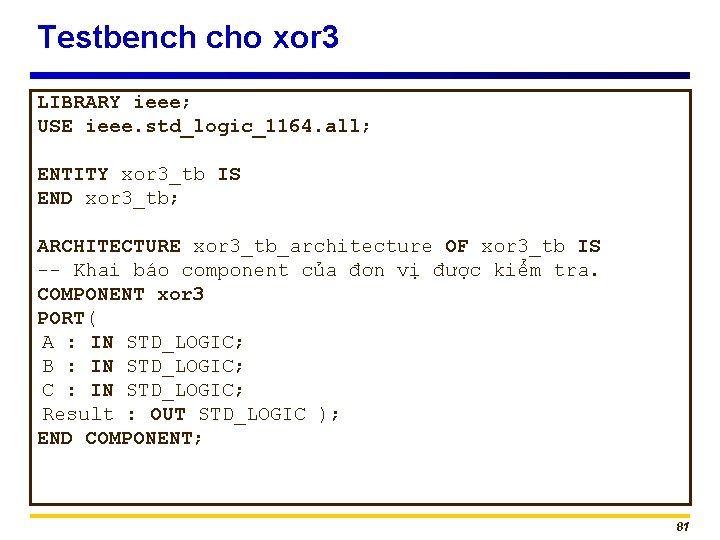

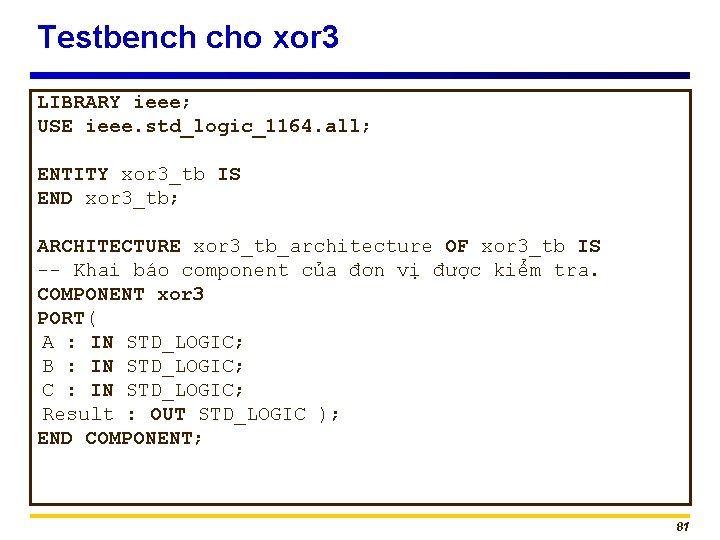

Testbench cho xor 3 LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY xor 3_tb IS END xor 3_tb; ARCHITECTURE xor 3_tb_architecture OF xor 3_tb IS -- Khai báo component của đơn vị được kiểm tra. COMPONENT xor 3 PORT( A : IN STD_LOGIC; B : IN STD_LOGIC; C : IN STD_LOGIC; Result : OUT STD_LOGIC ); END COMPONENT; 81

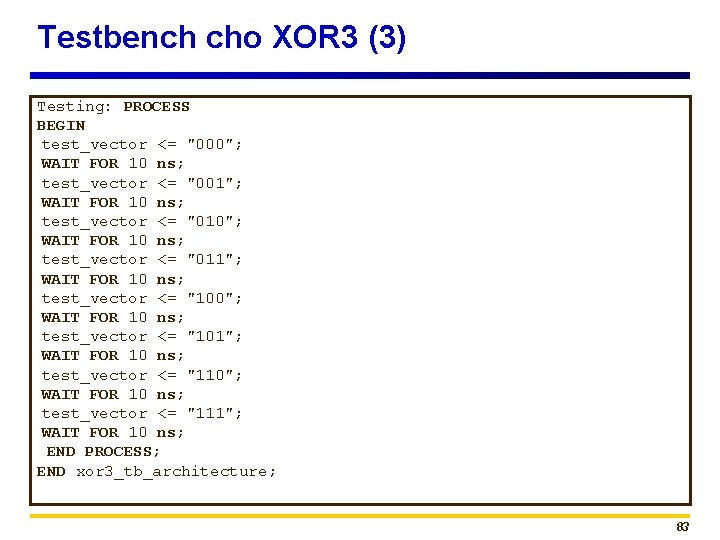

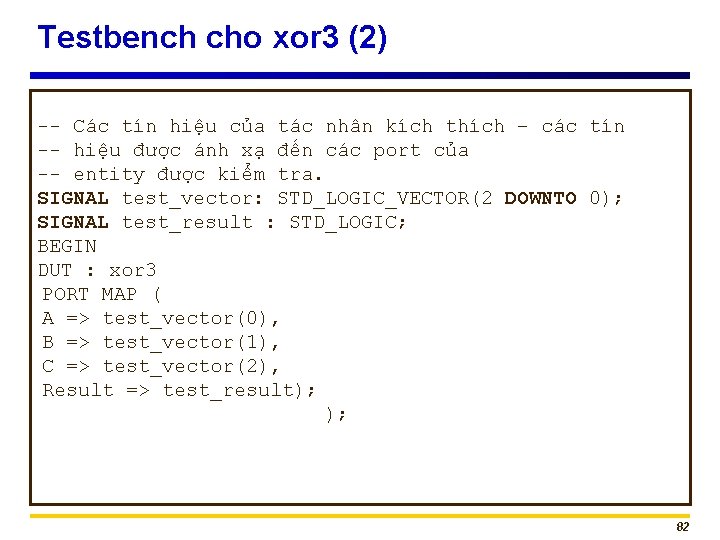

Testbench cho xor 3 (2) -- Các tín hiệu của tác nhân kích thích – các tín -- hiệu được ánh xạ đến các port của -- entity được kiểm tra. SIGNAL test_vector: STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL test_result : STD_LOGIC; BEGIN DUT : xor 3 PORT MAP ( A => test_vector(0), B => test_vector(1), C => test_vector(2), Result => test_result); ); 82

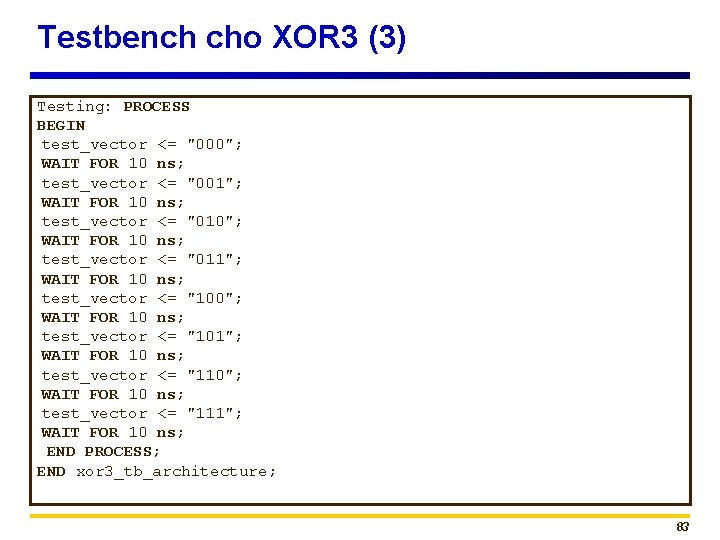

Testbench cho XOR 3 (3) Testing: PROCESS BEGIN test_vector <= "000"; WAIT FOR 10 ns; test_vector <= "001"; WAIT FOR 10 ns; test_vector <= "010"; WAIT FOR 10 ns; test_vector <= "011"; WAIT FOR 10 ns; test_vector <= "100"; WAIT FOR 10 ns; test_vector <= "101"; WAIT FOR 10 ns; test_vector <= "110"; WAIT FOR 10 ns; test_vector <= "111"; WAIT FOR 10 ns; END PROCESS; END xor 3_tb_architecture; 83

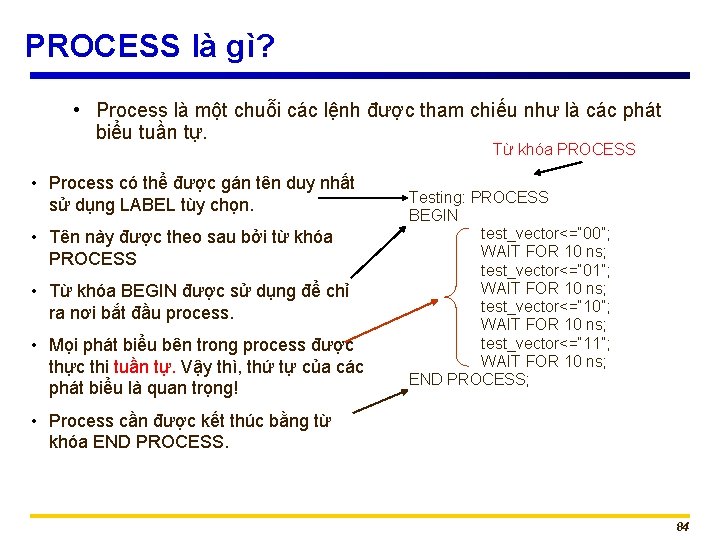

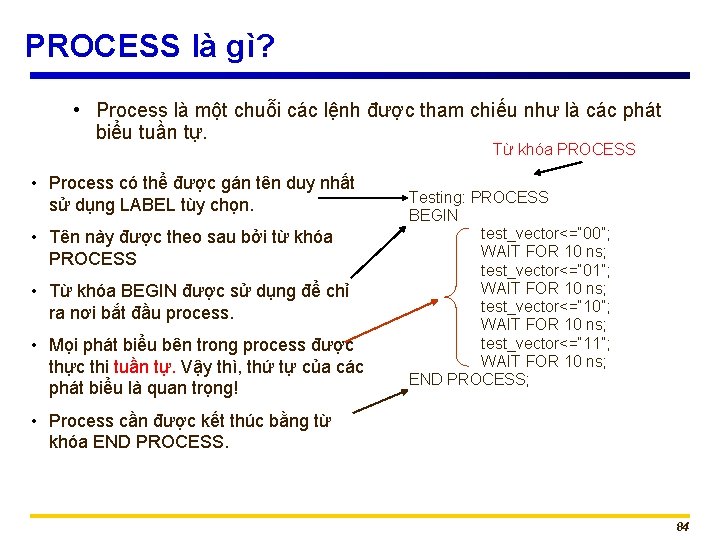

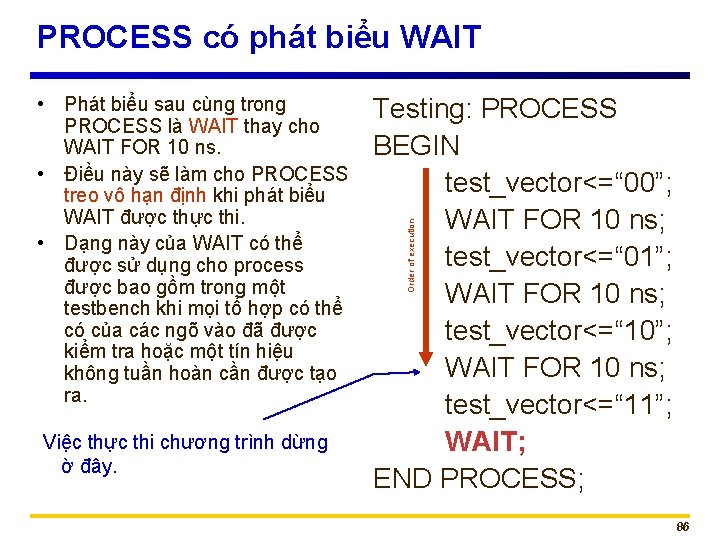

PROCESS là gì? • Process là một chuỗi các lệnh được tham chiếu như là các phát biểu tuần tự. Từ khóa PROCESS • Process có thể được gán tên duy nhất sử dụng LABEL tùy chọn. • Tên này được theo sau bởi từ khóa PROCESS • Từ khóa BEGIN được sử dụng để chỉ ra nơi bắt đầu process. • Mọi phát biểu bên trong process được thực thi tuần tự. Vậy thì, thứ tự của các phát biểu là quan trọng! Testing: PROCESS BEGIN test_vector<=“ 00”; WAIT FOR 10 ns; test_vector<=“ 01”; WAIT FOR 10 ns; test_vector<=“ 10”; WAIT FOR 10 ns; test_vector<=“ 11”; WAIT FOR 10 ns; END PROCESS; • Process cần được kết thúc bằng từ khóa END PROCESS. 84

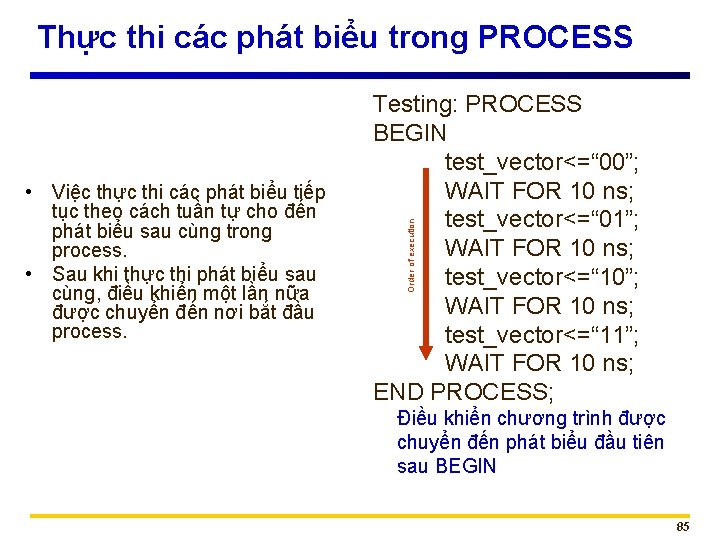

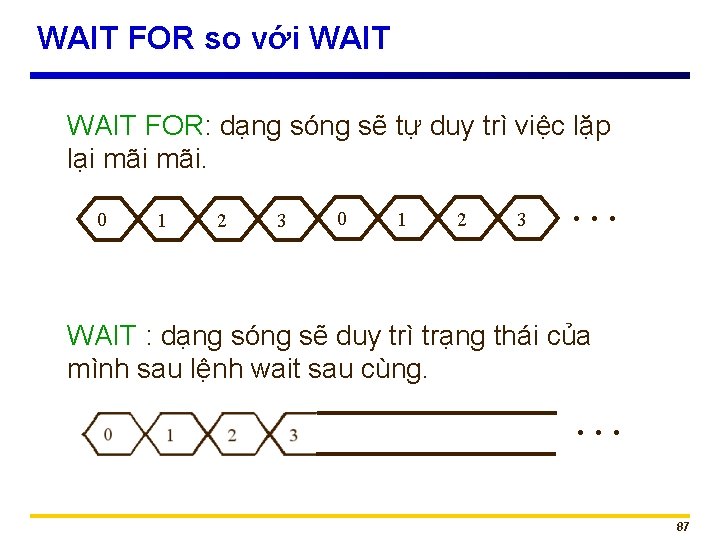

Thực thi các phát biểu trong PROCESS Order of execution • Việc thực thi các phát biểu tiếp tục theo cách tuần tự cho đến phát biểu sau cùng trong process. • Sau khi thực thi phát biểu sau cùng, điều khiển một lần nữa được chuyển đến nơi bắt đầu process. Testing: PROCESS BEGIN test_vector<=“ 00”; WAIT FOR 10 ns; test_vector<=“ 01”; WAIT FOR 10 ns; test_vector<=“ 10”; WAIT FOR 10 ns; test_vector<=“ 11”; WAIT FOR 10 ns; END PROCESS; Điều khiển chương trình được chuyển đến phát biểu đầu tiên sau BEGIN 85

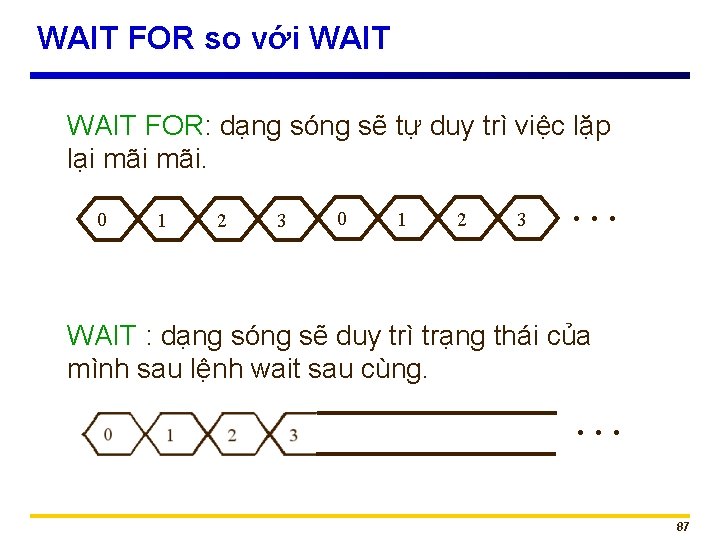

PROCESS có phát biểu WAIT Việc thực thi chương trình dừng ờ đây. Testing: PROCESS BEGIN test_vector<=“ 00”; WAIT FOR 10 ns; test_vector<=“ 01”; WAIT FOR 10 ns; test_vector<=“ 10”; WAIT FOR 10 ns; test_vector<=“ 11”; WAIT; END PROCESS; Order of execution • Phát biểu sau cùng trong PROCESS là WAIT thay cho WAIT FOR 10 ns. • Điều này sẽ làm cho PROCESS treo vô hạn định khi phát biểu WAIT được thực thi. • Dạng này của WAIT có thể được sử dụng cho process được bao gồm trong một testbench khi mọi tổ hợp có thể có của các ngõ vào đã được kiểm tra hoặc một tín hiệu không tuần hoàn cần được tạo ra. 86

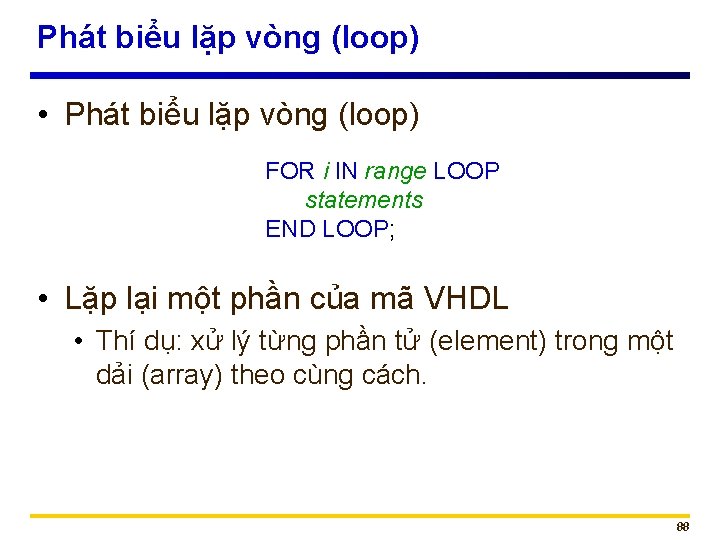

WAIT FOR so với WAIT FOR: dạng sóng sẽ tự duy trì việc lặp lại mãi. 0 1 2 3 … WAIT : dạng sóng sẽ duy trì trạng thái của mình sau lệnh wait sau cùng. … 87

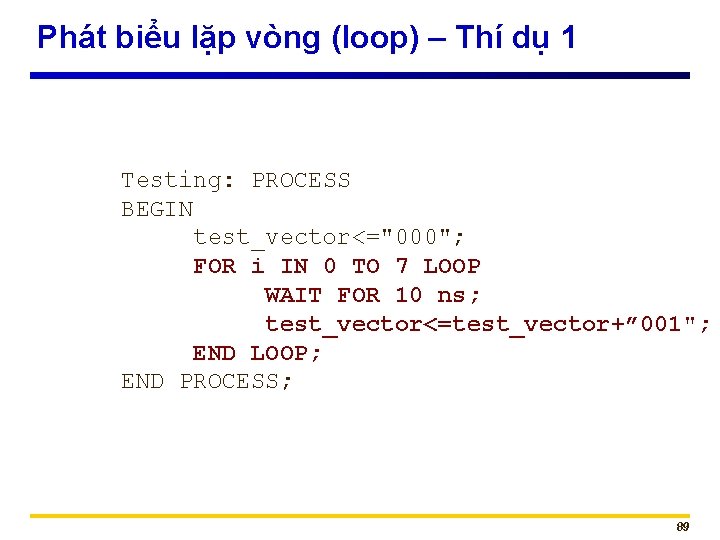

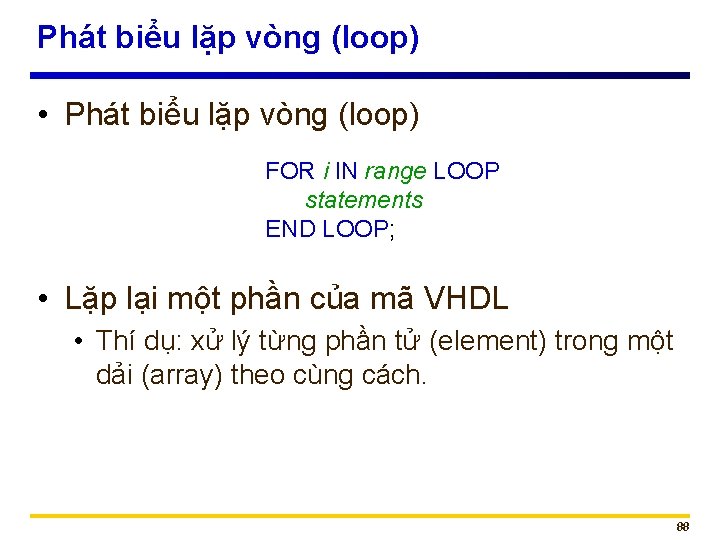

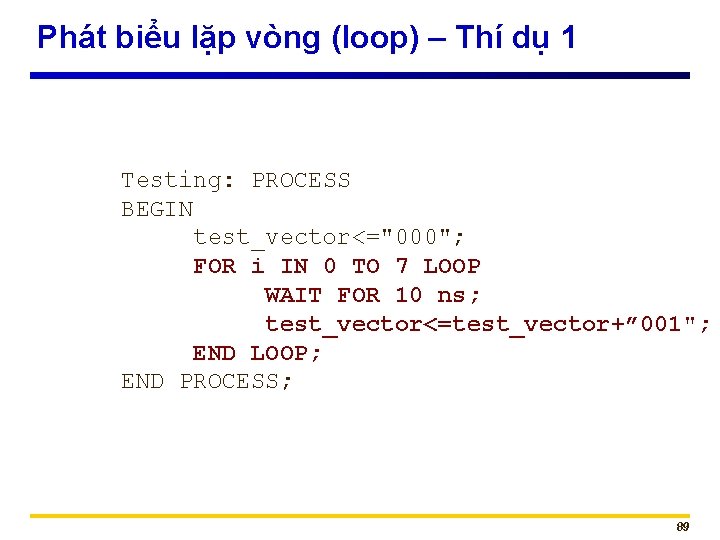

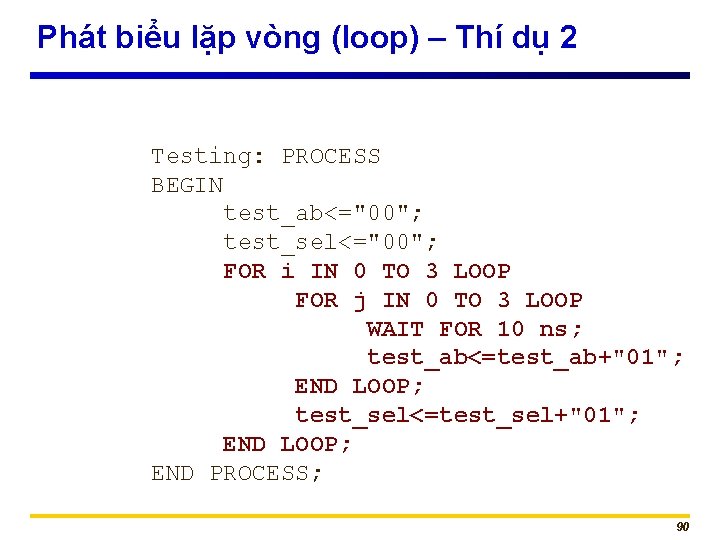

Phát biểu lặp vòng (loop) • Phát biểu lặp vòng (loop) FOR i IN range LOOP statements END LOOP; • Lặp lại một phần của mã VHDL • Thí dụ: xử lý từng phần tử (element) trong một dải (array) theo cùng cách. 88

Phát biểu lặp vòng (loop) – Thí dụ 1 Testing: PROCESS BEGIN test_vector<="000"; FOR i IN 0 TO 7 LOOP WAIT FOR 10 ns; test_vector<=test_vector+” 001"; END LOOP; END PROCESS; 89

Phát biểu lặp vòng (loop) – Thí dụ 2 Testing: PROCESS BEGIN test_ab<="00"; test_sel<="00"; FOR i IN 0 TO 3 LOOP FOR j IN 0 TO 3 LOOP WAIT FOR 10 ns; test_ab<=test_ab+"01"; END LOOP; test_sel<=test_sel+"01"; END LOOP; END PROCESS; 90