Diseo de Lgica Sincrnica Secuencial Circuito Lgico Secuencial

- Slides: 50

Diseño de Lógica Sincrónica Secuencial

Circuito Lógico Secuencial Es aquel en el que cuya(s) salida(s) dependen no solo de la entradas actuales, sino también de la secuencia pasada de sus entradas ICTP FPGA-VHDL 2

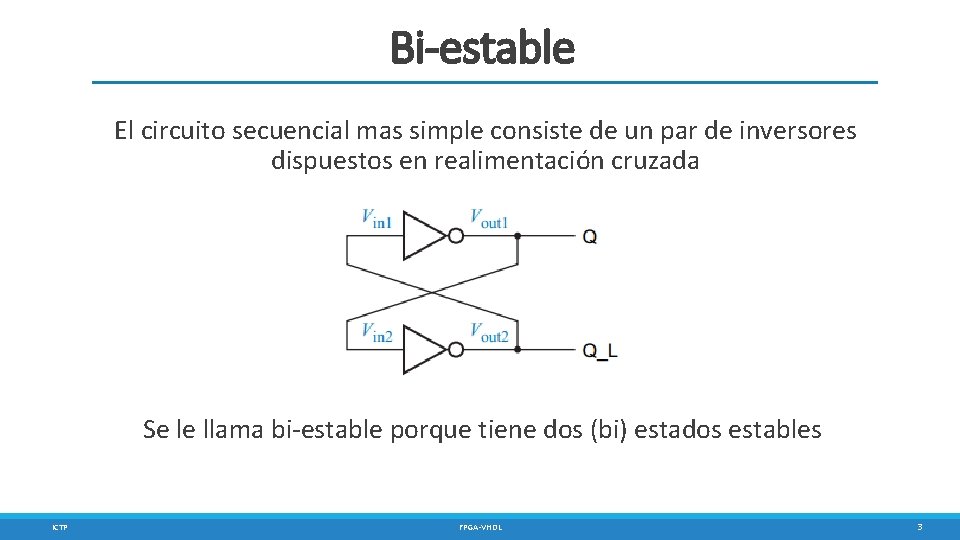

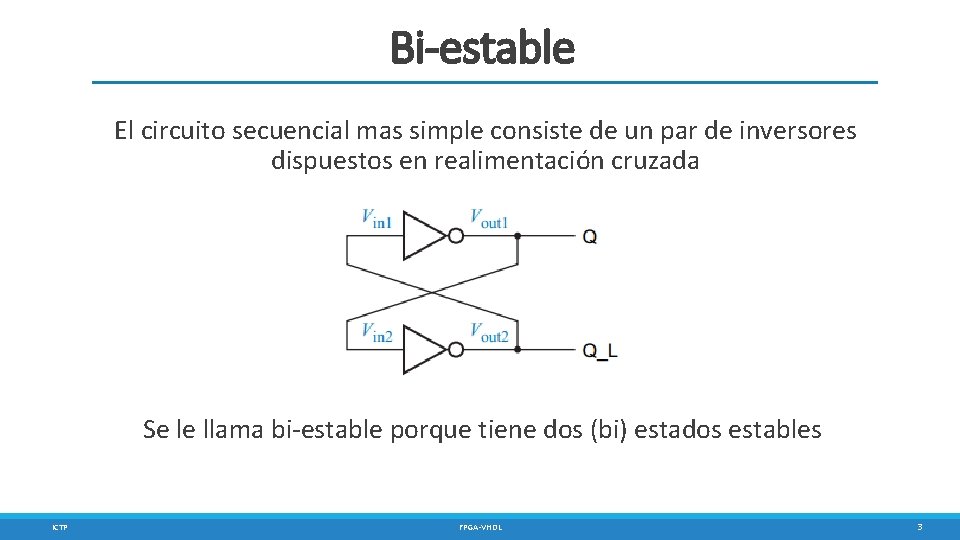

Bi-estable El circuito secuencial mas simple consiste de un par de inversores dispuestos en realimentación cruzada Se le llama bi-estable porque tiene dos (bi) estados estables ICTP FPGA-VHDL 3

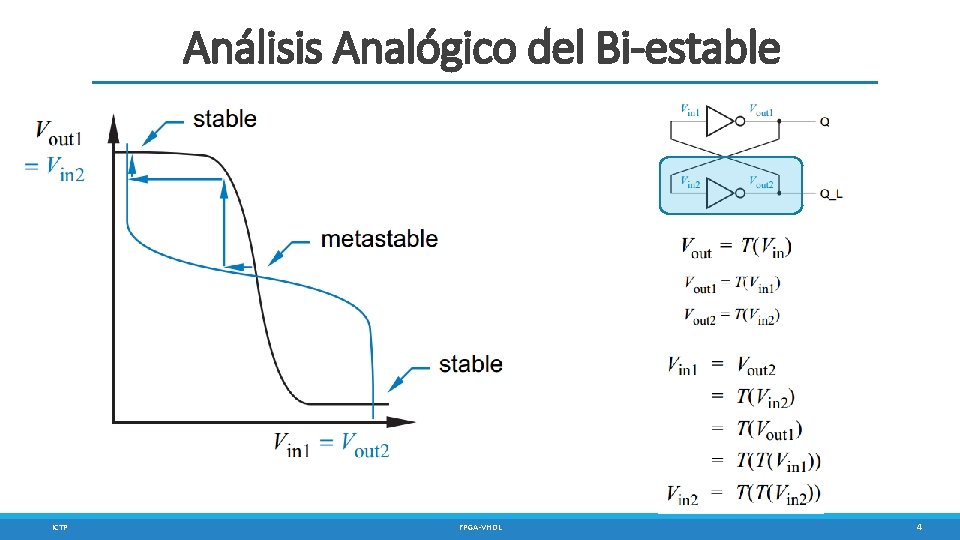

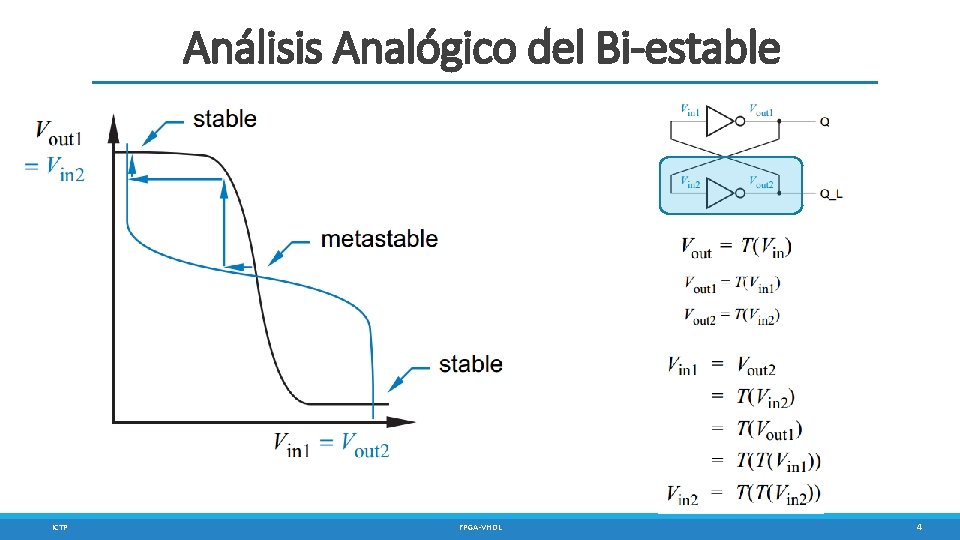

Análisis Analógico del Bi-estable ICTP FPGA-VHDL 4

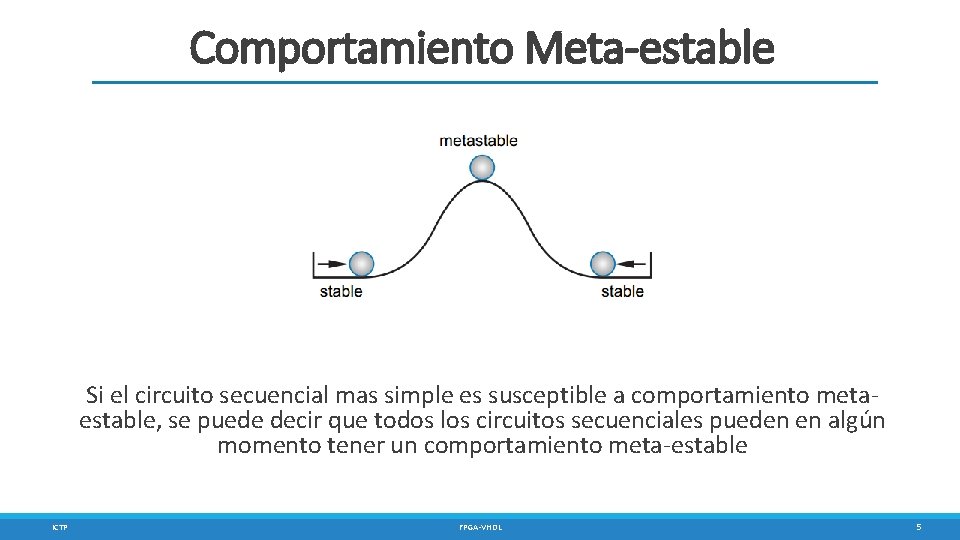

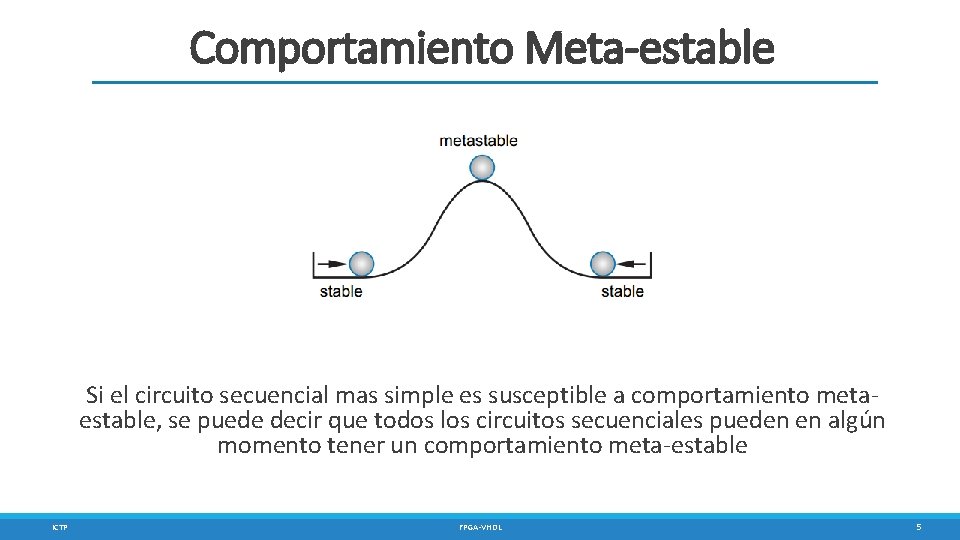

Comportamiento Meta-estable Si el circuito secuencial mas simple es susceptible a comportamiento metaestable, se puede decir que todos los circuitos secuenciales pueden en algún momento tener un comportamiento meta-estable ICTP FPGA-VHDL 5

Latches y Flip-Flops son los bloques básicos para el diseño y construcción de circuitos secuenciales Un Flip-Flop es un dispositivo secuencial que muestrea sus entradas y cambia sus salidas solamente en tiempos determinados por una señal de reloj Un Latch es un dispositivo secuencial que mira a sus entradas de forma continua y cuya salida cambia en cualquier momento, independiente de la señal de reloj ICTP FPGA-VHDL 6

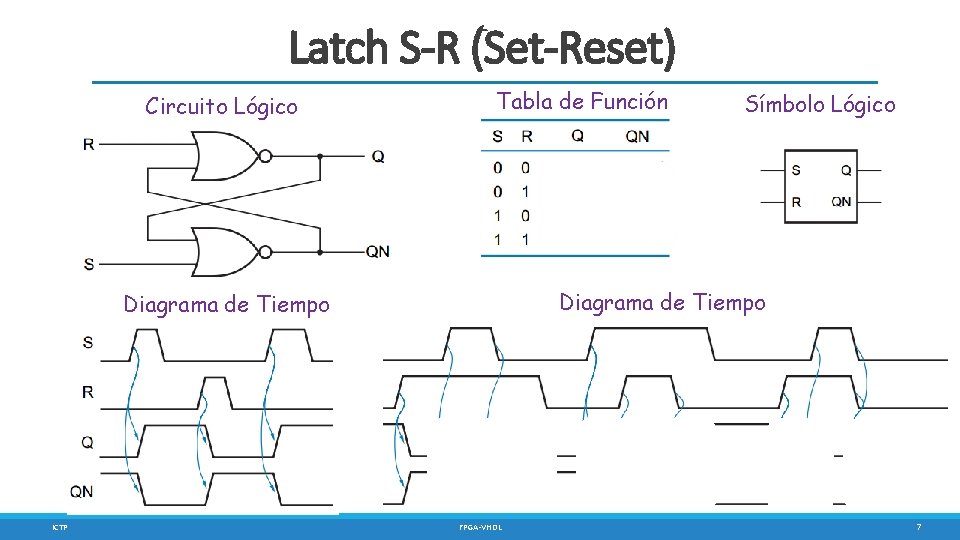

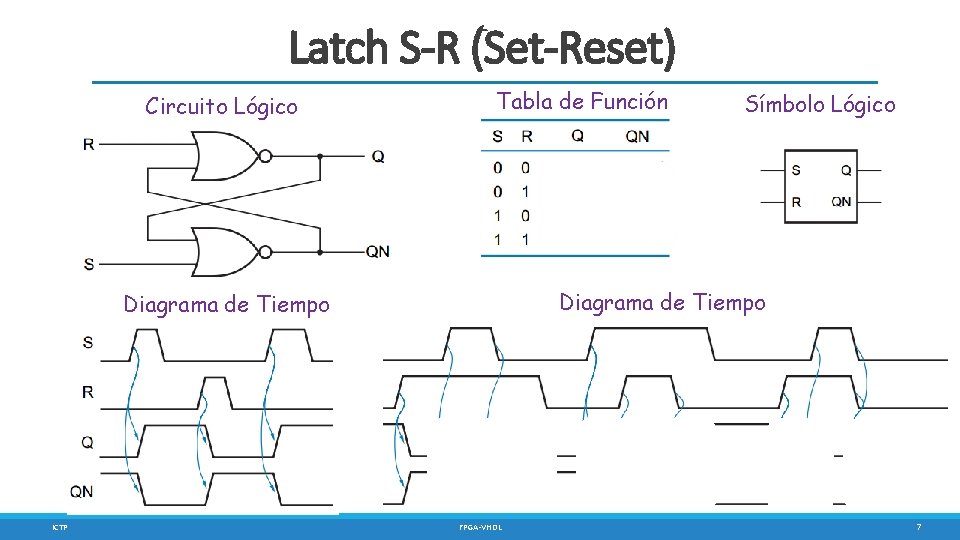

Latch S-R (Set-Reset) Circuito Lógico Tabla de Función Diagrama de Tiempo ICTP Símbolo Lógico FPGA-VHDL 7

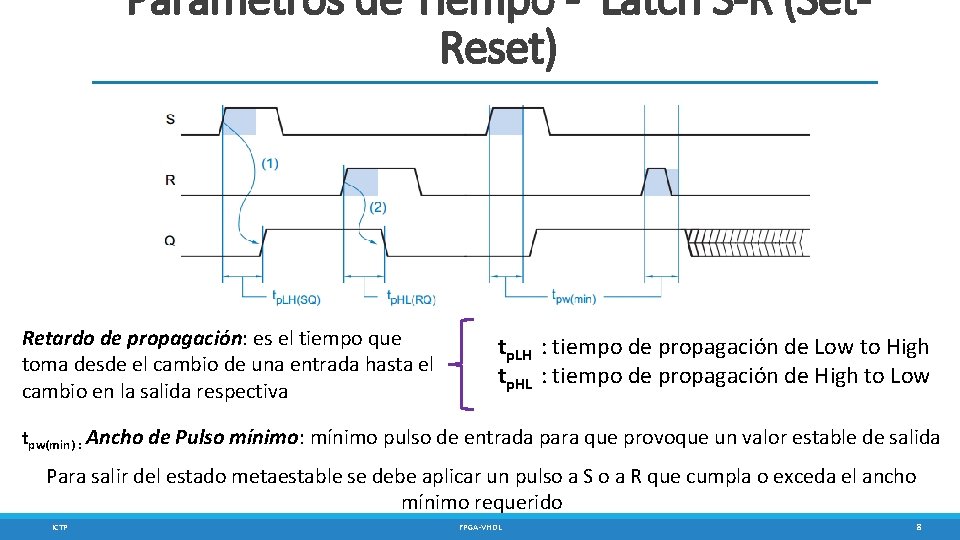

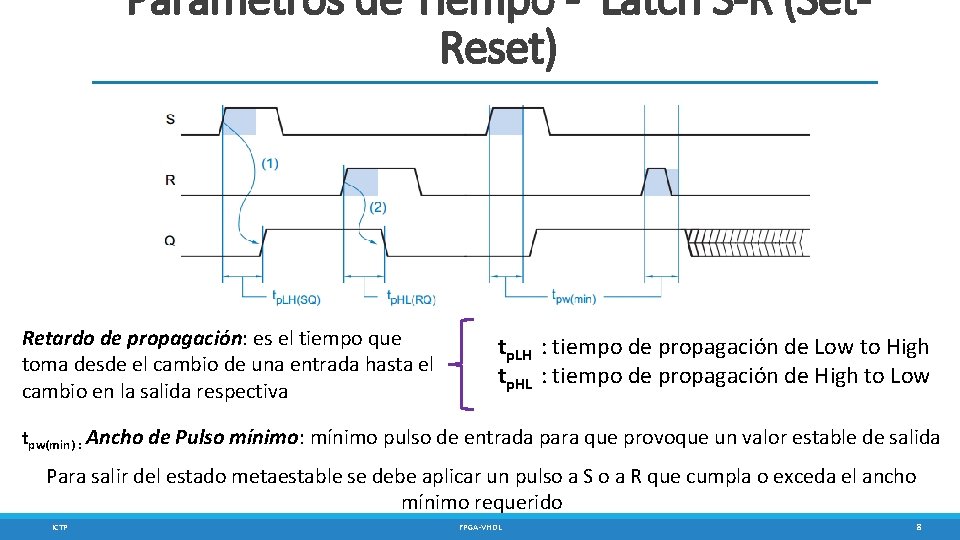

Parámetros de Tiempo - Latch S-R (Set. Reset) Retardo de propagación: es el tiempo que toma desde el cambio de una entrada hasta el cambio en la salida respectiva tp. LH : tiempo de propagación de Low to High tp. HL : tiempo de propagación de High to Low tpw(min) : Ancho de Pulso mínimo: mínimo pulso de entrada para que provoque un valor estable de salida Para salir del estado metaestable se debe aplicar un pulso a S o a R que cumpla o exceda el ancho mínimo requerido ICTP FPGA-VHDL 8

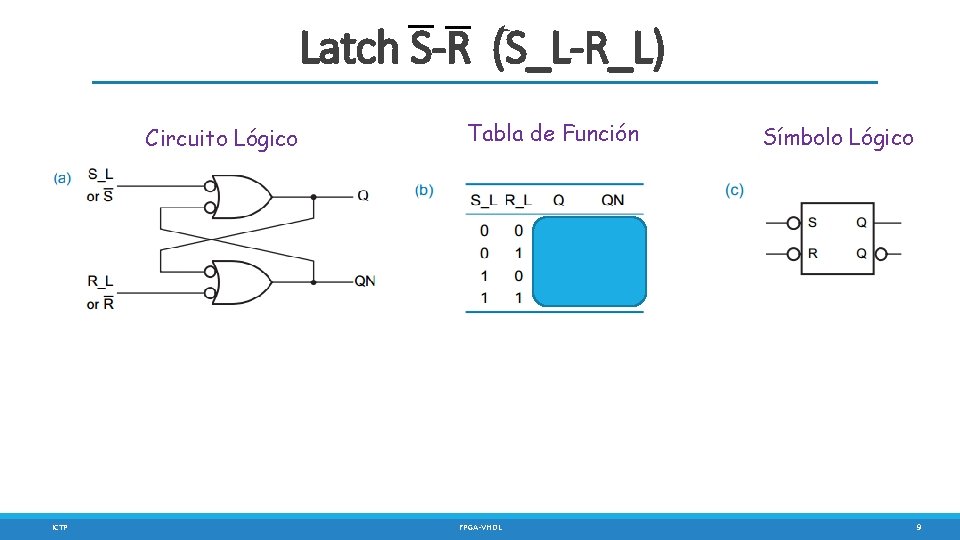

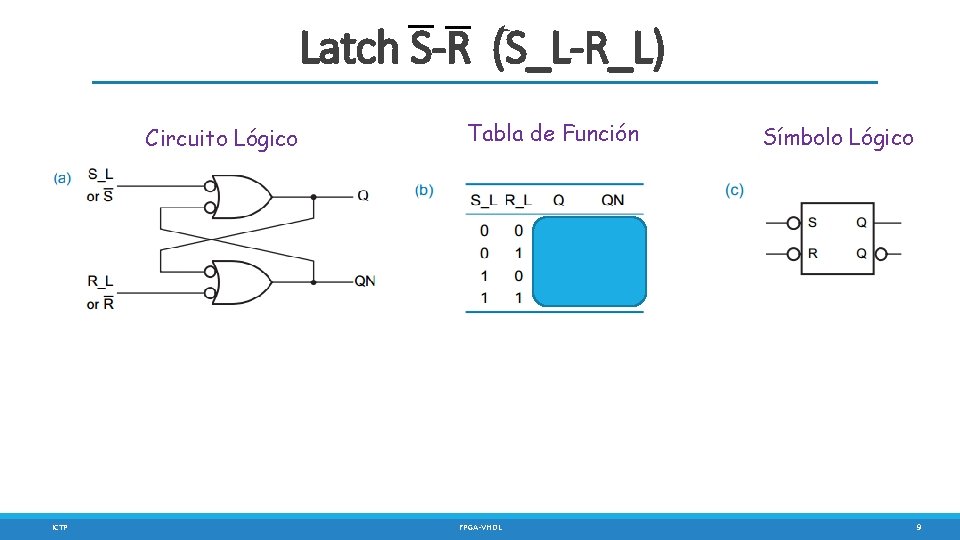

Latch S-R (S_L-R_L) Circuito Lógico ICTP Tabla de Función FPGA-VHDL Símbolo Lógico 9

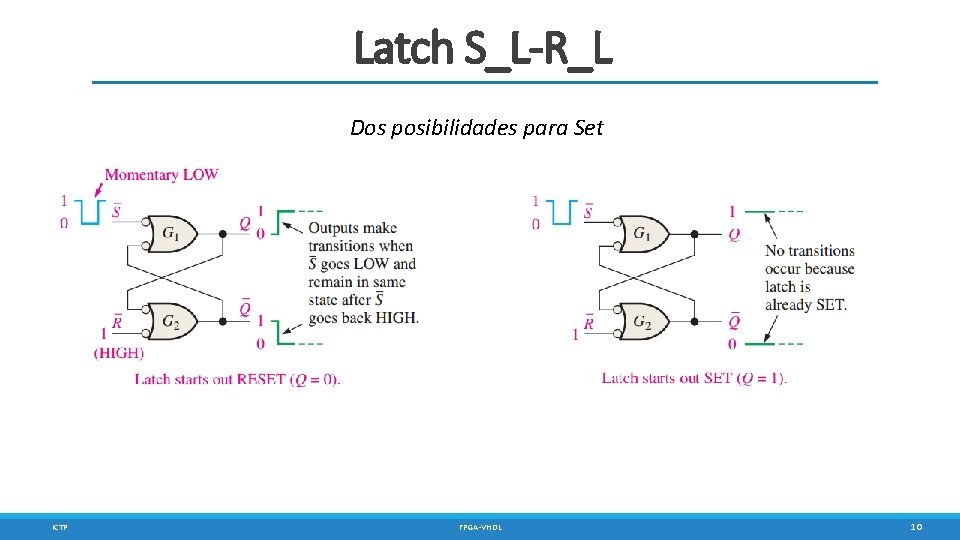

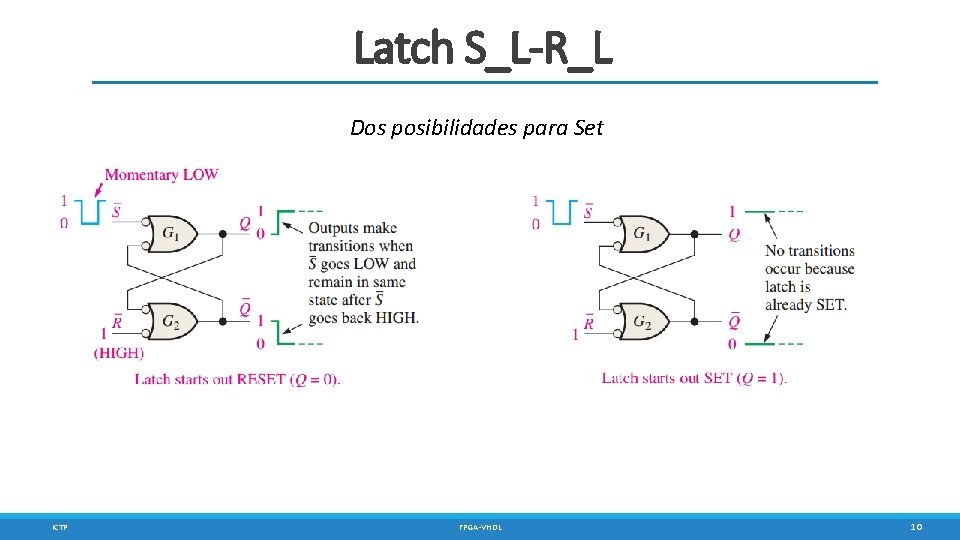

Latch S_L-R_L Dos posibilidades para Set ICTP FPGA-VHDL 10

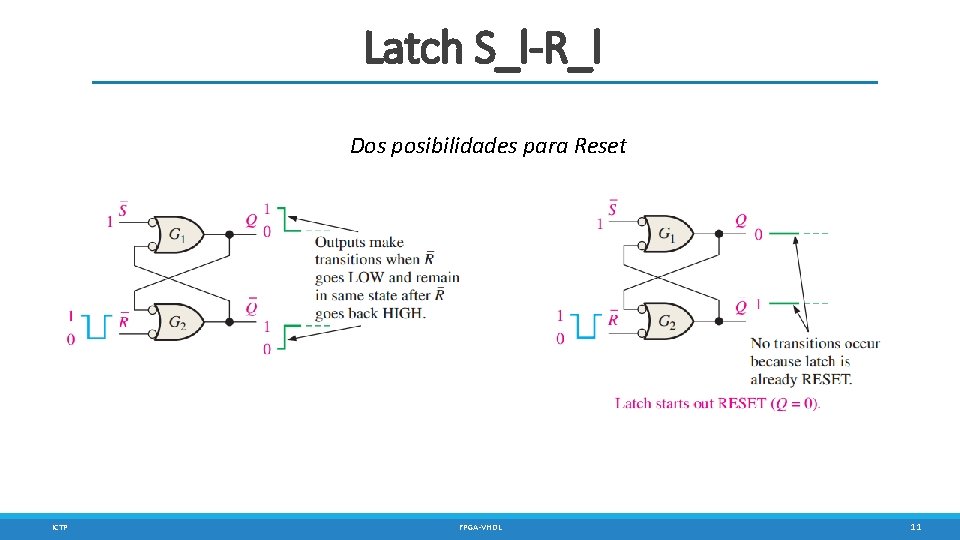

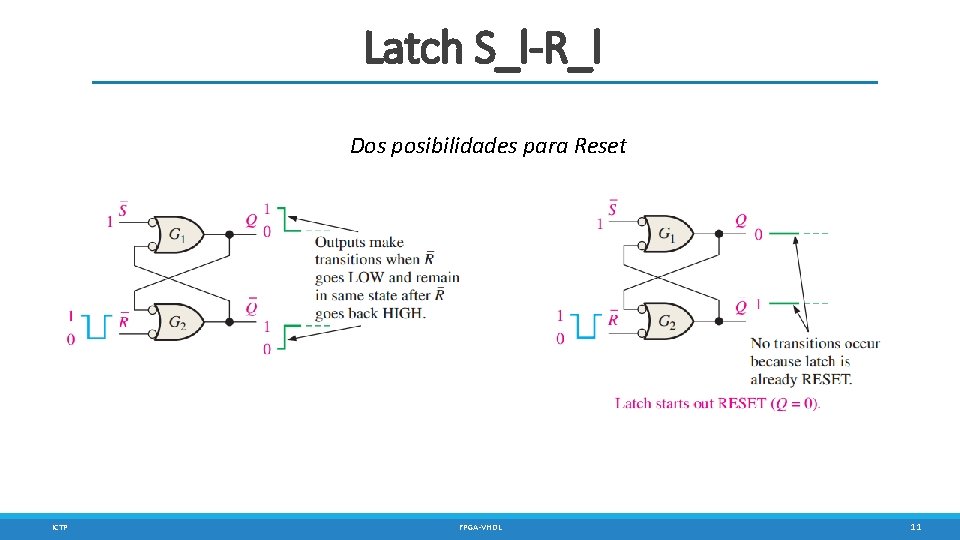

Latch S_l-R_l Dos posibilidades para Reset ICTP FPGA-VHDL 11

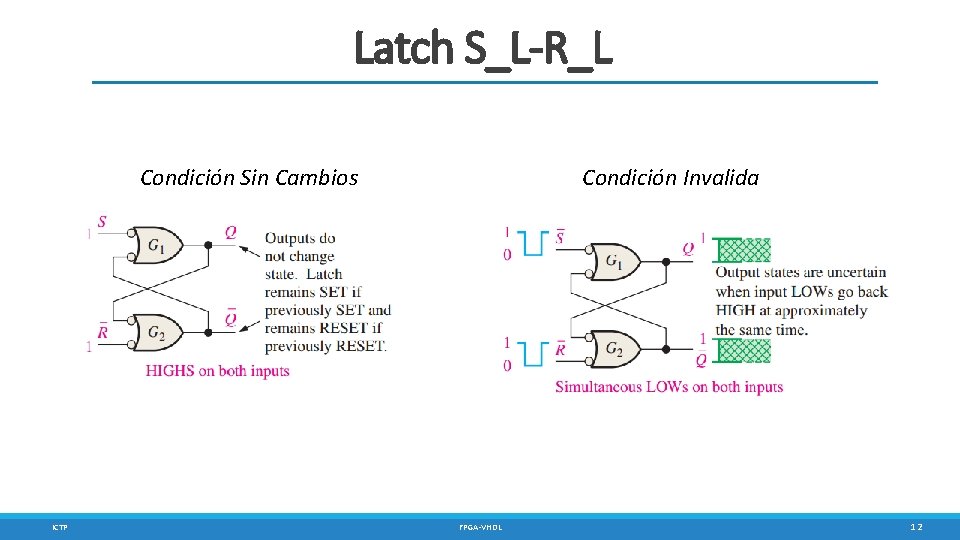

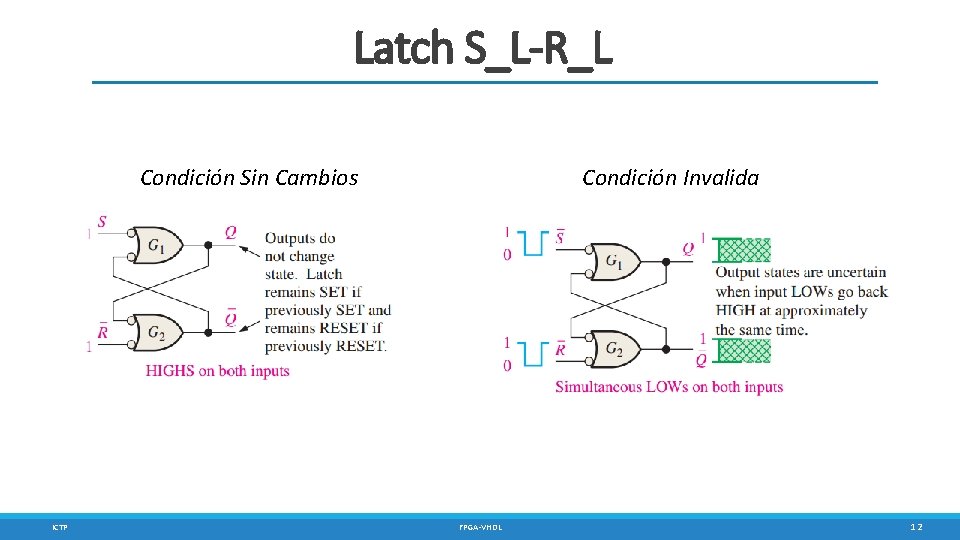

Latch S_L-R_L Condición Sin Cambios ICTP Condición Invalida FPGA-VHDL 12

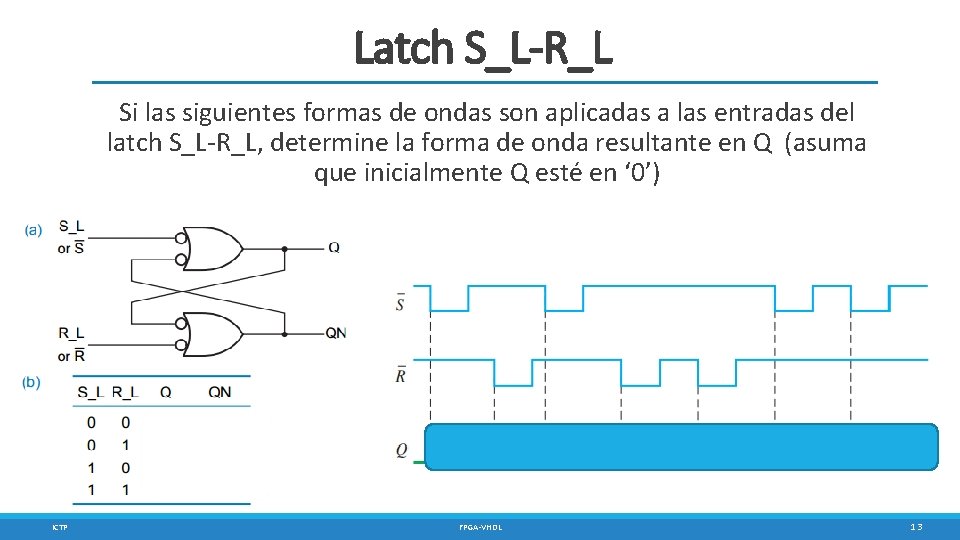

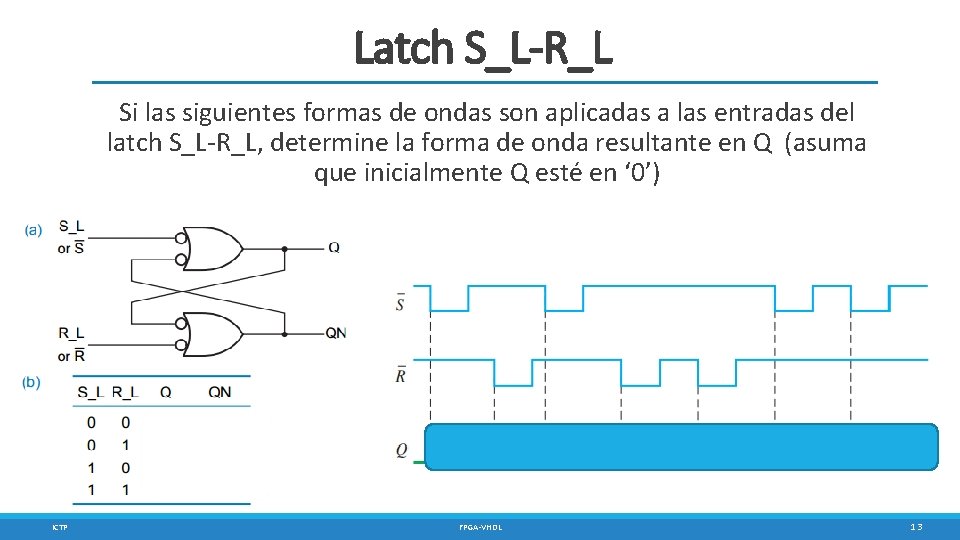

Latch S_L-R_L Si las siguientes formas de ondas son aplicadas a las entradas del latch S_L-R_L, determine la forma de onda resultante en Q (asuma que inicialmente Q esté en ‘ 0’) ICTP FPGA-VHDL 13

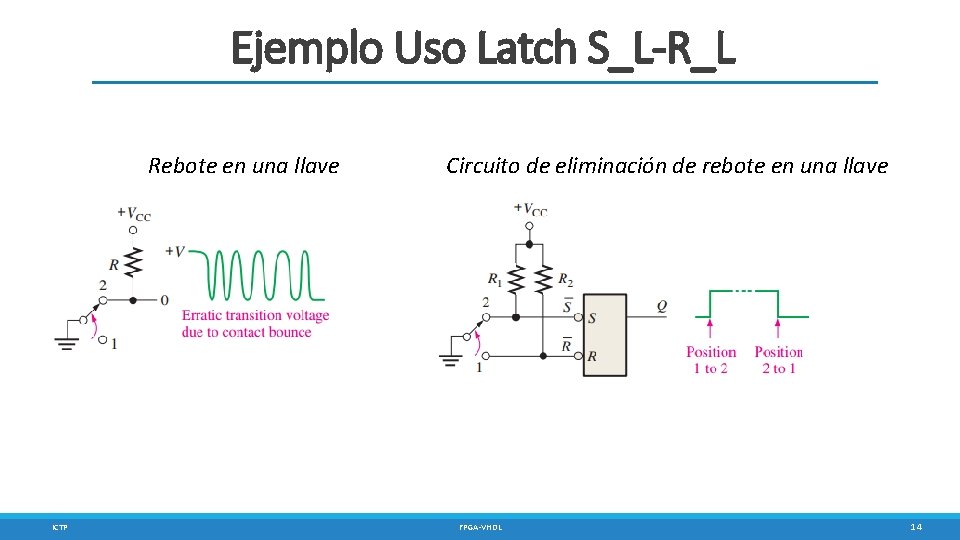

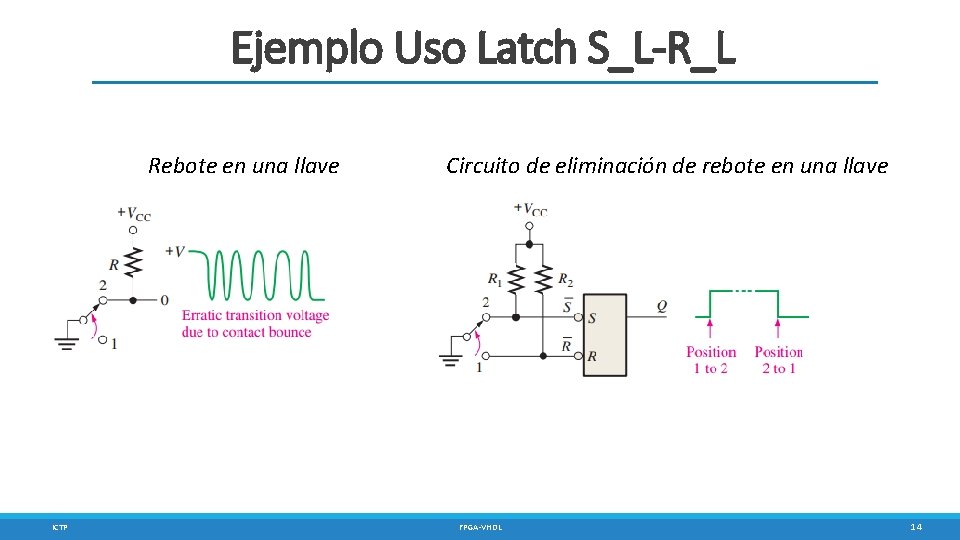

Ejemplo Uso Latch S_L-R_L Rebote en una llave ICTP Circuito de eliminación de rebote en una llave FPGA-VHDL 14

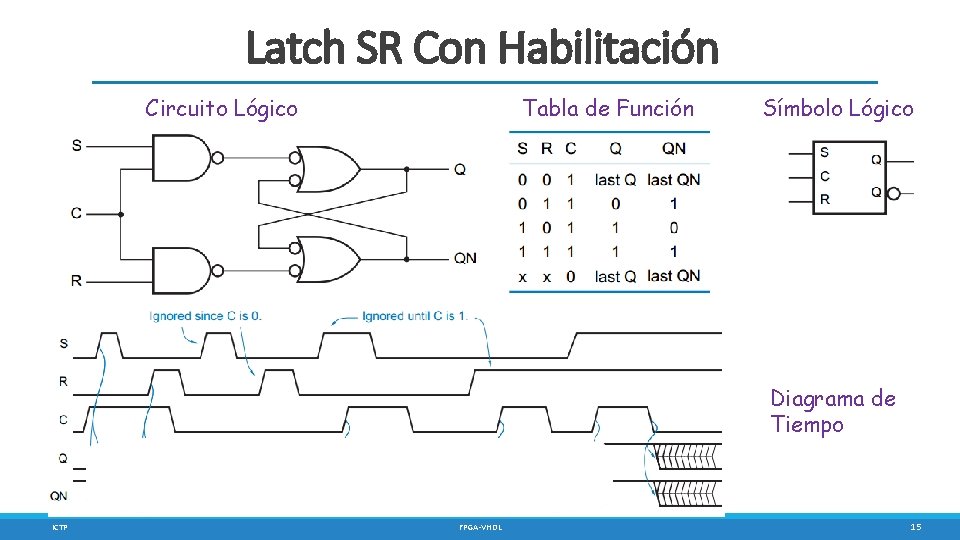

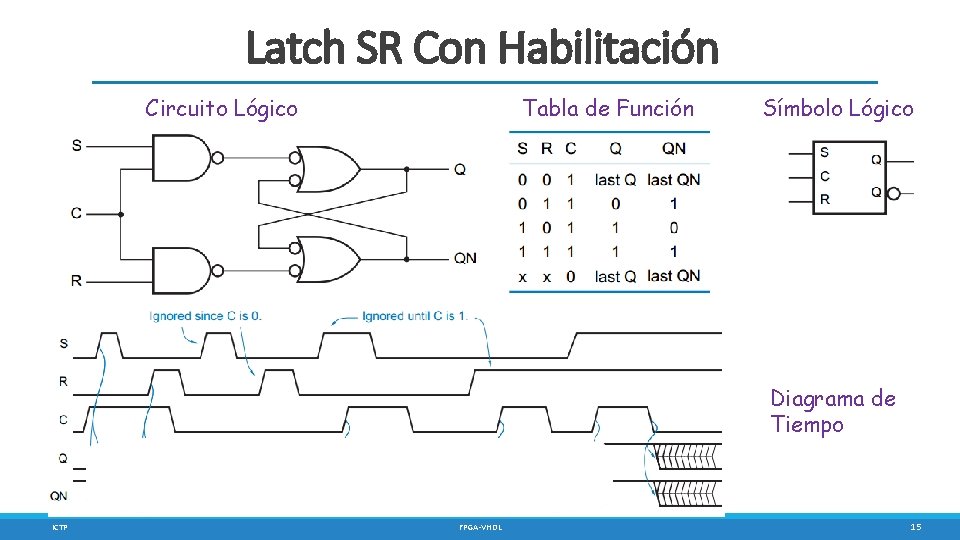

Latch SR Con Habilitación Tabla de Función Circuito Lógico Símbolo Lógico Diagrama de Tiempo ICTP FPGA-VHDL 15

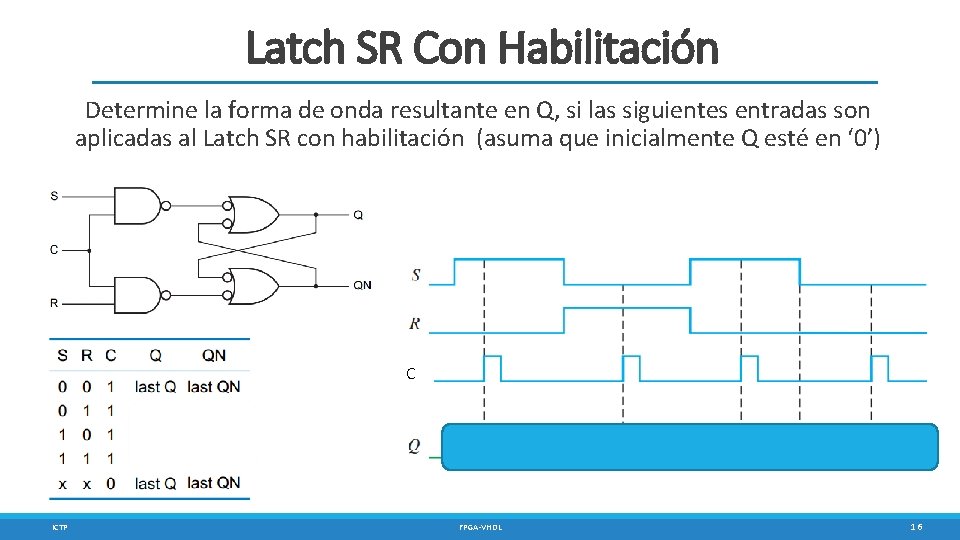

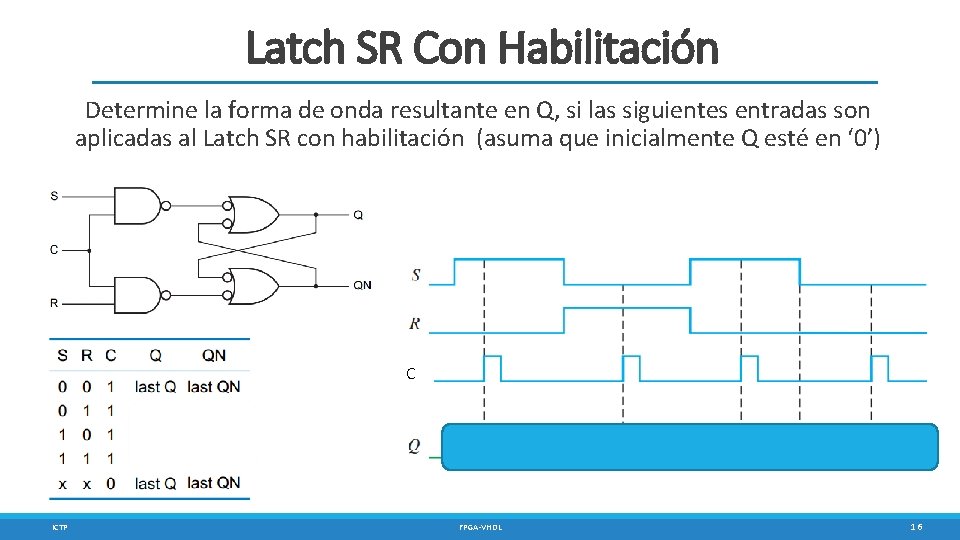

Latch SR Con Habilitación Determine la forma de onda resultante en Q, si las siguientes entradas son aplicadas al Latch SR con habilitación (asuma que inicialmente Q esté en ‘ 0’) C ICTP FPGA-VHDL 16

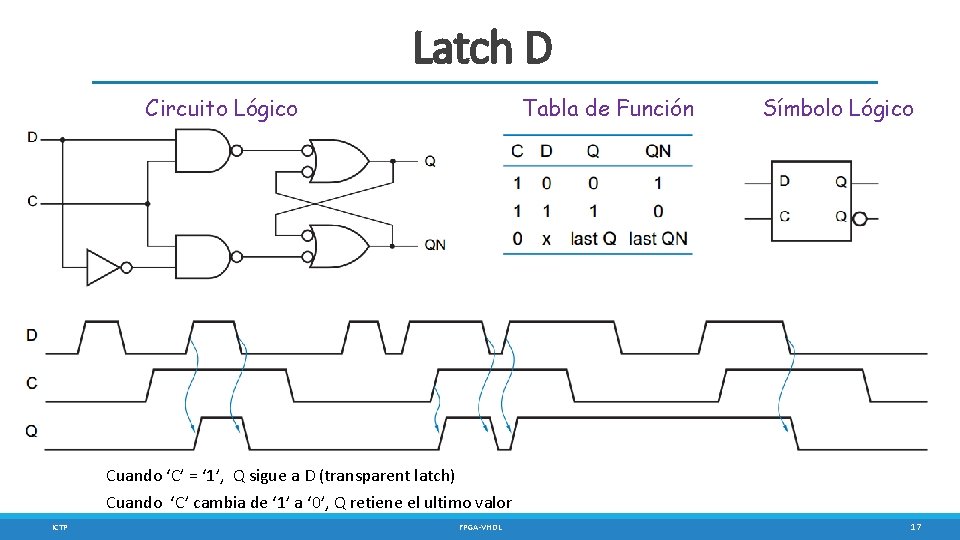

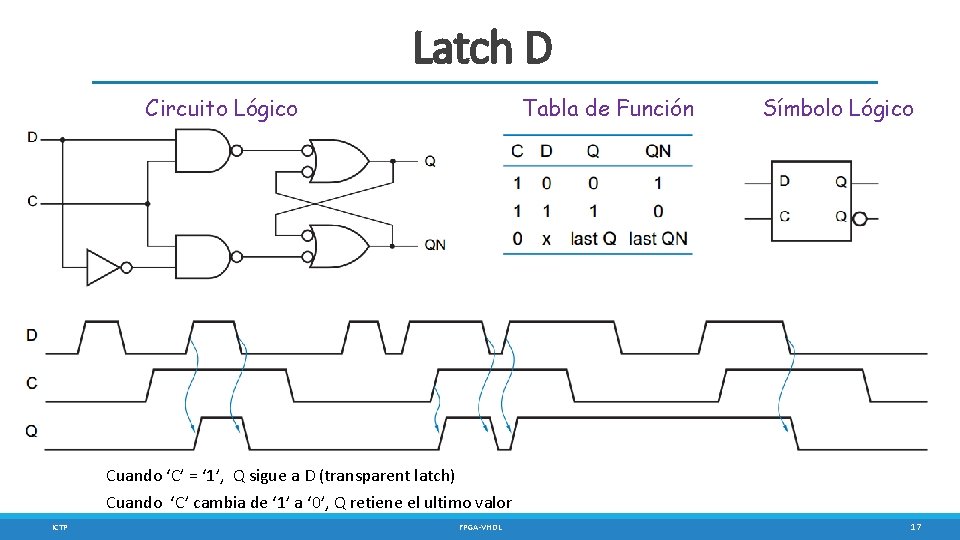

Latch D Tabla de Función Circuito Lógico Símbolo Lógico Cuando ‘C’ = ‘ 1’, Q sigue a D (transparent latch) Cuando ‘C’ cambia de ‘ 1’ a ‘ 0’, Q retiene el ultimo valor ICTP FPGA-VHDL 17

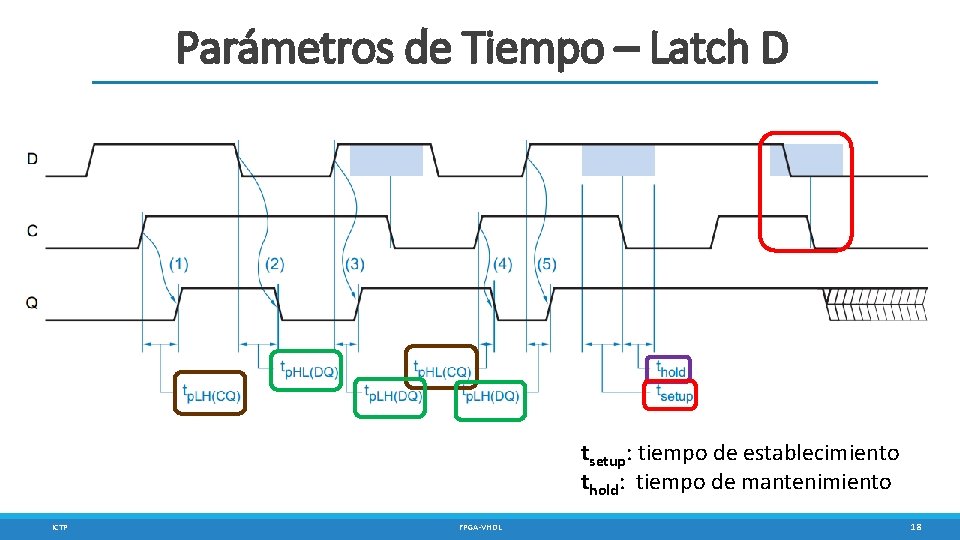

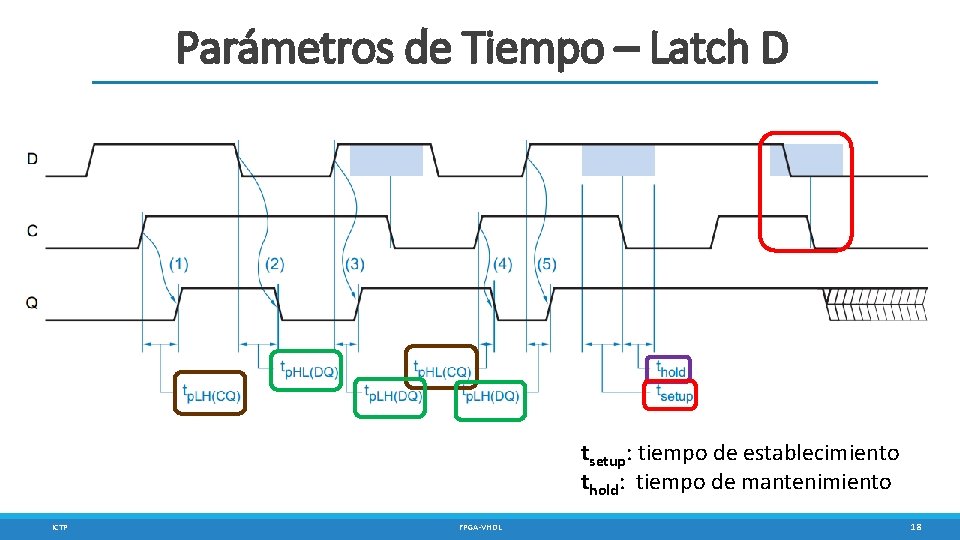

Parámetros de Tiempo – Latch D tsetup: tiempo de establecimiento thold: tiempo de mantenimiento ICTP FPGA-VHDL 18

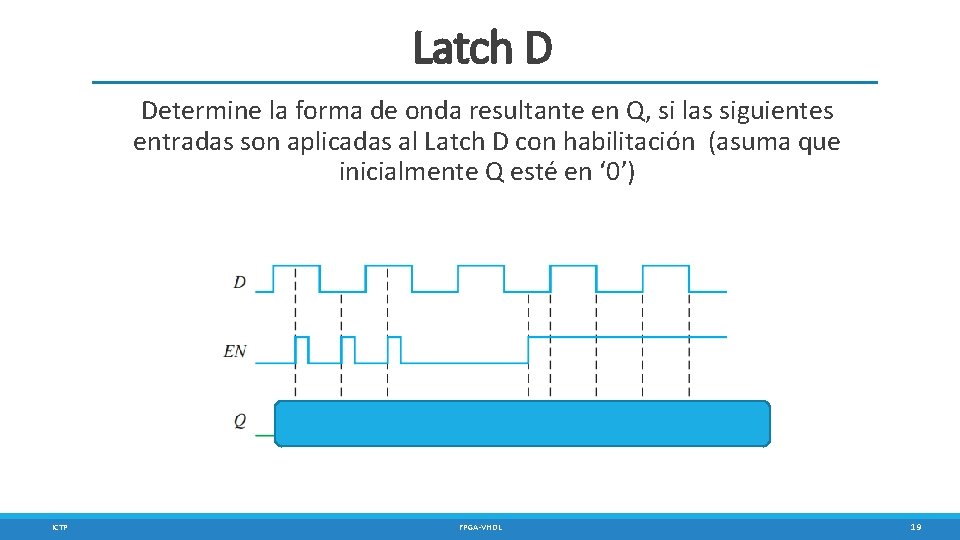

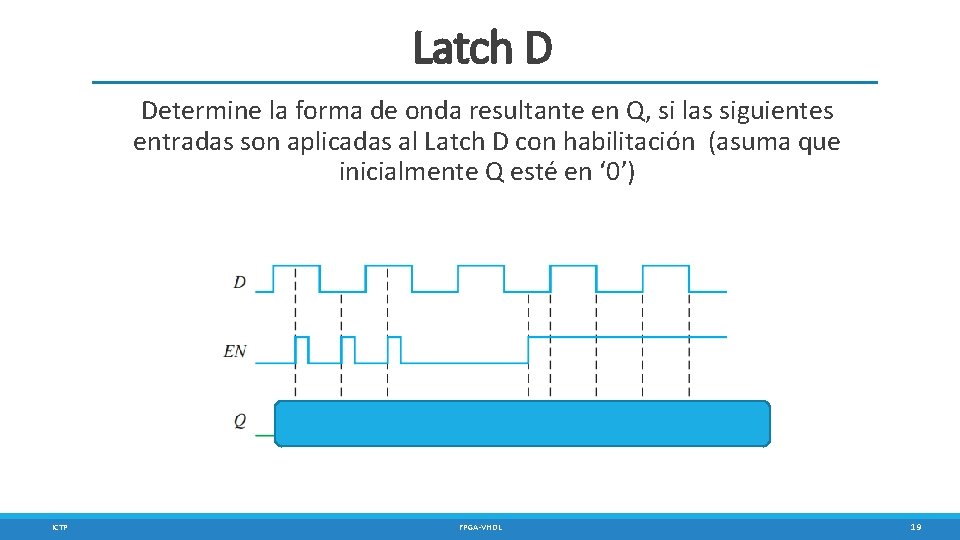

Latch D Determine la forma de onda resultante en Q, si las siguientes entradas son aplicadas al Latch D con habilitación (asuma que inicialmente Q esté en ‘ 0’) ICTP FPGA-VHDL 19

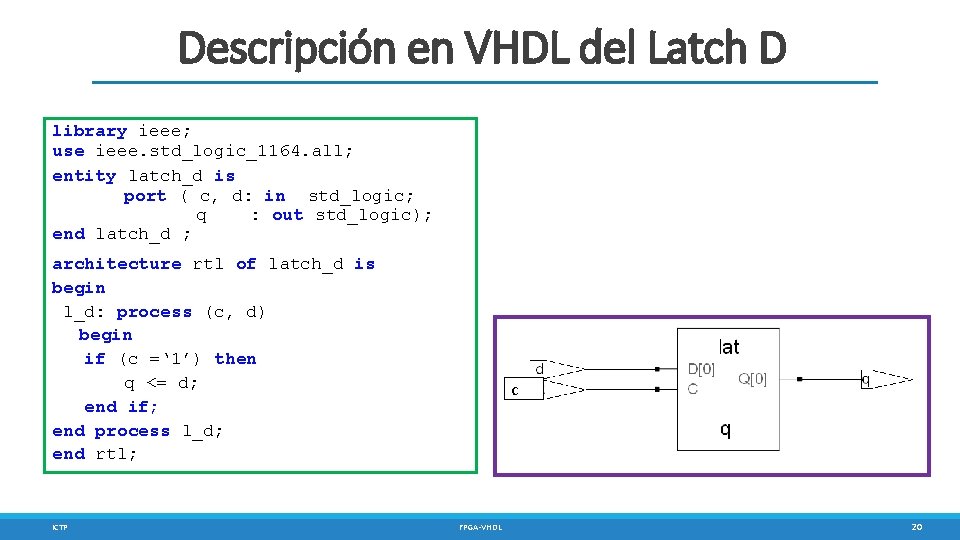

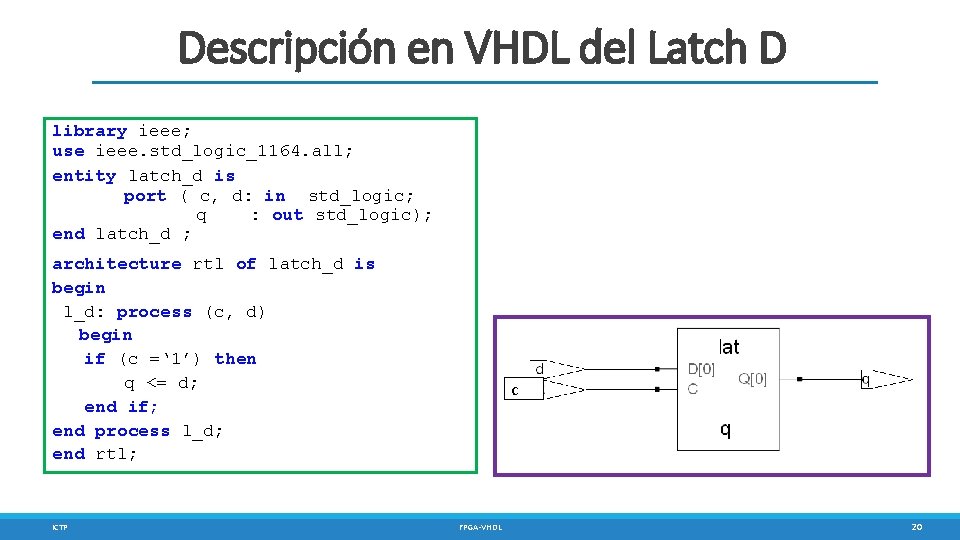

Descripción en VHDL del Latch D library ieee; use ieee. std_logic_1164. all; entity latch_d is port ( c, d: in std_logic; q : out std_logic); end latch_d ; architecture rtl of latch_d is begin l_d: process (c, d) begin if (c =‘ 1’) then q <= d; end if; end process l_d; end rtl; ICTP c FPGA-VHDL 20

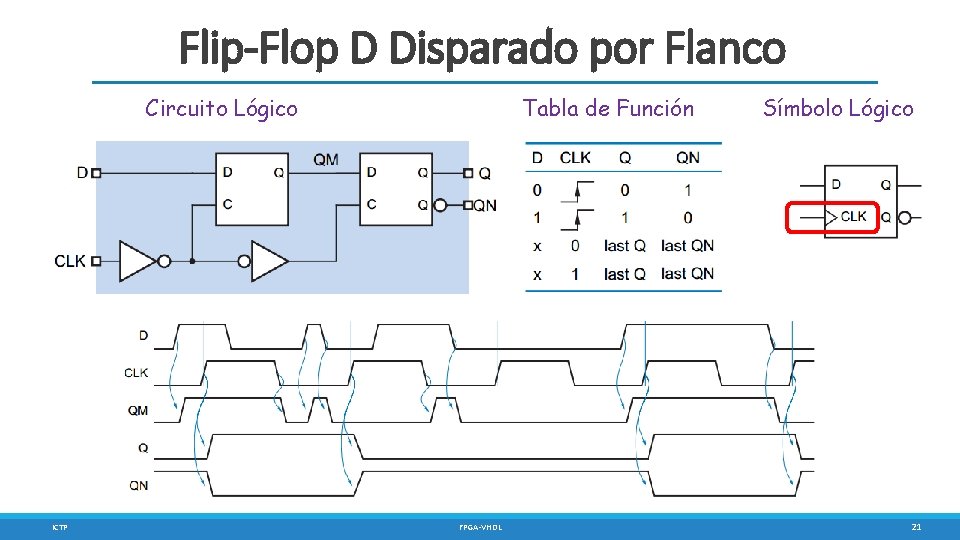

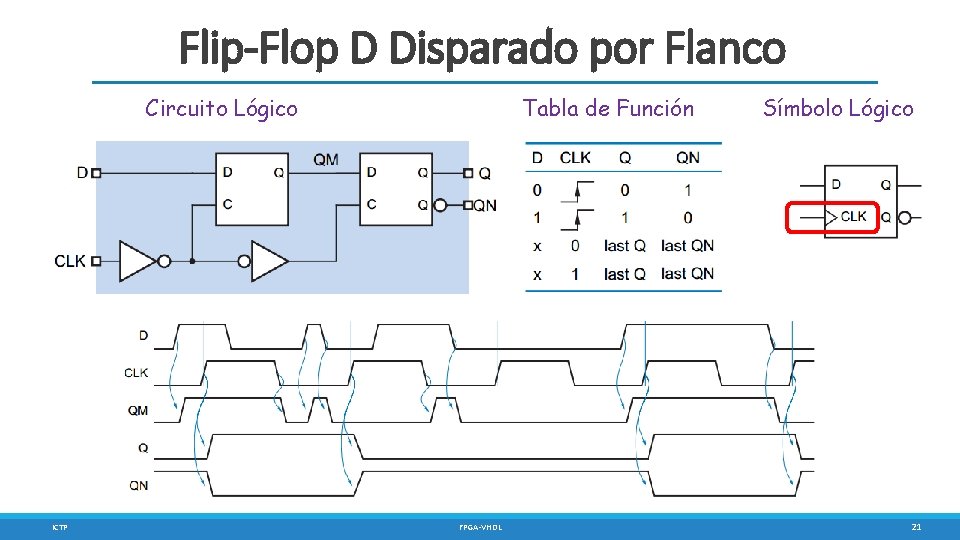

Flip-Flop D Disparado por Flanco Tabla de Función Circuito Lógico ICTP FPGA-VHDL Símbolo Lógico 21

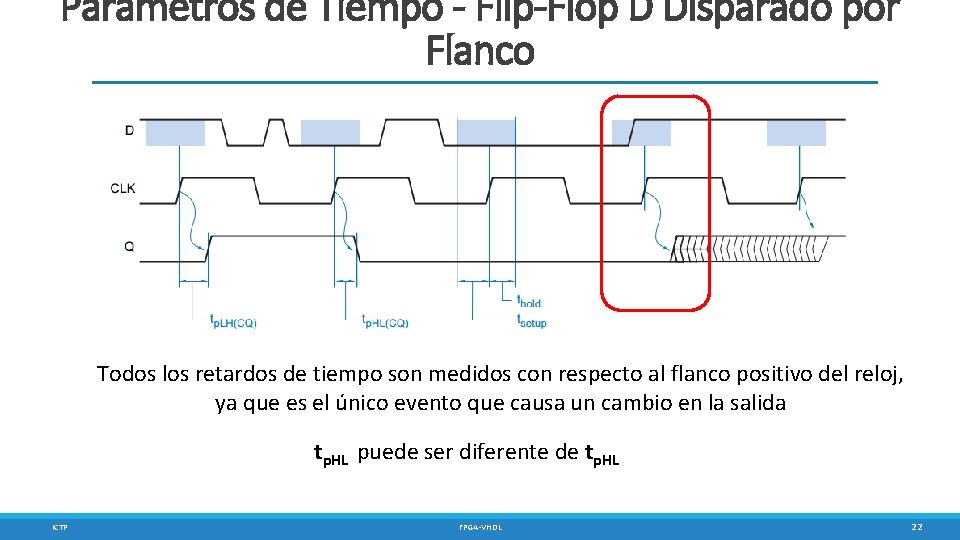

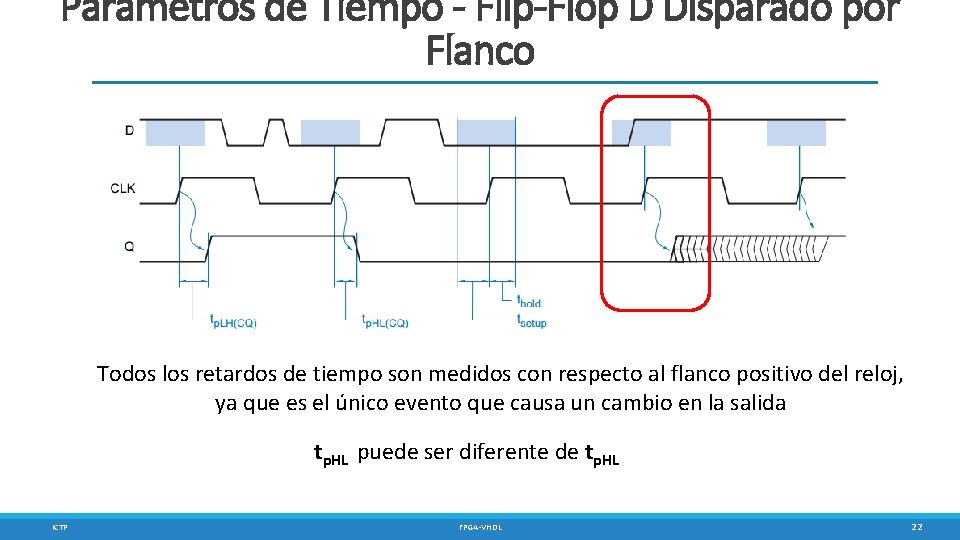

Parámetros de Tiempo - Flip-Flop D Disparado por Flanco Todos los retardos de tiempo son medidos con respecto al flanco positivo del reloj, ya que es el único evento que causa un cambio en la salida tp. HL puede ser diferente de tp. HL ICTP FPGA-VHDL 22

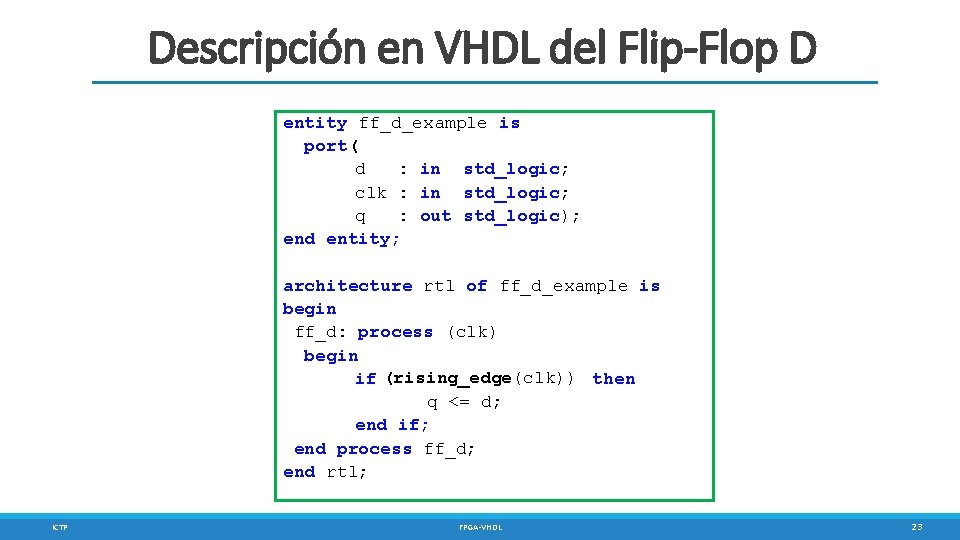

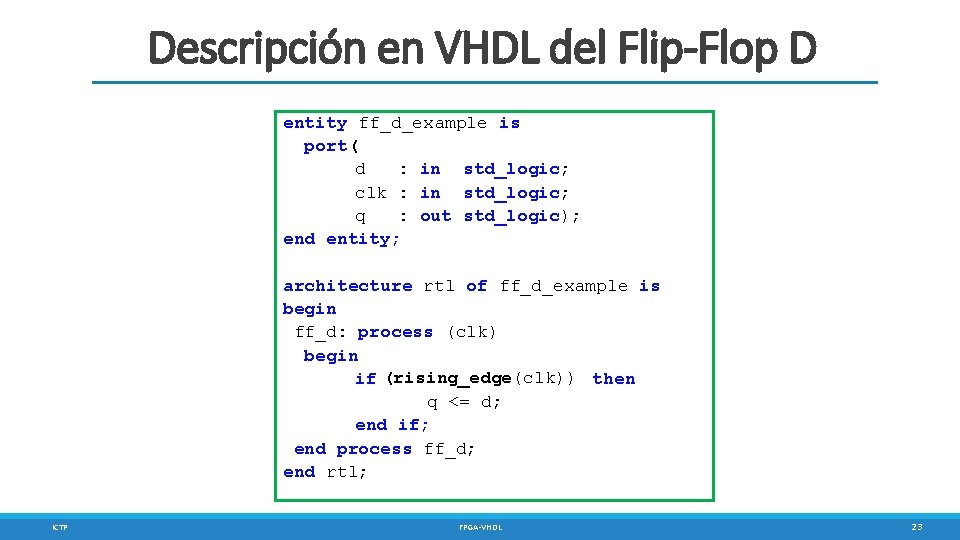

Descripción en VHDL del Flip-Flop D entity ff_d_example is port( d : in std_logic; clk : in std_logic; q : out std_logic); end entity; architecture rtl of ff_d_example is begin ff_d: process (clk) begin if (rising_edge(clk)) then q <= d; end if; end process ff_d; end rtl; ICTP FPGA-VHDL 23

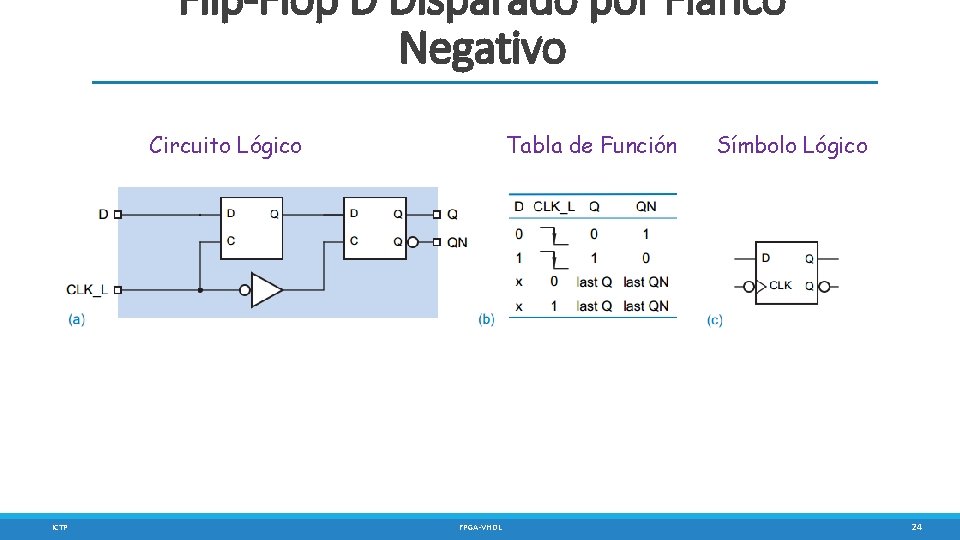

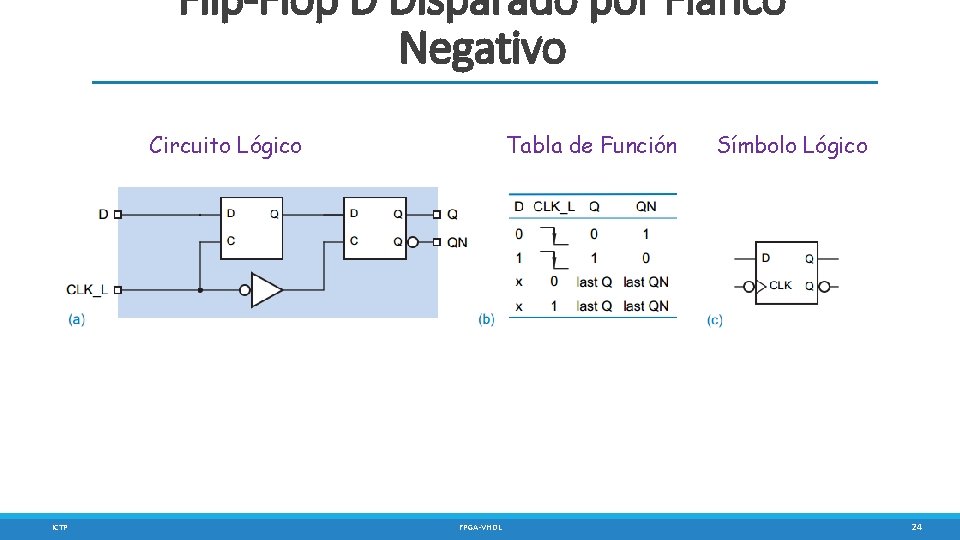

Flip-Flop D Disparado por Flanco Negativo Circuito Lógico ICTP Tabla de Función FPGA-VHDL Símbolo Lógico 24

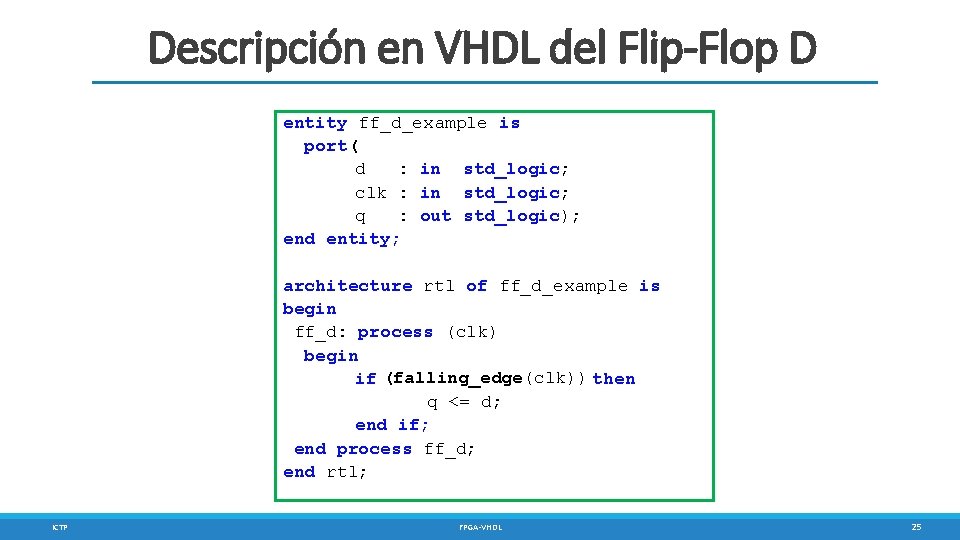

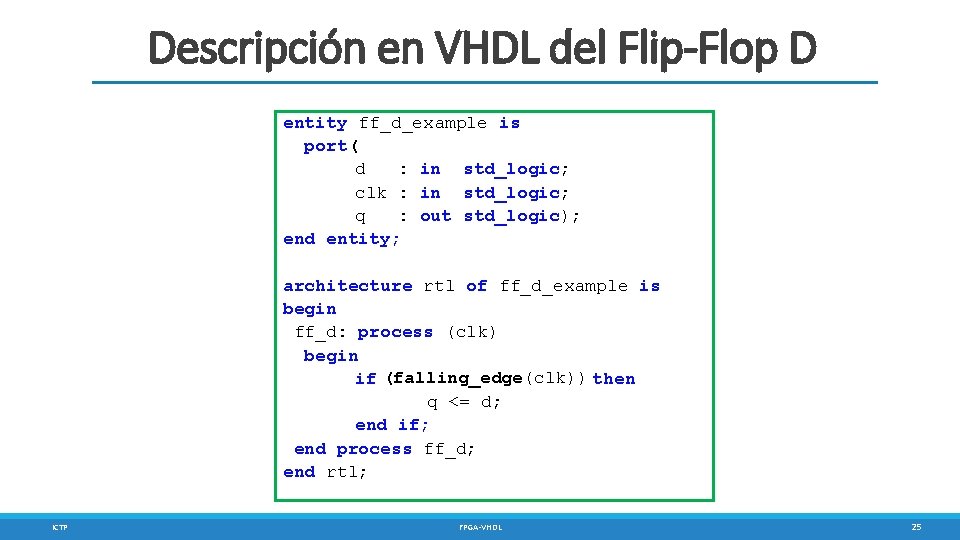

Descripción en VHDL del Flip-Flop D entity ff_d_example is port( d : in std_logic; clk : in std_logic; q : out std_logic); end entity; architecture rtl of ff_d_example is begin ff_d: process (clk) begin if (falling_edge(clk)) (rising_edge(clk)) then q <= d; end if; end process ff_d; end rtl; ICTP FPGA-VHDL 25

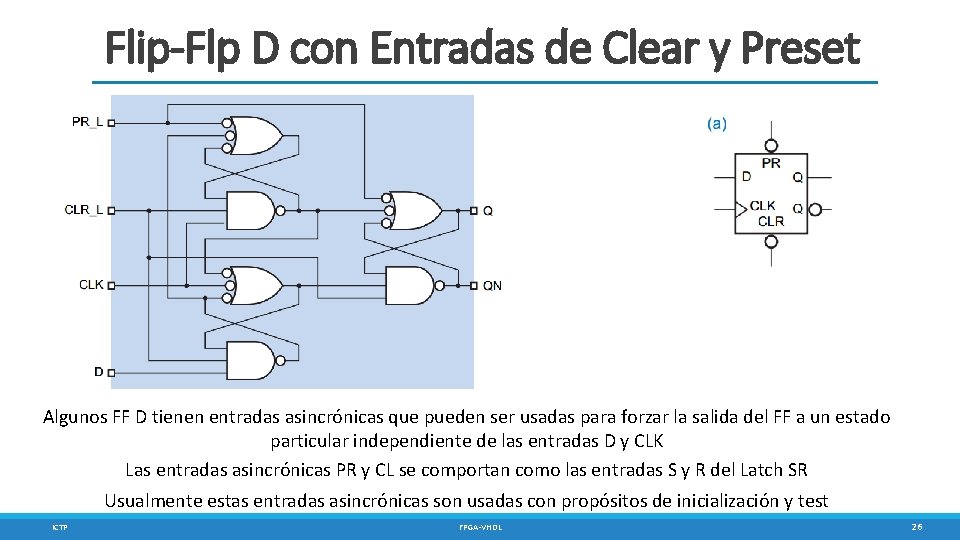

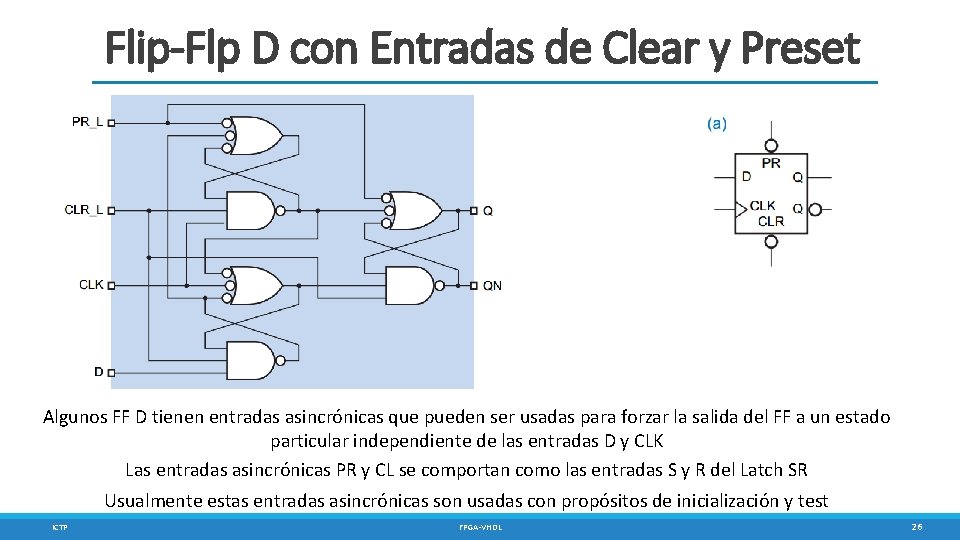

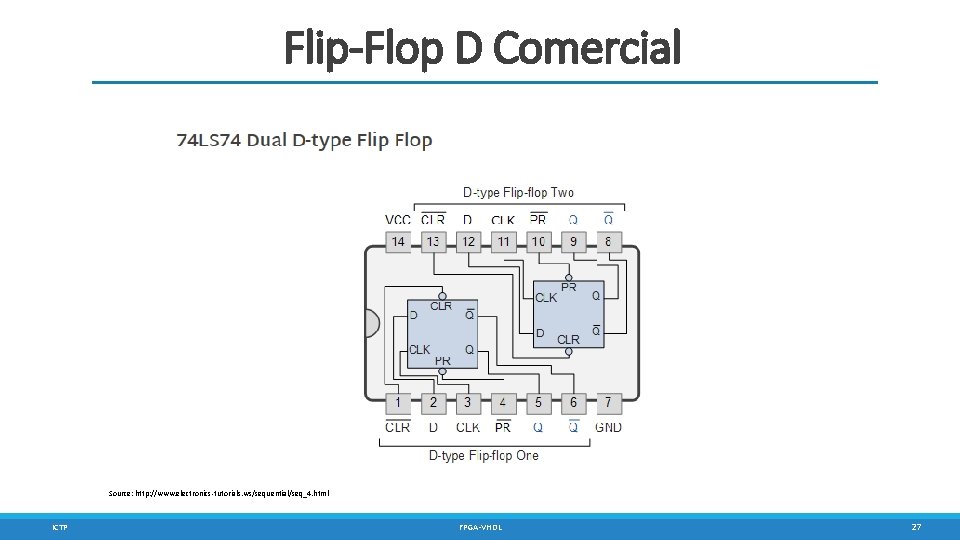

Flip-Flp D con Entradas de Clear y Preset Algunos FF D tienen entradas asincrónicas que pueden ser usadas para forzar la salida del FF a un estado particular independiente de las entradas D y CLK Las entradas asincrónicas PR y CL se comportan como las entradas S y R del Latch SR Usualmente estas entradas asincrónicas son usadas con propósitos de inicialización y test ICTP FPGA-VHDL 26

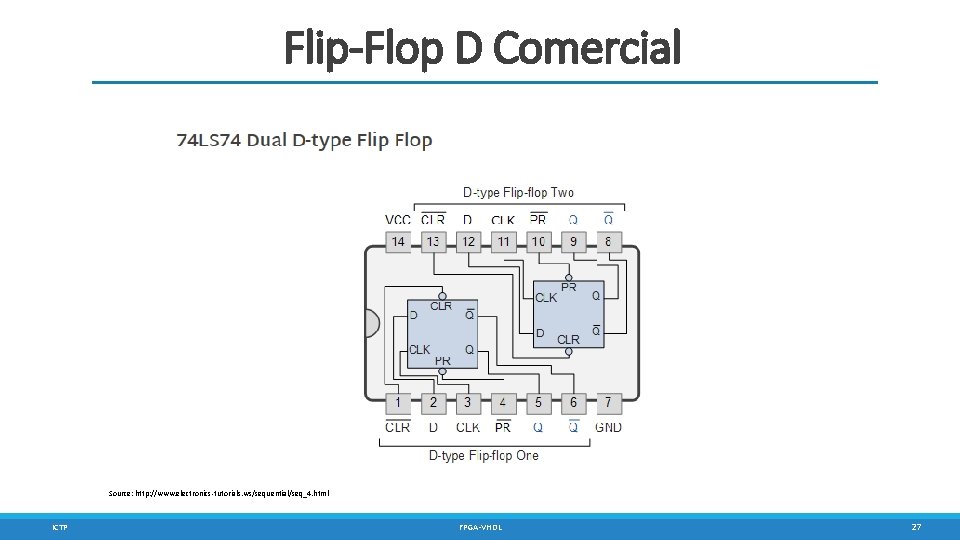

Flip-Flop D Comercial Source: http: //www. electronics-tutorials. ws/sequential/seq_4. html ICTP FPGA-VHDL 27

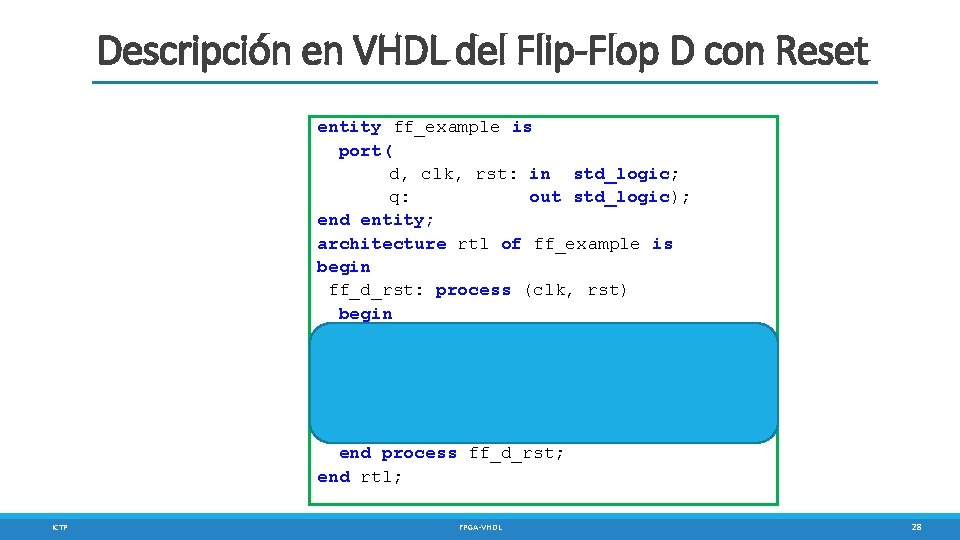

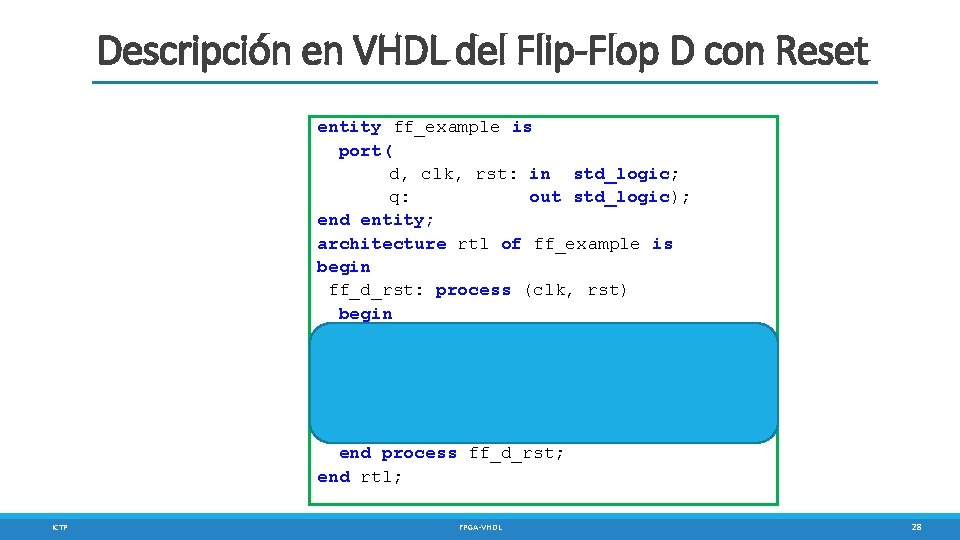

Descripción en VHDL del Flip-Flop D con Reset entity ff_example is port( d, clk, rst: in std_logic; q: out std_logic); end entity; architecture rtl of ff_example is begin ff_d_rst: process (clk, rst) begin if (rst=‘ 1’) then q <= ‘ 0’; elsif (rising_edge (clk)) then q <= d; end if; end process ff_d_rst; end rtl; ICTP FPGA-VHDL 28

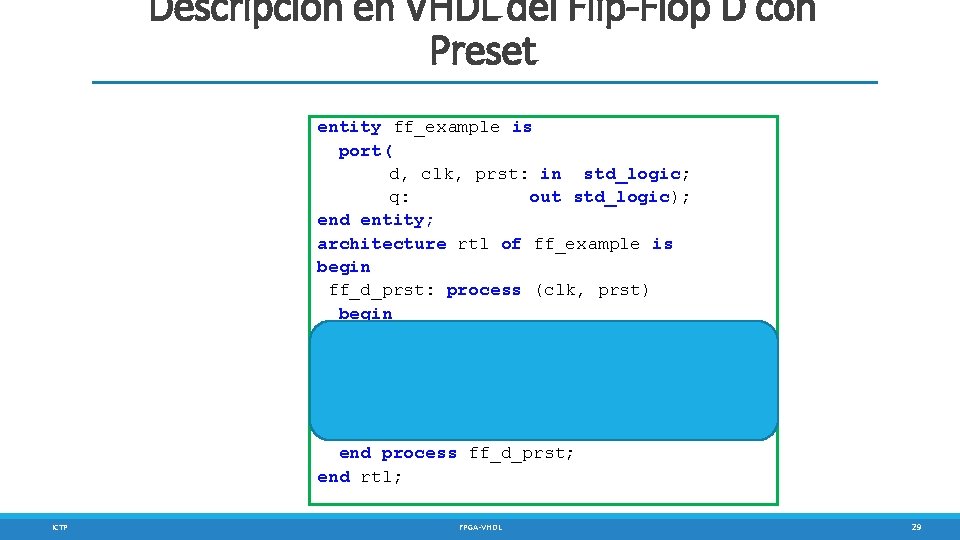

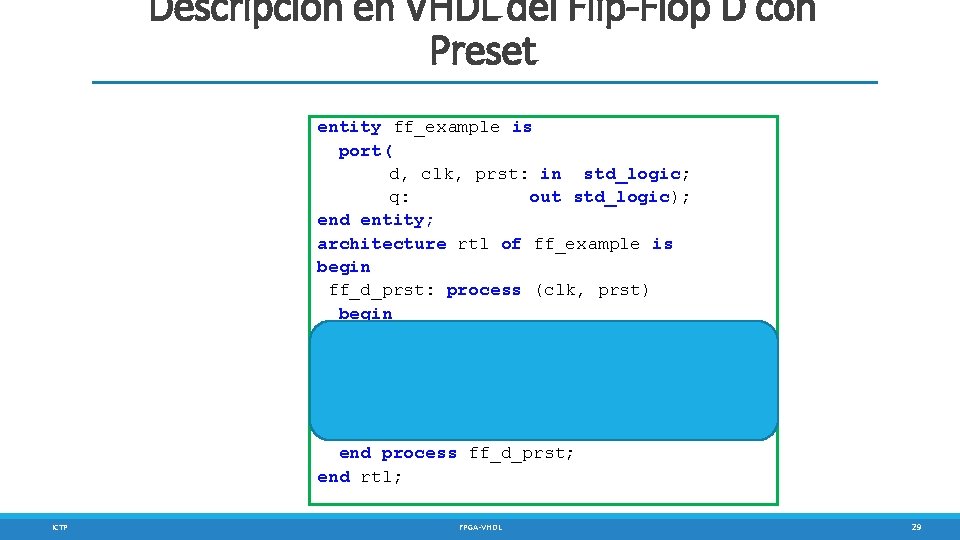

Descripción en VHDL del Flip-Flop D con Preset entity ff_example is port( d, clk, prst: in std_logic; q: out std_logic); end entity; architecture rtl of ff_example is begin ff_d_prst: process (clk, prst) begin if (prst=‘ 1’) then q <= ‘ 1’; elsif (rising_edge (clk)) then q <= d; end if; end process ff_d_prst; end rtl; ICTP FPGA-VHDL 29

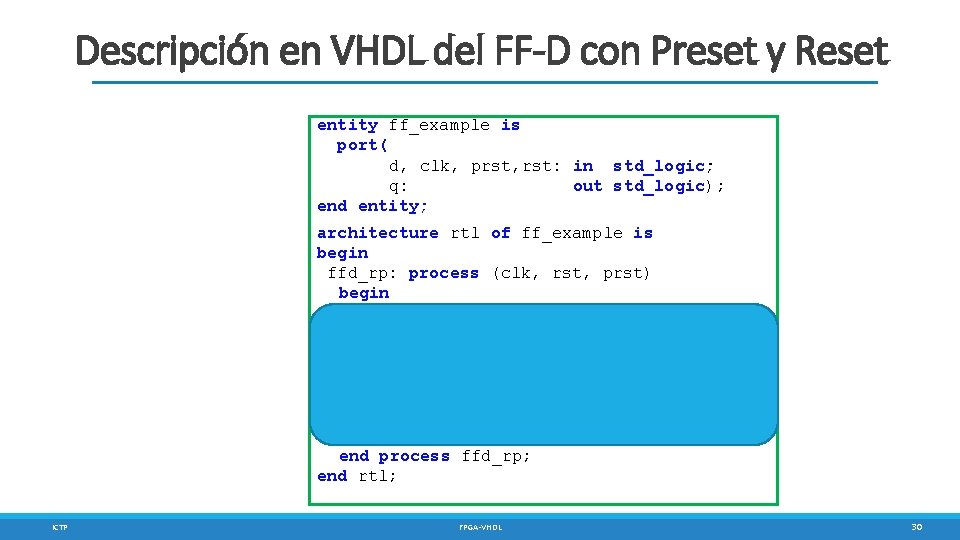

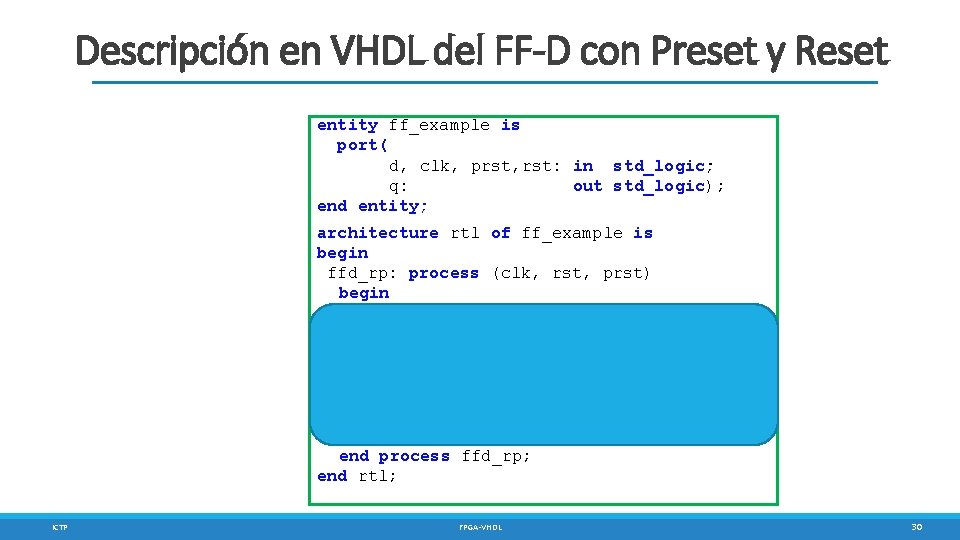

Descripción en VHDL del FF-D con Preset y Reset entity ff_example is port( d, clk, prst, rst: in std_logic; q: out std_logic); end entity; architecture rtl of ff_example is begin ffd_rp: process (clk, rst, prst) begin if (prst=‘ 1’) then q <= ‘ 1’; elsif (rst=‘ 1’) then q <= ‘ 0’; elsif (rising_edge (clk)) then q <= d; end if; end process ffd_rp; end rtl; ICTP FPGA-VHDL 30

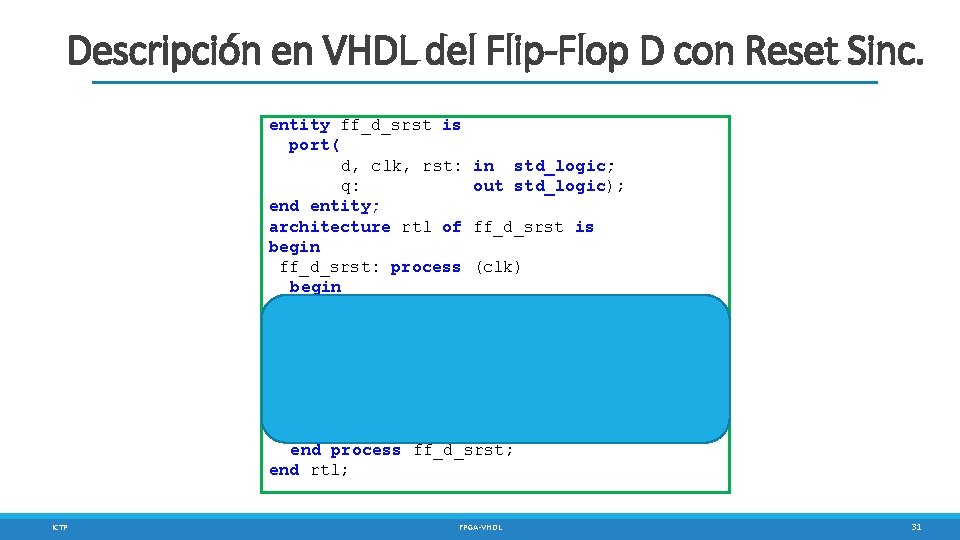

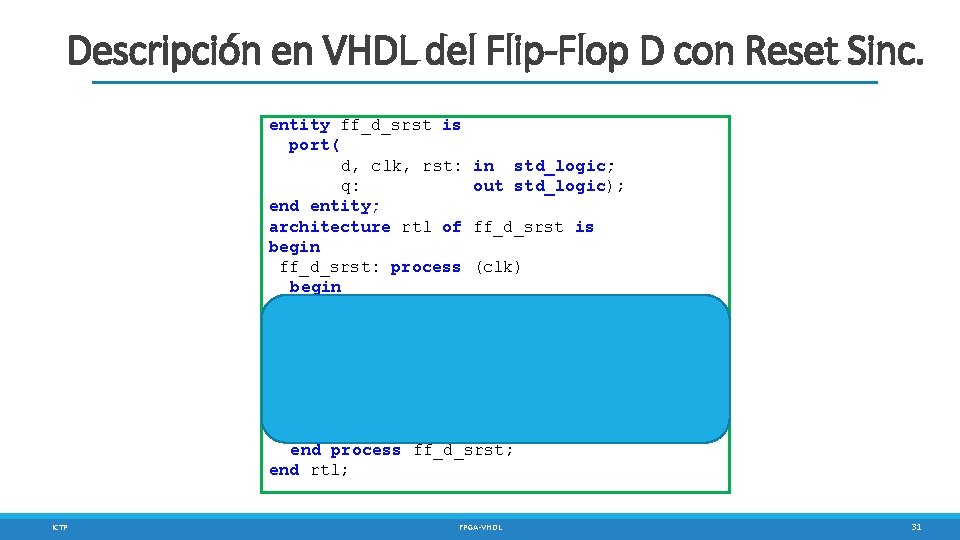

Descripción en VHDL del Flip-Flop D con Reset Sinc. entity ff_d_srst is port( d, clk, rst: in std_logic; q: out std_logic); end entity; architecture rtl of ff_d_srst is begin ff_d_srst: process (clk) begin if (rising_edge (clk)) then if (rst=‘ 1’) then q <= ‘ 0’; else q <= d; end if; end process ff_d_srst; end rtl; ICTP FPGA-VHDL 31

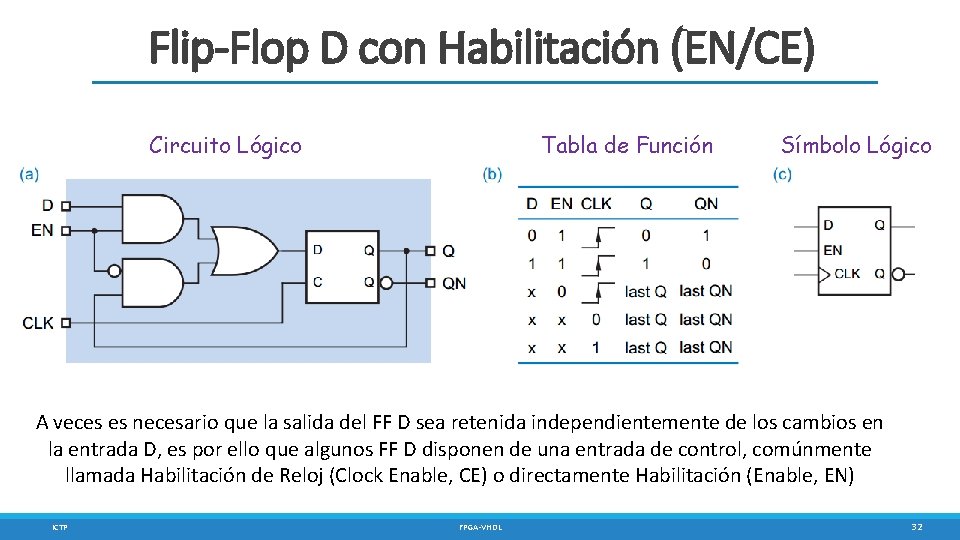

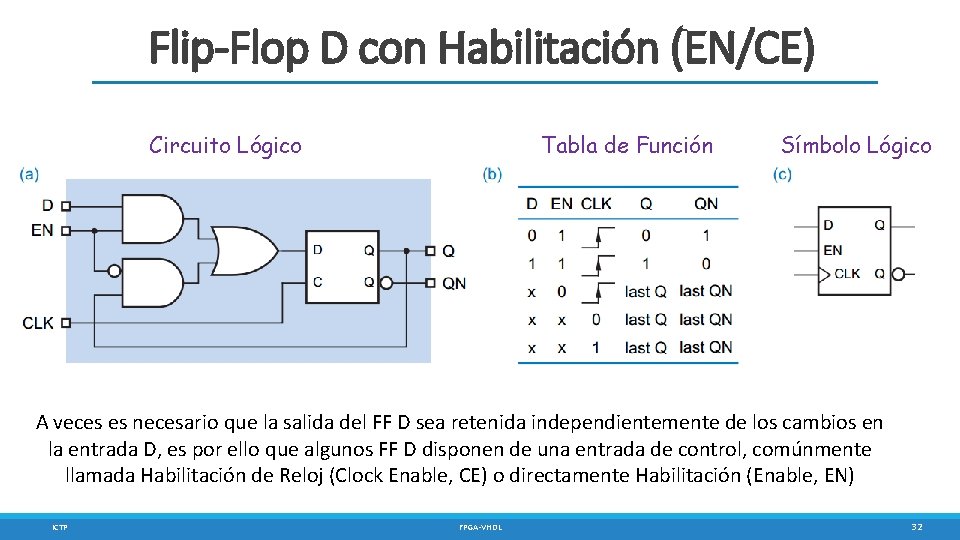

Flip-Flop D con Habilitación (EN/CE) Circuito Lógico Tabla de Función Símbolo Lógico A veces es necesario que la salida del FF D sea retenida independientemente de los cambios en la entrada D, es por ello que algunos FF D disponen de una entrada de control, comúnmente llamada Habilitación de Reloj (Clock Enable, CE) o directamente Habilitación (Enable, EN) ICTP FPGA-VHDL 32

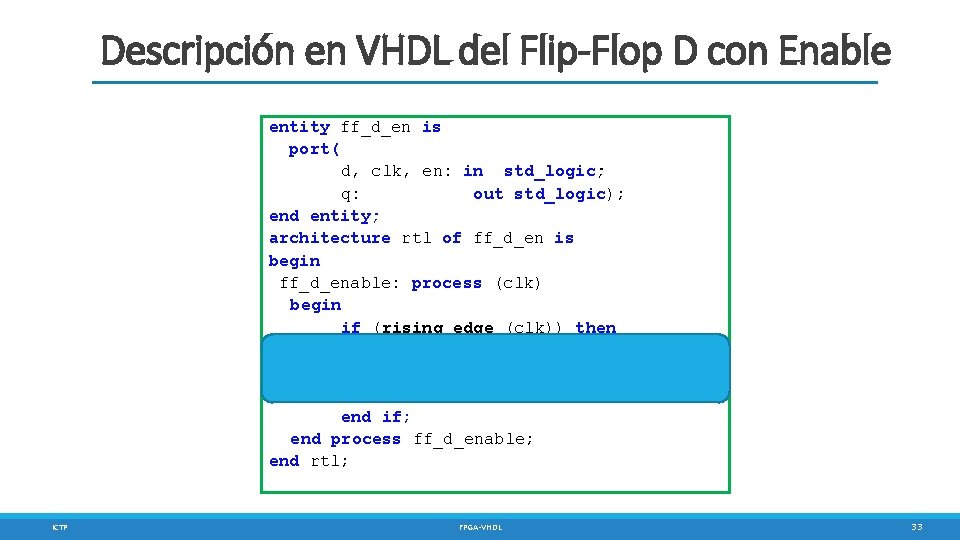

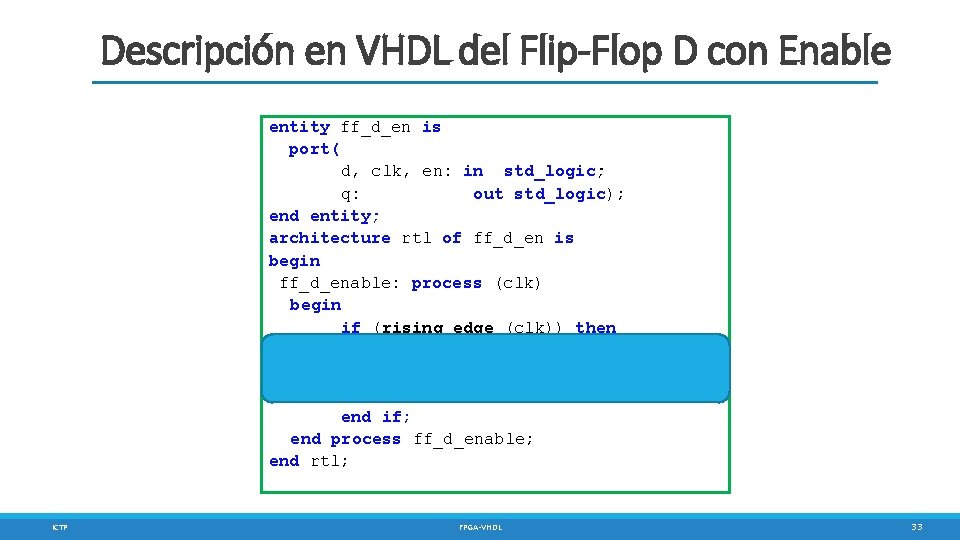

Descripción en VHDL del Flip-Flop D con Enable entity ff_d_en is port( d, clk, en: in std_logic; q: out std_logic); end entity; architecture rtl of ff_d_en is begin ff_d_enable: process (clk) begin if (rising_edge (clk)) then if (en=‘ 1’) then q <= d; end if; end process ff_d_enable; end rtl; ICTP FPGA-VHDL 33

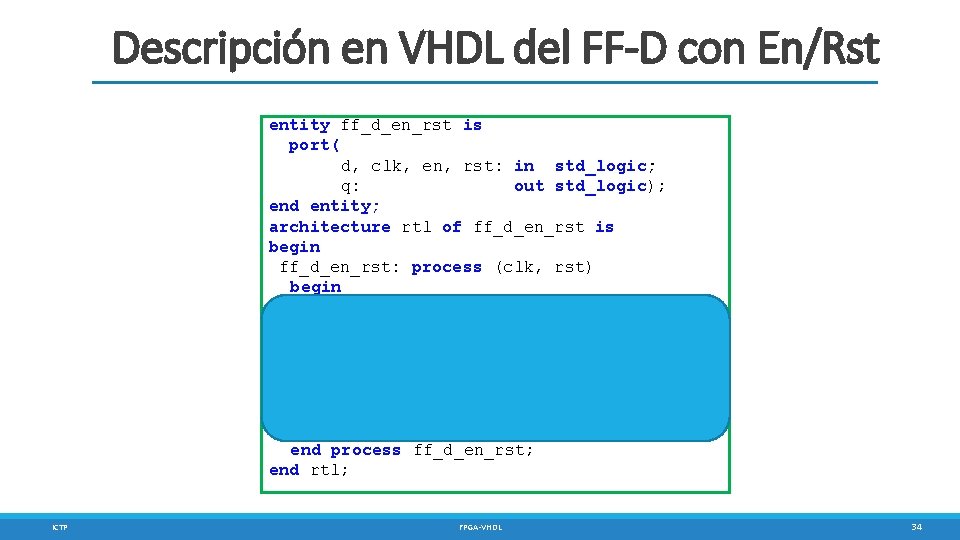

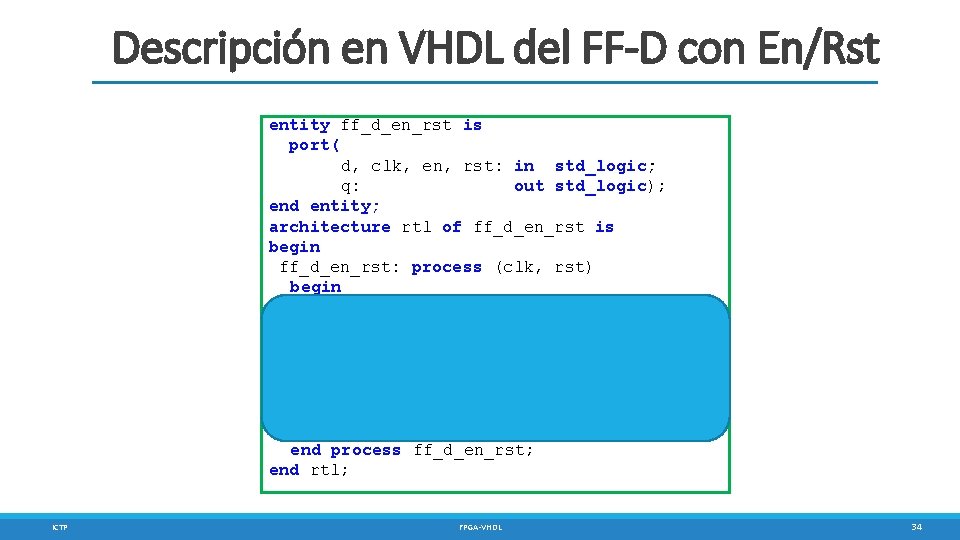

Descripción en VHDL del FF-D con En/Rst entity ff_d_en_rst is port( d, clk, en, rst: in std_logic; q: out std_logic); end entity; architecture rtl of ff_d_en_rst is begin ff_d_en_rst: process (clk, rst) begin if (rst=‘ 1’) then q <= ‘ 0’; elsif (rising_edge (clk)) then if (en=‘ 1’) then q <= d; end if; end process ff_d_en_rst; end rtl; ICTP FPGA-VHDL 34

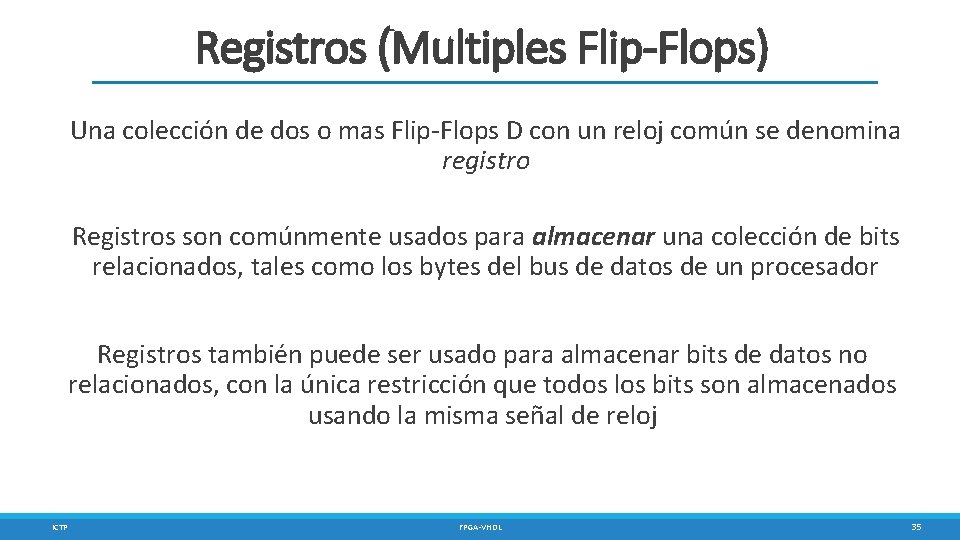

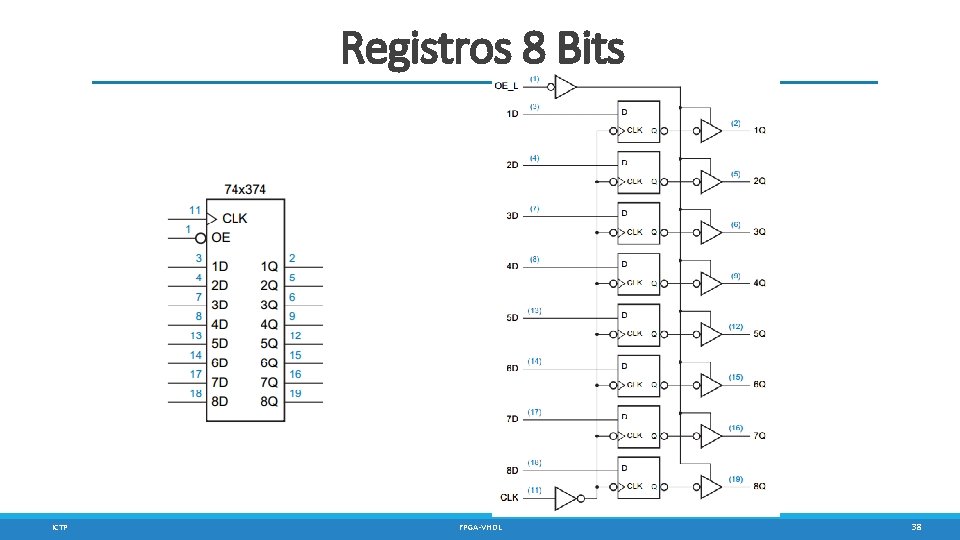

Registros (Multiples Flip-Flops) Una colección de dos o mas Flip-Flops D con un reloj común se denomina registro Registros son comúnmente usados para almacenar una colección de bits relacionados, tales como los bytes del bus de datos de un procesador Registros también puede ser usado para almacenar bits de datos no relacionados, con la única restricción que todos los bits son almacenados usando la misma señal de reloj ICTP FPGA-VHDL 35

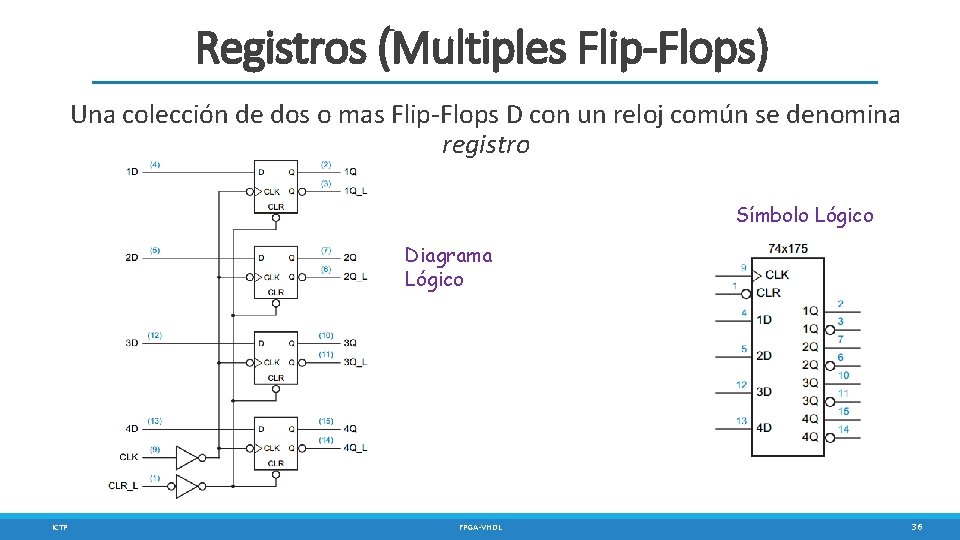

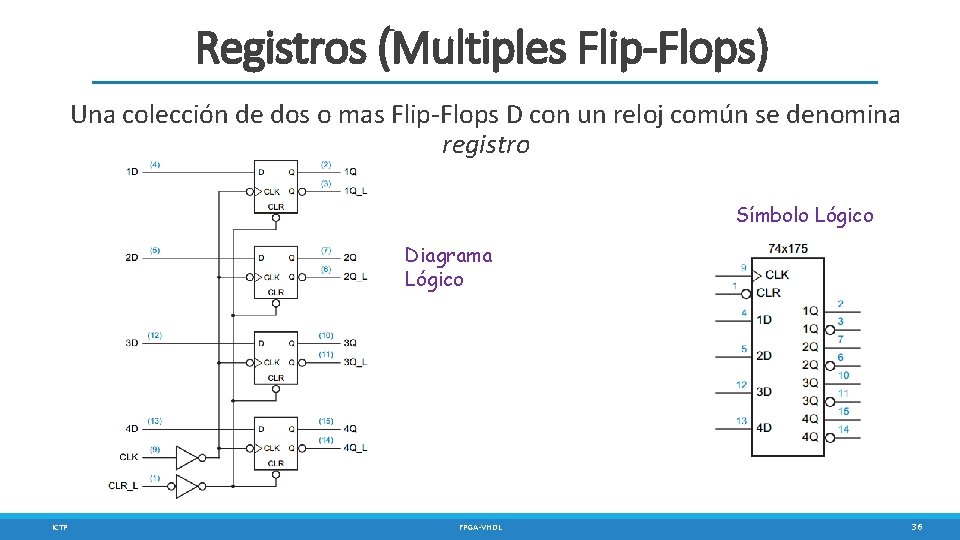

Registros (Multiples Flip-Flops) Una colección de dos o mas Flip-Flops D con un reloj común se denomina registro Símbolo Lógico Diagrama Lógico ICTP FPGA-VHDL 36

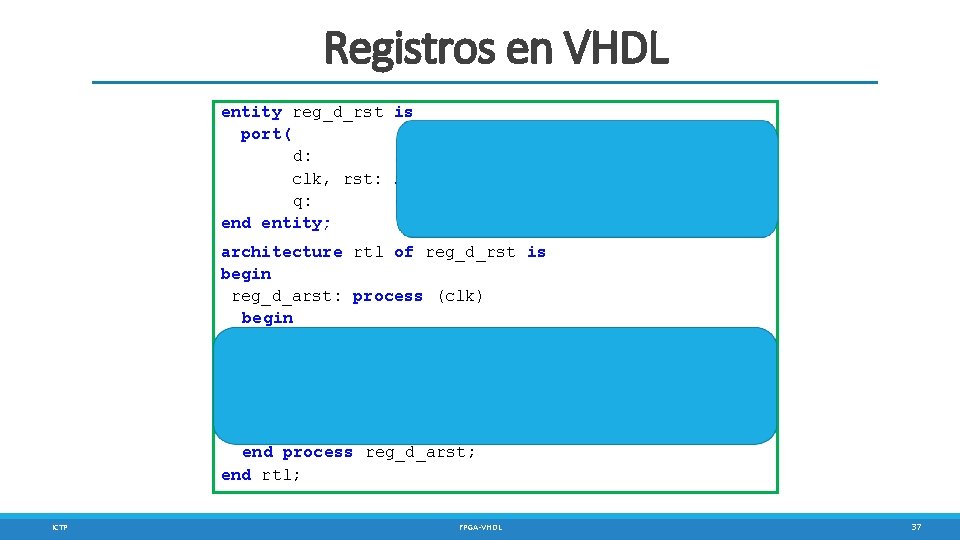

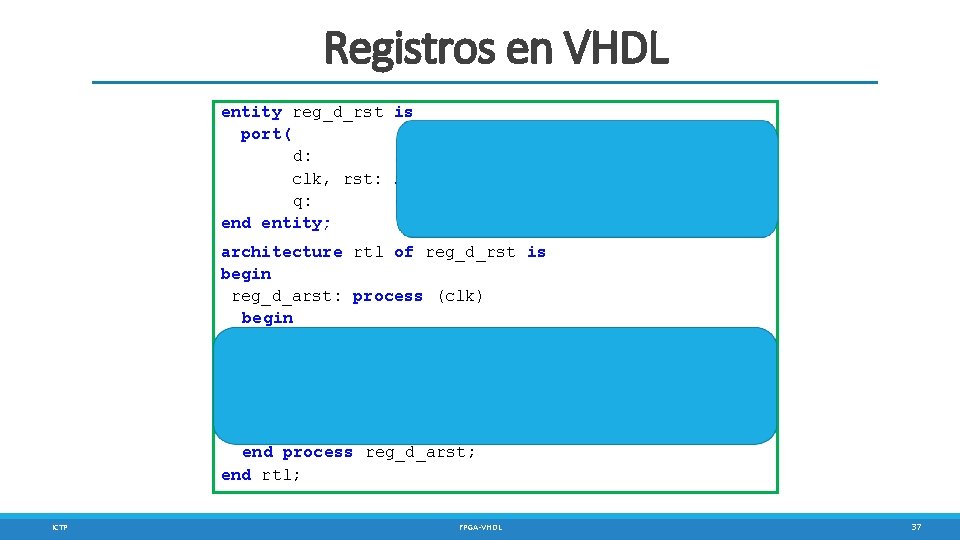

Registros en VHDL entity reg_d_rst port( d: clk, rst: q: end entity; is in std_logic_vector(7 downto 0); in std_logic; out std_logic_vector(7 downto 0)); architecture rtl of reg_d_rst is begin reg_d_arst: process (clk) begin if (rst=‘ 1’) then q <= (others =>‘ 0’); -- q <= ‘ 0000’ elsif(rising_edge (clk)) then q <= d; end if; end process reg_d_arst; end rtl; ICTP FPGA-VHDL 37

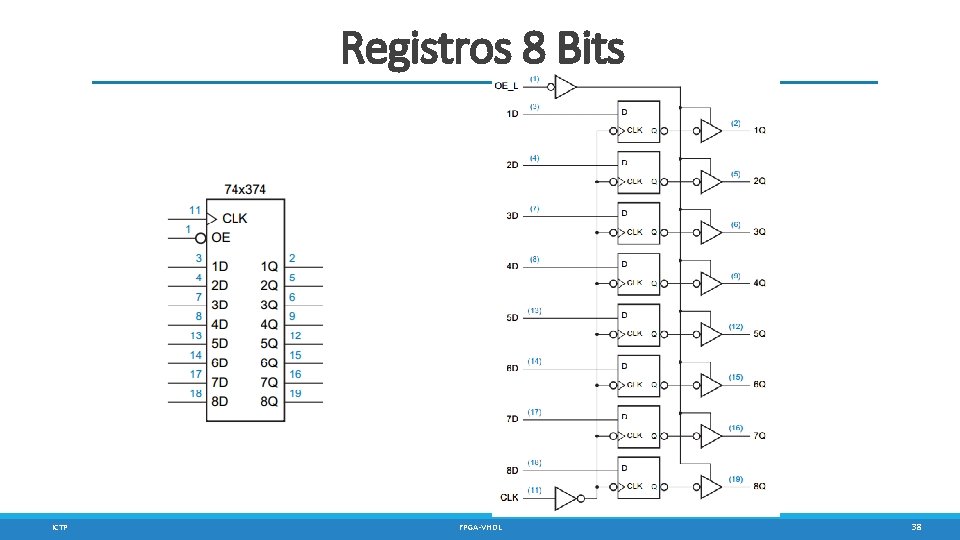

Registros 8 Bits ICTP FPGA-VHDL 38

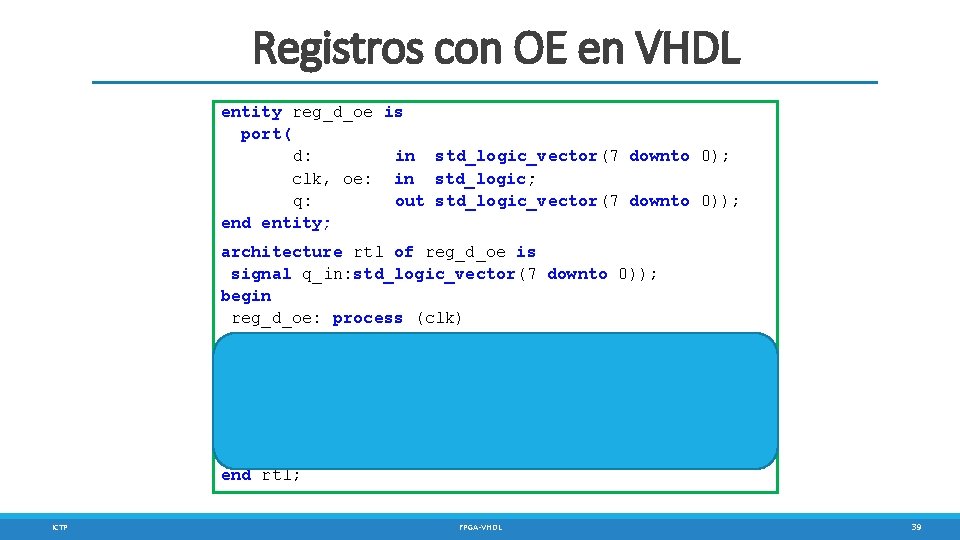

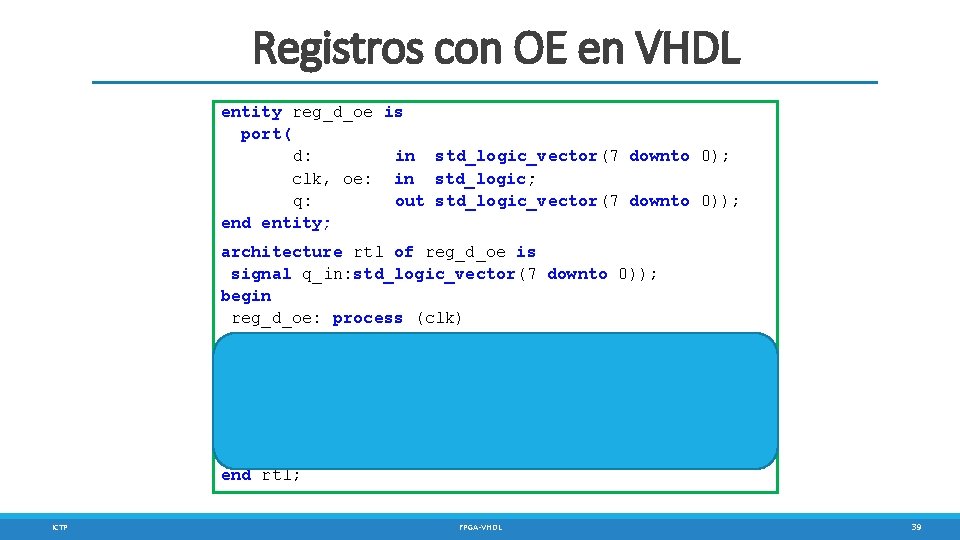

Registros con OE en VHDL entity reg_d_oe is port( d: in std_logic_vector(7 downto 0); clk, oe: in std_logic; q: out std_logic_vector(7 downto 0)); end entity; architecture rtl of reg_d_oe is signal q_in: std_logic_vector(7 downto 0)); begin reg_d_oe: process (clk) begin if(rising_edge (clk)) then q_in <= d; end if; end process reg_d_oe; q <= q_in when (oe= ‘ 1’) else (others => ‘Z’); end rtl; ICTP FPGA-VHDL 39

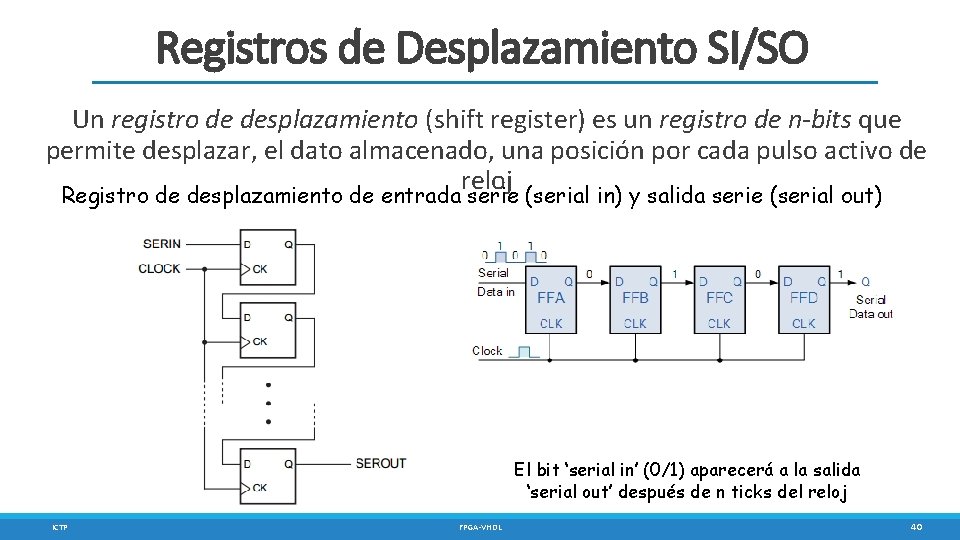

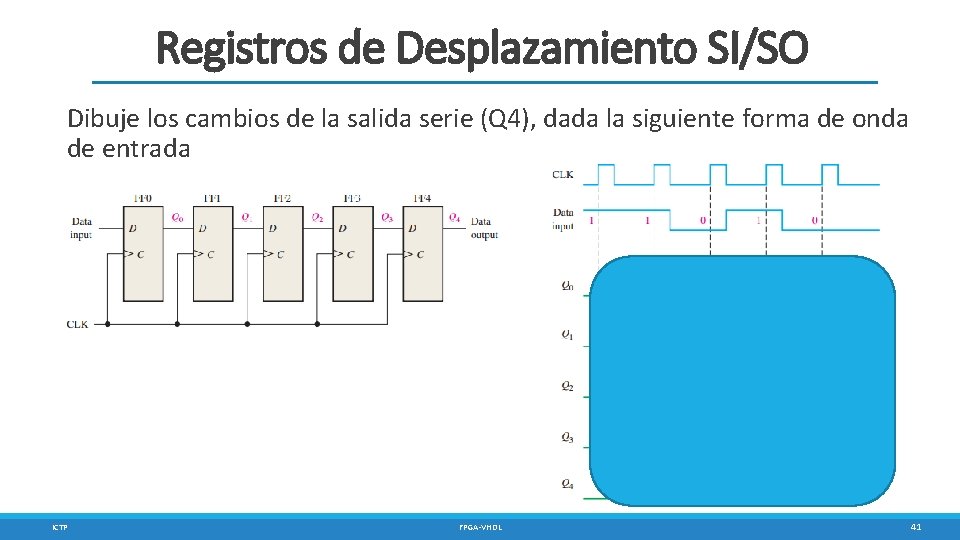

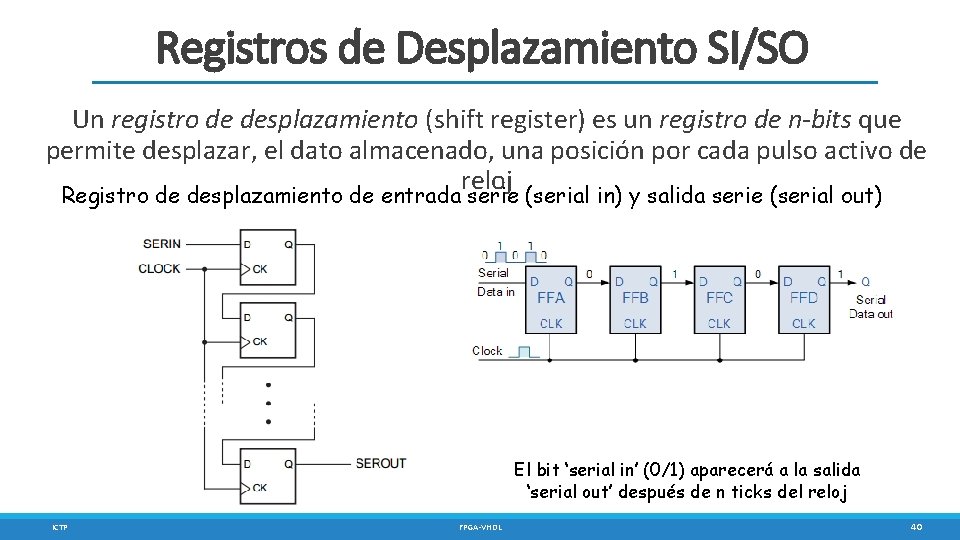

Registros de Desplazamiento SI/SO Un registro de desplazamiento (shift register) es un registro de n-bits que permite desplazar, el dato almacenado, una posición por cada pulso activo de reloj Registro de desplazamiento de entrada serie (serial in) y salida serie (serial out) El bit ‘serial in’ (0/1) aparecerá a la salida ‘serial out’ después de n ticks del reloj ICTP FPGA-VHDL 40

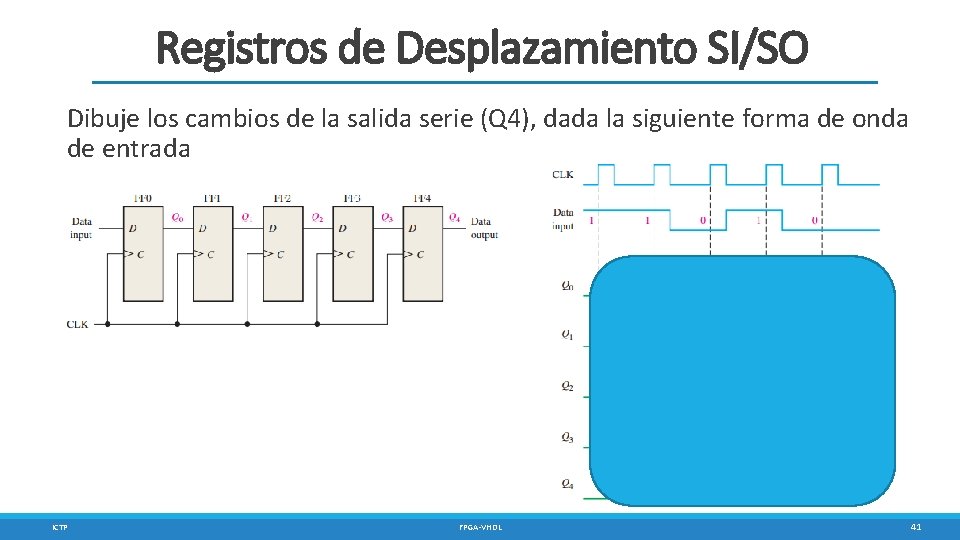

Registros de Desplazamiento SI/SO Dibuje los cambios de la salida serie (Q 4), dada la siguiente forma de onda de entrada ICTP FPGA-VHDL 41

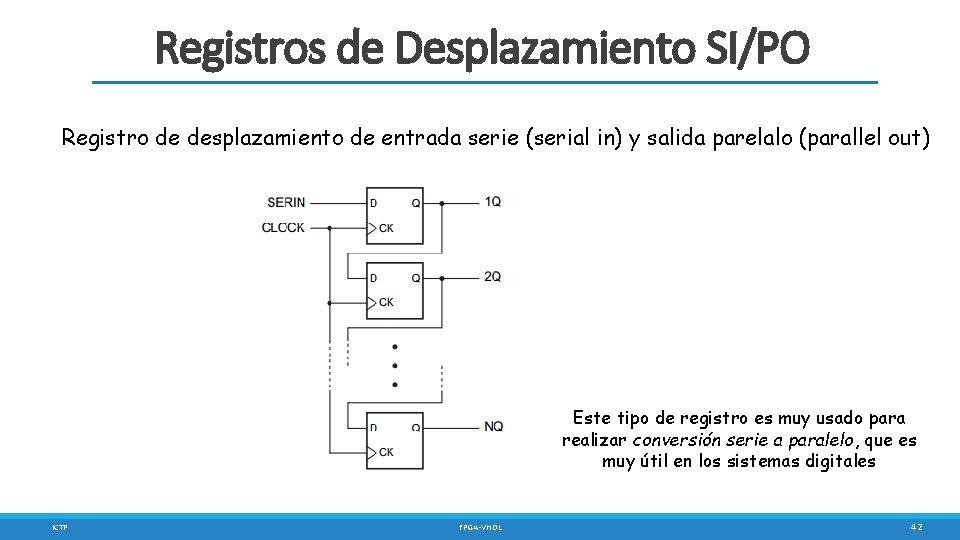

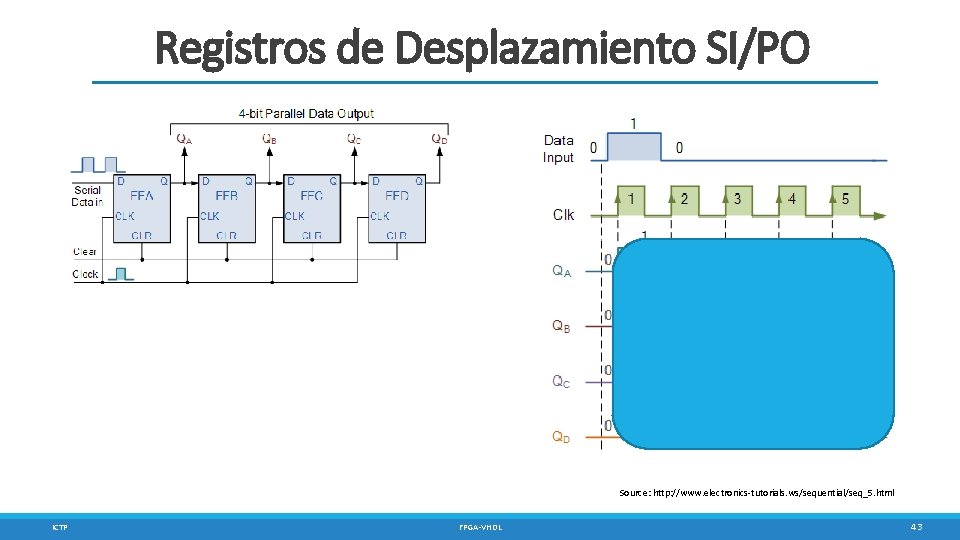

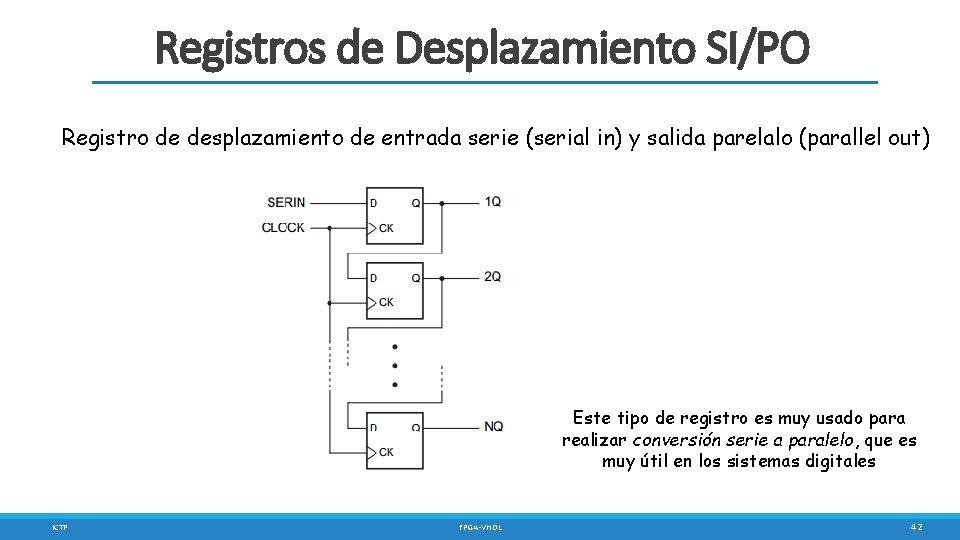

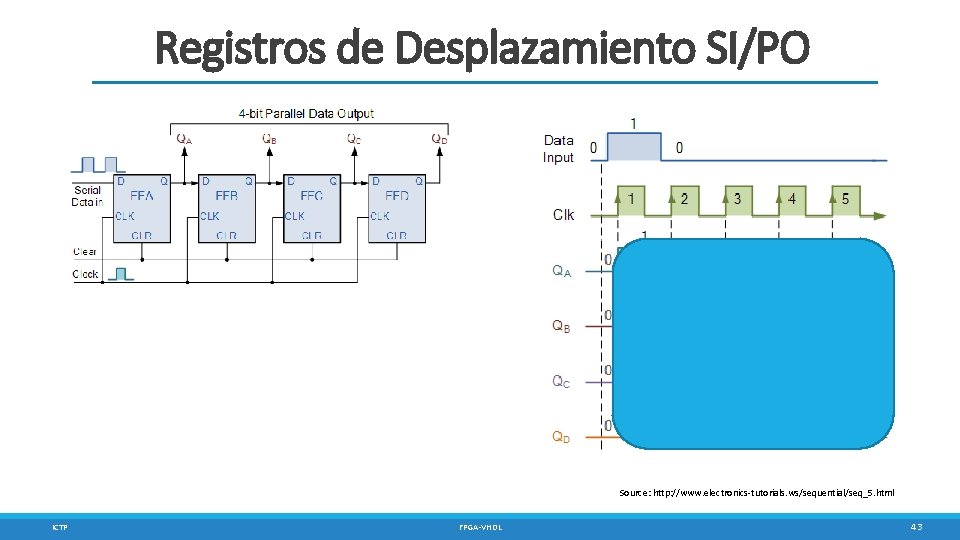

Registros de Desplazamiento SI/PO Registro de desplazamiento de entrada serie (serial in) y salida parelalo (parallel out) Este tipo de registro es muy usado para realizar conversión serie a paralelo, que es muy útil en los sistemas digitales ICTP FPGA-VHDL 42

Registros de Desplazamiento SI/PO Source: http: //www. electronics-tutorials. ws/sequential/seq_5. html ICTP FPGA-VHDL 43

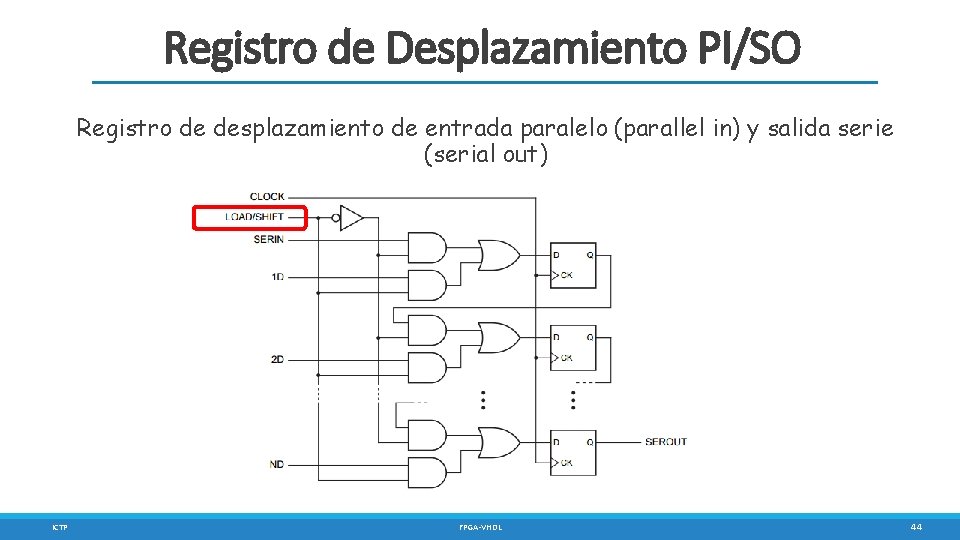

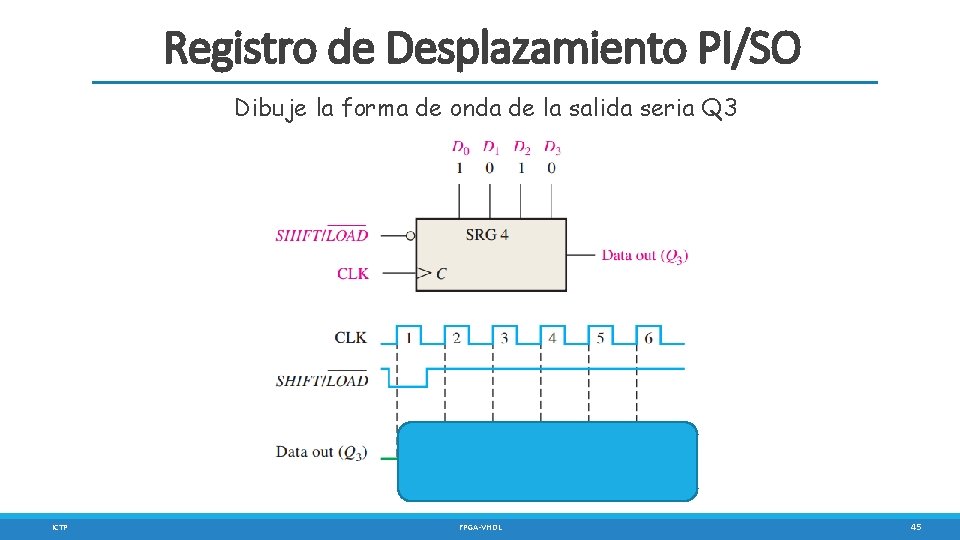

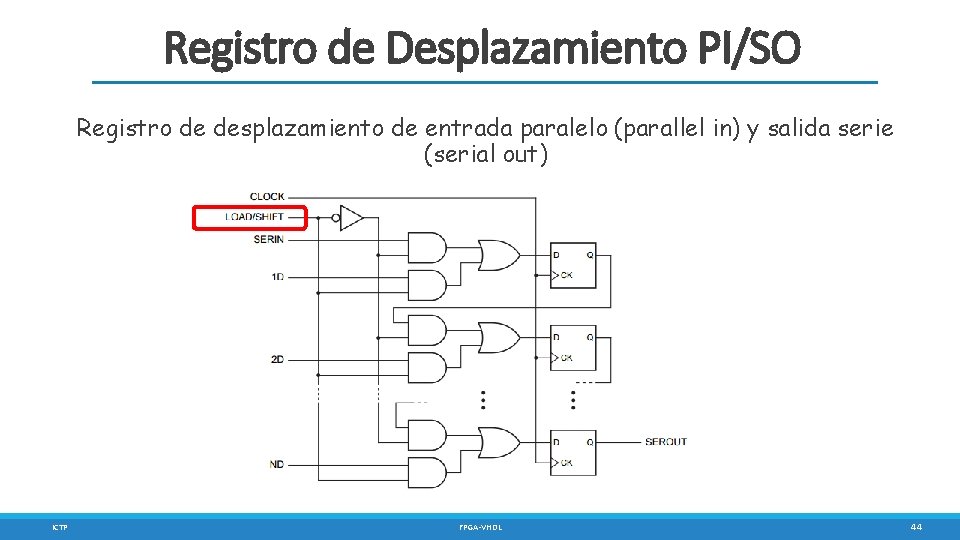

Registro de Desplazamiento PI/SO Registro de desplazamiento de entrada paralelo (parallel in) y salida serie (serial out) ICTP FPGA-VHDL 44

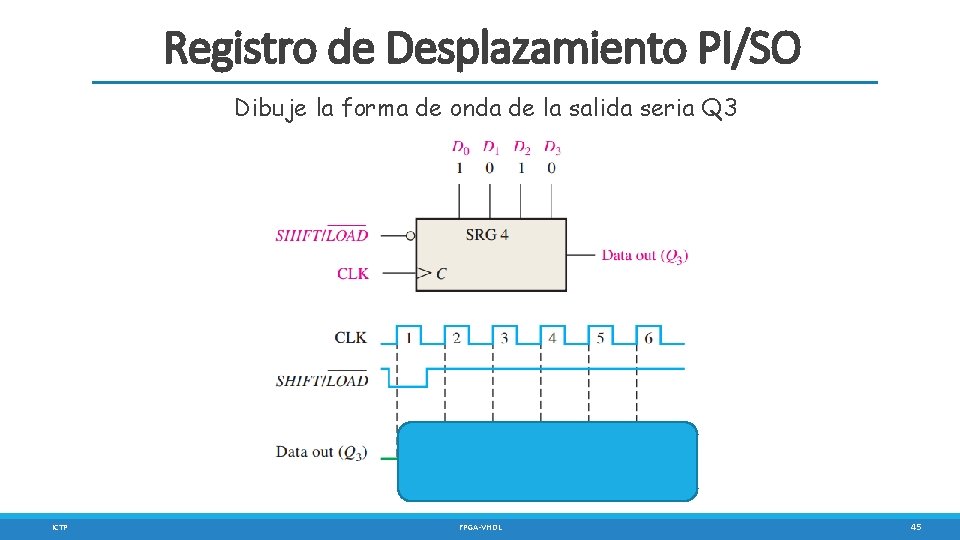

Registro de Desplazamiento PI/SO Dibuje la forma de onda de la salida seria Q 3 ICTP FPGA-VHDL 45

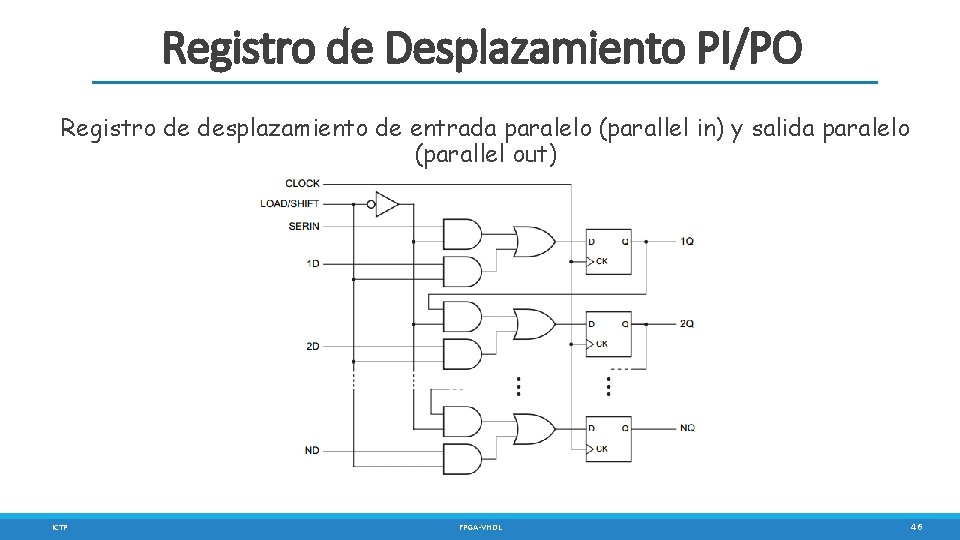

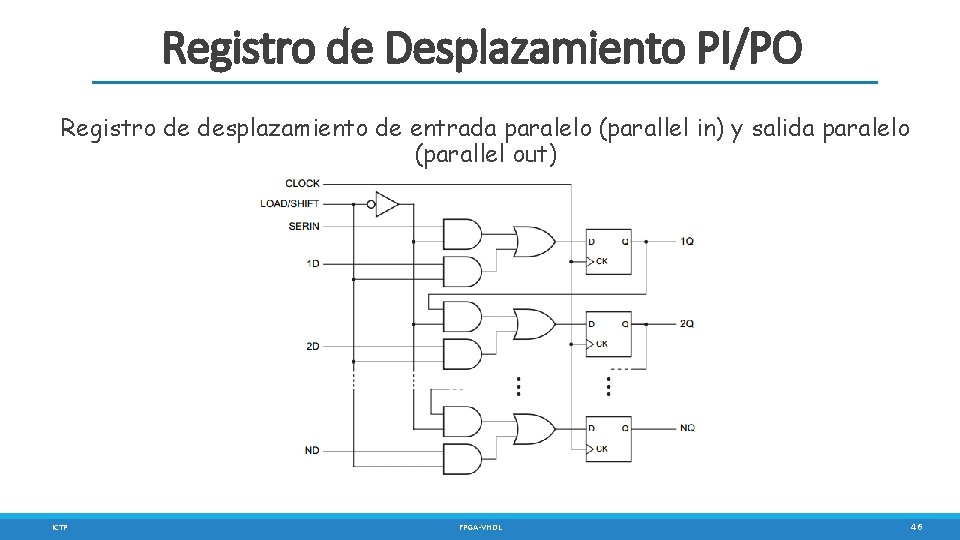

Registro de Desplazamiento PI/PO Registro de desplazamiento de entrada paralelo (parallel in) y salida paralelo (parallel out) ICTP FPGA-VHDL 46

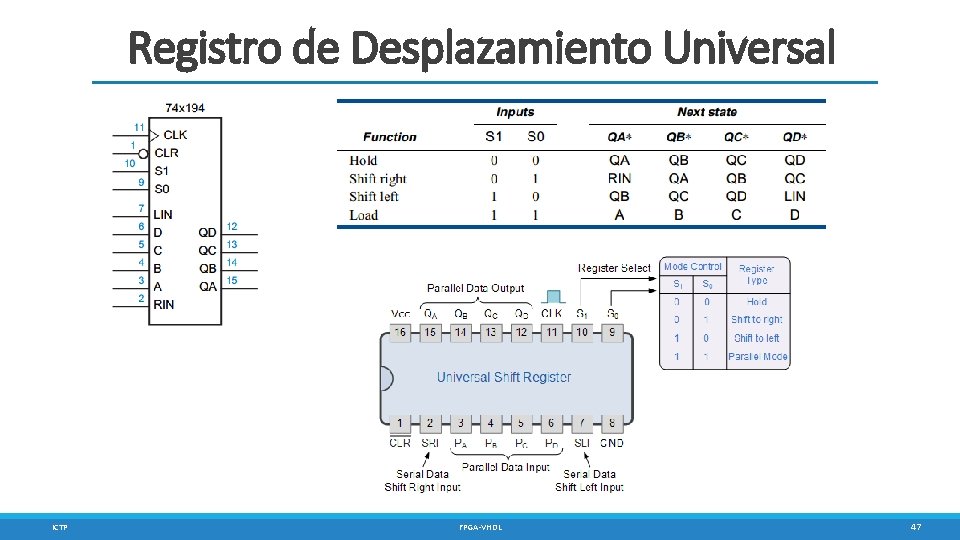

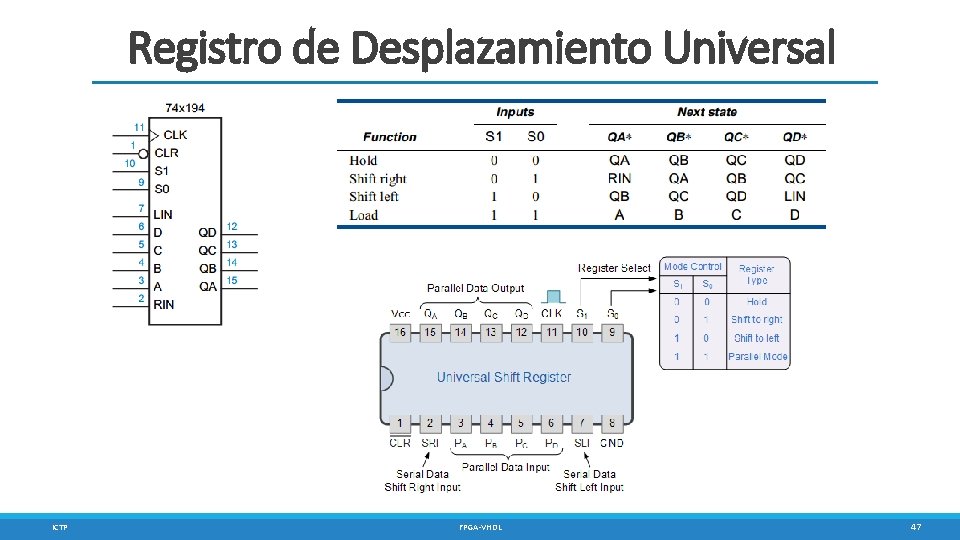

Registro de Desplazamiento Universal ICTP FPGA-VHDL 47

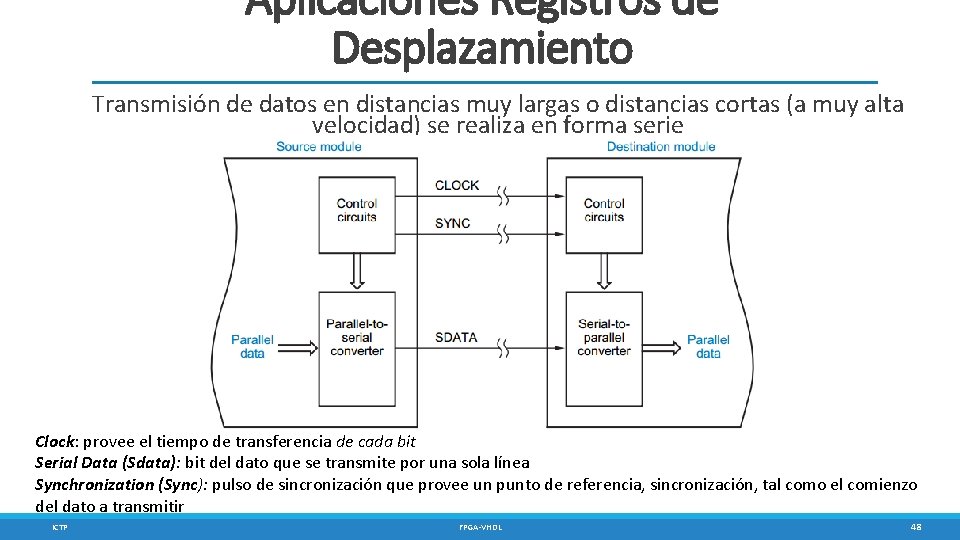

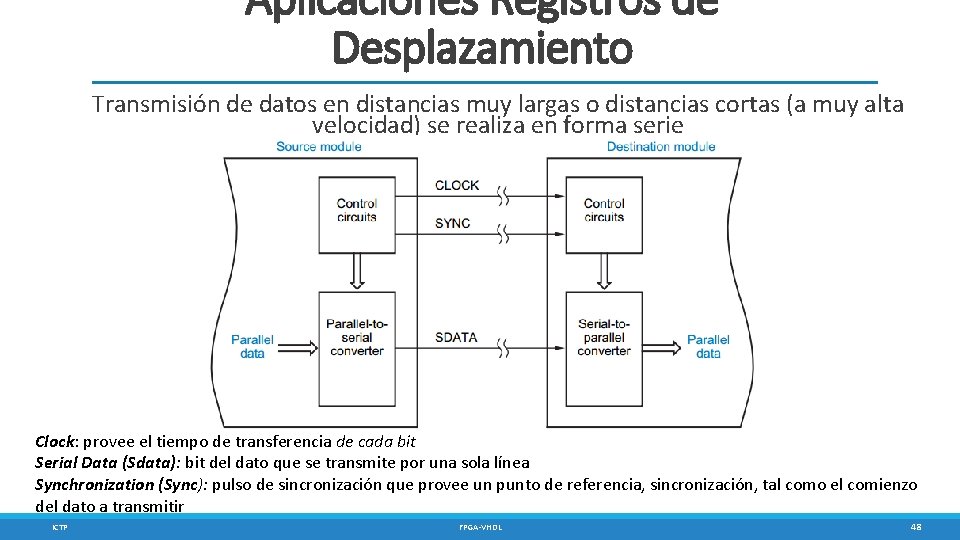

Aplicaciones Registros de Desplazamiento Transmisión de datos en distancias muy largas o distancias cortas (a muy alta velocidad) se realiza en forma serie Clock: provee el tiempo de transferencia de cada bit Serial Data (Sdata): bit del dato que se transmite por una sola línea Synchronization (Sync): pulso de sincronización que provee un punto de referencia, sincronización, tal como el comienzo del dato a transmitir ICTP FPGA-VHDL 48

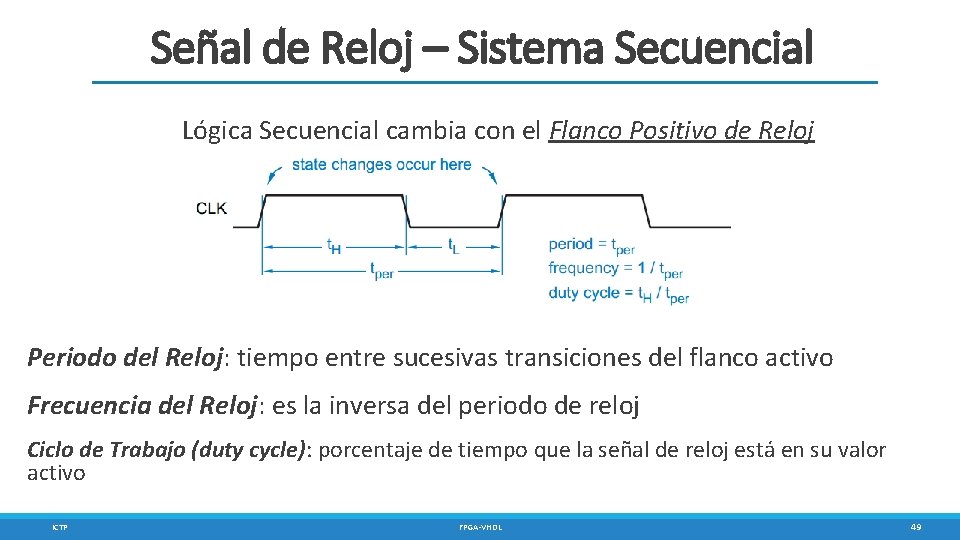

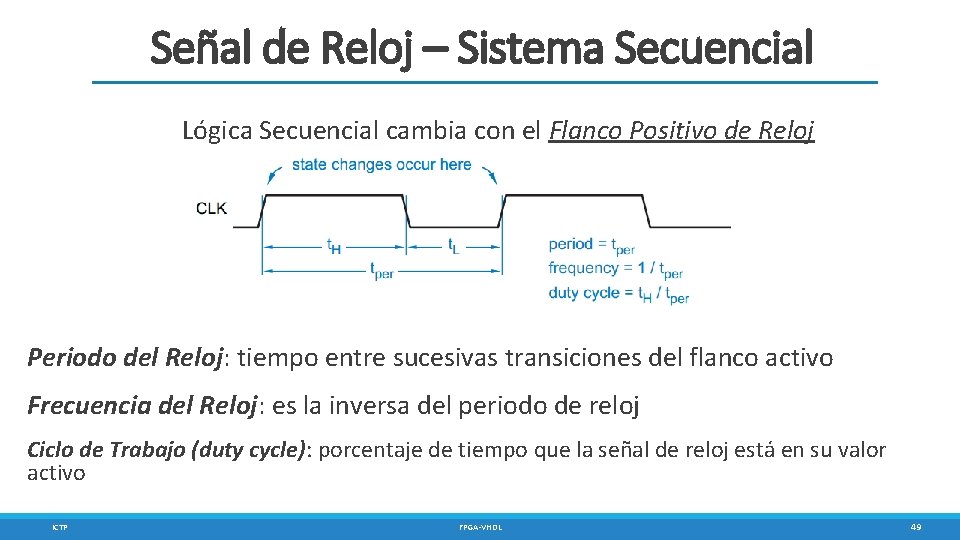

Señal de Reloj – Sistema Secuencial Lógica Secuencial cambia con el Flanco Positivo de Reloj Periodo del Reloj: tiempo entre sucesivas transiciones del flanco activo Frecuencia del Reloj: es la inversa del periodo de reloj Ciclo de Trabajo (duty cycle): porcentaje de tiempo que la señal de reloj está en su valor activo ICTP FPGA-VHDL 49

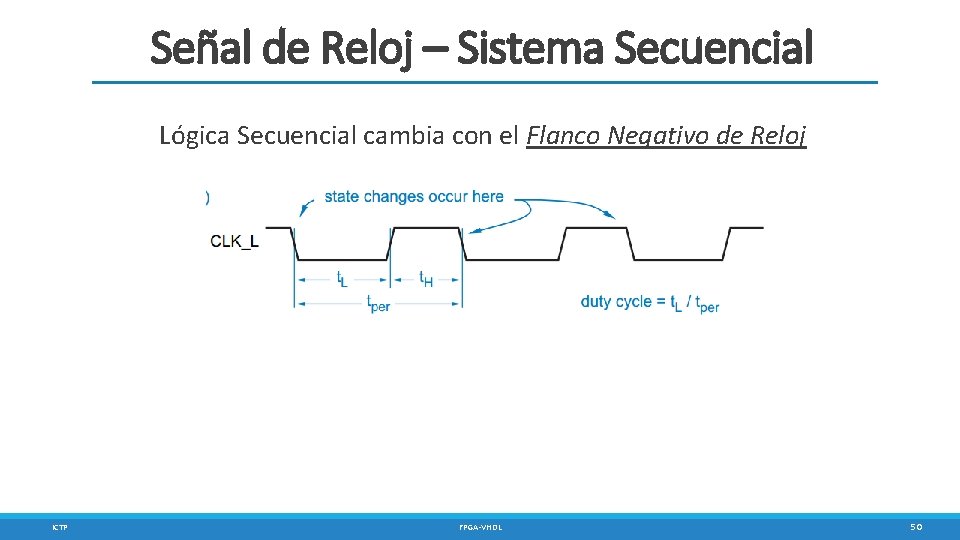

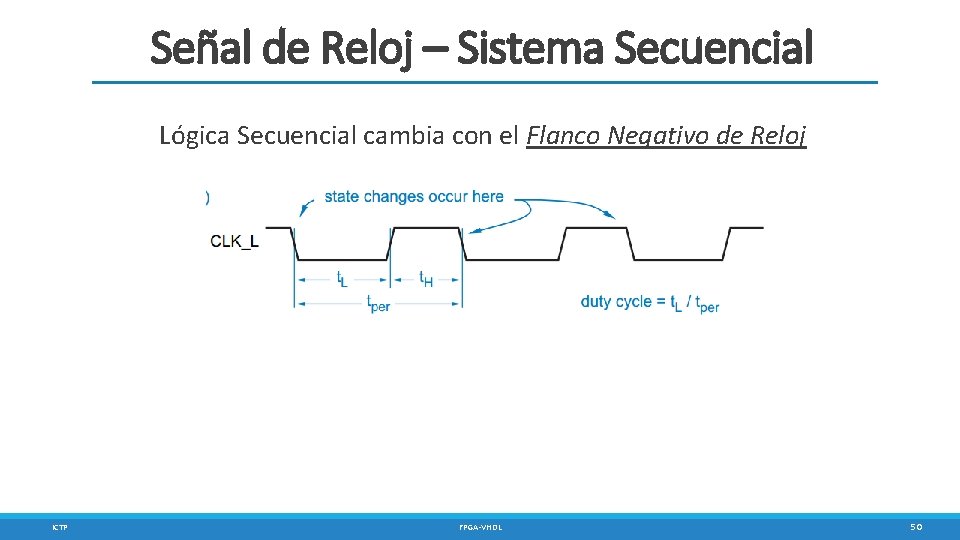

Señal de Reloj – Sistema Secuencial Lógica Secuencial cambia con el Flanco Negativo de Reloj ICTP FPGA-VHDL 50