VHDL Training PROGRAMMABLE LOGIC DESIGN WITH VHDL 1997

VHDL Training PROGRAMMABLE LOGIC DESIGN WITH VHDL © 1997 Cypress Semiconductor, rev 2. 5. 3 1

VHDL Training Objectives m Upon completion of this training, your VHDL knowledge will enable you to: q q Implement efficient combinatorial and sequential logic Design state machines and understand implementation trade-offs Use hierarchy / Create reusable components Identify how VHDL will synthesize and fit into a PLD or CPLD © 1997 Cypress Semiconductor, rev 2. 5. 3 2

VHDL Training Agenda m m m m Introduction, Why Use VHDL? PLD Design Flow VHDL Design Descriptions The Entity, Ports, Modes, Types Exercise #1 The Architecture, Architecture Styles VHDL Statements, Combinational Logic Processes, Signals vs. Variables VHDL Operators/Overloading/Inferencing Tri-State Logic, Don't Cares VHDL Identifiers Exercise #2, Exercise #3 Registers/Sequential Logic © 1997 Cypress Semiconductor, rev 2. 5. 3 3 m Wait Statement, Implicit Memory m Exercise #4 - Lunch m State Machines and State Encoding m Exercise #5 m Hierarchy (components, packages, and libraries) m Exercise #6 m Generate Statement m Multiplexing I/O pins m Exercise #7 m Attributes, Miscellaneous Topics, Wrap-up

VHDL Training Introduction m VHDL is used to: q document circuits q simulate circuits q synthesize design descriptions m Synthesis is the reduction of a design description to a lower-level representation (such as a netlist or a set of equations). m This training course covers VHDL for PLD synthesis m The course will at times draw upon the concepts of VHDL as a simulation language © 1997 Cypress Semiconductor, rev 2. 5. 3 4

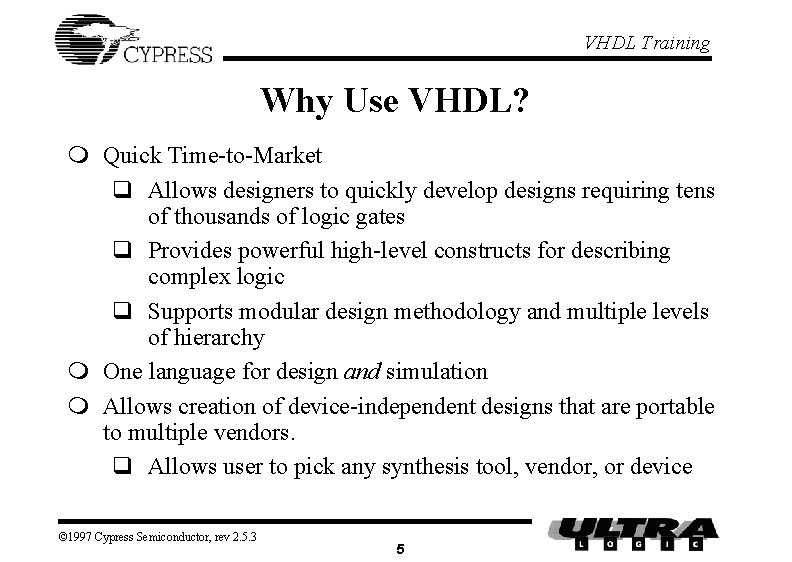

VHDL Training Why Use VHDL? m Quick Time-to-Market q Allows designers to quickly develop designs requiring tens of thousands of logic gates q Provides powerful high-level constructs for describing complex logic q Supports modular design methodology and multiple levels of hierarchy m One language for design and simulation m Allows creation of device-independent designs that are portable to multiple vendors. q Allows user to pick any synthesis tool, vendor, or device © 1997 Cypress Semiconductor, rev 2. 5. 3 5

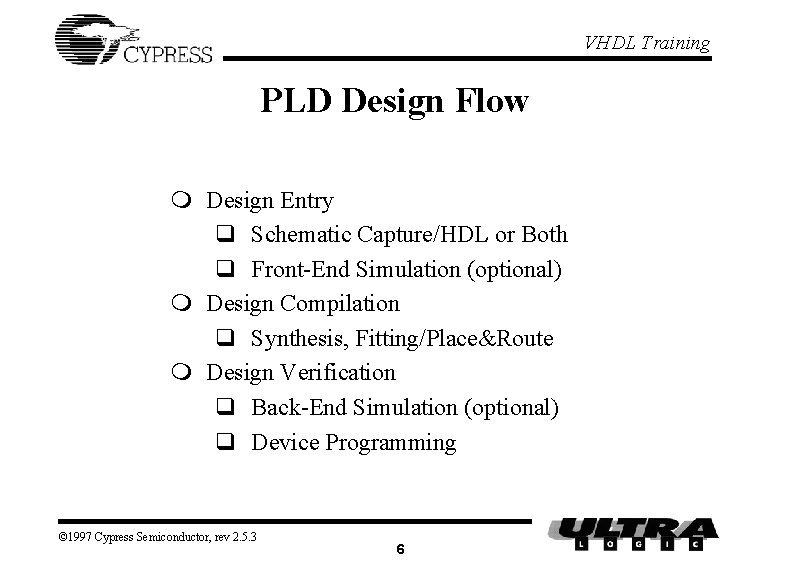

VHDL Training PLD Design Flow m Design Entry q Schematic Capture/HDL or Both q Front-End Simulation (optional) m Design Compilation q Synthesis, Fitting/Place&Route m Design Verification q Back-End Simulation (optional) q Device Programming © 1997 Cypress Semiconductor, rev 2. 5. 3 6

VHDL Training Design Entry Schematic Text Simulation Front End Synthesis Design Compilation Fitting Place&Route Sim. Model Design Verification JEDEC File Simulation Programmer © 1997 Cypress Semiconductor, rev 2. 5. 3 7 Prog. File Back End

VHDL Training VHDL Design Descriptions m VHDL design descriptions (referred to as "design entities") consist of an ENTITY declaration and ARCHITECTURE body pair q The ENTITY declaration describes the design I/O q The ARCHITECTURE body describes the content of the design © 1997 Cypress Semiconductor, rev 2. 5. 3 8

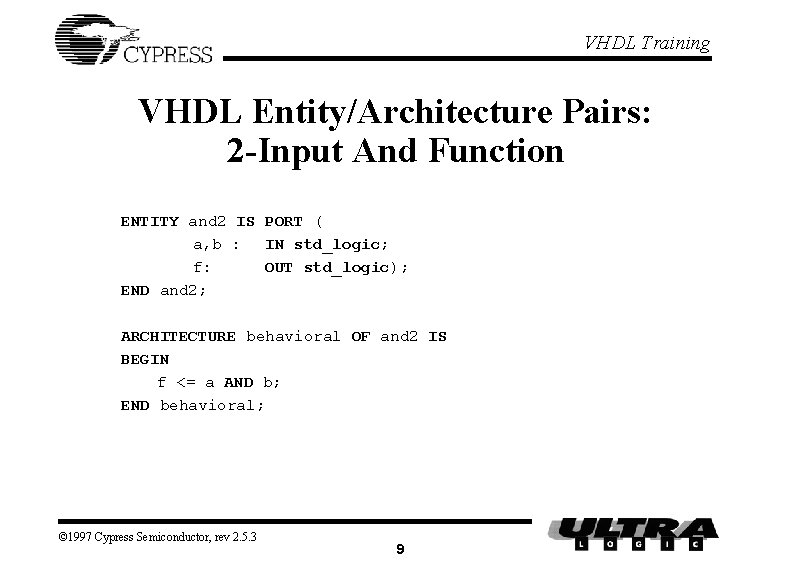

VHDL Training VHDL Entity/Architecture Pairs: 2 -Input And Function ENTITY and 2 IS PORT ( a, b : IN std_logic; f: OUT std_logic); END and 2; ARCHITECTURE behavioral OF and 2 IS BEGIN f <= a AND b; END behavioral; © 1997 Cypress Semiconductor, rev 2. 5. 3 9

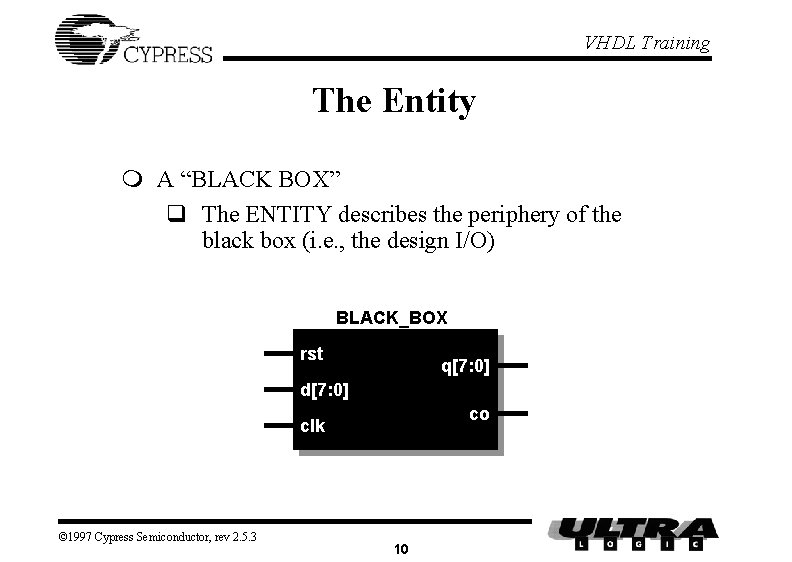

VHDL Training The Entity m A “BLACK BOX” q The ENTITY describes the periphery of the black box (i. e. , the design I/O) BLACK_BOX rst q[7: 0] d[7: 0] co clk © 1997 Cypress Semiconductor, rev 2. 5. 3 10

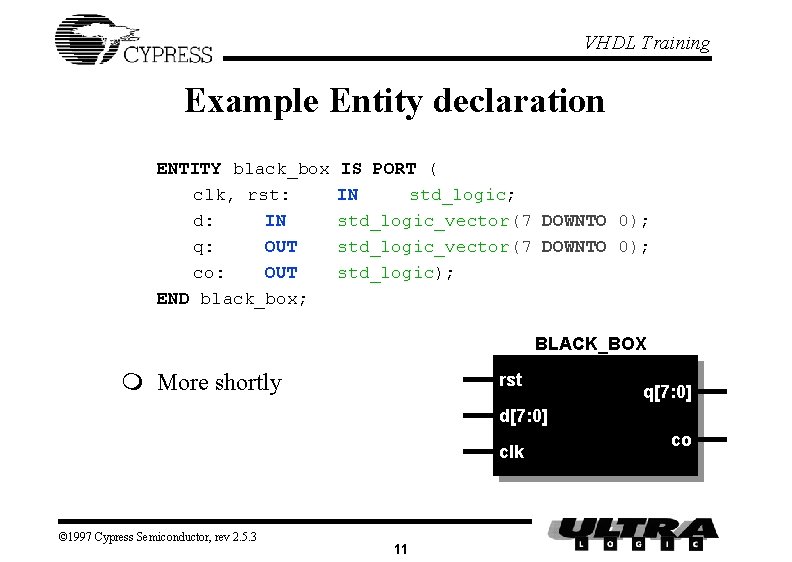

VHDL Training Example Entity declaration ENTITY black_box clk, rst: d: IN q: OUT co: OUT END black_box; IS PORT ( IN std_logic; std_logic_vector(7 DOWNTO 0); std_logic); BLACK_BOX m More shortly rst q[7: 0] d[7: 0] clk © 1997 Cypress Semiconductor, rev 2. 5. 3 11 co

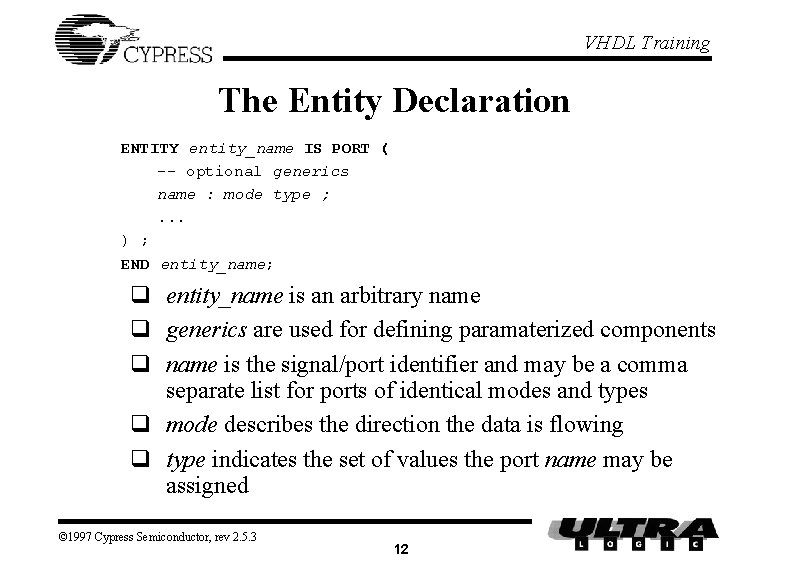

VHDL Training The Entity Declaration ENTITY entity_name IS PORT ( -- optional generics name : mode type ; . . . ) ; END entity_name; q entity_name is an arbitrary name q generics are used for defining paramaterized components q name is the signal/port identifier and may be a comma separate list for ports of identical modes and types q mode describes the direction the data is flowing q type indicates the set of values the port name may be assigned © 1997 Cypress Semiconductor, rev 2. 5. 3 12

VHDL Training Ports m The Entity (“BLACK BOX”) has PORTS q PORTS are points of communication • PORTS are often associated with the device pins q PORTS are a special class of SIGNAL q PORTS have an associated SIGNAL name, mode, and type © 1997 Cypress Semiconductor, rev 2. 5. 3 13

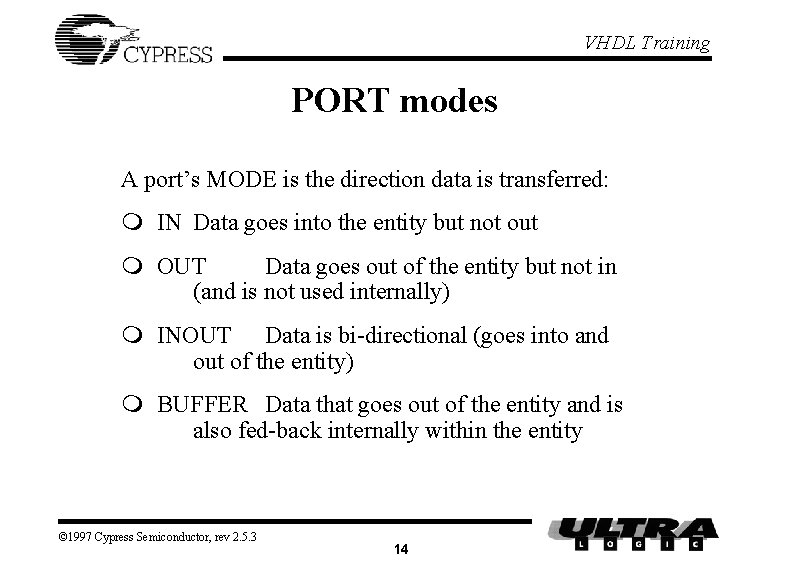

VHDL Training PORT modes A port’s MODE is the direction data is transferred: m IN Data goes into the entity but not out m OUT Data goes out of the entity but not in (and is not used internally) m INOUT Data is bi-directional (goes into and out of the entity) m BUFFER Data that goes out of the entity and is also fed-back internally within the entity © 1997 Cypress Semiconductor, rev 2. 5. 3 14

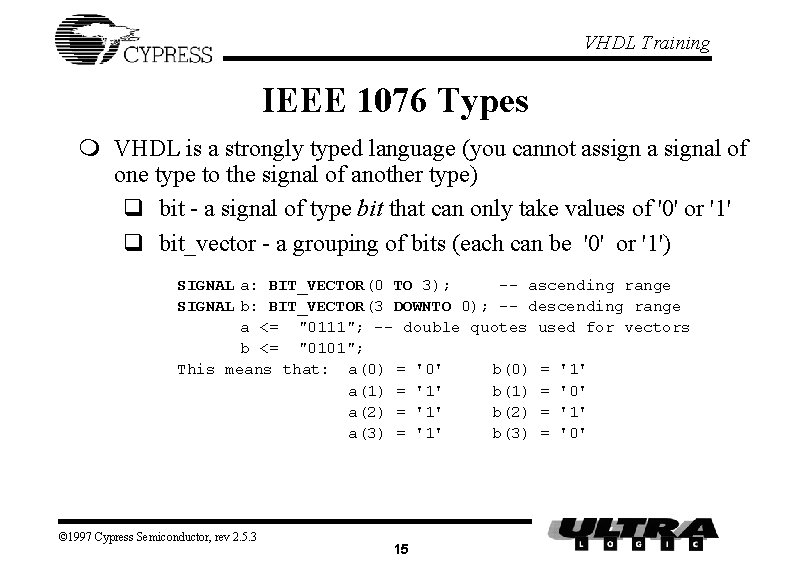

VHDL Training IEEE 1076 Types m VHDL is a strongly typed language (you cannot assign a signal of one type to the signal of another type) q bit - a signal of type bit that can only take values of '0' or '1' q bit_vector - a grouping of bits (each can be '0' or '1') SIGNAL a: BIT_VECTOR(0 TO 3); -- ascending range SIGNAL b: BIT_VECTOR(3 DOWNTO 0); -- descending range a <= "0111"; -- double quotes used for vectors b <= "0101"; This means that: a(0) = '0' b(0) = '1' a(1) = '1' b(1) = '0' a(2) = '1' b(2) = '1' a(3) = '1' b(3) = '0' © 1997 Cypress Semiconductor, rev 2. 5. 3 15

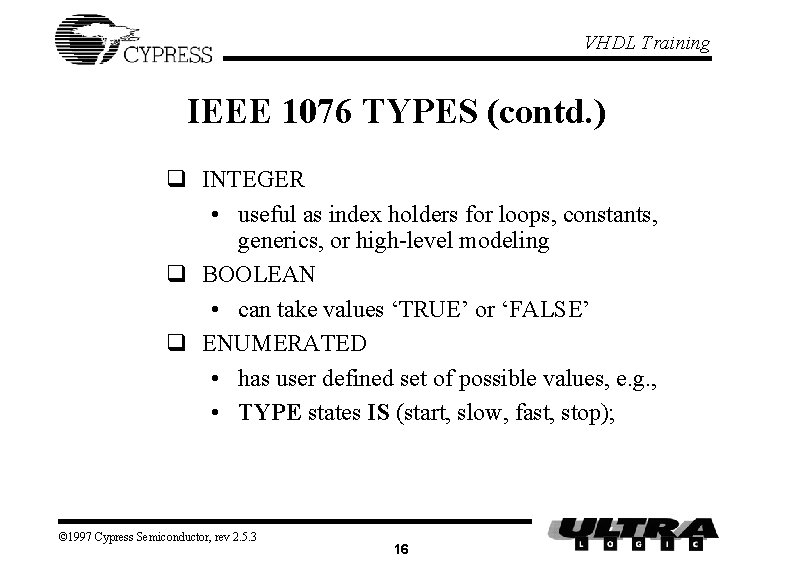

VHDL Training IEEE 1076 TYPES (contd. ) q INTEGER • useful as index holders for loops, constants, generics, or high-level modeling q BOOLEAN • can take values ‘TRUE’ or ‘FALSE’ q ENUMERATED • has user defined set of possible values, e. g. , • TYPE states IS (start, slow, fast, stop); © 1997 Cypress Semiconductor, rev 2. 5. 3 16

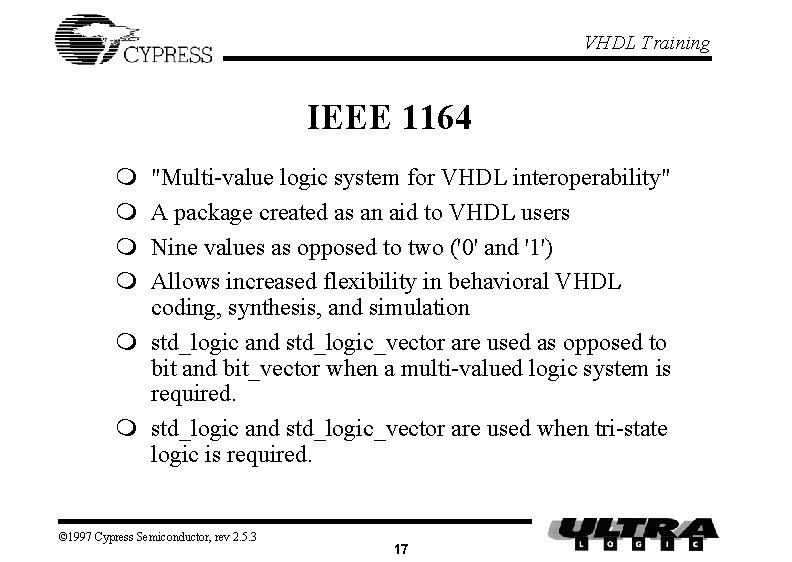

VHDL Training IEEE 1164 m m "Multi-value logic system for VHDL interoperability" A package created as an aid to VHDL users Nine values as opposed to two ('0' and '1') Allows increased flexibility in behavioral VHDL coding, synthesis, and simulation m std_logic and std_logic_vector are used as opposed to bit and bit_vector when a multi-valued logic system is required. m std_logic and std_logic_vector are used when tri-state logic is required. © 1997 Cypress Semiconductor, rev 2. 5. 3 17

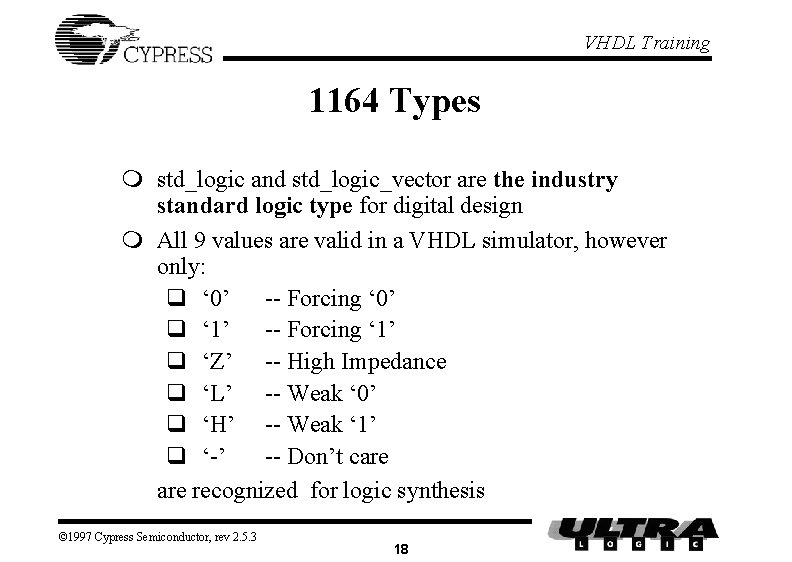

VHDL Training 1164 Types m std_logic and std_logic_vector are the industry standard logic type for digital design m All 9 values are valid in a VHDL simulator, however only: q ‘ 0’ -- Forcing ‘ 0’ q ‘ 1’ -- Forcing ‘ 1’ q ‘Z’ -- High Impedance q ‘L’ -- Weak ‘ 0’ q ‘H’ -- Weak ‘ 1’ q ‘-’ -- Don’t care recognized for logic synthesis © 1997 Cypress Semiconductor, rev 2. 5. 3 18

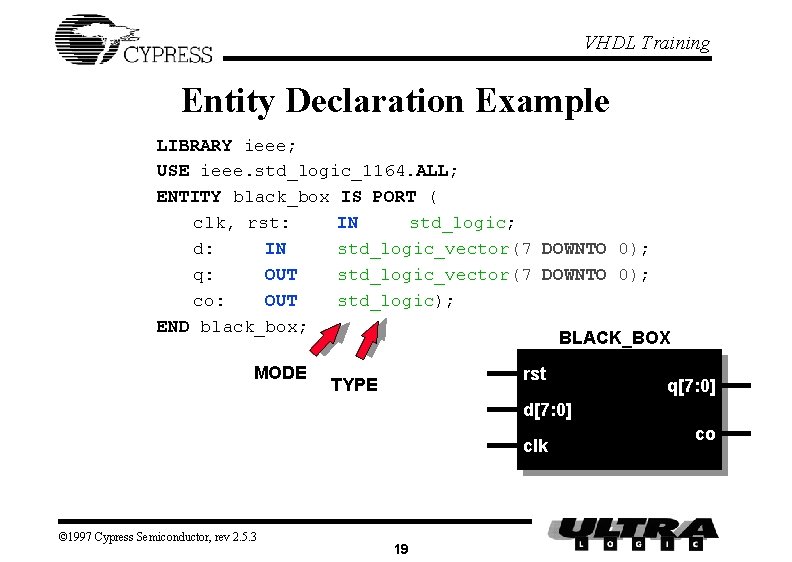

VHDL Training Entity Declaration Example LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY black_box IS PORT ( clk, rst: IN std_logic; d: IN std_logic_vector(7 DOWNTO 0); q: OUT std_logic_vector(7 DOWNTO 0); co: OUT std_logic); END black_box; BLACK_BOX MODE rst TYPE q[7: 0] d[7: 0] clk © 1997 Cypress Semiconductor, rev 2. 5. 3 19 co

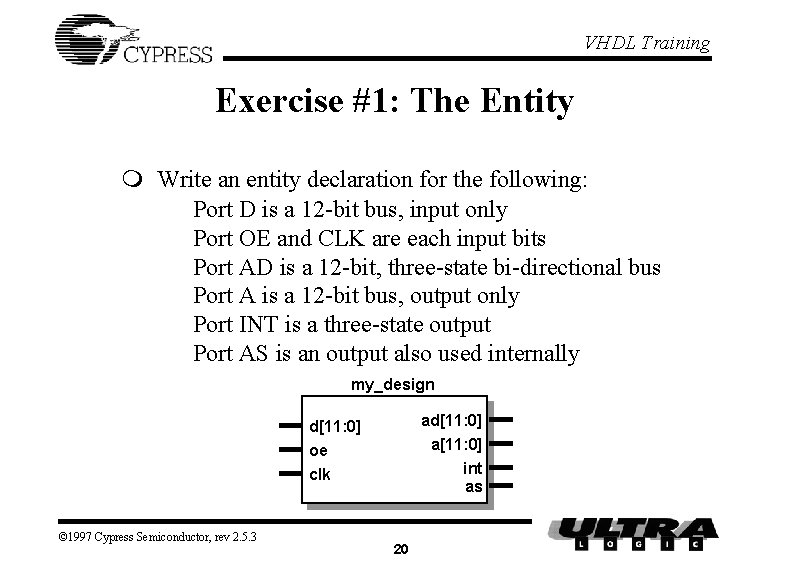

VHDL Training Exercise #1: The Entity m Write an entity declaration for the following: Port D is a 12 -bit bus, input only Port OE and CLK are each input bits Port AD is a 12 -bit, three-state bi-directional bus Port A is a 12 -bit bus, output only Port INT is a three-state output Port AS is an output also used internally my_design ad[11: 0] a[11: 0] int as d[11: 0] oe clk © 1997 Cypress Semiconductor, rev 2. 5. 3 20

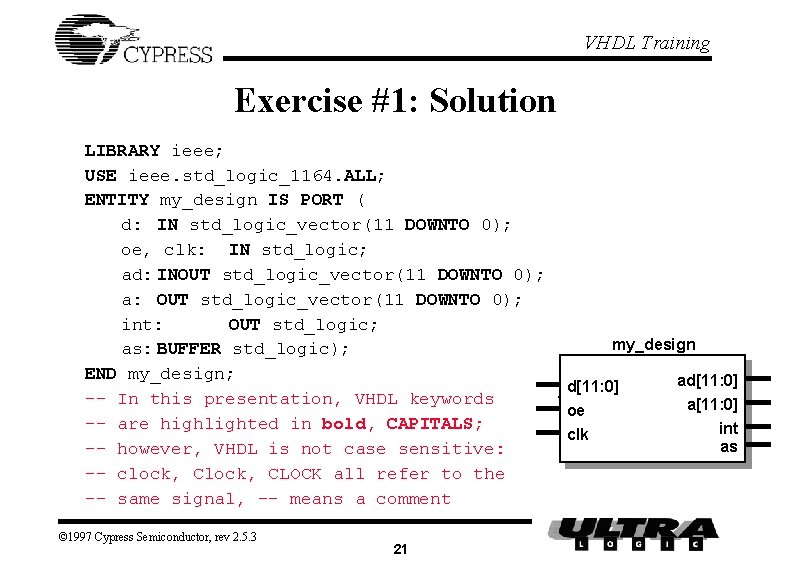

VHDL Training Exercise #1: Solution LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY my_design IS PORT ( d: IN std_logic_vector(11 DOWNTO 0); oe, clk: IN std_logic; ad: INOUT std_logic_vector(11 DOWNTO 0); a: OUT std_logic_vector(11 DOWNTO 0); int: OUT std_logic; as: BUFFER std_logic); END my_design; -- In this presentation, VHDL keywords -- are highlighted in bold, CAPITALS; -- however, VHDL is not case sensitive: -- clock, CLOCK all refer to the -- same signal, -- means a comment © 1997 Cypress Semiconductor, rev 2. 5. 3 21 my_design d[11: 0] oe clk ad[11: 0] a[11: 0] int as

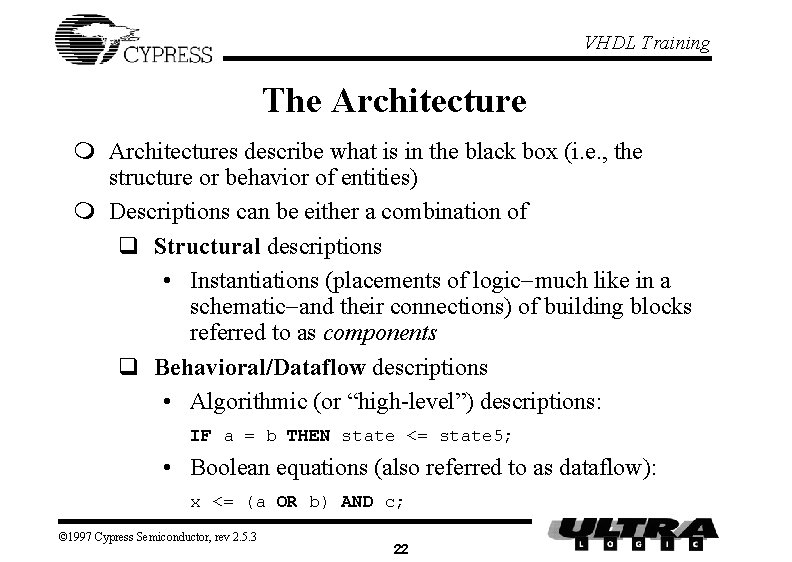

VHDL Training The Architecture m Architectures describe what is in the black box (i. e. , the structure or behavior of entities) m Descriptions can be either a combination of q Structural descriptions • Instantiations (placements of logic-much like in a schematic-and their connections) of building blocks referred to as components q Behavioral/Dataflow descriptions • Algorithmic (or “high-level”) descriptions: IF a = b THEN state <= state 5; • Boolean equations (also referred to as dataflow): x <= (a OR b) AND c; © 1997 Cypress Semiconductor, rev 2. 5. 3 22

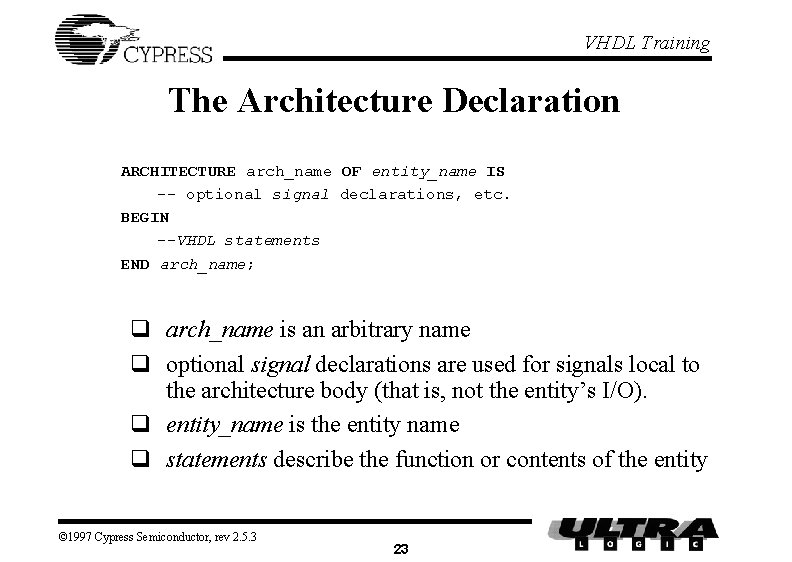

VHDL Training The Architecture Declaration ARCHITECTURE arch_name OF entity_name IS -- optional signal declarations, etc. BEGIN --VHDL statements END arch_name; q arch_name is an arbitrary name q optional signal declarations are used for signals local to the architecture body (that is, not the entity’s I/O). q entity_name is the entity name q statements describe the function or contents of the entity © 1997 Cypress Semiconductor, rev 2. 5. 3 23

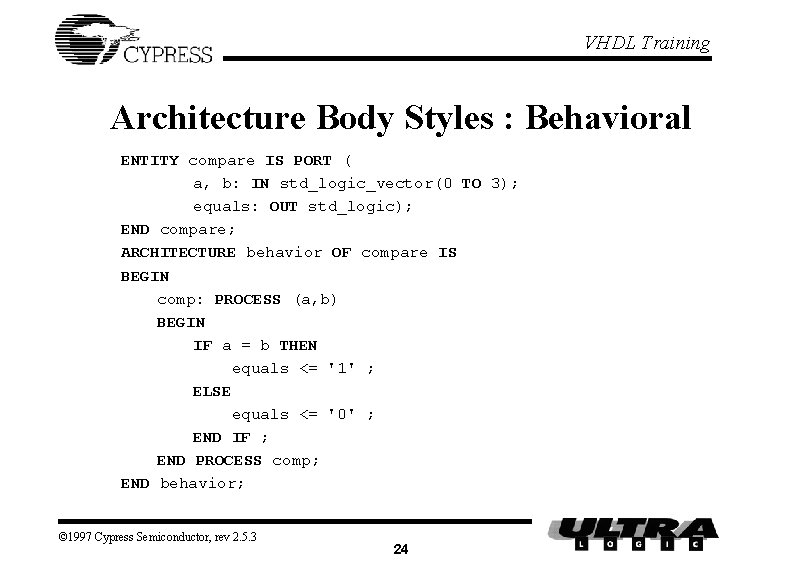

VHDL Training Architecture Body Styles : Behavioral ENTITY compare IS PORT ( a, b: IN std_logic_vector(0 TO 3); equals: OUT std_logic); END compare; ARCHITECTURE behavior OF compare IS BEGIN comp: PROCESS (a, b) BEGIN IF a = b THEN equals <= '1' ; ELSE equals <= '0' ; END IF ; END PROCESS comp; END behavior; © 1997 Cypress Semiconductor, rev 2. 5. 3 24

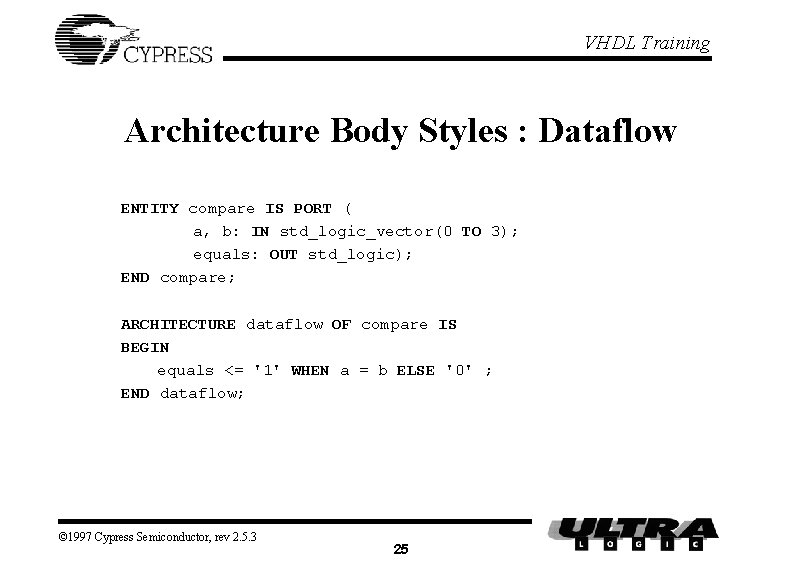

VHDL Training Architecture Body Styles : Dataflow ENTITY compare IS PORT ( a, b: IN std_logic_vector(0 TO 3); equals: OUT std_logic); END compare; ARCHITECTURE dataflow OF compare IS BEGIN equals <= '1' WHEN a = b ELSE '0' ; END dataflow; © 1997 Cypress Semiconductor, rev 2. 5. 3 25

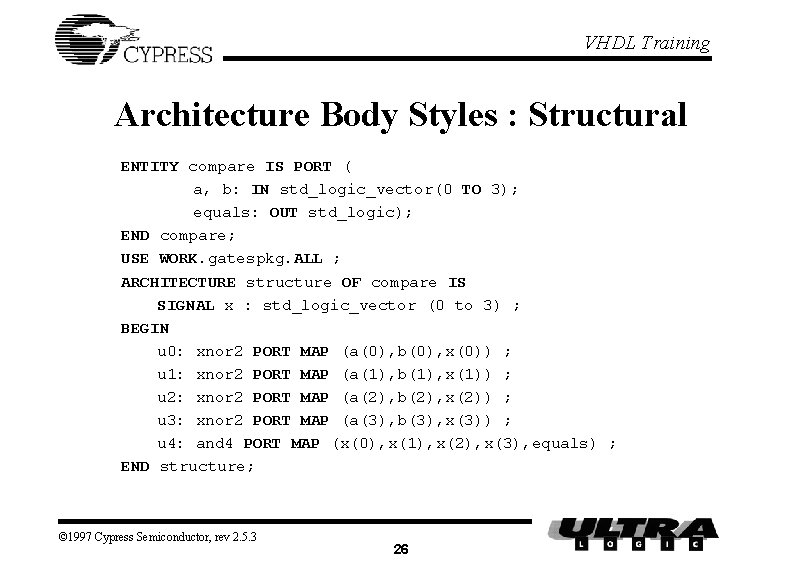

VHDL Training Architecture Body Styles : Structural ENTITY compare IS PORT ( a, b: IN std_logic_vector(0 TO 3); equals: OUT std_logic); END compare; USE WORK. gatespkg. ALL ; ARCHITECTURE structure OF compare IS SIGNAL x : std_logic_vector (0 to 3) ; BEGIN u 0: xnor 2 PORT MAP (a(0), b(0), x(0)) ; u 1: xnor 2 PORT MAP (a(1), b(1), x(1)) ; u 2: xnor 2 PORT MAP (a(2), b(2), x(2)) ; u 3: xnor 2 PORT MAP (a(3), b(3), x(3)) ; u 4: and 4 PORT MAP (x(0), x(1), x(2), x(3), equals) ; END structure; © 1997 Cypress Semiconductor, rev 2. 5. 3 26

VHDL Training Comparing Architecture Styles m These examples synthesize to equivalent circuits m In more elaborate designs, some descriptions may yield more efficient circuits q sloppy code = inefficient results (see section 3. 3. 4) m Use styles that make your designs easier to describe and maintain q Behavioral/Dataflow exploit module generation (described later) q Structural descriptions may make the design less portable (may rely on a library of vendor-specific components) © 1997 Cypress Semiconductor, rev 2. 5. 3 27

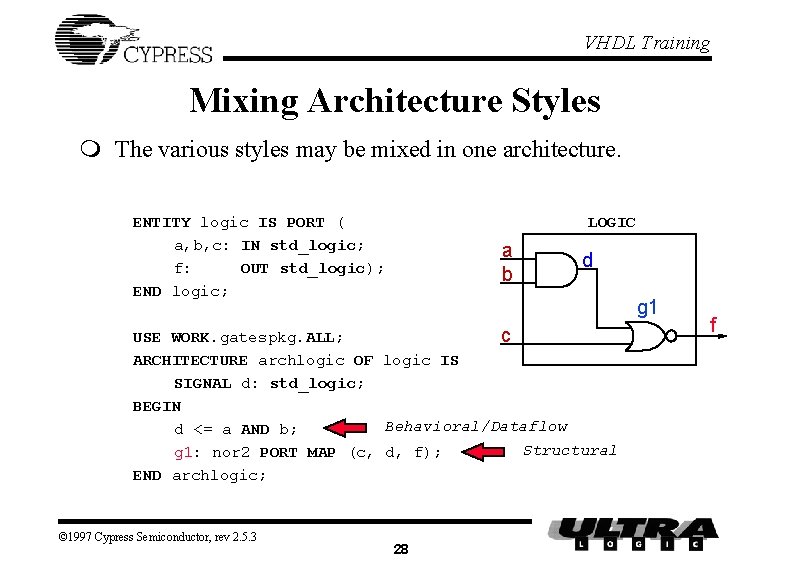

VHDL Training Mixing Architecture Styles m The various styles may be mixed in one architecture. ENTITY logic IS PORT ( a, b, c: IN std_logic; f: OUT std_logic); END logic; LOGIC a b d g 1 USE WORK. gatespkg. ALL; c ARCHITECTURE archlogic OF logic IS SIGNAL d: std_logic; BEGIN Behavioral/Dataflow d <= a AND b; Structural g 1: nor 2 PORT MAP (c, d, f); END archlogic; © 1997 Cypress Semiconductor, rev 2. 5. 3 28 f

VHDL Training VHDL Statements m There are two types of statements q Sequential • Though hardware is concurrent, it may be modeled with algorithms, by a series of sequential statements • By definition, sequential statements are grouped using a process statement. q Concurrent • Statements outside of a process are evaluated concurrently during simulation • Processes are concurrent statements © 1997 Cypress Semiconductor, rev 2. 5. 3 29

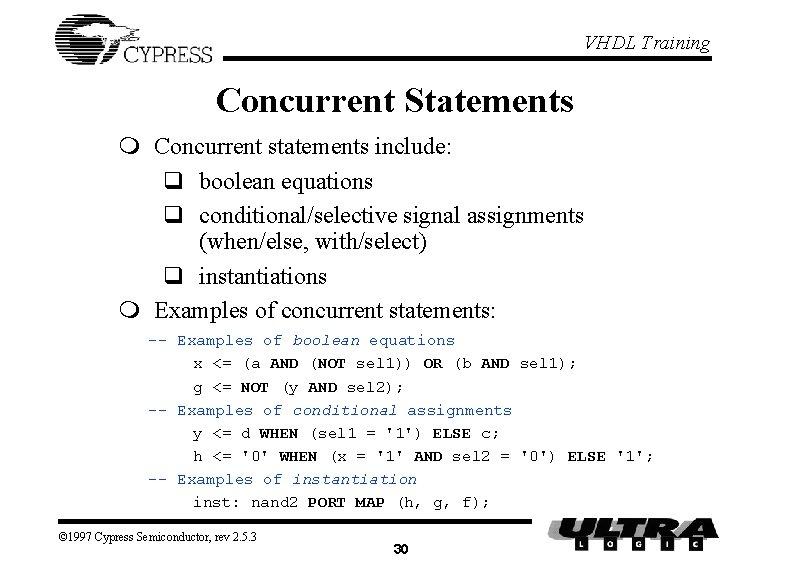

VHDL Training Concurrent Statements m Concurrent statements include: q boolean equations q conditional/selective signal assignments (when/else, with/select) q instantiations m Examples of concurrent statements: -- Examples of boolean equations x <= (a AND (NOT sel 1)) OR (b AND sel 1); g <= NOT (y AND sel 2); -- Examples of conditional assignments y <= d WHEN (sel 1 = '1') ELSE c; h <= '0' WHEN (x = '1' AND sel 2 = '0') ELSE '1'; -- Examples of instantiation inst: nand 2 PORT MAP (h, g, f); © 1997 Cypress Semiconductor, rev 2. 5. 3 30

VHDL Training The Process Statement m Used to construct algorithms/group sequential statements m Statements within a process are sequential statements -they execute sequentially during simulation m An architecture can contain multiple processes. Each process is executed concurrently m Processes may be used to model combinational or synchronous logic © 1997 Cypress Semiconductor, rev 2. 5. 3 31

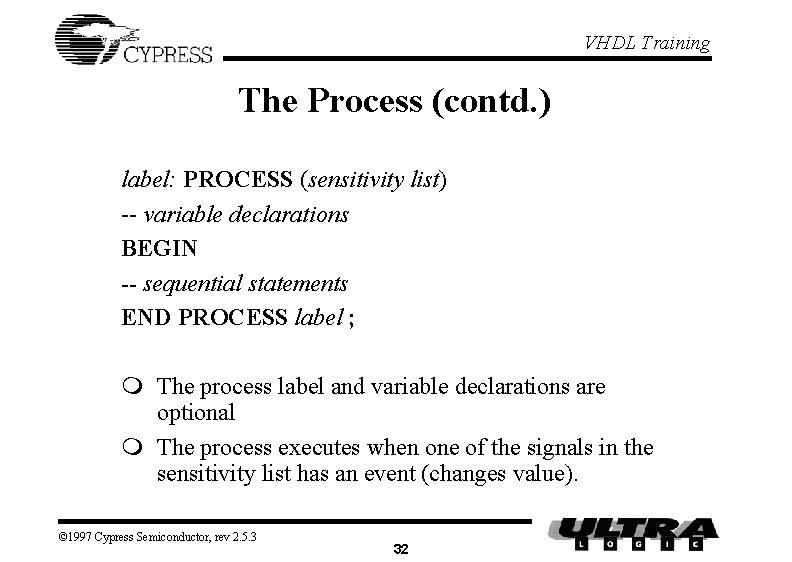

VHDL Training The Process (contd. ) label: PROCESS (sensitivity list) -- variable declarations BEGIN -- sequential statements END PROCESS label ; m The process label and variable declarations are optional m The process executes when one of the signals in the sensitivity list has an event (changes value). © 1997 Cypress Semiconductor, rev 2. 5. 3 32

VHDL Training Process (contd. ) m Processes are executing or suspended (active or inactive/awake or asleep) m A process typically has a sensitivity list q When a signal in the sensitivity list changes value, the process is executed by the simulator q e. g. , a process with a clock signal in its sensitivity list becomes active on changes of the clock signal m All signal assignments occur at the END PROCESS statement in terms of simulation q The process is then suspended until there is an event (change in value) on a signal in the sensitivity list © 1997 Cypress Semiconductor, rev 2. 5. 3 33

VHDL Training Combinational Logic m Can be described with concurrent statements q e. g. with-select-when, when-else, boolean equations, component instantiatons m Can be described with sequential statements q e. g. if-then-else, case-when © 1997 Cypress Semiconductor, rev 2. 5. 3 34

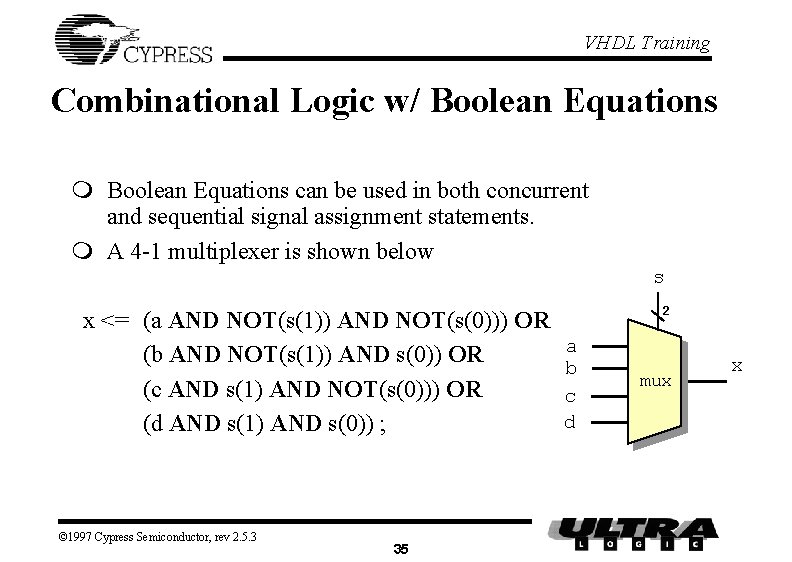

VHDL Training Combinational Logic w/ Boolean Equations m Boolean Equations can be used in both concurrent and sequential signal assignment statements. m A 4 -1 multiplexer is shown below s x <= (a AND NOT(s(1)) AND NOT(s(0))) OR (b AND NOT(s(1)) AND s(0)) OR (c AND s(1) AND NOT(s(0))) OR (d AND s(1) AND s(0)) ; © 1997 Cypress Semiconductor, rev 2. 5. 3 35 2 a b c d mux x

VHDL Training m m Selective Signal Assignment: with-select-when Assignment based on a selection signal WHEN clauses must be mutually exclusive Use a WHEN OTHERS to avoid latches Only one reference to the signal, only one assignment operator (<=) WITH selection_signal SELECT signal_name <= value_1 WHEN value_1 of selection_signal, value_2 WHEN value_2 of selection_signal, . . . value_n WHEN value_n of selection_signal, value_x WHEN OTHERS; © 1997 Cypress Semiconductor, rev 2. 5. 3 36

VHDL Training Combinational Logic w/ Selective Signal Assignment m The same 4 -1 multiplexer is shown below with s select x <= a when “ 00” , b when “ 01” , c when “ 10” , d when others ; © 1997 Cypress Semiconductor, rev 2. 5. 3 37

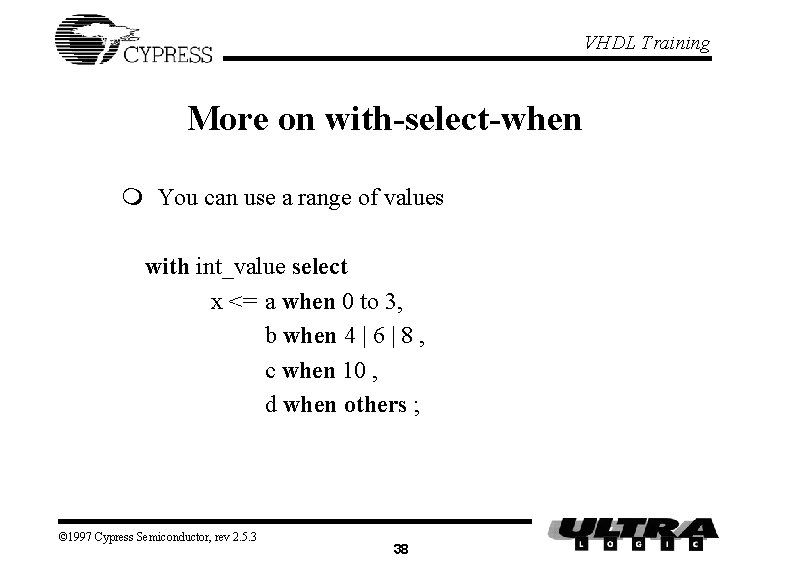

VHDL Training More on with-select-when m You can use a range of values with int_value select x <= a when 0 to 3, b when 4 | 6 | 8 , c when 10 , d when others ; © 1997 Cypress Semiconductor, rev 2. 5. 3 38

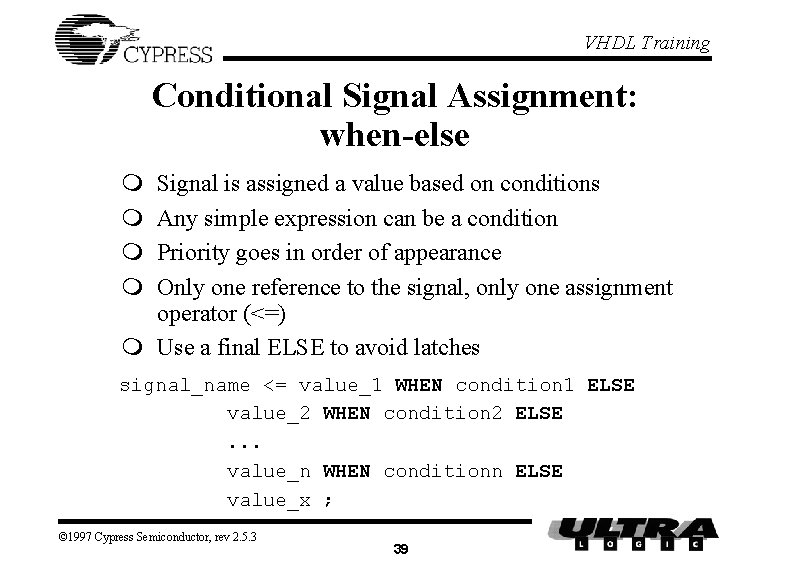

VHDL Training Conditional Signal Assignment: when-else m m Signal is assigned a value based on conditions Any simple expression can be a condition Priority goes in order of appearance Only one reference to the signal, only one assignment operator (<=) m Use a final ELSE to avoid latches signal_name <= value_1 WHEN condition 1 ELSE value_2 WHEN condition 2 ELSE. . . value_n WHEN conditionn ELSE value_x ; © 1997 Cypress Semiconductor, rev 2. 5. 3 39

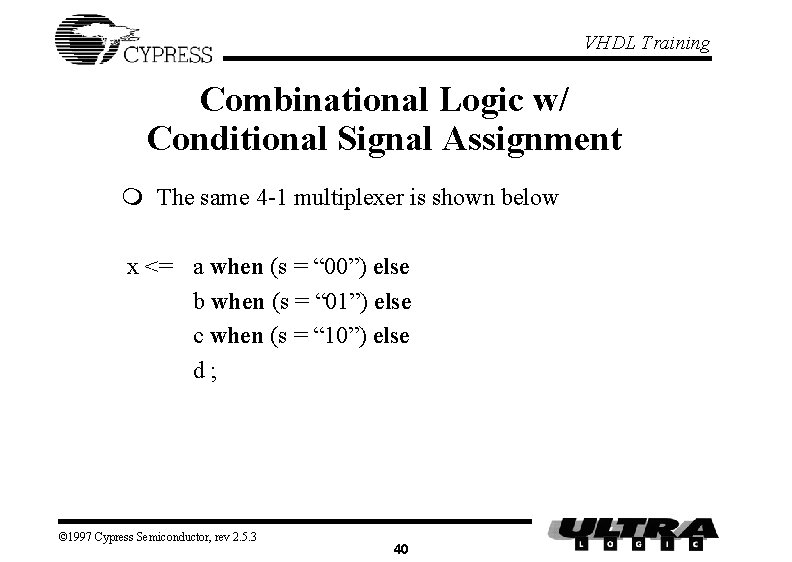

VHDL Training Combinational Logic w/ Conditional Signal Assignment m The same 4 -1 multiplexer is shown below x <= a when (s = “ 00”) else b when (s = “ 01”) else c when (s = “ 10”) else d; © 1997 Cypress Semiconductor, rev 2. 5. 3 40

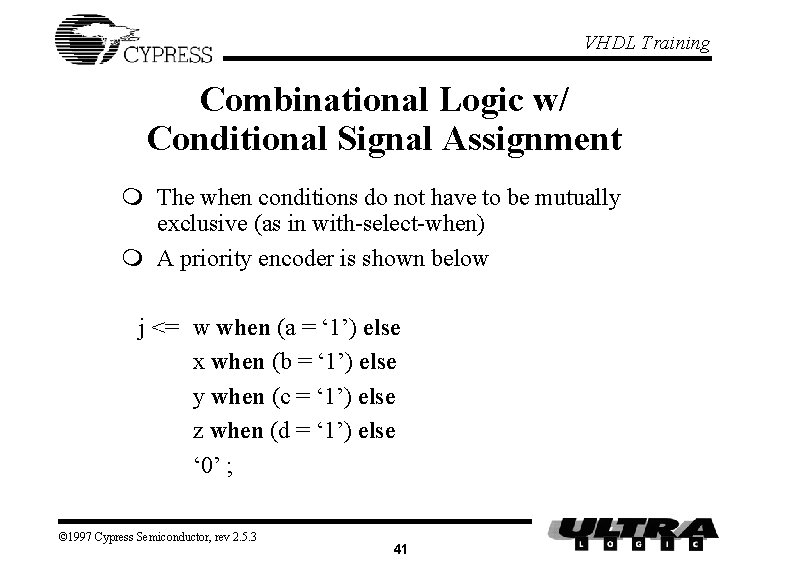

VHDL Training Combinational Logic w/ Conditional Signal Assignment m The when conditions do not have to be mutually exclusive (as in with-select-when) m A priority encoder is shown below j <= w when (a = ‘ 1’) else x when (b = ‘ 1’) else y when (c = ‘ 1’) else z when (d = ‘ 1’) else ‘ 0’ ; © 1997 Cypress Semiconductor, rev 2. 5. 3 41

VHDL Training Combinational Logic w/ Sequential Statements m Grouped together with Processes m Processes are concurrent with one another and with concurrent statements m Order of sequential statements does make a difference in synthesis © 1997 Cypress Semiconductor, rev 2. 5. 3 42

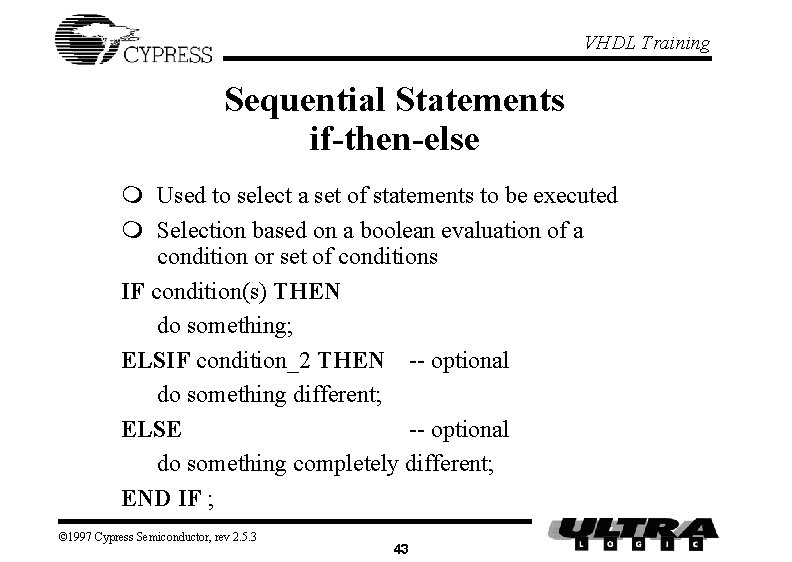

VHDL Training Sequential Statements if-then-else m Used to select a set of statements to be executed m Selection based on a boolean evaluation of a condition or set of conditions IF condition(s) THEN do something; ELSIF condition_2 THEN -- optional do something different; ELSE -- optional do something completely different; END IF ; © 1997 Cypress Semiconductor, rev 2. 5. 3 43

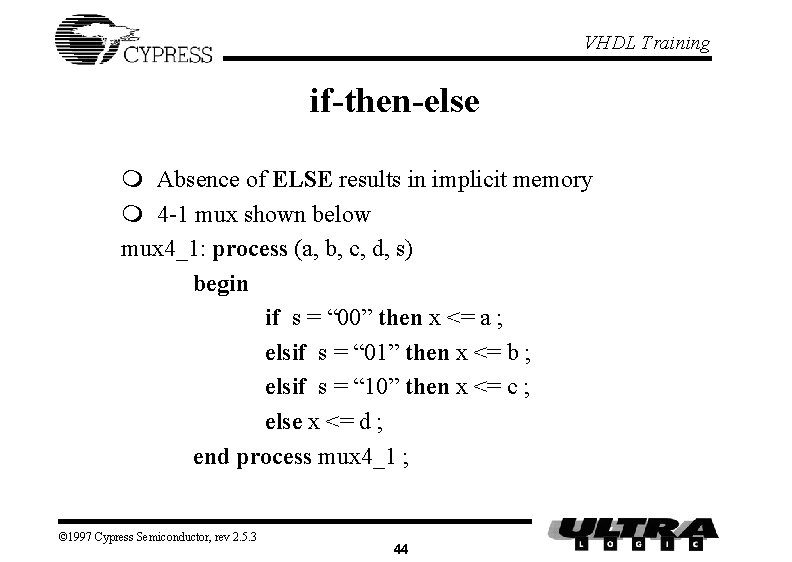

VHDL Training if-then-else m Absence of ELSE results in implicit memory m 4 -1 mux shown below mux 4_1: process (a, b, c, d, s) begin if s = “ 00” then x <= a ; elsif s = “ 01” then x <= b ; elsif s = “ 10” then x <= c ; else x <= d ; end process mux 4_1 ; © 1997 Cypress Semiconductor, rev 2. 5. 3 44

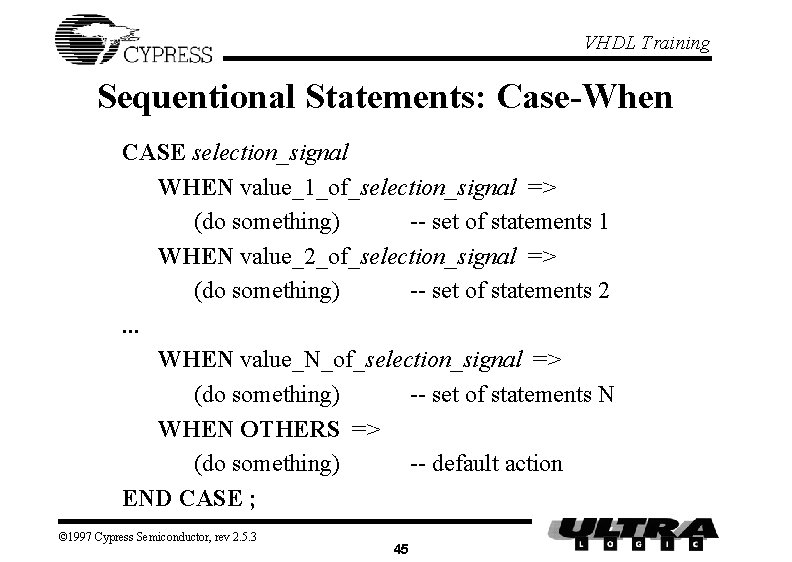

VHDL Training Sequentional Statements: Case-When CASE selection_signal WHEN value_1_of_selection_signal => (do something) -- set of statements 1 WHEN value_2_of_selection_signal => (do something) -- set of statements 2. . . WHEN value_N_of_selection_signal => (do something) -- set of statements N WHEN OTHERS => (do something) -- default action END CASE ; © 1997 Cypress Semiconductor, rev 2. 5. 3 45

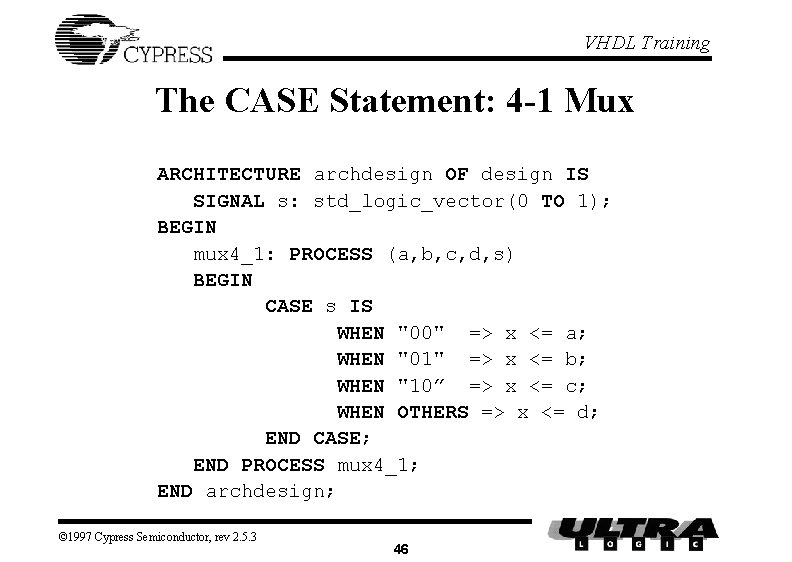

VHDL Training The CASE Statement: 4 -1 Mux ARCHITECTURE archdesign OF design IS SIGNAL s: std_logic_vector(0 TO 1); BEGIN mux 4_1: PROCESS (a, b, c, d, s) BEGIN CASE s IS WHEN "00" => x <= a; WHEN "01" => x <= b; WHEN "10” => x <= c; WHEN OTHERS => x <= d; END CASE; END PROCESS mux 4_1; END archdesign; © 1997 Cypress Semiconductor, rev 2. 5. 3 46

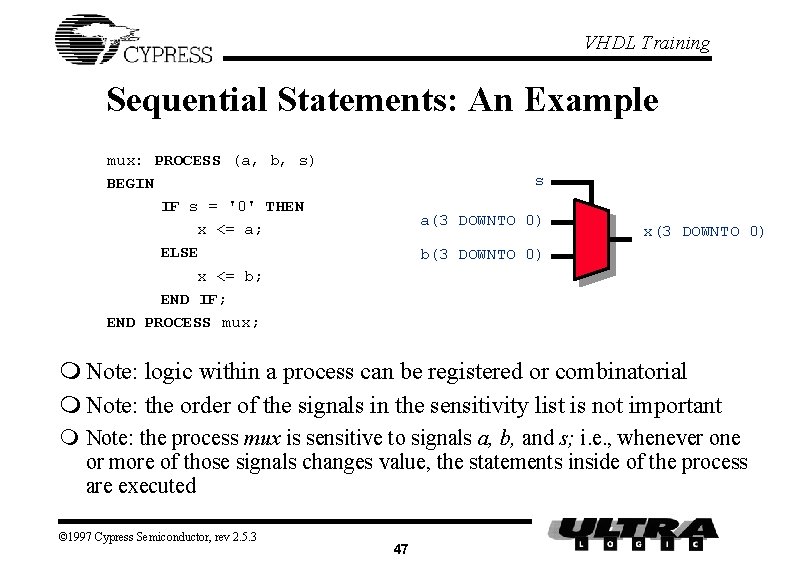

VHDL Training Sequential Statements: An Example mux: PROCESS (a, b, s) BEGIN IF s = '0' THEN x <= a; ELSE x <= b; END IF; END PROCESS mux; s a(3 DOWNTO 0) x(3 DOWNTO 0) b(3 DOWNTO 0) m Note: logic within a process can be registered or combinatorial m Note: the order of the signals in the sensitivity list is not important m Note: the process mux is sensitive to signals a, b, and s; i. e. , whenever one or more of those signals changes value, the statements inside of the process are executed © 1997 Cypress Semiconductor, rev 2. 5. 3 47

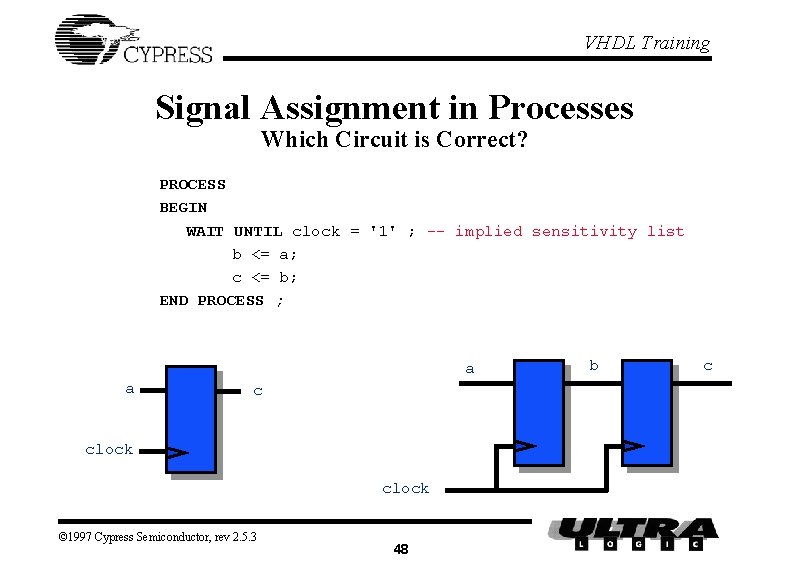

VHDL Training Signal Assignment in Processes Which Circuit is Correct? PROCESS BEGIN WAIT UNTIL clock = '1' ; -- implied sensitivity list b <= a; c <= b; END PROCESS ; a a c clock © 1997 Cypress Semiconductor, rev 2. 5. 3 48 b c

VHDL Training Signal Assignment in Processes (contd. ) m Signals are not updated immediately. Rather, they are scheduled. m The signals are not updated until time advances (after the End Process statement) m Therefore, two registers will be synthesized m Note: In some instances, the use of concurrent statements outside the process may alleviate the problem, but this is not possible with registered logic. © 1997 Cypress Semiconductor, rev 2. 5. 3 49

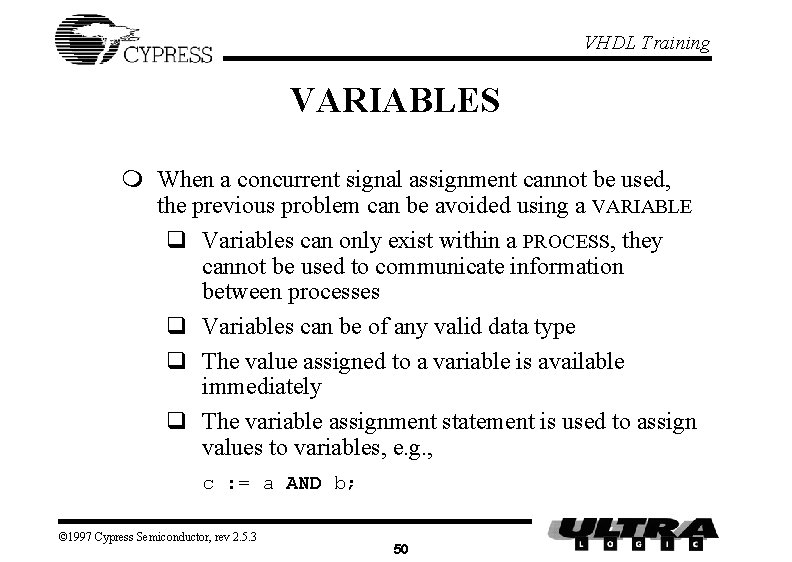

VHDL Training VARIABLES m When a concurrent signal assignment cannot be used, the previous problem can be avoided using a VARIABLE q Variables can only exist within a PROCESS, they cannot be used to communicate information between processes q Variables can be of any valid data type q The value assigned to a variable is available immediately q The variable assignment statement is used to assign values to variables, e. g. , c : = a AND b; © 1997 Cypress Semiconductor, rev 2. 5. 3 50

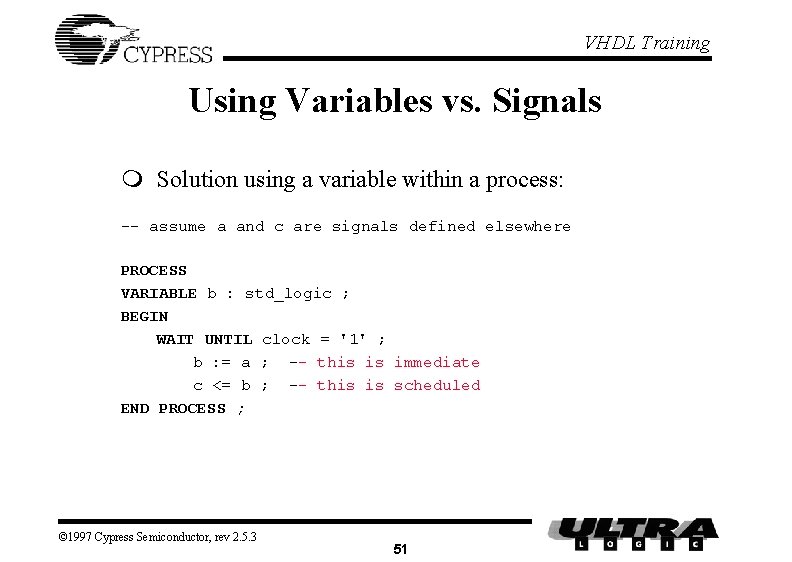

VHDL Training Using Variables vs. Signals m Solution using a variable within a process: -- assume a and c are signals defined elsewhere PROCESS VARIABLE b : std_logic ; BEGIN WAIT UNTIL clock = '1' ; b : = a ; -- this is immediate c <= b ; -- this is scheduled END PROCESS ; © 1997 Cypress Semiconductor, rev 2. 5. 3 51

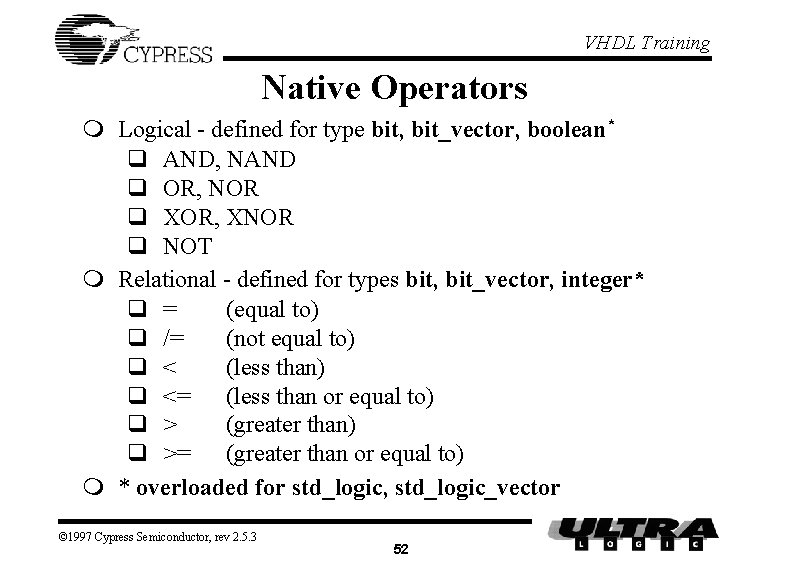

VHDL Training Native Operators m Logical - defined for type bit, bit_vector, boolean* q AND, NAND q OR, NOR q XOR, XNOR q NOT m Relational - defined for types bit, bit_vector, integer* q = (equal to) q /= (not equal to) q < (less than) q <= (less than or equal to) q > (greater than) q >= (greater than or equal to) m * overloaded for std_logic, std_logic_vector © 1997 Cypress Semiconductor, rev 2. 5. 3 52

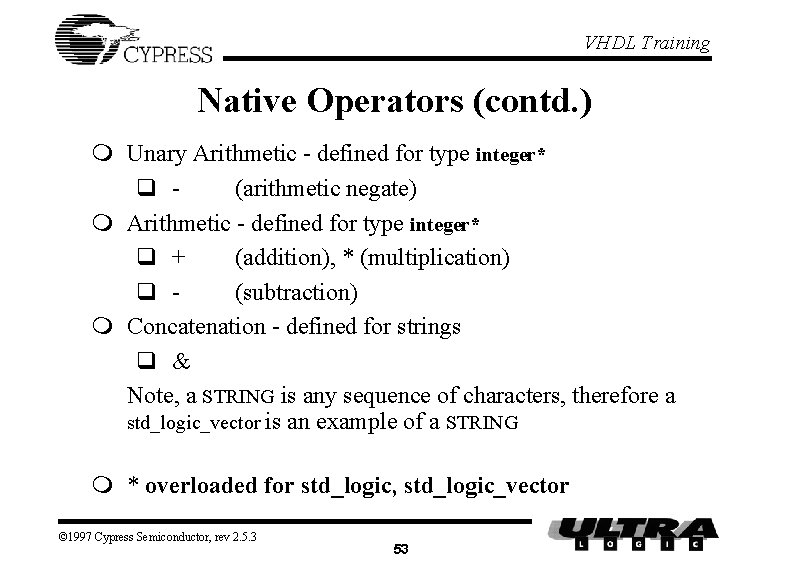

VHDL Training Native Operators (contd. ) m Unary Arithmetic - defined for type integer* q (arithmetic negate) m Arithmetic - defined for type integer* q + (addition), * (multiplication) q (subtraction) m Concatenation - defined for strings q & Note, a STRING is any sequence of characters, therefore a std_logic_vector is an example of a STRING m * overloaded for std_logic, std_logic_vector © 1997 Cypress Semiconductor, rev 2. 5. 3 53

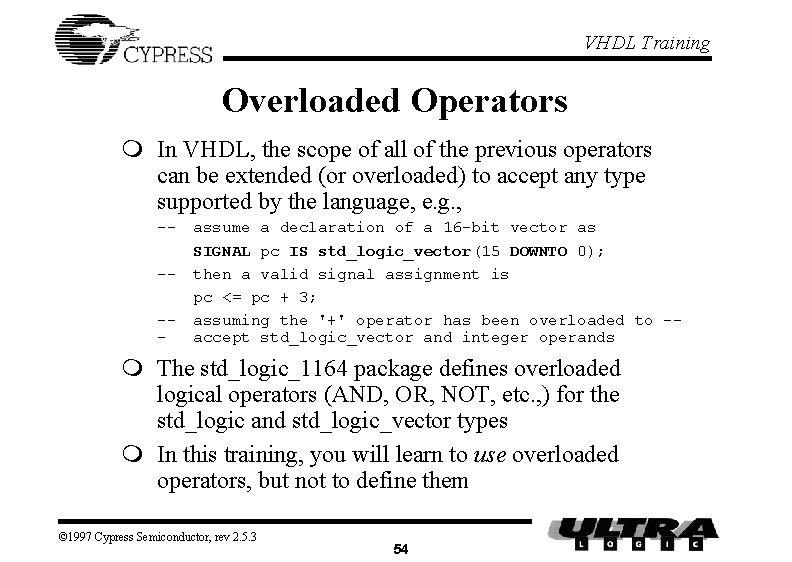

VHDL Training Overloaded Operators m In VHDL, the scope of all of the previous operators can be extended (or overloaded) to accept any type supported by the language, e. g. , ---- assume a declaration of a 16 -bit vector as SIGNAL pc IS std_logic_vector(15 DOWNTO 0); then a valid signal assignment is pc <= pc + 3; assuming the '+' operator has been overloaded to -accept std_logic_vector and integer operands m The std_logic_1164 package defines overloaded logical operators (AND, OR, NOT, etc. , ) for the std_logic and std_logic_vector types m In this training, you will learn to use overloaded operators, but not to define them © 1997 Cypress Semiconductor, rev 2. 5. 3 54

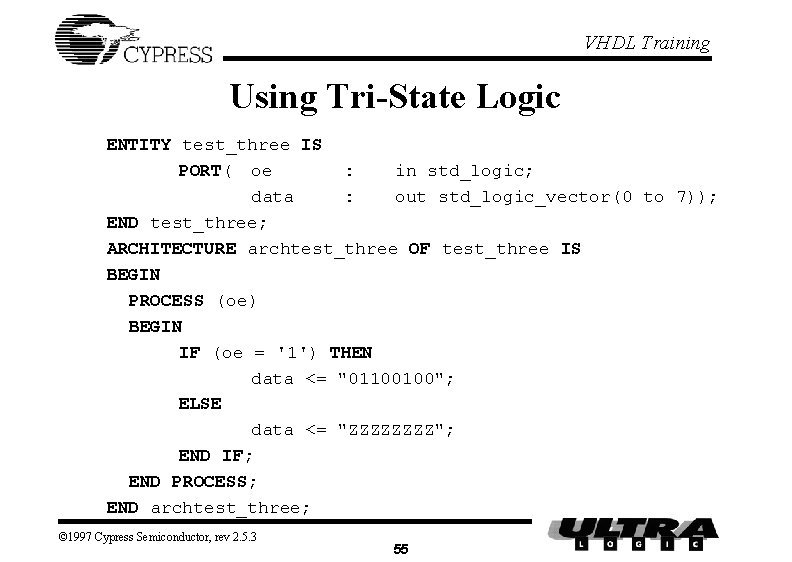

VHDL Training Using Tri-State Logic ENTITY test_three IS PORT( oe : in std_logic; data : out std_logic_vector(0 to 7)); END test_three; ARCHITECTURE archtest_three OF test_three IS BEGIN PROCESS (oe) BEGIN IF (oe = '1') THEN data <= "01100100"; ELSE data <= "ZZZZ"; END IF; END PROCESS; END archtest_three; © 1997 Cypress Semiconductor, rev 2. 5. 3 55

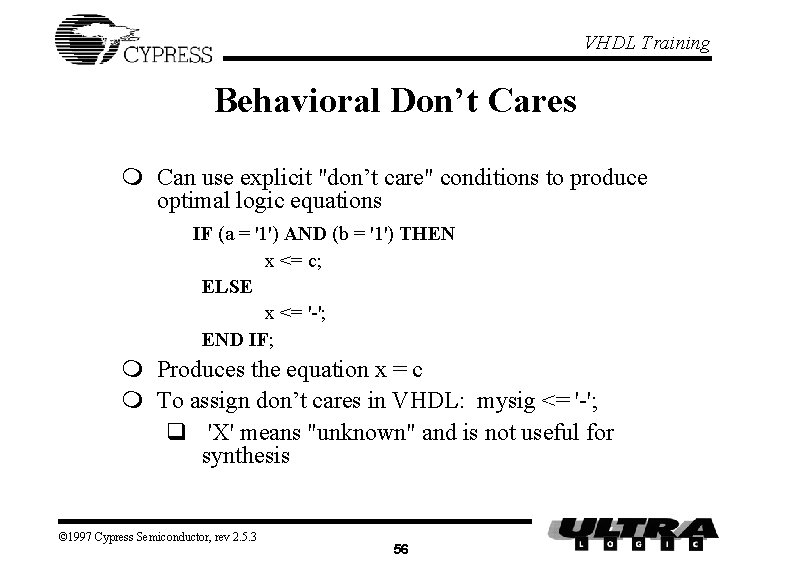

VHDL Training Behavioral Don’t Cares m Can use explicit "don’t care" conditions to produce optimal logic equations IF (a = '1') AND (b = '1') THEN x <= c; ELSE x <= '-'; END IF; m Produces the equation x = c m To assign don’t cares in VHDL: mysig <= '-'; q 'X' means "unknown" and is not useful for synthesis © 1997 Cypress Semiconductor, rev 2. 5. 3 56

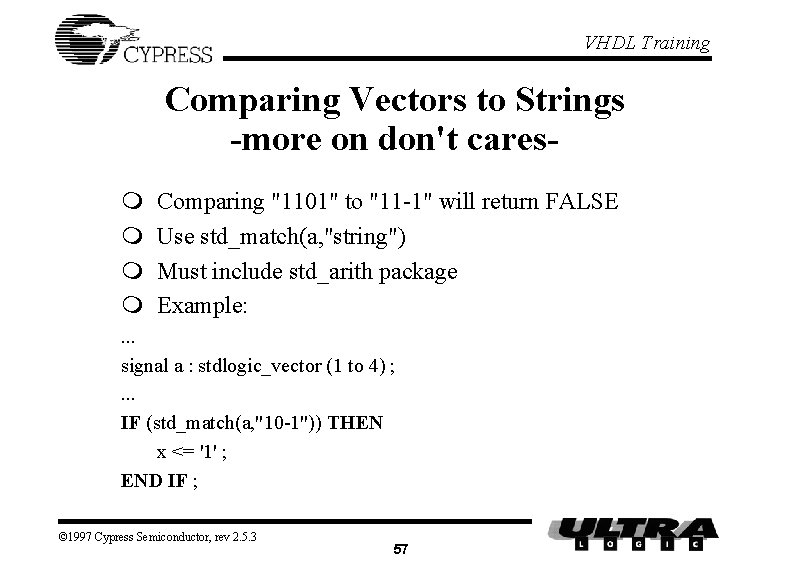

VHDL Training Comparing Vectors to Strings -more on don't caresm m Comparing "1101" to "11 -1" will return FALSE Use std_match(a, "string") Must include std_arith package Example: . . . signal a : stdlogic_vector (1 to 4) ; . . . IF (std_match(a, "10 -1")) THEN x <= '1' ; END IF ; © 1997 Cypress Semiconductor, rev 2. 5. 3 57

VHDL Training Legal VHDL Identifiers m Letters, digits, and underscores only (first character must be a letter) m The last character cannot be an underscore m Two underscores in succession are not allowed m Using reserved words is not allowed m Examples q Legal • tx_clk, Three_State_Enable, sel 7 D, HIT_1124 q Not Legal • _tx_clk, 8 B 10 B, large#num, register, clk_ © 1997 Cypress Semiconductor, rev 2. 5. 3 58

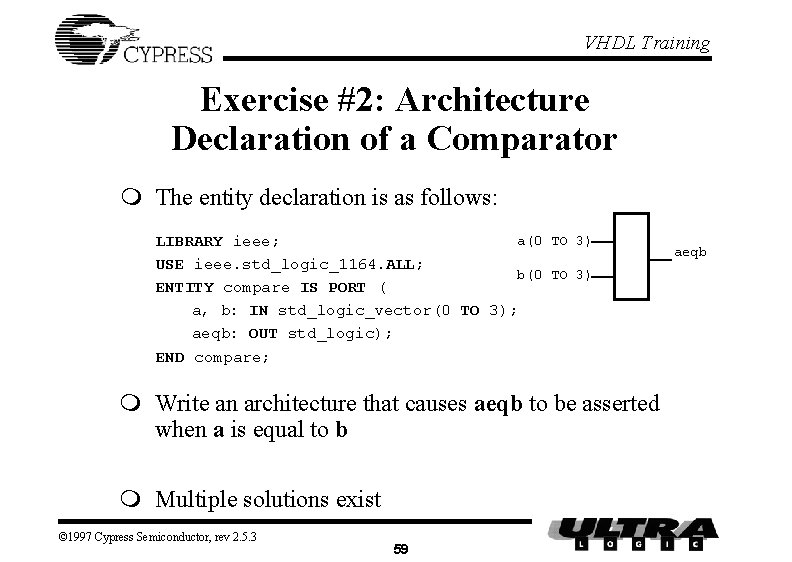

VHDL Training Exercise #2: Architecture Declaration of a Comparator m The entity declaration is as follows: a(0 TO 3) LIBRARY ieee; USE ieee. std_logic_1164. ALL; b(0 TO 3) ENTITY compare IS PORT ( a, b: IN std_logic_vector(0 TO 3); aeqb: OUT std_logic); END compare; m Write an architecture that causes aeqb to be asserted when a is equal to b m Multiple solutions exist © 1997 Cypress Semiconductor, rev 2. 5. 3 59 aeqb

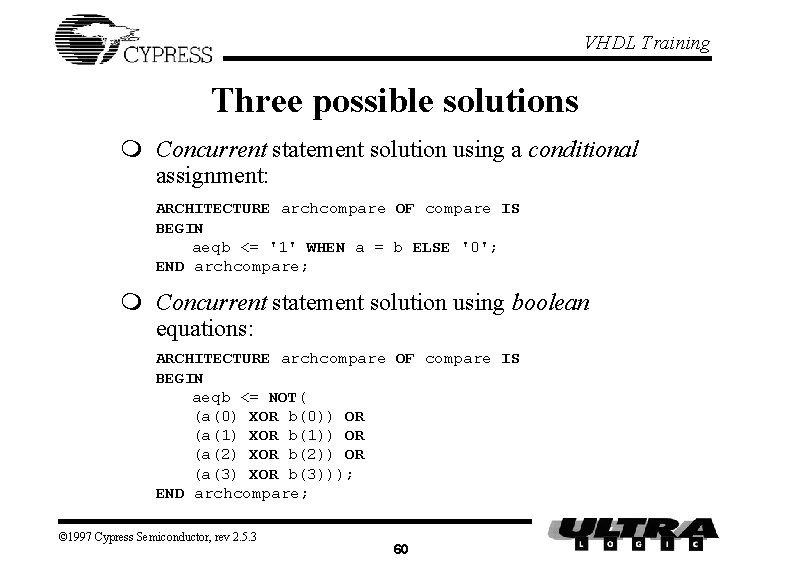

VHDL Training Three possible solutions m Concurrent statement solution using a conditional assignment: ARCHITECTURE archcompare OF compare IS BEGIN aeqb <= '1' WHEN a = b ELSE '0'; END archcompare; m Concurrent statement solution using boolean equations: ARCHITECTURE archcompare OF compare IS BEGIN aeqb <= NOT( (a(0) XOR b(0)) OR (a(1) XOR b(1)) OR (a(2) XOR b(2)) OR (a(3) XOR b(3))); END archcompare; © 1997 Cypress Semiconductor, rev 2. 5. 3 60

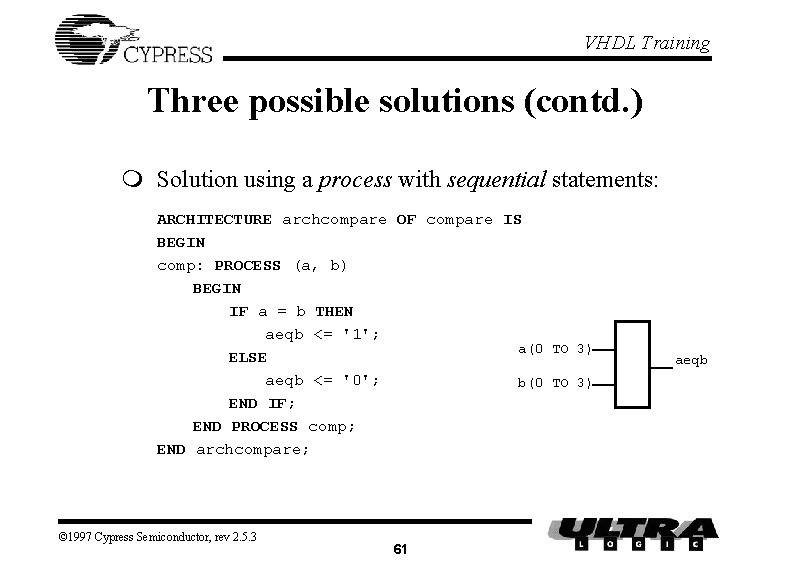

VHDL Training Three possible solutions (contd. ) m Solution using a process with sequential statements: ARCHITECTURE archcompare OF compare IS BEGIN comp: PROCESS (a, b) BEGIN IF a = b THEN aeqb <= '1'; a(0 TO 3) ELSE aeqb <= '0'; b(0 TO 3) END IF; END PROCESS comp; END archcompare; © 1997 Cypress Semiconductor, rev 2. 5. 3 61 aeqb

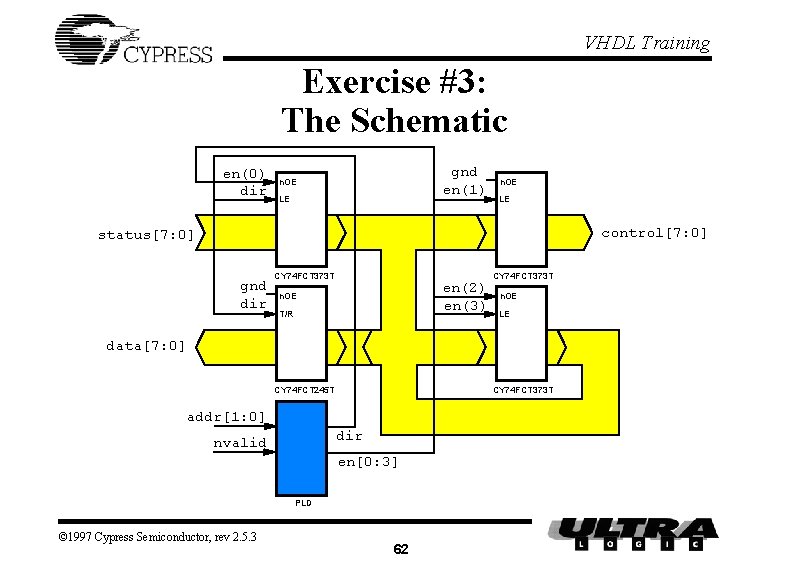

VHDL Training Exercise #3: The Schematic en(0) dir gnd en(1) n. OE LE control[7: 0] status[7: 0] gnd dir CY 74 FCT 373 T en(2) en(3) n. OE T/R CY 74 FCT 373 T n. OE LE data[7: 0] CY 74 FCT 245 T CY 74 FCT 373 T addr[1: 0] dir nvalid en[0: 3] PLD © 1997 Cypress Semiconductor, rev 2. 5. 3 62

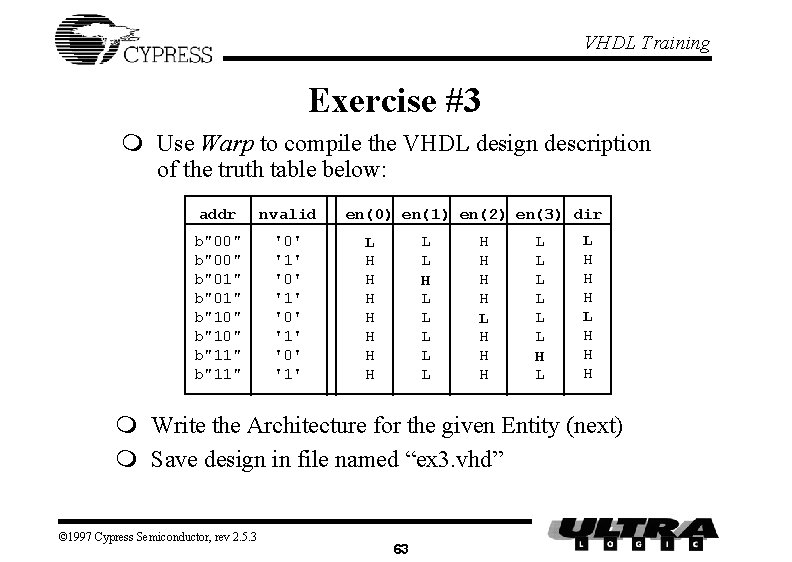

VHDL Training Exercise #3 m Use Warp to compile the VHDL design description of the truth table below: addr nvalid b"00" b"01" b"10" b"11" '0' '1' en(0) en(1) en(2) en(3) dir L L H L L L H H H L H H H L L L H H H m Write the Architecture for the given Entity (next) m Save design in file named “ex 3. vhd” © 1997 Cypress Semiconductor, rev 2. 5. 3 63

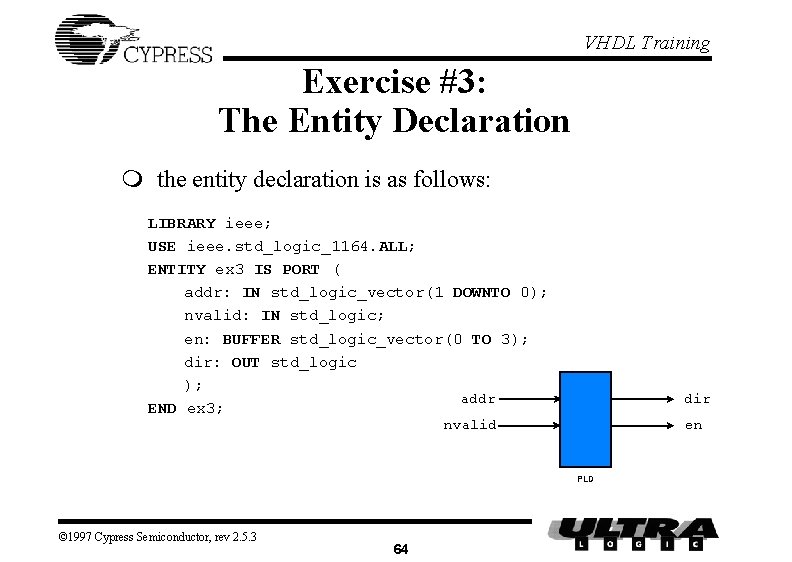

VHDL Training Exercise #3: The Entity Declaration m the entity declaration is as follows: LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY ex 3 IS PORT ( addr: IN std_logic_vector(1 DOWNTO 0); nvalid: IN std_logic; en: BUFFER std_logic_vector(0 TO 3); dir: OUT std_logic ); addr END ex 3; dir nvalid en PLD © 1997 Cypress Semiconductor, rev 2. 5. 3 64

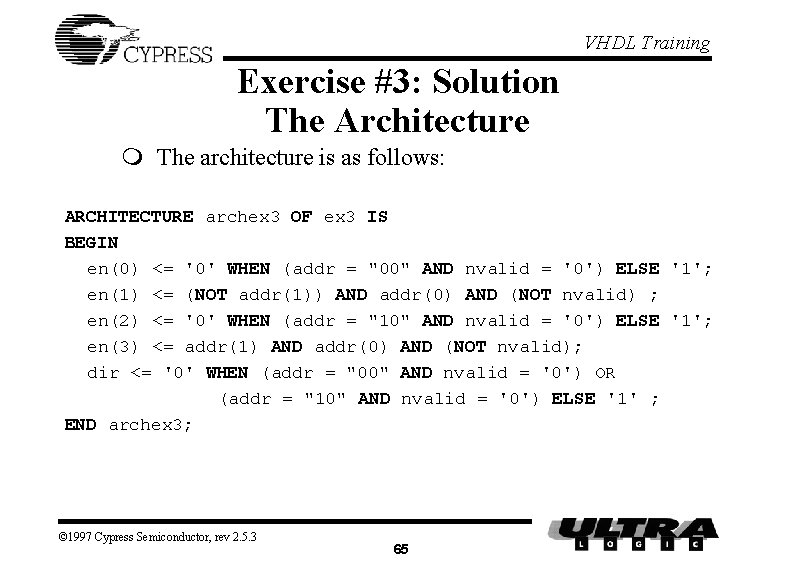

VHDL Training Exercise #3: Solution The Architecture m The architecture is as follows: ARCHITECTURE archex 3 OF ex 3 IS BEGIN en(0) <= '0' WHEN (addr = "00" AND nvalid = '0') ELSE '1'; en(1) <= (NOT addr(1)) AND addr(0) AND (NOT nvalid) ; en(2) <= '0' WHEN (addr = "10" AND nvalid = '0') ELSE '1'; en(3) <= addr(1) AND addr(0) AND (NOT nvalid); dir <= '0' WHEN (addr = "00" AND nvalid = '0') OR (addr = "10" AND nvalid = '0') ELSE '1' ; END archex 3; © 1997 Cypress Semiconductor, rev 2. 5. 3 65

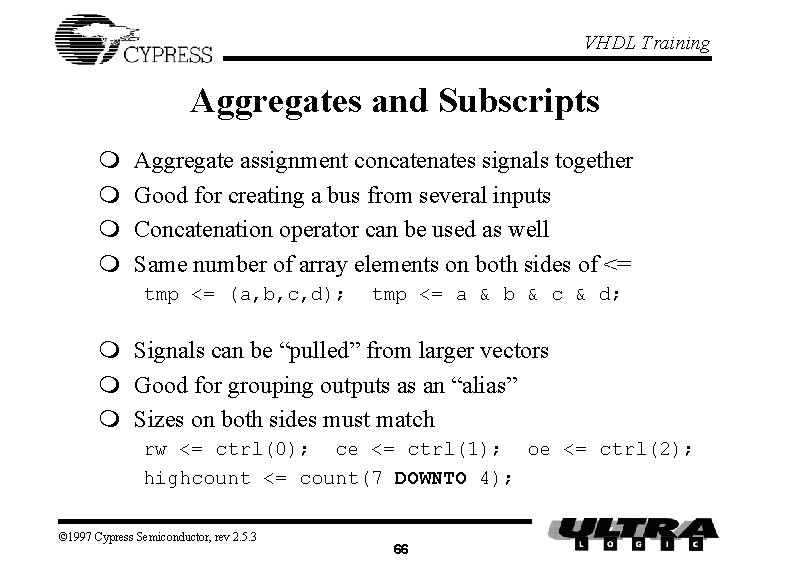

VHDL Training Aggregates and Subscripts m m Aggregate assignment concatenates signals together Good for creating a bus from several inputs Concatenation operator can be used as well Same number of array elements on both sides of <= tmp <= (a, b, c, d); tmp <= a & b & c & d; m Signals can be “pulled” from larger vectors m Good for grouping outputs as an “alias” m Sizes on both sides must match rw <= ctrl(0); ce <= ctrl(1); oe <= ctrl(2); highcount <= count(7 DOWNTO 4); © 1997 Cypress Semiconductor, rev 2. 5. 3 66

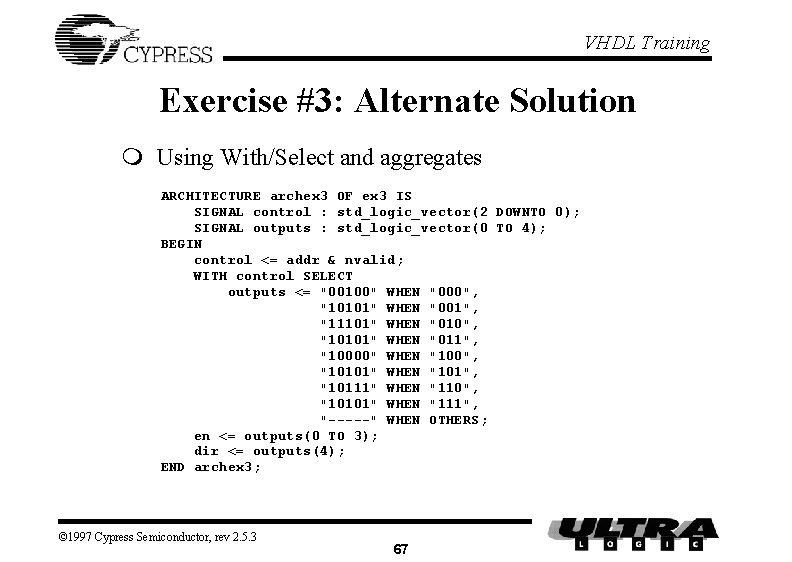

VHDL Training Exercise #3: Alternate Solution m Using With/Select and aggregates ARCHITECTURE archex 3 OF ex 3 IS SIGNAL control : std_logic_vector(2 DOWNTO 0); SIGNAL outputs : std_logic_vector(0 TO 4); BEGIN control <= addr & nvalid; WITH control SELECT outputs <= "00100" WHEN "000", "10101" WHEN "001", "11101" WHEN "010", "10101" WHEN "011", "10000" WHEN "100", "10101" WHEN "101", "10111" WHEN "110", "10101" WHEN "111", "-----" WHEN OTHERS; en <= outputs(0 TO 3); dir <= outputs(4); END archex 3; © 1997 Cypress Semiconductor, rev 2. 5. 3 67

VHDL Training Designs that use Registers m There are two methods of utilizing and generating flip-flops: q Instantiate (place) a flip-flop or a component that contains a flip-flop q Use a process that is sensitive to a clock edge © 1997 Cypress Semiconductor, rev 2. 5. 3 68

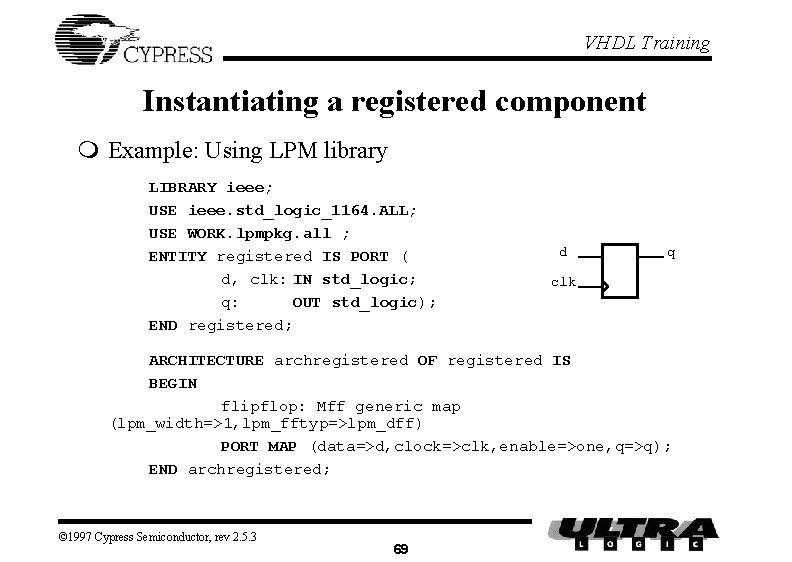

VHDL Training Instantiating a registered component m Example: Using LPM library LIBRARY ieee; USE ieee. std_logic_1164. ALL; USE WORK. lpmpkg. all ; ENTITY registered IS PORT ( d, clk: IN std_logic; q: OUT std_logic); END registered; d q clk ARCHITECTURE archregistered OF registered IS BEGIN flipflop: Mff generic map (lpm_width=>1, lpm_fftyp=>lpm_dff) PORT MAP (data=>d, clock=>clk, enable=>one, q=>q); END archregistered; © 1997 Cypress Semiconductor, rev 2. 5. 3 69

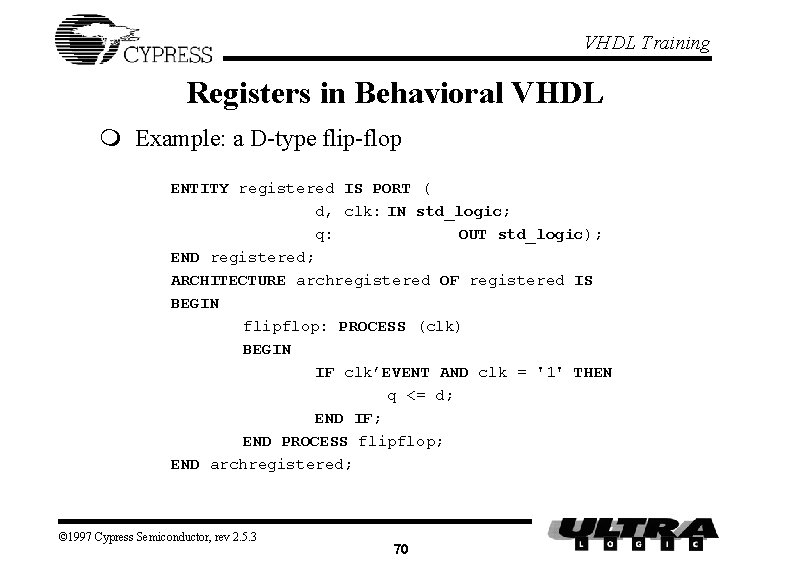

VHDL Training Registers in Behavioral VHDL m Example: a D-type flip-flop ENTITY registered IS PORT ( d, clk: IN std_logic; q: OUT std_logic); END registered; ARCHITECTURE archregistered OF registered IS BEGIN flipflop: PROCESS (clk) BEGIN IF clk’EVENT AND clk = '1' THEN q <= d; END IF; END PROCESS flipflop; END archregistered; © 1997 Cypress Semiconductor, rev 2. 5. 3 70

VHDL Training Registers in Behavioral VHDL m The synthesis compiler infers that a register is to be created for which signal q is the output because q The clock (clk) is in the sensitivity list q The construct, clk’event and clk = ‘ 1’, appears in the process m The clk’event and clk = ‘ 1’ statement implies that subsequent signal assignments occur on the risingedge of the clock m The absence of an “else” clause in the “if-then” statement implies that if the clk’event and clk = ‘ 1’ condition is not fulfilled (i. e. not a rising-edge), q will retain its value until the next assignment occurs (this is referred to as implied memory) © 1997 Cypress Semiconductor, rev 2. 5. 3 71

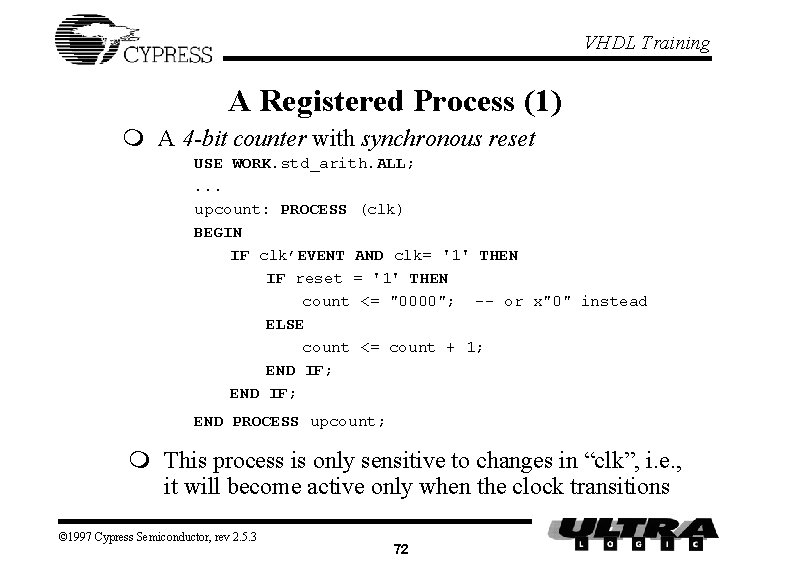

VHDL Training A Registered Process (1) m A 4 -bit counter with synchronous reset USE WORK. std_arith. ALL; . . . upcount: PROCESS (clk) BEGIN IF clk’EVENT AND clk= '1' THEN IF reset = '1' THEN count <= "0000"; -- or x"0" instead ELSE count <= count + 1; END IF; END PROCESS upcount; m This process is only sensitive to changes in “clk”, i. e. , it will become active only when the clock transitions © 1997 Cypress Semiconductor, rev 2. 5. 3 72

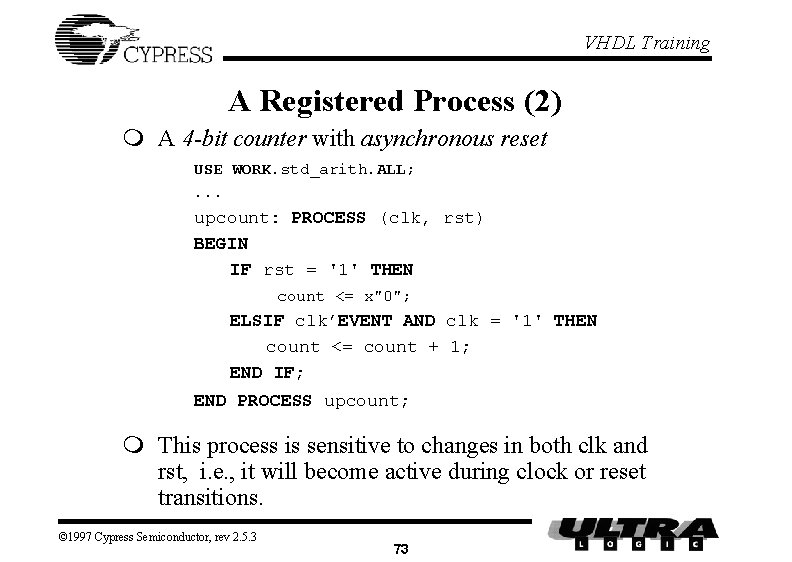

VHDL Training A Registered Process (2) m A 4 -bit counter with asynchronous reset USE WORK. std_arith. ALL; . . . upcount: PROCESS (clk, rst) BEGIN IF rst = '1' THEN count <= x"0"; ELSIF clk’EVENT AND clk = '1' THEN count <= count + 1; END IF; END PROCESS upcount; m This process is sensitive to changes in both clk and rst, i. e. , it will become active during clock or reset transitions. © 1997 Cypress Semiconductor, rev 2. 5. 3 73

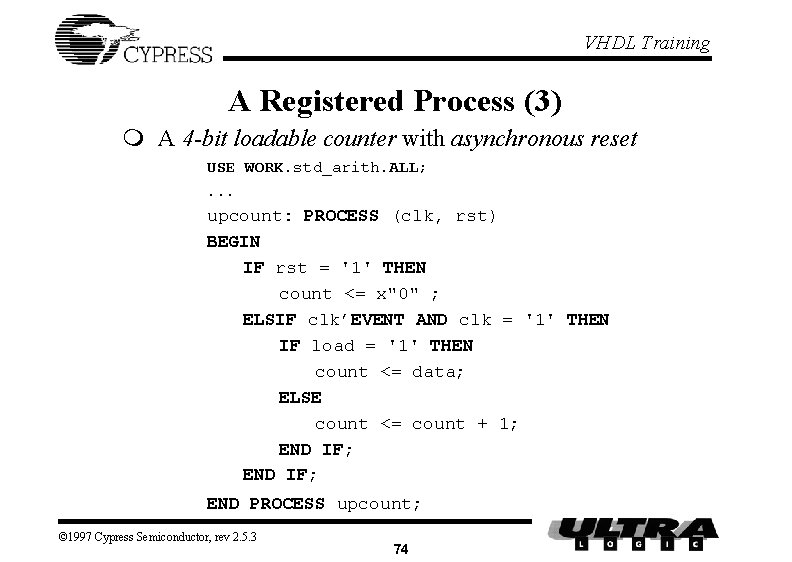

VHDL Training A Registered Process (3) m A 4 -bit loadable counter with asynchronous reset USE WORK. std_arith. ALL; . . . upcount: PROCESS (clk, rst) BEGIN IF rst = '1' THEN count <= x"0" ; ELSIF clk’EVENT AND clk = '1' THEN IF load = '1' THEN count <= data; ELSE count <= count + 1; END IF; END PROCESS upcount; © 1997 Cypress Semiconductor, rev 2. 5. 3 74

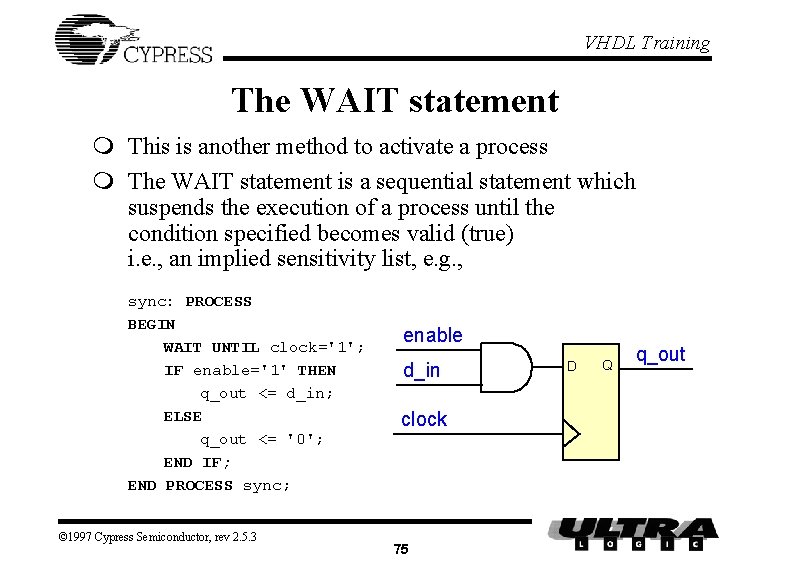

VHDL Training The WAIT statement m This is another method to activate a process m The WAIT statement is a sequential statement which suspends the execution of a process until the condition specified becomes valid (true) i. e. , an implied sensitivity list, e. g. , sync: PROCESS BEGIN WAIT UNTIL clock='1'; IF enable='1' THEN q_out <= d_in; ELSE q_out <= '0'; END IF; END PROCESS sync; © 1997 Cypress Semiconductor, rev 2. 5. 3 enable d_in clock 75 D Q q_out

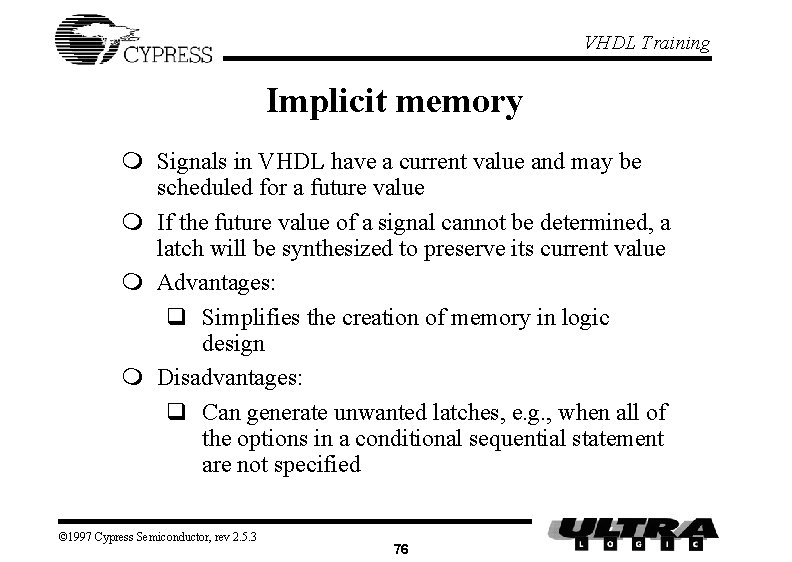

VHDL Training Implicit memory m Signals in VHDL have a current value and may be scheduled for a future value m If the future value of a signal cannot be determined, a latch will be synthesized to preserve its current value m Advantages: q Simplifies the creation of memory in logic design m Disadvantages: q Can generate unwanted latches, e. g. , when all of the options in a conditional sequential statement are not specified © 1997 Cypress Semiconductor, rev 2. 5. 3 76

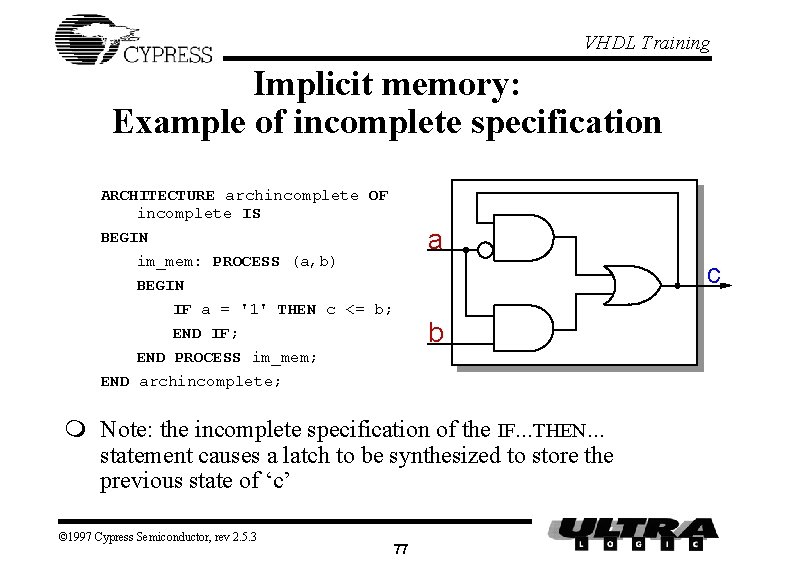

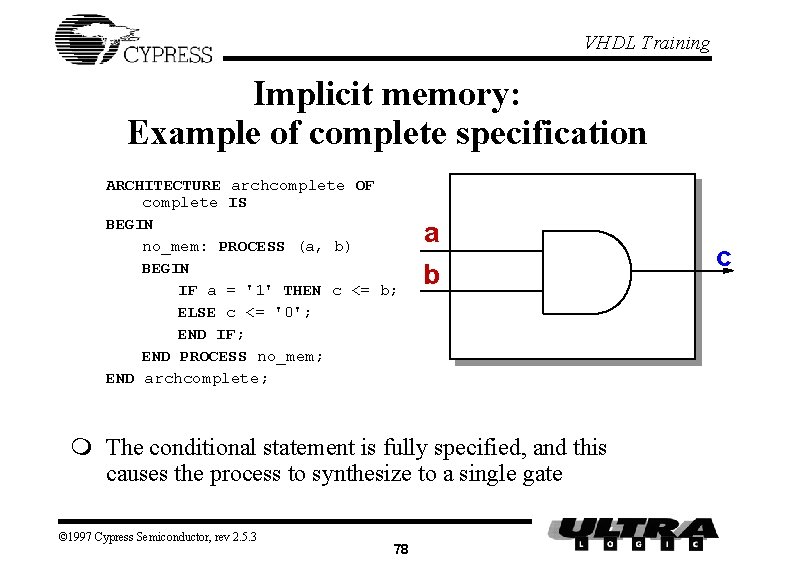

VHDL Training Implicit memory: Example of incomplete specification ARCHITECTURE archincomplete OF incomplete IS BEGIN im_mem: PROCESS (a, b) a c BEGIN IF a = '1' THEN c <= b; END IF; END PROCESS im_mem; END archincomplete; b m Note: the incomplete specification of the IF. . . THEN. . . statement causes a latch to be synthesized to store the previous state of ‘c’ © 1997 Cypress Semiconductor, rev 2. 5. 3 77

VHDL Training Implicit memory: Example of complete specification ARCHITECTURE archcomplete OF complete IS BEGIN no_mem: PROCESS (a, b) BEGIN IF a = '1' THEN c <= b; ELSE c <= '0'; END IF; END PROCESS no_mem; END archcomplete; a b m The conditional statement is fully specified, and this causes the process to synthesize to a single gate © 1997 Cypress Semiconductor, rev 2. 5. 3 78 c

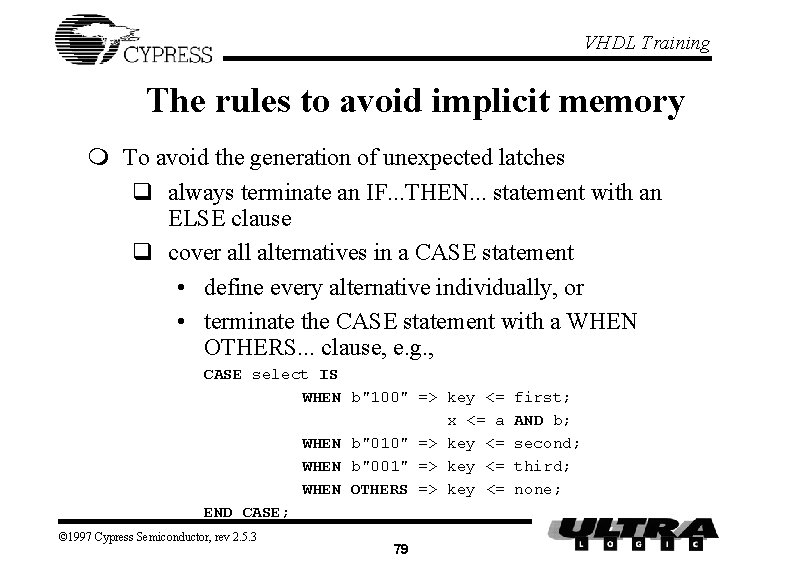

VHDL Training The rules to avoid implicit memory m To avoid the generation of unexpected latches q always terminate an IF. . . THEN. . . statement with an ELSE clause q cover all alternatives in a CASE statement • define every alternative individually, or • terminate the CASE statement with a WHEN OTHERS. . . clause, e. g. , CASE select IS WHEN b"100" => key <= x <= a WHEN b"010" => key <= WHEN b"001" => key <= WHEN OTHERS => key <= END CASE; © 1997 Cypress Semiconductor, rev 2. 5. 3 79 first; AND b; second; third; none;

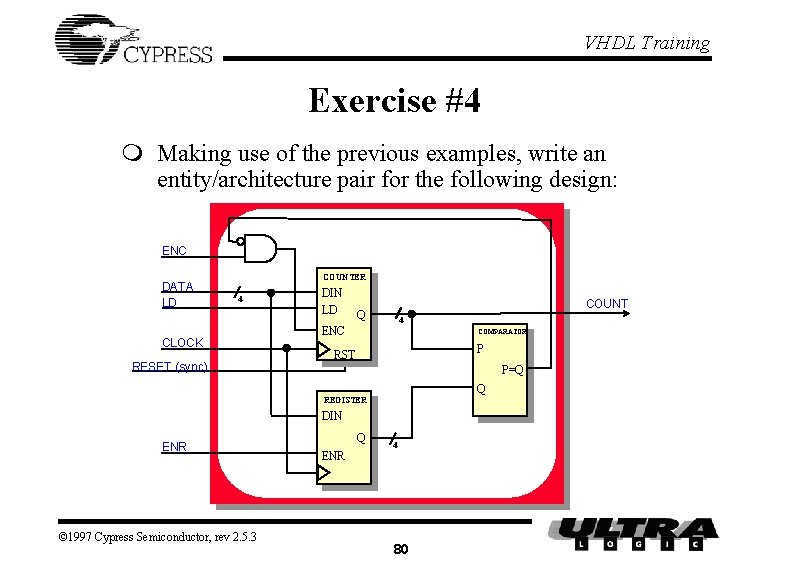

VHDL Training Exercise #4 m Making use of the previous examples, write an entity/architecture pair for the following design: ENC DATA LD COUNTER 4 CLOCK RESET (sync) DIN LD COUNT Q 4 ENC COMPARATOR P RST P=Q Q REGISTER DIN ENR © 1997 Cypress Semiconductor, rev 2. 5. 3 Q ENR 4 80

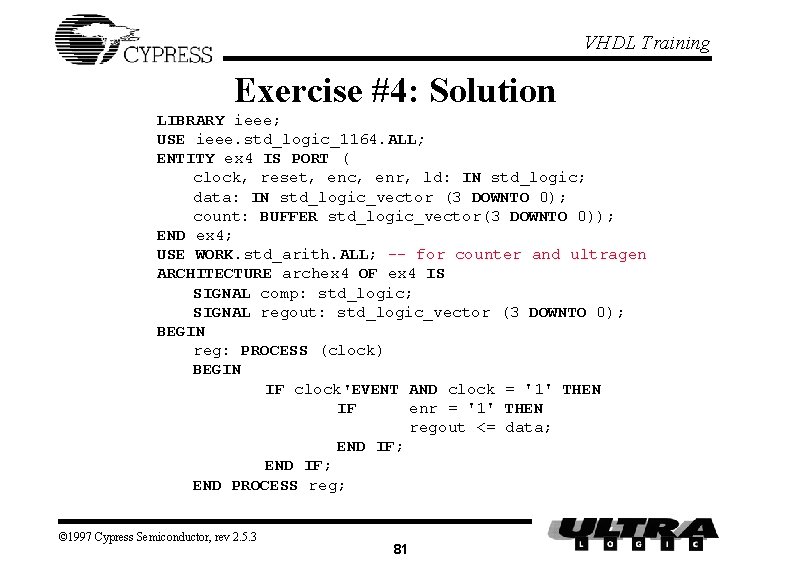

VHDL Training Exercise #4: Solution LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY ex 4 IS PORT ( clock, reset, enc, enr, ld: IN std_logic; data: IN std_logic_vector (3 DOWNTO 0); count: BUFFER std_logic_vector(3 DOWNTO 0)); END ex 4; USE WORK. std_arith. ALL; -- for counter and ultragen ARCHITECTURE archex 4 OF ex 4 IS SIGNAL comp: std_logic; SIGNAL regout: std_logic_vector (3 DOWNTO 0); BEGIN reg: PROCESS (clock) BEGIN IF clock'EVENT AND clock = '1' THEN IF enr = '1' THEN regout <= data; END IF; END PROCESS reg; © 1997 Cypress Semiconductor, rev 2. 5. 3 81

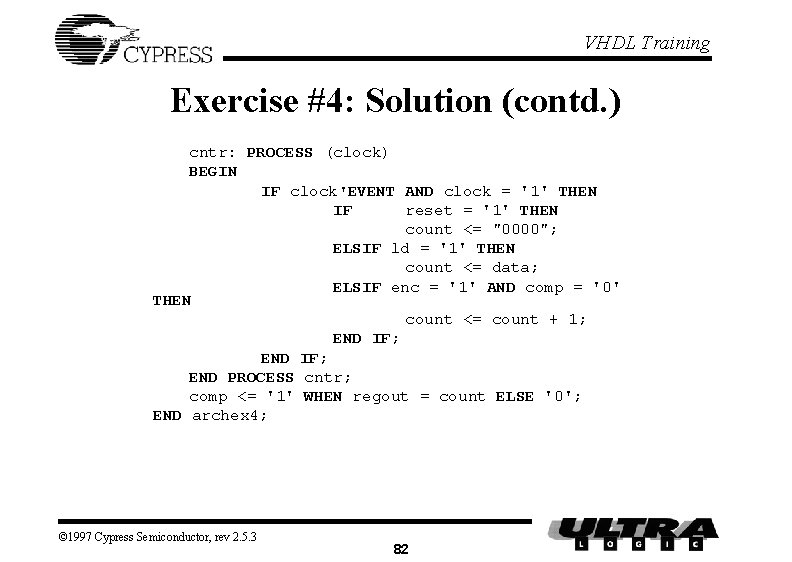

VHDL Training Exercise #4: Solution (contd. ) cntr: PROCESS (clock) BEGIN IF clock'EVENT AND clock = '1' THEN IF reset = '1' THEN count <= "0000"; ELSIF ld = '1' THEN count <= data; ELSIF enc = '1' AND comp = '0' THEN count <= count + 1; END IF; END PROCESS cntr; comp <= '1' WHEN regout = count ELSE '0'; END archex 4; © 1997 Cypress Semiconductor, rev 2. 5. 3 82

VHDL Training State machines m Moore Machines q A finite state machine in which the outputs change due to a change of state m Mealy Machines q A finite state machine in which the outputs can change asynchronously i. e. , an input can cause an output to change immediately © 1997 Cypress Semiconductor, rev 2. 5. 3 83

VHDL Training Moore machines m Outputs may change only with a change of state m Multiple implementations include: q Arbitrary state assignment • outputs must be decoded from the state bits • combinatorial decode • registered decode q Specific state assignment • outputs may be encoded within the state bits • one-hot encoding © 1997 Cypress Semiconductor, rev 2. 5. 3 84

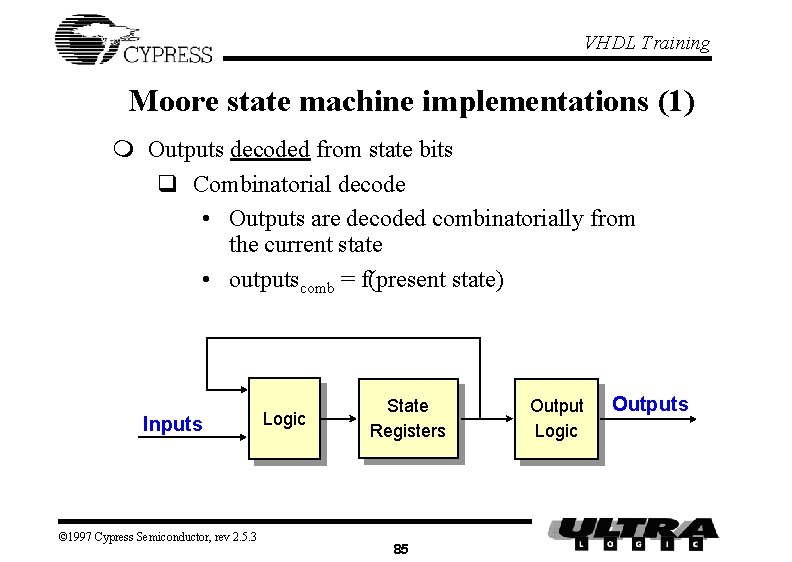

VHDL Training Moore state machine implementations (1) m Outputs decoded from state bits q Combinatorial decode • Outputs are decoded combinatorially from the current state • outputscomb = f(present state) Inputs © 1997 Cypress Semiconductor, rev 2. 5. 3 Logic State Registers 85 Output Logic Outputs

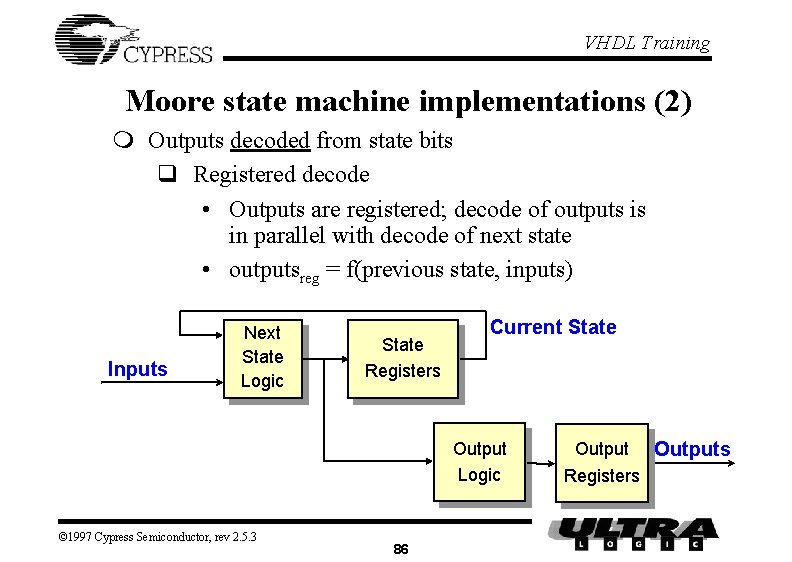

VHDL Training Moore state machine implementations (2) m Outputs decoded from state bits q Registered decode • Outputs are registered; decode of outputs is in parallel with decode of next state • outputsreg = f(previous state, inputs) Inputs Next State Logic State Registers Current State Output Logic © 1997 Cypress Semiconductor, rev 2. 5. 3 86 Outputs Registers

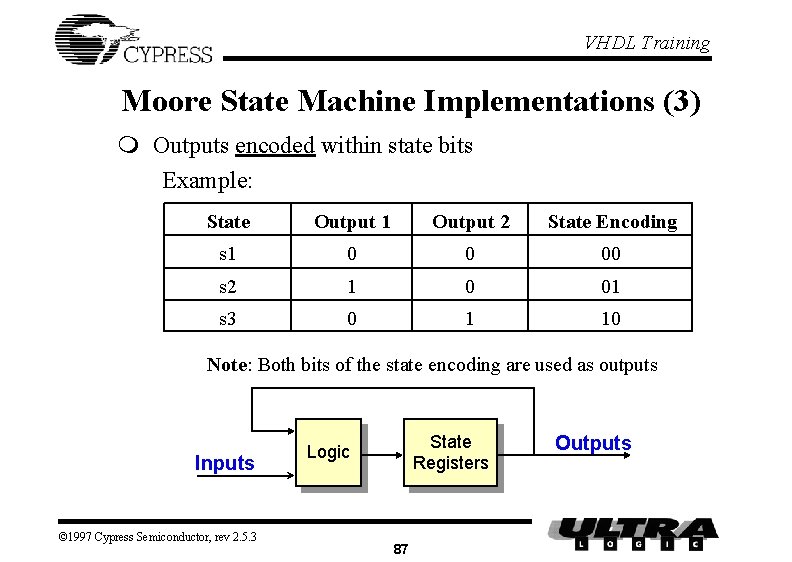

VHDL Training Moore State Machine Implementations (3) m Outputs encoded within state bits Example: State Output 1 Output 2 State Encoding s 1 0 0 00 s 2 1 0 01 s 3 0 1 10 Note: Both bits of the state encoding are used as outputs Inputs © 1997 Cypress Semiconductor, rev 2. 5. 3 State Registers Logic 87 Outputs

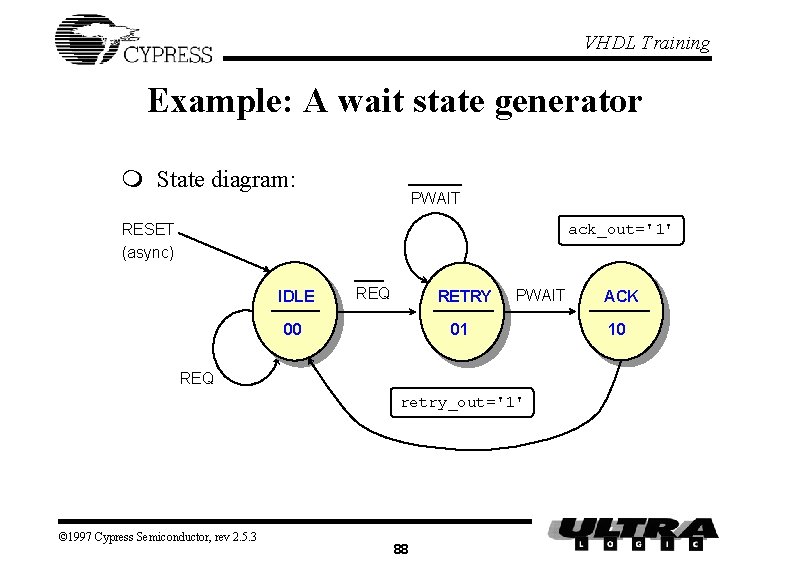

VHDL Training Example: A wait state generator m State diagram: PWAIT RESET (async) ack_out='1' IDLE REQ RETRY 00 PWAIT 01 REQ retry_out='1' © 1997 Cypress Semiconductor, rev 2. 5. 3 88 ACK 10

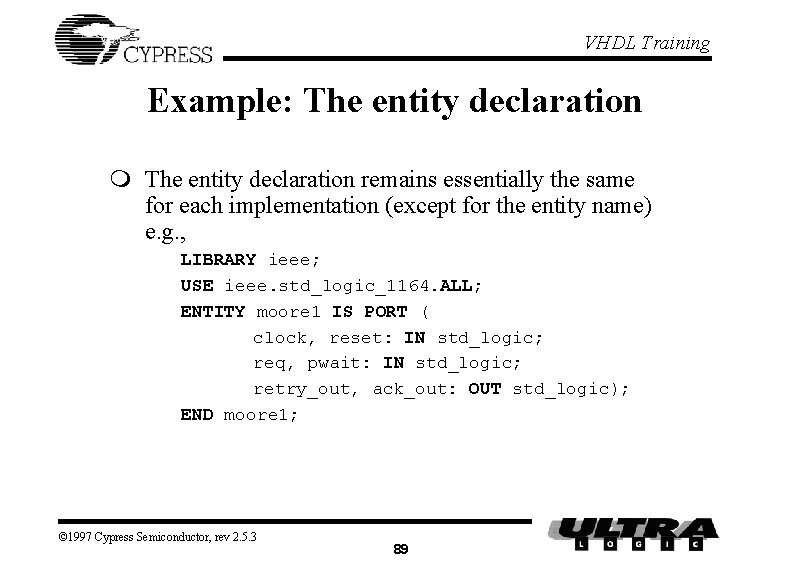

VHDL Training Example: The entity declaration m The entity declaration remains essentially the same for each implementation (except for the entity name) e. g. , LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY moore 1 IS PORT ( clock, reset: IN std_logic; req, pwait: IN std_logic; retry_out, ack_out: OUT std_logic); END moore 1; © 1997 Cypress Semiconductor, rev 2. 5. 3 89

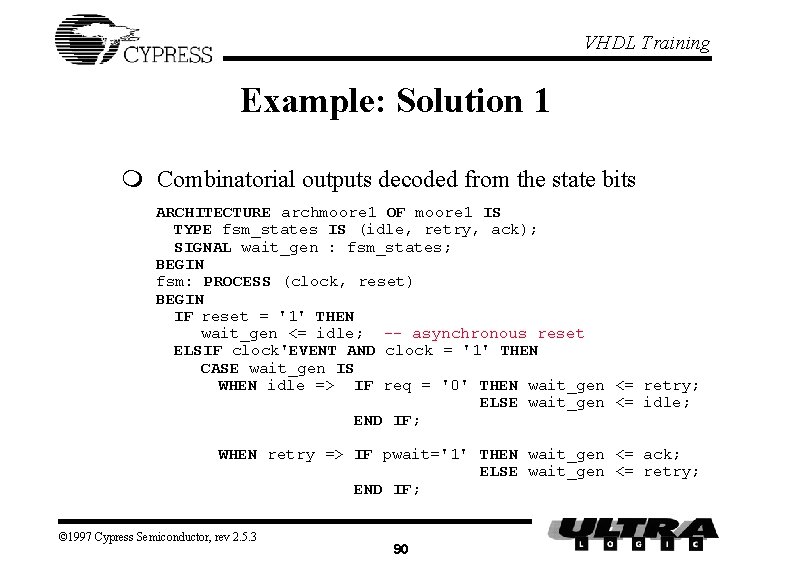

VHDL Training Example: Solution 1 m Combinatorial outputs decoded from the state bits ARCHITECTURE archmoore 1 OF moore 1 IS TYPE fsm_states IS (idle, retry, ack); SIGNAL wait_gen : fsm_states; BEGIN fsm: PROCESS (clock, reset) BEGIN IF reset = '1' THEN wait_gen <= idle; -- asynchronous reset ELSIF clock'EVENT AND clock = '1' THEN CASE wait_gen IS WHEN idle => IF req = '0' THEN wait_gen <= retry; ELSE wait_gen <= idle; END IF; WHEN retry => IF pwait='1' THEN wait_gen <= ack; ELSE wait_gen <= retry; END IF; © 1997 Cypress Semiconductor, rev 2. 5. 3 90

VHDL Training Example: Solution 1 (contd. ) WHEN ack => wait_gen <= idle; WHEN OTHERS => wait_gen <= idle; END CASE; END IF; END PROCESS fsm; retry_out <= '1' WHEN (wait_gen = retry) ELSE '0'; ack_out <= '1' WHEN (wait_gen = ack) ELSE '0'; END archmoore 1; © 1997 Cypress Semiconductor, rev 2. 5. 3 91

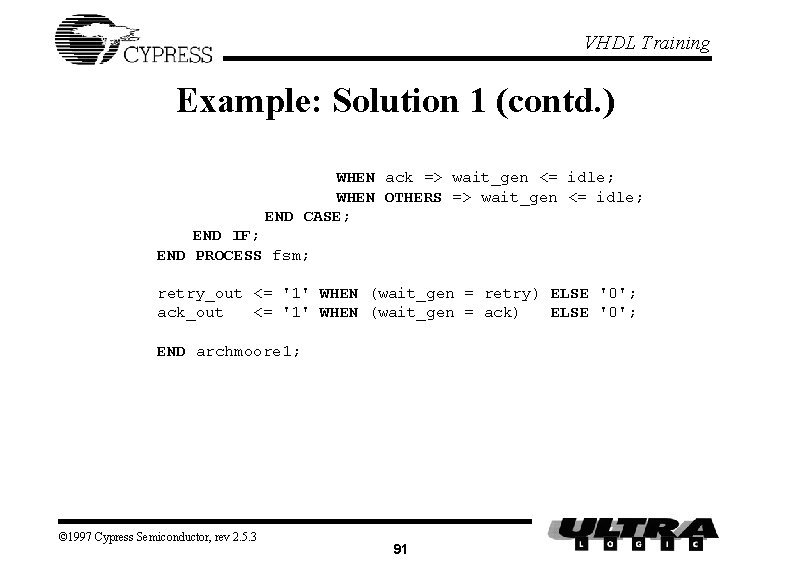

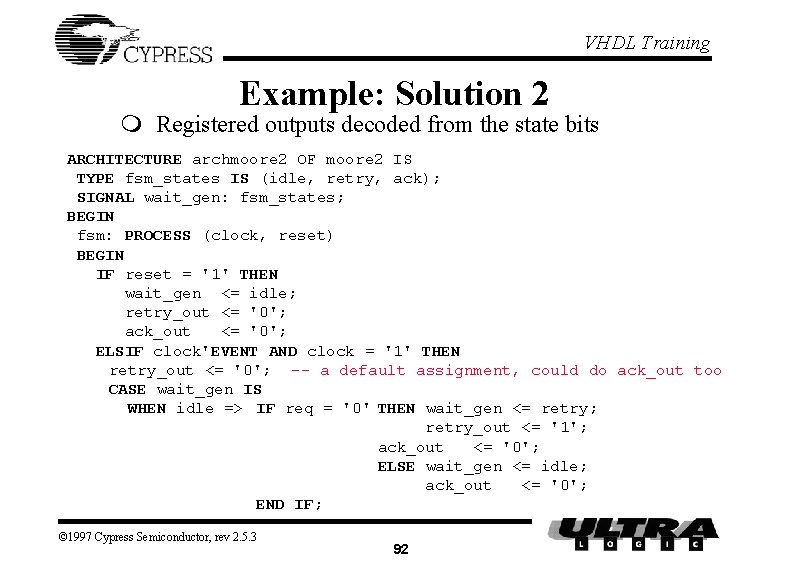

VHDL Training Example: Solution 2 m Registered outputs decoded from the state bits ARCHITECTURE archmoore 2 OF moore 2 IS TYPE fsm_states IS (idle, retry, ack); SIGNAL wait_gen: fsm_states; BEGIN fsm: PROCESS (clock, reset) BEGIN IF reset = '1' THEN wait_gen <= idle; retry_out <= '0'; ack_out <= '0'; ELSIF clock'EVENT AND clock = '1' THEN retry_out <= '0'; -- a default assignment, could do ack_out too CASE wait_gen IS WHEN idle => IF req = '0' THEN wait_gen <= retry; retry_out <= '1'; ack_out <= '0'; ELSE wait_gen <= idle; ack_out <= '0'; END IF; © 1997 Cypress Semiconductor, rev 2. 5. 3 92

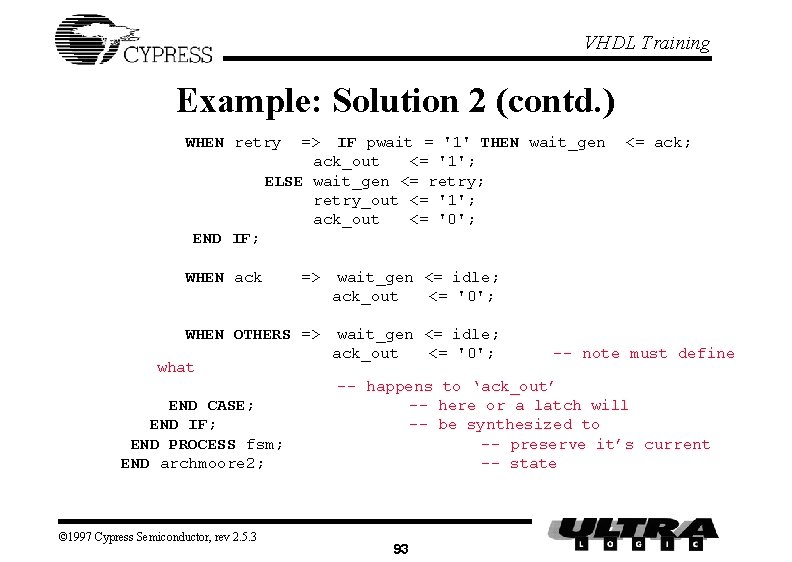

VHDL Training Example: Solution 2 (contd. ) WHEN retry => IF pwait = '1' THEN wait_gen ack_out <= '1'; ELSE wait_gen <= retry; retry_out <= '1'; ack_out <= '0'; <= ack; END IF; WHEN ack => wait_gen <= idle; ack_out <= '0'; WHEN OTHERS => wait_gen <= idle; ack_out <= '0'; what END CASE; END IF; END PROCESS fsm; END archmoore 2; © 1997 Cypress Semiconductor, rev 2. 5. 3 -- note must define -- happens to ‘ack_out’ -- here or a latch will -- be synthesized to -- preserve it’s current -- state 93

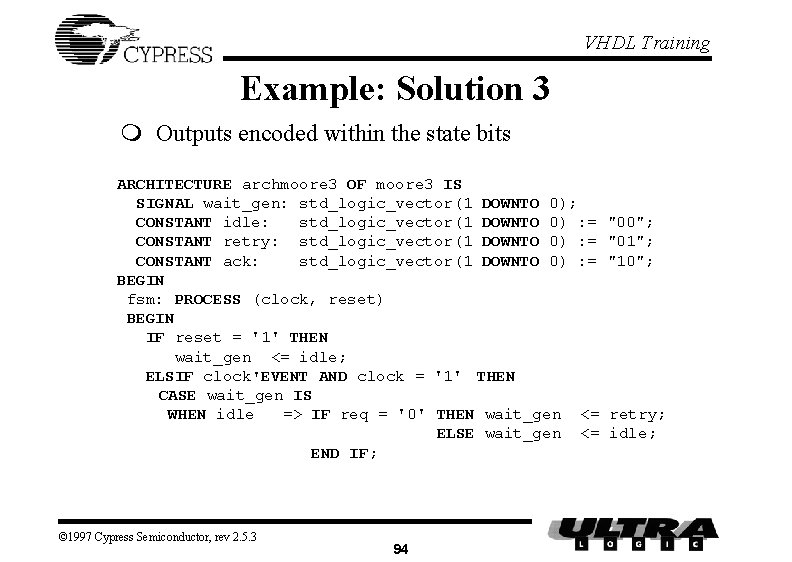

VHDL Training Example: Solution 3 m Outputs encoded within the state bits ARCHITECTURE archmoore 3 OF moore 3 IS SIGNAL wait_gen: std_logic_vector(1 DOWNTO 0); CONSTANT idle: std_logic_vector(1 DOWNTO 0) : = CONSTANT retry: std_logic_vector(1 DOWNTO 0) : = CONSTANT ack: std_logic_vector(1 DOWNTO 0) : = BEGIN fsm: PROCESS (clock, reset) BEGIN IF reset = '1' THEN wait_gen <= idle; ELSIF clock'EVENT AND clock = '1' THEN CASE wait_gen IS WHEN idle => IF req = '0' THEN wait_gen <= ELSE wait_gen <= END IF; © 1997 Cypress Semiconductor, rev 2. 5. 3 94 "00"; "01"; "10"; retry; idle;

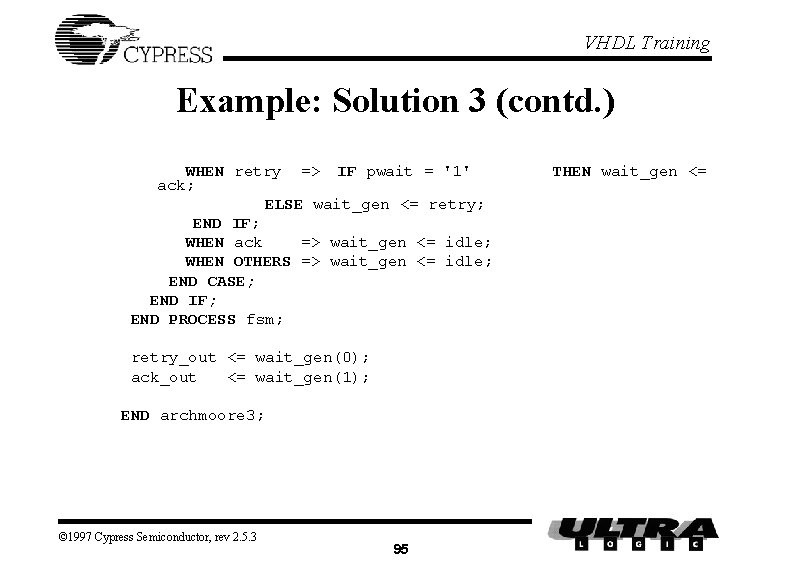

VHDL Training Example: Solution 3 (contd. ) WHEN retry => IF pwait = '1' ack; ELSE wait_gen <= retry; END IF; WHEN ack => wait_gen <= idle; WHEN OTHERS => wait_gen <= idle; END CASE; END IF; END PROCESS fsm; retry_out <= wait_gen(0); ack_out <= wait_gen(1); END archmoore 3; © 1997 Cypress Semiconductor, rev 2. 5. 3 95 THEN wait_gen <=

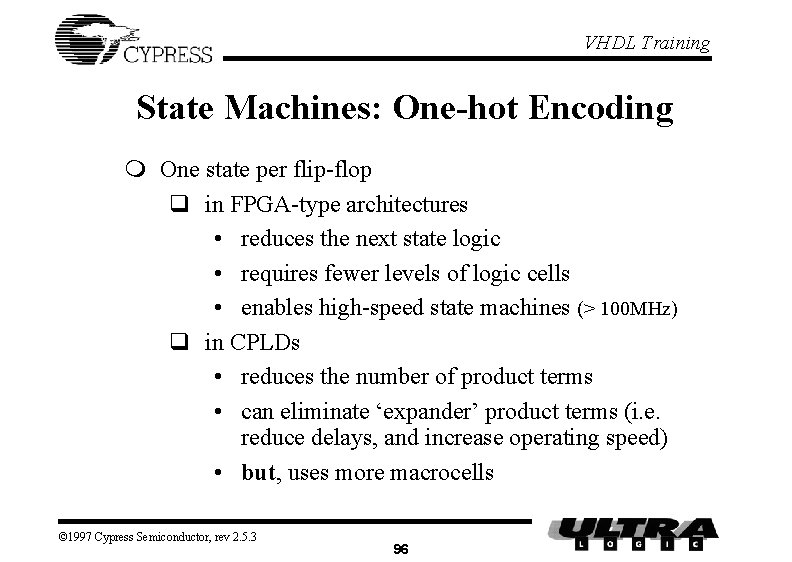

VHDL Training State Machines: One-hot Encoding m One state per flip-flop q in FPGA-type architectures • reduces the next state logic • requires fewer levels of logic cells • enables high-speed state machines (> 100 MHz) q in CPLDs • reduces the number of product terms • can eliminate ‘expander’ product terms (i. e. reduce delays, and increase operating speed) • but, uses more macrocells © 1997 Cypress Semiconductor, rev 2. 5. 3 96

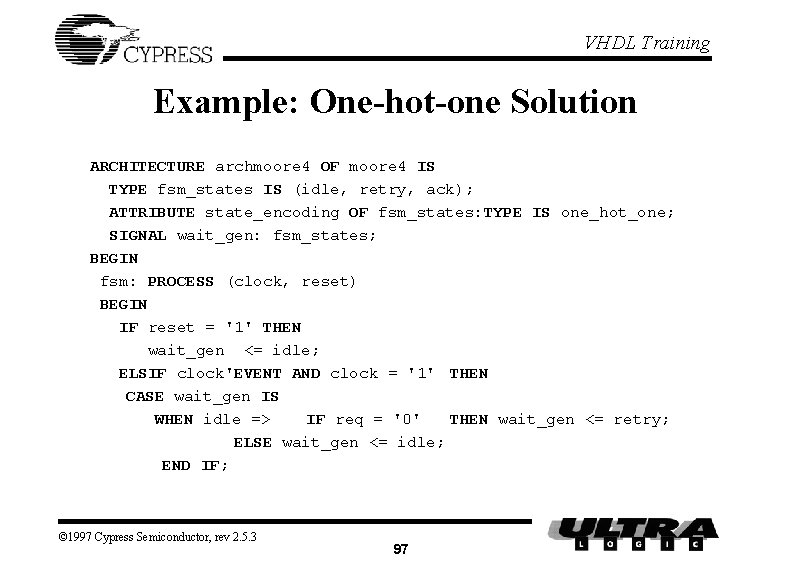

VHDL Training Example: One-hot-one Solution ARCHITECTURE archmoore 4 OF moore 4 IS TYPE fsm_states IS (idle, retry, ack); ATTRIBUTE state_encoding OF fsm_states: TYPE IS one_hot_one; SIGNAL wait_gen: fsm_states; BEGIN fsm: PROCESS (clock, reset) BEGIN IF reset = '1' THEN wait_gen <= idle; ELSIF clock'EVENT AND clock = '1' THEN CASE wait_gen IS WHEN idle => IF req = '0' THEN wait_gen <= retry; ELSE wait_gen <= idle; END IF; © 1997 Cypress Semiconductor, rev 2. 5. 3 97

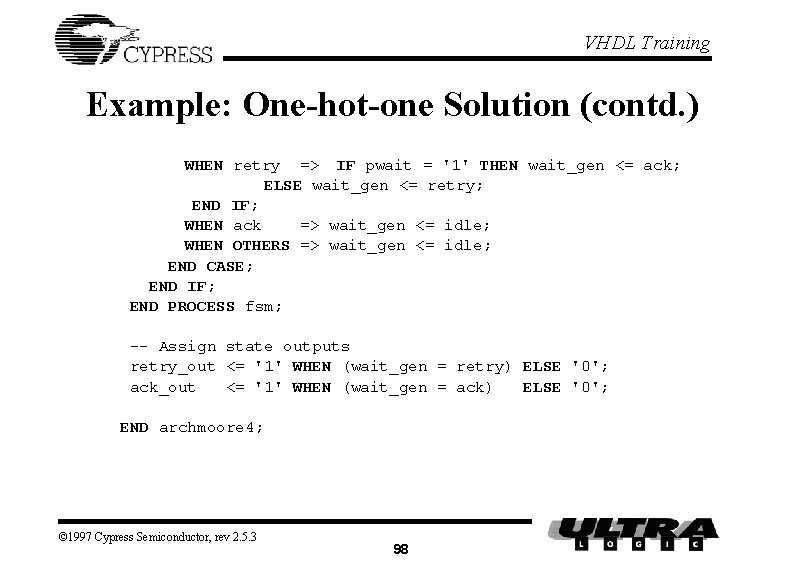

VHDL Training Example: One-hot-one Solution (contd. ) WHEN retry => IF pwait = '1' THEN wait_gen <= ack; ELSE wait_gen <= retry; END IF; WHEN ack => wait_gen <= idle; WHEN OTHERS => wait_gen <= idle; END CASE; END IF; END PROCESS fsm; -- Assign state outputs retry_out <= '1' WHEN (wait_gen = retry) ELSE '0'; ack_out <= '1' WHEN (wait_gen = ack) ELSE '0'; END archmoore 4; © 1997 Cypress Semiconductor, rev 2. 5. 3 98

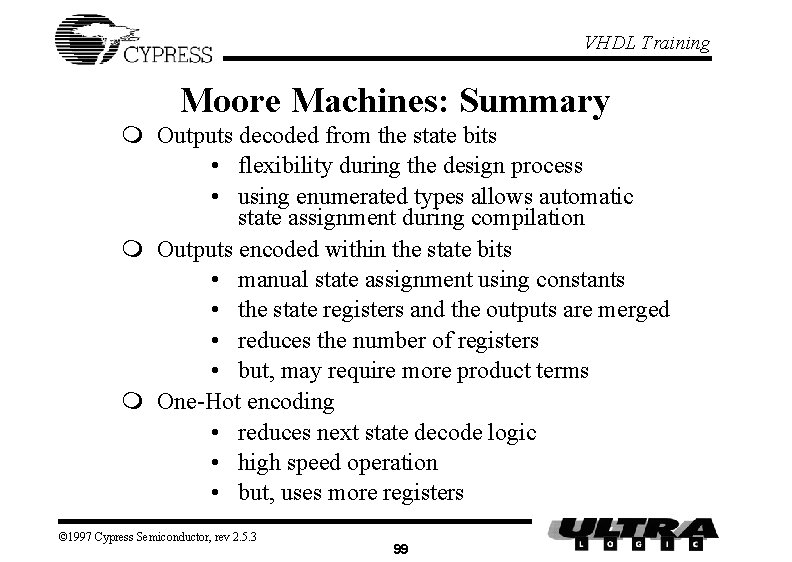

VHDL Training Moore Machines: Summary m Outputs decoded from the state bits • flexibility during the design process • using enumerated types allows automatic state assignment during compilation m Outputs encoded within the state bits • manual state assignment using constants • the state registers and the outputs are merged • reduces the number of registers • but, may require more product terms m One-Hot encoding • reduces next state decode logic • high speed operation • but, uses more registers © 1997 Cypress Semiconductor, rev 2. 5. 3 99

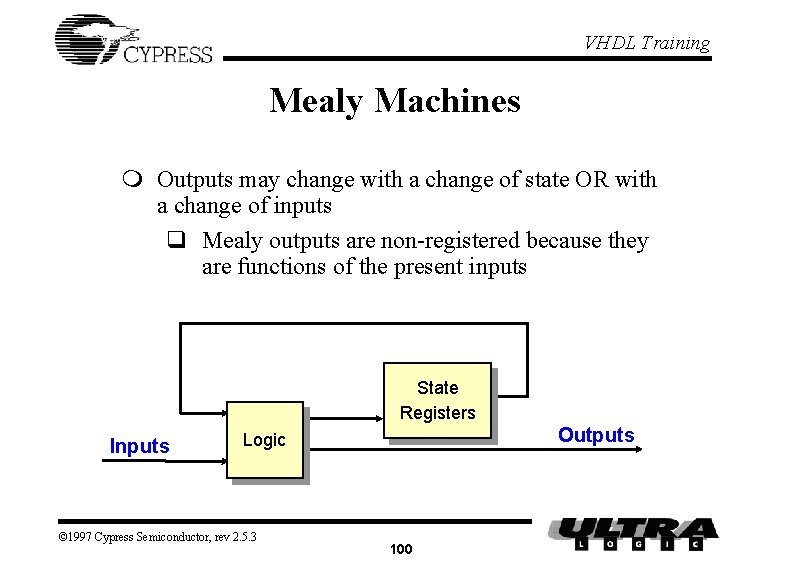

VHDL Training Mealy Machines m Outputs may change with a change of state OR with a change of inputs q Mealy outputs are non-registered because they are functions of the present inputs State Registers Inputs Outputs Logic © 1997 Cypress Semiconductor, rev 2. 5. 3 100

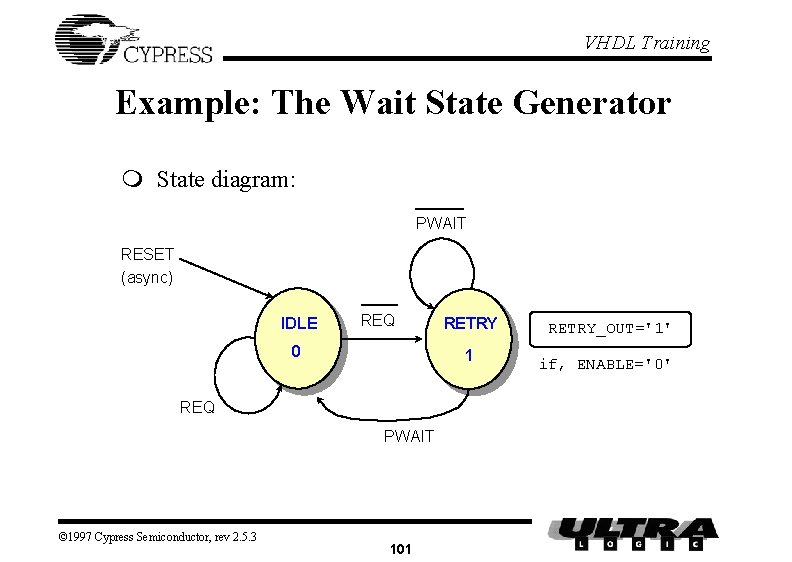

VHDL Training Example: The Wait State Generator m State diagram: PWAIT RESET (async) IDLE REQ 0 1 REQ PWAIT © 1997 Cypress Semiconductor, rev 2. 5. 3 RETRY 101 RETRY_OUT='1' if, ENABLE='0'

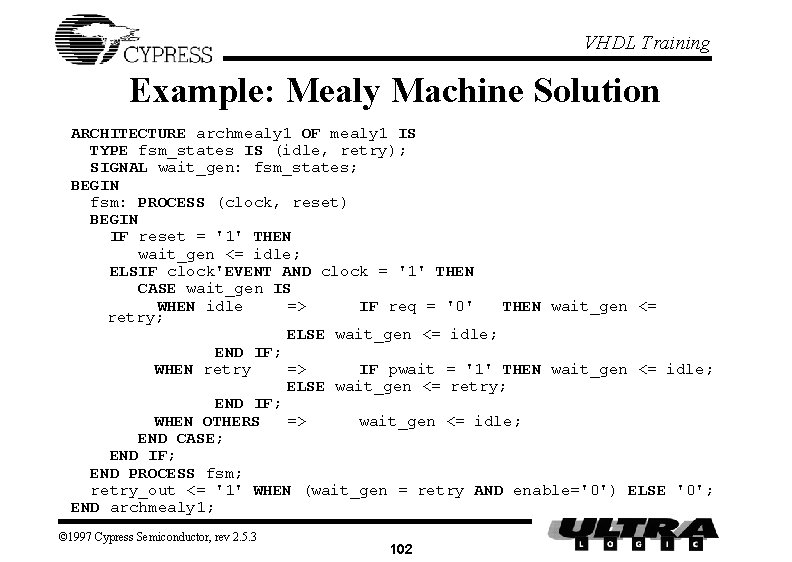

VHDL Training Example: Mealy Machine Solution ARCHITECTURE archmealy 1 OF mealy 1 IS TYPE fsm_states IS (idle, retry); SIGNAL wait_gen: fsm_states; BEGIN fsm: PROCESS (clock, reset) BEGIN IF reset = '1' THEN wait_gen <= idle; ELSIF clock'EVENT AND clock = '1' THEN CASE wait_gen IS WHEN idle => IF req = '0' THEN wait_gen <= retry; ELSE wait_gen <= idle; END IF; WHEN retry => IF pwait = '1' THEN wait_gen <= idle; ELSE wait_gen <= retry; END IF; WHEN OTHERS => wait_gen <= idle; END CASE; END IF; END PROCESS fsm; retry_out <= '1' WHEN (wait_gen = retry AND enable='0') ELSE '0'; END archmealy 1; © 1997 Cypress Semiconductor, rev 2. 5. 3 102

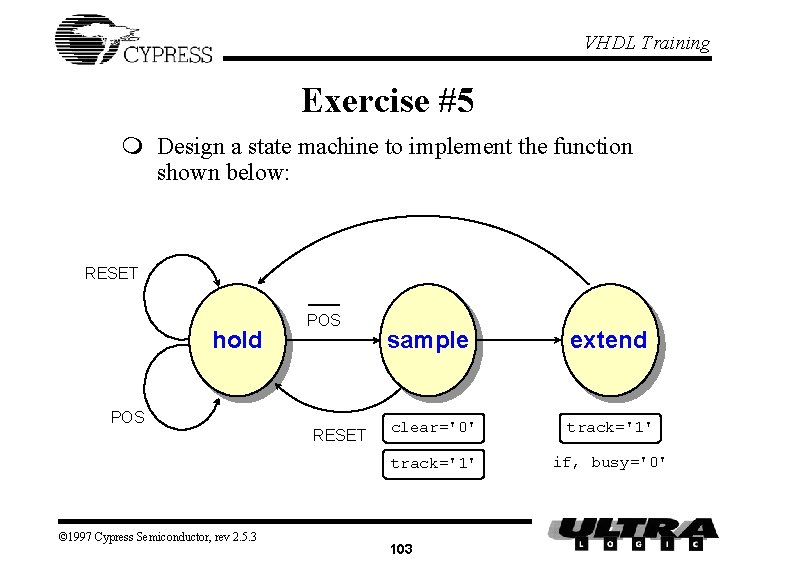

VHDL Training Exercise #5 m Design a state machine to implement the function shown below: RESET hold POS RESET © 1997 Cypress Semiconductor, rev 2. 5. 3 sample extend clear='0' track='1' if, busy='0' 103

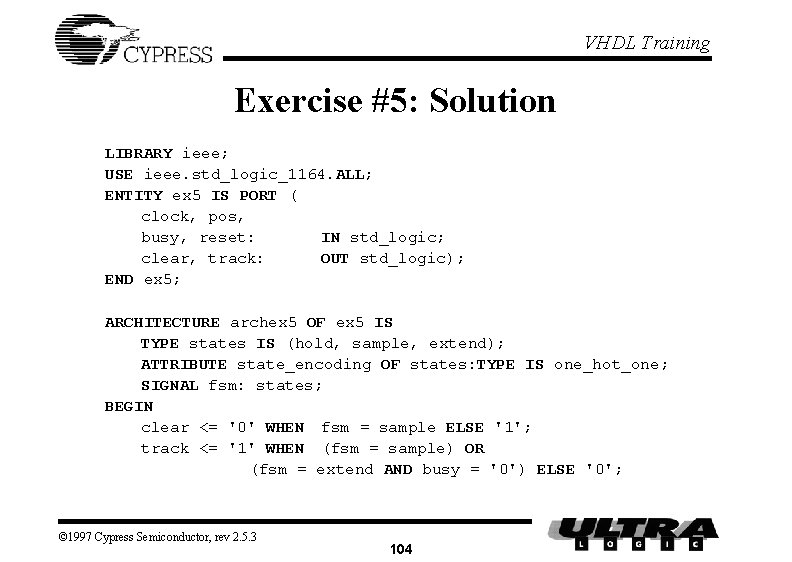

VHDL Training Exercise #5: Solution LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY ex 5 IS PORT ( clock, pos, busy, reset: IN std_logic; clear, track: OUT std_logic); END ex 5; ARCHITECTURE archex 5 OF ex 5 IS TYPE states IS (hold, sample, extend); ATTRIBUTE state_encoding OF states: TYPE IS one_hot_one; SIGNAL fsm: states; BEGIN clear <= '0' WHEN fsm = sample ELSE '1'; track <= '1' WHEN (fsm = sample) OR (fsm = extend AND busy = '0') ELSE '0'; © 1997 Cypress Semiconductor, rev 2. 5. 3 104

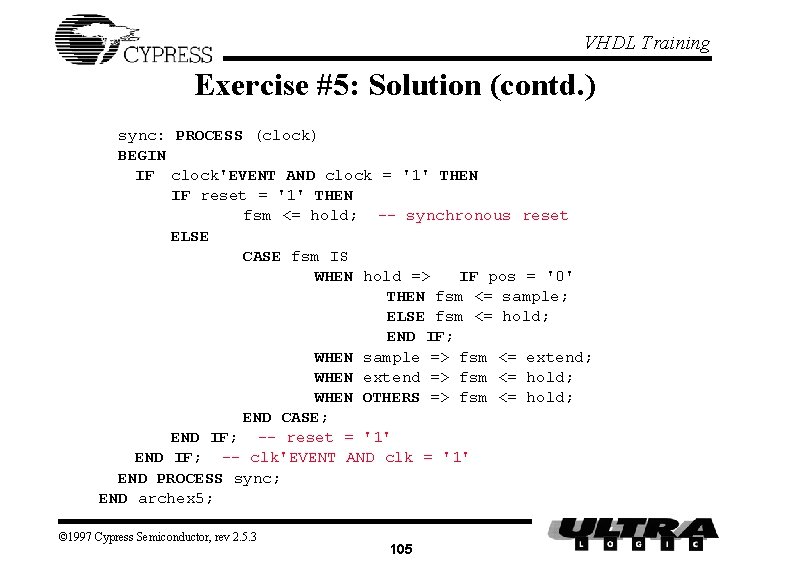

VHDL Training Exercise #5: Solution (contd. ) sync: PROCESS (clock) BEGIN IF clock'EVENT AND clock = '1' THEN IF reset = '1' THEN fsm <= hold; -- synchronous reset ELSE CASE fsm IS WHEN hold => IF pos = '0' THEN fsm <= sample; ELSE fsm <= hold; END IF; WHEN sample => fsm <= extend; WHEN extend => fsm <= hold; WHEN OTHERS => fsm <= hold; END CASE; END IF; -- reset = '1' END IF; -- clk'EVENT AND clk = '1' END PROCESS sync; END archex 5; © 1997 Cypress Semiconductor, rev 2. 5. 3 105

VHDL Training Hierarchical design methodology m Advantages: q Allows the re-use of common building blocks q Components (VHDL models or schematic symbols) can be created, tested and held for later use q Smaller components can be more easily integrated with other blocks q Designs are more readable q Designs are more portable q The design task can be split among several members of a team © 1997 Cypress Semiconductor, rev 2. 5. 3 106

VHDL Training Hierarchy decomposition m A VHDL hierarchy is composed of q COMPONENTs • declarations of VHDL models which can be instantiated (placed) within other models q PACKAGEs • a collection of one or more COMPONENT (and other) declarations © 1997 Cypress Semiconductor, rev 2. 5. 3 107

VHDL Training Packages and hierarchical designs m Packages contain components, types, and/or subtypes which can be used in other designs m Components are entity/architecture pairs with component declarations m Designs that make use of components or types in packages must include a USE clause, e. g. , USE WORK. my_package. ALL; q The above allows the VHDL code to instantiate all components/types in my_package USE WORK. my_package. cnt 4; q The above allows the VHDL code to instantiate only the cnt 4 components in my_package © 1997 Cypress Semiconductor, rev 2. 5. 3 108

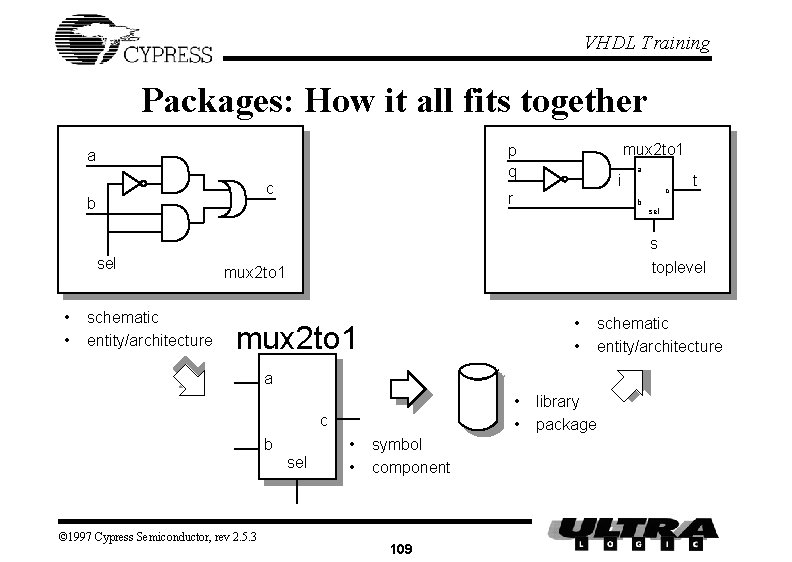

VHDL Training Packages: How it all fits together c b sel • • schematic entity/architecture mux 2 to 1 p q a i r c t b sel s toplevel mux 2 to 1 • • mux 2 to 1 a • • c b sel © 1997 Cypress Semiconductor, rev 2. 5. 3 a • • symbol component 109 library package schematic entity/architecture

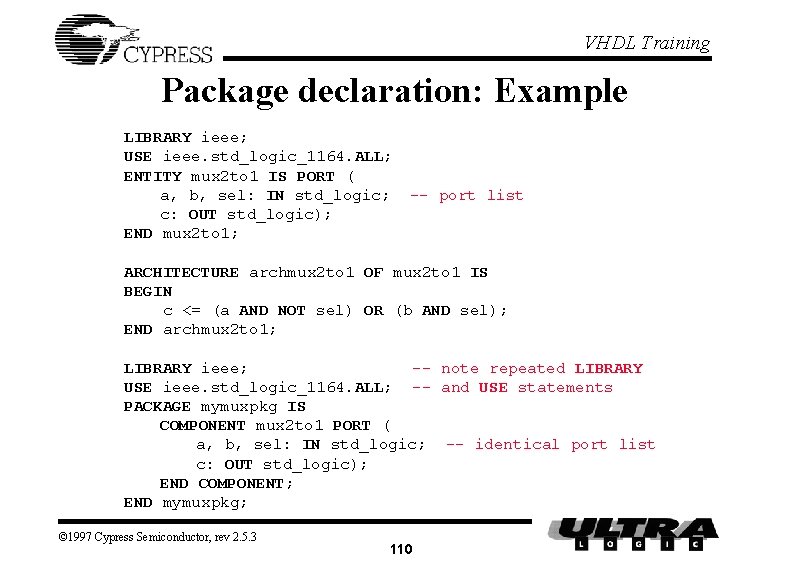

VHDL Training Package declaration: Example LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY mux 2 to 1 IS PORT ( a, b, sel: IN std_logic; c: OUT std_logic); END mux 2 to 1; -- port list ARCHITECTURE archmux 2 to 1 OF mux 2 to 1 IS BEGIN c <= (a AND NOT sel) OR (b AND sel); END archmux 2 to 1; LIBRARY ieee; -- note repeated LIBRARY USE ieee. std_logic_1164. ALL; -- and USE statements PACKAGE mymuxpkg IS COMPONENT mux 2 to 1 PORT ( a, b, sel: IN std_logic; -- identical port list c: OUT std_logic); END COMPONENT; END mymuxpkg; © 1997 Cypress Semiconductor, rev 2. 5. 3 110

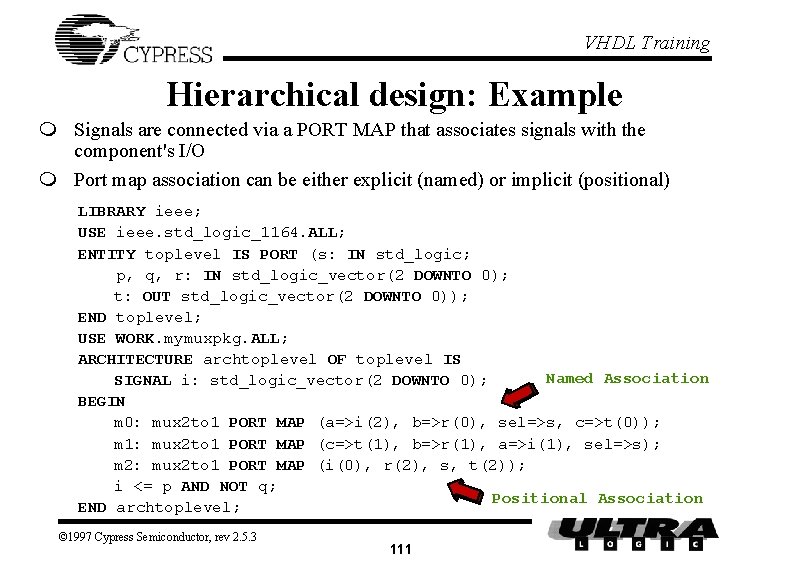

VHDL Training Hierarchical design: Example m Signals are connected via a PORT MAP that associates signals with the component's I/O m Port map association can be either explicit (named) or implicit (positional) LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY toplevel IS PORT (s: IN std_logic; p, q, r: IN std_logic_vector(2 DOWNTO 0); t: OUT std_logic_vector(2 DOWNTO 0)); END toplevel; USE WORK. mymuxpkg. ALL; ARCHITECTURE archtoplevel OF toplevel IS Named Association SIGNAL i: std_logic_vector(2 DOWNTO 0); BEGIN m 0: mux 2 to 1 PORT MAP (a=>i(2), b=>r(0), sel=>s, c=>t(0)); m 1: mux 2 to 1 PORT MAP (c=>t(1), b=>r(1), a=>i(1), sel=>s); m 2: mux 2 to 1 PORT MAP (i(0), r(2), s, t(2)); i <= p AND NOT q; Positional Association END archtoplevel; © 1997 Cypress Semiconductor, rev 2. 5. 3 111

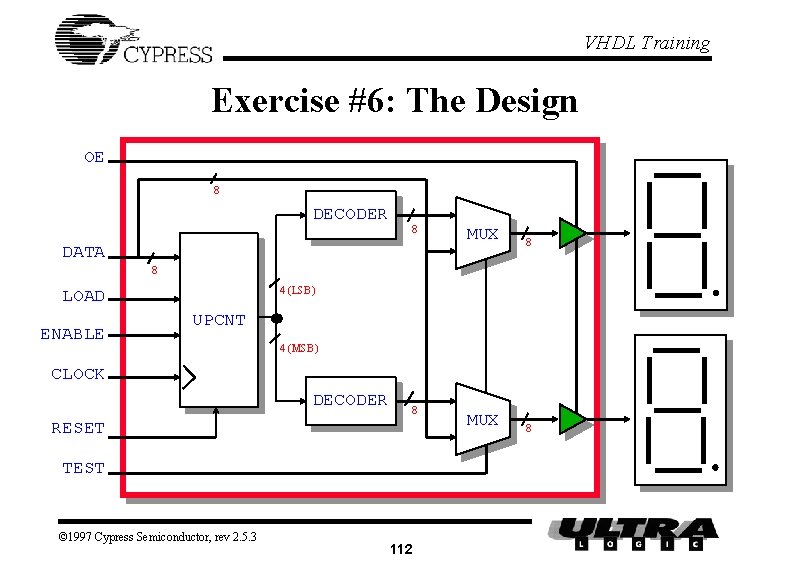

VHDL Training Exercise #6: The Design OE 8 DECODER 8 DATA MUX 8 8 4 (LSB) LOAD ENABLE UPCNT 4 (MSB) CLOCK DECODER 8 RESET TEST © 1997 Cypress Semiconductor, rev 2. 5. 3 112

VHDL Training Exercise #6 m Write a hierarchical VHDL description of the previous schematic which instantiates all of the components shown in the design q entity/architecture given for top-level design q package/entity/architecture given for decoder q entity/architecture given for counter, write package m The target device is a CY 7 C 371 I-143 JC m Compile and synthesize your design using Warp © 1997 Cypress Semiconductor, rev 2. 5. 3 113

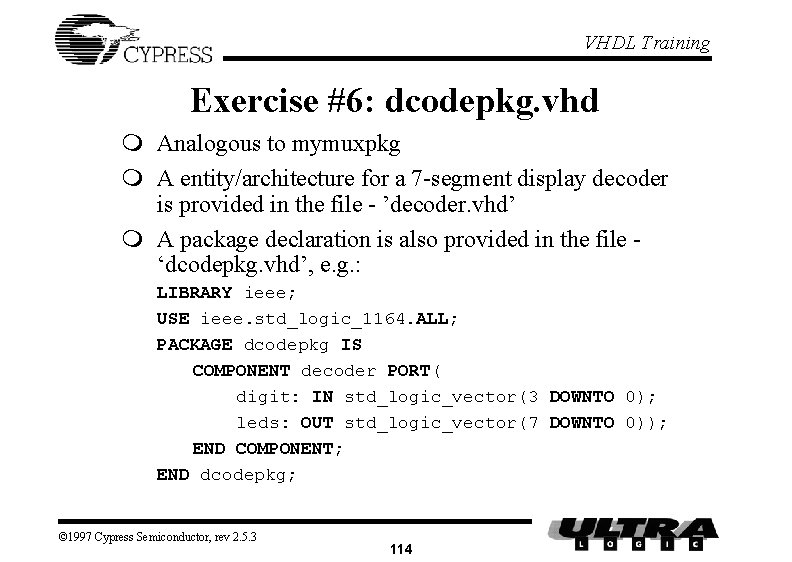

VHDL Training Exercise #6: dcodepkg. vhd m Analogous to mymuxpkg m A entity/architecture for a 7 -segment display decoder is provided in the file - ’decoder. vhd’ m A package declaration is also provided in the file ‘dcodepkg. vhd’, e. g. : LIBRARY ieee; USE ieee. std_logic_1164. ALL; PACKAGE dcodepkg IS COMPONENT decoder PORT( digit: IN std_logic_vector(3 DOWNTO 0); leds: OUT std_logic_vector(7 DOWNTO 0)); END COMPONENT; END dcodepkg; © 1997 Cypress Semiconductor, rev 2. 5. 3 114

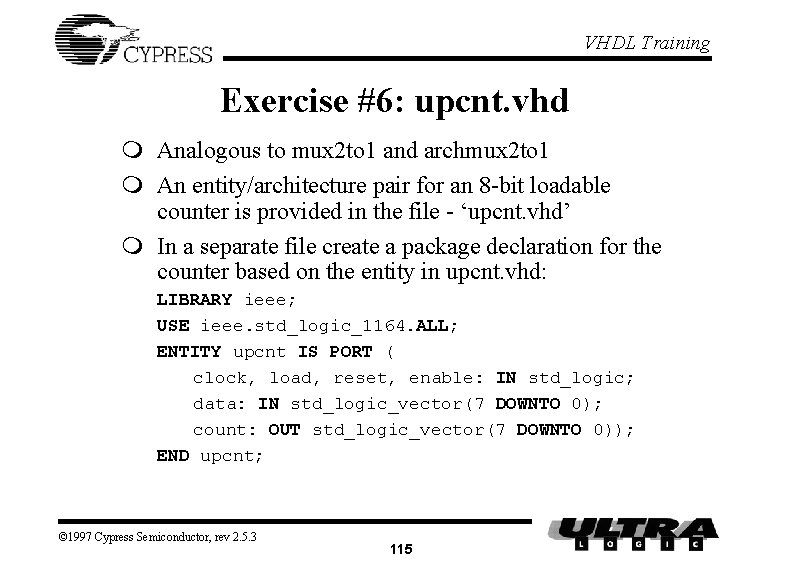

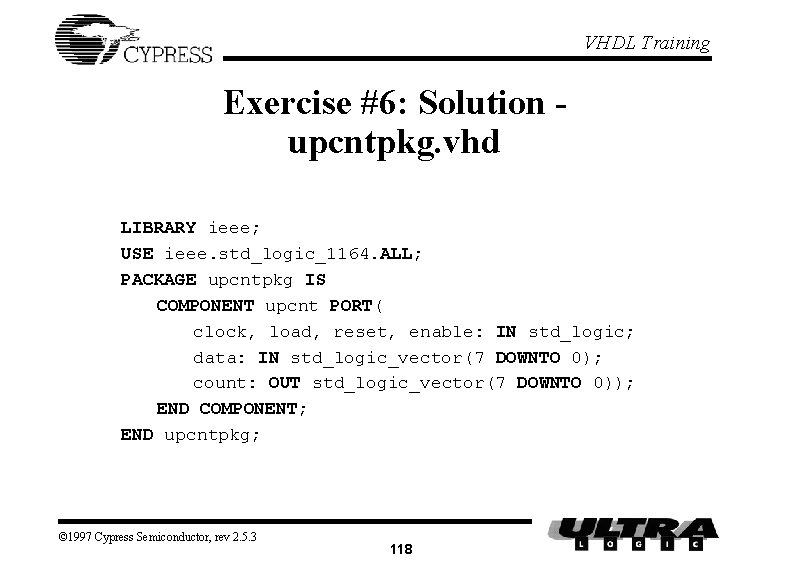

VHDL Training Exercise #6: upcnt. vhd m Analogous to mux 2 to 1 and archmux 2 to 1 m An entity/architecture pair for an 8 -bit loadable counter is provided in the file - ‘upcnt. vhd’ m In a separate file create a package declaration for the counter based on the entity in upcnt. vhd: LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY upcnt IS PORT ( clock, load, reset, enable: IN std_logic; data: IN std_logic_vector(7 DOWNTO 0); count: OUT std_logic_vector(7 DOWNTO 0)); END upcnt; © 1997 Cypress Semiconductor, rev 2. 5. 3 115

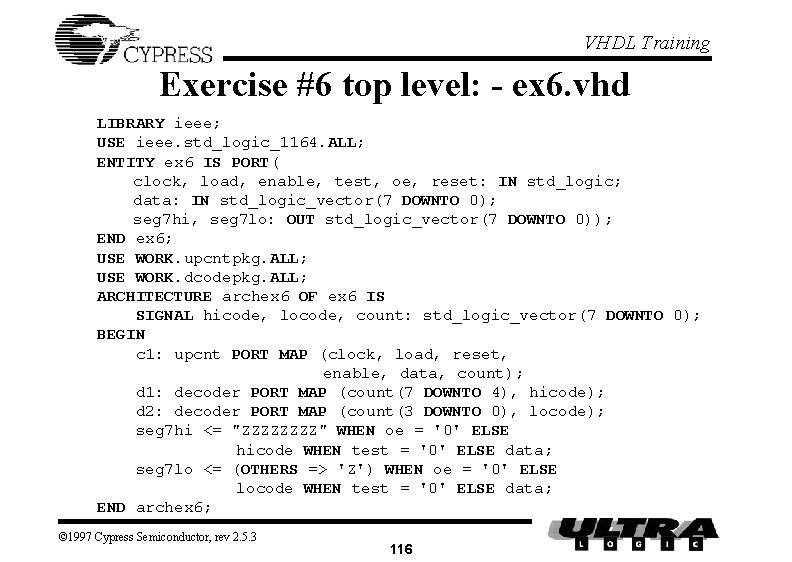

VHDL Training Exercise #6 top level: - ex 6. vhd LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY ex 6 IS PORT( clock, load, enable, test, oe, reset: IN std_logic; data: IN std_logic_vector(7 DOWNTO 0); seg 7 hi, seg 7 lo: OUT std_logic_vector(7 DOWNTO 0)); END ex 6; USE WORK. upcntpkg. ALL; USE WORK. dcodepkg. ALL; ARCHITECTURE archex 6 OF ex 6 IS SIGNAL hicode, locode, count: std_logic_vector(7 DOWNTO 0); BEGIN c 1: upcnt PORT MAP (clock, load, reset, enable, data, count); d 1: decoder PORT MAP (count(7 DOWNTO 4), hicode); d 2: decoder PORT MAP (count(3 DOWNTO 0), locode); seg 7 hi <= "ZZZZ" WHEN oe = '0' ELSE hicode WHEN test = '0' ELSE data; seg 7 lo <= (OTHERS => 'Z') WHEN oe = '0' ELSE locode WHEN test = '0' ELSE data; END archex 6; © 1997 Cypress Semiconductor, rev 2. 5. 3 116

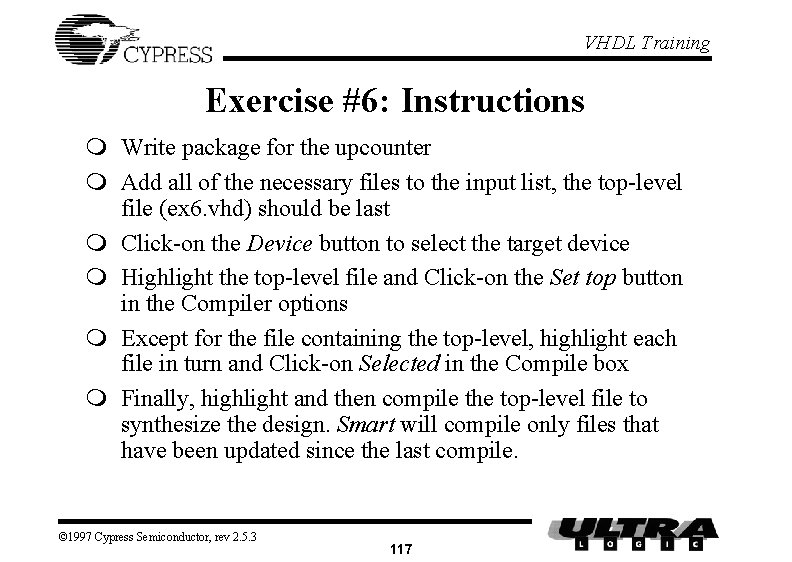

VHDL Training Exercise #6: Instructions m Write package for the upcounter m Add all of the necessary files to the input list, the top-level file (ex 6. vhd) should be last m Click-on the Device button to select the target device m Highlight the top-level file and Click-on the Set top button in the Compiler options m Except for the file containing the top-level, highlight each file in turn and Click-on Selected in the Compile box m Finally, highlight and then compile the top-level file to synthesize the design. Smart will compile only files that have been updated since the last compile. © 1997 Cypress Semiconductor, rev 2. 5. 3 117

VHDL Training Exercise #6: Solution upcntpkg. vhd LIBRARY ieee; USE ieee. std_logic_1164. ALL; PACKAGE upcntpkg IS COMPONENT upcnt PORT( clock, load, reset, enable: IN std_logic; data: IN std_logic_vector(7 DOWNTO 0); count: OUT std_logic_vector(7 DOWNTO 0)); END COMPONENT; END upcntpkg; © 1997 Cypress Semiconductor, rev 2. 5. 3 118

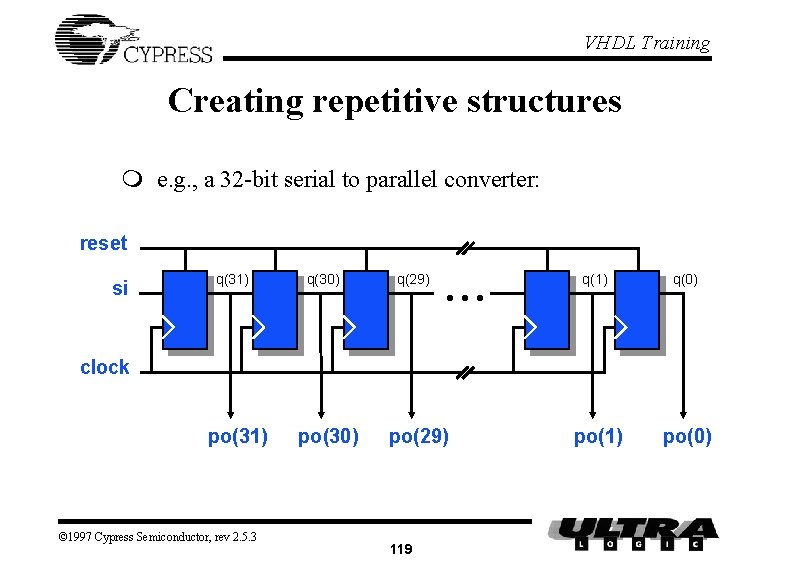

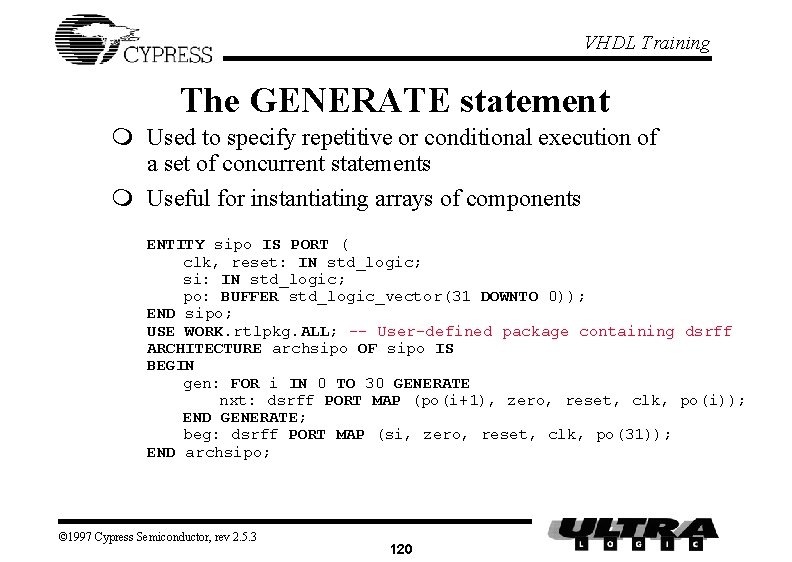

VHDL Training Creating repetitive structures m e. g. , a 32 -bit serial to parallel converter: reset si q(31) q(30) q(29) • • • q(1) q(0) po(1) po(0) clock po(31) © 1997 Cypress Semiconductor, rev 2. 5. 3 po(30) po(29) 119

VHDL Training The GENERATE statement m Used to specify repetitive or conditional execution of a set of concurrent statements m Useful for instantiating arrays of components ENTITY sipo IS PORT ( clk, reset: IN std_logic; si: IN std_logic; po: BUFFER std_logic_vector(31 DOWNTO 0)); END sipo; USE WORK. rtlpkg. ALL; -- User-defined package containing dsrff ARCHITECTURE archsipo OF sipo IS BEGIN gen: FOR i IN 0 TO 30 GENERATE nxt: dsrff PORT MAP (po(i+1), zero, reset, clk, po(i)); END GENERATE; beg: dsrff PORT MAP (si, zero, reset, clk, po(31)); END archsipo; © 1997 Cypress Semiconductor, rev 2. 5. 3 120

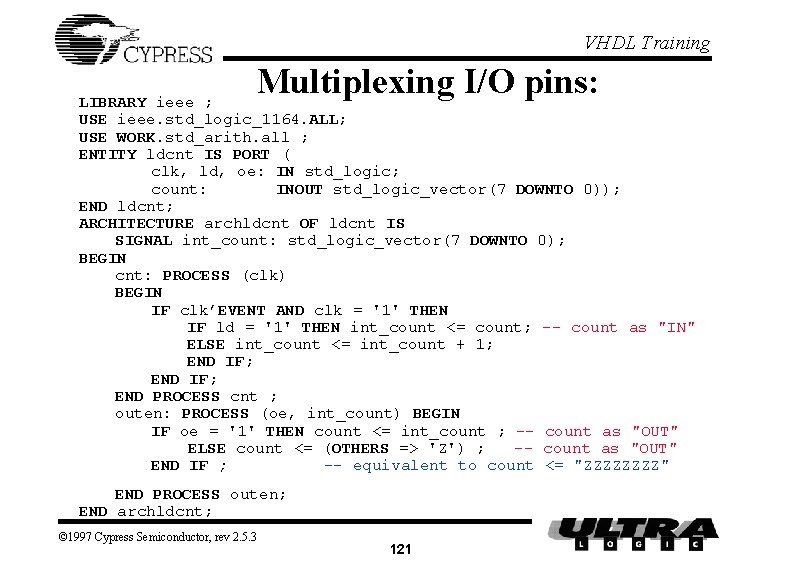

VHDL Training Multiplexing I/O pins: LIBRARY ieee ; USE ieee. std_logic_1164. ALL; USE WORK. std_arith. all ; ENTITY ldcnt IS PORT ( clk, ld, oe: IN std_logic; count: INOUT std_logic_vector(7 DOWNTO 0)); END ldcnt; ARCHITECTURE archldcnt OF ldcnt IS SIGNAL int_count: std_logic_vector(7 DOWNTO 0); BEGIN cnt: PROCESS (clk) BEGIN IF clk’EVENT AND clk = '1' THEN IF ld = '1' THEN int_count <= count; -- count as "IN" ELSE int_count <= int_count + 1; END IF; END PROCESS cnt ; outen: PROCESS (oe, int_count) BEGIN IF oe = '1' THEN count <= int_count ; -- count as "OUT" ELSE count <= (OTHERS => 'Z') ; -- count as "OUT" END IF ; -- equivalent to count <= "ZZZZ" END PROCESS outen; END archldcnt; © 1997 Cypress Semiconductor, rev 2. 5. 3 121

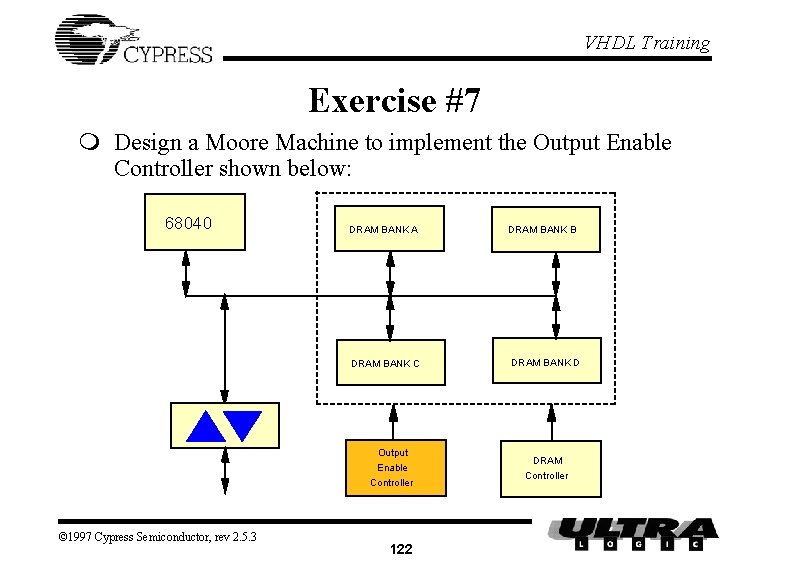

VHDL Training Exercise #7 m Design a Moore Machine to implement the Output Enable Controller shown below: 68040 DRAM BANK A DRAM BANK C Output Enable Controller © 1997 Cypress Semiconductor, rev 2. 5. 3 122 DRAM BANK B DRAM BANK D DRAM Controller

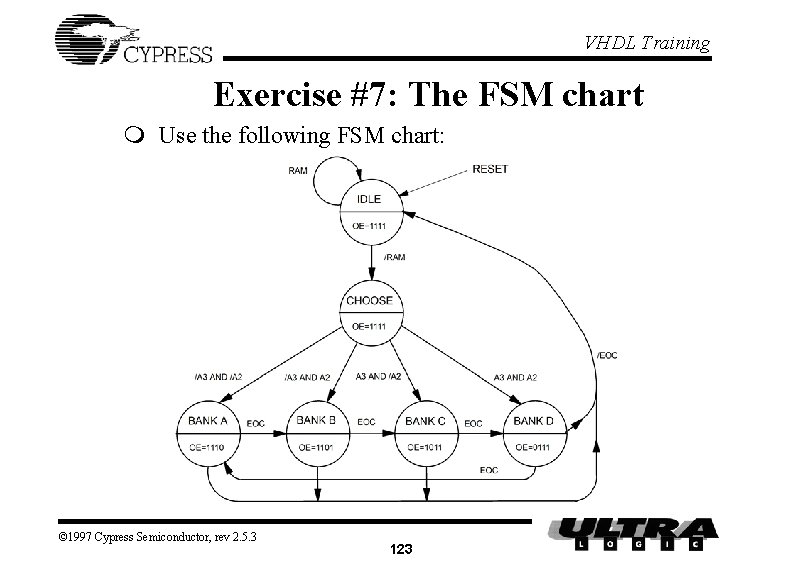

VHDL Training Exercise #7: The FSM chart m Use the following FSM chart: © 1997 Cypress Semiconductor, rev 2. 5. 3 123

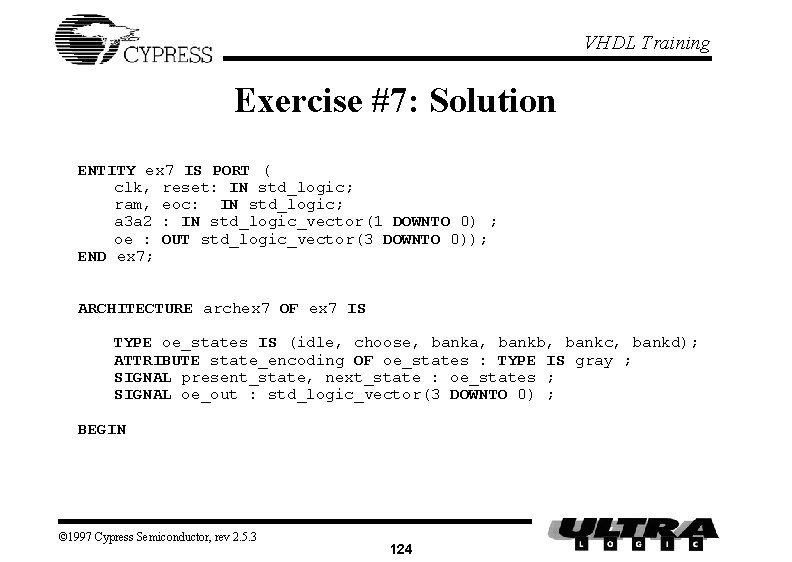

VHDL Training Exercise #7: Solution ENTITY ex 7 IS PORT ( clk, reset: IN std_logic; ram, eoc: IN std_logic; a 3 a 2 : IN std_logic_vector(1 DOWNTO 0) ; oe : OUT std_logic_vector(3 DOWNTO 0)); END ex 7; ARCHITECTURE archex 7 OF ex 7 IS TYPE oe_states IS (idle, choose, banka, bankb, bankc, bankd); ATTRIBUTE state_encoding OF oe_states : TYPE IS gray ; SIGNAL present_state, next_state : oe_states ; SIGNAL oe_out : std_logic_vector(3 DOWNTO 0) ; BEGIN © 1997 Cypress Semiconductor, rev 2. 5. 3 124

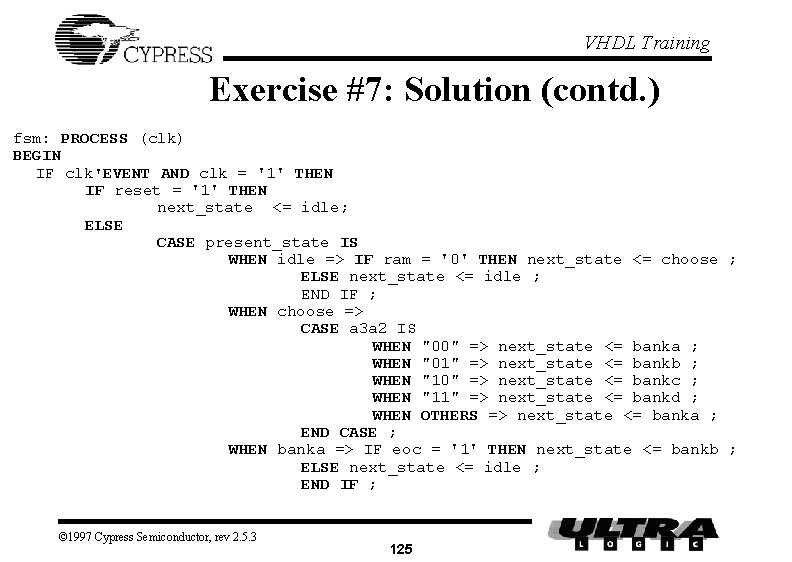

VHDL Training Exercise #7: Solution (contd. ) fsm: PROCESS (clk) BEGIN IF clk'EVENT AND clk = '1' THEN IF reset = '1' THEN next_state <= idle; ELSE CASE present_state IS WHEN idle => IF ram = '0' THEN next_state <= choose ; ELSE next_state <= idle ; END IF ; WHEN choose => CASE a 3 a 2 IS WHEN "00" => next_state <= banka ; WHEN "01" => next_state <= bankb ; WHEN "10" => next_state <= bankc ; WHEN "11" => next_state <= bankd ; WHEN OTHERS => next_state <= banka ; END CASE ; WHEN banka => IF eoc = '1' THEN next_state <= bankb ; ELSE next_state <= idle ; END IF ; © 1997 Cypress Semiconductor, rev 2. 5. 3 125

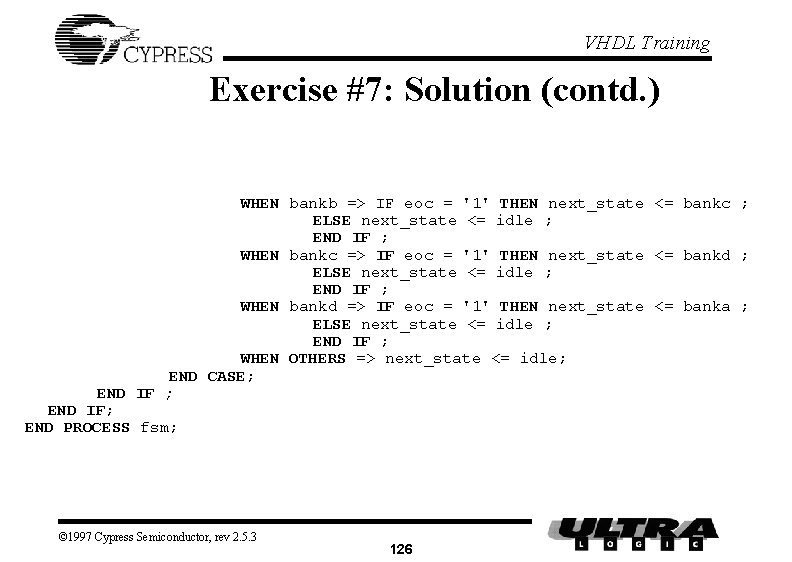

VHDL Training Exercise #7: Solution (contd. ) WHEN bankb => IF eoc = '1' THEN next_state <= bankc ; ELSE next_state <= idle ; END IF ; WHEN bankc => IF eoc = '1' THEN next_state <= bankd ; ELSE next_state <= idle ; END IF ; WHEN bankd => IF eoc = '1' THEN next_state <= banka ; ELSE next_state <= idle ; END IF ; WHEN OTHERS => next_state <= idle; END CASE; END IF; END PROCESS fsm; © 1997 Cypress Semiconductor, rev 2. 5. 3 126

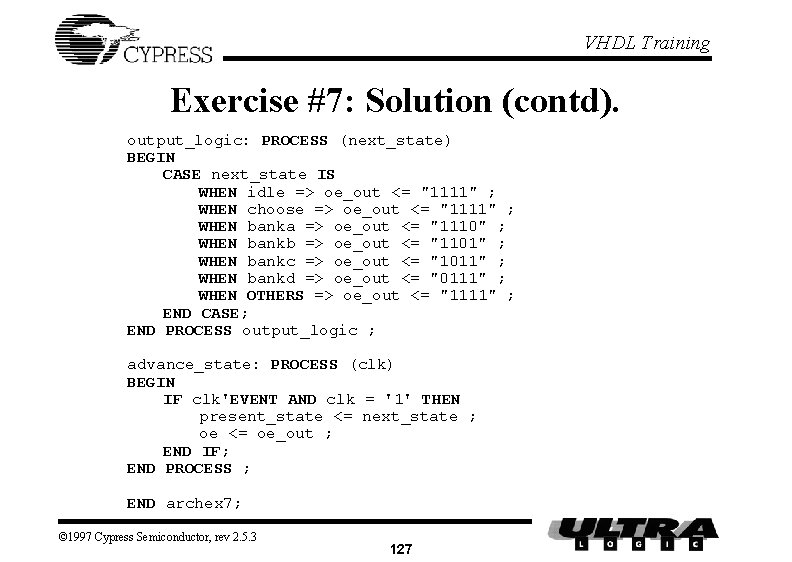

VHDL Training Exercise #7: Solution (contd). output_logic: PROCESS (next_state) BEGIN CASE next_state IS WHEN idle => oe_out <= "1111" ; WHEN choose => oe_out <= "1111" ; WHEN banka => oe_out <= "1110" ; WHEN bankb => oe_out <= "1101" ; WHEN bankc => oe_out <= "1011" ; WHEN bankd => oe_out <= "0111" ; WHEN OTHERS => oe_out <= "1111" ; END CASE; END PROCESS output_logic ; advance_state: PROCESS (clk) BEGIN IF clk'EVENT AND clk = '1' THEN present_state <= next_state ; oe <= oe_out ; END IF; END PROCESS ; END archex 7; © 1997 Cypress Semiconductor, rev 2. 5. 3 127

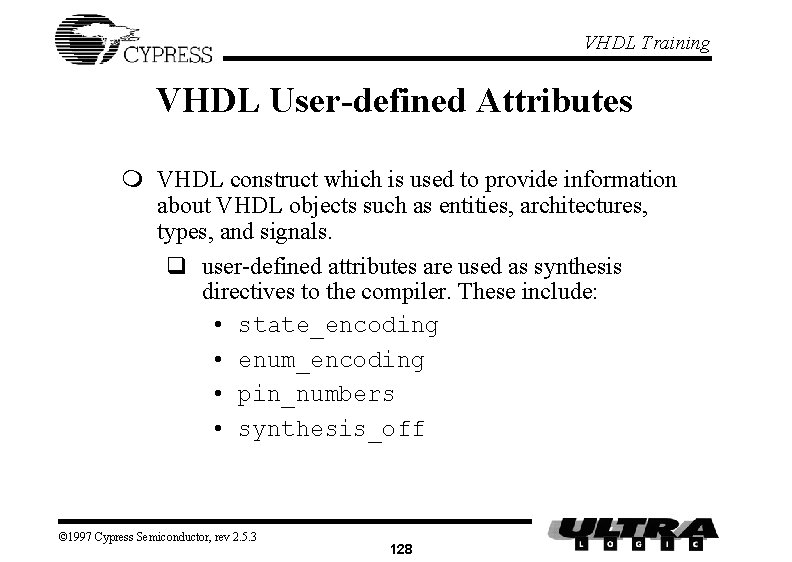

VHDL Training VHDL User-defined Attributes m VHDL construct which is used to provide information about VHDL objects such as entities, architectures, types, and signals. q user-defined attributes are used as synthesis directives to the compiler. These include: • state_encoding • enum_encoding • pin_numbers • synthesis_off © 1997 Cypress Semiconductor, rev 2. 5. 3 128

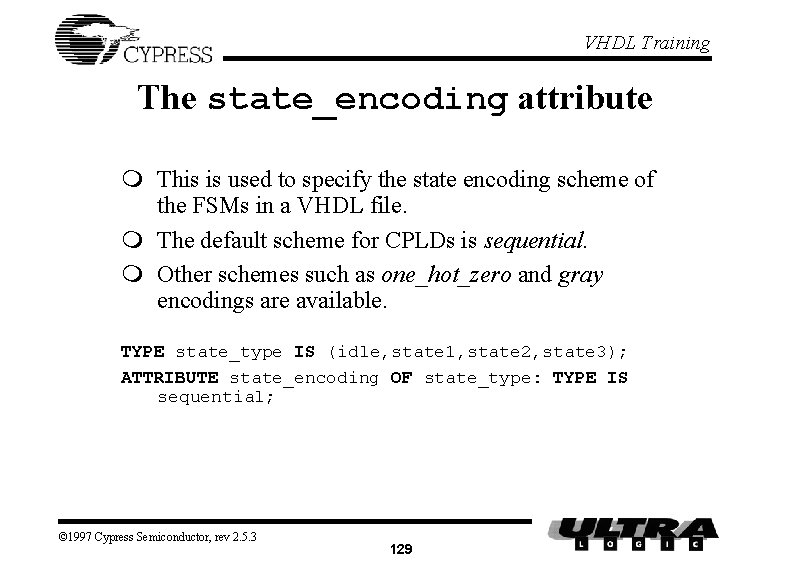

VHDL Training The state_encoding attribute m This is used to specify the state encoding scheme of the FSMs in a VHDL file. m The default scheme for CPLDs is sequential. m Other schemes such as one_hot_zero and gray encodings are available. TYPE state_type IS (idle, state 1, state 2, state 3); ATTRIBUTE state_encoding OF state_type: TYPE IS sequential; © 1997 Cypress Semiconductor, rev 2. 5. 3 129

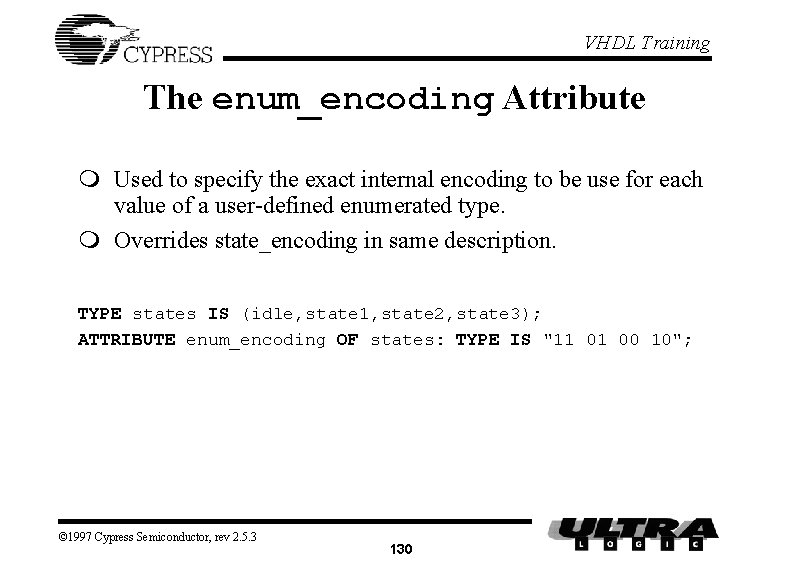

VHDL Training The enum_encoding Attribute m Used to specify the exact internal encoding to be use for each value of a user-defined enumerated type. m Overrides state_encoding in same description. TYPE states IS (idle, state 1, state 2, state 3); ATTRIBUTE enum_encoding OF states: TYPE IS "11 01 00 10"; © 1997 Cypress Semiconductor, rev 2. 5. 3 130

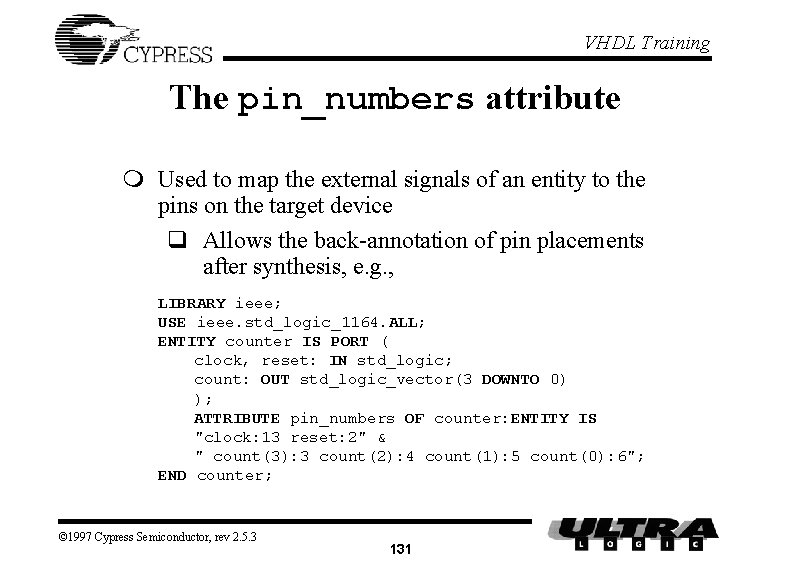

VHDL Training The pin_numbers attribute m Used to map the external signals of an entity to the pins on the target device q Allows the back-annotation of pin placements after synthesis, e. g. , LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY counter IS PORT ( clock, reset: IN std_logic; count: OUT std_logic_vector(3 DOWNTO 0) ); ATTRIBUTE pin_numbers OF counter: ENTITY IS "clock: 13 reset: 2" & " count(3): 3 count(2): 4 count(1): 5 count(0): 6"; END counter; © 1997 Cypress Semiconductor, rev 2. 5. 3 131

VHDL Training The synthesis_off attribute m Controls the flattening and factoring of signals q Makes the signal a factoring point m Useful when a signal with a large number of product terms is used in other equations q Helpful in cases where substitution causes unacceptable compile time (due to exponentially increasing CPU and memory requirements) q Achieves more efficient implementation m Should only be used on combinatorial equations q Registered equations are natural factoring points © 1997 Cypress Semiconductor, rev 2. 5. 3 132

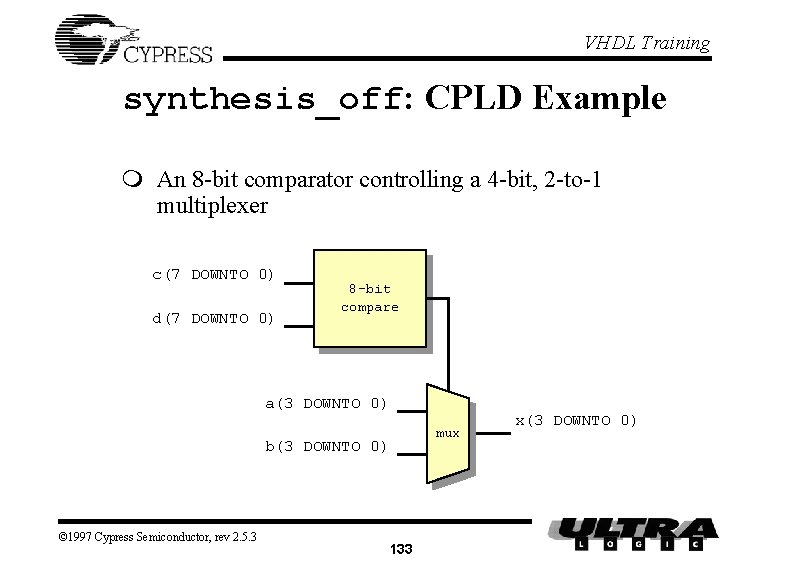

VHDL Training synthesis_off: CPLD Example m An 8 -bit comparator controlling a 4 -bit, 2 -to-1 multiplexer c(7 DOWNTO 0) d(7 DOWNTO 0) 8 -bit compare a(3 DOWNTO 0) mux b(3 DOWNTO 0) © 1997 Cypress Semiconductor, rev 2. 5. 3 133 x(3 DOWNTO 0)

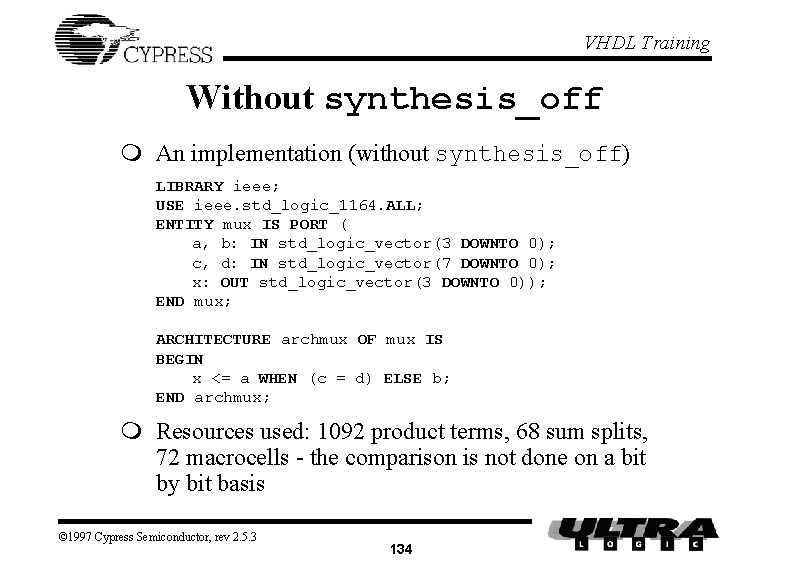

VHDL Training Without synthesis_off m An implementation (without synthesis_off) LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY mux IS PORT ( a, b: IN std_logic_vector(3 DOWNTO 0); c, d: IN std_logic_vector(7 DOWNTO 0); x: OUT std_logic_vector(3 DOWNTO 0)); END mux; ARCHITECTURE archmux OF mux IS BEGIN x <= a WHEN (c = d) ELSE b; END archmux; m Resources used: 1092 product terms, 68 sum splits, 72 macrocells - the comparison is not done on a bit by bit basis © 1997 Cypress Semiconductor, rev 2. 5. 3 134

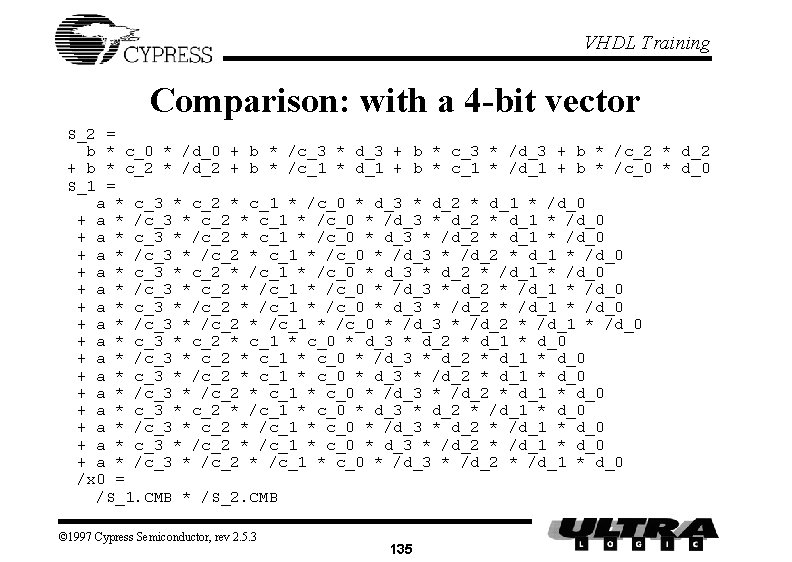

VHDL Training Comparison: with a 4 -bit vector S_2 b + b S_1 = * c_0 * /d_0 + b * /c_3 * d_3 + b * c_3 * /d_3 + b * /c_2 * d_2 * c_2 * /d_2 + b * /c_1 * d_1 + b * c_1 * /d_1 + b * /c_0 * d_0 = a * c_3 * c_2 * c_1 * /c_0 * d_3 * d_2 * d_1 * /d_0 + a * /c_3 * c_2 * c_1 * /c_0 * /d_3 * d_2 * d_1 * /d_0 + a * c_3 * /c_2 * c_1 * /c_0 * d_3 * /d_2 * d_1 * /d_0 + a * /c_3 * /c_2 * c_1 * /c_0 * /d_3 * /d_2 * d_1 * /d_0 + a * c_3 * c_2 * /c_1 * /c_0 * d_3 * d_2 * /d_1 * /d_0 + a * /c_3 * c_2 * /c_1 * /c_0 * /d_3 * d_2 * /d_1 * /d_0 + a * c_3 * /c_2 * /c_1 * /c_0 * d_3 * /d_2 * /d_1 * /d_0 + a * /c_3 * /c_2 * /c_1 * /c_0 * /d_3 * /d_2 * /d_1 * /d_0 + a * c_3 * c_2 * c_1 * c_0 * d_3 * d_2 * d_1 * d_0 + a * /c_3 * c_2 * c_1 * c_0 * /d_3 * d_2 * d_1 * d_0 + a * c_3 * /c_2 * c_1 * c_0 * d_3 * /d_2 * d_1 * d_0 + a * /c_3 * /c_2 * c_1 * c_0 * /d_3 * /d_2 * d_1 * d_0 + a * c_3 * c_2 * /c_1 * c_0 * d_3 * d_2 * /d_1 * d_0 + a * /c_3 * c_2 * /c_1 * c_0 * /d_3 * d_2 * /d_1 * d_0 + a * c_3 * /c_2 * /c_1 * c_0 * d_3 * /d_2 * /d_1 * d_0 + a * /c_3 * /c_2 * /c_1 * c_0 * /d_3 * /d_2 * /d_1 * d_0 /x 0 = /S_1. CMB * /S_2. CMB © 1997 Cypress Semiconductor, rev 2. 5. 3 135

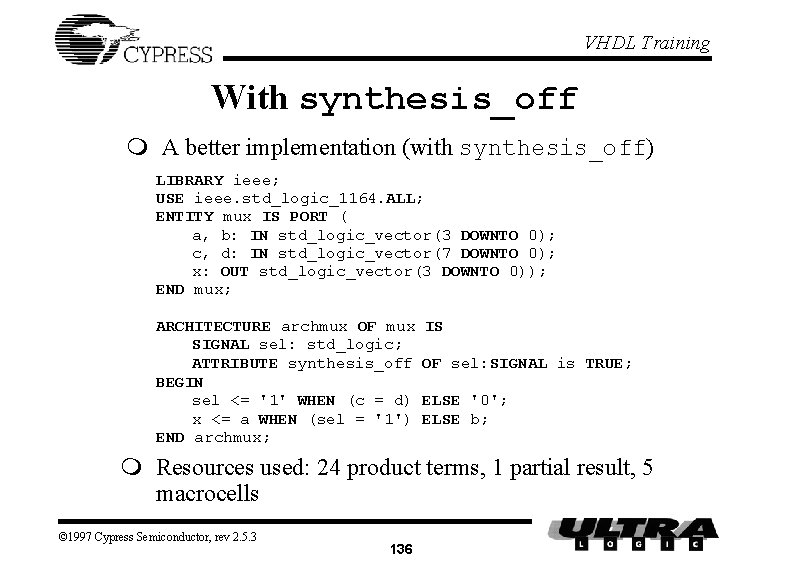

VHDL Training With synthesis_off m A better implementation (with synthesis_off) LIBRARY ieee; USE ieee. std_logic_1164. ALL; ENTITY mux IS PORT ( a, b: IN std_logic_vector(3 DOWNTO 0); c, d: IN std_logic_vector(7 DOWNTO 0); x: OUT std_logic_vector(3 DOWNTO 0)); END mux; ARCHITECTURE archmux OF mux SIGNAL sel: std_logic; ATTRIBUTE synthesis_off BEGIN sel <= '1' WHEN (c = d) x <= a WHEN (sel = '1') END archmux; IS OF sel: SIGNAL is TRUE; ELSE '0'; ELSE b; m Resources used: 24 product terms, 1 partial result, 5 macrocells © 1997 Cypress Semiconductor, rev 2. 5. 3 136

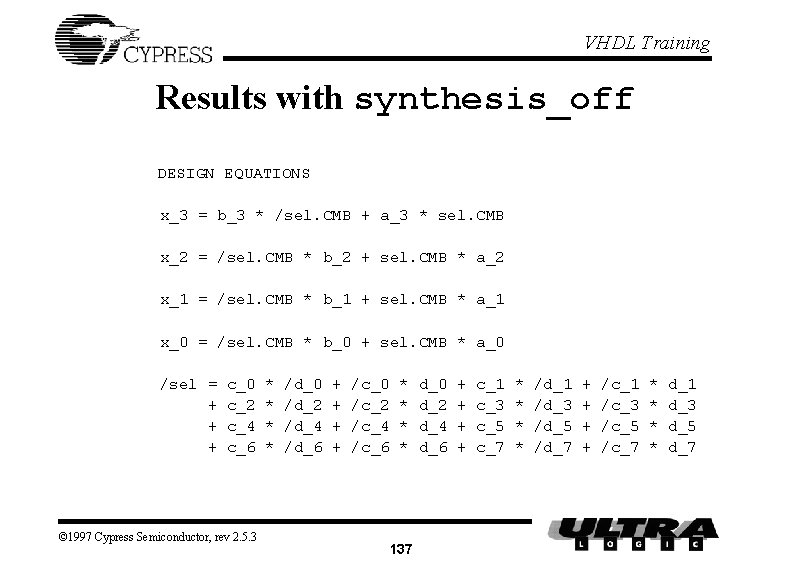

VHDL Training Results with synthesis_off DESIGN EQUATIONS x_3 = b_3 * /sel. CMB + a_3 * sel. CMB x_2 = /sel. CMB * b_2 + sel. CMB * a_2 x_1 = /sel. CMB * b_1 + sel. CMB * a_1 x_0 = /sel. CMB * b_0 + sel. CMB * a_0 /sel = + + + c_0 c_2 c_4 c_6 © 1997 Cypress Semiconductor, rev 2. 5. 3 * * /d_0 /d_2 /d_4 /d_6 + + /c_0 /c_2 /c_4 /c_6 * * 137 d_0 d_2 d_4 d_6 + + c_1 c_3 c_5 c_7 * * /d_1 /d_3 /d_5 /d_7 + + /c_1 /c_3 /c_5 /c_7 * * d_1 d_3 d_5 d_7

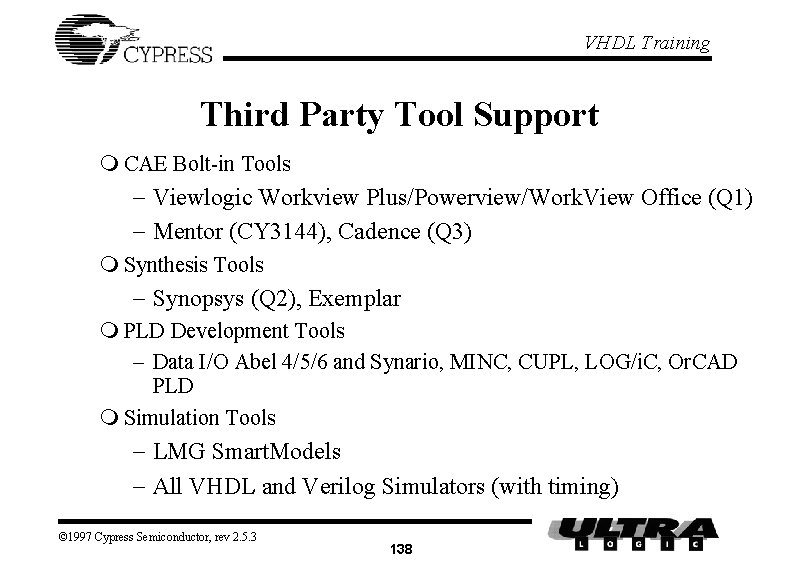

VHDL Training Third Party Tool Support m CAE Bolt-in Tools - Viewlogic Workview Plus/Powerview/Work. View Office (Q 1) - Mentor (CY 3144), Cadence (Q 3) m Synthesis Tools - Synopsys (Q 2), Exemplar m PLD Development Tools - Data I/O Abel 4/5/6 and Synario, MINC, CUPL, LOG/i. C, Or. CAD PLD m Simulation Tools - LMG Smart. Models - All VHDL and Verilog Simulators (with timing) © 1997 Cypress Semiconductor, rev 2. 5. 3 138

- Slides: 138