VHDL XILINX VHDL Class Presented by Training Design

VHDL XILINX VHDL Class Presented by Training & Design Center Introduction to VHDL Page 1 - 1

VHDL XILINX VHDL Class Agenda 1. Introduction to VHDL 2. Design with VHDL 1 (Combinatorial Logic) 3. Design with VHDL 2 (Sequential Logic) 4. Design with VHDL 3 (Hierarchical Design) 5. Implementation Introduction to VHDL Page 1 - 2

VHDL Introduction to VHDL Very High Speed Integrated Circuit Hardware Description Language Introduction to VHDL Page 1 - 3

VHDL Design Method • Schematic Design Method • Language Based Design – VHDL – Verilog Introduction to VHDL Page 1 - 5

Design Method 1 (Schematic) VHDL • Schematic Design Method (장점) – 설계 방법 습득이 쉬움. • AND, OR, NOT, Latch, Flip-Flop이면 Cover – Best Performance for Best Engineer – Tool 비용이 저렴 Introduction to VHDL Page 1 - 6

Design Method 1 (Schematic) VHDL • Schematic Design Method (단점) – Flexibility가 떨어짐. • Target Technology를 Fix해야 함. • Design에 따라 Logic Size가 결정됨. • Design에 따라 System Performance가 결정됨 – Tool, Technology에 대한 호환성 부족 – 수정이 어려움 (Time Consuming, Risc) • 대용량 설계에 제약 – Verify Stage (Gate Level부터 가능) – Documentation이 어려움. Introduction to VHDL Page 1 - 7

Design Method 1 (VHDL) VHDL • VHDL Design Method (장점) – 개발 기간 단축 효과 – Flexibility가 높음 • Target Technology에 Independent. • Logic Size vs System Performance 절충 가능. – Tool, Technology에 대한 탁월한 호환성 – 수정이 용이 (Text Edit & Quick Simulation) • 대용량 설계에 적합 – Verify Stage (Behavioral, RTL, Gate Level) – Design File(Text)에 Documentation 포함. Introduction to VHDL Page 1 - 8

Design Method 1 (VHDL) VHDL • VHDL Design Method (단점) – Schematic Designer에게 익숙치 않은 방법 • 초기 접근(습득)에 어려움. – Better Performance (? ) but. . . • Best Schematic Design보다는 경우에 따라 열세 • 그러나 개발 기간은. . . Introduction to VHDL Page 1 - 9

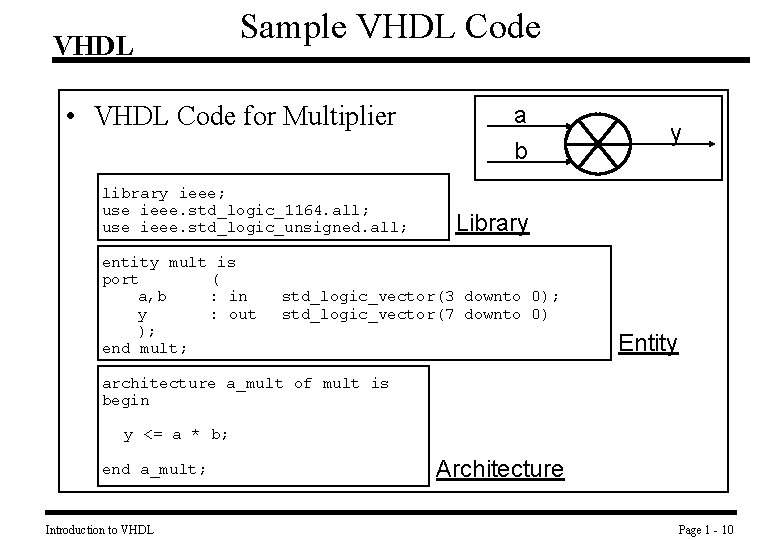

VHDL Sample VHDL Code • VHDL Code for Multiplier a b library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity mult is port ( a, b : in y : out ); end mult; y Library std_logic_vector(3 downto 0); std_logic_vector(7 downto 0) Entity architecture a_mult of mult is begin y <= a * b; end a_mult; Introduction to VHDL Architecture Page 1 - 10

VHDL Design의 목적 • VHDL Design의 목적 – H/W Implementation – H/W Modeling for Simulation first – More Effective with Synthesis and Simulation Introduction to VHDL Page 1 - 11

VHDL Simulation 과 Synthesis • Simulation – 설계한 Code의 동작을 검증 – Behavioral, RTL, Gate Level등에서 검증 • Synthesis – 설계한 Code를 Gate Level H/W로 변환. – Translation and Optimization – Mapping with Target Technology Introduction to VHDL Page 1 - 12

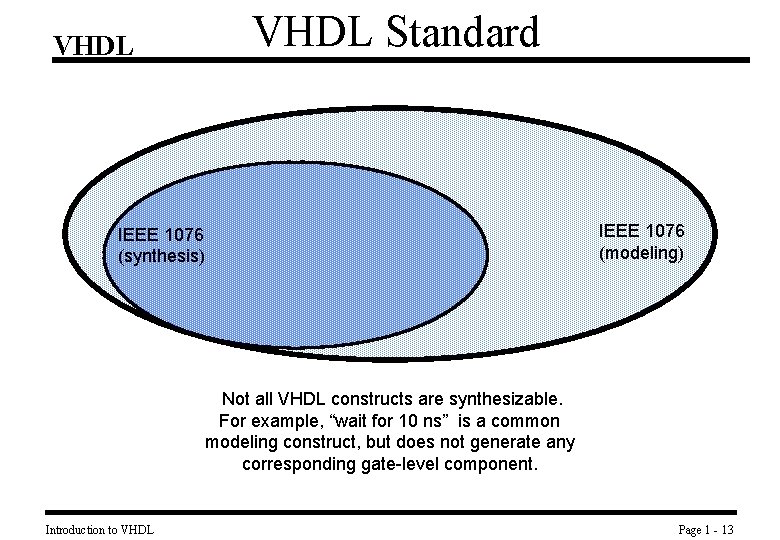

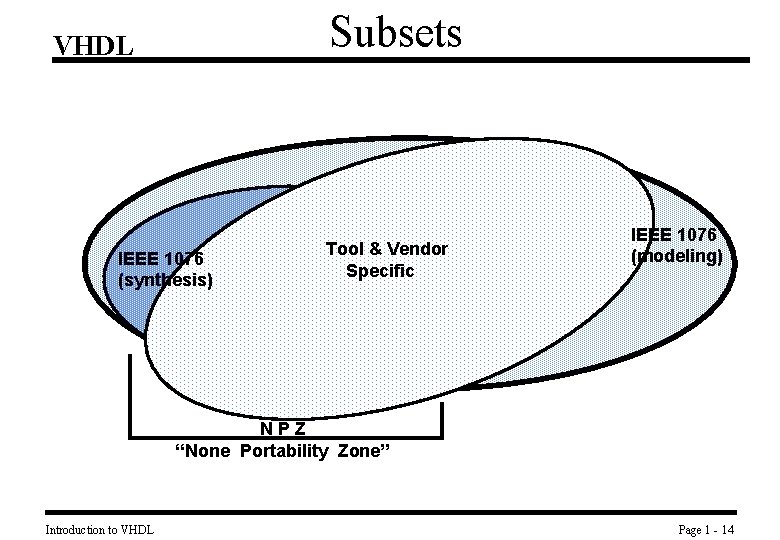

VHDL Standard IEEE 1076 (modeling) IEEE 1076 (synthesis) Not all VHDL constructs are synthesizable. For example, “wait for 10 ns” is a common modeling construct, but does not generate any corresponding gate-level component. Introduction to VHDL Page 1 - 13

Subsets VHDL IEEE 1076 (synthesis) Tool & Vendor Specific IEEE 1076 (modeling) NPZ “None Portability Zone” Introduction to VHDL Page 1 - 14

VHDL Design시 고려 사항 VHDL • VHDL Design시 고려해야 할 사항 – 어떤 H/W로 구현 될 것인가 • Logic Size, Architecture, Glitch. . • Propagation Delay and Timing Margin – Flexible, but need Consideration Introduction to VHDL Page 1 - 15

VHDL Quiz • Schematic Design의 장, 단점은? • Language Based Design의 장, 단점은? • VHDL Design의 목적은? • Simulation, Synthesis란 무엇인가? Introduction to VHDL Page 1 - 17

VHDL Design with VHDL(1) (Combinatorial Logic) Introduction to VHDL Page 1 - 1

VHDL Data-Types Ø Data-types are very important in VHDL. A given data-type define all possible values within its range. Only values within that range may be applied. Each VHDL object (signal, variable, constant) or port must have its type defined when declared. VHDL is considered to be a strongly “typed” language, connected signals must be of the same type! The wide range of data-types available provides both flexibility in hardware modeling, and built-in error checking to ensure signal compatibility in large and complex models. Introduction to VHDL Page 1 - 3

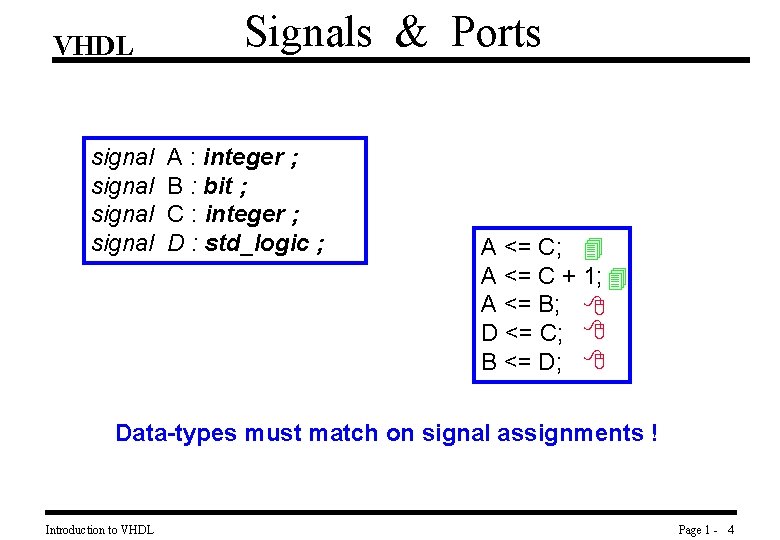

VHDL signal Signals & Ports A : integer ; B : bit ; C : integer ; D : std_logic ; A <= C; 4 A <= C + 1; 4 A <= B; 8 D <= C; 8 B <= D; 8 Data-types must match on signal assignments ! Introduction to VHDL Page 1 - 4

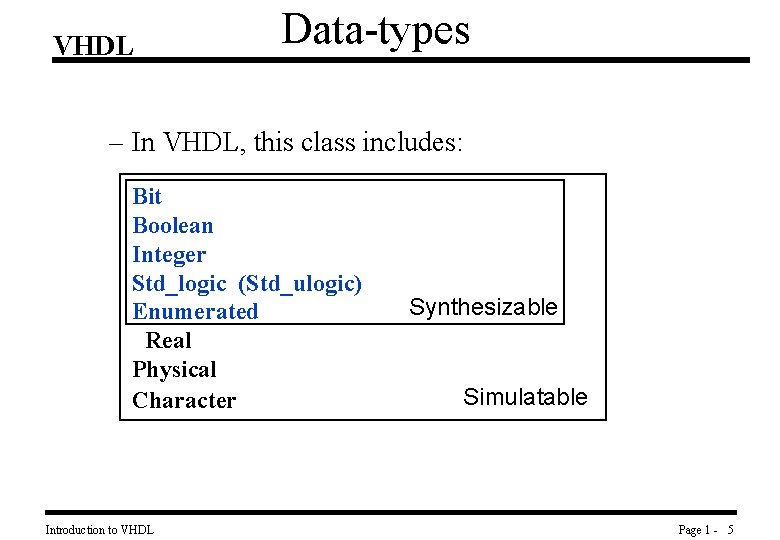

VHDL Data-types – In VHDL, this class includes: Bit Boolean Integer Std_logic (Std_ulogic) Enumerated Real Physical Character Introduction to VHDL Synthesizable Simulatable Page 1 - 5

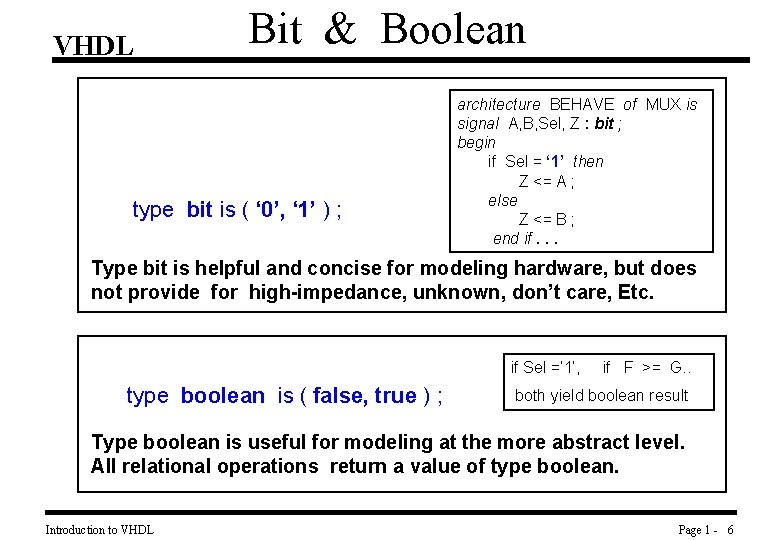

VHDL Bit & Boolean type bit is ( ‘ 0’, ‘ 1’ ) ; architecture BEHAVE of MUX is signal A, B, Sel, Z : bit ; begin if Sel = ‘ 1’ then Z <= A ; else Z <= B ; end if. . . Type bit is helpful and concise for modeling hardware, but does not provide for high-impedance, unknown, don’t care, Etc. if Sel =‘ 1’, type boolean is ( false, true ) ; if F >= G. . both yield boolean result Type boolean is useful for modeling at the more abstract level. All relational operations return a value of type boolean. Introduction to VHDL Page 1 - 6

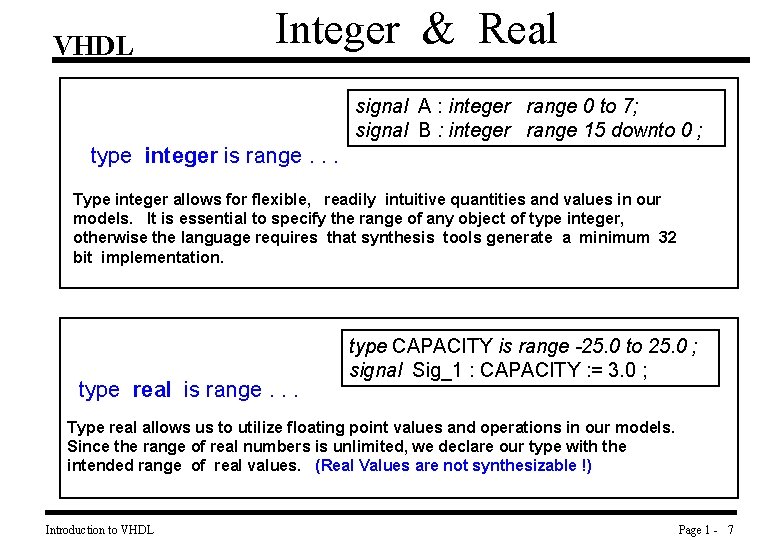

VHDL Integer & Real signal A : integer range 0 to 7; signal B : integer range 15 downto 0 ; type integer is range. . . Type integer allows for flexible, readily intuitive quantities and values in our models. It is essential to specify the range of any object of type integer, otherwise the language requires that synthesis tools generate a minimum 32 bit implementation. type real is range. . . type CAPACITY is range -25. 0 to 25. 0 ; signal Sig_1 : CAPACITY : = 3. 0 ; Type real allows us to utilize floating point values and operations in our models. Since the range of real numbers is unlimited, we declare our type with the intended range of real values. (Real Values are not synthesizable !) Introduction to VHDL Page 1 - 7

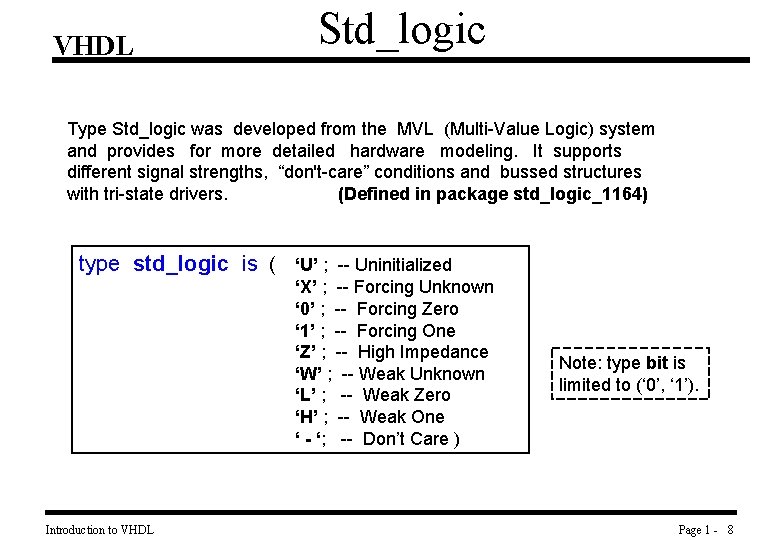

VHDL Std_logic Type Std_logic was developed from the MVL (Multi-Value Logic) system and provides for more detailed hardware modeling. It supports different signal strengths, “don't-care” conditions and bussed structures with tri-state drivers. (Defined in package std_logic_1164) type std_logic is ( ‘U’ ; -- Uninitialized ‘X’ ; -- Forcing Unknown ‘ 0’ ; -- Forcing Zero ‘ 1’ ; -- Forcing One ‘Z’ ; -- High Impedance ‘W’ ; -- Weak Unknown ‘L’ ; -- Weak Zero ‘H’ ; -- Weak One ‘ - ‘; -- Don’t Care ) Introduction to VHDL Note: type bit is limited to (‘ 0’, ‘ 1’). Page 1 - 8

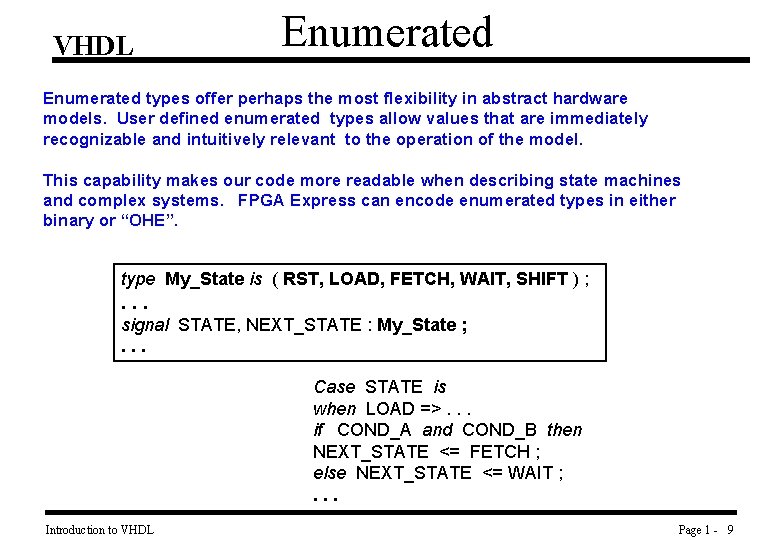

VHDL Enumerated types offer perhaps the most flexibility in abstract hardware models. User defined enumerated types allow values that are immediately recognizable and intuitively relevant to the operation of the model. This capability makes our code more readable when describing state machines and complex systems. FPGA Express can encode enumerated types in either binary or “OHE”. type My_State is ( RST, LOAD, FETCH, WAIT, SHIFT ) ; . . . signal STATE, NEXT_STATE : My_State ; . . . Case STATE is when LOAD =>. . . if COND_A and COND_B then NEXT_STATE <= FETCH ; else NEXT_STATE <= WAIT ; . . . Introduction to VHDL Page 1 - 9

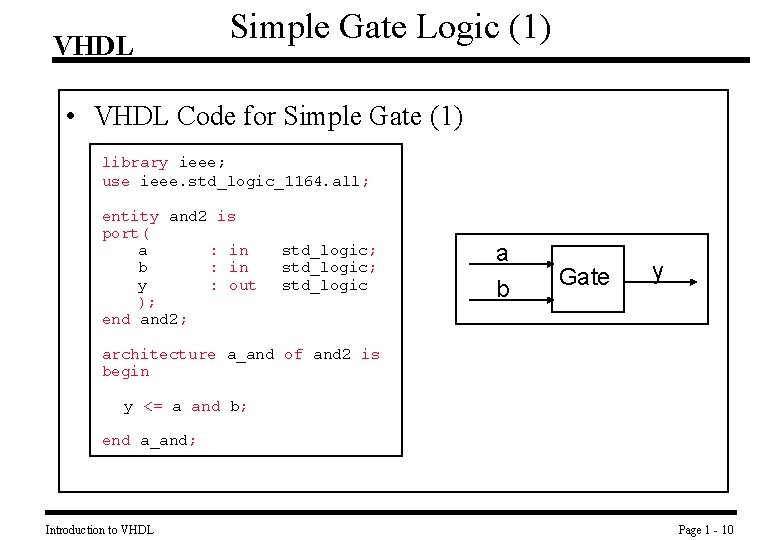

VHDL Simple Gate Logic (1) • VHDL Code for Simple Gate (1) library ieee; use ieee. std_logic_1164. all; entity and 2 is port( a : in b : in y : out ); end and 2; std_logic; std_logic a b Gate y architecture a_and of and 2 is begin y <= a and b; end a_and; Introduction to VHDL Page 1 - 10

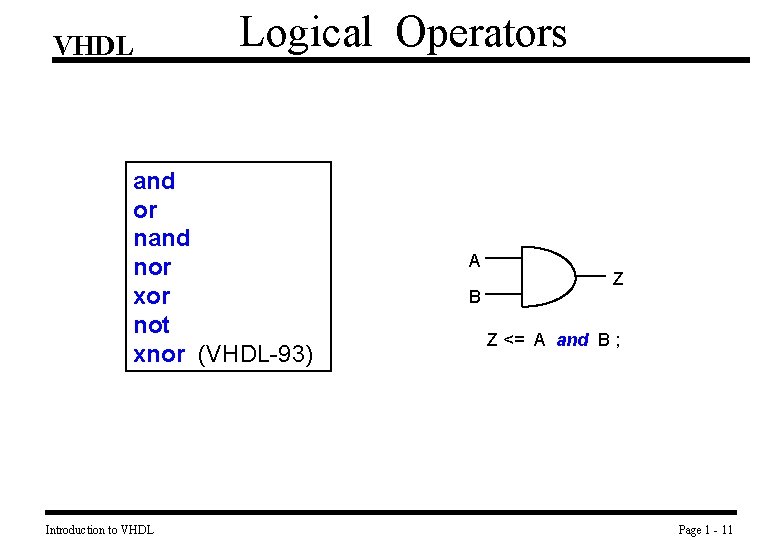

VHDL Logical Operators and or nand nor xor not xnor (VHDL-93) Introduction to VHDL A B Z Z <= A and B ; Page 1 - 11

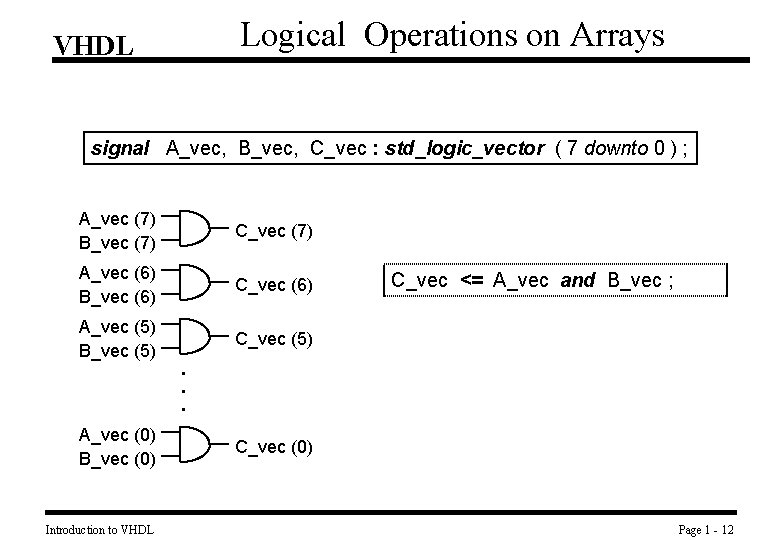

Logical Operations on Arrays VHDL signal A_vec, B_vec, C_vec : std_logic_vector ( 7 downto 0 ) ; A_vec (7) B_vec (7) C_vec (7) A_vec (6) B_vec (6) C_vec (6) A_vec (5) B_vec (5) C_vec (5) A_vec (0) B_vec (0) Introduction to VHDL C_vec <= A_vec and B_vec ; . . . C_vec (0) Page 1 - 12

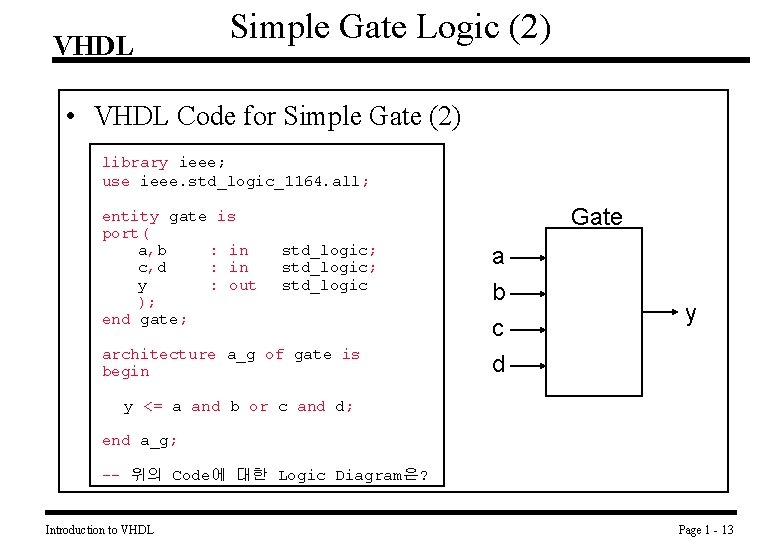

VHDL Simple Gate Logic (2) • VHDL Code for Simple Gate (2) library ieee; use ieee. std_logic_1164. all; entity gate is port( a, b : in c, d : in y : out ); end gate; Gate std_logic; std_logic architecture a_g of gate is begin a b c d y y <= a and b or c and d; end a_g; -- 위의 Code에 대한 Logic Diagram은? Introduction to VHDL Page 1 - 13

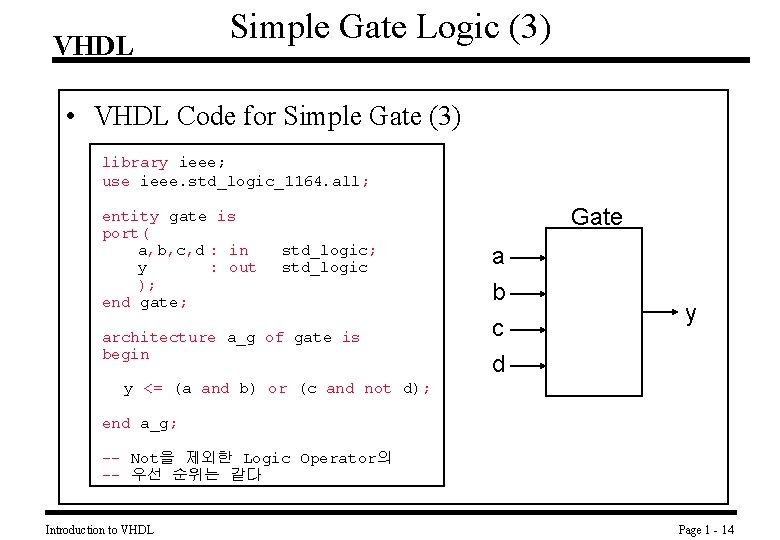

VHDL Simple Gate Logic (3) • VHDL Code for Simple Gate (3) library ieee; use ieee. std_logic_1164. all; entity gate is port( a, b, c, d : in y : out ); end gate; Gate std_logic; std_logic architecture a_g of gate is begin a b c d y y <= (a and b) or (c and not d); end a_g; -- Not을 제외한 Logic Operator의 -- 우선 순위는 같다 Introduction to VHDL Page 1 - 14

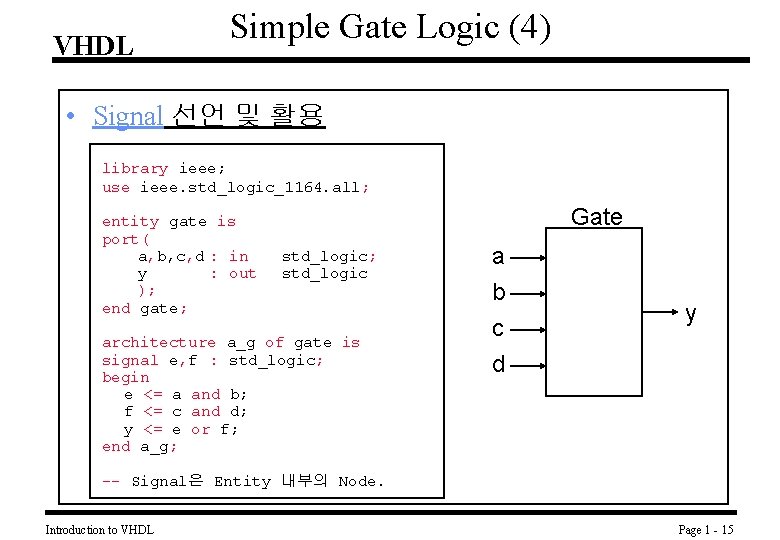

VHDL Simple Gate Logic (4) • Signal 선언 및 활용 library ieee; use ieee. std_logic_1164. all; entity gate is port( a, b, c, d : in y : out ); end gate; Gate std_logic; std_logic architecture a_g of gate is signal e, f : std_logic; begin e <= a and b; f <= c and d; y <= e or f; end a_g; a b c d y -- Signal은 Entity 내부의 Node. Introduction to VHDL Page 1 - 15

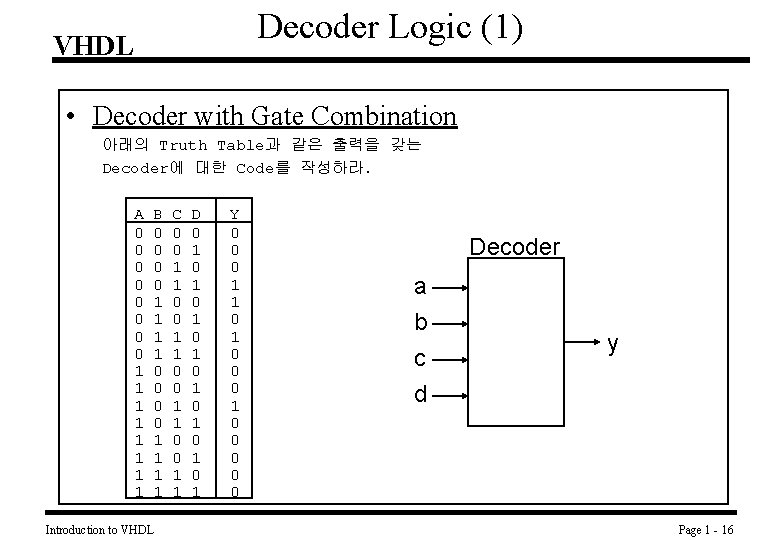

Decoder Logic (1) VHDL • Decoder with Gate Combination 아래의 Truth Table과 같은 출력을 갖는 Decoder에 대한 Code를 작성하라. A 0 0 0 0 1 1 1 1 B 0 0 0 0 1 1 1 1 Introduction to VHDL C 0 0 1 1 D 0 1 0 1 Y 0 0 0 1 1 0 0 0 Decoder a b c d y Page 1 - 16

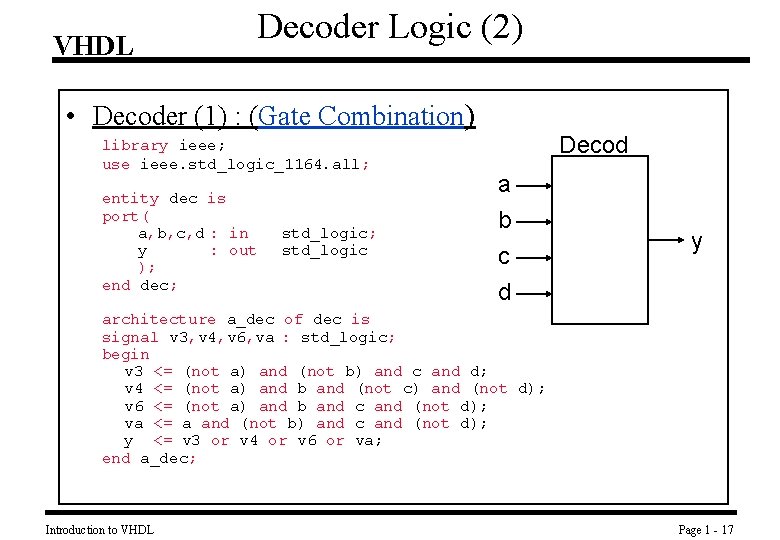

VHDL Decoder Logic (2) • Decoder (1) : (Gate Combination) library ieee; use ieee. std_logic_1164. all; entity dec is port( a, b, c, d : in y : out ); end dec; std_logic; std_logic Decod a b c d y architecture a_dec of dec is signal v 3, v 4, v 6, va : std_logic; begin v 3 <= (not a) and (not b) and c and d; v 4 <= (not a) and b and (not c) and (not d); v 6 <= (not a) and b and c and (not d); va <= a and (not b) and c and (not d); y <= v 3 or v 4 or v 6 or va; end a_dec; Introduction to VHDL Page 1 - 17

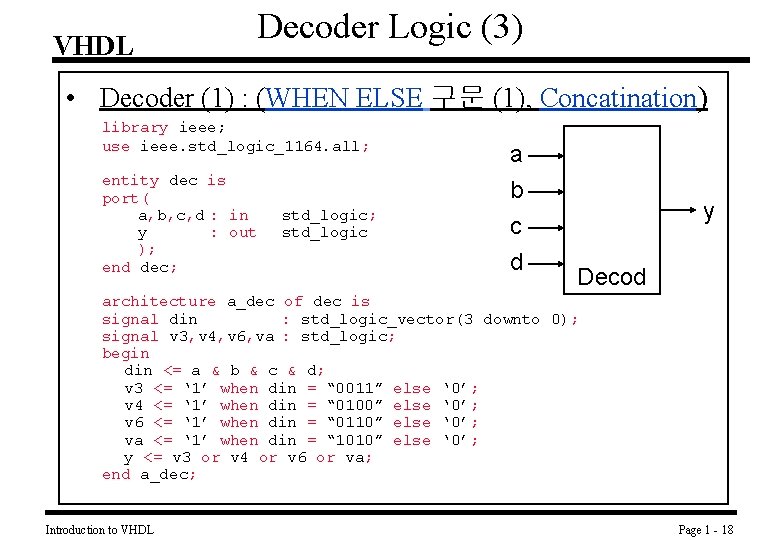

VHDL Decoder Logic (3) • Decoder (1) : (WHEN ELSE 구문 (1), Concatination) library ieee; use ieee. std_logic_1164. all; entity dec is port( a, b, c, d : in y : out ); end dec; std_logic; std_logic a b c d y Decod architecture a_dec of dec is signal din : std_logic_vector(3 downto 0); signal v 3, v 4, v 6, va : std_logic; begin din <= a & b & c & d; v 3 <= ‘ 1’ when din = “ 0011” else ‘ 0’; v 4 <= ‘ 1’ when din = “ 0100” else ‘ 0’; v 6 <= ‘ 1’ when din = “ 0110” else ‘ 0’; va <= ‘ 1’ when din = “ 1010” else ‘ 0’; y <= v 3 or v 4 or v 6 or va; end a_dec; Introduction to VHDL Page 1 - 18

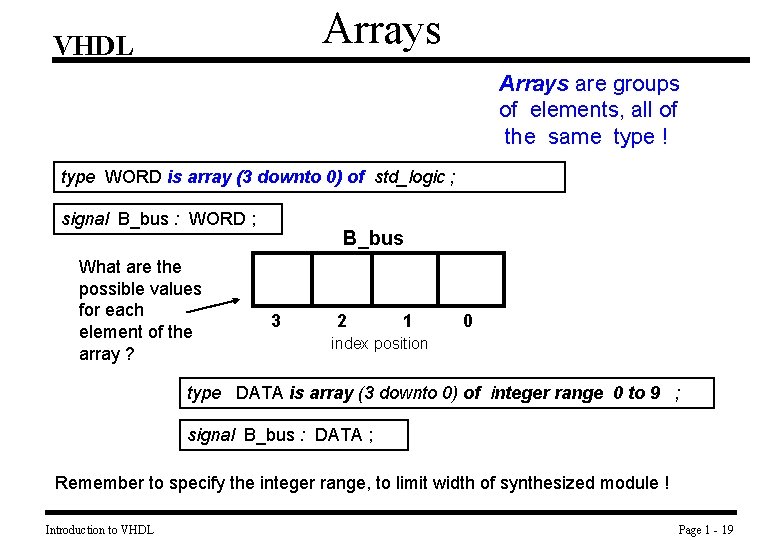

Arrays VHDL Arrays are groups of elements, all of the same type ! type WORD is array (3 downto 0) of std_logic ; signal B_bus : WORD ; What are the possible values for each element of the array ? B_bus 3 2 1 0 index position type DATA is array (3 downto 0) of integer range 0 to 9 ; signal B_bus : DATA ; Remember to specify the integer range, to limit width of synthesized module ! Introduction to VHDL Page 1 - 19

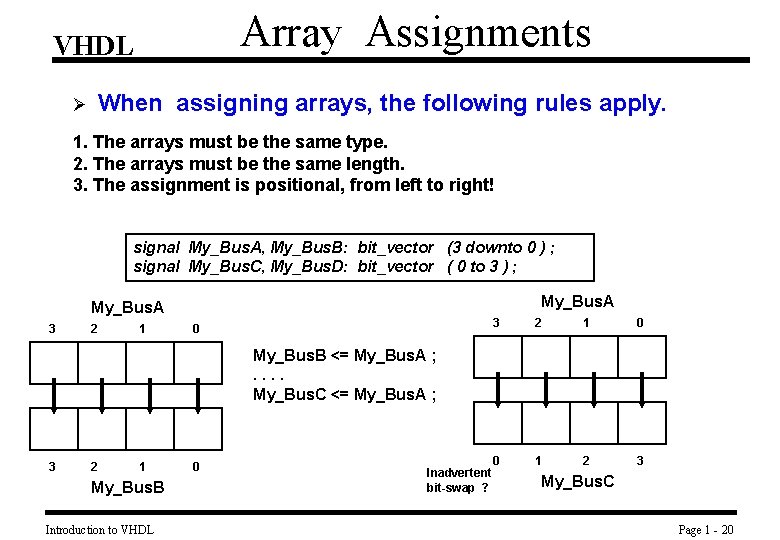

Array Assignments VHDL Ø When assigning arrays, the following rules apply. 1. The arrays must be the same type. 2. The arrays must be the same length. 3. The assignment is positional, from left to right! signal My_Bus. A, My_Bus. B: bit_vector (3 downto 0 ) ; signal My_Bus. C, My_Bus. D: bit_vector ( 0 to 3 ) ; My_Bus. A 3 2 1 0 0 1 2 3 My_Bus. B <= My_Bus. A ; . . My_Bus. C <= My_Bus. A ; 3 2 1 My_Bus. B Introduction to VHDL 0 Inadvertent bit-swap ? My_Bus. C Page 1 - 20

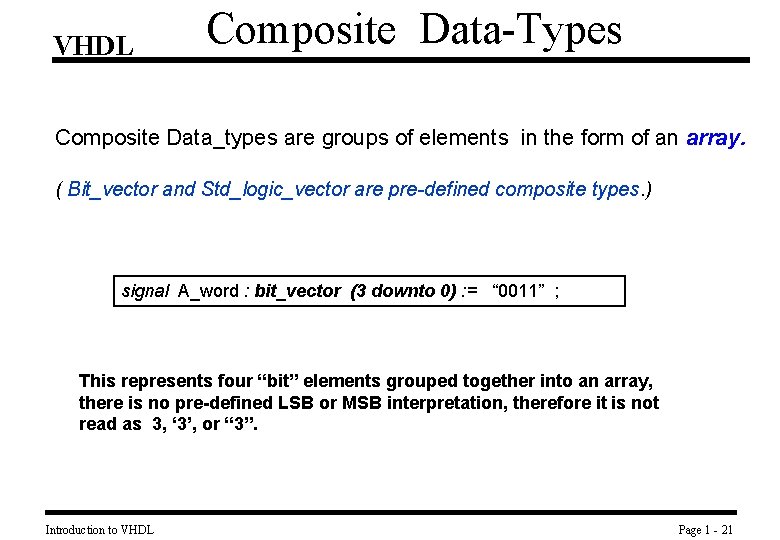

VHDL Composite Data-Types Composite Data_types are groups of elements in the form of an array. ( Bit_vector and Std_logic_vector are pre-defined composite types. ) signal A_word : bit_vector (3 downto 0) : = “ 0011” ; This represents four “bit” elements grouped together into an array, there is no pre-defined LSB or MSB interpretation, therefore it is not read as 3, ‘ 3’, or “ 3”. Introduction to VHDL Page 1 - 21

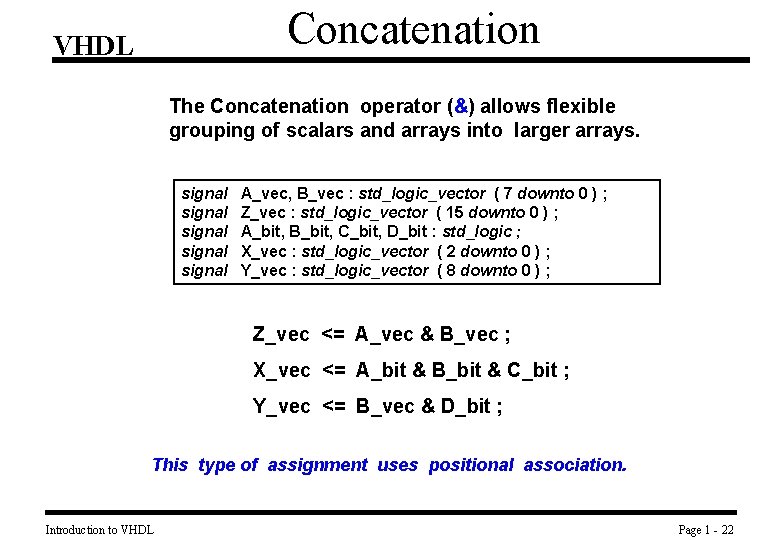

Concatenation VHDL The Concatenation operator (&) allows flexible grouping of scalars and arrays into larger arrays. signal signal A_vec, B_vec : std_logic_vector ( 7 downto 0 ) ; Z_vec : std_logic_vector ( 15 downto 0 ) ; A_bit, B_bit, C_bit, D_bit : std_logic ; X_vec : std_logic_vector ( 2 downto 0 ) ; Y_vec : std_logic_vector ( 8 downto 0 ) ; Z_vec <= A_vec & B_vec ; X_vec <= A_bit & B_bit & C_bit ; Y_vec <= B_vec & D_bit ; This type of assignment uses positional association. Introduction to VHDL Page 1 - 22

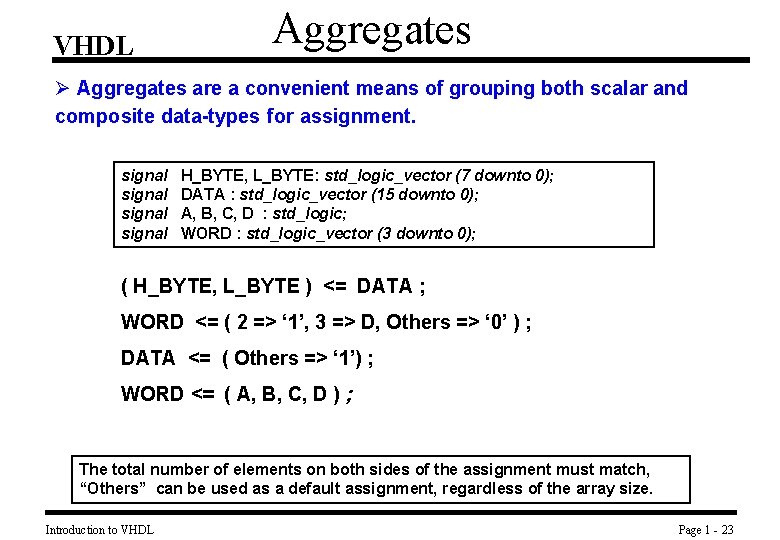

VHDL Aggregates Ø Aggregates are a convenient means of grouping both scalar and composite data-types for assignment. signal H_BYTE, L_BYTE: std_logic_vector (7 downto 0); DATA : std_logic_vector (15 downto 0); A, B, C, D : std_logic; WORD : std_logic_vector (3 downto 0); ( H_BYTE, L_BYTE ) <= DATA ; WORD <= ( 2 => ‘ 1’, 3 => D, Others => ‘ 0’ ) ; DATA <= ( Others => ‘ 1’) ; WORD <= ( A, B, C, D ) ; The total number of elements on both sides of the assignment must match, “Others” can be used as a default assignment, regardless of the array size. Introduction to VHDL Page 1 - 23

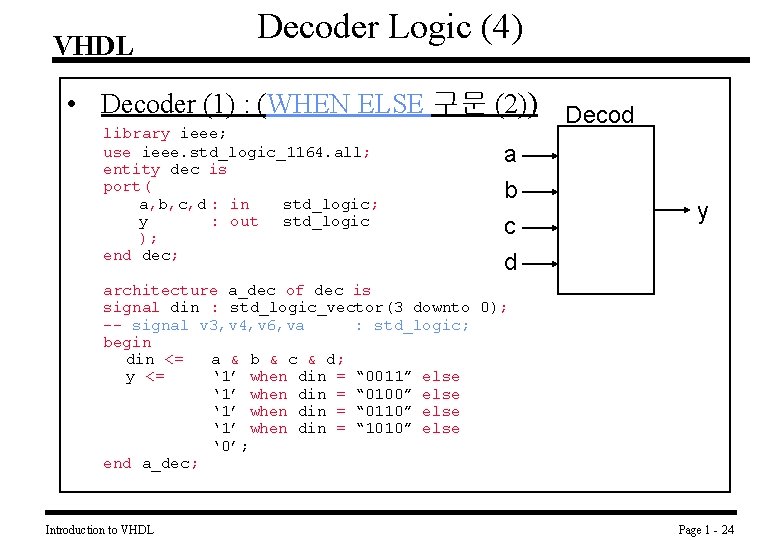

VHDL Decoder Logic (4) • Decoder (1) : (WHEN ELSE 구문 (2)) Decod library ieee; use ieee. std_logic_1164. all; entity dec is port( a, b, c, d : in std_logic; y : out std_logic ); end dec; a b c d y architecture a_dec of dec is signal din : std_logic_vector(3 downto 0); -- signal v 3, v 4, v 6, va : std_logic; begin din <= a & b & c & d; y <= ‘ 1’ when din = “ 0011” else ‘ 1’ when din = “ 0100” else ‘ 1’ when din = “ 0110” else ‘ 1’ when din = “ 1010” else ‘ 0’; end a_dec; Introduction to VHDL Page 1 - 24

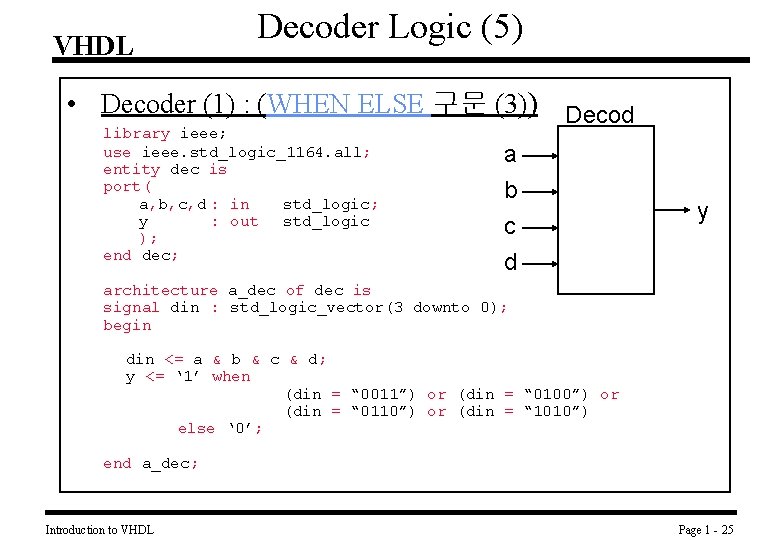

VHDL Decoder Logic (5) • Decoder (1) : (WHEN ELSE 구문 (3)) Decod library ieee; use ieee. std_logic_1164. all; entity dec is port( a, b, c, d : in std_logic; y : out std_logic ); end dec; a b c d y architecture a_dec of dec is signal din : std_logic_vector(3 downto 0); begin din <= a & b & c & d; y <= ‘ 1’ when (din = “ 0011”) or (din = “ 0100”) or (din = “ 0110”) or (din = “ 1010”) else ‘ 0’; end a_dec; Introduction to VHDL Page 1 - 25

VHDL Multiplexer Logic (1) • 2 to 1 Multiplexer – 2 to 1 mux에 대한 Gate 조합형 Code를 작성 하라. sel I 0 I 1 Mux – 2 to 1 mux 에 대한 Behavioral Code를 작성하라. Introduction to VHDL y Page 1 - 26

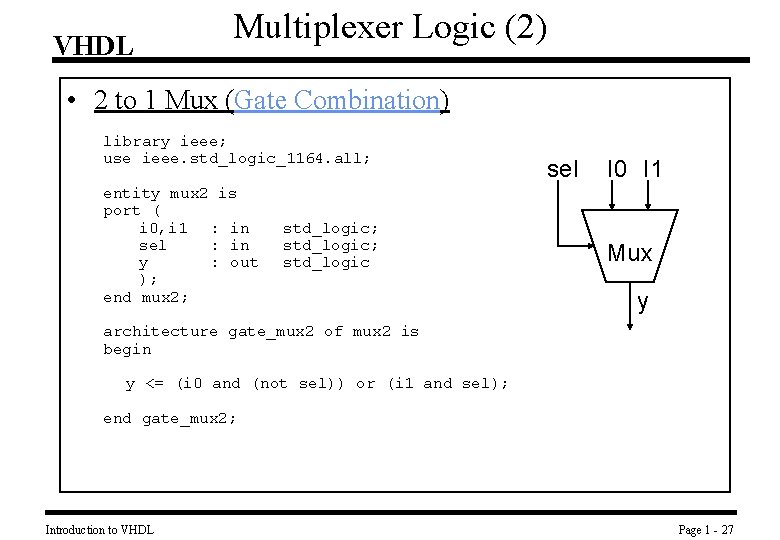

VHDL Multiplexer Logic (2) • 2 to 1 Mux (Gate Combination) library ieee; use ieee. std_logic_1164. all; entity mux 2 is port ( i 0, i 1 : in sel : in y : out ); end mux 2; std_logic; std_logic sel I 0 I 1 Mux y architecture gate_mux 2 of mux 2 is begin y <= (i 0 and (not sel)) or (i 1 and sel); end gate_mux 2; Introduction to VHDL Page 1 - 27

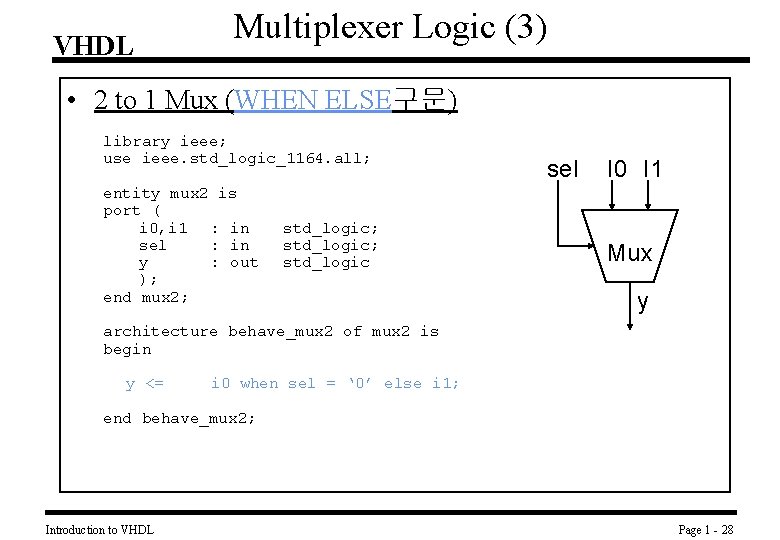

VHDL Multiplexer Logic (3) • 2 to 1 Mux (WHEN ELSE구문) library ieee; use ieee. std_logic_1164. all; entity mux 2 is port ( i 0, i 1 : in sel : in y : out ); end mux 2; std_logic; std_logic sel I 0 I 1 Mux y architecture behave_mux 2 of mux 2 is begin y <= i 0 when sel = ‘ 0’ else i 1; end behave_mux 2; Introduction to VHDL Page 1 - 28

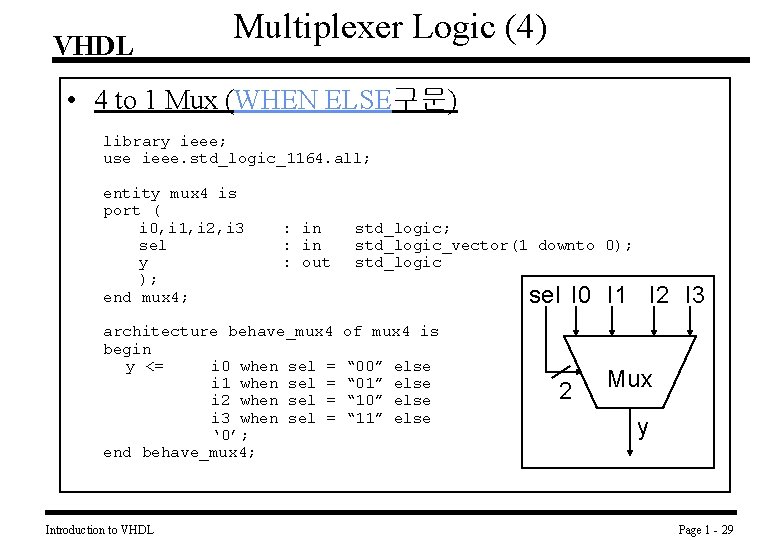

VHDL Multiplexer Logic (4) • 4 to 1 Mux (WHEN ELSE구문) library ieee; use ieee. std_logic_1164. all; entity mux 4 is port ( i 0, i 1, i 2, i 3 sel y ); end mux 4; : in : out architecture behave_mux 4 begin y <= i 0 when sel = i 1 when sel = i 2 when sel = i 3 when sel = ‘ 0’; end behave_mux 4; Introduction to VHDL std_logic; std_logic_vector(1 downto 0); std_logic sel I 0 I 1 I 2 I 3 of mux 4 is “ 00” “ 01” “ 10” “ 11” else 2 Mux y Page 1 - 29

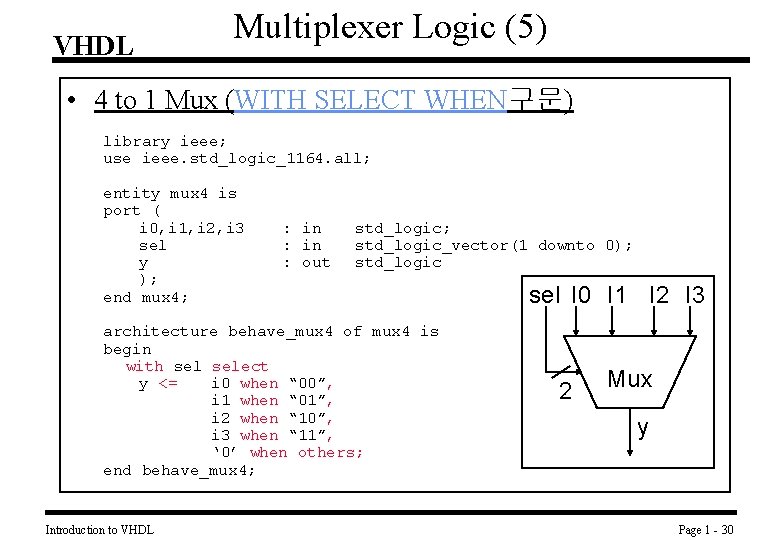

VHDL Multiplexer Logic (5) • 4 to 1 Mux (WITH SELECT WHEN구문) library ieee; use ieee. std_logic_1164. all; entity mux 4 is port ( i 0, i 1, i 2, i 3 sel y ); end mux 4; : in : out std_logic; std_logic_vector(1 downto 0); std_logic architecture behave_mux 4 of mux 4 is begin with select y <= i 0 when “ 00”, i 1 when “ 01”, i 2 when “ 10”, i 3 when “ 11”, ‘ 0’ when others; end behave_mux 4; Introduction to VHDL sel I 0 I 1 I 2 I 3 2 Mux y Page 1 - 30

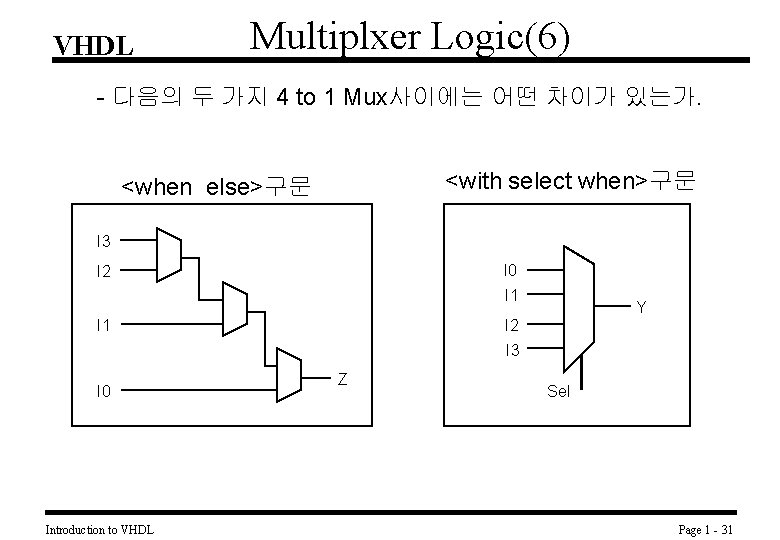

VHDL Multiplxer Logic(6) - 다음의 두 가지 4 to 1 Mux사이에는 어떤 차이가 있는가. <with select when>구문 <when else>구문 I 3 I 0 I 2 I 1 Y I 2 I 3 I 0 Introduction to VHDL Z Sel Page 1 - 31

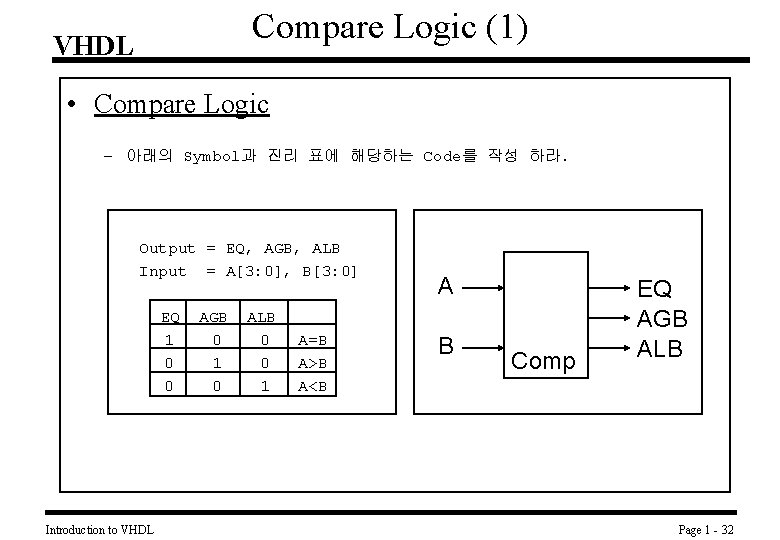

Compare Logic (1) VHDL • Compare Logic – 아래의 Symbol과 진리 표에 해당하는 Code를 작성 하라. Output = EQ, AGB, ALB Input = A[3: 0], B[3: 0] EQ 1 0 0 Introduction to VHDL AGB 0 1 0 ALB 0 0 1 A=B A>B A<B A B Comp EQ AGB ALB Page 1 - 32

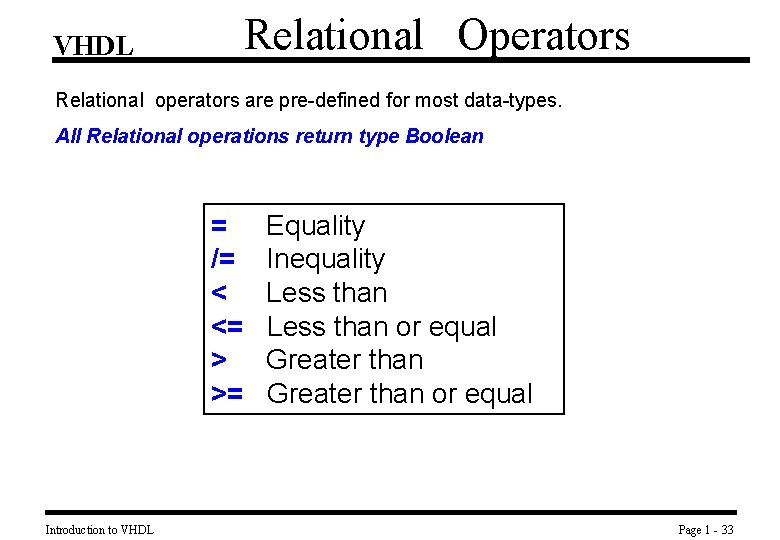

Relational Operators VHDL Relational operators are pre-defined for most data-types. All Relational operations return type Boolean = /= < <= > >= Introduction to VHDL Equality Inequality Less than or equal Greater than or equal Page 1 - 33

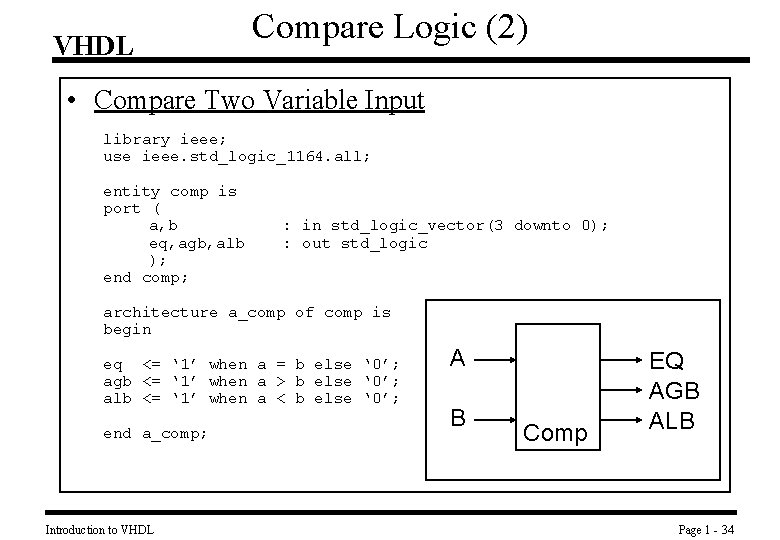

VHDL Compare Logic (2) • Compare Two Variable Input library ieee; use ieee. std_logic_1164. all; entity comp is port ( a, b eq, agb, alb ); end comp; : in std_logic_vector(3 downto 0); : out std_logic architecture a_comp of comp is begin eq <= ‘ 1’ when a = b else ‘ 0’; agb <= ‘ 1’ when a > b else ‘ 0’; alb <= ‘ 1’ when a < b else ‘ 0’; end a_comp; Introduction to VHDL A B Comp EQ AGB ALB Page 1 - 34

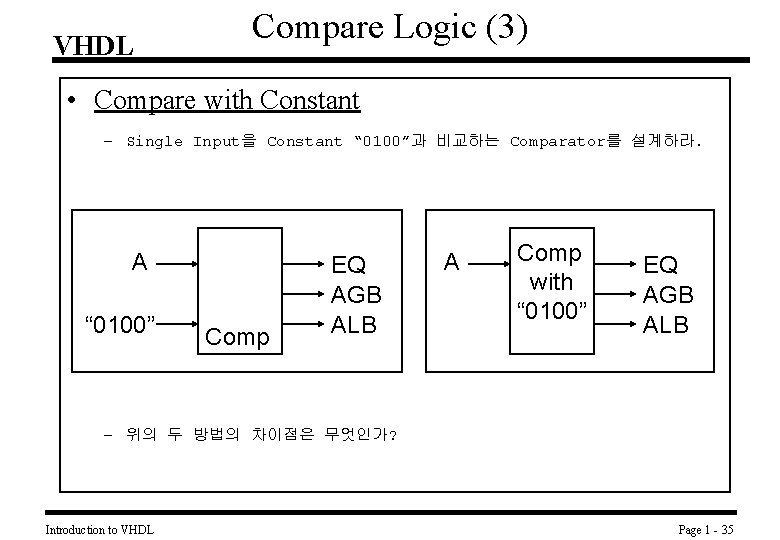

VHDL Compare Logic (3) • Compare with Constant – Single Input을 Constant “ 0100”과 비교하는 Comparator를 설계하라. A “ 0100” Comp EQ AGB ALB A Comp with “ 0100” EQ AGB ALB – 위의 두 방법의 차이점은 무엇인가? Introduction to VHDL Page 1 - 35

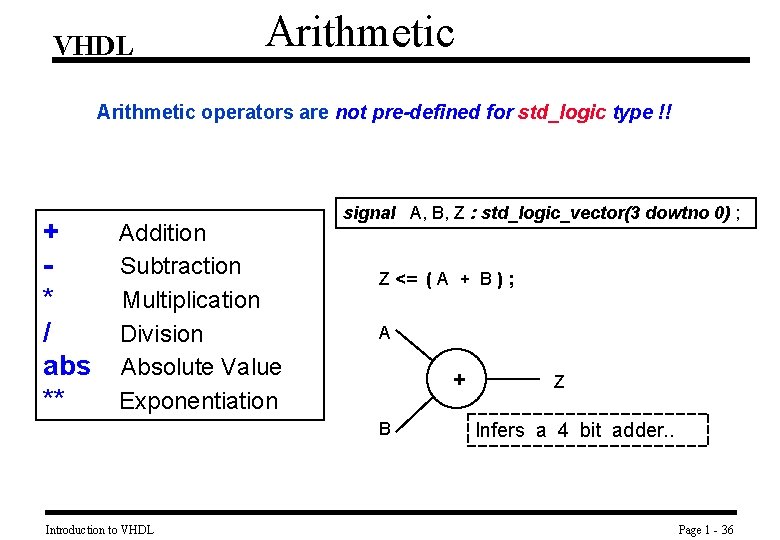

VHDL Arithmetic operators are not pre-defined for std_logic type !! + * / abs ** Addition Subtraction Multiplication Division Absolute Value Exponentiation signal A, B, Z : std_logic_vector(3 dowtno 0) ; Z <= ( A + B ) ; A + B Introduction to VHDL Z Infers a 4 bit adder. . Page 1 - 36

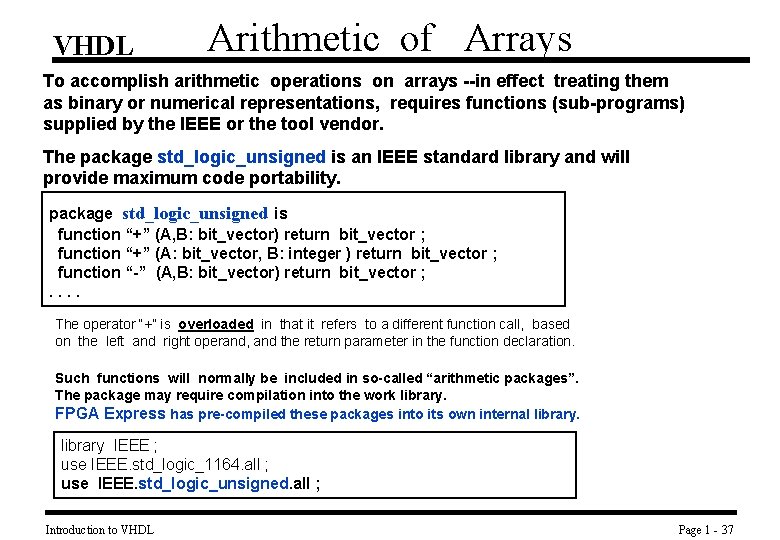

VHDL Arithmetic of Arrays To accomplish arithmetic operations on arrays --in effect treating them as binary or numerical representations, requires functions (sub-programs) supplied by the IEEE or the tool vendor. The package std_logic_unsigned is an IEEE standard library and will provide maximum code portability. package std_logic_unsigned is function “+” (A, B: bit_vector) return bit_vector ; function “+” (A: bit_vector, B: integer ) return bit_vector ; function “-” (A, B: bit_vector) return bit_vector ; . . The operator “+” is overloaded in that it refers to a different function call, based on the left and right operand, and the return parameter in the function declaration. Such functions will normally be included in so-called “arithmetic packages”. The package may require compilation into the work library. FPGA Express has pre-compiled these packages into its own internal library IEEE ; use IEEE. std_logic_1164. all ; use IEEE. std_logic_unsigned. all ; Introduction to VHDL Page 1 - 37

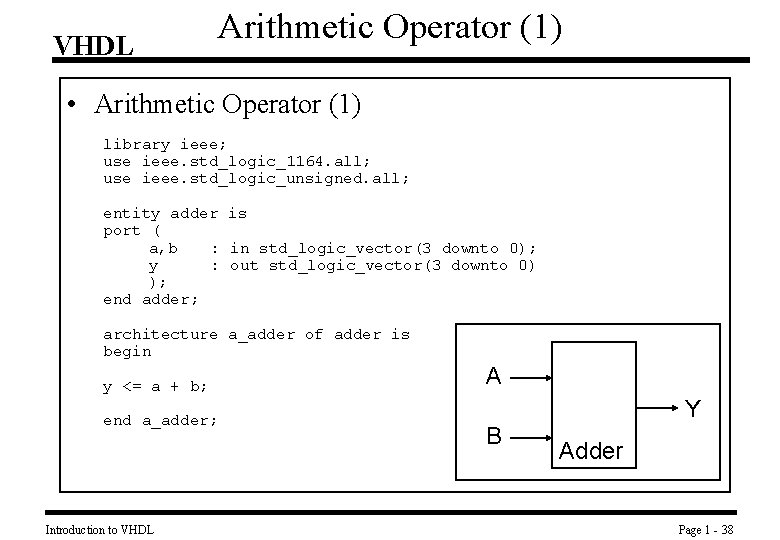

VHDL Arithmetic Operator (1) • Arithmetic Operator (1) library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity adder is port ( a, b : in std_logic_vector(3 downto 0); y : out std_logic_vector(3 downto 0) ); end adder; architecture a_adder of adder is begin y <= a + b; end a_adder; Introduction to VHDL A Y B Adder Page 1 - 38

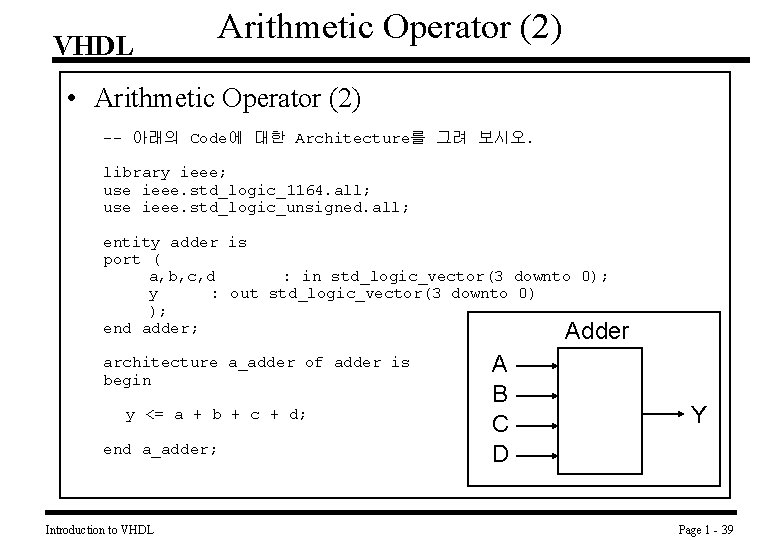

VHDL Arithmetic Operator (2) • Arithmetic Operator (2) -- 아래의 Code에 대한 Architecture를 그려 보시오. library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity adder is port ( a, b, c, d : in std_logic_vector(3 downto 0); y : out std_logic_vector(3 downto 0) ); end adder; Adder architecture a_adder of adder is begin y <= a + b + c + d; end a_adder; Introduction to VHDL A B C D Y Page 1 - 39

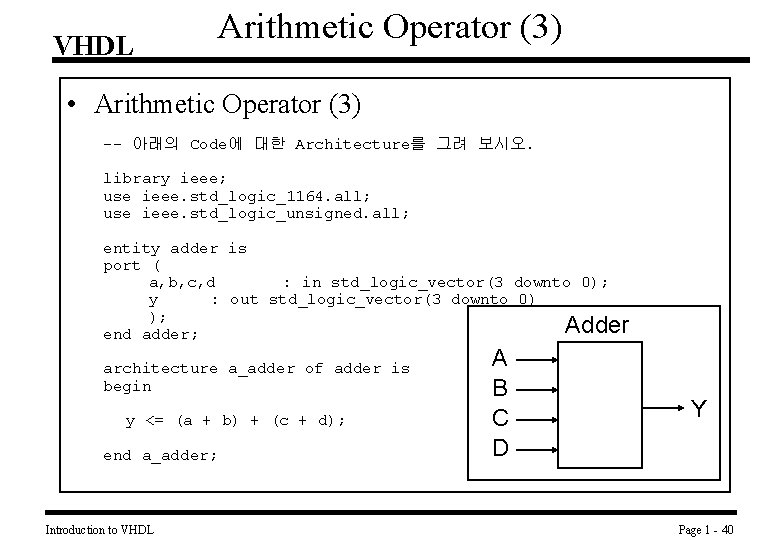

VHDL Arithmetic Operator (3) • Arithmetic Operator (3) -- 아래의 Code에 대한 Architecture를 그려 보시오. library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity adder is port ( a, b, c, d : in std_logic_vector(3 downto 0); y : out std_logic_vector(3 downto 0) ); Adder end adder; architecture a_adder of adder is begin y <= (a + b) + (c + d); end a_adder; Introduction to VHDL A B C D Y Page 1 - 40

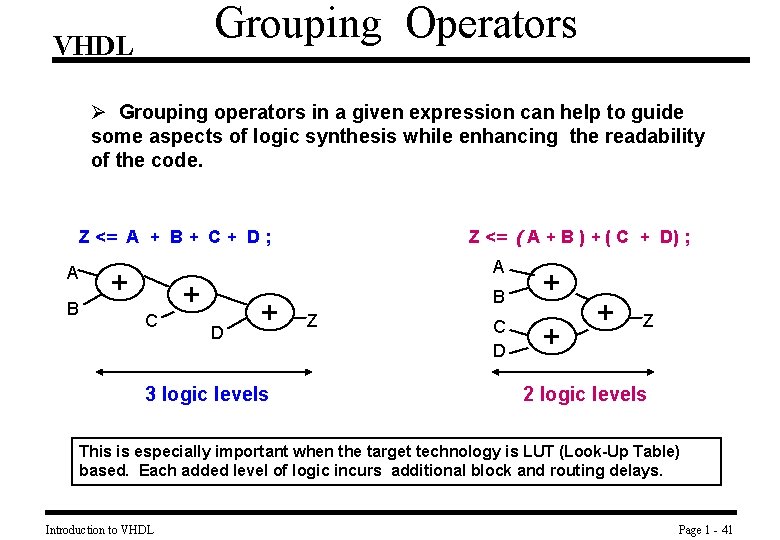

Grouping Operators VHDL Ø Grouping operators in a given expression can help to guide some aspects of logic synthesis while enhancing the readability of the code. Z <= A + B + C + D ; A B Z <= ( A + B ) + ( C + D) ; A + C + D + 3 logic levels B Z C D + + + Z 2 logic levels This is especially important when the target technology is LUT (Look-Up Table) based. Each added level of logic incurs additional block and routing delays. Introduction to VHDL Page 1 - 41

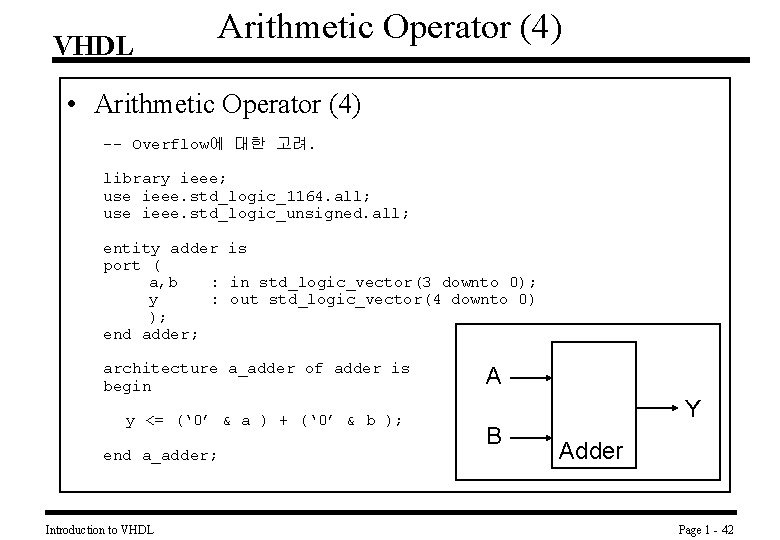

VHDL Arithmetic Operator (4) • Arithmetic Operator (4) -- Overflow에 대한 고려. library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity adder is port ( a, b : in std_logic_vector(3 downto 0); y : out std_logic_vector(4 downto 0) ); end adder; architecture a_adder of adder is begin y <= (‘ 0’ & a ) + (‘ 0’ & b ); end a_adder; Introduction to VHDL A Y B Adder Page 1 - 42

VHDL • • Combinational Logic Summary Logic Operator Arithmetic Operator Relational Operator Concatenation Bus < bit direction > when < > else 구문 with < > select < > when 구문 Introduction to VHDL Page 1 - 43

VHDL Synthesis에 대한 고려 • RTL Synthesis : Single Cycle만 설정 가능. • Hard Ware Architecture Design은 Manual로 – (A + B + C + D ) vs (A + B) + (C + D) • Synthesis Tool의 한계 • 좋은 Synthesis Tool이란? Introduction to VHDL Page 1 - 44

VHDL Design with VHDL(2) (Sequential Logic ) Introduction to VHDL Page 1 - 1

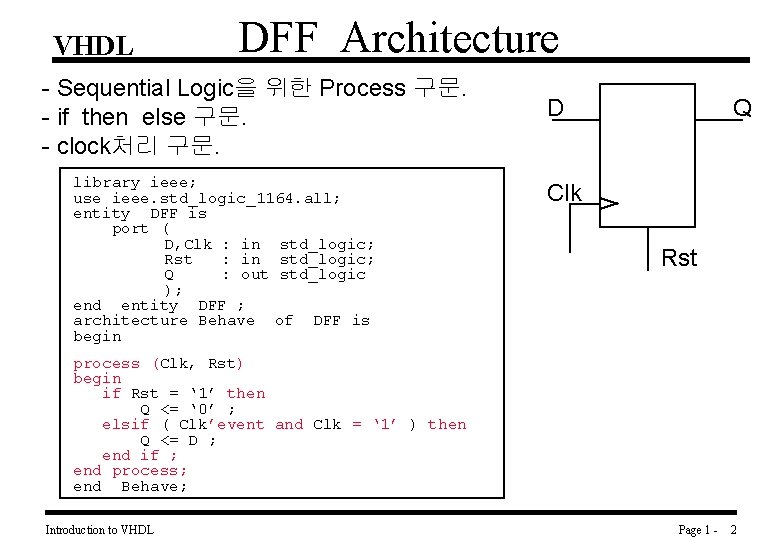

VHDL DFF Architecture - Sequential Logic을 위한 Process 구문. - if then else 구문. - clock처리 구문. library ieee; use ieee. std_logic_1164. all; entity DFF is port ( D, Clk : in std_logic; Rst : in std_logic; Q : out std_logic ); end entity DFF ; architecture Behave of DFF is begin D Q Clk Rst process (Clk, Rst) begin if Rst = ‘ 1’ then Q <= ‘ 0’ ; elsif ( Clk’event and Clk = ‘ 1’ ) then Q <= D ; end if ; end process; end Behave; Introduction to VHDL Page 1 - 2

Process 구문 VHDL * Sequential Control을 위한 구문. * Architecture 내부에 존재. * Sensitivity List의 Signal에 변화있을 때 구동. * Process 구문 내의 Instruction들은 순차적으로 수행. (Process 밖의 구문은 Concurrent로 수행. ) process (sensitivity list here) begin end process; . Introduction to VHDL Page 1 - 3

If then else 구문 VHDL * Alternative Selection을 위한 구문. * Process문 내부에 존재. * 존재 가능한 모든 Selection 조건을 Cover해야 함. if (condition 1) then elsif (condition 2) then elsif (condition 3) then else end if; . Introduction to VHDL Page 1 - 4

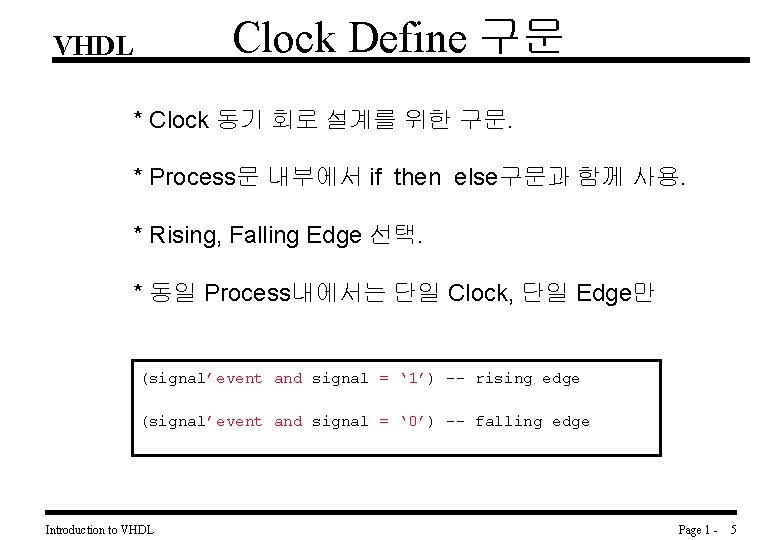

Clock Define 구문 VHDL * Clock 동기 회로 설계를 위한 구문. * Process문 내부에서 if then else구문과 함께 사용. * Rising, Falling Edge 선택. * 동일 Process내에서는 단일 Clock, 단일 Edge만. (signal’event and signal = ‘ 1’) -- rising edge (signal’event and signal = ‘ 0’) -- falling edge Introduction to VHDL Page 1 - 5

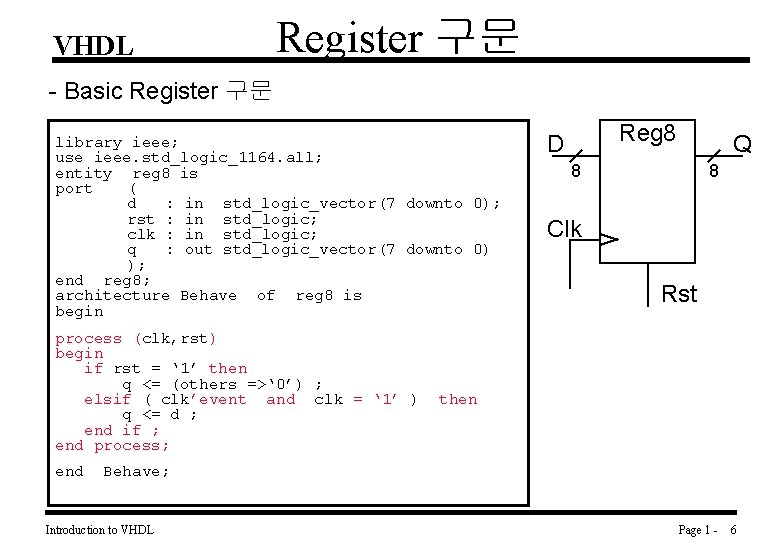

VHDL Register 구문 - Basic Register 구문 library ieee; use ieee. std_logic_1164. all; entity reg 8 is port ( d : in std_logic_vector(7 downto 0); rst : in std_logic; clk : in std_logic; q : out std_logic_vector(7 downto 0) ); end reg 8; architecture Behave of reg 8 is begin process (clk, rst) begin if rst = ‘ 1’ then q <= (others =>‘ 0’) ; elsif ( clk’event and clk = ‘ 1’ ) q <= d ; end if ; end process; end Reg 8 D Q 8 8 Clk Rst then Behave; Introduction to VHDL Page 1 - 6

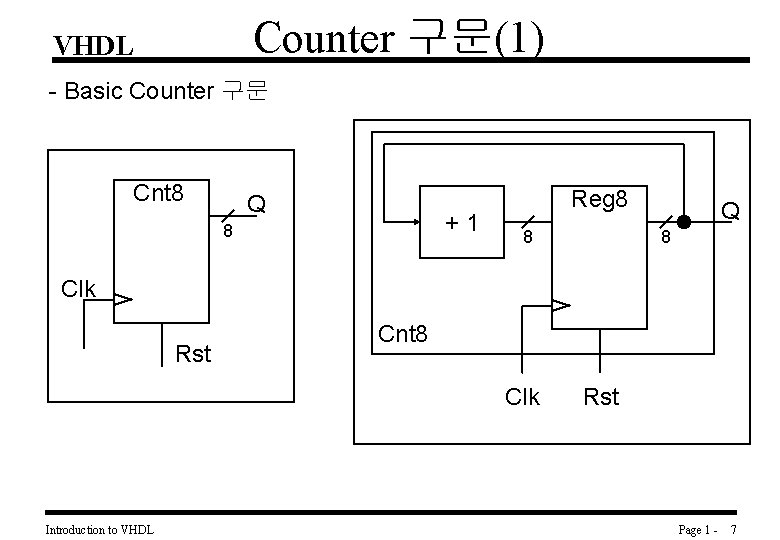

Counter 구문(1) VHDL - Basic Counter 구문 Cnt 8 Q +1 8 Reg 8 8 Q 8 Clk Rst Cnt 8 Clk Introduction to VHDL Rst Page 1 - 7

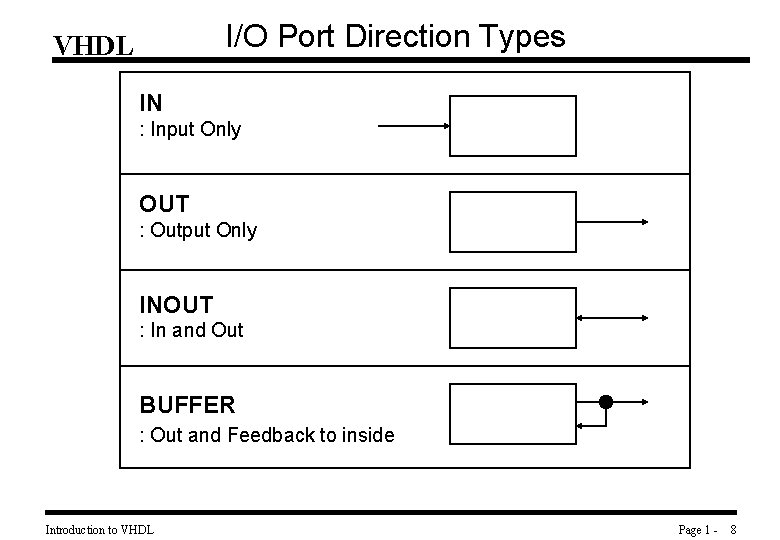

I/O Port Direction Types VHDL IN : Input Only OUT : Output Only INOUT : In and Out BUFFER : Out and Feedback to inside Introduction to VHDL Page 1 - 8

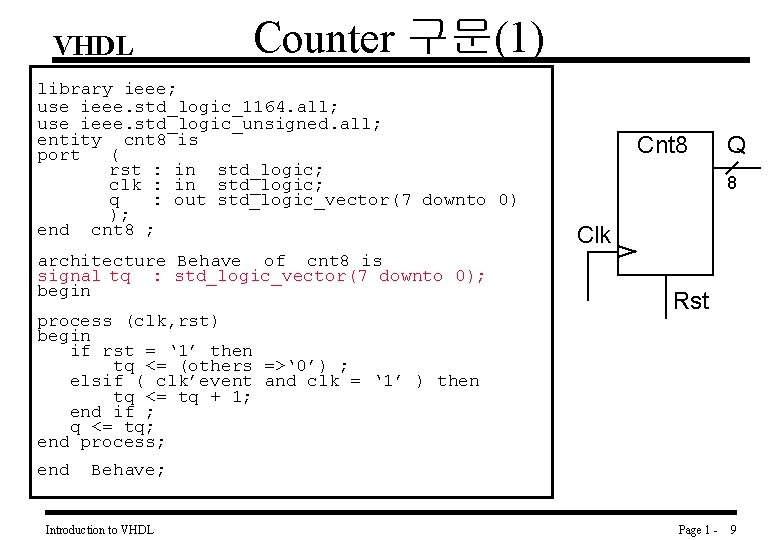

VHDL Counter 구문(1) library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity cnt 8 is port ( rst : in std_logic; clk : in std_logic; q : out std_logic_vector(7 downto 0) ); end cnt 8 ; architecture Behave of cnt 8 is signal tq : std_logic_vector(7 downto 0); begin process (clk, rst) begin if rst = ‘ 1’ then tq <= (others =>‘ 0’) ; elsif ( clk’event and clk = ‘ 1’ ) then tq <= tq + 1; end if ; q <= tq; end process; end Cnt 8 Q 8 Clk Rst Behave; Introduction to VHDL Page 1 - 9

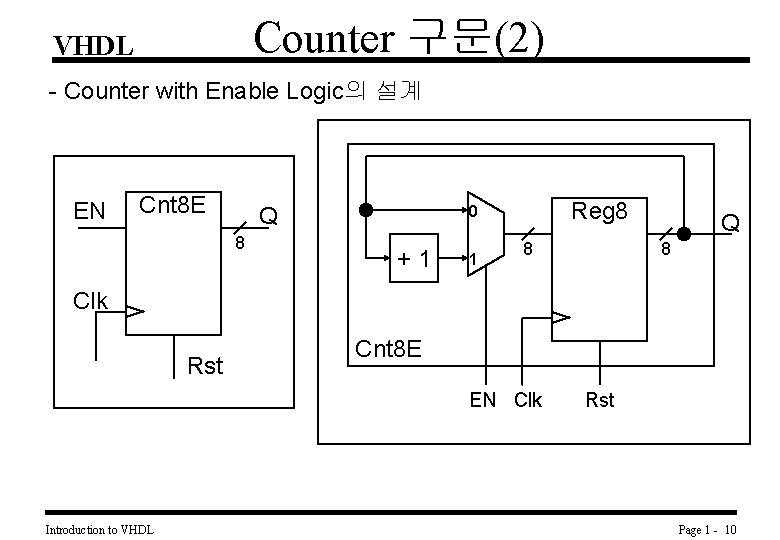

Counter 구문(2) VHDL - Counter with Enable Logic의 설계 EN Cnt 8 E 8 Reg 8 0 Q +1 1 8 Q 8 Clk Rst Cnt 8 E EN Clk Introduction to VHDL Rst Page 1 - 10

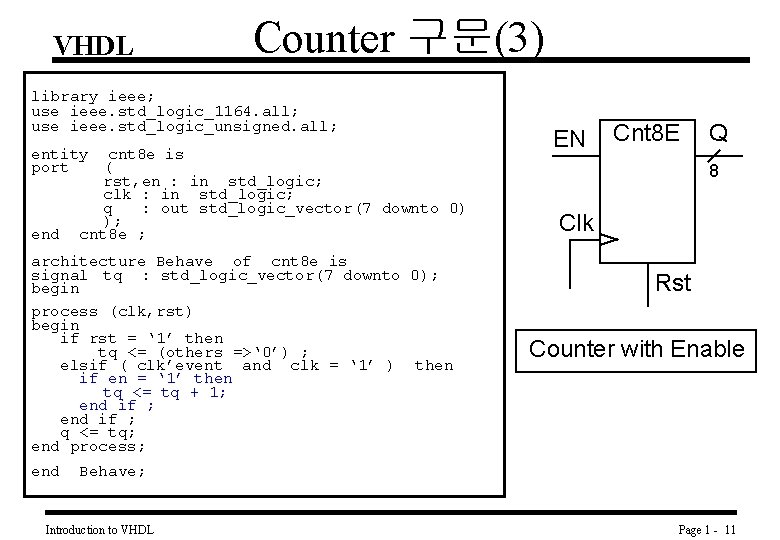

VHDL Counter 구문(3) library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity cnt 8 e is port ( rst, en : in std_logic; clk : in std_logic; q : out std_logic_vector(7 downto 0) ); end cnt 8 e ; architecture Behave of cnt 8 e is signal tq : std_logic_vector(7 downto 0); begin process (clk, rst) begin if rst = ‘ 1’ then tq <= (others =>‘ 0’) ; elsif ( clk’event and clk = ‘ 1’ ) then if en = ‘ 1’ then tq <= tq + 1; end if ; q <= tq; end process; end EN Cnt 8 E Q 8 Clk Rst Counter with Enable Behave; Introduction to VHDL Page 1 - 11

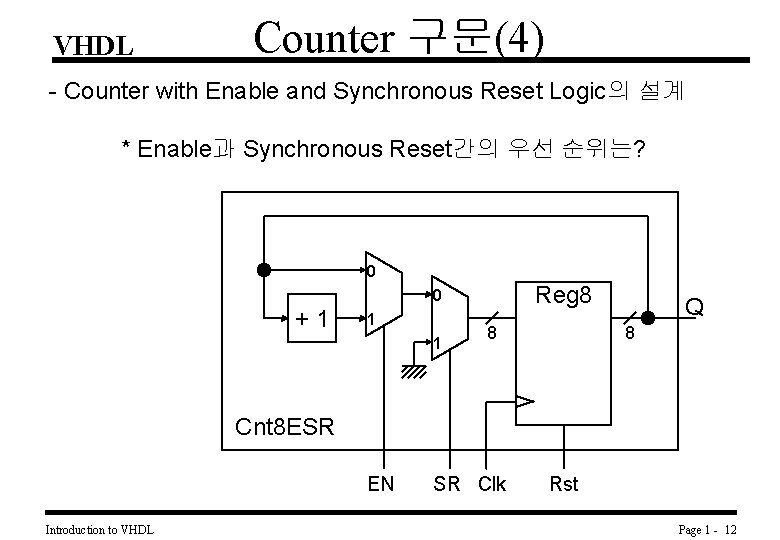

VHDL Counter 구문(4) - Counter with Enable and Synchronous Reset Logic의 설계 * Enable과 Synchronous Reset간의 우선 순위는? 0 Reg 8 0 +1 1 1 8 Q 8 Cnt 8 ESR EN Introduction to VHDL SR Clk Rst Page 1 - 12

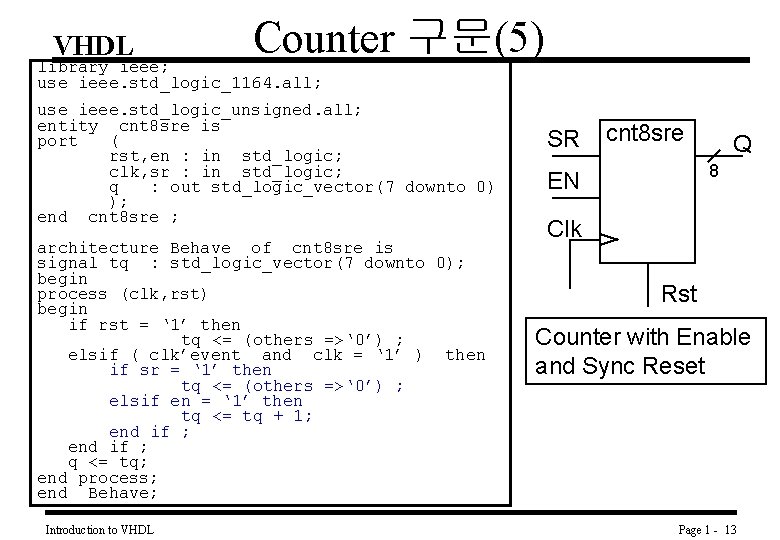

VHDL Counter 구문(5) library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity cnt 8 sre is port ( rst, en : in std_logic; clk, sr : in std_logic; q : out std_logic_vector(7 downto 0) ); end cnt 8 sre ; architecture Behave of cnt 8 sre is signal tq : std_logic_vector(7 downto 0); begin process (clk, rst) begin if rst = ‘ 1’ then tq <= (others =>‘ 0’) ; elsif ( clk’event and clk = ‘ 1’ ) then if sr = ‘ 1’ then tq <= (others =>‘ 0’) ; elsif en = ‘ 1’ then tq <= tq + 1; end if ; q <= tq; end process; end Behave; Introduction to VHDL SR cnt 8 sre Q 8 EN Clk Rst Counter with Enable and Sync Reset Page 1 - 13

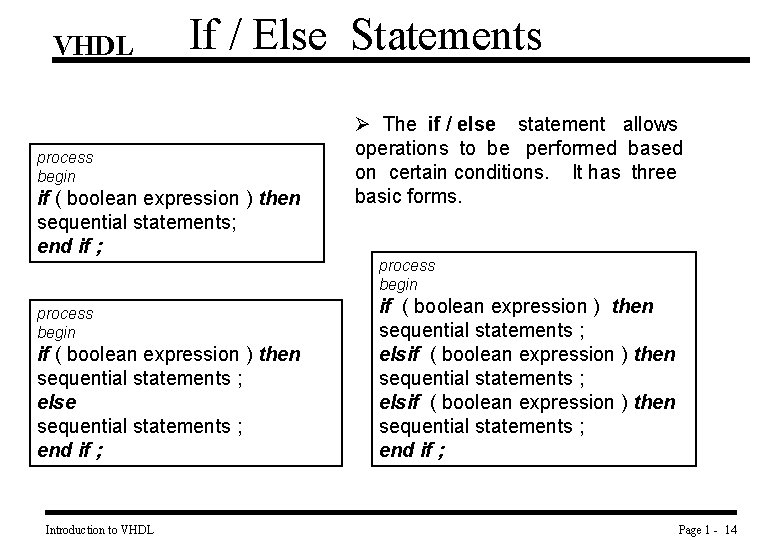

VHDL If / Else Statements process begin if ( boolean expression ) then sequential statements; end if ; process begin if ( boolean expression ) then sequential statements ; else sequential statements ; end if ; Introduction to VHDL Ø The if / else statement allows operations to be performed based on certain conditions. It has three basic forms. process begin if ( boolean expression ) then sequential statements ; elsif ( boolean expression ) then sequential statements ; end if ; Page 1 - 14

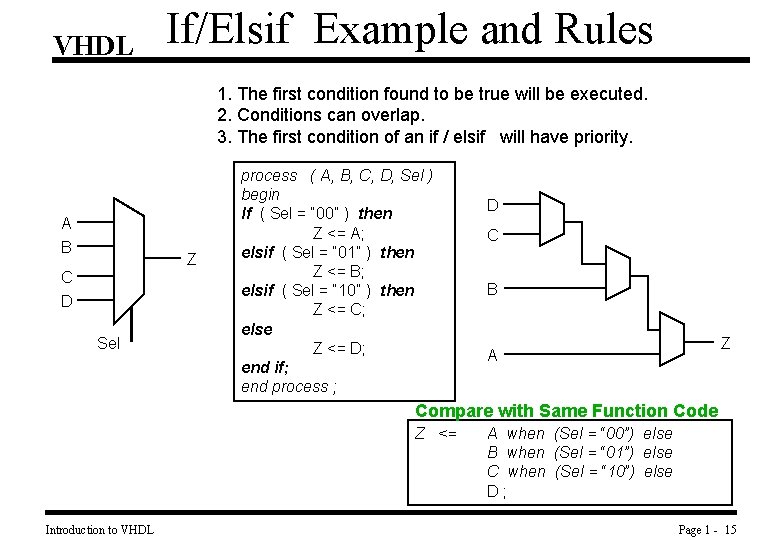

VHDL If/Elsif Example and Rules 1. The first condition found to be true will be executed. 2. Conditions can overlap. 3. The first condition of an if / elsif will have priority. A B Z C D Sel process ( A, B, C, D, Sel ) begin If ( Sel = “ 00” ) then Z <= A; elsif ( Sel = “ 01” ) then Z <= B; elsif ( Sel = “ 10” ) then Z <= C; else Z <= D; end if; end process ; D C B Z A Compare with Same Function Code Z <= Introduction to VHDL A when (Sel = “ 00”) else B when (Sel = “ 01”) else C when (Sel = “ 10”) else D; Page 1 - 15

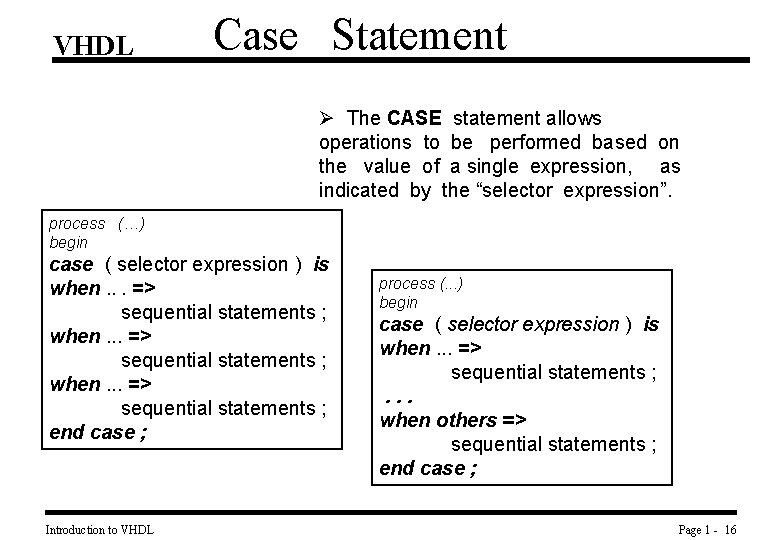

VHDL Case Statement Ø The CASE statement allows operations to be performed based on the value of a single expression, as indicated by the “selector expression”. process (…) begin case ( selector expression ) is when. . . => sequential statements ; end case ; Introduction to VHDL process (. . . ) begin case ( selector expression ) is when. . . => sequential statements ; . . . when others => sequential statements ; end case ; Page 1 - 16

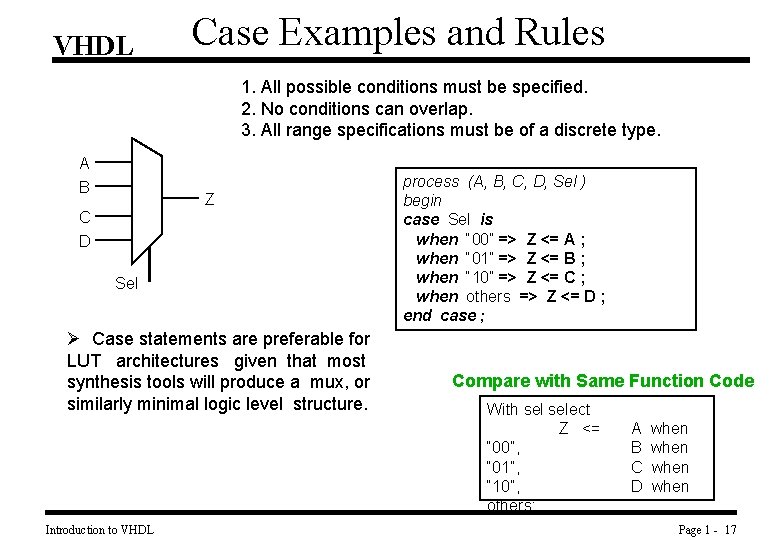

VHDL Case Examples and Rules 1. All possible conditions must be specified. 2. No conditions can overlap. 3. All range specifications must be of a discrete type. A B Z C D Sel Ø Case statements are preferable for LUT architectures given that most synthesis tools will produce a mux, or similarly minimal logic level structure. Introduction to VHDL process (A, B, C, D, Sel ) begin case Sel is when “ 00” => Z <= A ; when “ 01” => Z <= B ; when “ 10” => Z <= C ; when others => Z <= D ; end case ; Compare with Same Function Code With select Z <= “ 00”, “ 01”, “ 10”, others; A B C D when Page 1 - 17

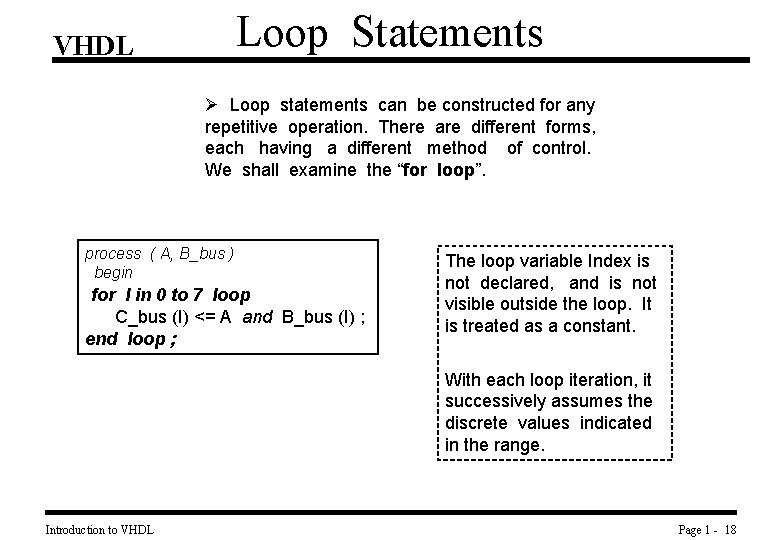

Loop Statements VHDL Ø Loop statements can be constructed for any repetitive operation. There are different forms, each having a different method of control. We shall examine the “for loop”. process ( A, B_bus ) begin for I in 0 to 7 loop C_bus (I) <= A and B_bus (I) ; end loop ; The loop variable Index is not declared, and is not visible outside the loop. It is treated as a constant. With each loop iteration, it successively assumes the discrete values indicated in the range. Introduction to VHDL Page 1 - 18

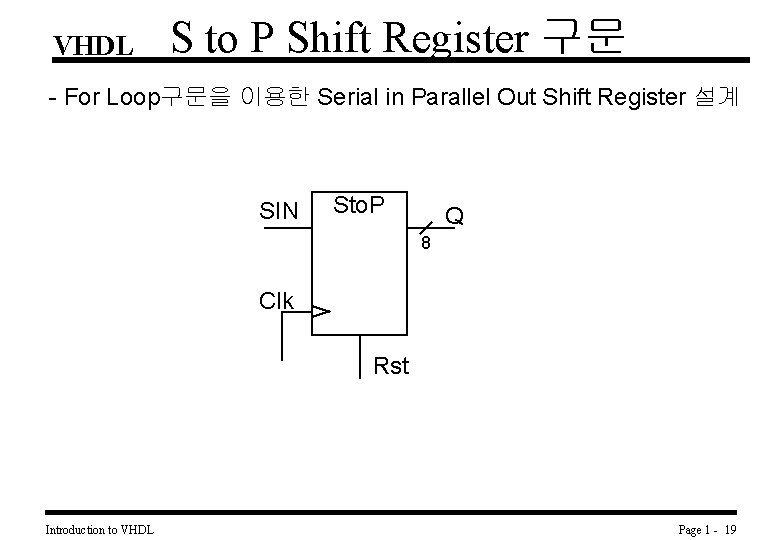

VHDL S to P Shift Register 구문 - For Loop구문을 이용한 Serial in Parallel Out Shift Register 설계 SIN Sto. P Q 8 Clk Rst Introduction to VHDL Page 1 - 19

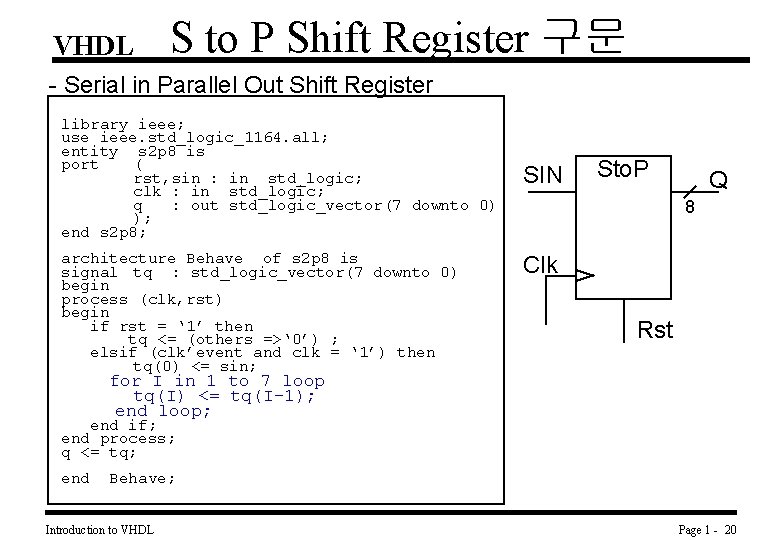

VHDL S to P Shift Register 구문 - Serial in Parallel Out Shift Register library ieee; use ieee. std_logic_1164. all; entity s 2 p 8 is port ( rst, sin : in std_logic; clk : in std_logic; q : out std_logic_vector(7 downto 0) ); end s 2 p 8; architecture Behave of s 2 p 8 is signal tq : std_logic_vector(7 downto 0) begin process (clk, rst) begin if rst = ‘ 1’ then tq <= (others =>‘ 0’) ; elsif (clk’event and clk = ‘ 1’) then tq(0) <= sin; SIN Sto. P Q 8 Clk Rst for I in 1 to 7 loop tq(I) <= tq(I-1); end loop; end if; end process; q <= tq; end Behave; Introduction to VHDL Page 1 - 20

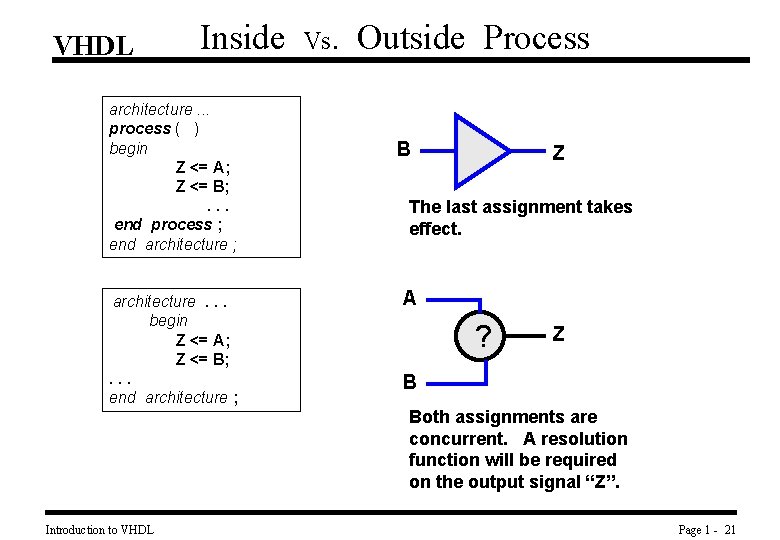

VHDL Inside architecture. . . process ( ) begin Z <= A; Z <= B; . . . end process ; end architecture ; architecture. . . begin Z <= A; Z <= B; . . . end architecture ; Vs. Outside Process B Z The last assignment takes effect. A ? Z B Both assignments are concurrent. A resolution function will be required on the output signal “Z”. Introduction to VHDL Page 1 - 21

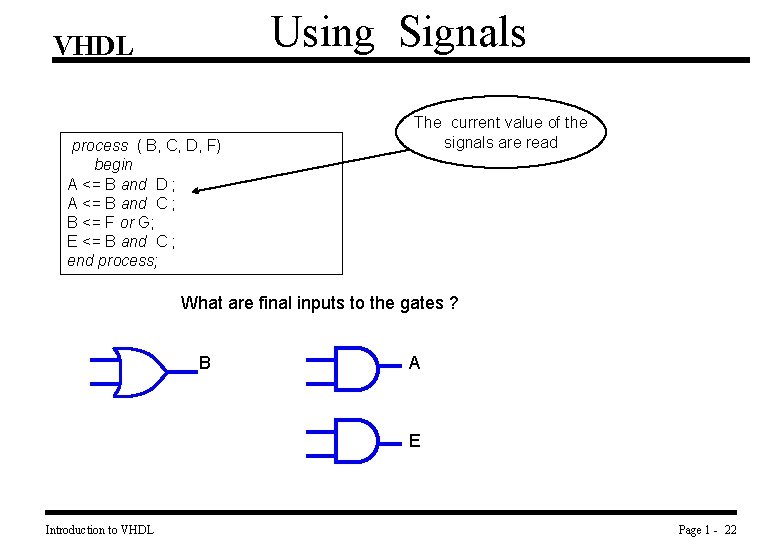

Using Signals VHDL process ( B, C, D, F) begin A <= B and D ; A <= B and C ; B <= F or G; E <= B and C ; end process; The current value of the signals are read What are final inputs to the gates ? B A E Introduction to VHDL Page 1 - 22

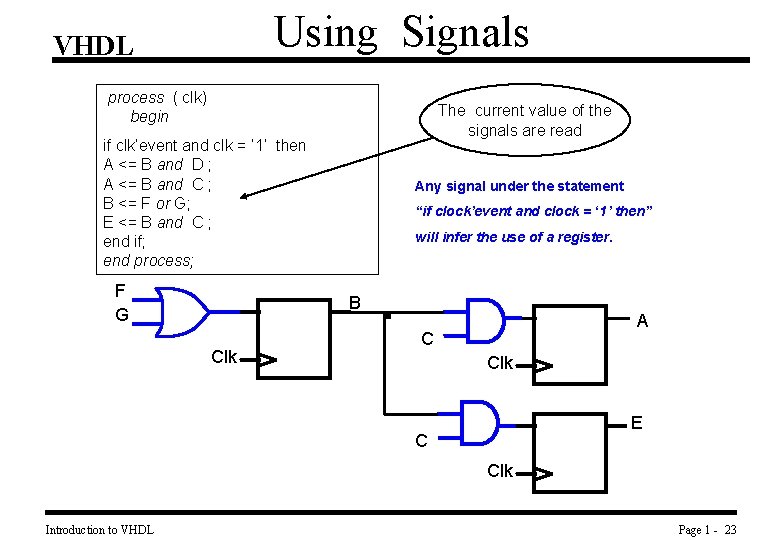

Using Signals VHDL process ( clk) begin The current value of the signals are read if clk’event and clk = ‘ 1’ then A <= B and D ; A <= B and C ; B <= F or G; E <= B and C ; end if; end process; F G Any signal under the statement “if clock’event and clock = ‘ 1’ then” will infer the use of a register. B Clk A C Clk E C Clk Introduction to VHDL Page 1 - 23

VHDL Design with VHDL (3) Hierarchy Design Flow Introduction to VHDL Page 1 - 1

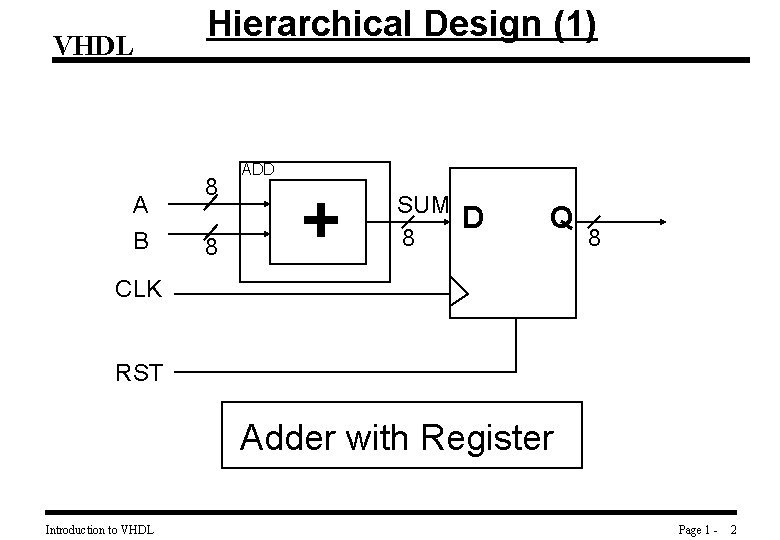

VHDL A B Hierarchical Design (1) 8 8 ADD + SUM 8 D Q 8 CLK RST Adder with Register Introduction to VHDL Page 1 - 2

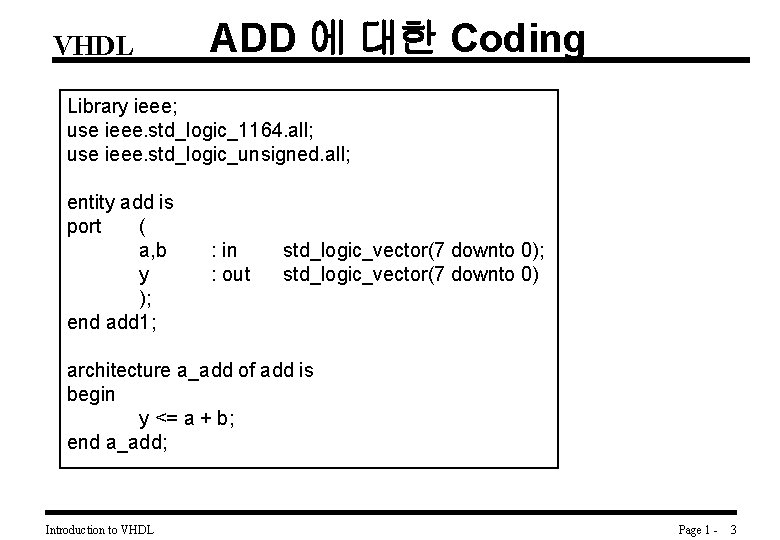

VHDL ADD 에 대한 Coding Library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity add is port ( a, b y ); end add 1; : in : out std_logic_vector(7 downto 0); std_logic_vector(7 downto 0) architecture a_add of add is begin y <= a + b; end a_add; Introduction to VHDL Page 1 - 3

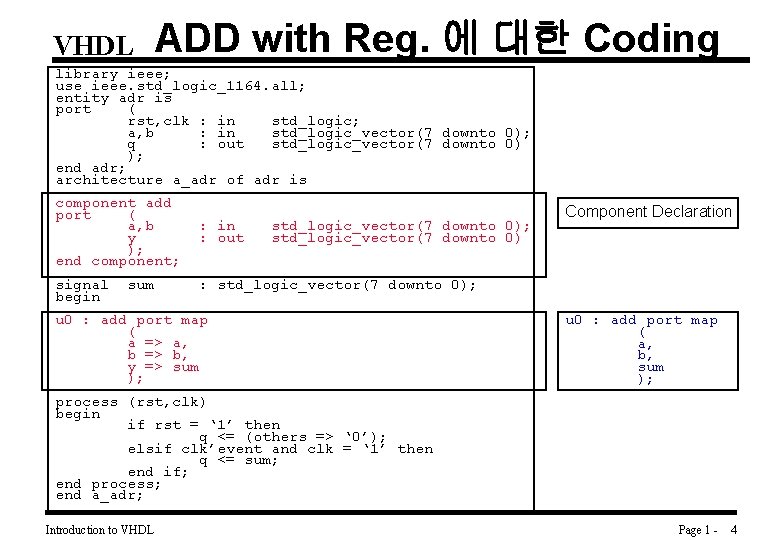

VHDL ADD with Reg. 에 대한 Coding library ieee; use ieee. std_logic_1164. all; entity adr is port ( rst, clk : in std_logic; a, b : in std_logic_vector(7 downto 0); q : out std_logic_vector(7 downto 0) ); end adr; architecture a_adr of adr is component add port ( a, b y ); end component; : in : out signal begin : std_logic_vector(7 downto 0); sum std_logic_vector(7 downto 0); std_logic_vector(7 downto 0) u 0 : add port map ( a => a, b => b, y => sum ); Component Declaration u 0 : add port map ( a, b, sum ); process (rst, clk) begin if rst = ‘ 1’ then q <= (others => ‘ 0’); elsif clk’event and clk = ‘ 1’ then q <= sum; end if; end process; end a_adr; Introduction to VHDL Page 1 - 4

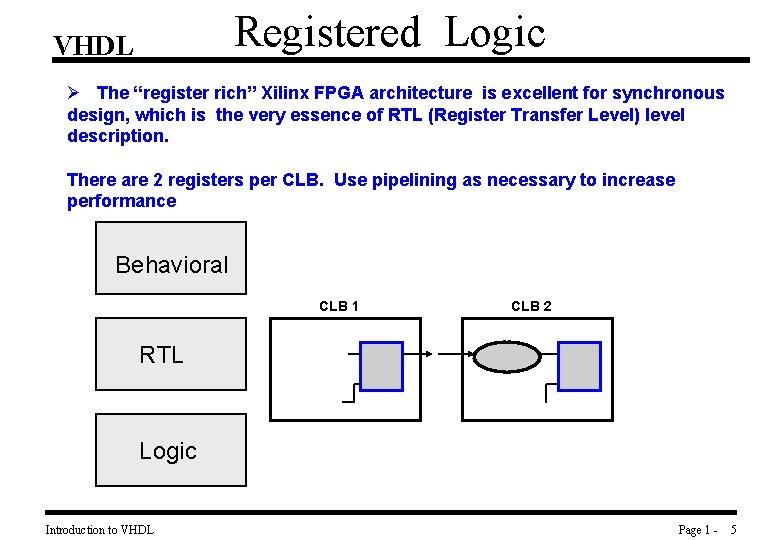

Registered Logic VHDL Ø The “register rich” Xilinx FPGA architecture is excellent for synchronous design, which is the very essence of RTL (Register Transfer Level) level description. There are 2 registers per CLB. Use pipelining as necessary to increase performance Behavioral CLB 1 CLB 2 RTL Logic Introduction to VHDL Page 1 - 5

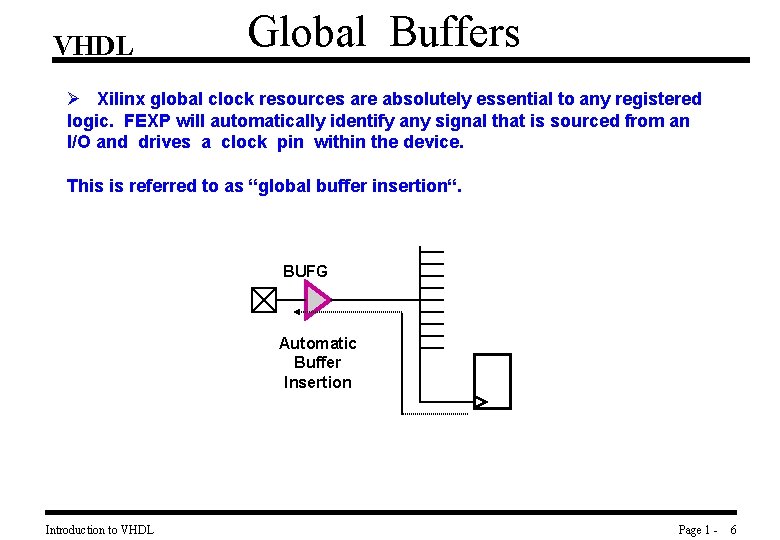

VHDL Global Buffers Ø Xilinx global clock resources are absolutely essential to any registered logic. FEXP will automatically identify any signal that is sourced from an I/O and drives a clock pin within the device. This is referred to as “global buffer insertion“. BUFG Automatic Buffer Insertion Introduction to VHDL Page 1 - 6

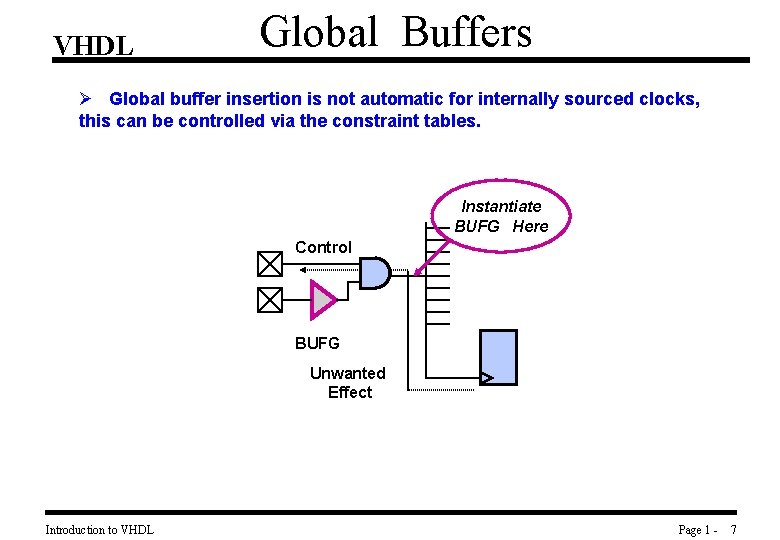

VHDL Global Buffers Ø Global buffer insertion is not automatic for internally sourced clocks, this can be controlled via the constraint tables. Instantiate BUFG Here Control BUFG Unwanted Effect Introduction to VHDL Page 1 - 7

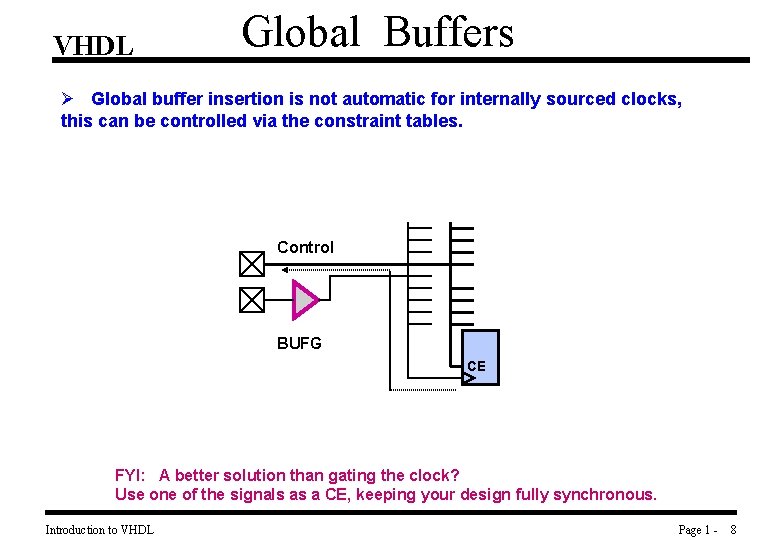

VHDL Global Buffers Ø Global buffer insertion is not automatic for internally sourced clocks, this can be controlled via the constraint tables. Control BUFG CE FYI: A better solution than gating the clock? Use one of the signals as a CE, keeping your design fully synchronous. Introduction to VHDL Page 1 - 8

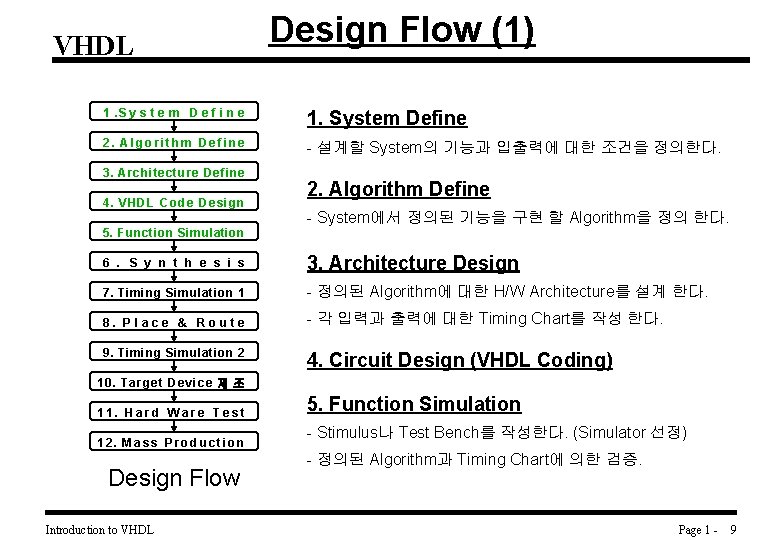

VHDL Design Flow (1) 1. S y s t e m D e f i n e 1. System Define 2. Algorithm Define - 설계할 System의 기능과 입출력에 대한 조건을 정의한다. 3. Architecture Define 4. VHDL Code Design 5. Function Simulation 2. Algorithm Define - System에서 정의된 기능을 구현 할 Algorithm을 정의 한다. 6. S y n t h e s i s 3. Architecture Design 7. Timing Simulation 1 - 정의된 Algorithm에 대한 H/W Architecture를 설계 한다. 8. Place & Route - 각 입력과 출력에 대한 Timing Chart를 작성 한다. 9. Timing Simulation 2 4. Circuit Design (VHDL Coding) 10. Target Device 제 조 11. Hard Ware Test 12. Mass Production Design Flow Introduction to VHDL 5. Function Simulation - Stimulus나 Test Bench를 작성한다. (Simulator 선정) - 정의된 Algorithm과 Timing Chart에 의한 검증. Page 1 - 9

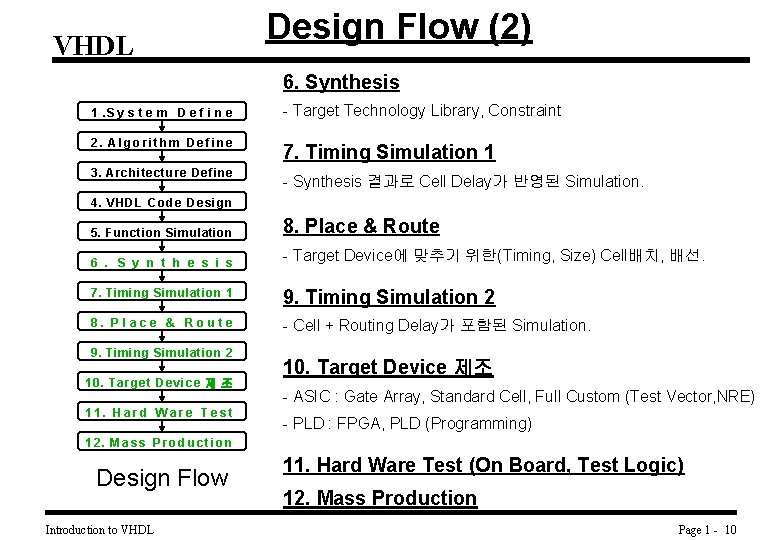

VHDL Design Flow (2) 6. Synthesis 1. S y s t e m D e f i n e - Target Technology Library, Constraint 2. Algorithm Define 7. Timing Simulation 1 3. Architecture Define - Synthesis 결과로 Cell Delay가 반영된 Simulation. 4. VHDL Code Design 5. Function Simulation 8. Place & Route 6. S y n t h e s i s - Target Device에 맞추기 위한(Timing, Size) Cell배치, 배선. 7. Timing Simulation 1 9. Timing Simulation 2 8. Place & Route - Cell + Routing Delay가 포함된 Simulation. 9. Timing Simulation 2 10. Target Device 제 조 11. Hard Ware Test 10. Target Device 제조 - ASIC : Gate Array, Standard Cell, Full Custom (Test Vector, NRE) - PLD : FPGA, PLD (Programming) 12. Mass Production Design Flow Introduction to VHDL 11. Hard Ware Test (On Board, Test Logic) 12. Mass Production Page 1 - 10

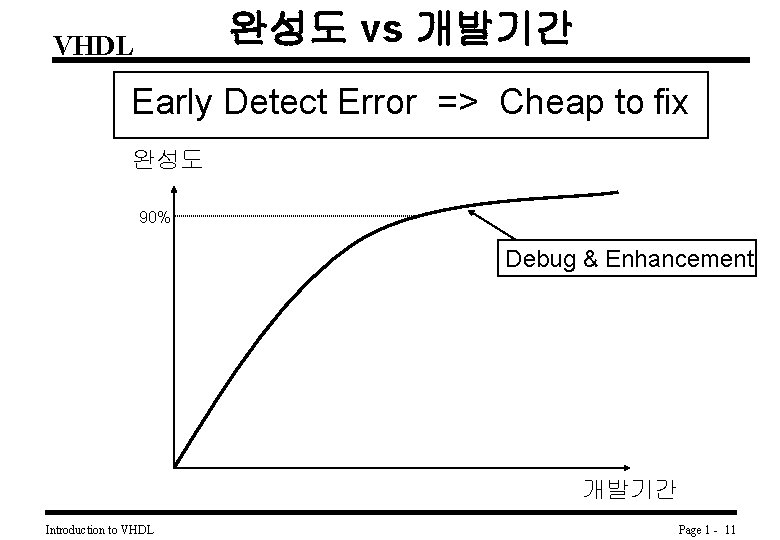

완성도 vs 개발기간 VHDL Early Detect Error => Cheap to fix 완성도 90% Debug & Enhancement 개발기간 Introduction to VHDL Page 1 - 11

VHDL 좋은 Solution을 얻으려면 1. 안정된 Design - Timing Margin, Fan Out등을 고려한 설계. - Synchronous Design (Counter, Example) - Target Technology에 맞는 설계 (FPGA Example) 2. Synthesis Tool에서의 Control. (Tool Performance, Option) 3. Place and Routing에서의 Control. Introduction to VHDL Page 1 - 12

VHDL Design with VHDL (4) - State Machine Design - Devices for Implementation Introduction to VHDL Page 1 -

State Machine Design (2) VHDL State Machine Design Example - 시, 분, 초 Control을 갖는 시계. - 동작 조건. 초기화, 시 조정, 분 조정, 정상 동작의 4개 Mode를 갖는다. - 입력 조건. Clock Input : 1 Hz Pulse. . Mode Key, Set Key. - 출력 조건. 시, 분, 초 Counter 출력. Introduction to VHDL Page 1 -

State Machine Design (3) VHDL State 동작 조건 - 초기화 State (Reset시). 시 Counter를 12로 Set. 분, 초 Counter는 Clear - 시 조정 State. Set 단자 입력의 Rising Edge에서 시 Counter Increment. - 분 조정 State. Set 단자 입력의 Rising Edge에서 분 Counter Increment. . 초 Counter는 Clear. - 정상 동작 State. 정상 시계 동작. - State Change는 Mode Key의 입력에 의해. Introduction to VHDL Page 1 -

VHDL State Machine Design (4) 1. VHDL Code 해설 2. Simulation 결과 해설 Introduction to VHDL Page 1 -

Potential Solutions VHDL • Discrete logic – not practical approach any longer – few available 3. 3 V/2. 5 V devices available • Chip sets – few available – expensive • Custom ASIC – long design cycle – costly to rework • Programmable Logic Introduction to VHDL Page 1 -

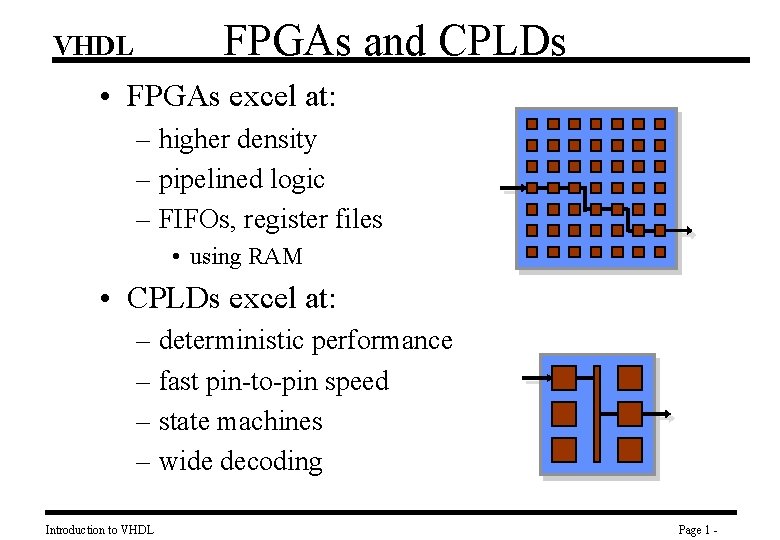

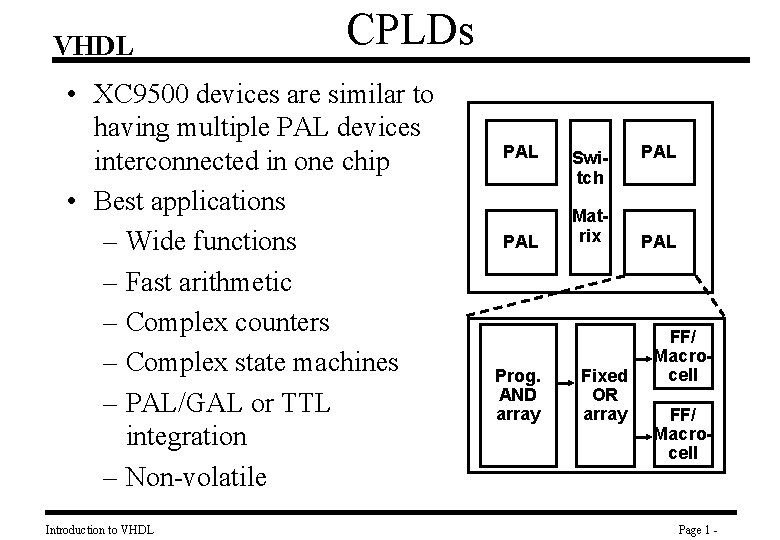

FPGAs and CPLDs VHDL • FPGAs excel at: – higher density – pipelined logic – FIFOs, register files • using RAM • CPLDs excel at: – deterministic performance – fast pin-to-pin speed – state machines – wide decoding Introduction to VHDL Page 1 -

VHDL Xilinx FPGA Architecture Benefits • SRAM programming cells – easy design changes • On-chip distributed Select. RAM memory – efficient FIFOs • Segmented routing – high speed and low power • Dedicated carry logic – high speed counters and arithmetic Introduction to VHDL Page 1 -

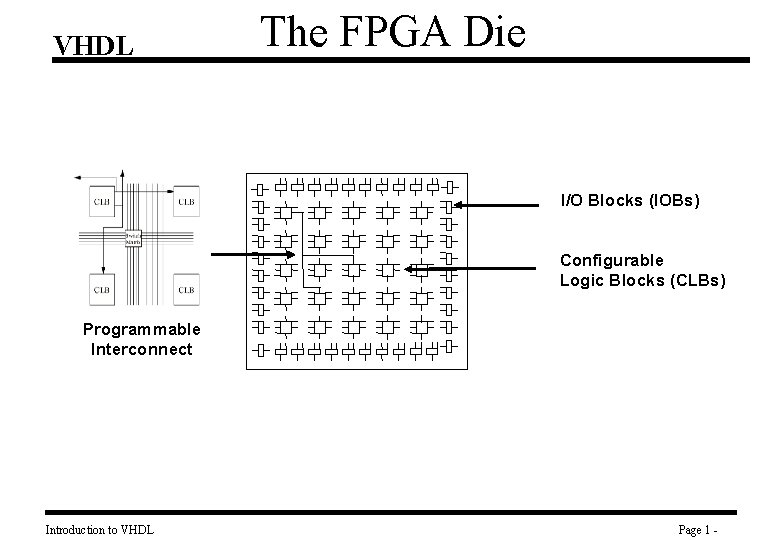

VHDL The FPGA Die I/O Blocks (IOBs) Configurable Logic Blocks (CLBs) Programmable Interconnect Introduction to VHDL Page 1 -

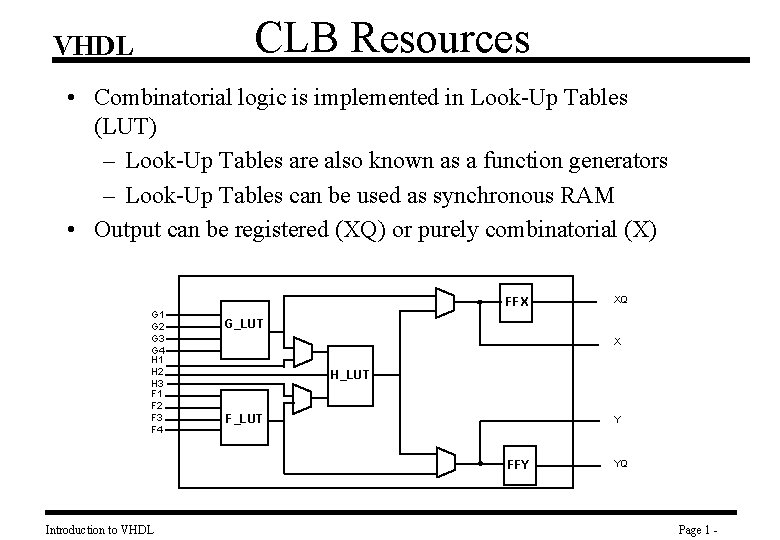

CLB Resources VHDL • Combinatorial logic is implemented in Look-Up Tables (LUT) – Look-Up Tables are also known as a function generators – Look-Up Tables can be used as synchronous RAM • Output can be registered (XQ) or purely combinatorial (X) FFX G 1 G 2 G 3 G 4 H 1 H 2 H 3 F 1 F 2 F 3 F 4 G_LUT X H_LUT F_LUT Y FFY Introduction to VHDL XQ YQ Page 1 -

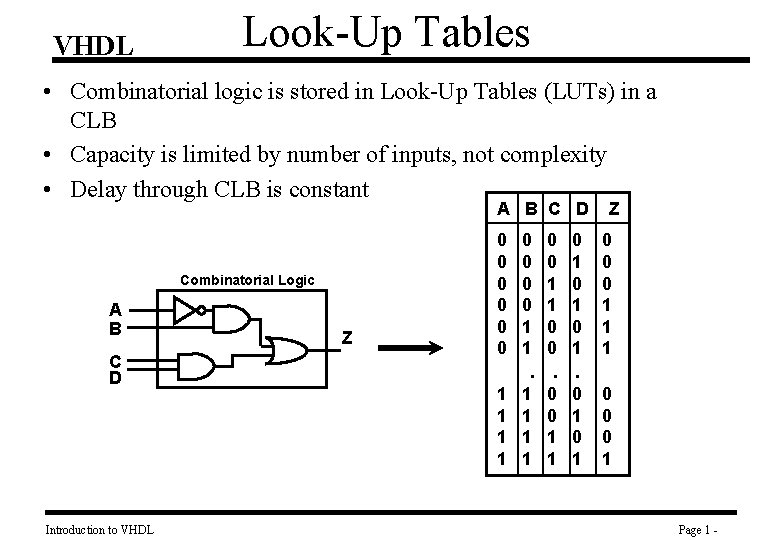

VHDL Look-Up Tables • Combinatorial logic is stored in Look-Up Tables (LUTs) in a CLB • Capacity is limited by number of inputs, not complexity • Delay through CLB is constant A B C D Combinatorial Logic A B C D Introduction to VHDL Z 0 0 0 0 0 1 1 0 0 0 1 0 1 Z 0 0 0 1 1 1 . . . 1 1 1 1 0 0 1 1 0 1 0 0 0 1 Page 1 -

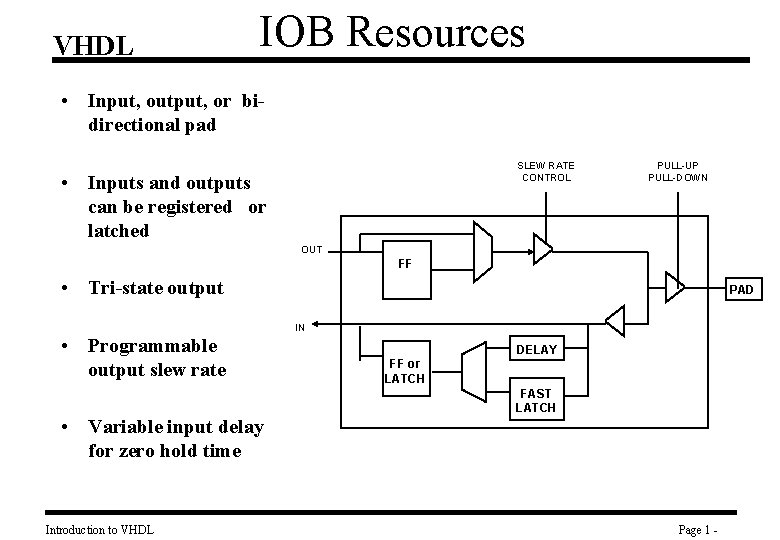

VHDL IOB Resources • Input, output, or bidirectional pad SLEW RATE CONTROL • Inputs and outputs can be registered or latched PULL-UP PULL-DOWN OUT FF • Tri-state output PAD IN • Programmable output slew rate DELAY FF or LATCH FAST LATCH • Variable input delay for zero hold time Introduction to VHDL Page 1 -

VHDL CPLDs • XC 9500 devices are similar to having multiple PAL devices interconnected in one chip • Best applications – Wide functions – Fast arithmetic – Complex counters – Complex state machines – PAL/GAL or TTL integration – Non-volatile Introduction to VHDL PAL Prog. AND array Switch Matrix Fixed OR array PAL FF/ Macrocell Page 1 -

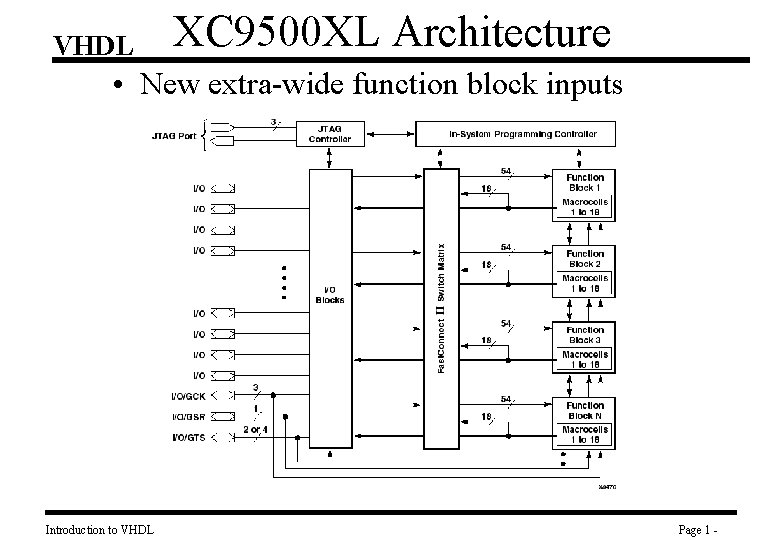

VHDL XC 9500 XL Architecture • New extra-wide function block inputs Introduction to VHDL Page 1 -

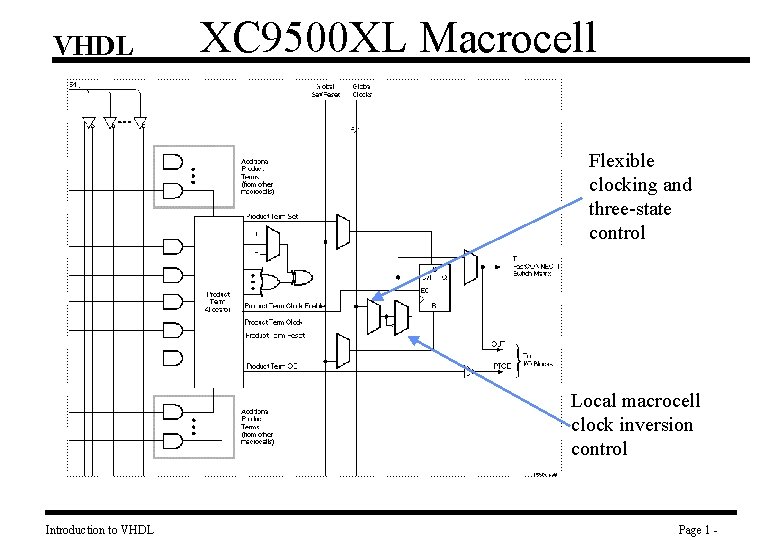

VHDL XC 9500 XL Macrocell Flexible clocking and three-state control Local macrocell clock inversion control Introduction to VHDL Page 1 -

VHDL Introduction to VHDL Compare FPGA and CPLD Page 1 -

- Slides: 113