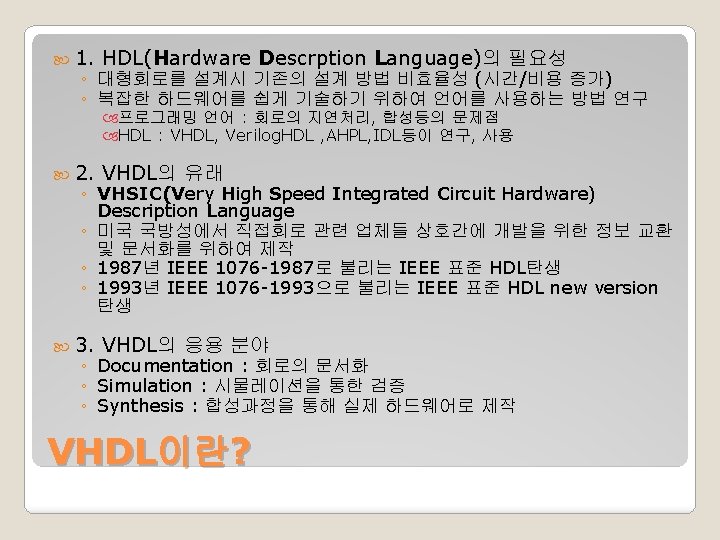

VHDL entity Design entity Entity Declaration VHDL Architecture

- Slides: 26

VHDL

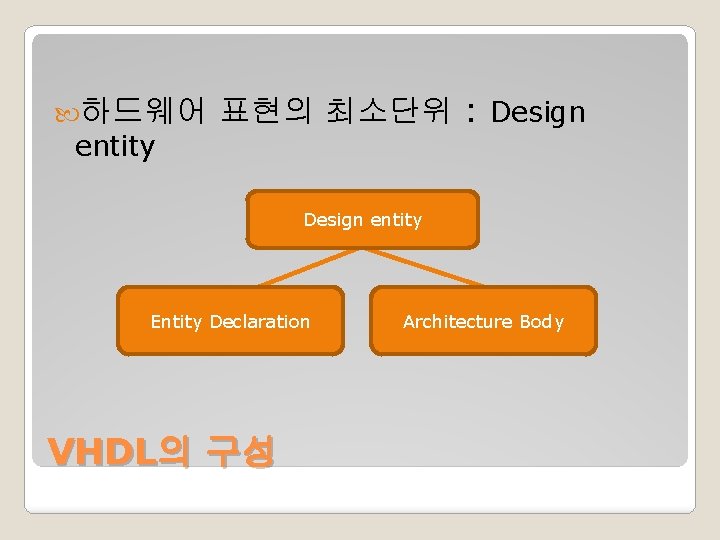

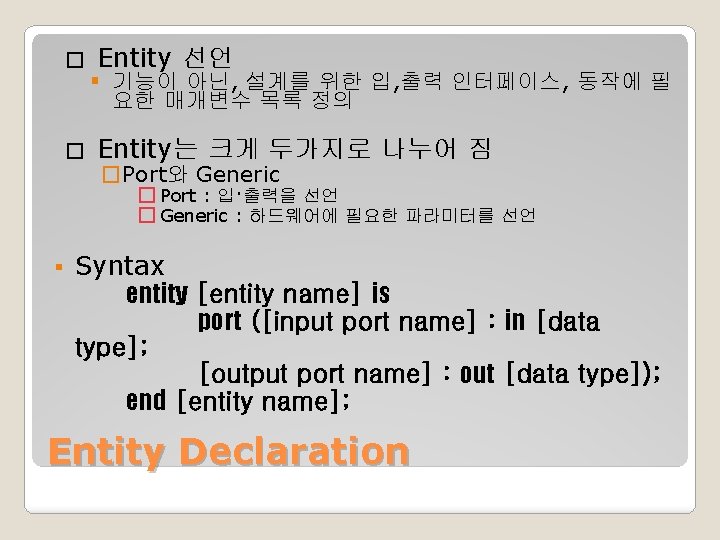

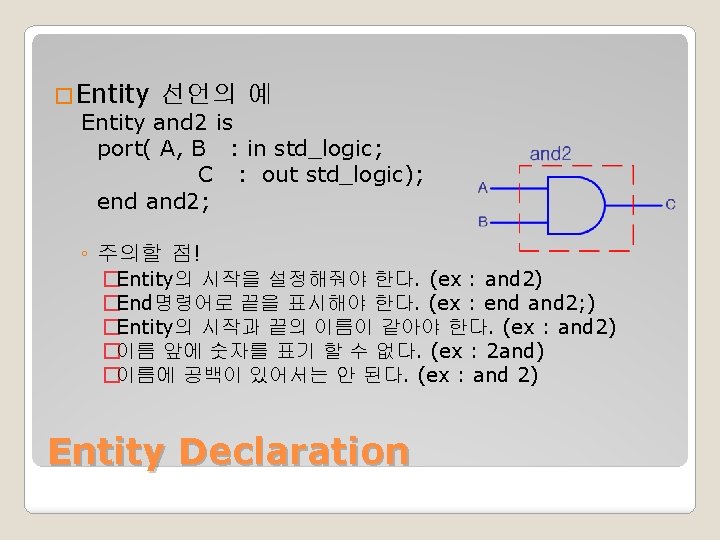

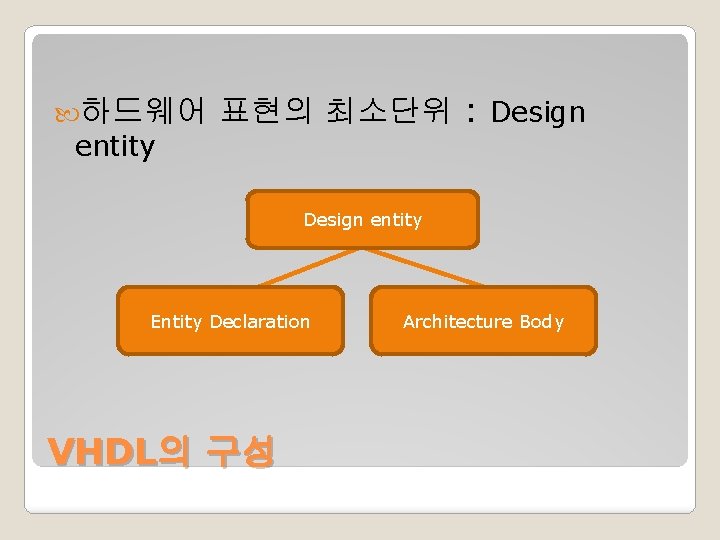

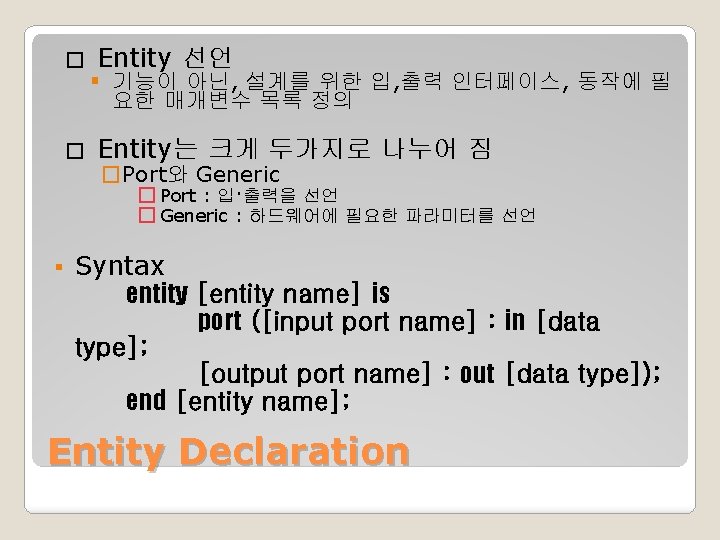

하드웨어 entity 표현의 최소단위 : Design entity Entity Declaration VHDL의 구성 Architecture Body

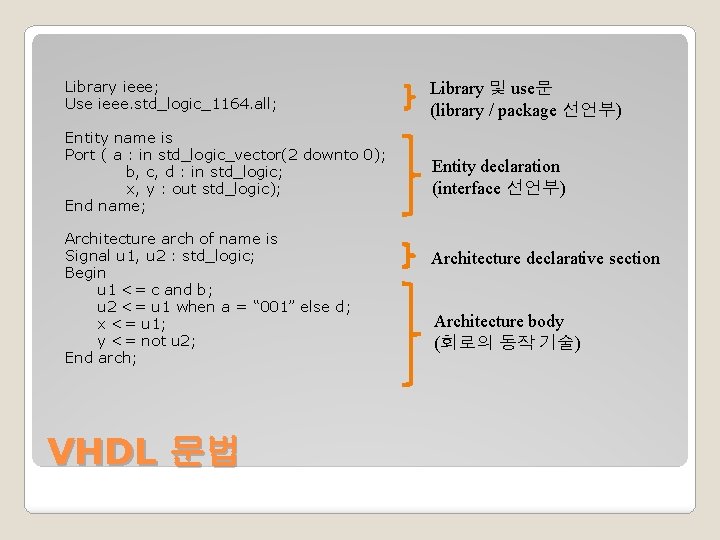

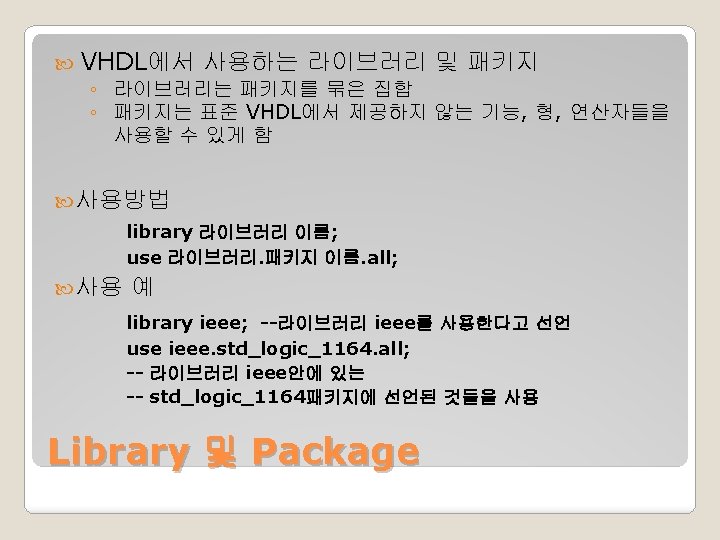

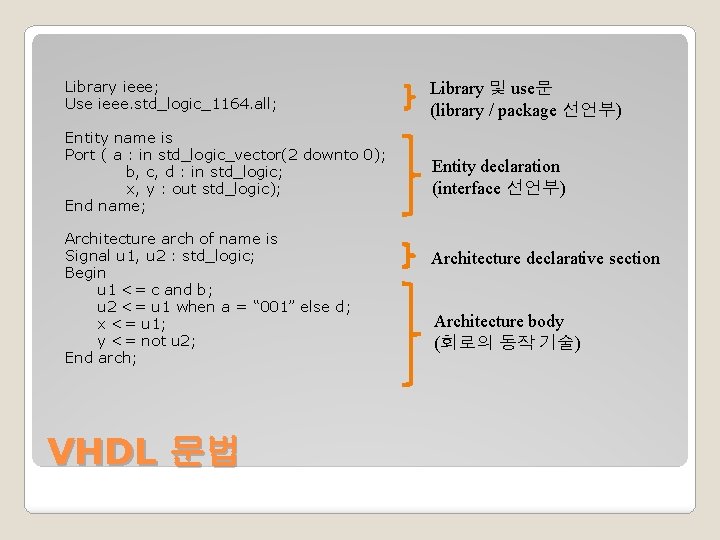

Library ieee; Use ieee. std_logic_1164. all; Library 및 use문 (library / package 선언부) Entity name is Port ( a : in std_logic_vector(2 downto 0); b, c, d : in std_logic; x, y : out std_logic); End name; Entity declaration (interface 선언부) Architecture arch of name is Signal u 1, u 2 : std_logic; Begin u 1 <= c and b; u 2 <= u 1 when a = “ 001” else d; x <= u 1; y <= not u 2; End arch; VHDL 문법 Architecture declarative section Architecture body (회로의 동작 기술)

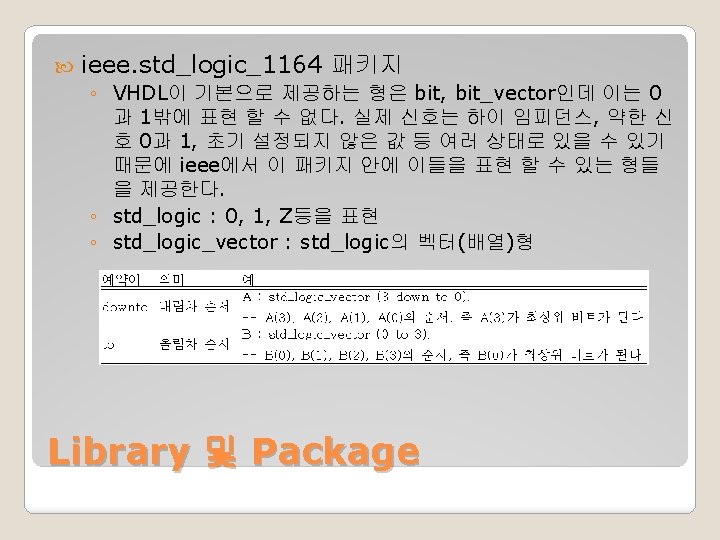

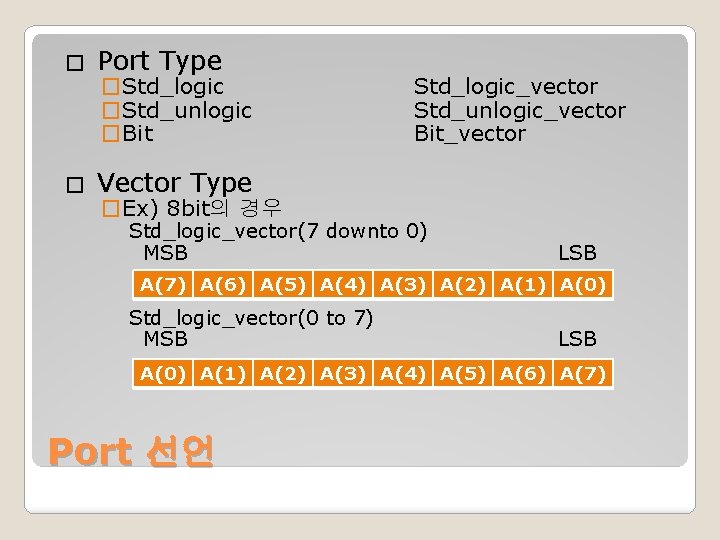

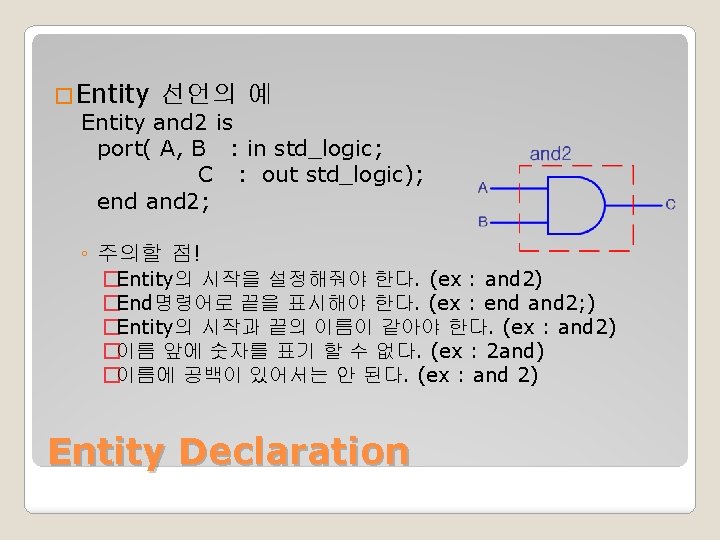

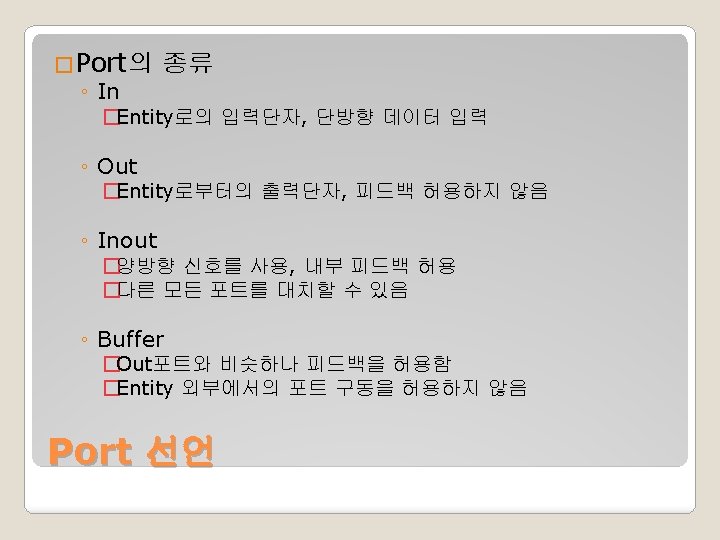

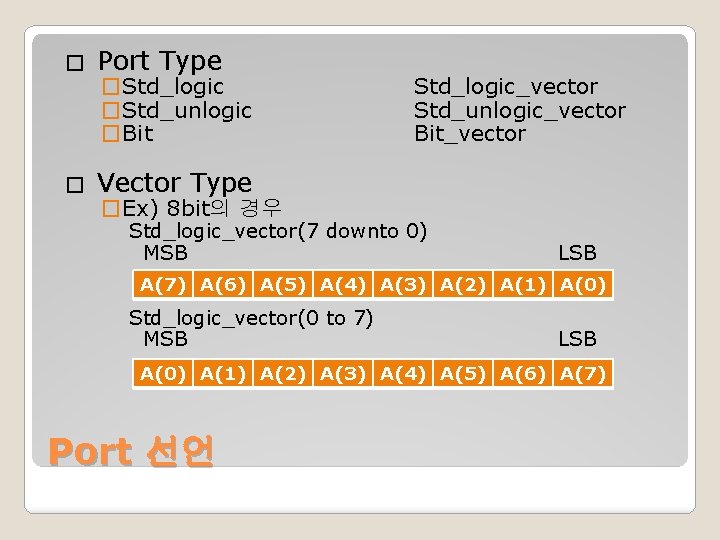

� Port Type � Vector Type �Std_logic �Std_unlogic �Bit Std_logic_vector Std_unlogic_vector Bit_vector �Ex) 8 bit의 경우 Std_logic_vector(7 downto 0) MSB LSB A(7) A(6) A(5) A(4) A(3) A(2) A(1) A(0) Std_logic_vector(0 to 7) MSB LSB A(0) A(1) A(2) A(3) A(4) A(5) A(6) A(7) Port 선언

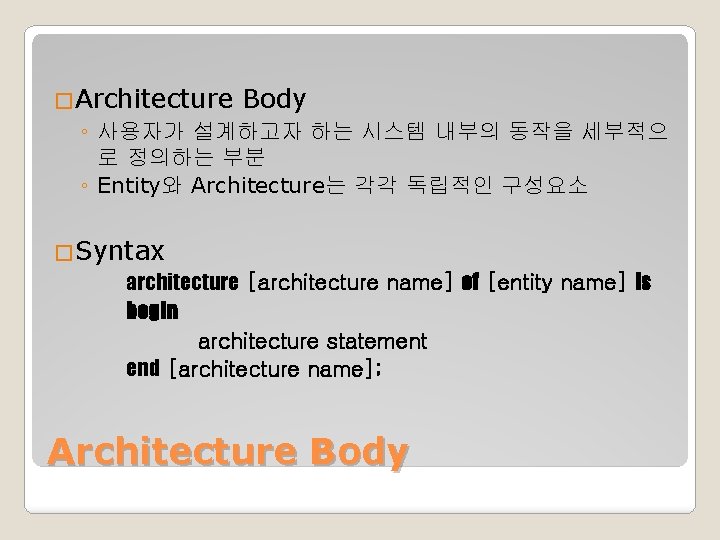

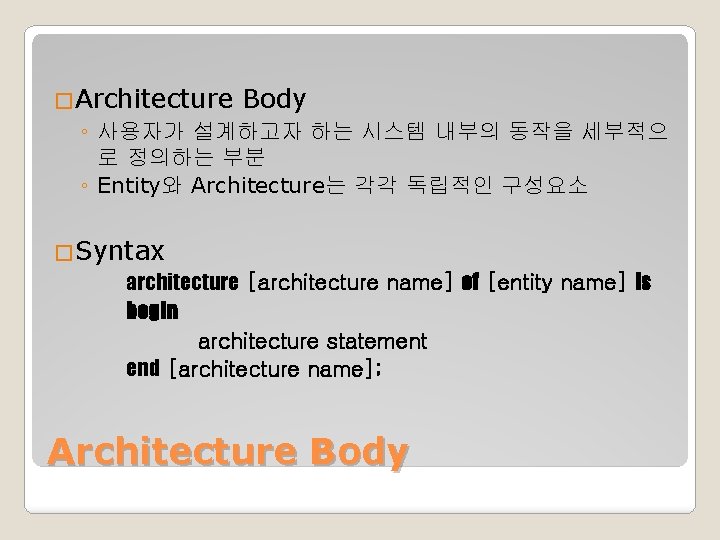

�Architecture Body ◦ 사용자가 설계하고자 하는 시스템 내부의 동작을 세부적으 로 정의하는 부분 ◦ Entity와 Architecture는 각각 독립적인 구성요소 �Syntax architecture [architecture name] of [entity name] is begin architecture statement end [architecture name]; Architecture Body

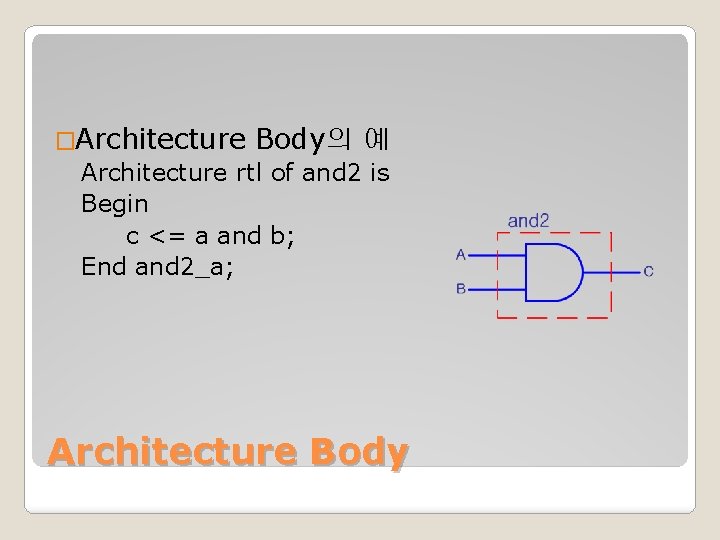

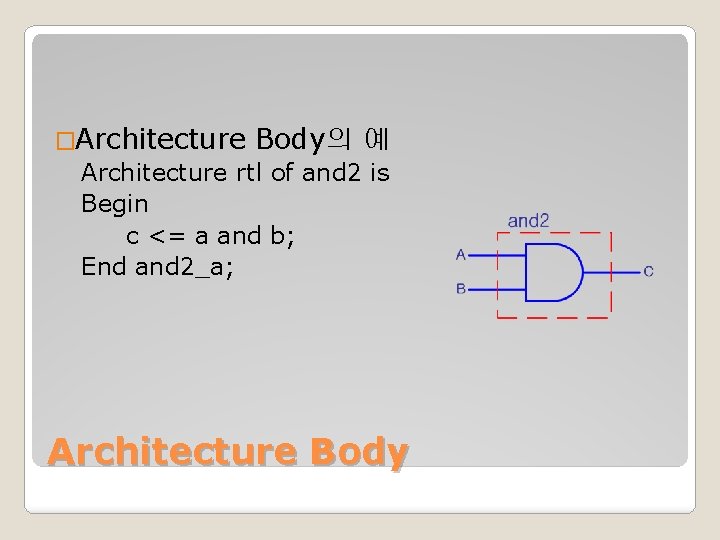

�Architecture Body의 예 Architecture rtl of and 2 is Begin c <= a and b; End and 2_a; Architecture Body

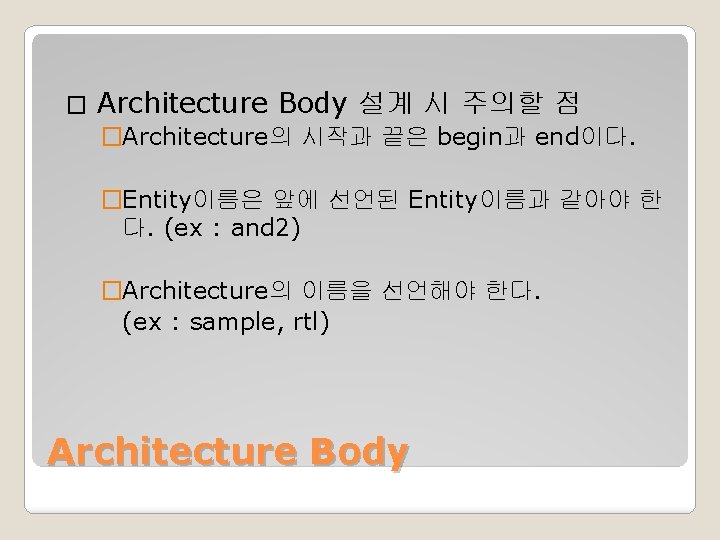

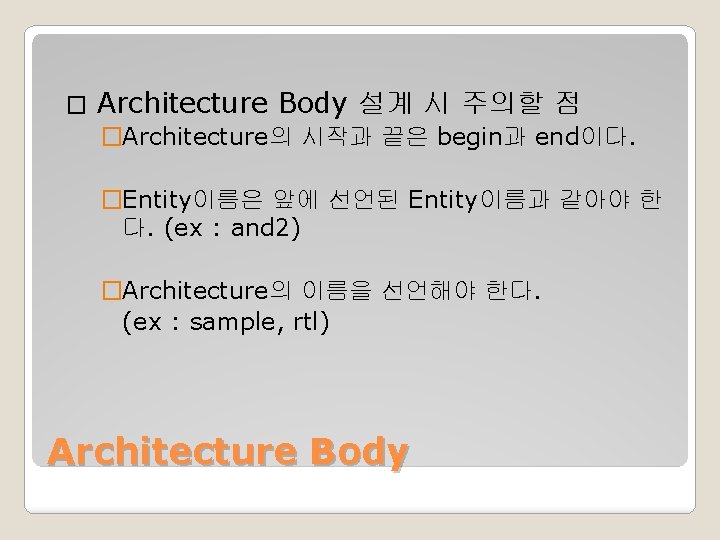

� Architecture Body 설계 시 주의할 점 �Architecture의 시작과 끝은 begin과 end이다. �Entity이름은 앞에 선언된 Entity이름과 같아야 한 다. (ex : and 2) �Architecture의 이름을 선언해야 한다. (ex : sample, rtl) Architecture Body

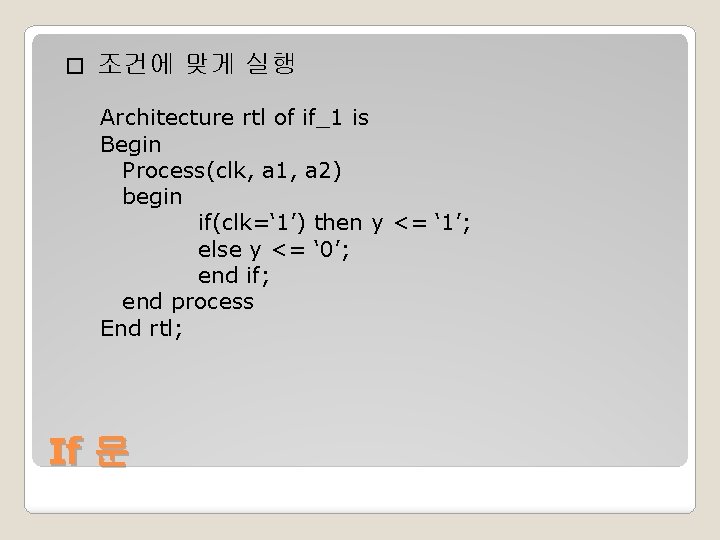

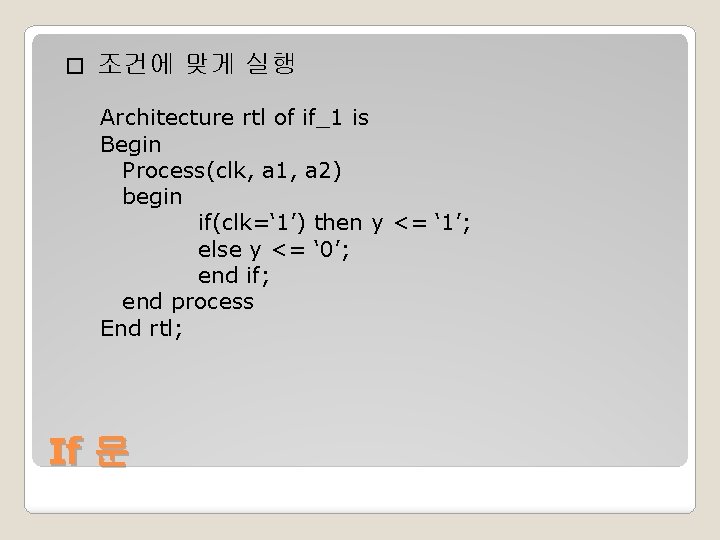

� 조건에 맞게 실행 Architecture rtl of if_1 is Begin Process(clk, a 1, a 2) begin if(clk=‘ 1’) then y <= ‘ 1’; else y <= ‘ 0’; end if; end process End rtl; If 문

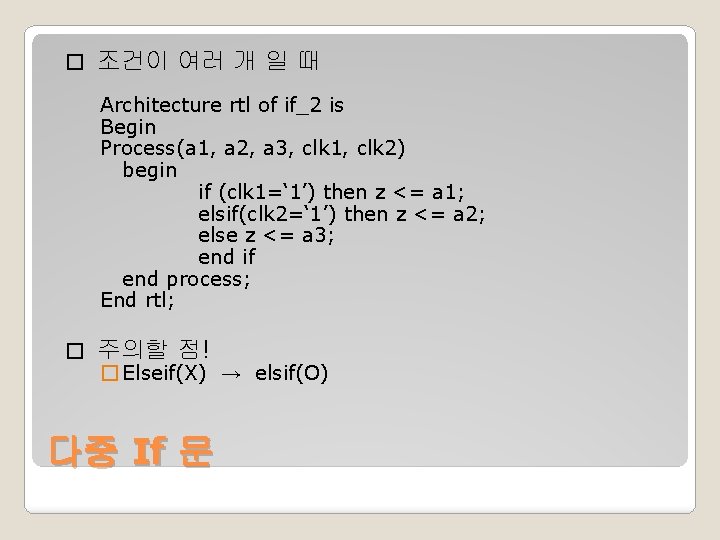

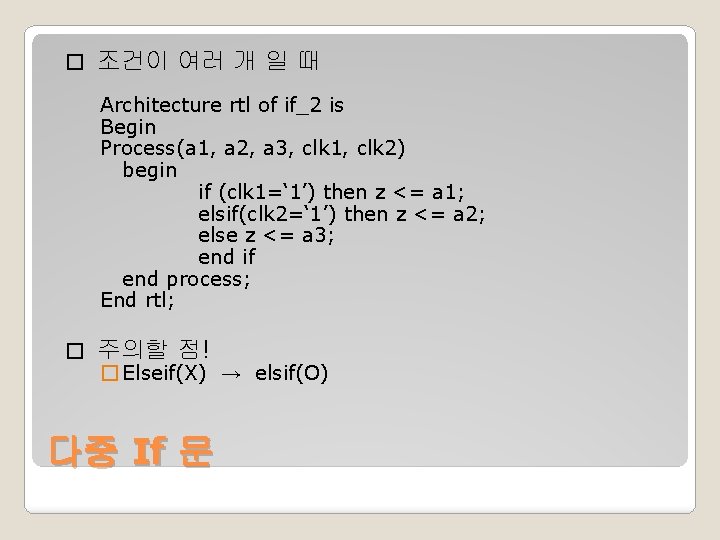

� 조건이 여러 개 일 때 Architecture rtl of if_2 is Begin Process(a 1, a 2, a 3, clk 1, clk 2) begin if (clk 1=‘ 1’) then z <= a 1; elsif(clk 2=‘ 1’) then z <= a 2; else z <= a 3; end if end process; End rtl; � 주의할 점! � Elseif(X) → elsif(O) 다중 If 문

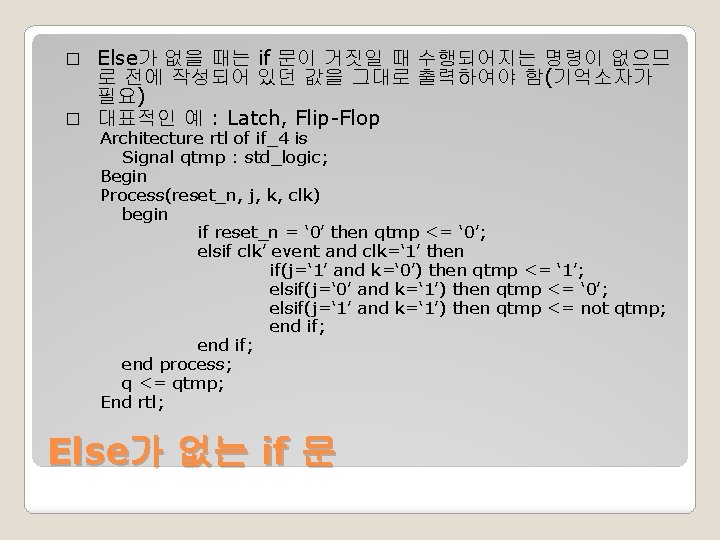

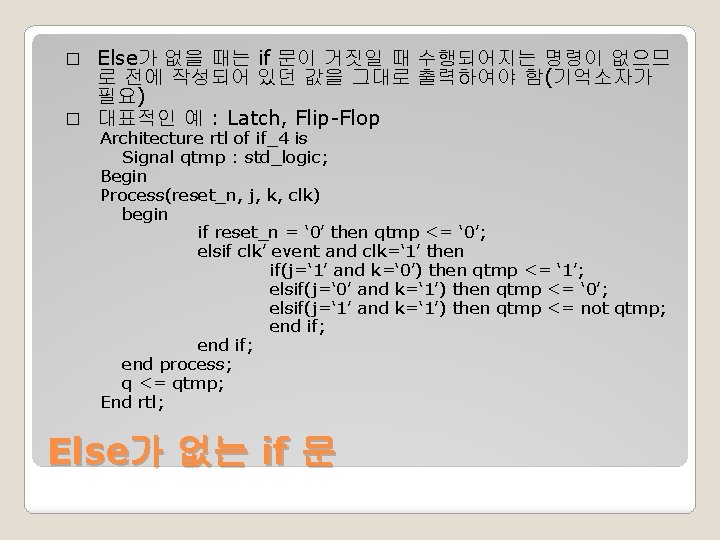

Else가 없을 때는 if 문이 거짓일 때 수행되어지는 명령이 없으므 로 전에 작성되어 있던 값을 그대로 출력하여야 함(기억소자가 필요) � 대표적인 예 : Latch, Flip-Flop � Architecture rtl of if_4 is Signal qtmp : std_logic; Begin Process(reset_n, j, k, clk) begin if reset_n = ‘ 0’ then qtmp <= ‘ 0’; elsif clk’ event and clk=‘ 1’ then if(j=‘ 1’ and k=‘ 0’) then qtmp <= ‘ 1’; elsif(j=‘ 0’ and k=‘ 1’) then qtmp <= ‘ 0’; elsif(j=‘ 1’ and k=‘ 1’) then qtmp <= not qtmp; end if; end process; q <= qtmp; End rtl; Else가 없는 if 문

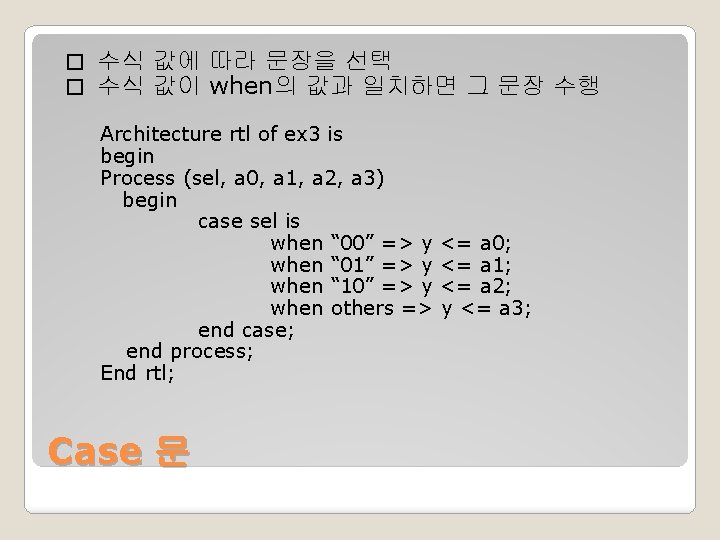

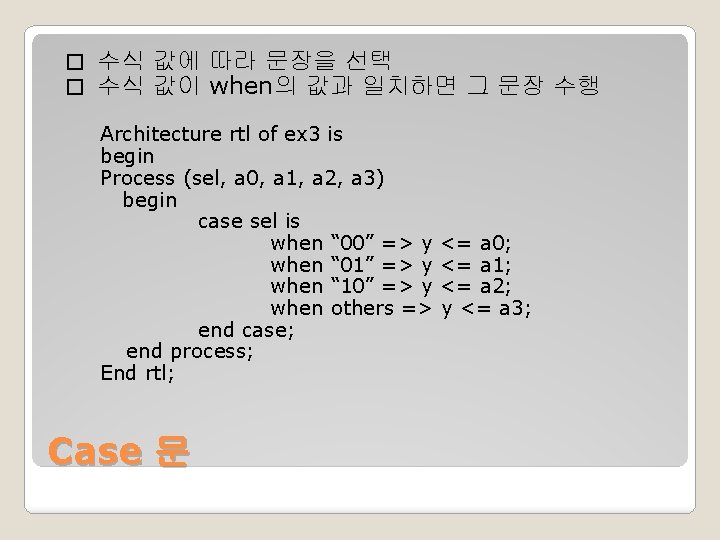

� � 수식 값에 따라 문장을 선택 수식 값이 when의 값과 일치하면 그 문장 수행 Architecture rtl of ex 3 is begin Process (sel, a 0, a 1, a 2, a 3) begin case sel is when “ 00” => y when “ 01” => y when “ 10” => y when others => end case; end process; End rtl; Case 문 <= a 0; <= a 1; <= a 2; y <= a 3;