VHDL Project I Serial Adder Slides Available at

VHDL Project I: Serial Adder Slides Available at: www. pages. drexel. edu/~mjm 46 Matthew Murach

Serial Adder Description Adds up values given over a length of time and computes the sum given. n This device is comprised of 4 components namely the adder itself, two shift registers for A and B, and a controller. n You have designed the adder component as previously given in the tutorial. n

Shift Register Description A shift register takes a std_logic_vector and outputs the bits serially each clock cycle. n Both A and B operand values should have an associated shift register. n Note that the contents of the shift register will be slowly feed to the adder one bit at a time. This is necessary since our adder can only take one bit at a time. n

Controller Description The controller component of the design simply acts as a logic diagram controlling which state the machine is in. n In the serial adder case there are three states n Idle – Machine is waiting n Loading – Machine is loading the shift registers n Shifting – The machine is dumping information from the shifters to the adder component n

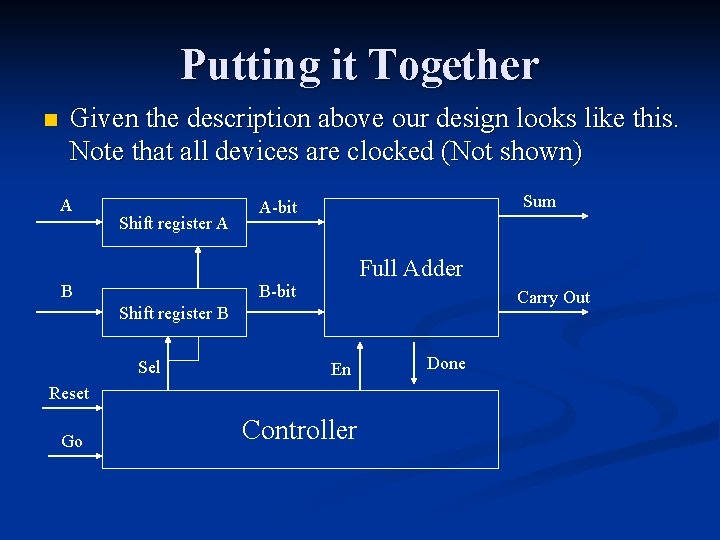

Putting it Together n Given the description above our design looks like this. Note that all devices are clocked (Not shown) A Shift register A B Sum A-bit Full Adder B-bit Carry Out Shift register B Sel En Reset Go Controller Done

Putting it all Together Previous wiring diagram is difficult to simulate since there are so many components and internal signals. n Notice that there are only 6 ports that connect with outside devices. n Wouldn’t it be nice if we could package these components into a single black box for testing…. . n

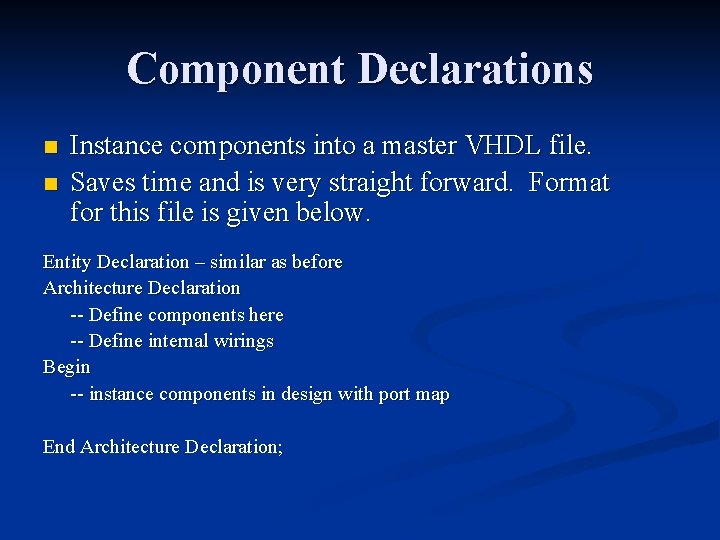

Component Declarations n n Instance components into a master VHDL file. Saves time and is very straight forward. Format for this file is given below. Entity Declaration – similar as before Architecture Declaration -- Define components here -- Define internal wirings Begin -- instance components in design with port map End Architecture Declaration;

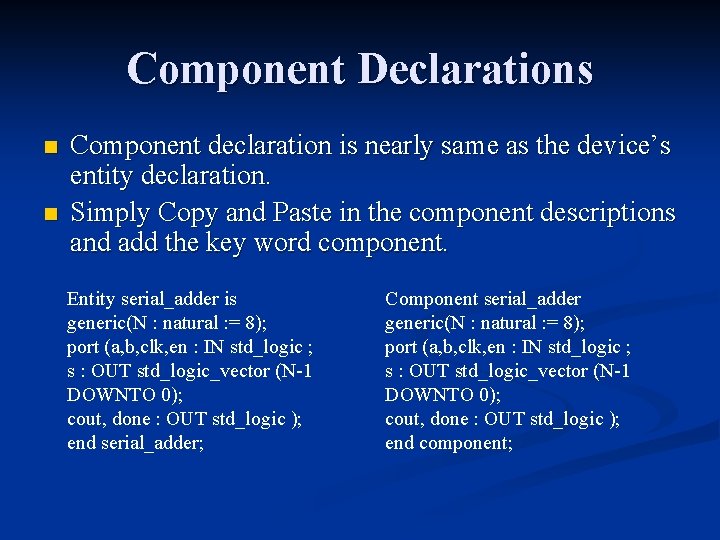

Component Declarations n n Component declaration is nearly same as the device’s entity declaration. Simply Copy and Paste in the component descriptions and add the key word component. Entity serial_adder is generic(N : natural : = 8); port (a, b, clk, en : IN std_logic ; s : OUT std_logic_vector (N-1 DOWNTO 0); cout, done : OUT std_logic ); end serial_adder; Component serial_adder generic(N : natural : = 8); port (a, b, clk, en : IN std_logic ; s : OUT std_logic_vector (N-1 DOWNTO 0); cout, done : OUT std_logic ); end component;

Internal Signals and Port Mappings Internal wiring is done with signals. Simply declare these signals like you have done in previous exercises. n Port mapping is the where the actual components are instantiated and mapped to their respective signals. n Note that you can instantiate more then one instance of each component. n

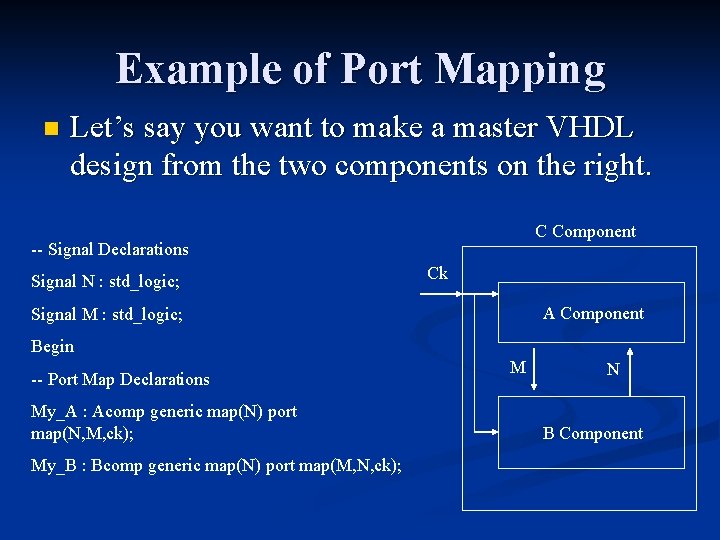

Example of Port Mapping n Let’s say you want to make a master VHDL design from the two components on the right. C Component -- Signal Declarations Signal N : std_logic; Ck A Component Signal M : std_logic; Begin -- Port Map Declarations My_A : Acomp generic map(N) port map(N, M, ck); My_B : Bcomp generic map(N) port map(M, N, ck); M N B Component

- Slides: 10