Comprehensive VHDL Module 6 Types November 2000 Types

Comprehensive VHDL Module 6 Types November 2000

Types Aim © To understand the use and synthesis of enumeration types, STD_LOGIC and STD_LOGIC_VECTOR Topics covered © Enumeration types © Type STD_LOGIC and bus resolution © Initial values © Slices and concatenation © Overloading and conversion © Standard packages 6 -2 • Comprehensive VHDL: Types Copyright © 2000 Doulos

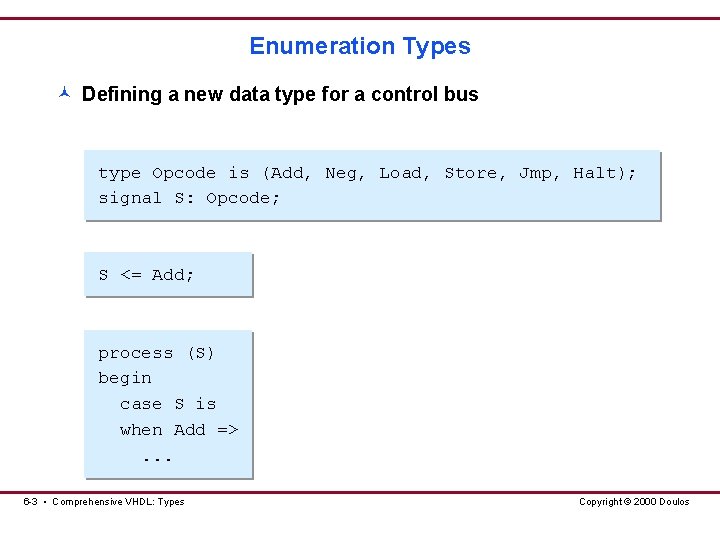

Enumeration Types © Defining a new data type for a control bus type Opcode is (Add, Neg, Load, Store, Jmp, Halt); signal S: Opcode; S <= Add; process (S) begin case S is when Add =>. . . 6 -3 • Comprehensive VHDL: Types Copyright © 2000 Doulos

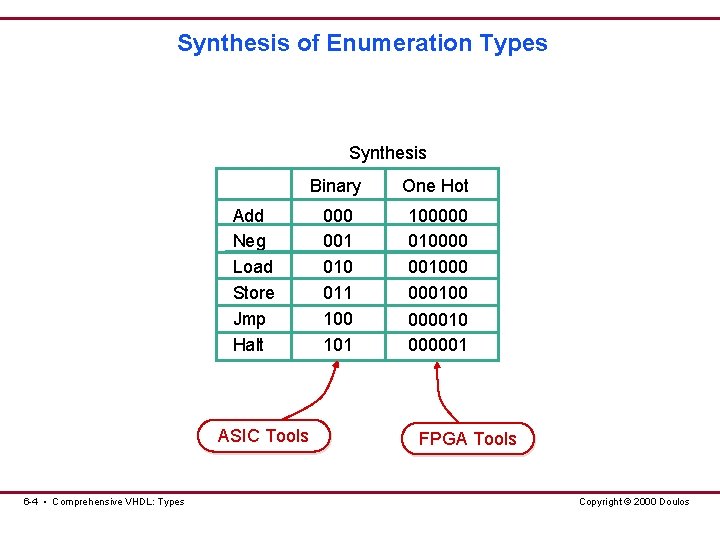

Synthesis of Enumeration Types Synthesis Add Neg Load Store Jmp Halt ASIC Tools 6 -4 • Comprehensive VHDL: Types Binary One Hot 000 001 010 011 100 101 100000 010000 001000 000100 000010 000001 FPGA Tools Copyright © 2000 Doulos

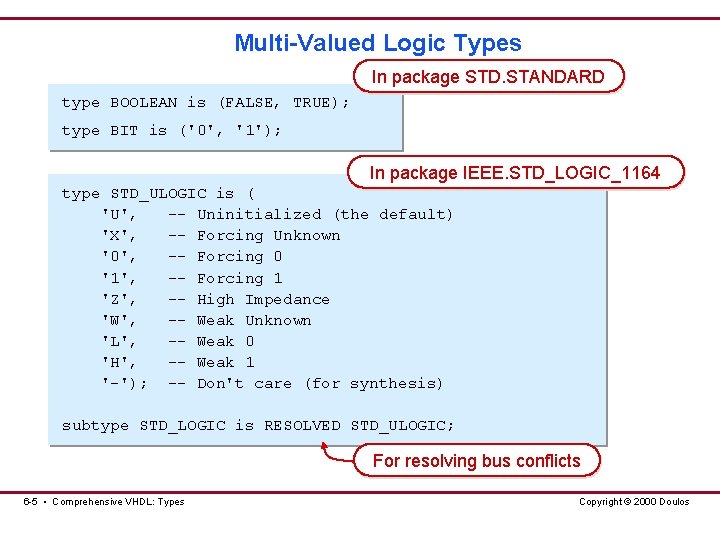

Multi-Valued Logic Types In package STD. STANDARD type BOOLEAN is (FALSE, TRUE); type BIT is ('0', '1'); In package IEEE. STD_LOGIC_1164 type STD_ULOGIC is ( 'U', -- Uninitialized (the default) 'X', -- Forcing Unknown '0', -- Forcing 0 '1', -- Forcing 1 'Z', -- High Impedance 'W', -- Weak Unknown 'L', -- Weak 0 'H', -- Weak 1 '-'); -- Don't care (for synthesis) subtype STD_LOGIC is RESOLVED STD_ULOGIC; For resolving bus conflicts 6 -5 • Comprehensive VHDL: Types Copyright © 2000 Doulos

Logical Operators Logical operators Defined on types and BOOLEAN nand BIT or BIT_VECTOR nor STD_LOGIC xor STD_LOGIC_VECTOR not xnor VHDL 93 6 -6 • Comprehensive VHDL: Types Copyright © 2000 Doulos

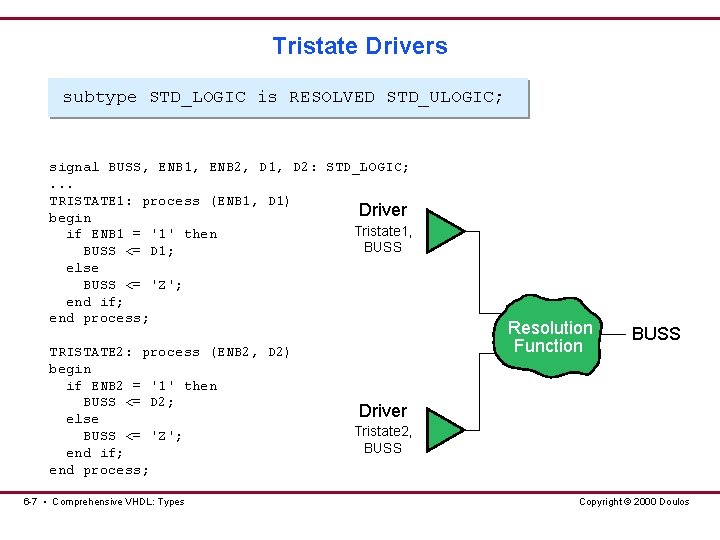

Tristate Drivers subtype STD_LOGIC is RESOLVED STD_ULOGIC; signal BUSS, ENB 1, ENB 2, D 1, D 2: STD_LOGIC; . . . TRISTATE 1: process (ENB 1, D 1) Driver begin Tristate 1, if ENB 1 = '1' then BUSS <= D 1; else BUSS <= 'Z'; end if; end process; TRISTATE 2: process (ENB 2, D 2) begin if ENB 2 = '1' then BUSS <= D 2; else BUSS <= 'Z'; end if; end process; 6 -7 • Comprehensive VHDL: Types Resolution Function BUSS Driver Tristate 2, BUSS Copyright © 2000 Doulos

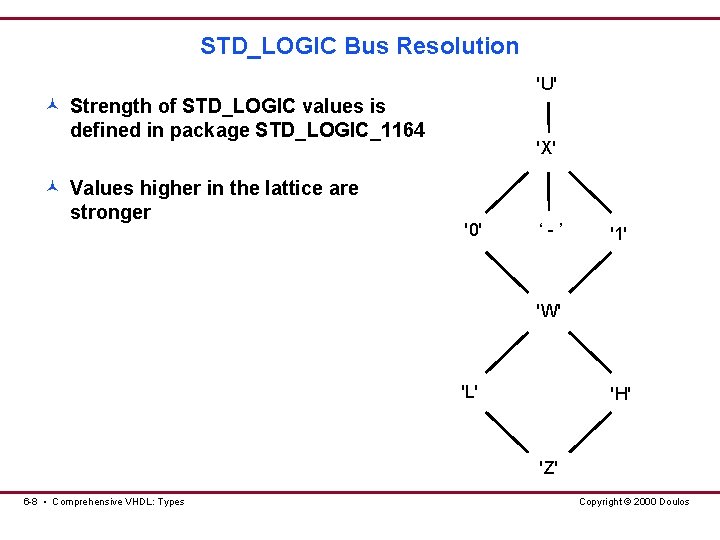

STD_LOGIC Bus Resolution 'U' © Strength of STD_LOGIC values is defined in package STD_LOGIC_1164 © Values higher in the lattice are stronger 'X' '0' ‘-’ '1' 'W' 'L' 'H' 'Z' 6 -8 • Comprehensive VHDL: Types Copyright © 2000 Doulos

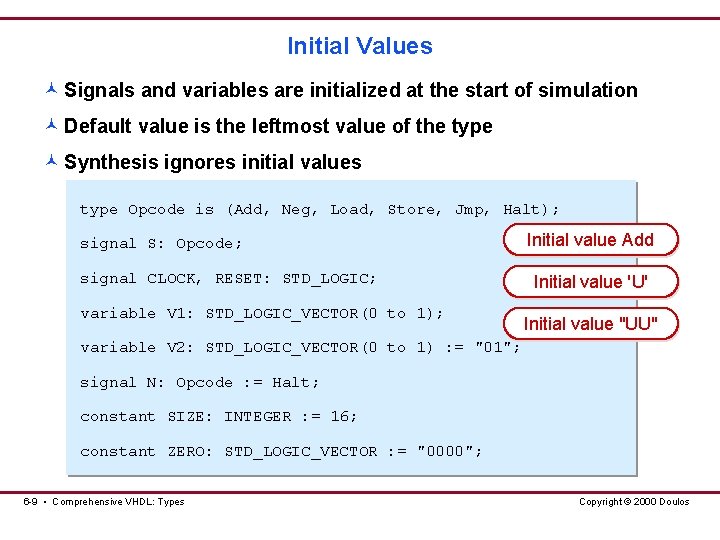

Initial Values © Signals and variables are initialized at the start of simulation © Default value is the leftmost value of the type © Synthesis ignores initial values type Opcode is (Add, Neg, Load, Store, Jmp, Halt); signal S: Opcode; signal CLOCK, RESET: STD_LOGIC; variable V 1: STD_LOGIC_VECTOR(0 to 1); Initial value Add Initial value 'U' Initial value "UU" variable V 2: STD_LOGIC_VECTOR(0 to 1) : = "01"; signal N: Opcode : = Halt; constant SIZE: INTEGER : = 16; constant ZERO: STD_LOGIC_VECTOR : = "0000"; 6 -9 • Comprehensive VHDL: Types Copyright © 2000 Doulos

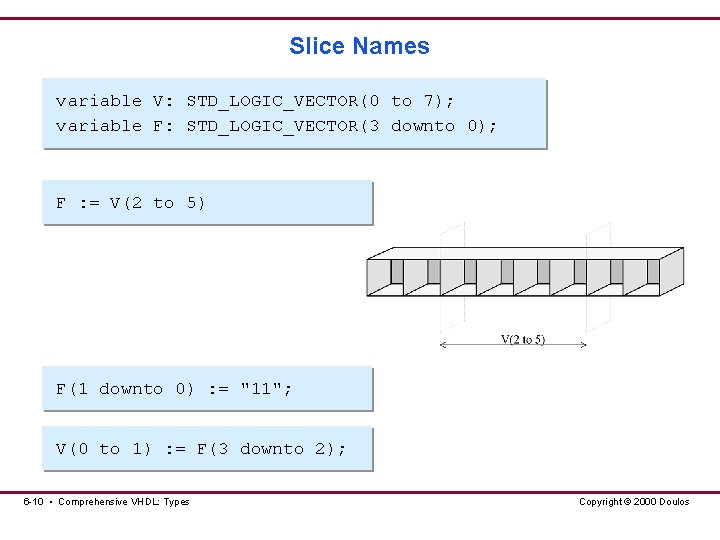

Slice Names variable V: STD_LOGIC_VECTOR(0 to 7); variable F: STD_LOGIC_VECTOR(3 downto 0); F : = V(2 to 5) F(1 downto 0) : = "11"; V(0 to 1) : = F(3 downto 2); 6 -10 • Comprehensive VHDL: Types Copyright © 2000 Doulos

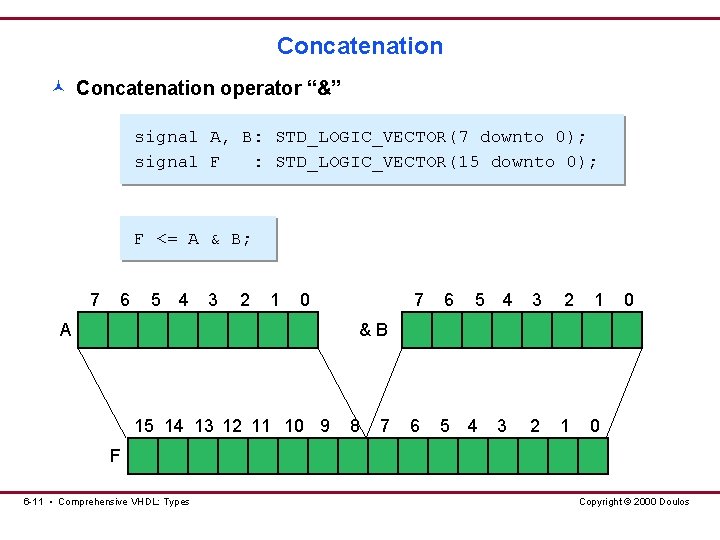

Concatenation © Concatenation operator “&” signal A, B: STD_LOGIC_VECTOR(7 downto 0); signal F : STD_LOGIC_VECTOR(15 downto 0); F <= A & B; 7 6 5 4 3 2 1 0 A 7 6 5 4 3 2 1 0 0 &B 15 14 13 12 11 10 9 8 7 3 F 6 -11 • Comprehensive VHDL: Types Copyright © 2000 Doulos

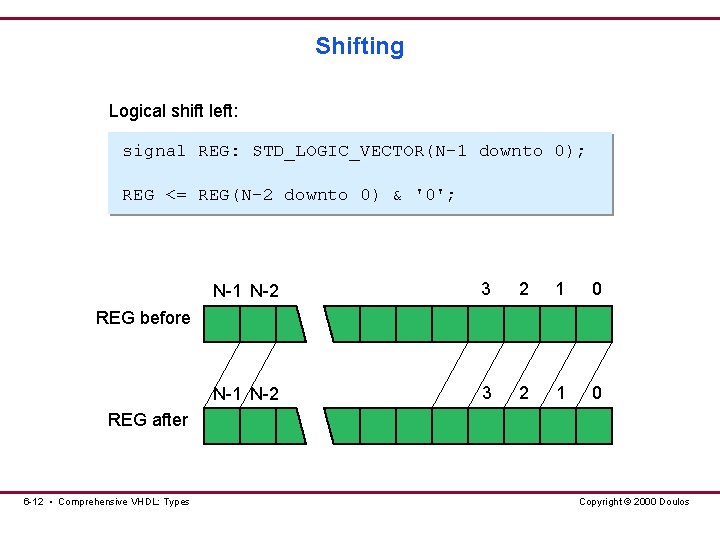

Shifting Logical shift left: signal REG: STD_LOGIC_VECTOR(N-1 downto 0); REG <= REG(N-2 downto 0) & '0'; N-1 N-2 3 2 1 0 REG before REG after 6 -12 • Comprehensive VHDL: Types 0 Copyright © 2000 Doulos

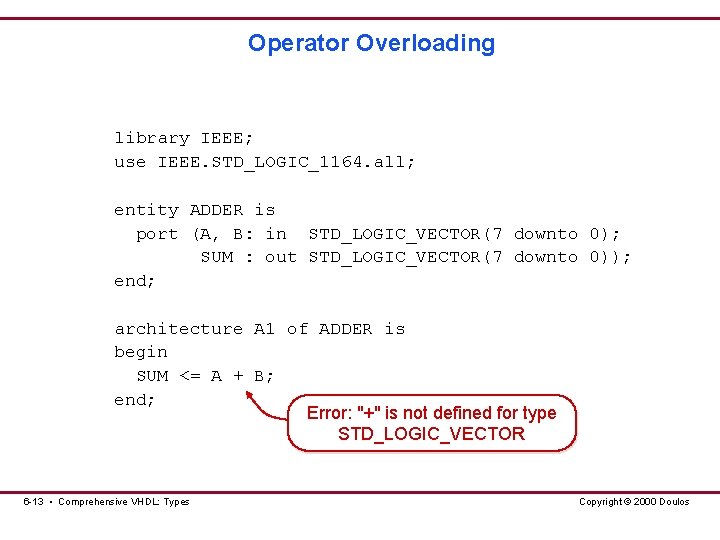

Operator Overloading library IEEE; use IEEE. STD_LOGIC_1164. all; entity ADDER is port (A, B: in STD_LOGIC_VECTOR(7 downto 0); SUM : out STD_LOGIC_VECTOR(7 downto 0)); end; architecture A 1 of ADDER is begin SUM <= A + B; end; Error: "+" is not defined for type STD_LOGIC_VECTOR 6 -13 • Comprehensive VHDL: Types Copyright © 2000 Doulos

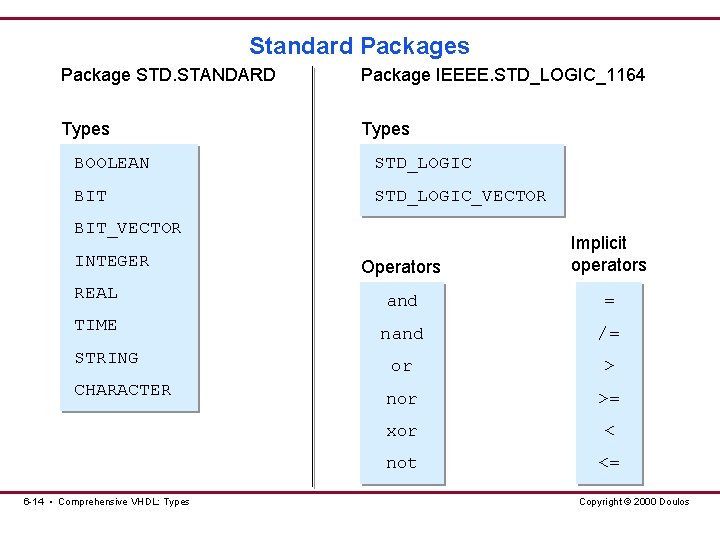

Standard Packages Package STD. STANDARD Package IEEEE. STD_LOGIC_1164 Types BOOLEAN STD_LOGIC BIT STD_LOGIC_VECTOR BIT_VECTOR Operators Implicit operators REAL and = TIME nand /= or > nor >= xor < not <= INTEGER STRING CHARACTER 6 -14 • Comprehensive VHDL: Types Copyright © 2000 Doulos

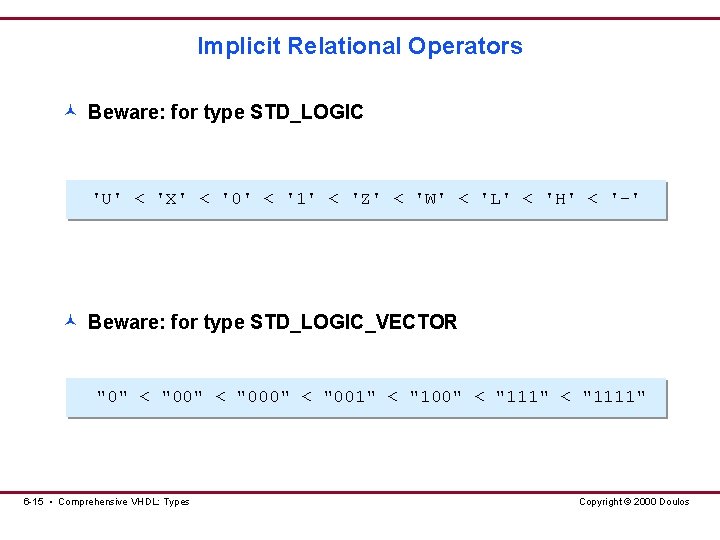

Implicit Relational Operators © Beware: for type STD_LOGIC 'U' < 'X' < '0' < '1' < 'Z' < 'W' < 'L' < 'H' < '-' © Beware: for type STD_LOGIC_VECTOR "0" < "000" < "001" < "100" < "1111" 6 -15 • Comprehensive VHDL: Types Copyright © 2000 Doulos

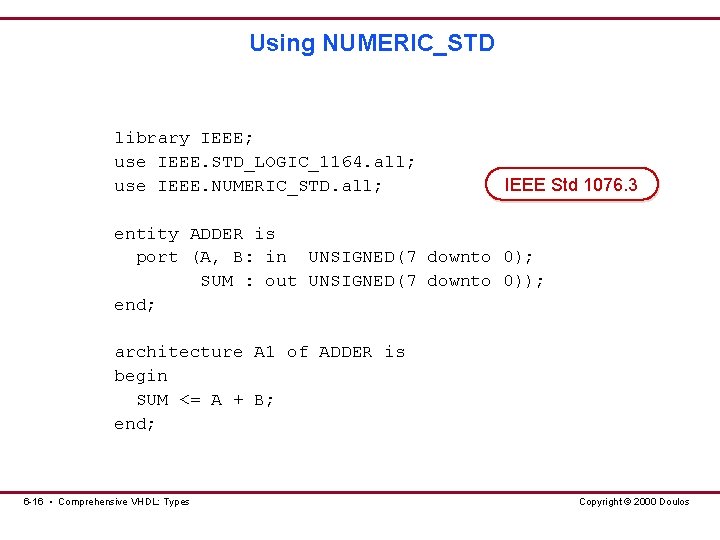

Using NUMERIC_STD library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; IEEE Std 1076. 3 entity ADDER is port (A, B: in UNSIGNED(7 downto 0); SUM : out UNSIGNED(7 downto 0)); end; architecture A 1 of ADDER is begin SUM <= A + B; end; 6 -16 • Comprehensive VHDL: Types Copyright © 2000 Doulos

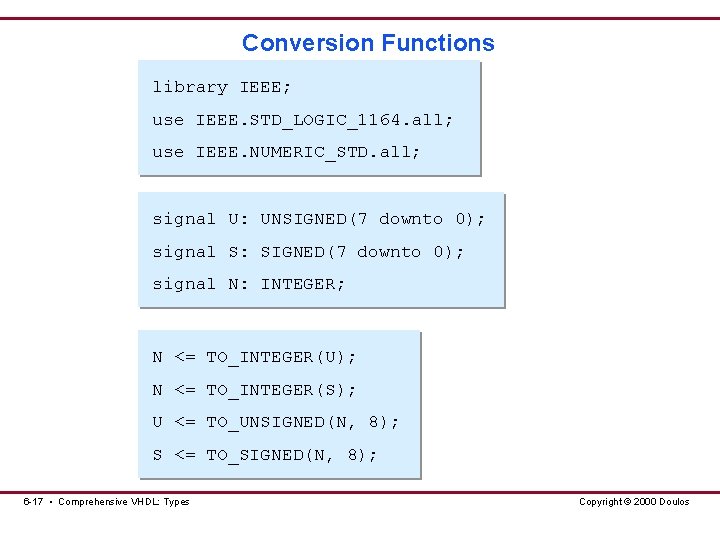

Conversion Functions library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; signal U: UNSIGNED(7 downto 0); signal S: SIGNED(7 downto 0); signal N: INTEGER; N <= TO_INTEGER(U); N <= TO_INTEGER(S); U <= TO_UNSIGNED(N, 8); S <= TO_SIGNED(N, 8); 6 -17 • Comprehensive VHDL: Types Copyright © 2000 Doulos

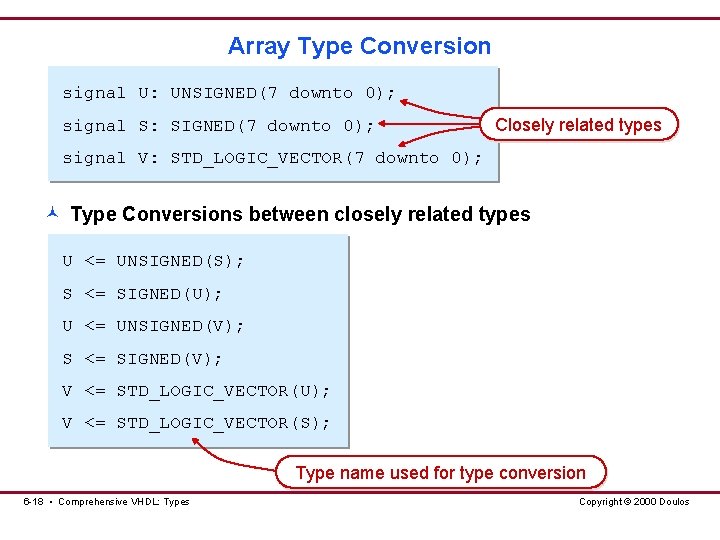

Array Type Conversion signal U: UNSIGNED(7 downto 0); signal S: SIGNED(7 downto 0); Closely related types signal V: STD_LOGIC_VECTOR(7 downto 0); © Type Conversions between closely related types U <= UNSIGNED(S); S <= SIGNED(U); U <= UNSIGNED(V); S <= SIGNED(V); V <= STD_LOGIC_VECTOR(U); V <= STD_LOGIC_VECTOR(S); Type name used for type conversion 6 -18 • Comprehensive VHDL: Types Copyright © 2000 Doulos

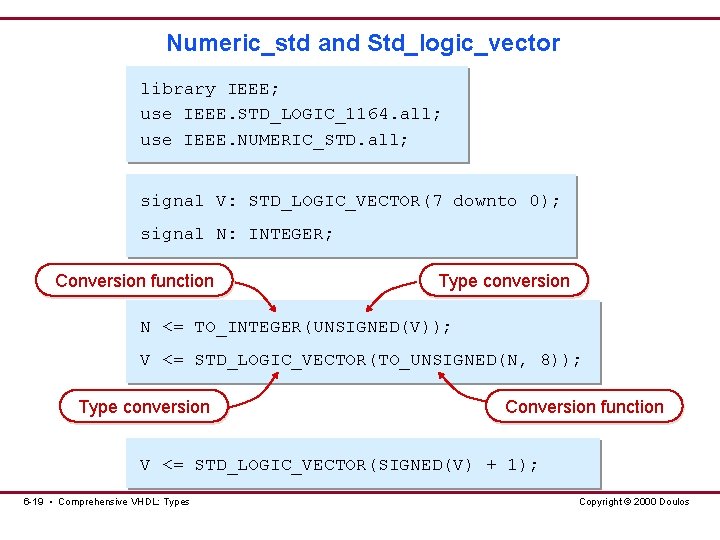

Numeric_std and Std_logic_vector library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; signal V: STD_LOGIC_VECTOR(7 downto 0); signal N: INTEGER; Conversion function Type conversion N <= TO_INTEGER(UNSIGNED(V)); V <= STD_LOGIC_VECTOR(TO_UNSIGNED(N, 8)); Type conversion Conversion function V <= STD_LOGIC_VECTOR(SIGNED(V) + 1); 6 -19 • Comprehensive VHDL: Types Copyright © 2000 Doulos

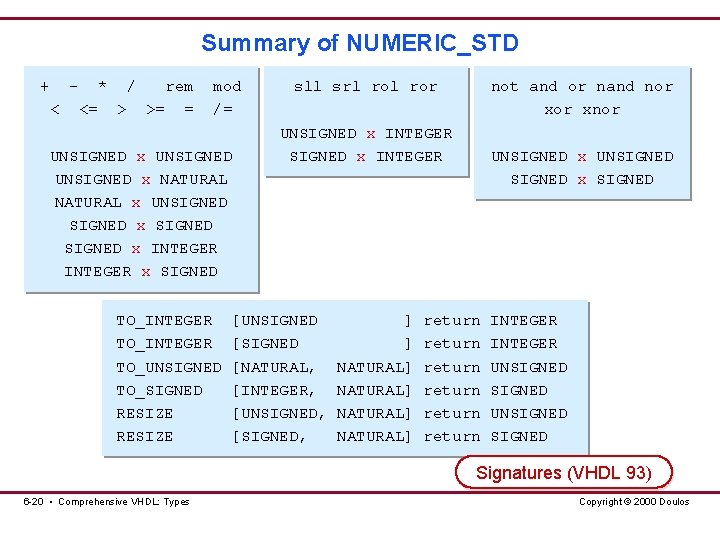

Summary of NUMERIC_STD + < * / rem <= > >= = mod /= UNSIGNED x NATURAL x UNSIGNED x INTEGER x SIGNED TO_INTEGER TO_UNSIGNED TO_SIGNED RESIZE sll srl ror not and or nand nor xnor UNSIGNED x INTEGER [UNSIGNED [NATURAL, [INTEGER, [UNSIGNED, [SIGNED, ] ] NATURAL] UNSIGNED x SIGNED return return INTEGER UNSIGNED Signatures (VHDL 93) 6 -20 • Comprehensive VHDL: Types Copyright © 2000 Doulos

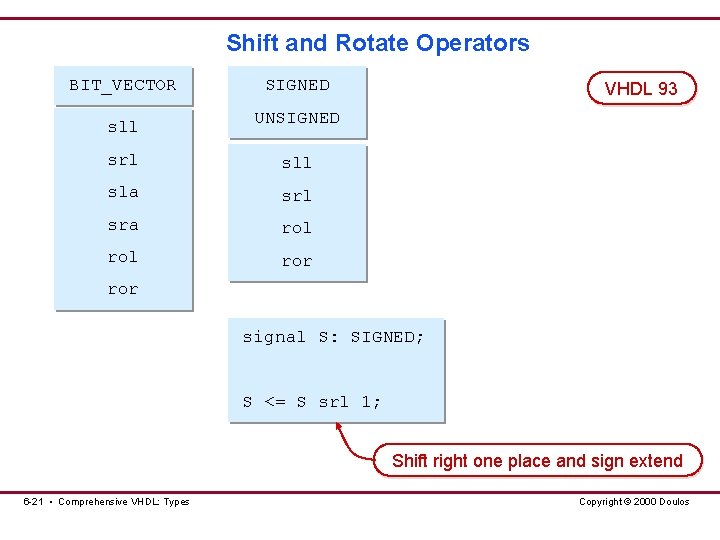

Shift and Rotate Operators BIT_VECTOR sll SIGNED VHDL 93 UNSIGNED srl sla srl sra rol ror signal S: SIGNED; S <= S srl 1; Shift right one place and sign extend 6 -21 • Comprehensive VHDL: Types Copyright © 2000 Doulos

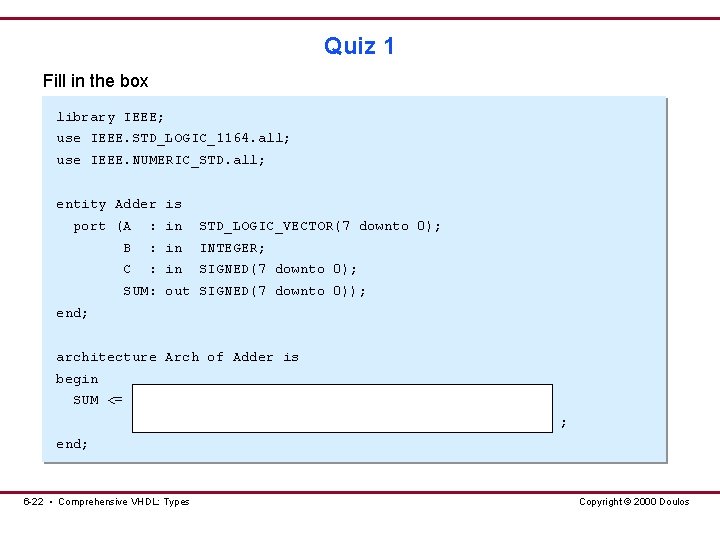

Quiz 1 Fill in the box library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; entity Adder is port (A : in STD_LOGIC_VECTOR(7 downto 0); B : in INTEGER; C : in SIGNED(7 downto 0); SUM: out SIGNED(7 downto 0)); end; architecture Arch of Adder is begin SUM <= ; end; 6 -22 • Comprehensive VHDL: Types Copyright © 2000 Doulos

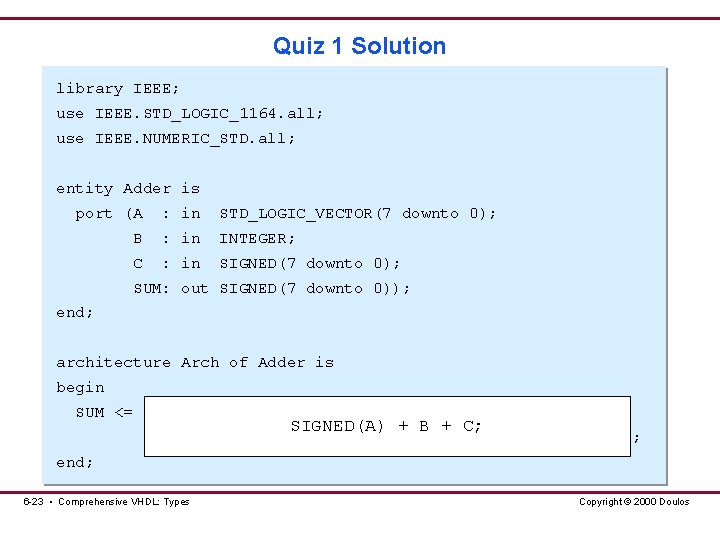

Quiz 1 Solution library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; entity Adder is port (A : in STD_LOGIC_VECTOR(7 downto 0); B : in INTEGER; C : in SIGNED(7 downto 0); SUM: out SIGNED(7 downto 0)); end; architecture Arch of Adder is begin SUM <= SIGNED(A) + B + C; ; end; 6 -23 • Comprehensive VHDL: Types Copyright © 2000 Doulos

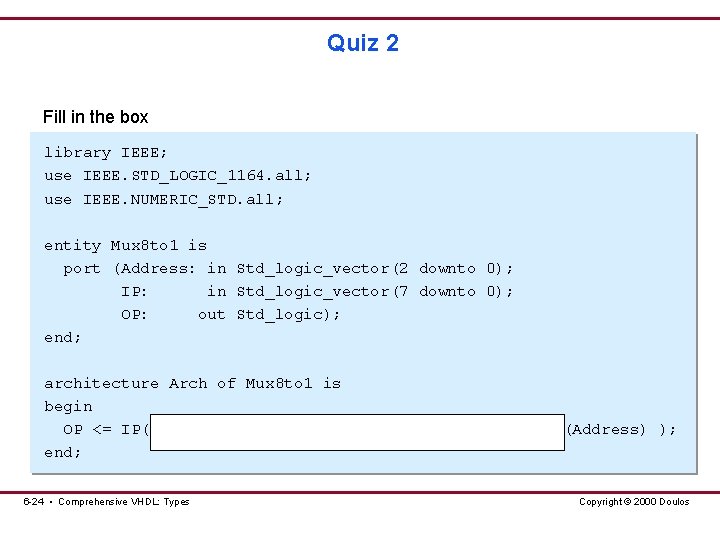

Quiz 2 Fill in the box library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; entity Mux 8 to 1 is port (Address: in Std_logic_vector(2 downto 0); IP: in Std_logic_vector(7 downto 0); OP: out Std_logic); end; architecture Arch of Mux 8 to 1 is begin OP <= IP( end; 6 -24 • Comprehensive VHDL: Types (Address) ); Copyright © 2000 Doulos

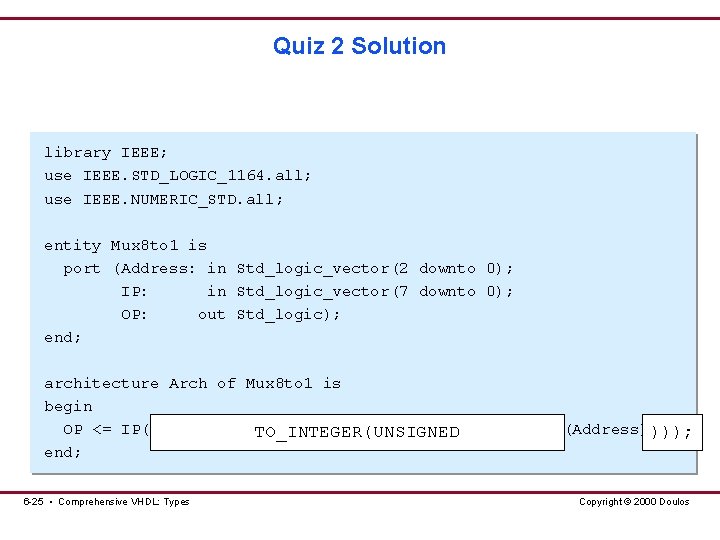

Quiz 2 Solution library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. NUMERIC_STD. all; entity Mux 8 to 1 is port (Address: in Std_logic_vector(2 downto 0); IP: in Std_logic_vector(7 downto 0); OP: out Std_logic); end; architecture Arch of Mux 8 to 1 is begin OP <= IP( TO_INTEGER(UNSIGNED end; 6 -25 • Comprehensive VHDL: Types (Address) ))); ); Copyright © 2000 Doulos

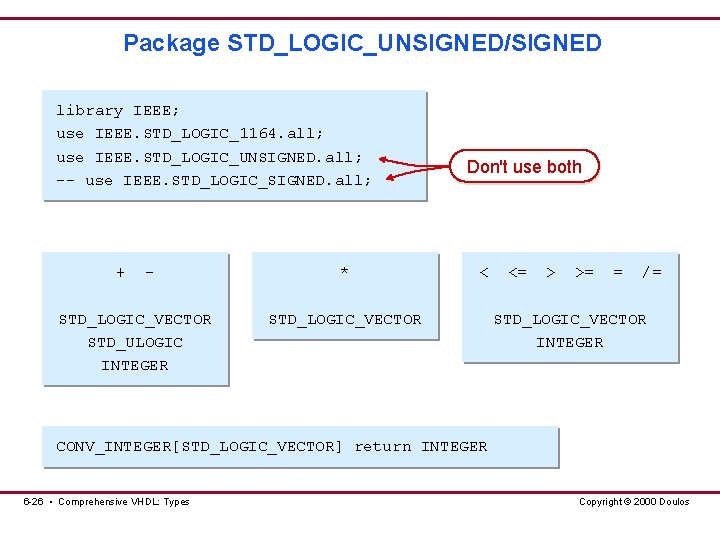

Package STD_LOGIC_UNSIGNED/SIGNED library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_UNSIGNED. all; -- use IEEE. STD_LOGIC_SIGNED. all; + - STD_LOGIC_VECTOR STD_ULOGIC INTEGER * Don't use both < STD_LOGIC_VECTOR <= > >= = /= STD_LOGIC_VECTOR INTEGER CONV_INTEGER[STD_LOGIC_VECTOR] return INTEGER 6 -26 • Comprehensive VHDL: Types Copyright © 2000 Doulos

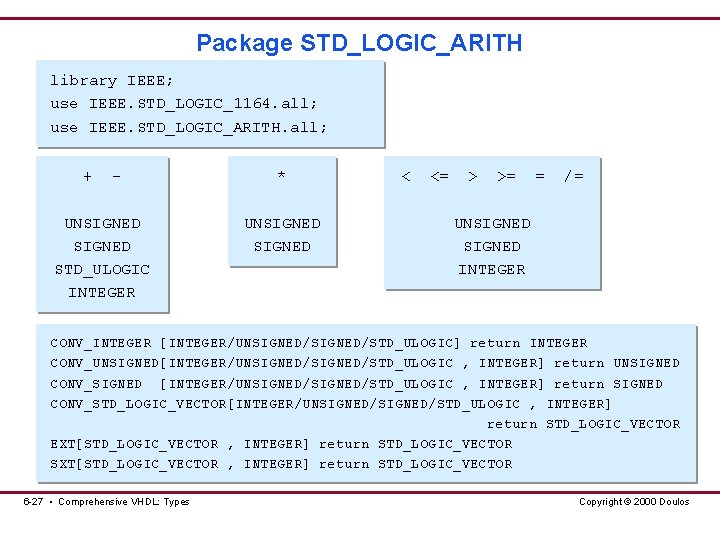

Package STD_LOGIC_ARITH library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_ARITH. all; + - UNSIGNED STD_ULOGIC INTEGER * UNSIGNED < <= > >= = /= UNSIGNED INTEGER CONV_INTEGER [INTEGER/UNSIGNED/STD_ULOGIC] return INTEGER CONV_UNSIGNED[INTEGER/UNSIGNED/STD_ULOGIC , INTEGER] return UNSIGNED CONV_SIGNED [INTEGER/UNSIGNED/STD_ULOGIC , INTEGER] return SIGNED CONV_STD_LOGIC_VECTOR[INTEGER/UNSIGNED/STD_ULOGIC , INTEGER] return STD_LOGIC_VECTOR EXT[STD_LOGIC_VECTOR , INTEGER] return STD_LOGIC_VECTOR SXT[STD_LOGIC_VECTOR , INTEGER] return STD_LOGIC_VECTOR 6 -27 • Comprehensive VHDL: Types Copyright © 2000 Doulos

- Slides: 27