VHDL Structural VHDL 1 Structural VHDL 12 Entity

- Slides: 13

VHDL σε επίπεδο δομής (Structural VHDL) 1

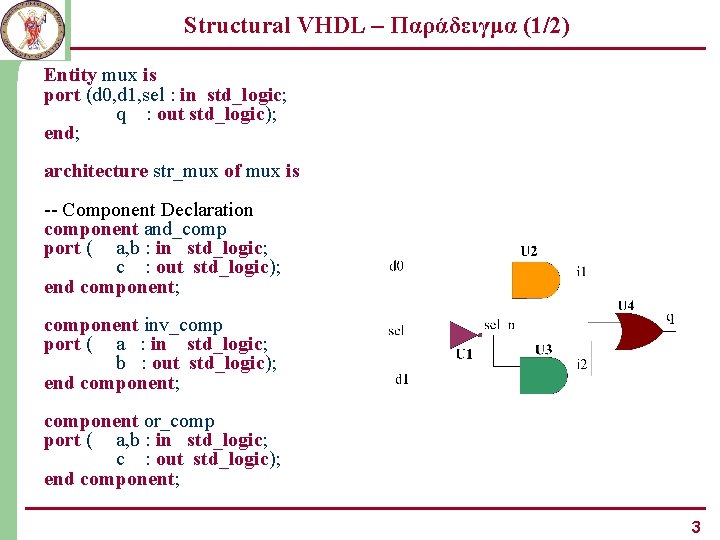

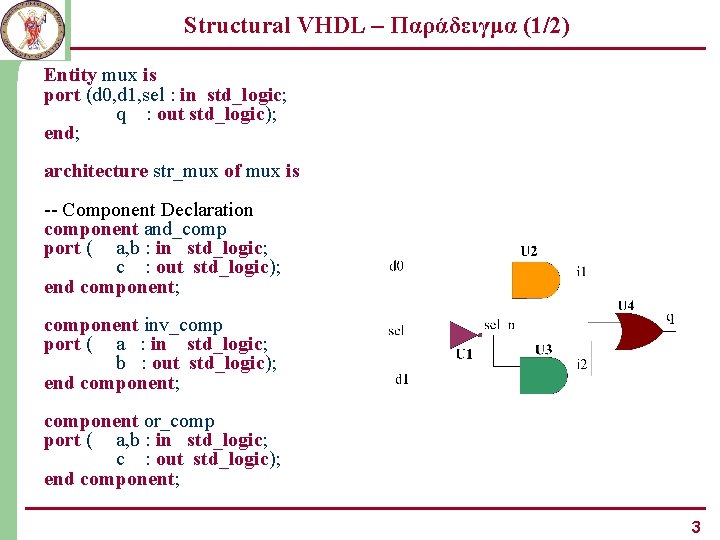

Structural VHDL – Παράδειγμα (1/2) Entity mux is port (d 0, d 1, sel : in std_logic; q : out std_logic); end; architecture str_mux of mux is -- Component Declaration component and_comp port ( a, b : in std_logic; c : out std_logic); end component; component inv_comp port ( a : in std_logic; b : out std_logic); end component; component or_comp port ( a, b : in std_logic; c : out std_logic); end component; 3

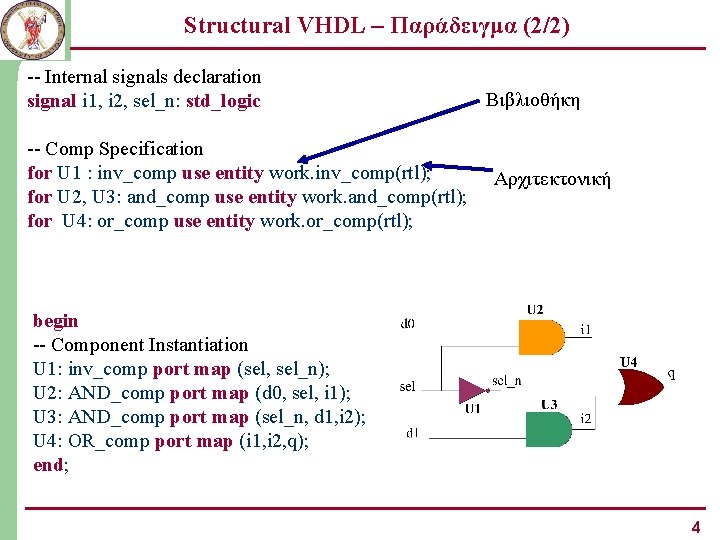

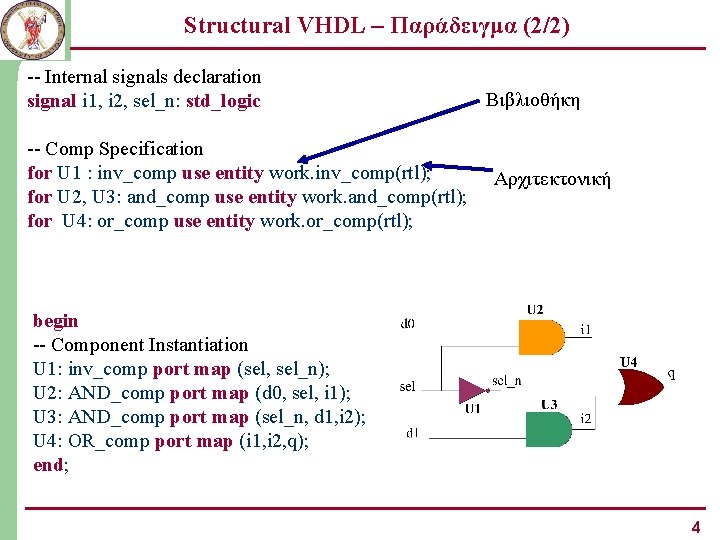

Structural VHDL – Παράδειγμα (2/2) -- Internal signals declaration signal i 1, i 2, sel_n: std_logic -- Comp Specification for U 1 : inv_comp use entity work. inv_comp(rtl); for U 2, U 3: and_comp use entity work. and_comp(rtl); for U 4: or_comp use entity work. or_comp(rtl); Βιβλιοθήκη Αρχιτεκτονική begin -- Component Instantiation U 1: inv_comp port map (sel, sel_n); U 2: AND_comp port map (d 0, sel, i 1); U 3: AND_comp port map (sel_n, d 1, i 2); U 4: OR_comp port map (i 1, i 2, q); end; 4

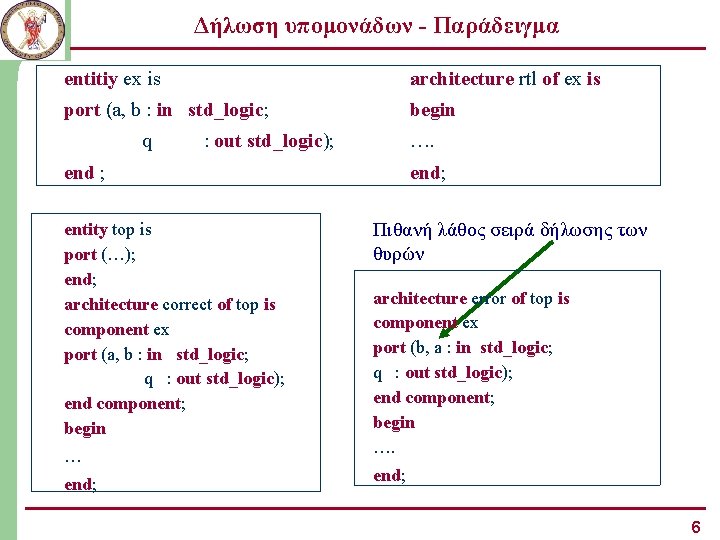

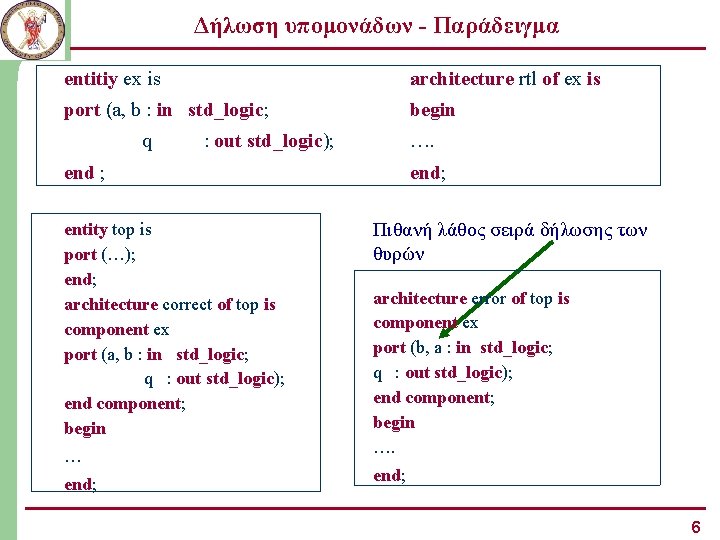

Δήλωση υπομονάδων - Παράδειγμα entitiy ex is architecture rtl of ex is port (a, b : in std_logic; begin q : out std_logic); …. end ; entity top is port (…); end; architecture correct of top is component ex port (a, b : in std_logic; q : out std_logic); end component; begin … end; Πιθανή λάθος σειρά δήλωσης των θυρών architecture error of top is component ex port (b, a : in std_logic; q : out std_logic); end component; begin …. end; 6

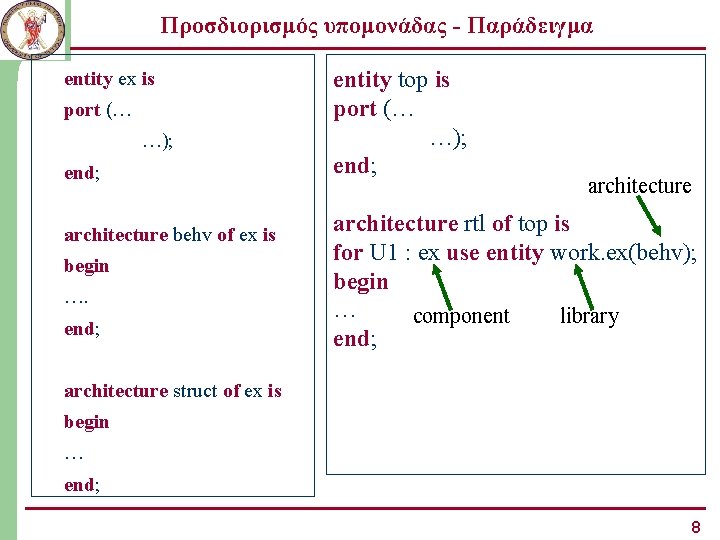

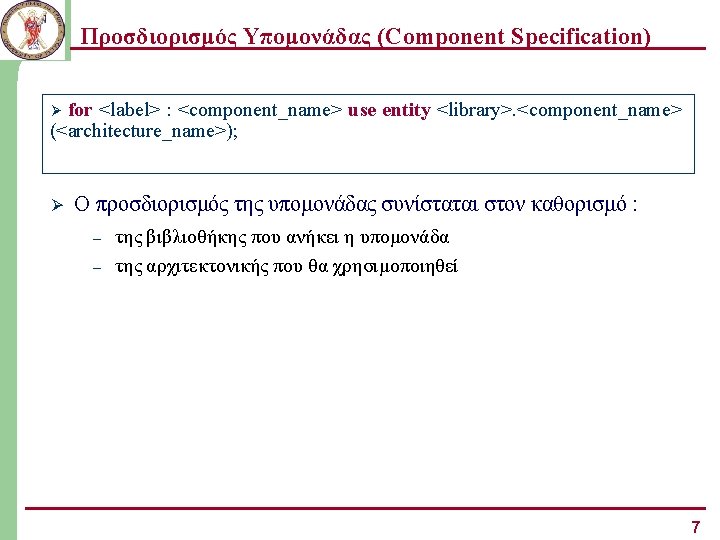

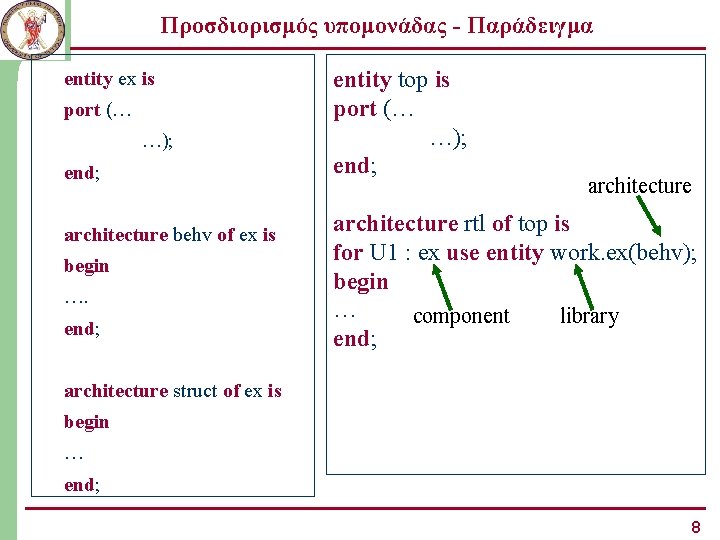

Προσδιορισμός υπομονάδας - Παράδειγμα entity ex is port (… …); end; architecture behv of ex is begin …. end; entity top is port (… …); end; architecture rtl of top is for U 1 : ex use entity work. ex(behv); begin … component library end; architecture struct of ex is begin … end; 8

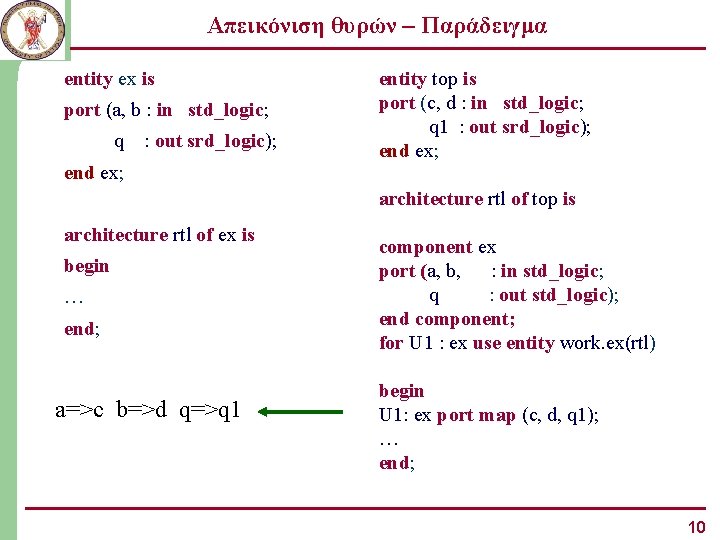

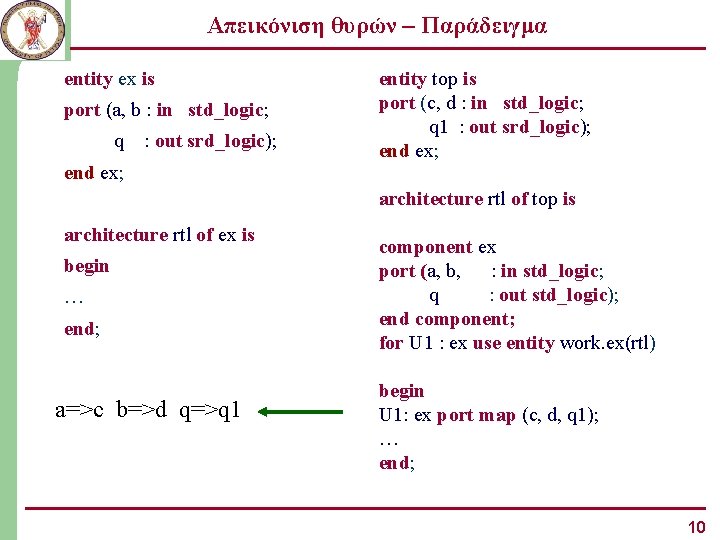

Απεικόνιση θυρών – Παράδειγμα entity ex is port (a, b : in std_logic; q : out srd_logic); end ex; entity top is port (c, d : in std_logic; q 1 : out srd_logic); end ex; architecture rtl of top is architecture rtl of ex is begin … end; a=>c b=>d q=>q 1 component ex port (a, b, : in std_logic; q : out std_logic); end component; for U 1 : ex use entity work. ex(rtl) begin U 1: ex port map (c, d, q 1); … end; 10

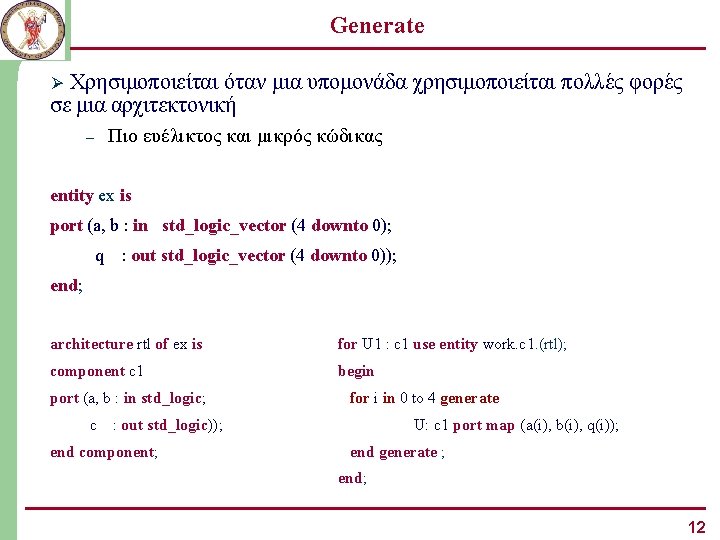

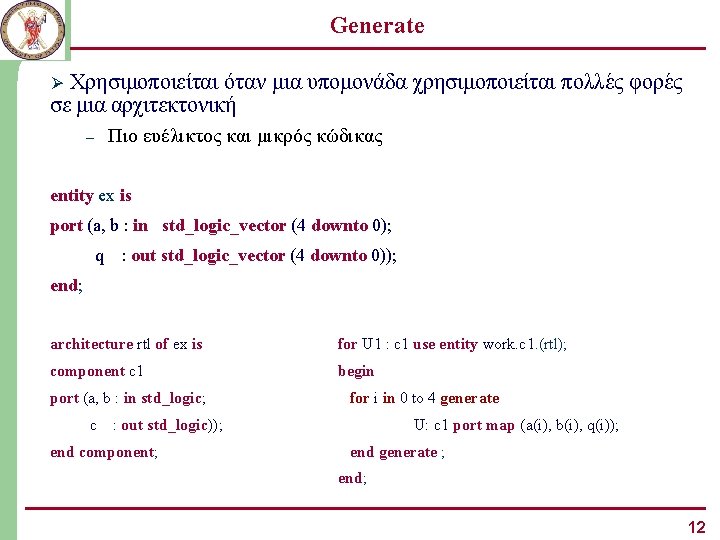

Generate Χρησιμοποιείται όταν μια υπομονάδα χρησιμοποιείται πολλές φορές σε μια αρχιτεκτονική Ø Πιο ευέλικτος και μικρός κώδικας – entity ex is port (a, b : in std_logic_vector (4 downto 0); q : out std_logic_vector (4 downto 0)); end; architecture rtl of ex is for U 1 : c 1 use entity work. c 1. (rtl); component c 1 begin port (a, b : in std_logic; c for i in 0 to 4 generate : out std_logic)); end component; U: c 1 port map (a(i), b(i), q(i)); end generate ; end; 12

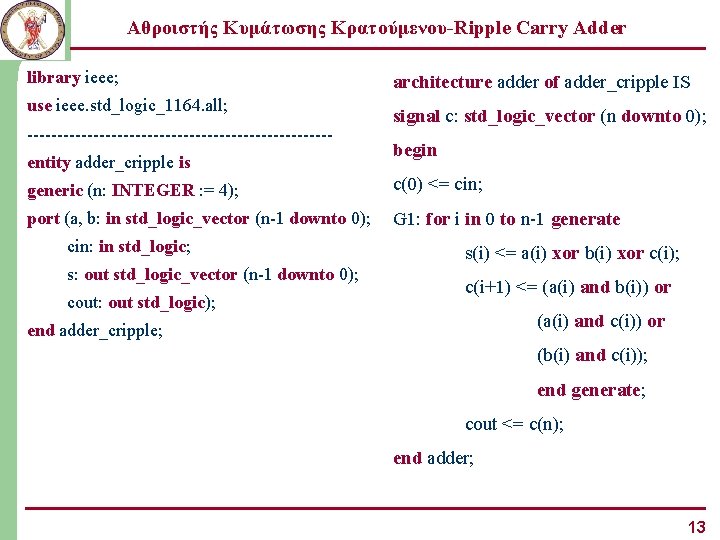

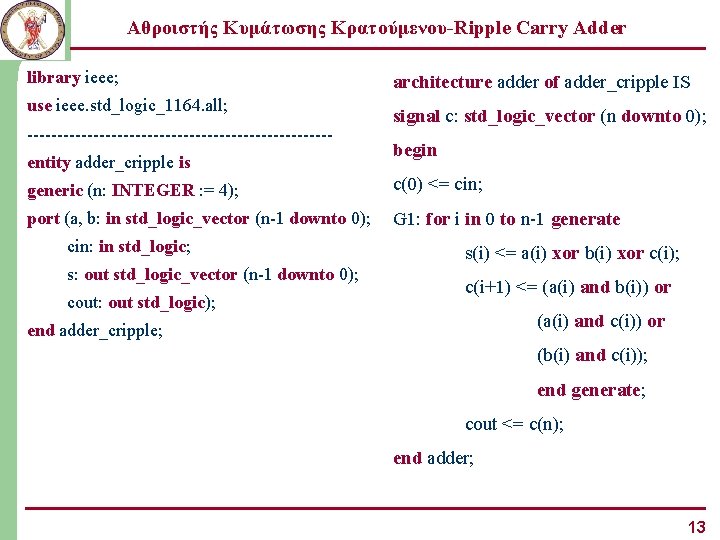

Αθροιστής Κυμάτωσης Κρατούμενου-Ripple Carry Adder library ieee; use ieee. std_logic_1164. all; -------------------------entity adder_cripple is architecture adder of adder_cripple IS signal c: std_logic_vector (n downto 0); begin generic (n: INTEGER : = 4); c(0) <= cin; port (a, b: in std_logic_vector (n-1 downto 0); G 1: for i in 0 to n-1 generate cin: in std_logic; s: out std_logic_vector (n-1 downto 0); cout: out std_logic); s(i) <= a(i) xor b(i) xor c(i); c(i+1) <= (a(i) and b(i)) or (a(i) and c(i)) or end adder_cripple; (b(i) and c(i)); end generate; cout <= c(n); end adder; 13