Uvod u VHDL Arhitektura mikrosistema VHDL o VHDL

- Slides: 32

Uvod u VHDL Arhitektura mikrosistema

VHDL o VHDL - standardni jezik za opis digitalnih kola i sistema. n n o VHDL standard usvojen 1987. god. (IEEE 1076). Revidiran i trenutno aktuelni VHDL standard, IEEE 1164, usvojen 1993. godine. Skraćenica od VHSIC Hardware Description Language. VHSIC skraćenica od Very High Speed Integrated Circuits” (Integrisana kola veoma velike brzine rada) Arhitektura mikrosistema

VHDL o Osnovna namena: n n o Savremena primena: n o Sinteza hardvera Naš cilj: n o Jezik za dokumentaciju Jezik za simulaciju Sinteza kombinacionih i sekvencijalnih kola i sistema niske i srednje složenosti u VHDL-u Obiman i složen jezik n Dobra vest: za sintezu, bitan je samo jedan manji deo mogućnosti VHDL jezika. Arhitektura mikrosistema

Programski jezik vs. jezik za opis hardvera o Programski jezik: n n n o Jezik za opis hardvera: n n n o Opis algoritma Sekvencijalni model izračunavanja Kompajlira se u mašinski program radi izvršenja na računaru Opis algoritma Opis strukture digitalnog sistema Konkurentni model izračunavanja Kompajlira se radi simulacije u RTL simulatoru Sintetiše se radi implementacije u hardveru Termini: n n Program - opis algoritma u programskom jeziku Kôd – opis algoritma ili strukture u jeziku za opis hardvera Arhitektura mikrosistema

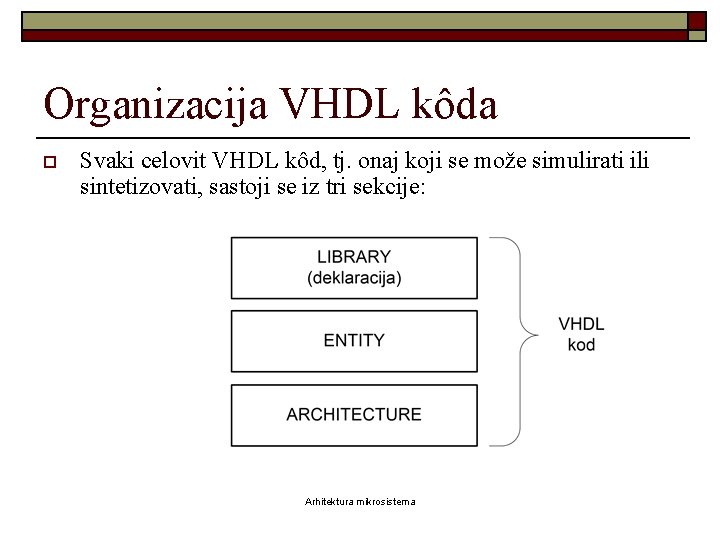

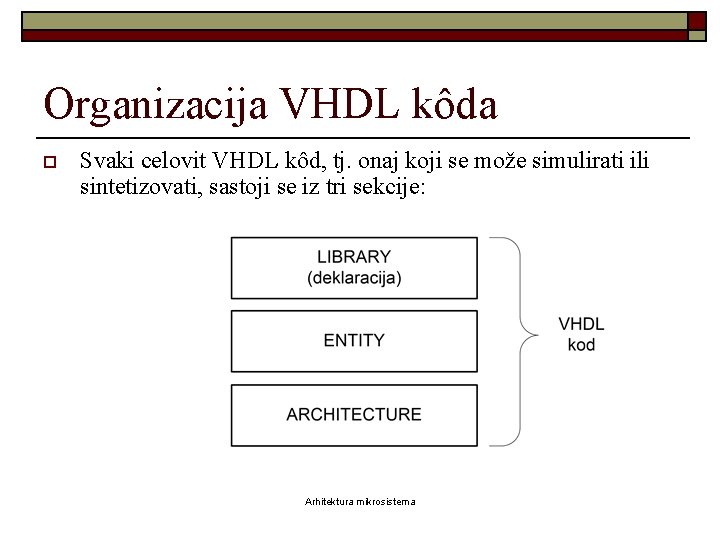

Organizacija VHDL kôda o Svaki celovit VHDL kôd, tj. onaj koji se može simulirati ili sintetizovati, sastoji se iz tri sekcije: Arhitektura mikrosistema

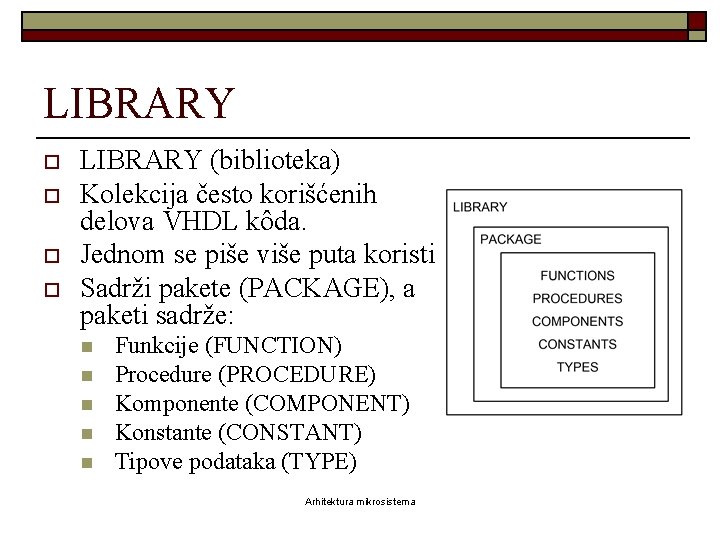

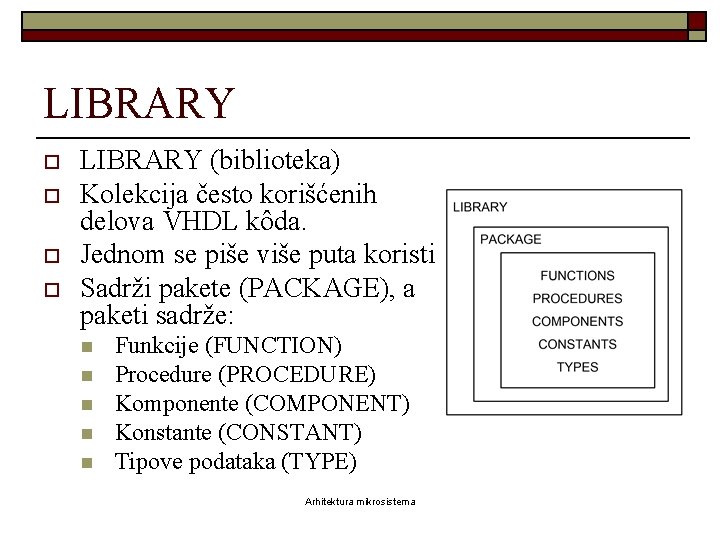

LIBRARY o o LIBRARY (biblioteka) Kolekcija često korišćenih delova VHDL kôda. Jednom se piše više puta koristi Sadrži pakete (PACKAGE), a paketi sadrže: n n n Funkcije (FUNCTION) Procedure (PROCEDURE) Komponente (COMPONENT) Konstante (CONSTANT) Tipove podataka (TYPE) Arhitektura mikrosistema

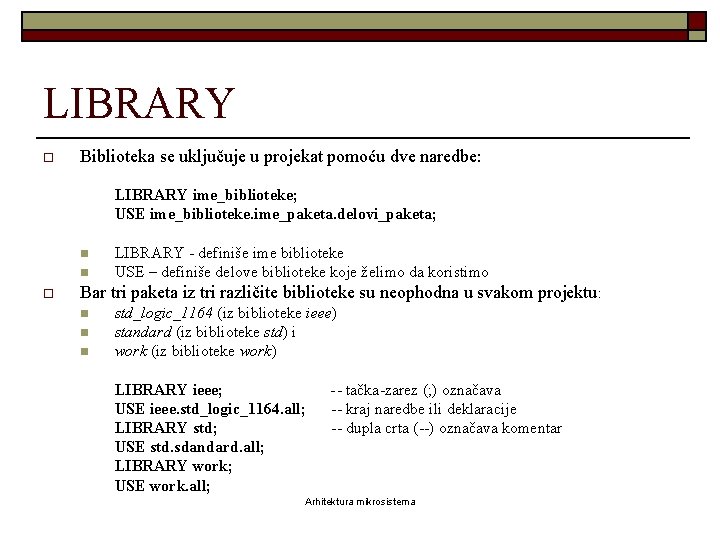

LIBRARY o Biblioteka se uključuje u projekat pomoću dve naredbe: LIBRARY ime_biblioteke; USE ime_biblioteke. ime_paketa. delovi_paketa; n n o LIBRARY - definiše ime biblioteke USE – definiše delove biblioteke koje želimo da koristimo Bar tri paketa iz tri različite biblioteke su neophodna u svakom projektu: n n n std_logic_1164 (iz biblioteke ieee) standard (iz biblioteke std) i work (iz biblioteke work) LIBRARY ieee; USE ieee. std_logic_1164. all; LIBRARY std; USE std. sdandard. all; LIBRARY work; USE work. all; -- tačka-zarez (; ) označava -- kraj naredbe ili deklaracije -- dupla crta (--) označava komentar Arhitektura mikrosistema

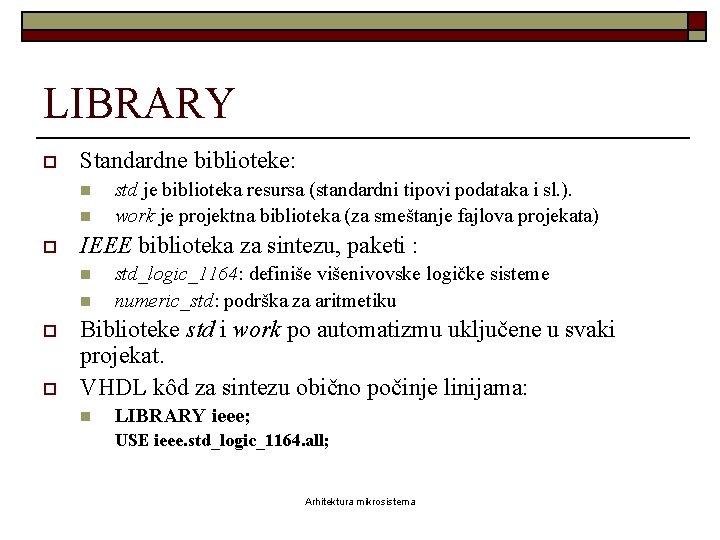

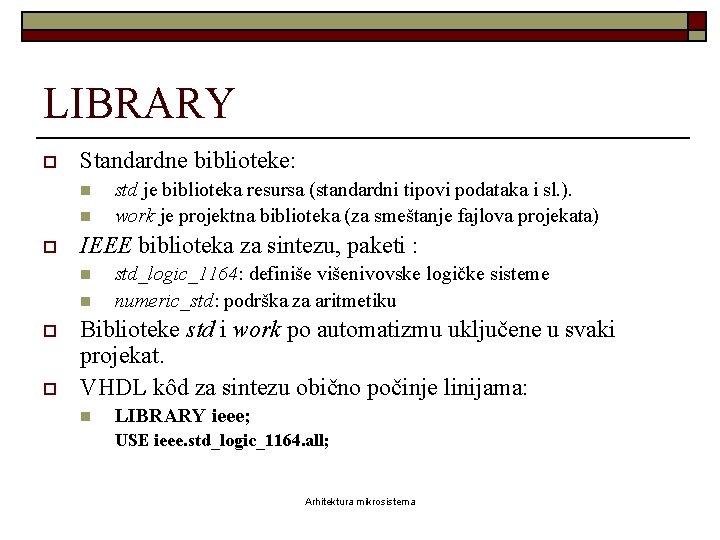

LIBRARY o Standardne biblioteke: n n o IEEE biblioteka za sintezu, paketi : n n o o std je biblioteka resursa (standardni tipovi podataka i sl. ). work je projektna biblioteka (za smeštanje fajlova projekata) std_logic_1164: definiše višenivovske logičke sisteme numeric_std: podrška za aritmetiku Biblioteke std i work po automatizmu uključene u svaki projekat. VHDL kôd za sintezu obično počinje linijama: n LIBRARY ieee; USE ieee. std_logic_1164. all; Arhitektura mikrosistema

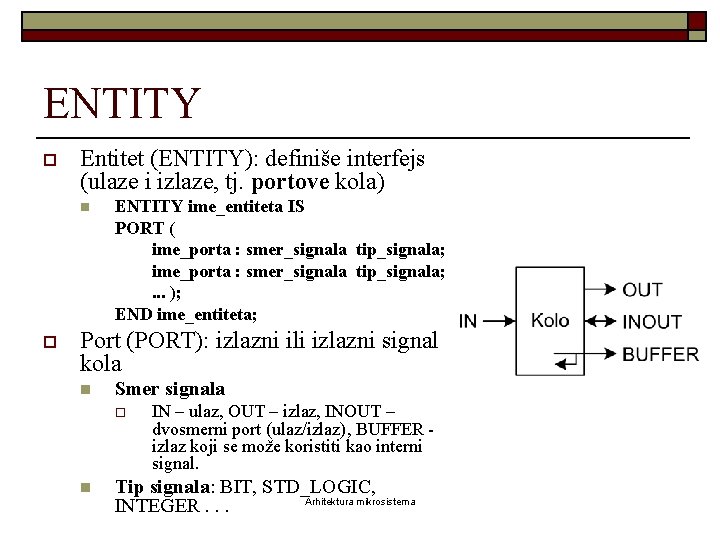

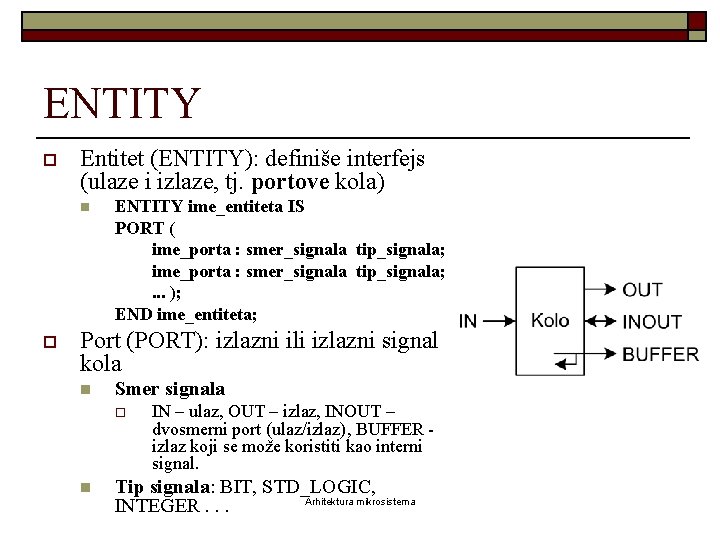

ENTITY o Entitet (ENTITY): definiše interfejs (ulaze i izlaze, tj. portove kola) n o ENTITY ime_entiteta IS PORT ( ime_porta : smer_signala tip_signala; . . . ); END ime_entiteta; Port (PORT): izlazni ili izlazni signal kola n Smer signala o n IN – ulaz, OUT – izlaz, INOUT – dvosmerni port (ulaz/izlaz), BUFFER izlaz koji se može koristiti kao interni signal. Tip signala: BIT, STD_LOGIC, Arhitektura mikrosistema INTEGER. . .

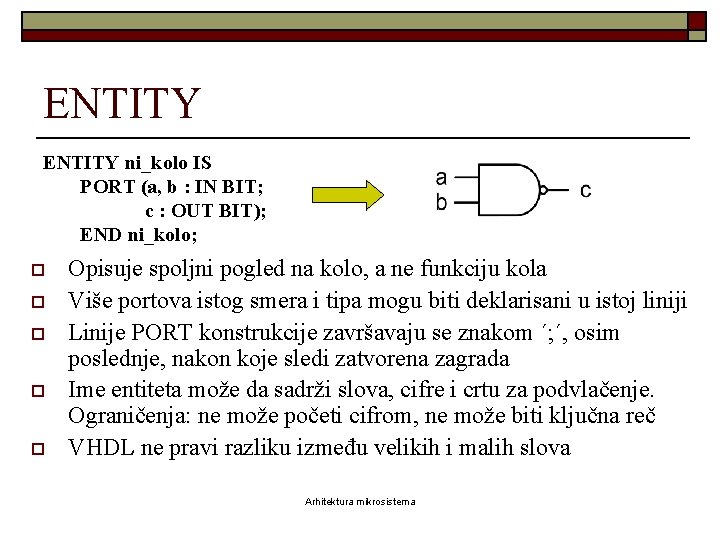

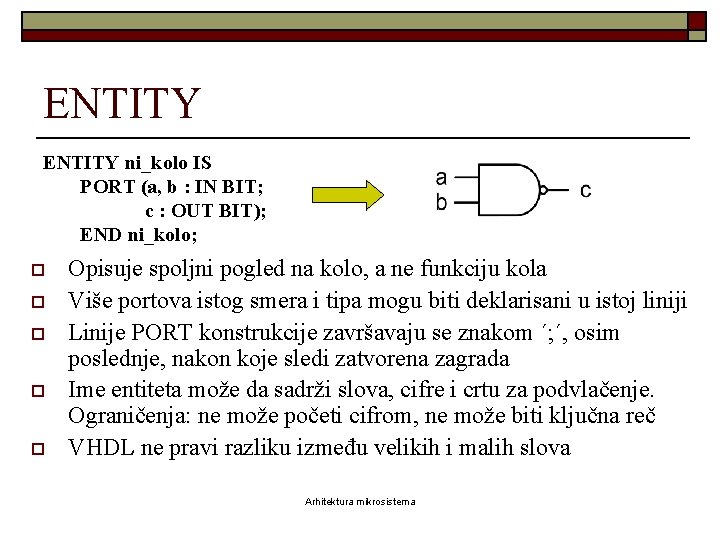

ENTITY ni_kolo IS PORT (a, b : IN BIT; c : OUT BIT); END ni_kolo; o o o Opisuje spoljni pogled na kolo, a ne funkciju kola Više portova istog smera i tipa mogu biti deklarisani u istoj liniji Linije PORT konstrukcije završavaju se znakom ΄; ΄, osim poslednje, nakon koje sledi zatvorena zagrada Ime entiteta može da sadrži slova, cifre i crtu za podvlačenje. Ograničenja: ne može početi cifrom, ne može biti ključna reč VHDL ne pravi razliku između velikih i malih slova Arhitektura mikrosistema

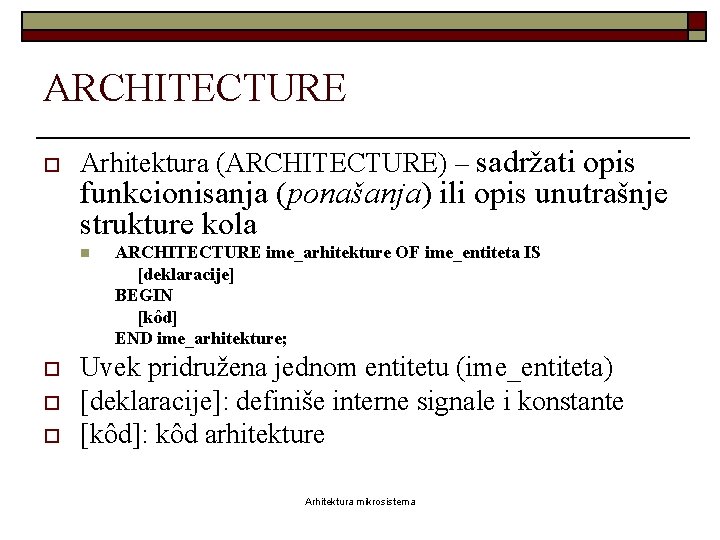

ARCHITECTURE o Arhitektura (ARCHITECTURE) – sadržati opis funkcionisanja (ponašanja) ili opis unutrašnje strukture kola n o o o ARCHITECTURE ime_arhitekture OF ime_entiteta IS [deklaracije] BEGIN [kôd] END ime_arhitekture; Uvek pridružena jednom entitetu (ime_entiteta) [deklaracije]: definiše interne signale i konstante [kôd]: kôd arhitekture Arhitektura mikrosistema

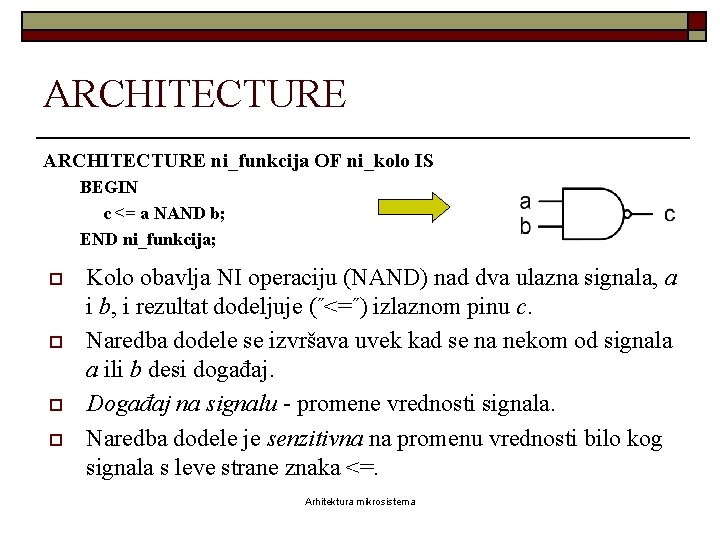

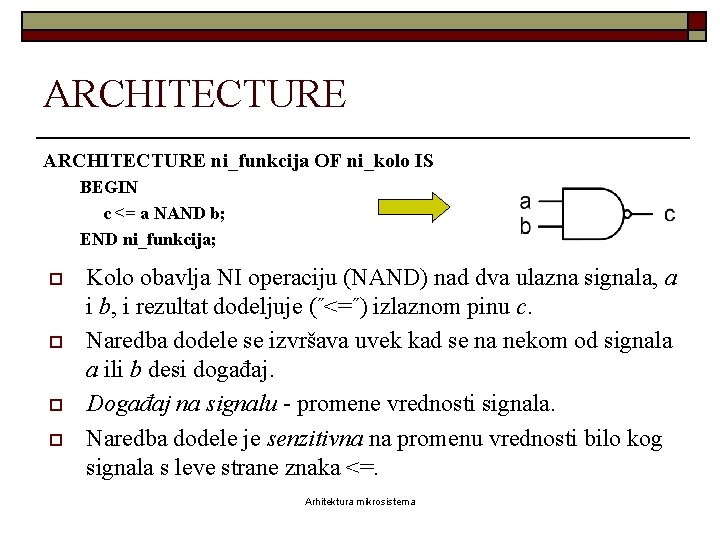

ARCHITECTURE ni_funkcija OF ni_kolo IS BEGIN c <= a NAND b; END ni_funkcija; o o Kolo obavlja NI operaciju (NAND) nad dva ulazna signala, a i b, i rezultat dodeljuje (˝<=˝) izlaznom pinu c. Naredba dodele se izvršava uvek kad se na nekom od signala a ili b desi događaj. Događaj na signalu - promene vrednosti signala. Naredba dodele je senzitivna na promenu vrednosti bilo kog signala s leve strane znaka <=. Arhitektura mikrosistema

Stilovi projektovanja u VHDL-u o Funkcionalni (ili bihejvioralni) n n o o Konkurentne naredbe (dataflow, tj. model toka podataka) Sekvencijalne naredbe (sekvencijalni model, kao kod programskih jezika) Strukturni (ekvivalentno blok dijagramu) Mešovit (kombinacija konkurentnih/ sekvencijalnih naredbi i strukturnog opisa) Arhitektura mikrosistema

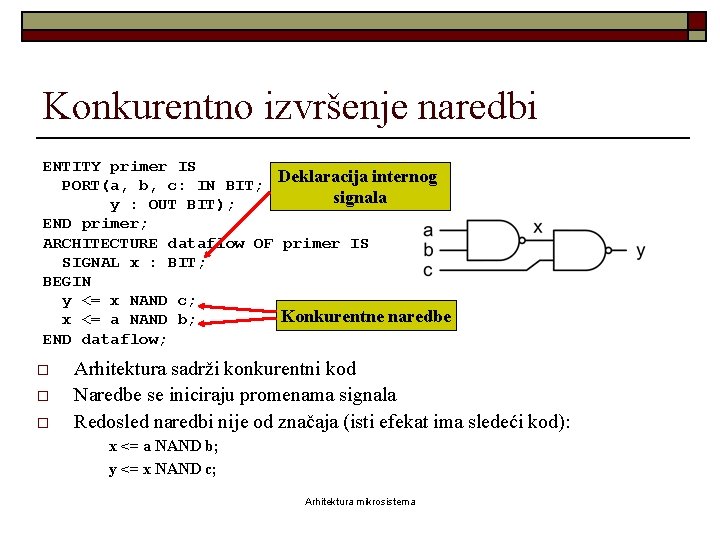

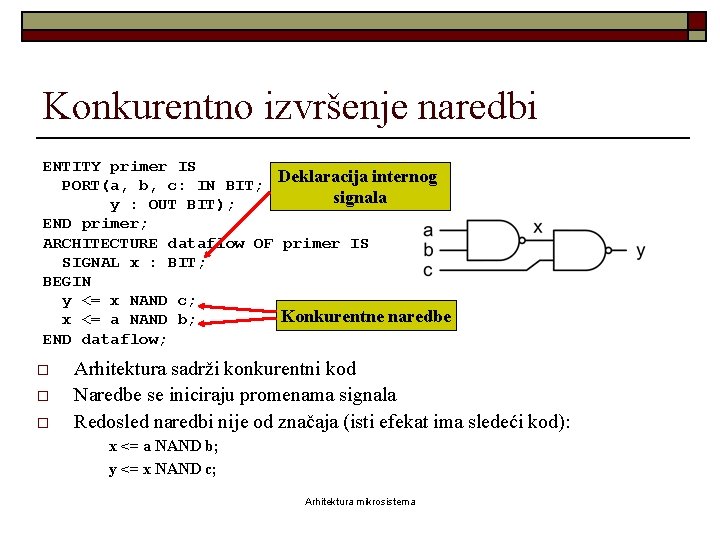

Konkurentno izvršenje naredbi ENTITY primer IS Deklaracija internog PORT(a, b, c: IN BIT; signala y : OUT BIT); END primer; ARCHITECTURE dataflow OF primer IS SIGNAL x : BIT; BEGIN y <= x NAND c; Konkurentne naredbe x <= a NAND b; END dataflow; o o o Arhitektura sadrži konkurentni kod Naredbe se iniciraju promenama signala Redosled naredbi nije od značaja (isti efekat ima sledeći kod): x <= a NAND b; y <= x NAND c; Arhitektura mikrosistema

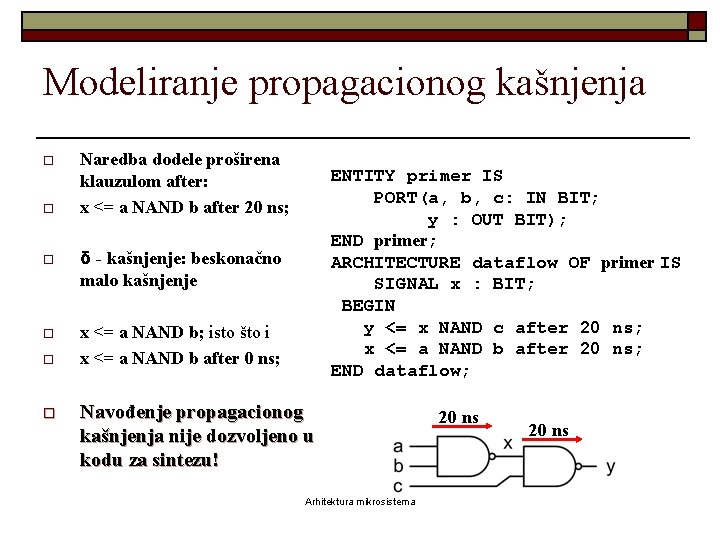

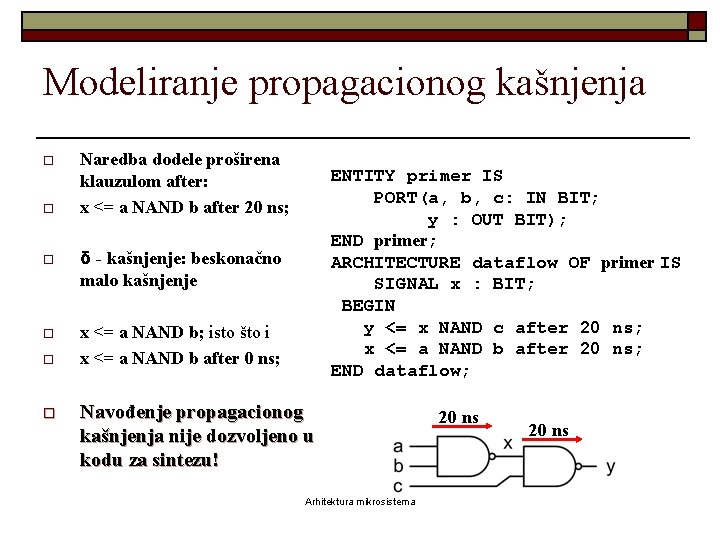

Modeliranje propagacionog kašnjenja o o Naredba dodele proširena klauzulom after: x <= a NAND b after 20 ns; o δ - kašnjenje: beskonačno malo kašnjenje o x <= a NAND b; isto što i x <= a NAND b after 0 ns; o o ENTITY primer IS PORT(a, b, c: IN BIT; y : OUT BIT); END primer; ARCHITECTURE dataflow OF primer IS SIGNAL x : BIT; BEGIN y <= x NAND c after 20 ns; x <= a NAND b after 20 ns; END dataflow; Navođenje propagacionog kašnjenja nije dozvoljeno u kodu za sintezu! Arhitektura mikrosistema 20 ns

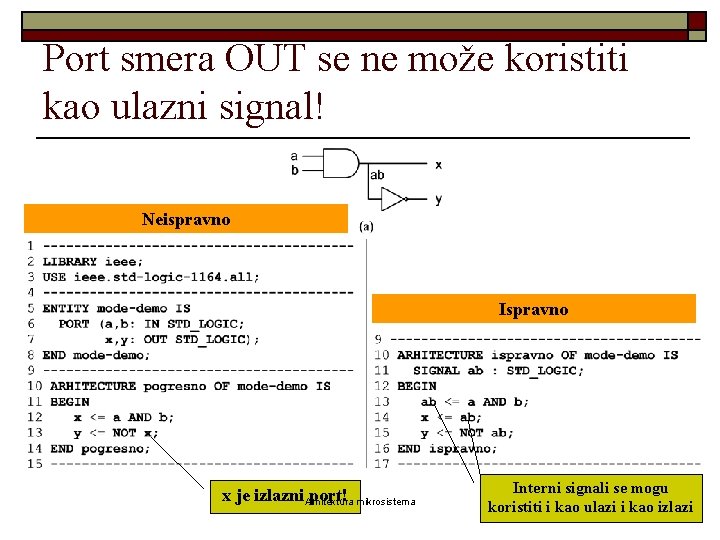

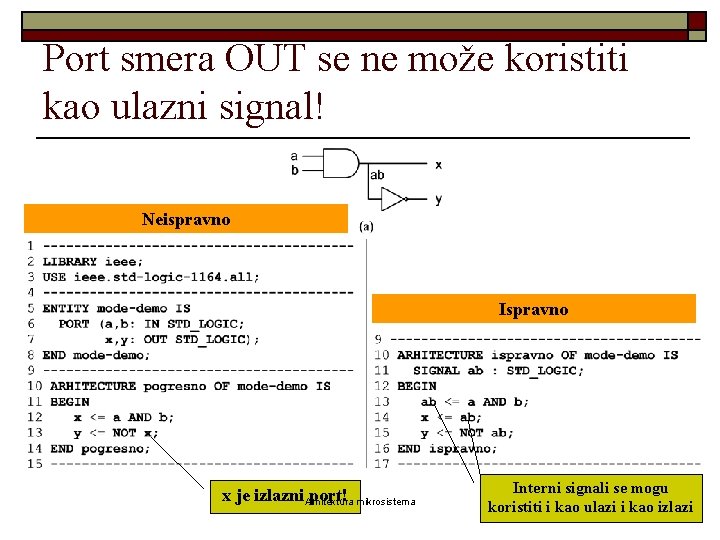

Port smera OUT se ne može koristiti kao ulazni signal! Neispravno Ispravno x je izlazni Arhitektura port! mikrosistema Interni signali se mogu koristiti i kao ulazi i kao izlazi

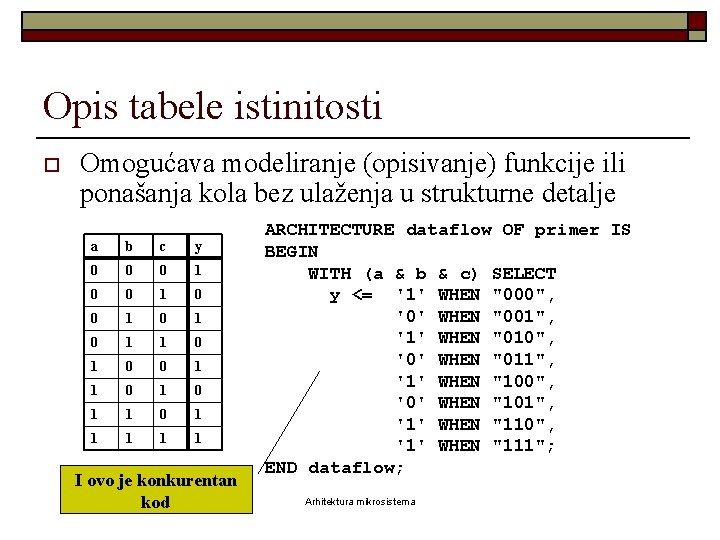

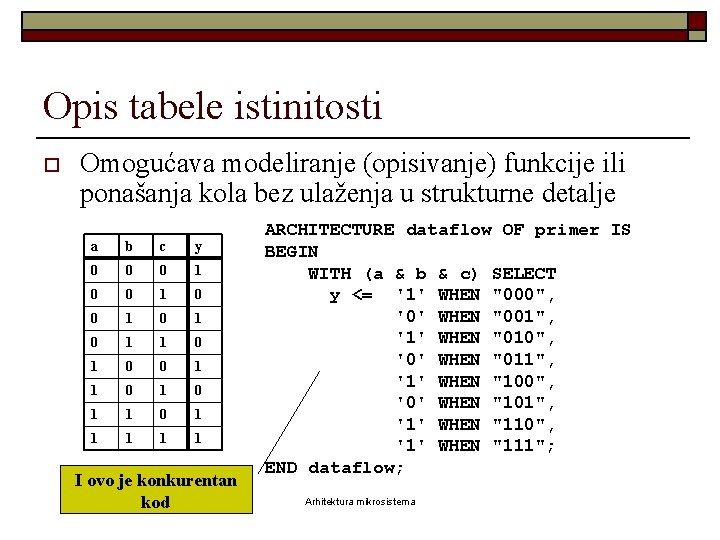

Opis tabele istinitosti o Omogućava modeliranje (opisivanje) funkcije ili ponašanja kola bez ulaženja u strukturne detalje a b c y 0 0 0 1 0 1 1 0 1 1 1 I ovo je konkurentan kod ARCHITECTURE dataflow OF primer IS BEGIN WITH (a & b & c) SELECT y <= '1' WHEN "000", '0' WHEN "001", '1' WHEN "010", '0' WHEN "011", '1' WHEN "100", '0' WHEN "101", '1' WHEN "110", '1' WHEN "111"; END dataflow; Arhitektura mikrosistema

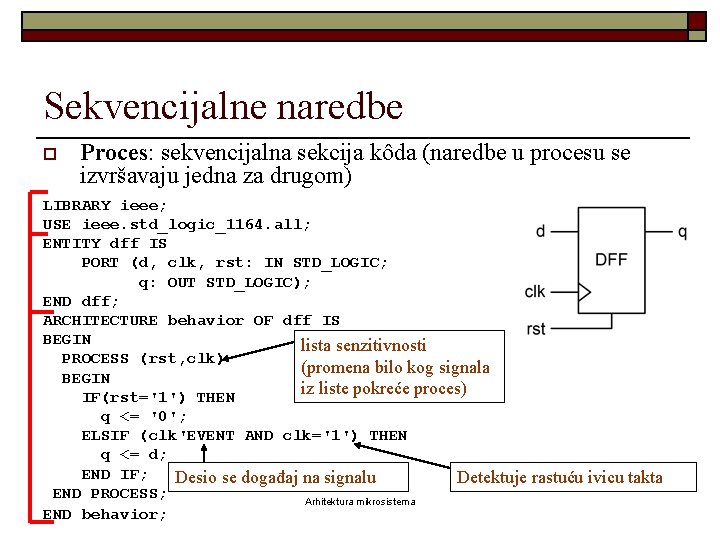

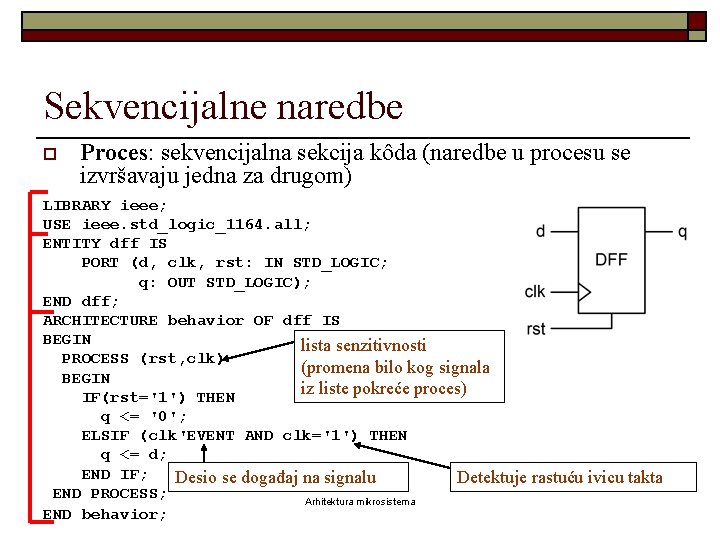

Sekvencijalne naredbe o Proces: sekvencijalna sekcija kôda (naredbe u procesu se izvršavaju jedna za drugom) LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY dff IS PORT (d, clk, rst: IN STD_LOGIC; q: OUT STD_LOGIC); END dff; ARCHITECTURE behavior OF dff IS BEGIN lista senzitivnosti PROCESS (rst, clk) (promena bilo kog signala BEGIN iz liste pokreće proces) IF(rst='1') THEN q <= '0'; ELSIF (clk'EVENT AND clk='1') THEN q <= d; END IF; Desio se događaj na signalu Detektuje rastuću ivicu takta END PROCESS; Arhitektura mikrosistema END behavior;

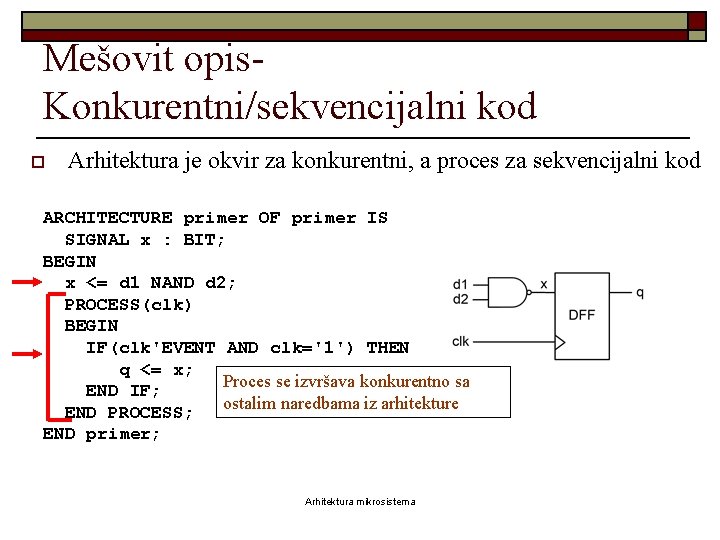

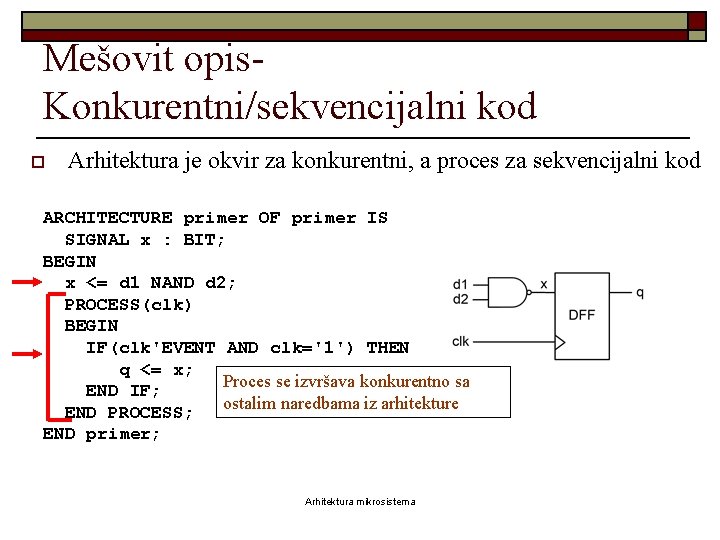

Mešovit opis. Konkurentni/sekvencijalni kod o Arhitektura je okvir za konkurentni, a proces za sekvencijalni kod ARCHITECTURE primer OF primer IS SIGNAL x : BIT; BEGIN x <= d 1 NAND d 2; PROCESS(clk) BEGIN IF(clk'EVENT AND clk='1') THEN q <= x; Proces se izvršava konkurentno sa END IF; ostalim naredbama iz arhitekture END PROCESS; END primer; Arhitektura mikrosistema

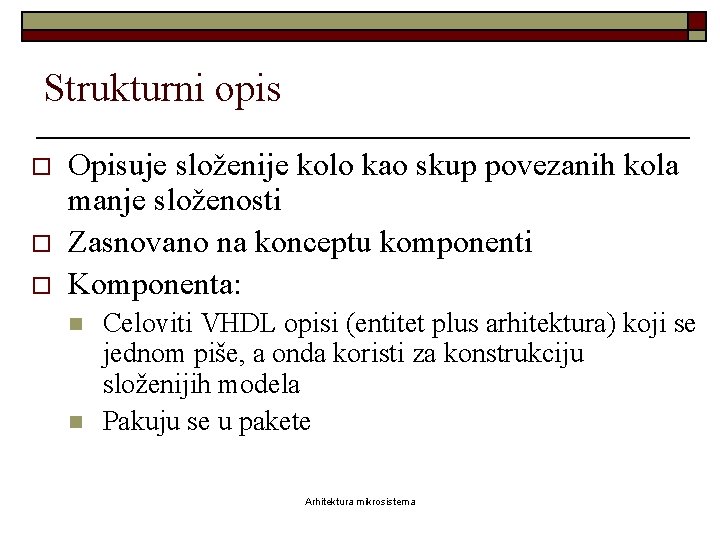

Strukturni opis o o o Opisuje složenije kolo kao skup povezanih kola manje složenosti Zasnovano na konceptu komponenti Komponenta: n n Celoviti VHDL opisi (entitet plus arhitektura) koji se jednom piše, a onda koristi za konstrukciju složenijih modela Pakuju se u pakete Arhitektura mikrosistema

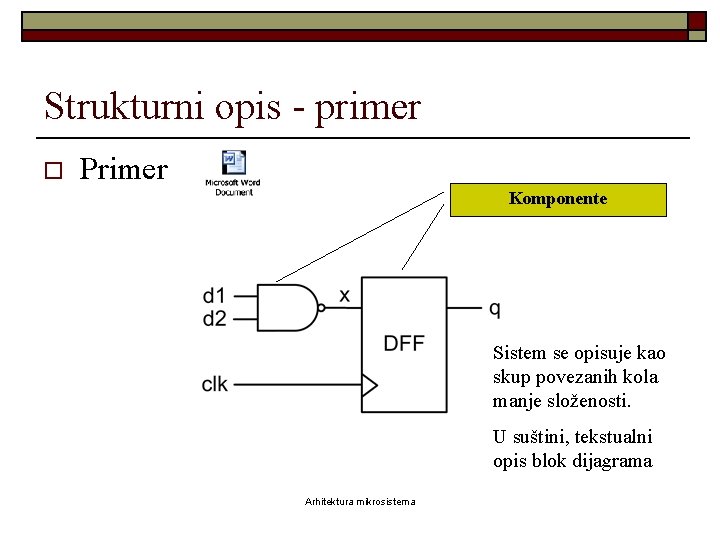

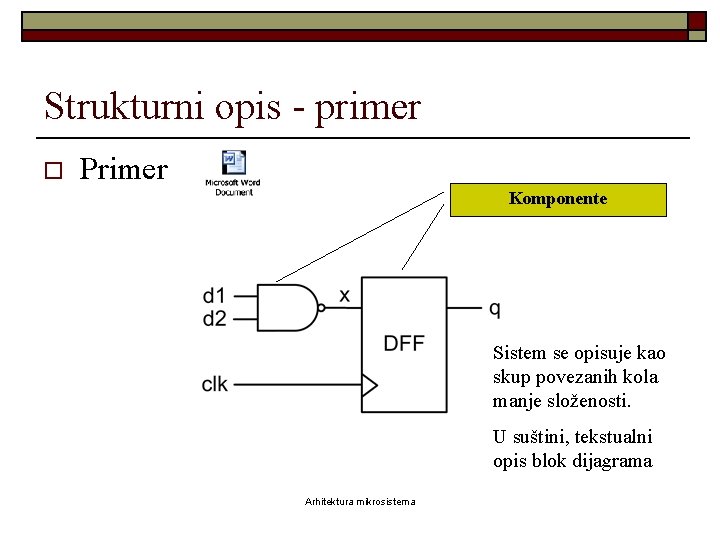

Strukturni opis - primer o Primer Komponente Sistem se opisuje kao skup povezanih kola manje složenosti. U suštini, tekstualni opis blok dijagrama Arhitektura mikrosistema

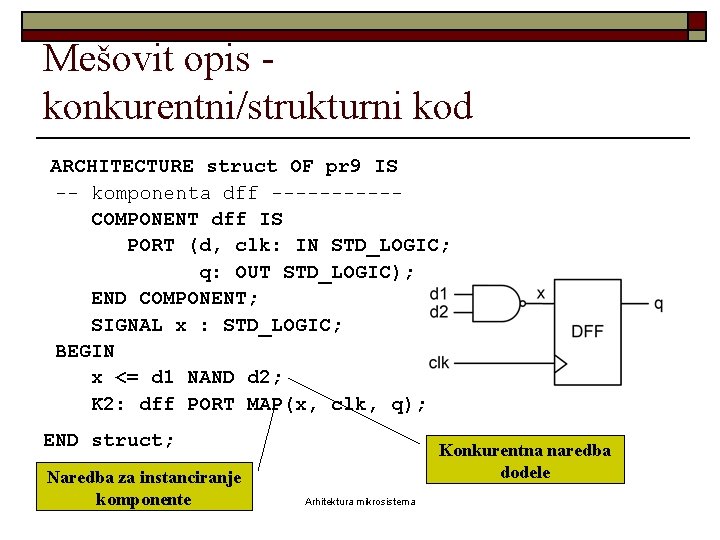

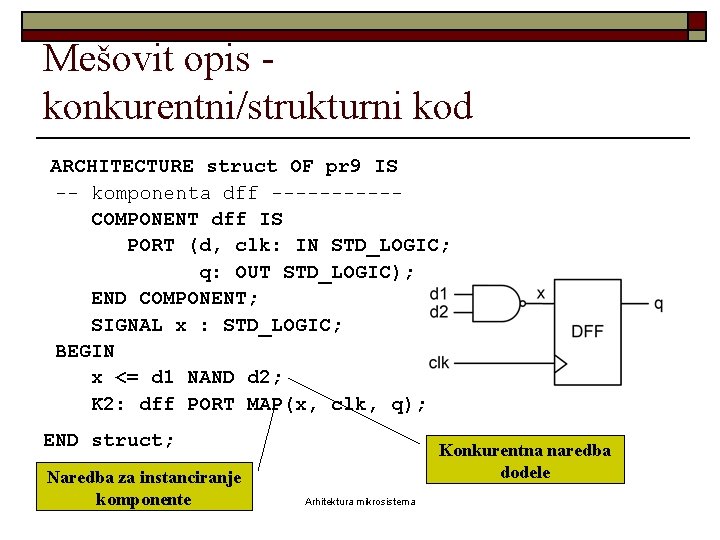

Mešovit opis konkurentni/strukturni kod ARCHITECTURE struct OF pr 9 IS -- komponenta dff -----COMPONENT dff IS PORT (d, clk: IN STD_LOGIC; q: OUT STD_LOGIC); END COMPONENT; SIGNAL x : STD_LOGIC; BEGIN x <= d 1 NAND d 2; K 2: dff PORT MAP(x, clk, q); END struct; Naredba za instanciranje komponente Konkurentna naredba dodele Arhitektura mikrosistema

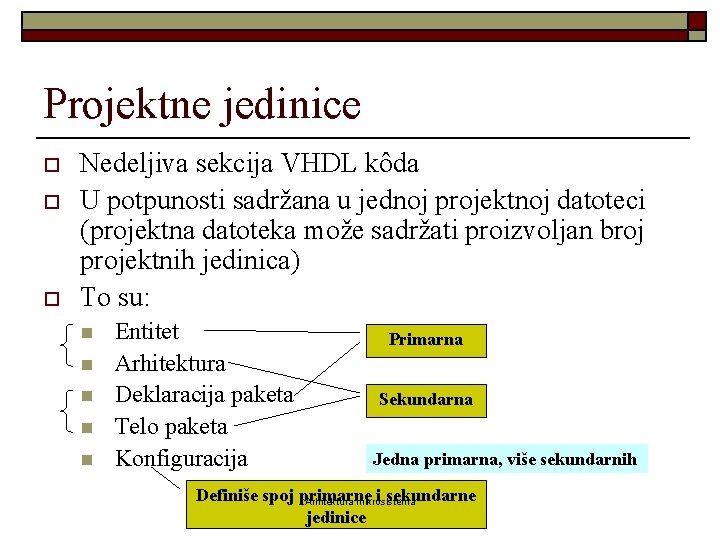

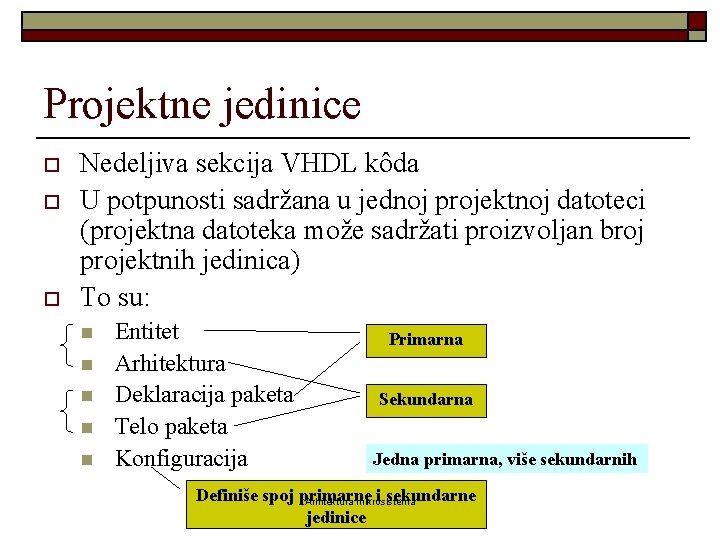

Projektne jedinice o o o Nedeljiva sekcija VHDL kôda U potpunosti sadržana u jednoj projektnoj datoteci (projektna datoteka može sadržati proizvoljan broj projektnih jedinica) To su: n n n Entitet Arhitektura Deklaracija paketa Telo paketa Konfiguracija Primarna Sekundarna Jedna primarna, više sekundarnih Definiše spoj primarne i sekundarne Arhitektura mikrosistema jedinice

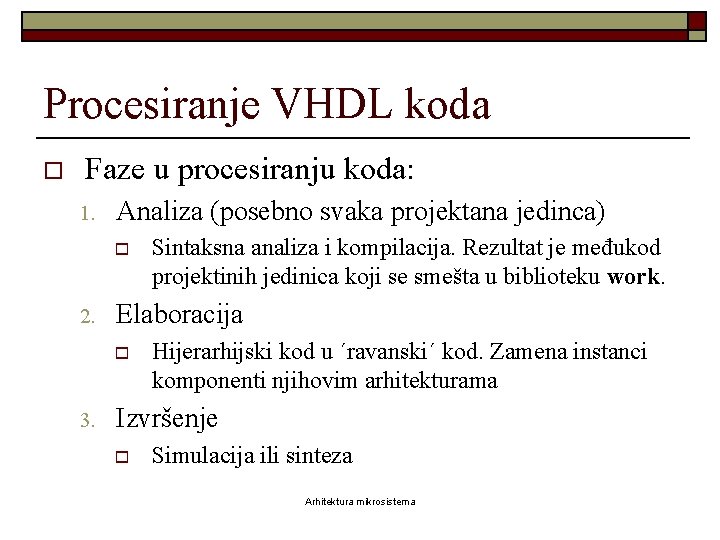

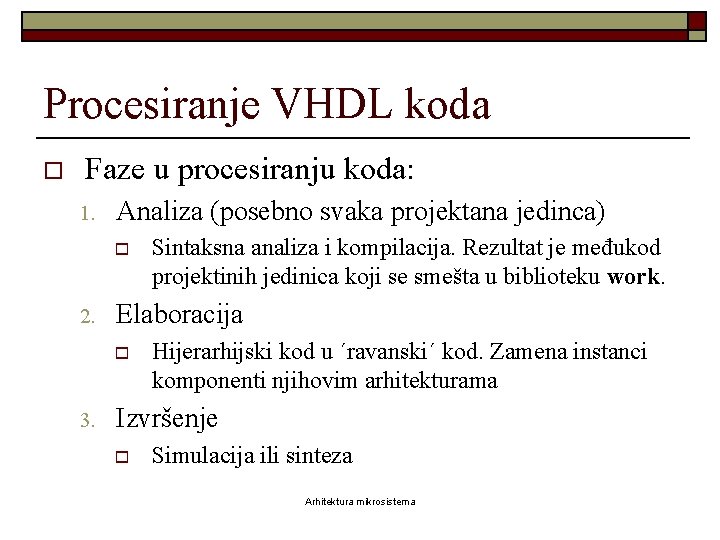

Procesiranje VHDL koda o Faze u procesiranju koda: 1. Analiza (posebno svaka projektana jedinca) o 2. Elaboracija o 3. Sintaksna analiza i kompilacija. Rezultat je međukod projektinih jedinica koji se smešta u biblioteku work. Hijerarhijski kod u ´ravanski´ kod. Zamena instanci komponenti njihovim arhitekturama Izvršenje o Simulacija ili sinteza Arhitektura mikrosistema

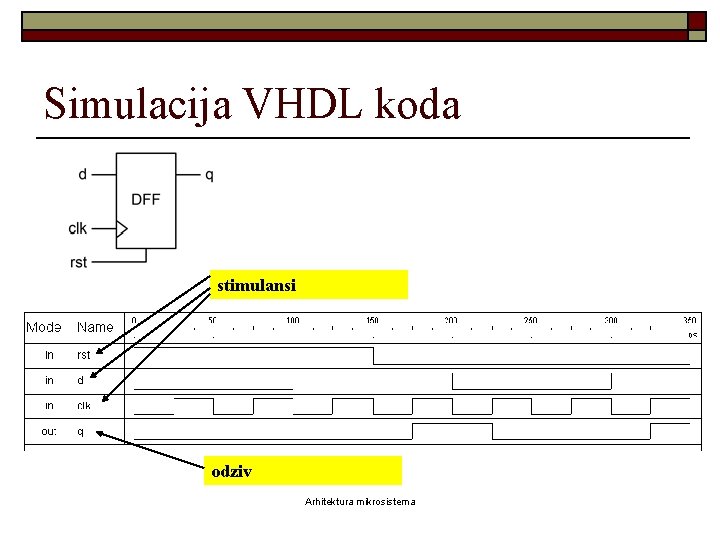

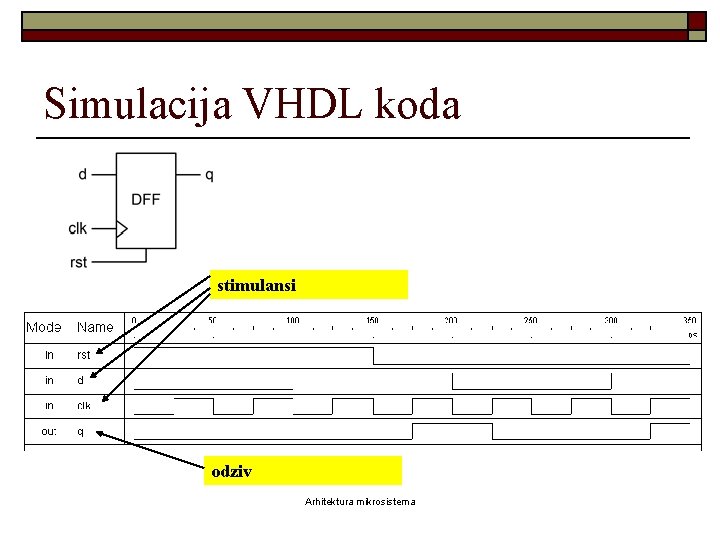

Simulacija VHDL koda stimulansi odziv Arhitektura mikrosistema

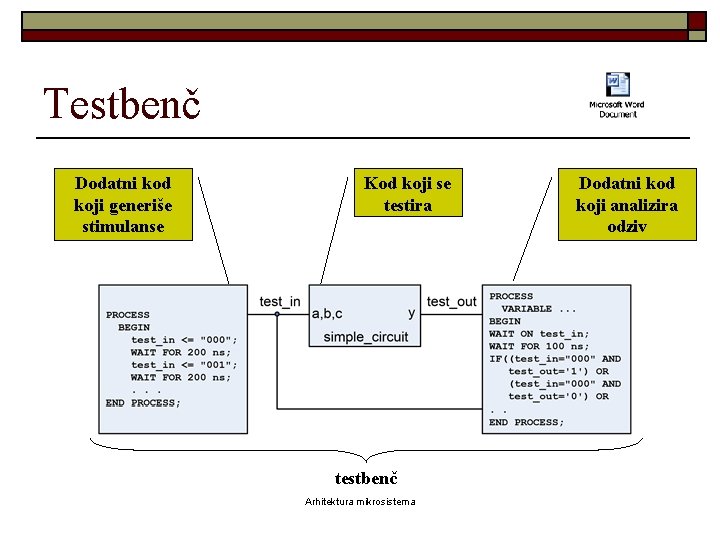

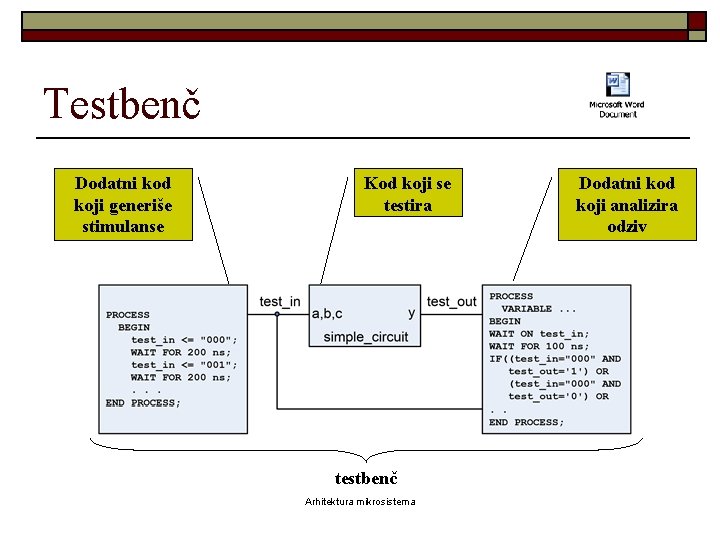

Testbenč Dodatni kod koji generiše stimulanse Kod koji se testira testbenč Arhitektura mikrosistema Dodatni kod koji analizira odziv

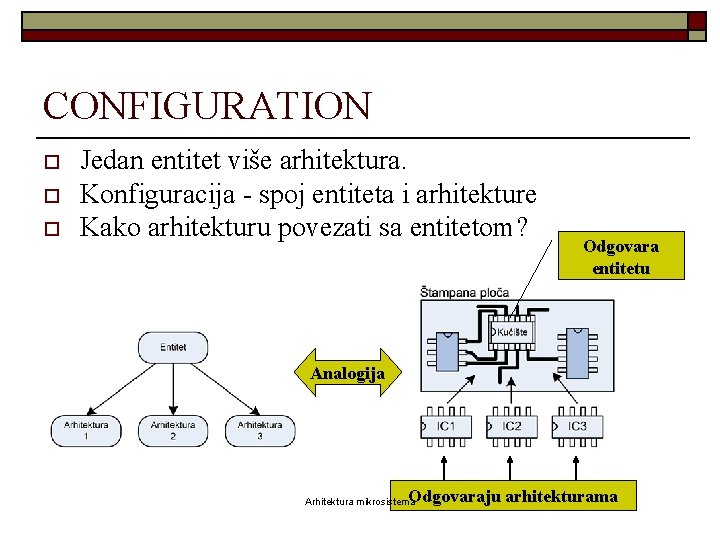

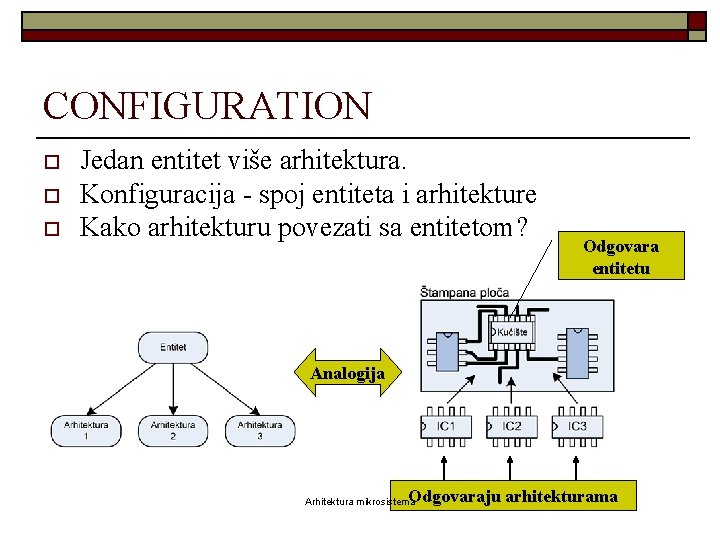

CONFIGURATION o o o Jedan entitet više arhitektura. Konfiguracija - spoj entiteta i arhitekture Kako arhitekturu povezati sa entitetom? Odgovara entitetu Analogija Odgovaraju arhitekturama Arhitektura mikrosistema

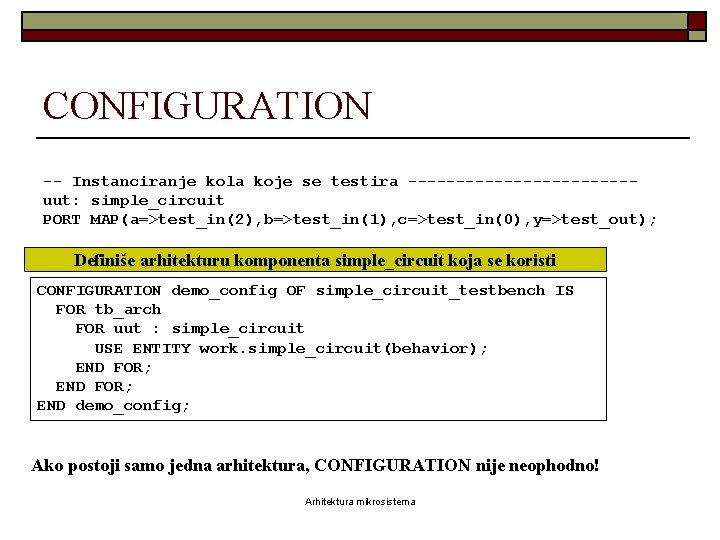

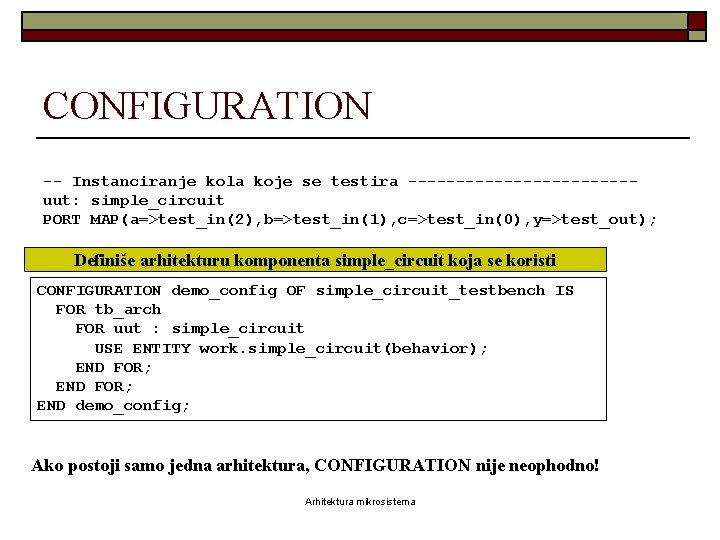

CONFIGURATION -- Instanciranje kola koje se testira ------------uut: simple_circuit PORT MAP(a=>test_in(2), b=>test_in(1), c=>test_in(0), y=>test_out); Definiše arhitekturu komponenta simple_circuit koja se koristi CONFIGURATION demo_config OF simple_circuit_testbench IS FOR tb_arch FOR uut : simple_circuit USE ENTITY work. simple_circuit(behavior); END FOR; END demo_config; Ako postoji samo jedna arhitektura, CONFIGURATION nije neophodno! Arhitektura mikrosistema

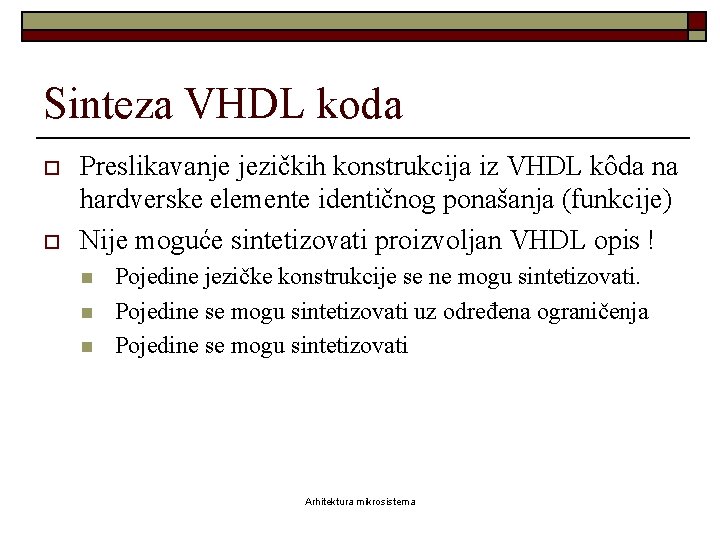

Sinteza VHDL koda o o Preslikavanje jezičkih konstrukcija iz VHDL kôda na hardverske elemente identičnog ponašanja (funkcije) Nije moguće sintetizovati proizvoljan VHDL opis ! n n n Pojedine jezičke konstrukcije se ne mogu sintetizovati. Pojedine se mogu sintetizovati uz određena ograničenja Pojedine se mogu sintetizovati Arhitektura mikrosistema

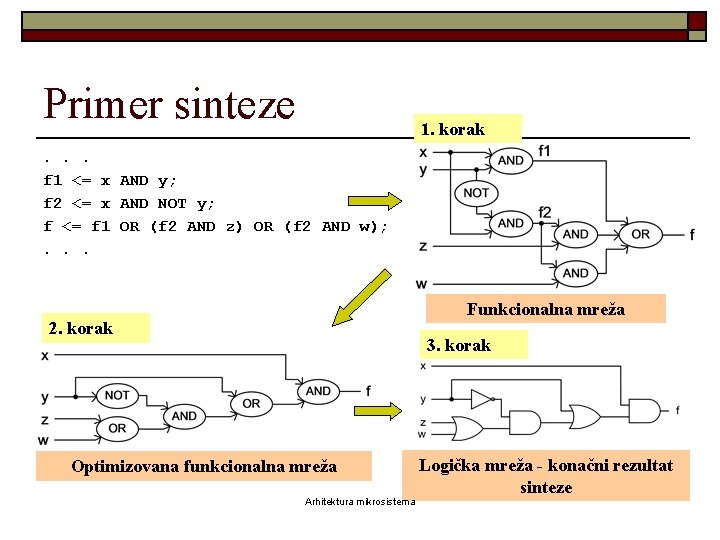

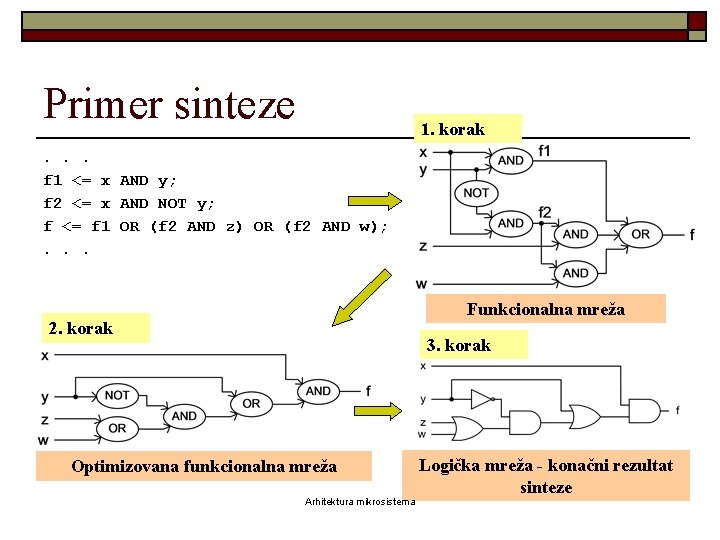

Primer sinteze 1. korak . . . f 1 <= x AND y; f 2 <= x AND NOT y; f <= f 1 OR (f 2 AND z) OR (f 2 AND w); . . . Funkcionalna mreža 2. korak 3. korak Optimizovana funkcionalna mreža Arhitektura mikrosistema Logička mreža - konačni rezultat sinteze

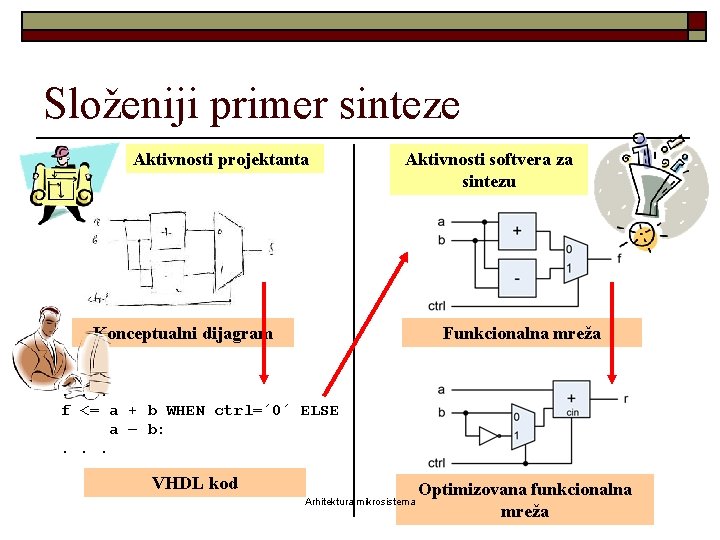

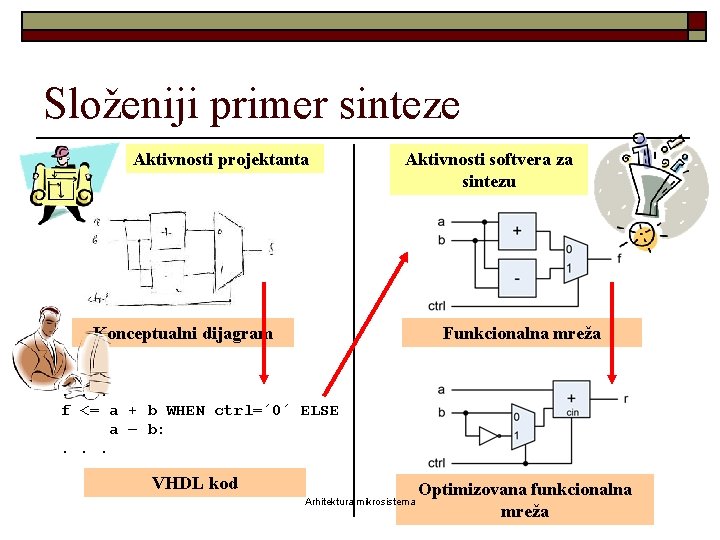

Složeniji primer sinteze Aktivnosti projektanta Aktivnosti softvera za sintezu Konceptualni dijagram Funkcionalna mreža . . . f <= a + b WHEN ctrl=´ 0´ ELSE a – b: . . . VHDL kod Arhitektura mikrosistema Optimizovana funkcionalna mreža

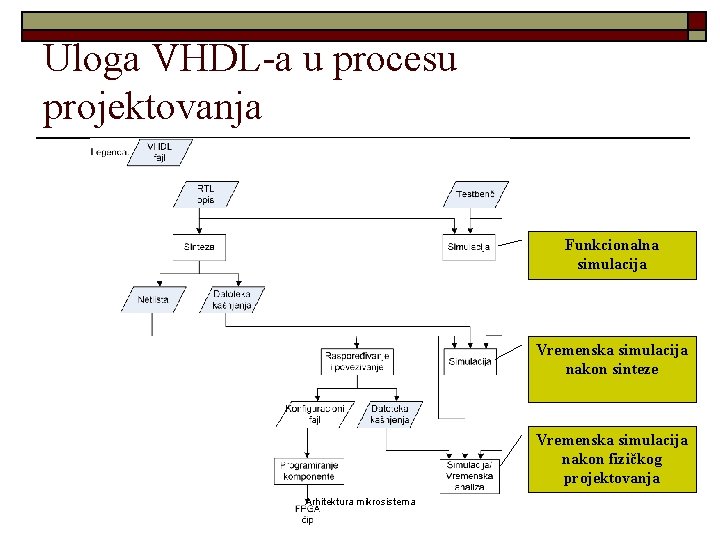

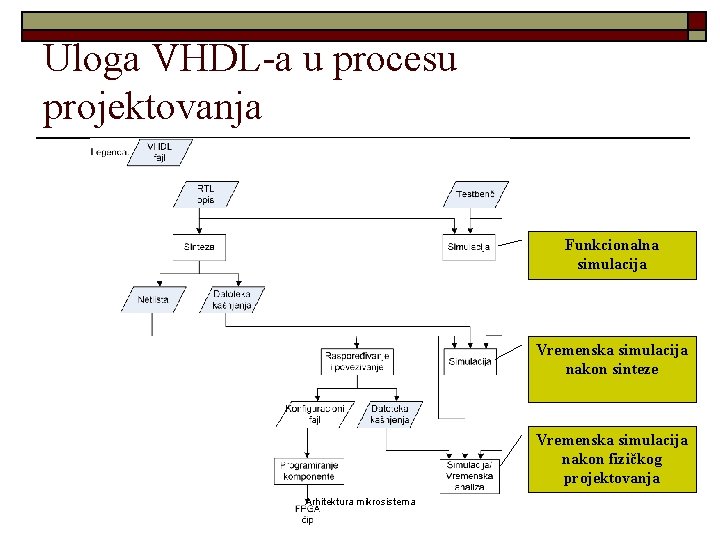

Uloga VHDL-a u procesu projektovanja Funkcionalna simulacija Vremenska simulacija nakon sinteze Vremenska simulacija nakon fizičkog projektovanja Arhitektura mikrosistema

Troslojna arhitektura

Troslojna arhitektura Romanička skulptura

Romanička skulptura Postmodernisms arhitektūrā

Postmodernisms arhitektūrā Isidora sekulic krug analiza

Isidora sekulic krug analiza Srpska srednjovekovna arhitektura

Srpska srednjovekovna arhitektura Pseudo arhitektura

Pseudo arhitektura Duzina procesorske reci

Duzina procesorske reci Harvardska arhitektura

Harvardska arhitektura Romanicka umetnost

Romanicka umetnost Renesansna italija

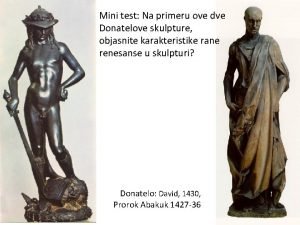

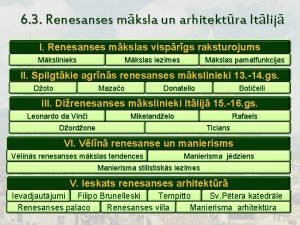

Renesansna italija Sema racunarskog sistema

Sema racunarskog sistema Piksīda

Piksīda Klijent server arhitektura

Klijent server arhitektura Travej arhitektura

Travej arhitektura Arhitektura procesora

Arhitektura procesora Trinivojska arhitektura

Trinivojska arhitektura Prelomljeni luk

Prelomljeni luk Renesansne crkve

Renesansne crkve Neoklasicizam arhitektura

Neoklasicizam arhitektura Zanos svete tereze

Zanos svete tereze Slidetodoc

Slidetodoc Arhitektura procesora

Arhitektura procesora Monumentalna arhitektura

Monumentalna arhitektura Mrežni model baze podataka

Mrežni model baze podataka Rimske skulpture

Rimske skulpture Arhitektura arm

Arhitektura arm Dinamička web stranica

Dinamička web stranica Aksonometrija arhitektura

Aksonometrija arhitektura Servisno orijentisana arhitektura

Servisno orijentisana arhitektura Arhitektura baze podataka

Arhitektura baze podataka Kā sauc katedrāli, pie kuras strādāja mikelandželo?

Kā sauc katedrāli, pie kuras strādāja mikelandželo? Fon nojmanova arhitektura

Fon nojmanova arhitektura Iskrivljena slova

Iskrivljena slova