Lecture 13 VHDL 31609 1 VHDL VHDL is

- Slides: 16

Lecture 13 VHDL 3/16/09 1

VHDL • VHDL is a hardware description language. • The behavior of a digital system can be described (specified) by writing a VHDL program. • The VHDL description can be simulate to verify the systems behavior and it can then be synthesized and programmed into an FPGA. • A VHDL program typically consists of at least two parts. These parts are called the entity and architecture. • Entity – Declaration of a modules input and output. o Analogous to schematic symbol showing signal pin outs. • Architecture – Describes actual behavior and implementation details. – An architecture can have only one entity associated with it, but several architectures may have the same entity. – This means we can have several architectures. 2

Example of Entity Architecture pair for a simple gate ENTITY AND 2 is port (X, Y: in BIT; Z: out BIT); end ENTITY AND 2; ARCHITECTURE ARC 1 OF AND 2 IS BEGIN -- After a delay of 2 ns Z <= X and Y after 2 ns; -- Z assumes the value of X and Y. END ARCHITECTURE ARC 1; 3

Constants, variables, and signals • VHDL objects include constants, variables, and signals. • The VHDL use of constants and variables is similar to that in other languages. • Signals are new and are typically used to represent voltages on wires. 4

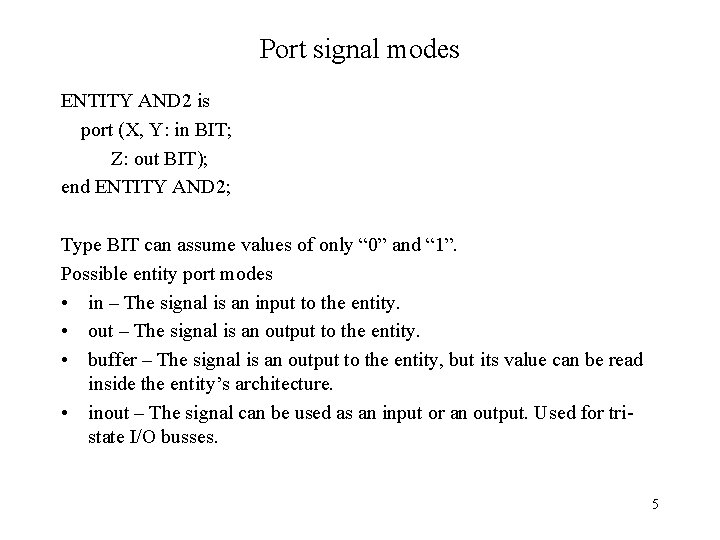

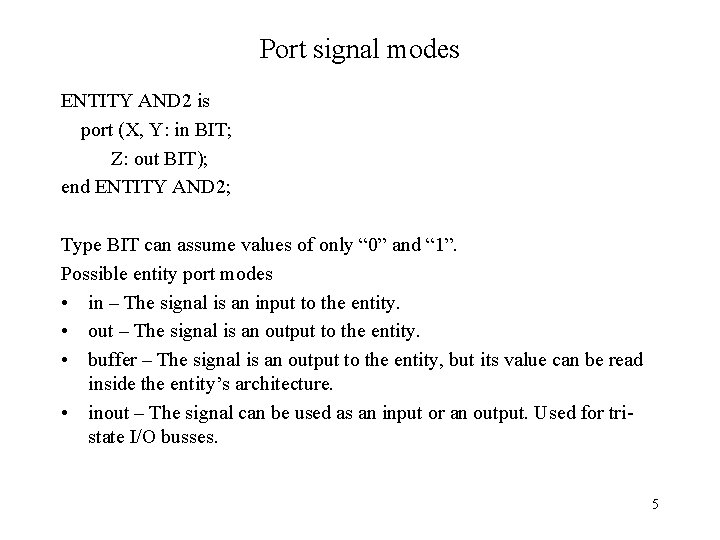

Port signal modes ENTITY AND 2 is port (X, Y: in BIT; Z: out BIT); end ENTITY AND 2; Type BIT can assume values of only “ 0” and “ 1”. Possible entity port modes • in – The signal is an input to the entity. • out – The signal is an output to the entity. • buffer – The signal is an output to the entity, but its value can be read inside the entity’s architecture. • inout – The signal can be used as an input or an output. Used for tristate I/O busses. 5

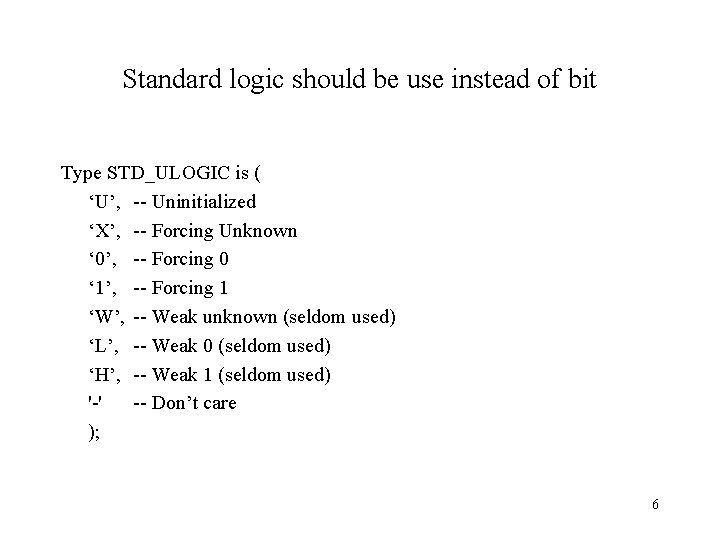

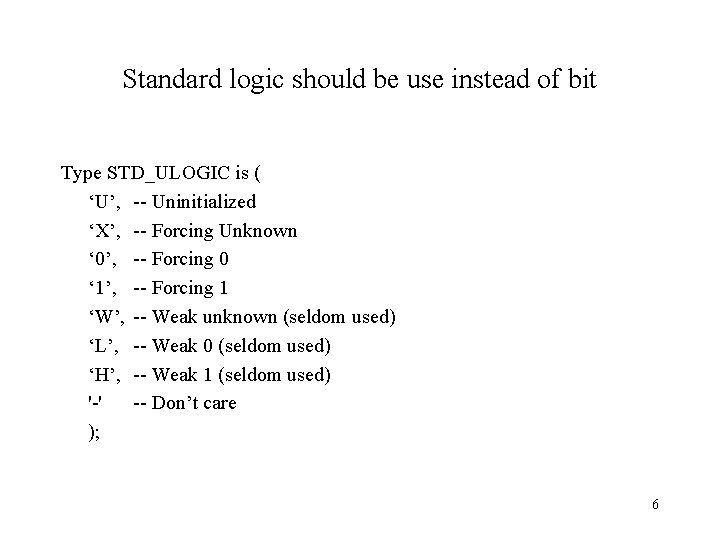

Standard logic should be use instead of bit Type STD_ULOGIC is ( ‘U’, -- Uninitialized ‘X’, -- Forcing Unknown ‘ 0’, -- Forcing 0 ‘ 1’, -- Forcing 1 ‘W’, -- Weak unknown (seldom used) ‘L’, -- Weak 0 (seldom used) ‘H’, -- Weak 1 (seldom used) '-' -- Don’t care ); 6

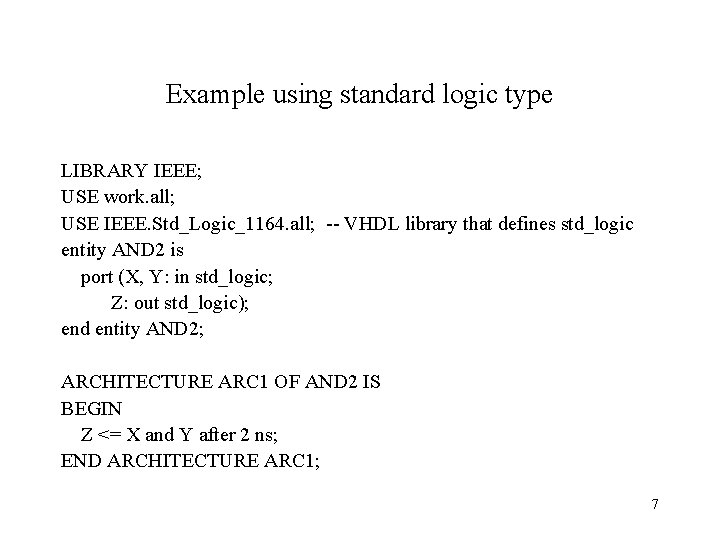

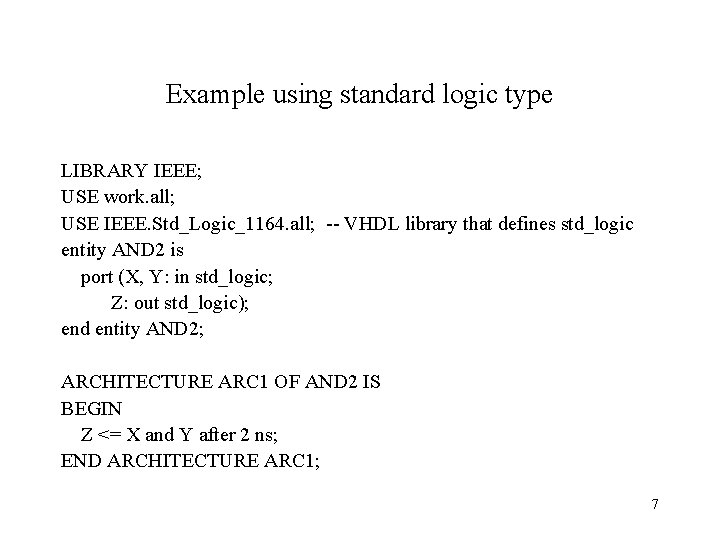

Example using standard logic type LIBRARY IEEE; USE work. all; USE IEEE. Std_Logic_1164. all; -- VHDL library that defines std_logic entity AND 2 is port (X, Y: in std_logic; Z: out std_logic); end entity AND 2; ARCHITECTURE ARC 1 OF AND 2 IS BEGIN Z <= X and Y after 2 ns; END ARCHITECTURE ARC 1; 7

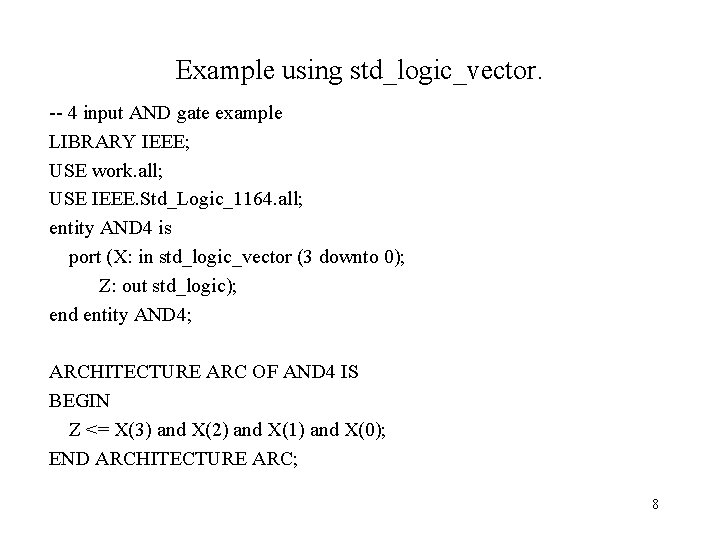

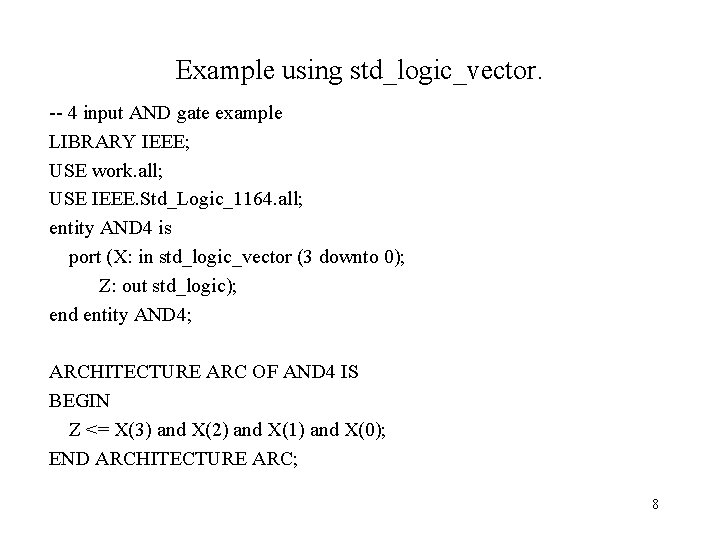

Example using std_logic_vector. -- 4 input AND gate example LIBRARY IEEE; USE work. all; USE IEEE. Std_Logic_1164. all; entity AND 4 is port (X: in std_logic_vector (3 downto 0); Z: out std_logic); end entity AND 4; ARCHITECTURE ARC OF AND 4 IS BEGIN Z <= X(3) and X(2) and X(1) and X(0); END ARCHITECTURE ARC; 8

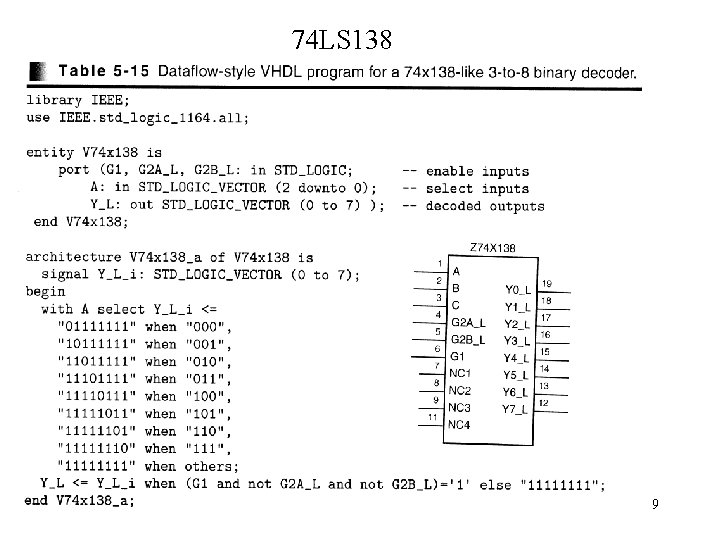

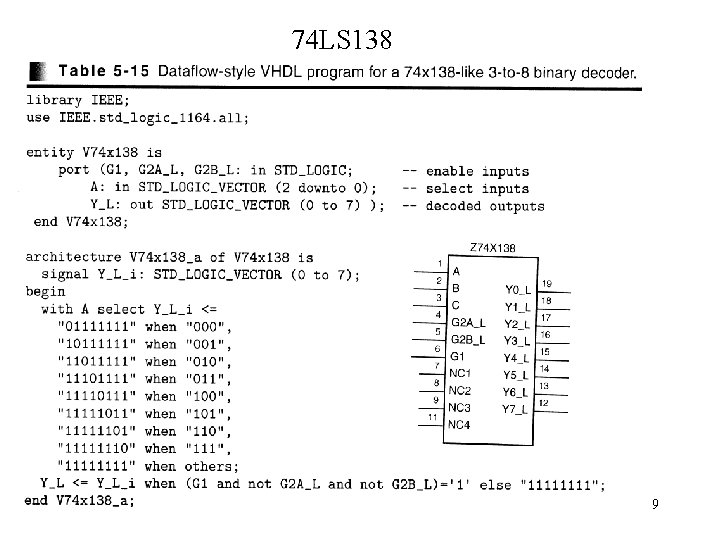

74 LS 138 9

Boolean Operators • • AND OR NAND NOR XNOR NOT 10

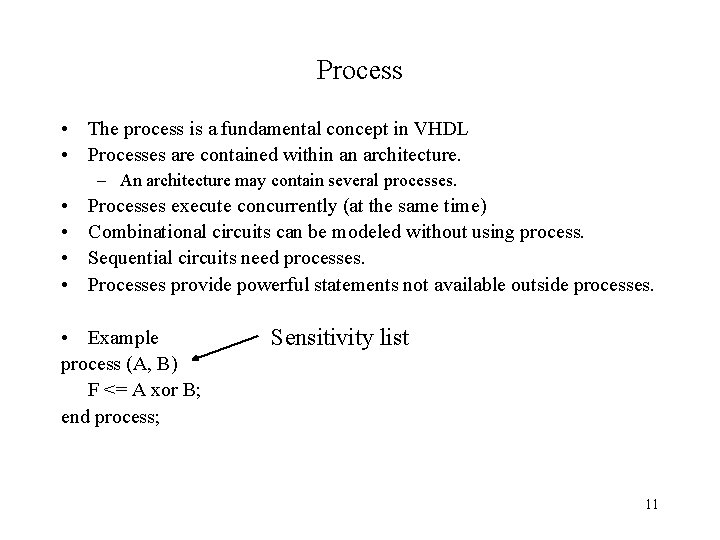

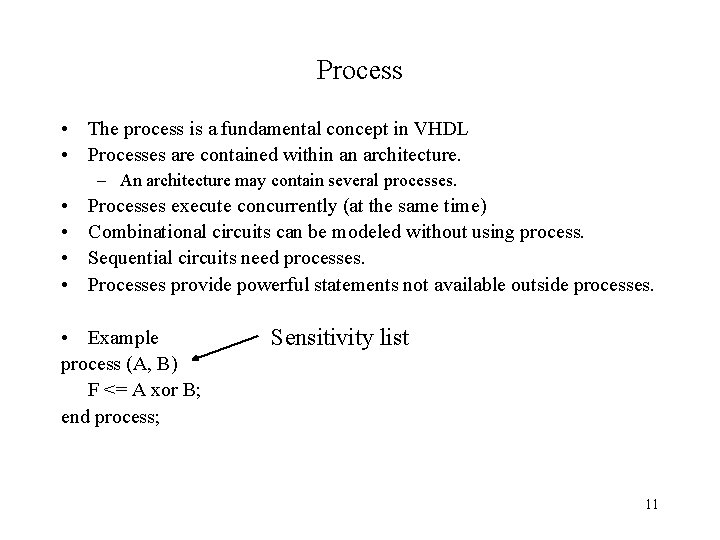

Process • The process is a fundamental concept in VHDL • Processes are contained within an architecture. – An architecture may contain several processes. • • Processes execute concurrently (at the same time) Combinational circuits can be modeled without using process. Sequential circuits need processes. Processes provide powerful statements not available outside processes. • Example process (A, B) F <= A xor B; end process; Sensitivity list 11

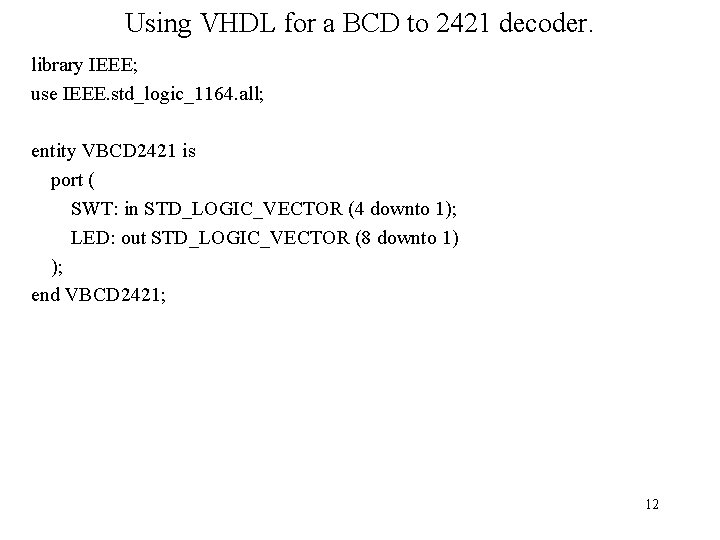

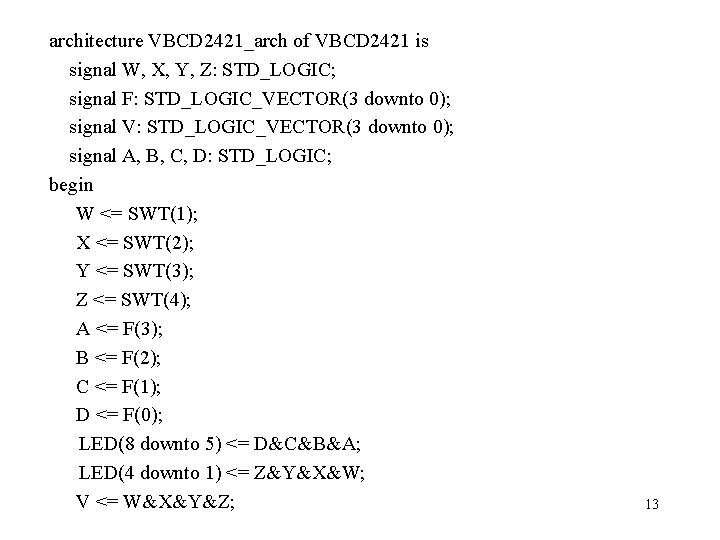

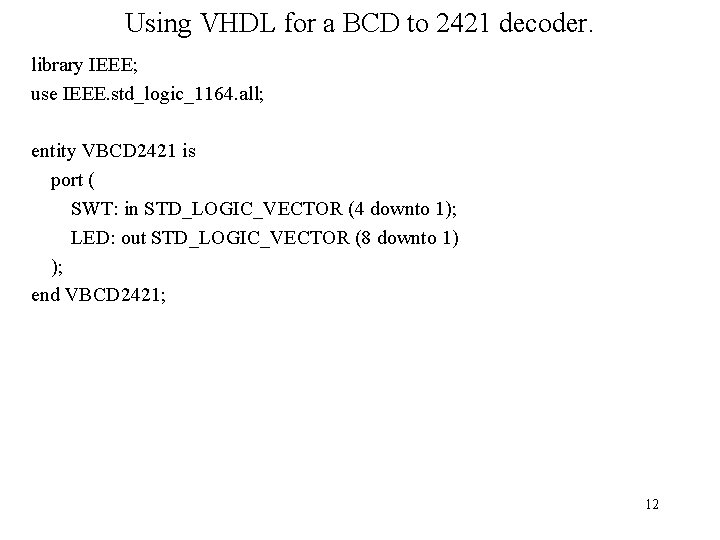

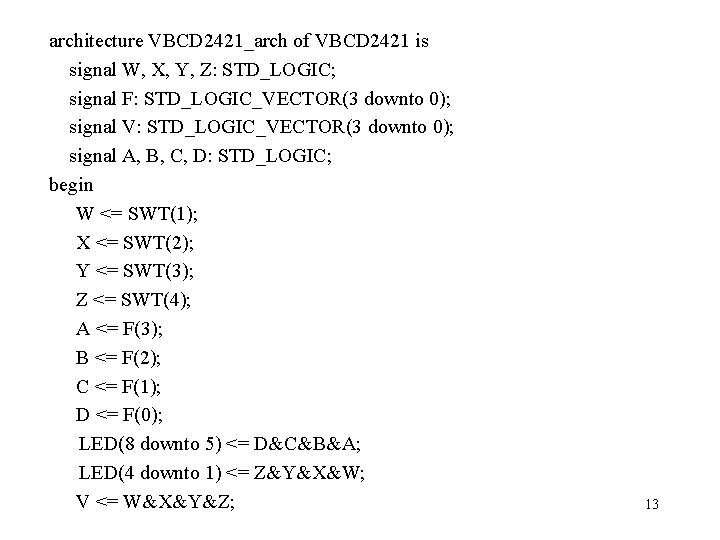

Using VHDL for a BCD to 2421 decoder. library IEEE; use IEEE. std_logic_1164. all; entity VBCD 2421 is port ( SWT: in STD_LOGIC_VECTOR (4 downto 1); LED: out STD_LOGIC_VECTOR (8 downto 1) ); end VBCD 2421; 12

architecture VBCD 2421_arch of VBCD 2421 is signal W, X, Y, Z: STD_LOGIC; signal F: STD_LOGIC_VECTOR(3 downto 0); signal V: STD_LOGIC_VECTOR(3 downto 0); signal A, B, C, D: STD_LOGIC; begin W <= SWT(1); X <= SWT(2); Y <= SWT(3); Z <= SWT(4); A <= F(3); B <= F(2); C <= F(1); D <= F(0); LED(8 downto 5) <= D&C&B&A; LED(4 downto 1) <= Z&Y&X&W; V <= W&X&Y&Z; 13

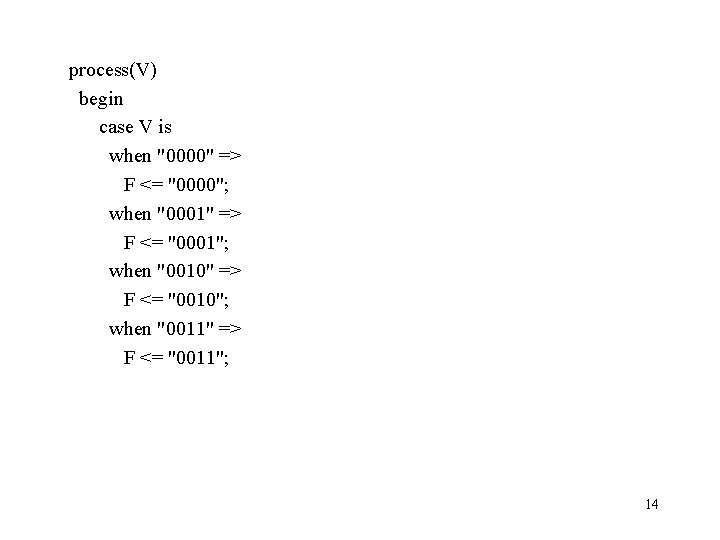

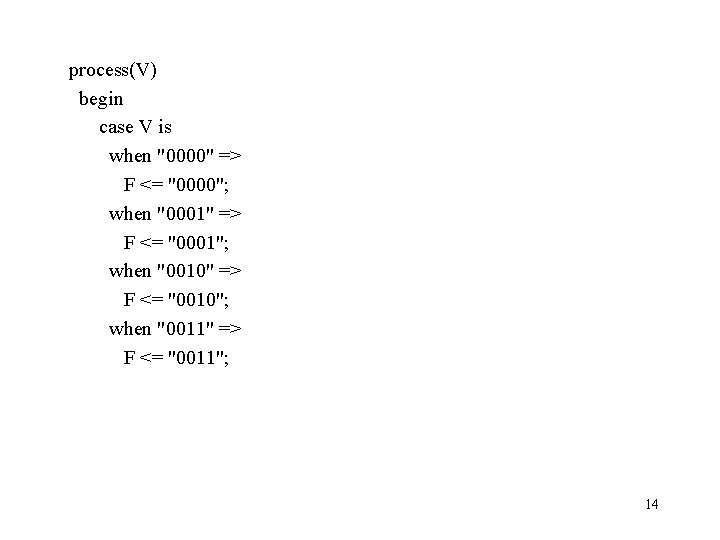

process(V) begin case V is when "0000" => F <= "0000"; when "0001" => F <= "0001"; when "0010" => F <= "0010"; when "0011" => F <= "0011"; 14

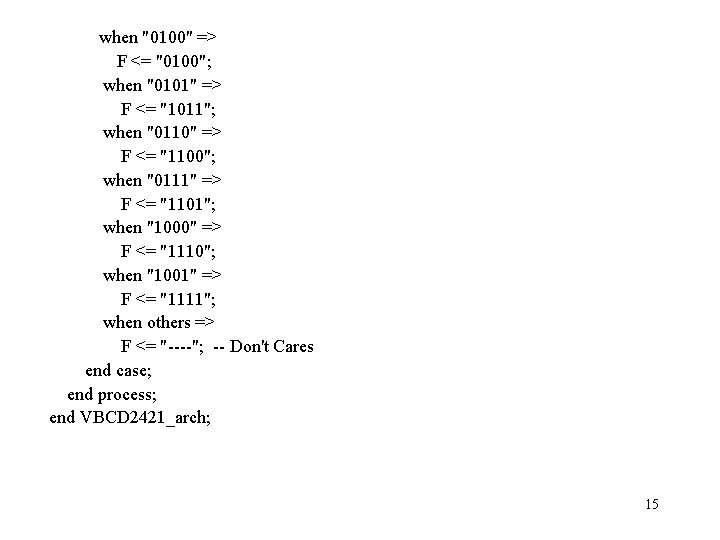

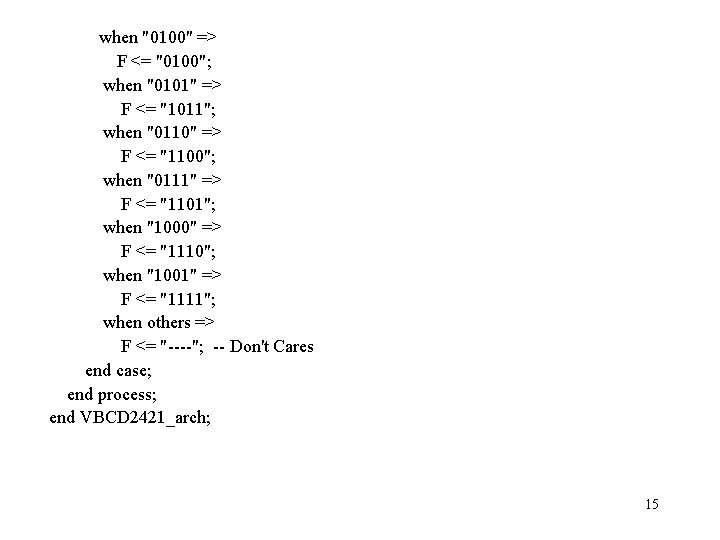

when "0100" => F <= "0100"; when "0101" => F <= "1011"; when "0110" => F <= "1100"; when "0111" => F <= "1101"; when "1000" => F <= "1110"; when "1001" => F <= "1111"; when others => F <= "----"; -- Don't Cares end case; end process; end VBCD 2421_arch; 15

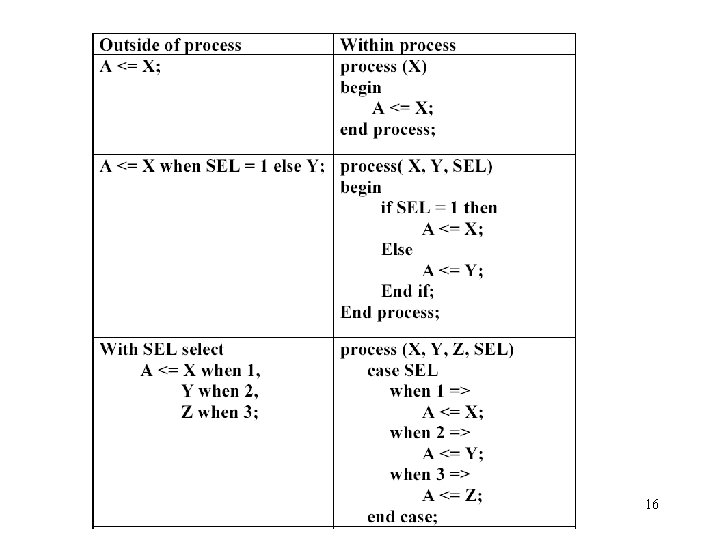

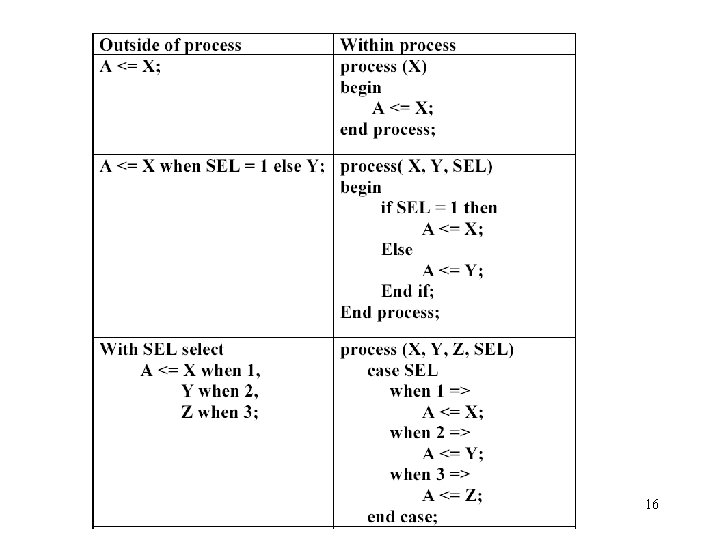

16