Cours VHDL Ing Mohamed MASMOUDI Mohamed masmoudialphatec com

![Déclarations d’une entité Circuit 1 rst q[N: 0] d[N: 0] co clk ENTITY circuit Déclarations d’une entité Circuit 1 rst q[N: 0] d[N: 0] co clk ENTITY circuit](https://slidetodoc.com/presentation_image_h/1c86774d70d4189eafe19cab22423167/image-18.jpg)

- Slides: 27

Cours VHDL Ing Mohamed MASMOUDI Mohamed. masmoudi@alphatec. com. tn

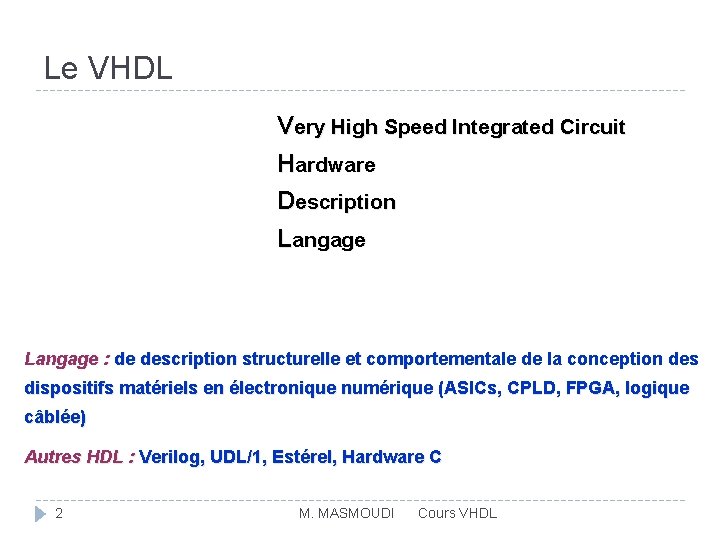

Le VHDL Very High Speed Integrated Circuit Hardware Description Langage : de description structurelle et comportementale de la conception des dispositifs matériels en électronique numérique (ASICs, CPLD, FPGA, logique câblée) Autres HDL : Verilog, UDL/1, Estérel, Hardware C 2 M. MASMOUDI Cours VHDL

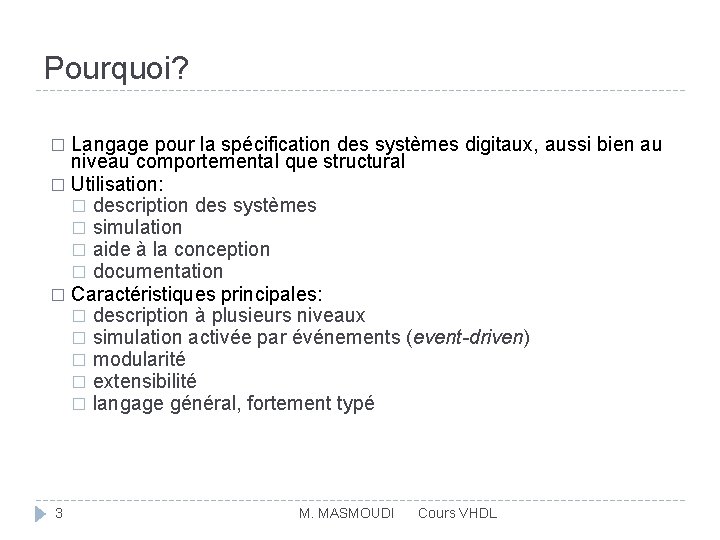

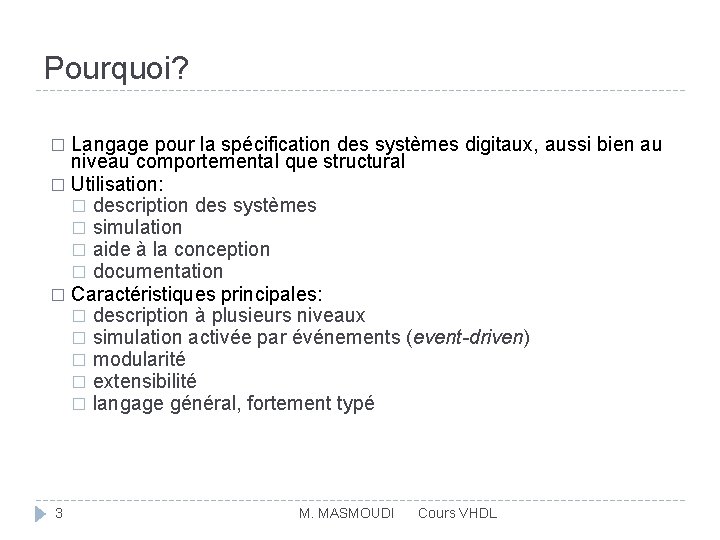

Pourquoi? Langage pour la spécification des systèmes digitaux, aussi bien au niveau comportemental que structural � Utilisation: � description des systèmes � simulation � aide à la conception � documentation � Caractéristiques principales: � description à plusieurs niveaux � simulation activée par événements (event-driven) � modularité � extensibilité � langage général, fortement typé � 3 M. MASMOUDI Cours VHDL

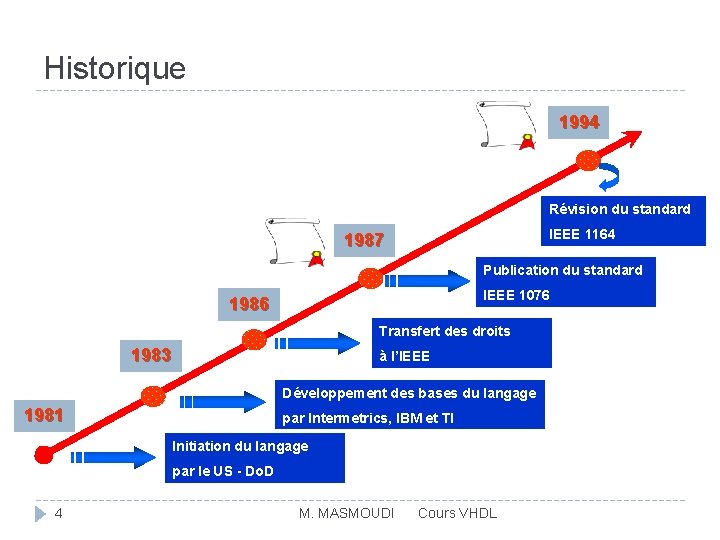

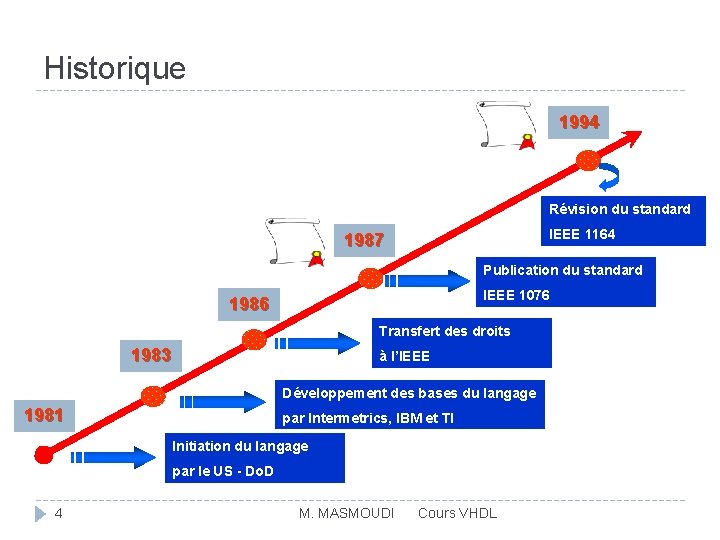

Historique 1994 Révision du standard IEEE 1164 1987 Publication du standard IEEE 1076 1986 Transfert des droits 1983 à l’IEEE Développement des bases du langage 1981 par Intermetrics, IBM et TI Initiation du langage par le US - Do. D 4 M. MASMOUDI Cours VHDL

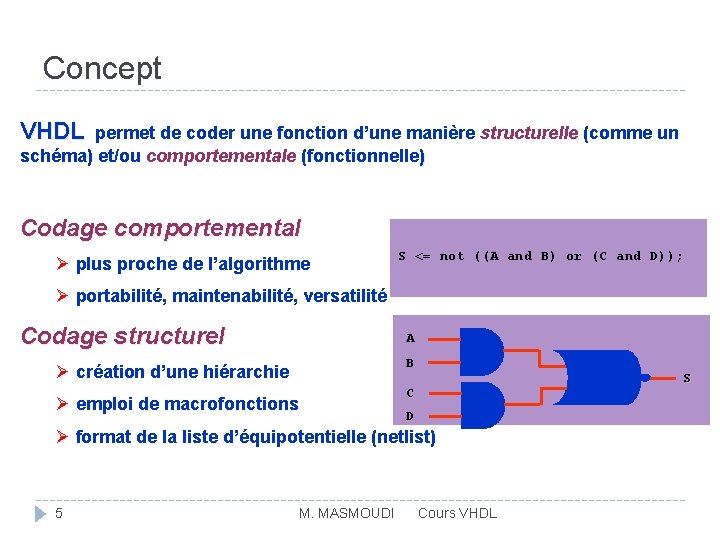

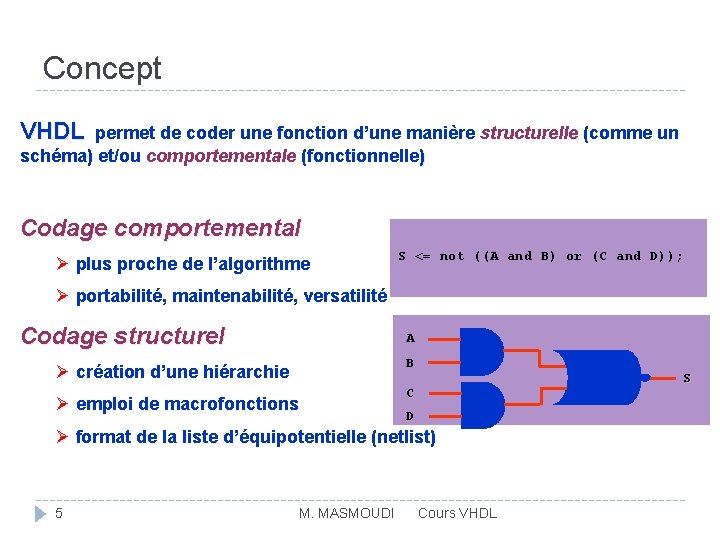

Concept VHDL permet de coder une fonction d’une manière structurelle (comme un schéma) et/ou comportementale (fonctionnelle) Codage comportemental Ø plus proche de l’algorithme S <= not ((A and B) or (C and D)); Ø portabilité, maintenabilité, versatilité Codage structurel A B Ø création d’une hiérarchie Ø emploi de macrofonctions S C D Ø format de la liste d’équipotentielle (netlist) 5 M. MASMOUDI Cours VHDL

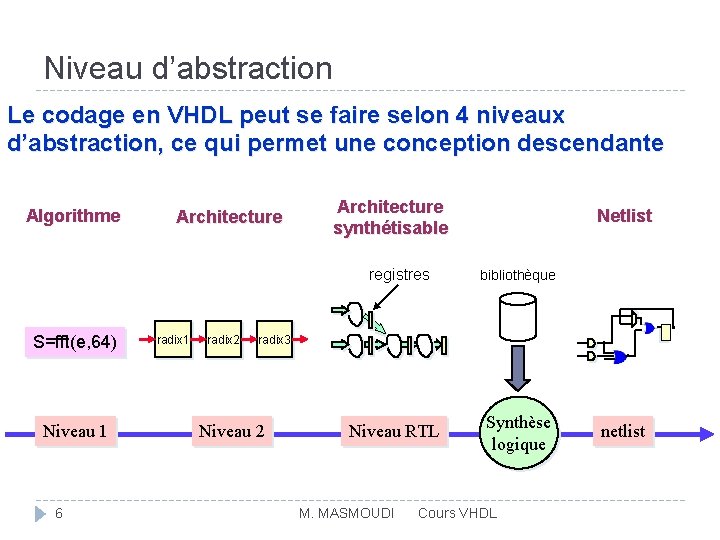

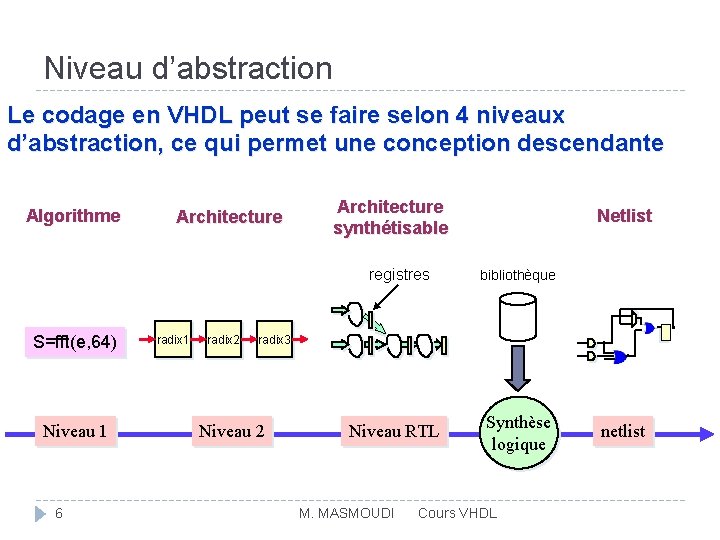

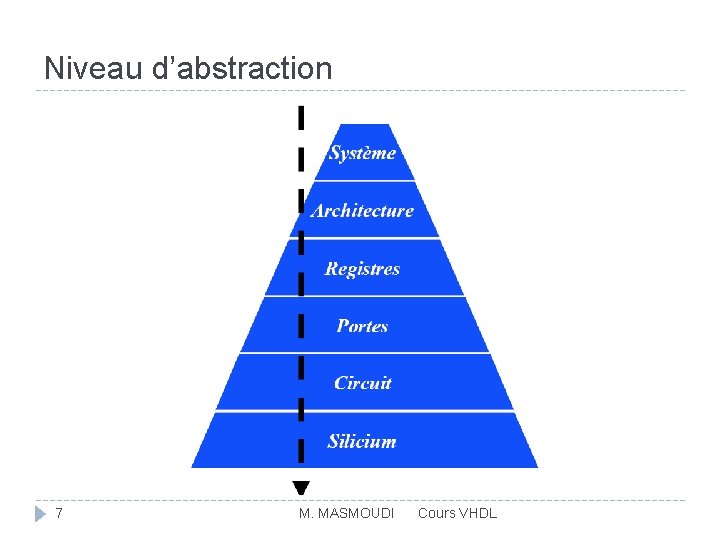

Niveau d’abstraction Le codage en VHDL peut se faire selon 4 niveaux d’abstraction, ce qui permet une conception descendante Algorithme Architecture synthétisable registres S=fft(e, 64) Niveau 1 6 radix 1 radix 2 Netlist bibliothèque radix 3 Niveau 2 Niveau RTL M. MASMOUDI Synthèse logique Cours VHDL netlist

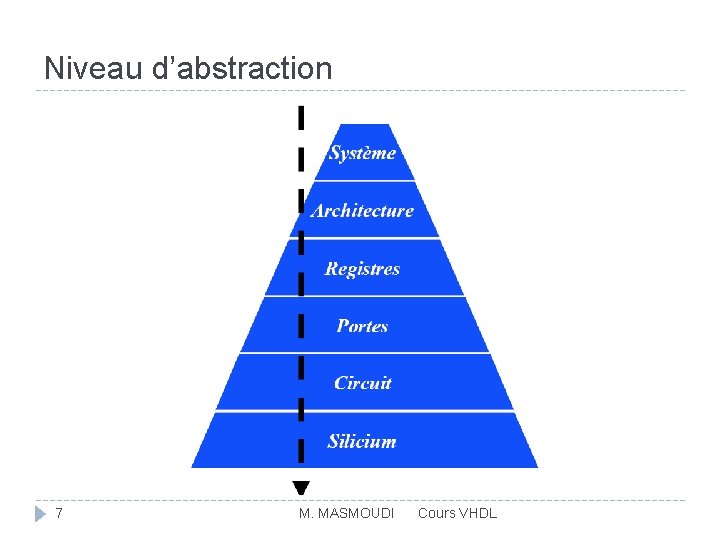

Niveau d’abstraction 7 M. MASMOUDI Cours VHDL

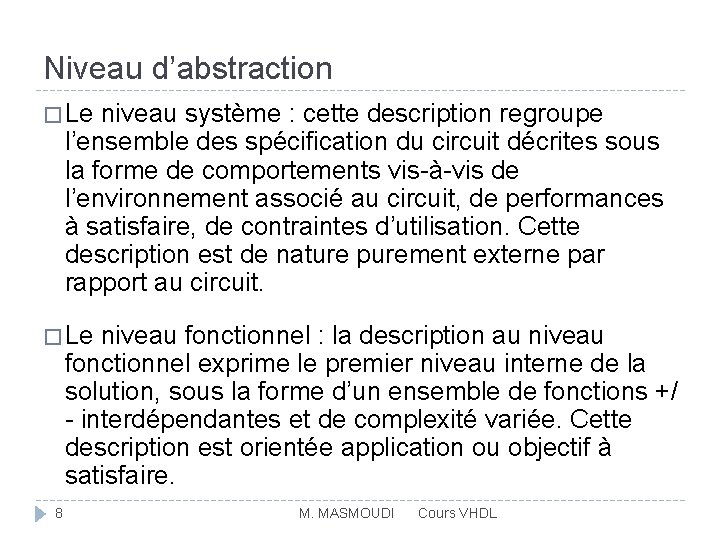

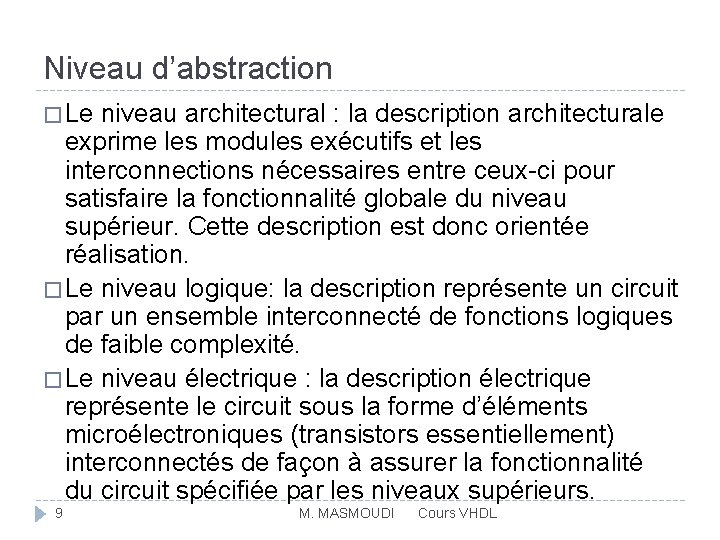

Niveau d’abstraction � Le niveau système : cette description regroupe l’ensemble des spécification du circuit décrites sous la forme de comportements vis-à-vis de l’environnement associé au circuit, de performances à satisfaire, de contraintes d’utilisation. Cette description est de nature purement externe par rapport au circuit. � Le niveau fonctionnel : la description au niveau fonctionnel exprime le premier niveau interne de la solution, sous la forme d’un ensemble de fonctions +/ - interdépendantes et de complexité variée. Cette description est orientée application ou objectif à satisfaire. 8 M. MASMOUDI Cours VHDL

Niveau d’abstraction � Le niveau architectural : la description architecturale exprime les modules exécutifs et les interconnections nécessaires entre ceux-ci pour satisfaire la fonctionnalité globale du niveau supérieur. Cette description est donc orientée réalisation. � Le niveau logique: la description représente un circuit par un ensemble interconnecté de fonctions logiques de faible complexité. � Le niveau électrique : la description électrique représente le circuit sous la forme d’éléments microélectroniques (transistors essentiellement) interconnectés de façon à assurer la fonctionnalité du circuit spécifiée par les niveaux supérieurs. 9 M. MASMOUDI Cours VHDL

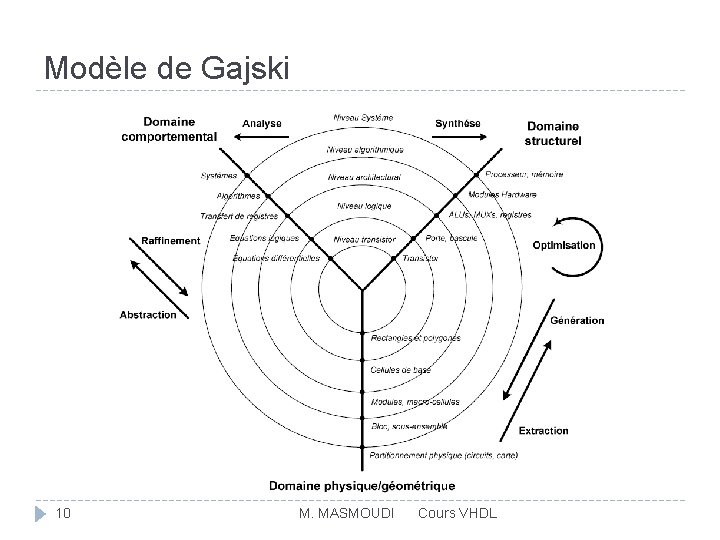

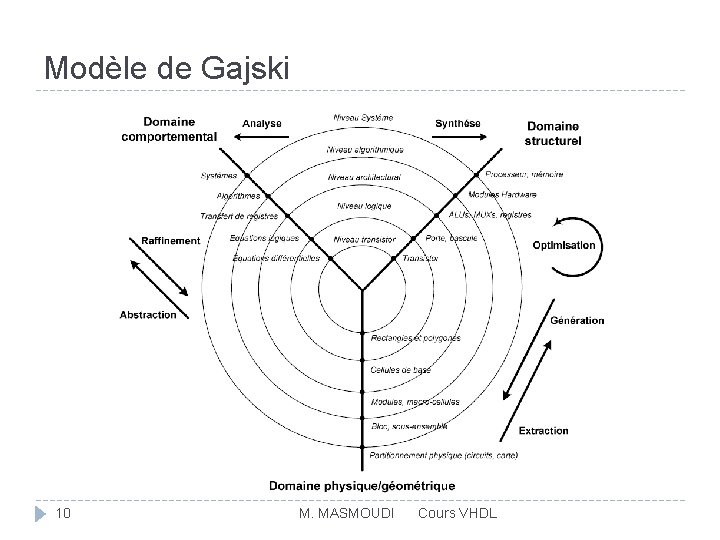

Modèle de Gajski 10 M. MASMOUDI Cours VHDL

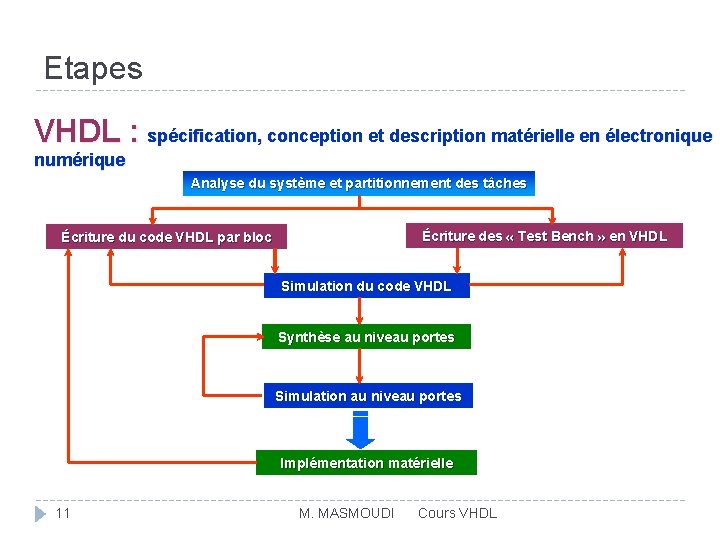

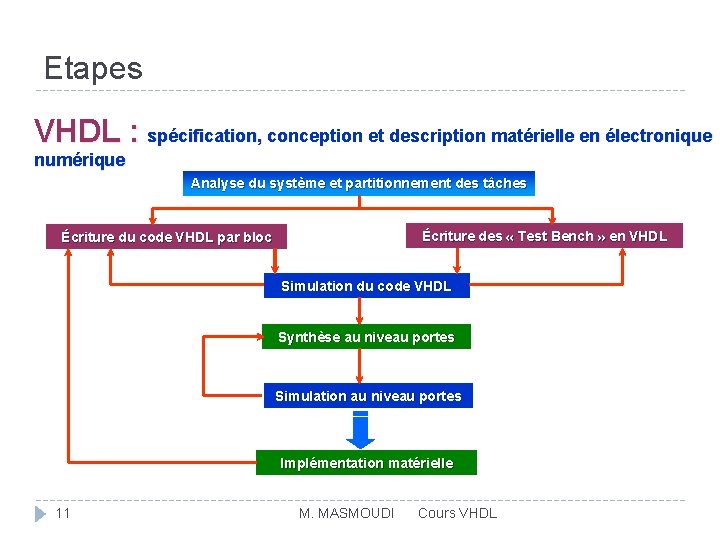

Etapes VHDL : spécification, conception et description matérielle en électronique numérique Analyse du système et partitionnement des tâches Écriture des « Test Bench » en VHDL Écriture du code VHDL par bloc Simulation du code VHDL Synthèse au niveau portes Simulation au niveau portes Implémentation matérielle 11 M. MASMOUDI Cours VHDL

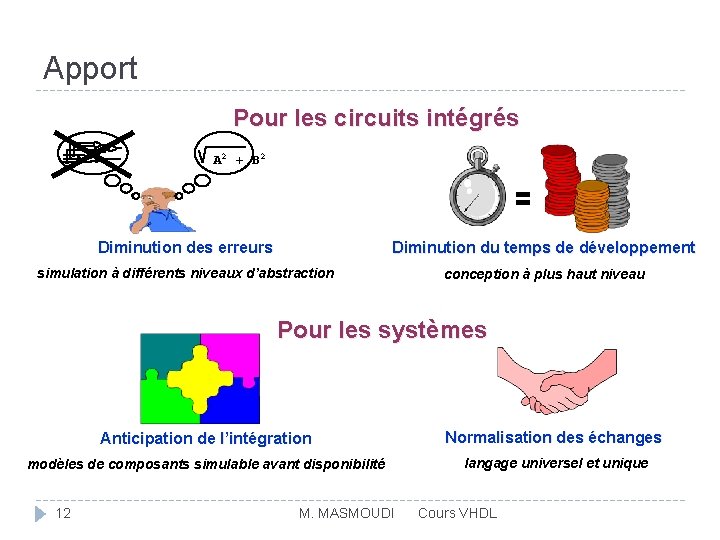

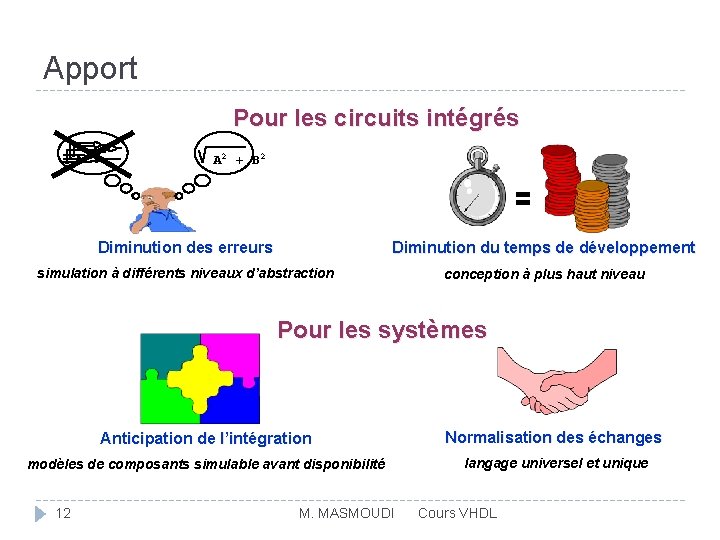

Apport Pour les circuits intégrés A 2 + B 2 Diminution des erreurs Diminution du temps de développement simulation à différents niveaux d’abstraction conception à plus haut niveau Pour les systèmes Anticipation de l’intégration Normalisation des échanges modèles de composants simulable avant disponibilité langage universel et unique 12 M. MASMOUDI Cours VHDL

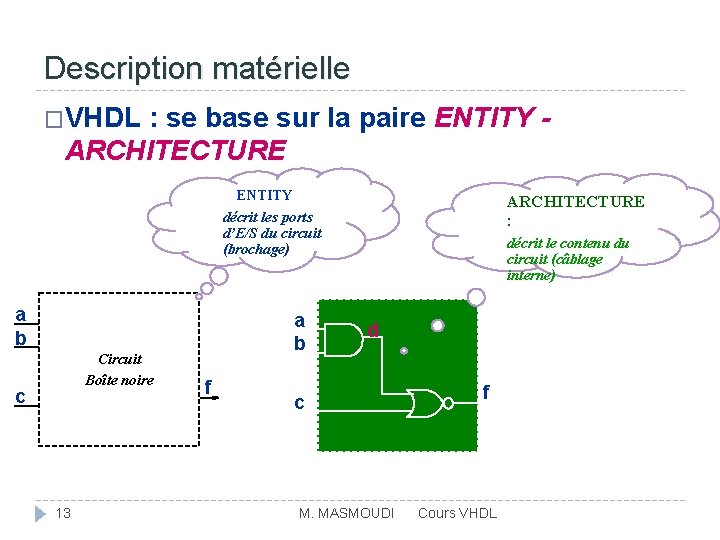

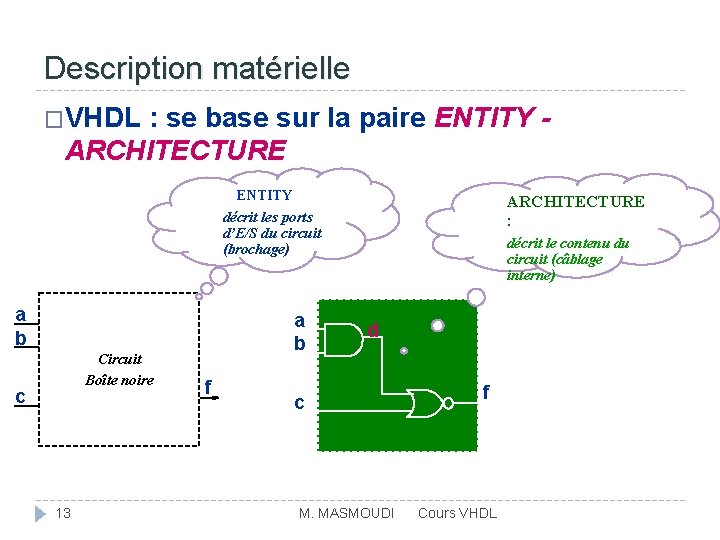

Description matérielle �VHDL : se base sur la paire ENTITY - ARCHITECTURE ENTITY décrit les ports d’E/S du circuit (brochage) a b d Circuit Boîte noire c 13 f ARCHITECTURE : décrit le contenu du circuit (câblage interne) d c M. MASMOUDI f Cours VHDL

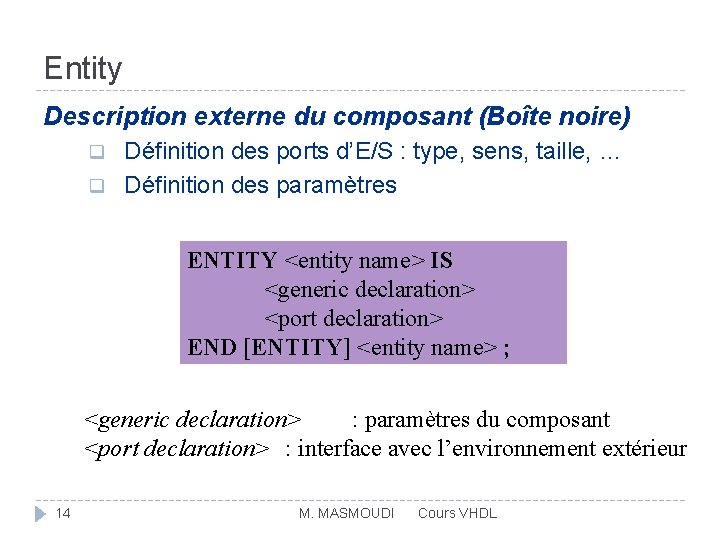

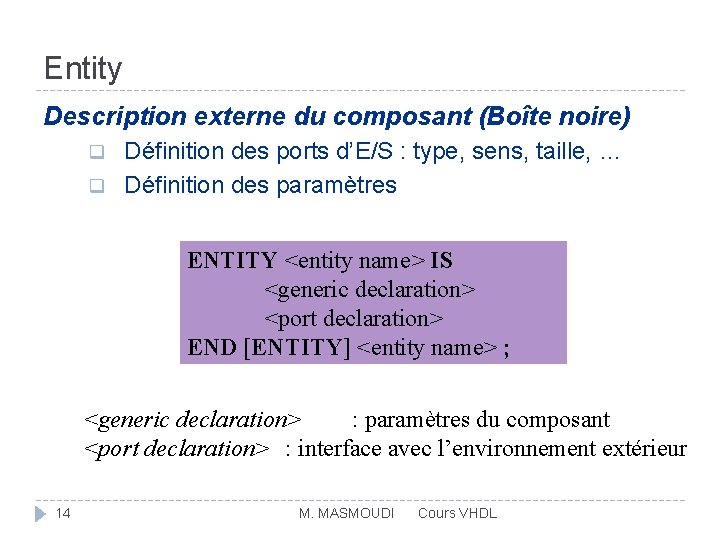

Entity Description externe du composant (Boîte noire) q q Définition des ports d’E/S : type, sens, taille, … Définition des paramètres ENTITY <entity name> IS <generic declaration> <port declaration> END [ENTITY] <entity name> ; <generic declaration> : paramètres du composant <port declaration> : interface avec l’environnement extérieur 14 M. MASMOUDI Cours VHDL

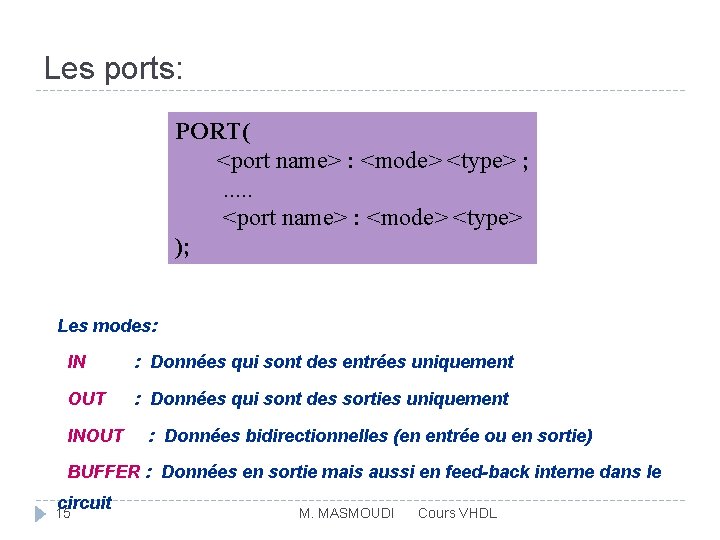

Les ports: PORT( <port name> : <mode> <type> ; . . . <port name> : <mode> <type> ); Les modes: IN : Données qui sont des entrées uniquement OUT : Données qui sont des sorties uniquement INOUT : Données bidirectionnelles (en entrée ou en sortie) BUFFER : Données en sortie mais aussi en feed-back interne dans le circuit 15 M. MASMOUDI Cours VHDL

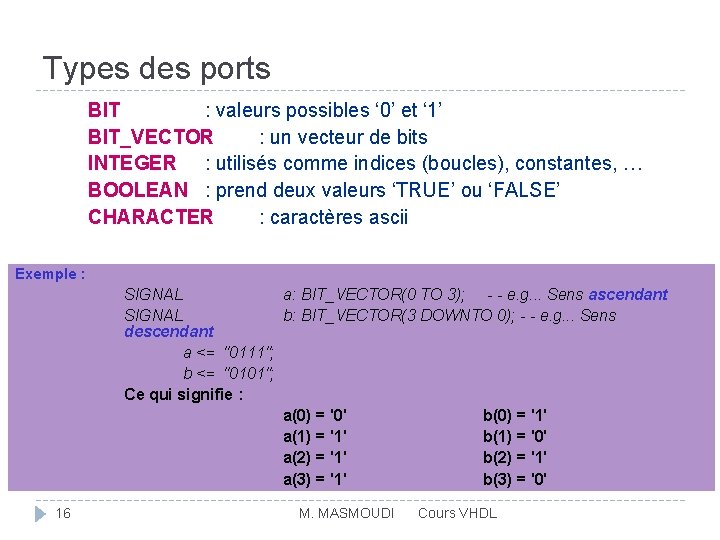

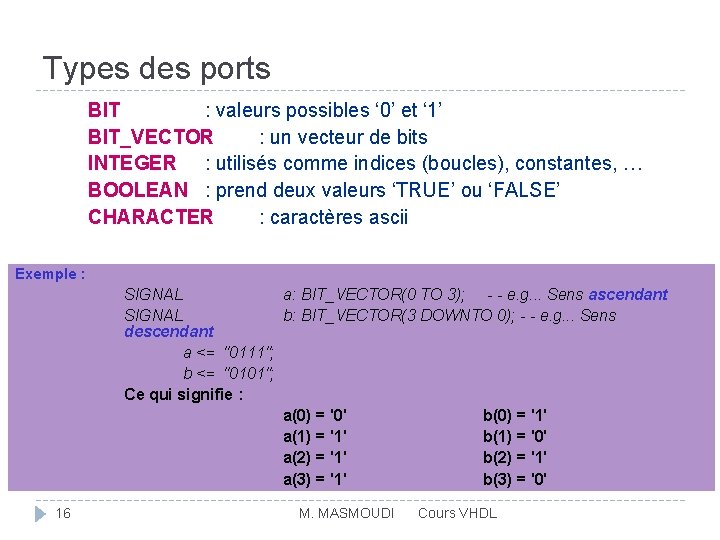

Types des ports BIT : valeurs possibles ‘ 0’ et ‘ 1’ BIT_VECTOR : un vecteur de bits INTEGER : utilisés comme indices (boucles), constantes, … BOOLEAN : prend deux valeurs ‘TRUE’ ou ‘FALSE’ CHARACTER : caractères ascii Exemple : SIGNAL a: BIT_VECTOR(0 TO 3); - - e. g. . . Sens ascendant SIGNAL b: BIT_VECTOR(3 DOWNTO 0); - - e. g. . . Sens descendant a <= "0111"; b <= "0101"; Ce qui signifie : a(0) = '0' b(0) = '1' a(1) = '1' b(1) = '0' a(2) = '1' b(2) = '1' a(3) = '1' b(3) = '0' 16 M. MASMOUDI Cours VHDL

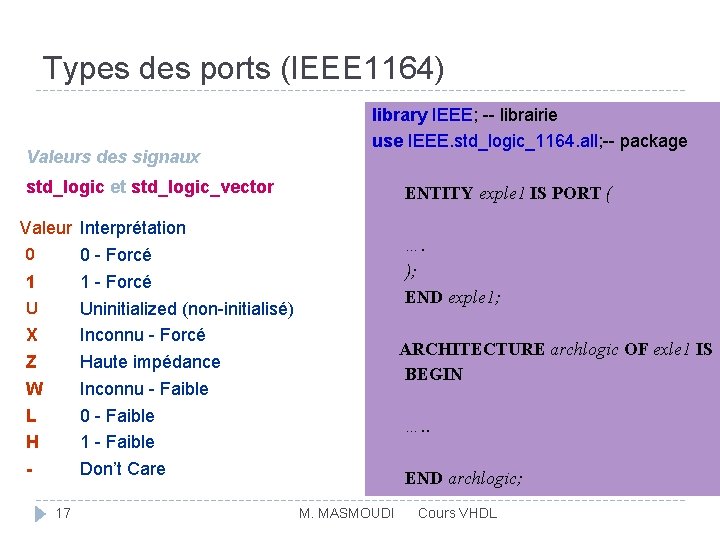

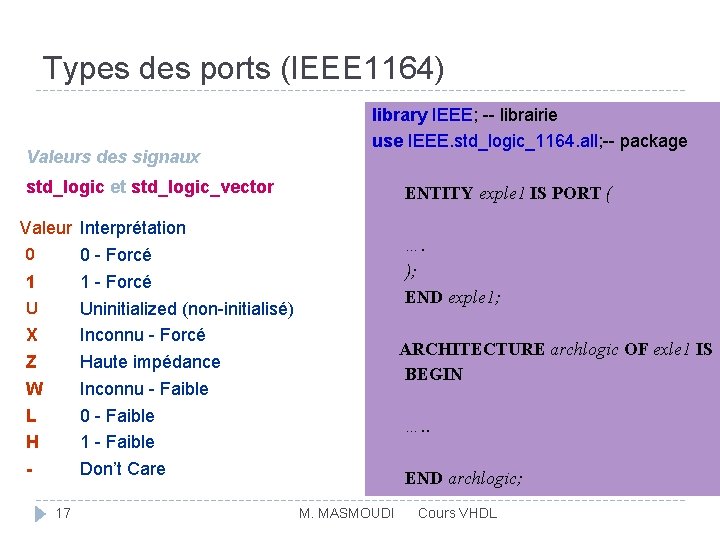

Types des ports (IEEE 1164) Valeurs des signaux library IEEE; -- librairie use IEEE. std_logic_1164. all; -- package std_logic et std_logic_vector ENTITY exple 1 IS PORT ( Valeur Interprétation 0 0 - Forcé 1 1 - Forcé U Uninitialized (non-initialisé) X Inconnu - Forcé Z Haute impédance W Inconnu - Faible L 0 - Faible H 1 - Faible Don’t Care 17 …. ); END exple 1; ARCHITECTURE archlogic OF exle 1 IS BEGIN …. . END archlogic; M. MASMOUDI Cours VHDL

![Déclarations dune entité Circuit 1 rst qN 0 dN 0 co clk ENTITY circuit Déclarations d’une entité Circuit 1 rst q[N: 0] d[N: 0] co clk ENTITY circuit](https://slidetodoc.com/presentation_image_h/1c86774d70d4189eafe19cab22423167/image-18.jpg)

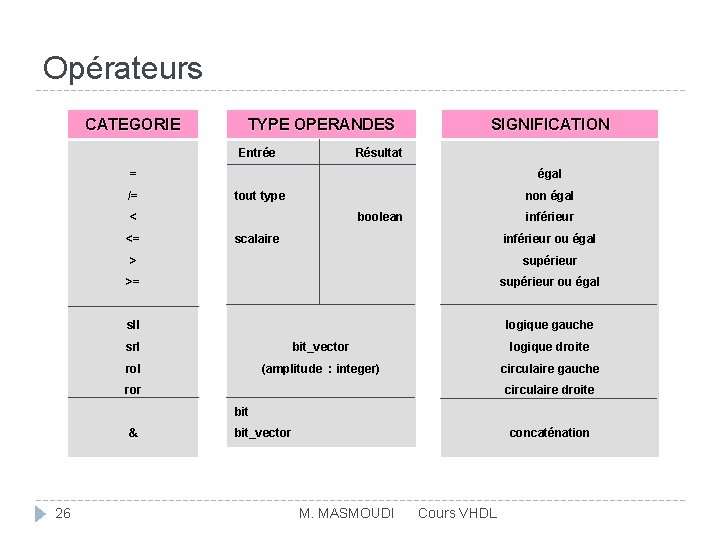

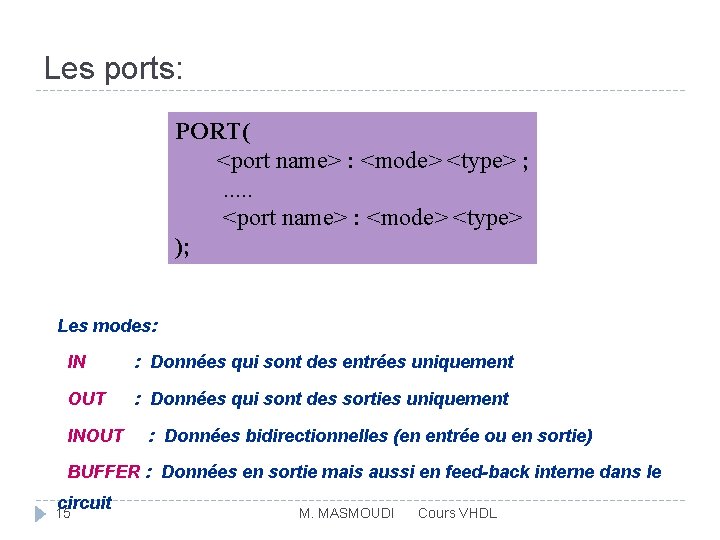

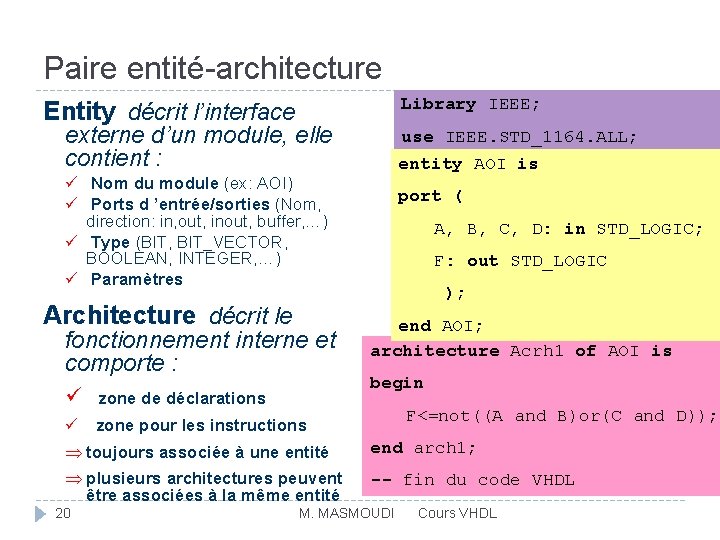

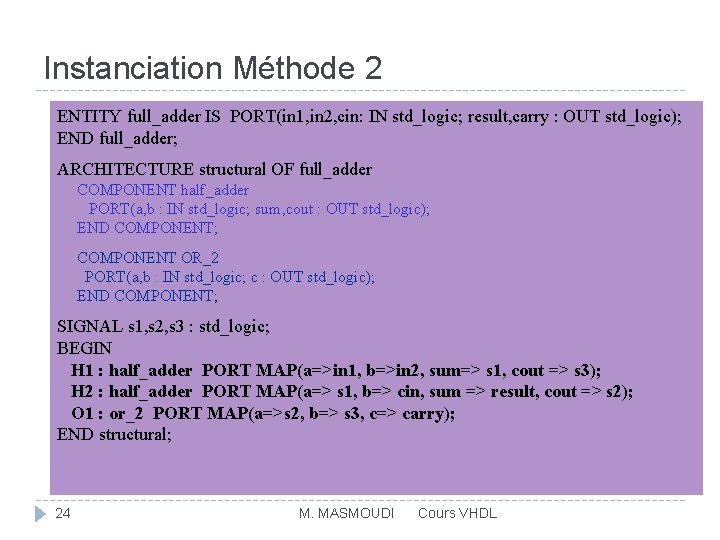

Déclarations d’une entité Circuit 1 rst q[N: 0] d[N: 0] co clk ENTITY circuit 1 IS GENERIC (N: INTEGER: =7); 18 PORT ( clk, rst: d: q: co: END circuit 1; IN BIT; IN BIT_VECTOR(7 DOWNTO 0); OUT BIT); M. MASMOUDI Cours VHDL

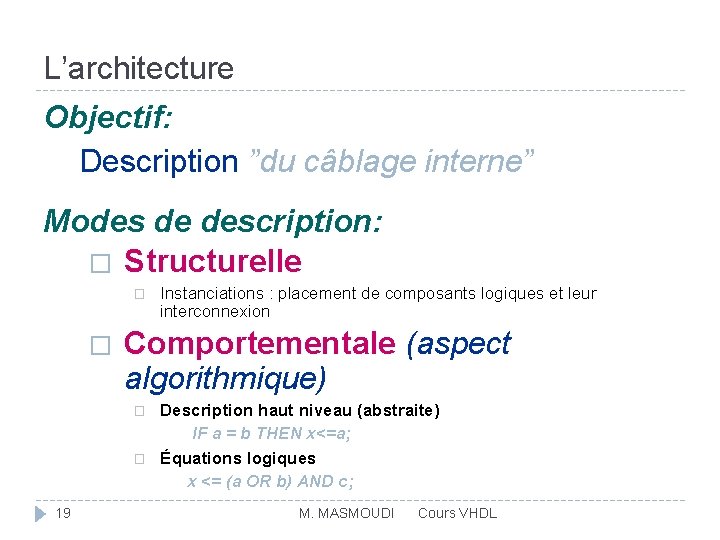

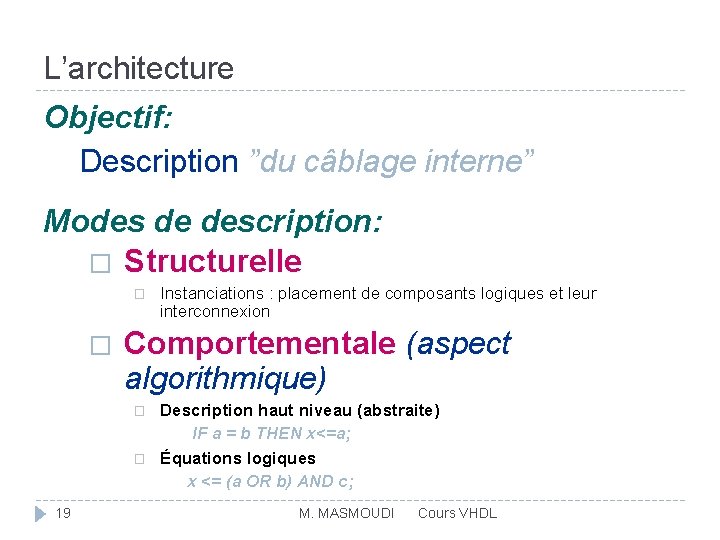

L’architecture Objectif: Description ”du câblage interne” Modes de description: � Structurelle � � Instanciations : placement de composants logiques et leur interconnexion Comportementale (aspect algorithmique) Description haut niveau (abstraite) IF a = b THEN x<=a; � Équations logiques x <= (a OR b) AND c; � 19 M. MASMOUDI Cours VHDL

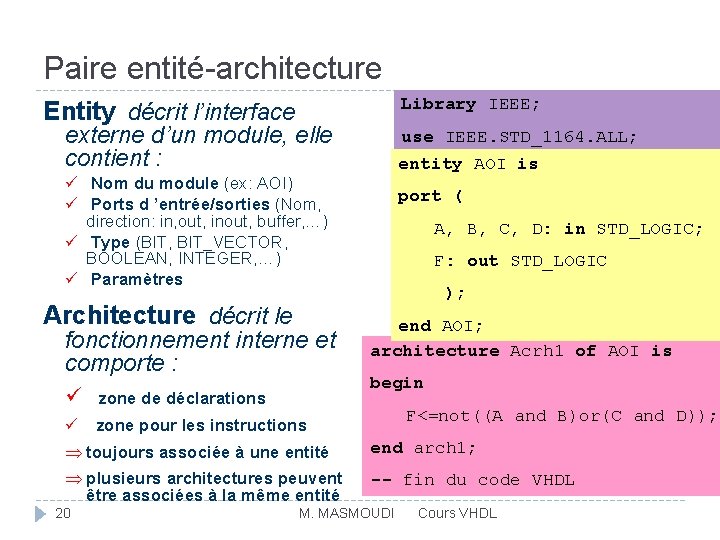

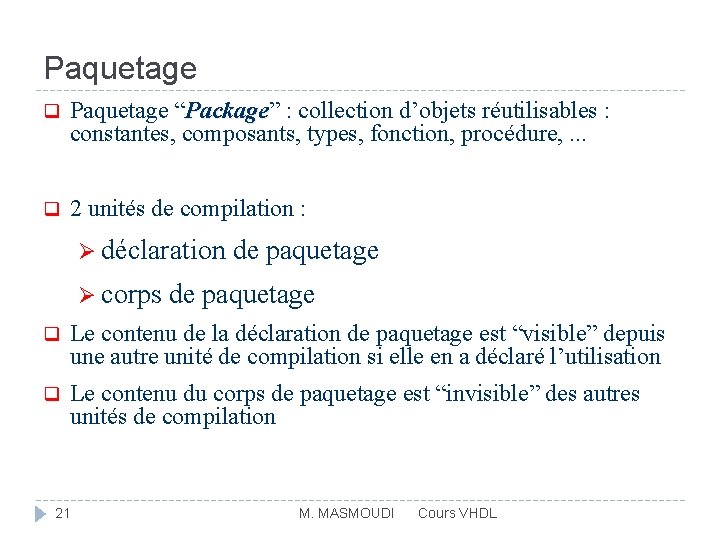

Paire entité-architecture Library IEEE; Entity décrit l’interface externe d’un module, elle contient : use IEEE. STD_1164. ALL; entity AOI is ü Nom du module (ex: AOI) ü Ports d ’entrée/sorties (Nom, direction: in, out, inout, buffer, …) ü Type (BIT, BIT_VECTOR, BOOLEAN, INTEGER, …) ü Paramètres Architecture décrit le fonctionnement interne et comporte : ü zone de déclarations port ( A, B, C, D: in STD_LOGIC; F: out STD_LOGIC ); end AOI; architecture Acrh 1 of AOI is begin F<=not((A and B)or(C and D)); ü zone pour les instructions Þ toujours associée à une entité end arch 1; Þ plusieurs architectures peuvent être associées à la même entité -- fin du code VHDL 20 M. MASMOUDI Cours VHDL

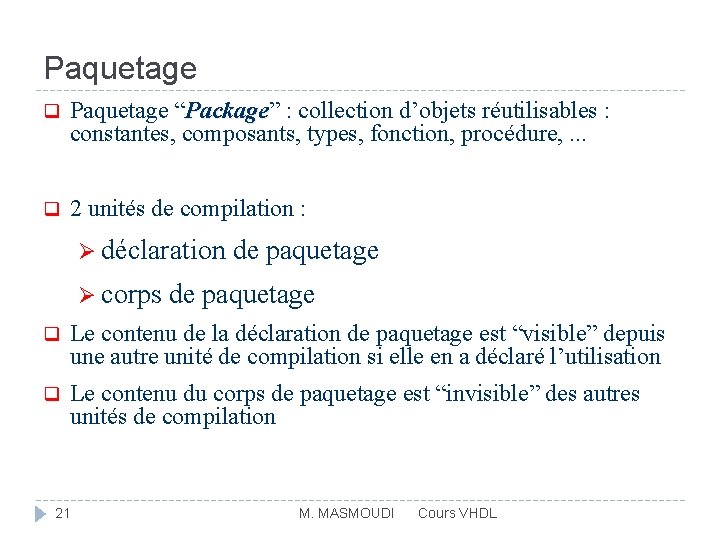

Paquetage q Paquetage “Package” Package : collection d’objets réutilisables : constantes, composants, types, fonction, procédure, . . . q 2 unités de compilation : Ø déclaration Ø corps de paquetage q Le contenu de la déclaration de paquetage est “visible” depuis une autre unité de compilation si elle en a déclaré l’utilisation q Le contenu du corps de paquetage est “invisible” des autres unités de compilation 21 M. MASMOUDI Cours VHDL

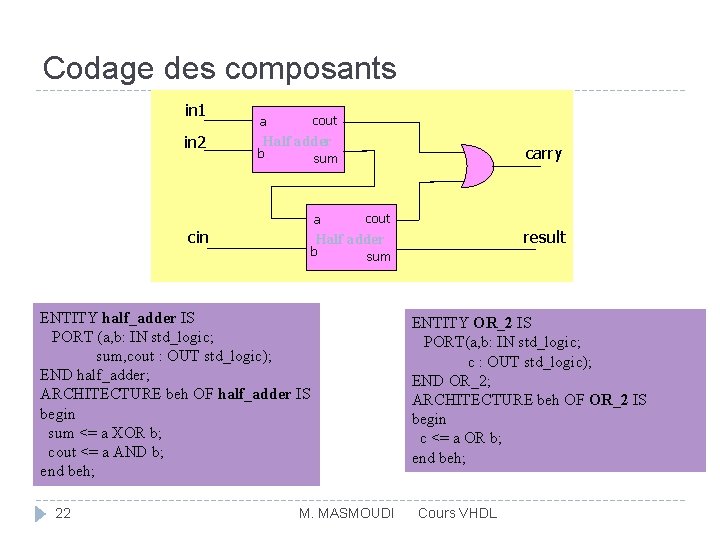

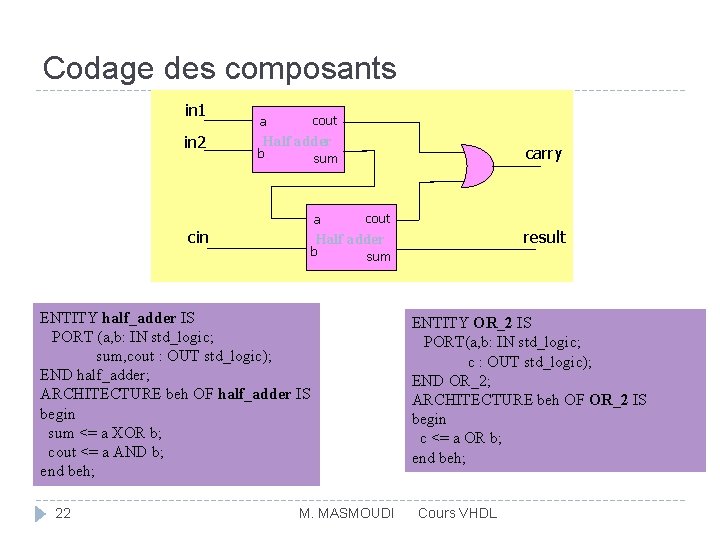

Codage des composants in 1 in 2 cout a Half adder b carry sum a cin cout b sum ENTITY half_adder IS PORT (a, b: IN std_logic; sum, cout : OUT std_logic); END half_adder; ARCHITECTURE beh OF half_adder IS begin sum <= a XOR b; cout <= a AND b; end beh; 22 result Half adder M. MASMOUDI ENTITY OR_2 IS PORT(a, b: IN std_logic; c : OUT std_logic); END OR_2; ARCHITECTURE beh OF OR_2 IS begin c <= a OR b; end beh; Cours VHDL

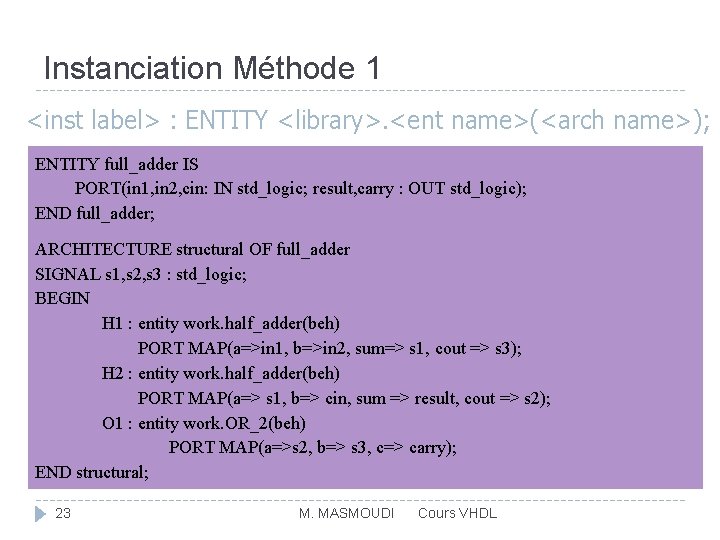

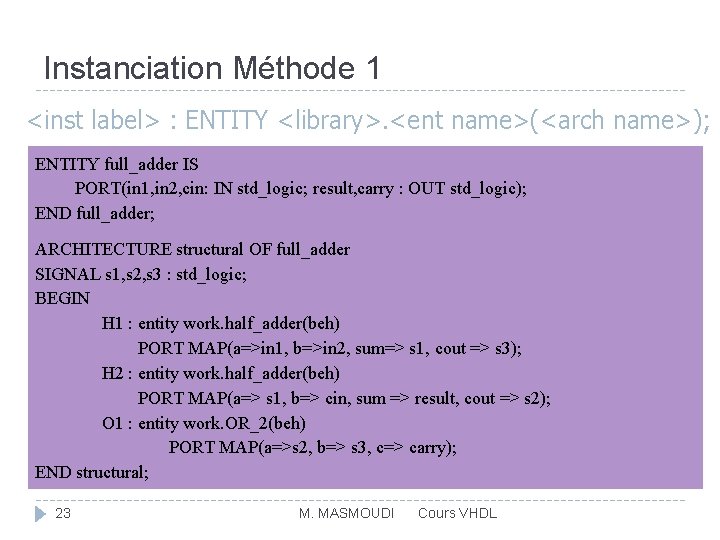

Instanciation Méthode 1 <inst label> : ENTITY <library>. <ent name>(<arch name>); ENTITY full_adder IS PORT(in 1, in 2, cin: IN std_logic; result, carry : OUT std_logic); END full_adder; ARCHITECTURE structural OF full_adder SIGNAL s 1, s 2, s 3 : std_logic; BEGIN H 1 : entity work. half_adder(beh) PORT MAP(a=>in 1, b=>in 2, sum=> s 1, cout => s 3); H 2 : entity work. half_adder(beh) PORT MAP(a=> s 1, b=> cin, sum => result, cout => s 2); O 1 : entity work. OR_2(beh) PORT MAP(a=>s 2, b=> s 3, c=> carry); END structural; 23 M. MASMOUDI Cours VHDL

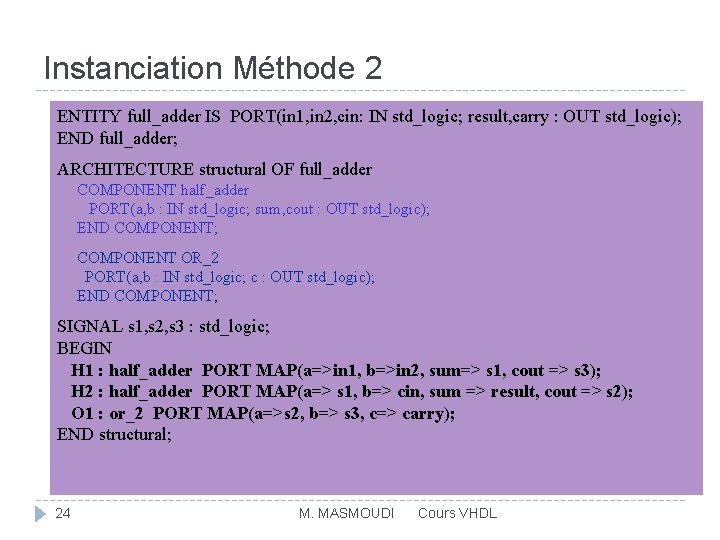

Instanciation Méthode 2 ENTITY full_adder IS PORT(in 1, in 2, cin: IN std_logic; result, carry : OUT std_logic); END full_adder; ARCHITECTURE structural OF full_adder COMPONENT half_adder PORT(a, b : IN std_logic; sum, cout : OUT std_logic); END COMPONENT; COMPONENT OR_2 PORT(a, b : IN std_logic; c : OUT std_logic); END COMPONENT; SIGNAL s 1, s 2, s 3 : std_logic; BEGIN H 1 : half_adder PORT MAP(a=>in 1, b=>in 2, sum=> s 1, cout => s 3); H 2 : half_adder PORT MAP(a=> s 1, b=> cin, sum => result, cout => s 2); O 1 : or_2 PORT MAP(a=>s 2, b=> s 3, c=> carry); END structural; 24 M. MASMOUDI Cours VHDL

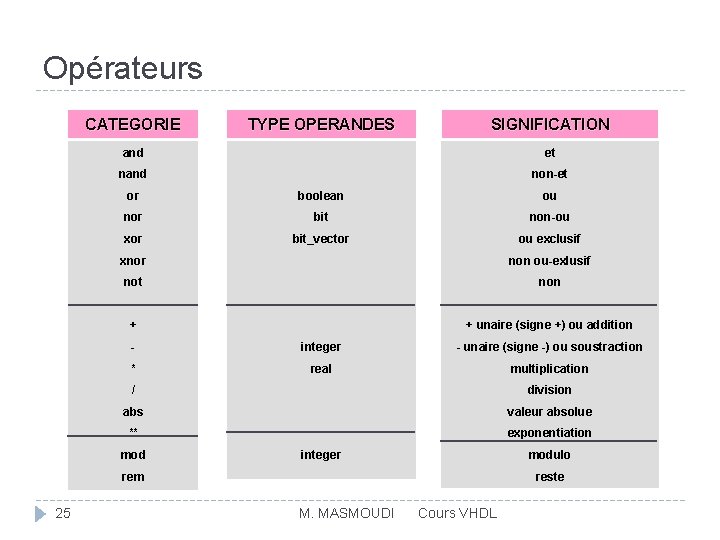

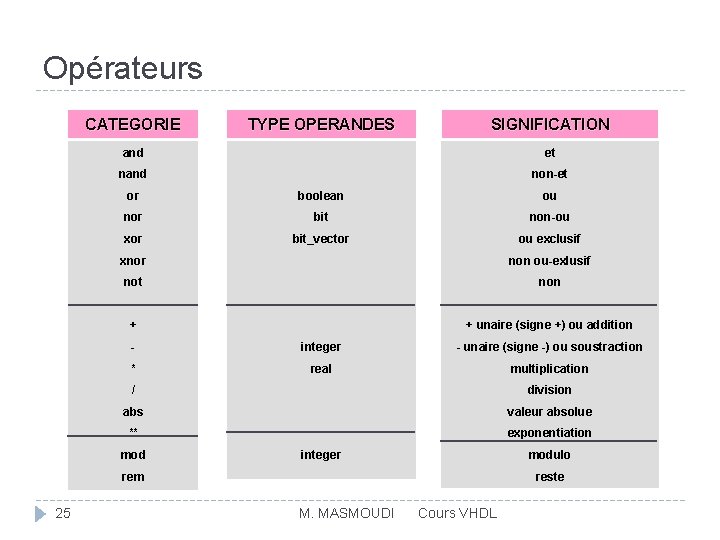

Opérateurs CATEGORIE TYPE OPERANDES SIGNIFICATION and et nand non-et or boolean ou nor bit non-ou xor bit_vector ou exclusif xnor non ou-exlusif not non + + unaire (signe +) ou addition - integer - unaire (signe -) ou soustraction * real multiplication / division abs valeur absolue ** exponentiation mod integer modulo rem 25 reste M. MASMOUDI Cours VHDL

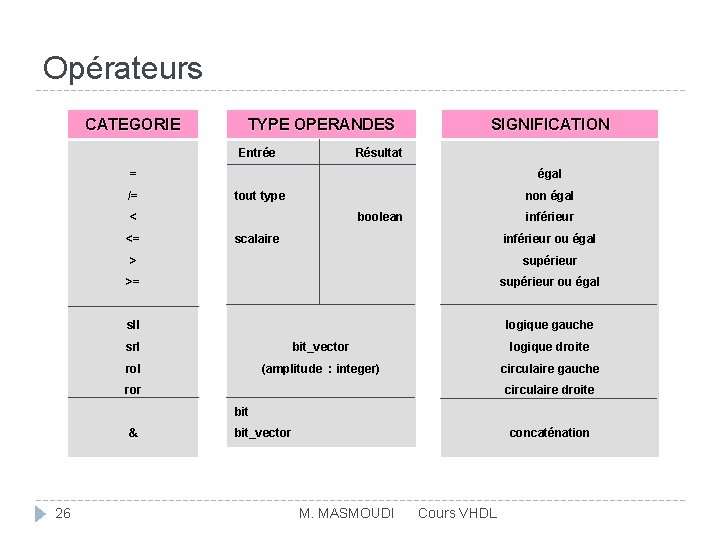

Opérateurs CATEGORIE TYPE OPERANDES SIGNIFICATION Entrée Résultat = égal /= tout type non égal < boolean inférieur <= scalaire inférieur ou égal > supérieur >= supérieur ou égal sll logique gauche srl bit_vector logique droite rol (amplitude : integer) circulaire gauche ror circulaire droite bit & 26 bit_vector concaténation M. MASMOUDI Cours VHDL

27 M. MASMOUDI Cours VHDL