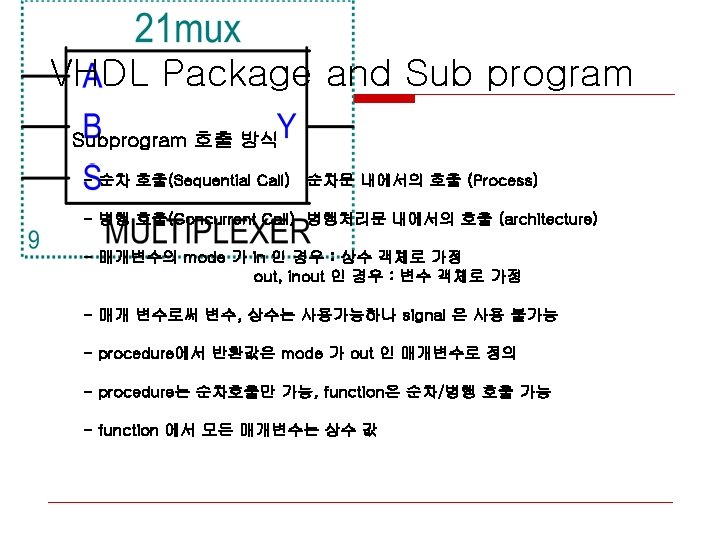

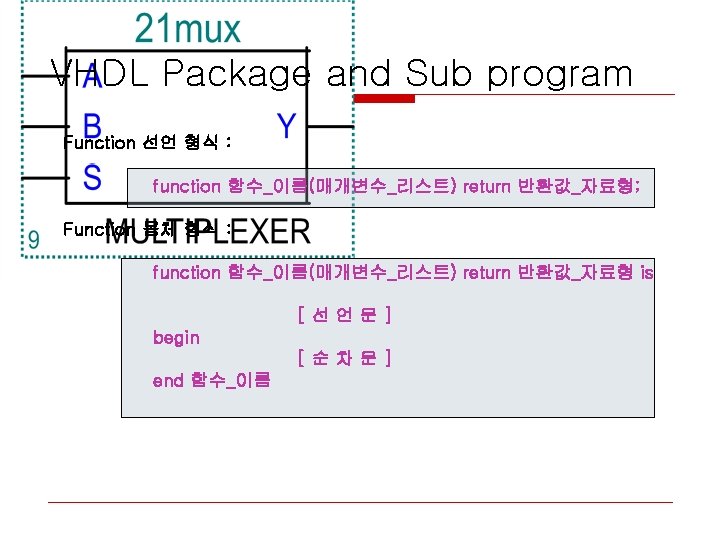

VHDL Package and Sub program Library package VHDL

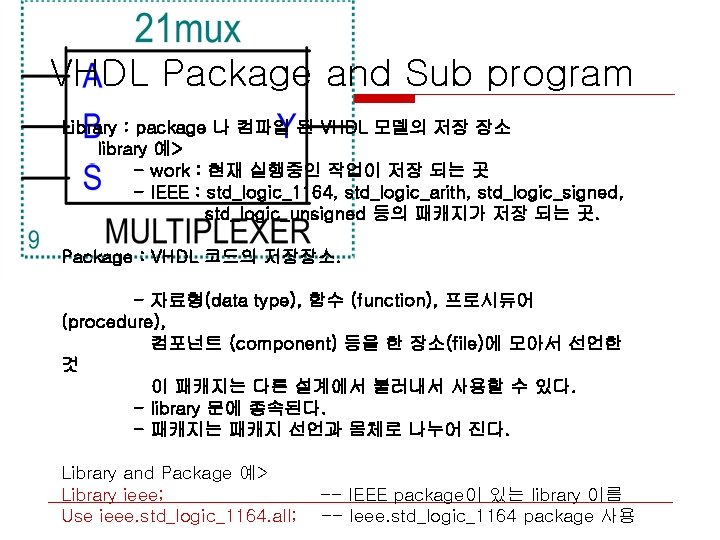

VHDL Package and Sub program Library : package 나 컴파일 된 VHDL 모델의 저장 장소 library 예> - work : 현재 실행중인 작업이 저장 되는 곳 - IEEE : std_logic_1164, std_logic_arith, std_logic_signed, std_logic_unsigned 등의 패캐지가 저장 되는 곳. Package : VHDL 코드의 저장장소. - 자료형(data type), 함수 (function), 프로시듀어 (procedure), 컴포넌트 (component) 등을 한 장소(file)에 모아서 선언한 것 이 패캐지는 다른 설계에서 불러내서 사용할 수 있다. - library 문에 종속된다. - 패캐지는 패캐지 선언과 몸체로 나누어 진다. Library and Package 예> Library ieee; Use ieee. std_logic_1164. all; -- IEEE package이 있는 library 이름 -- Ieee. std_logic_1164 package 사용

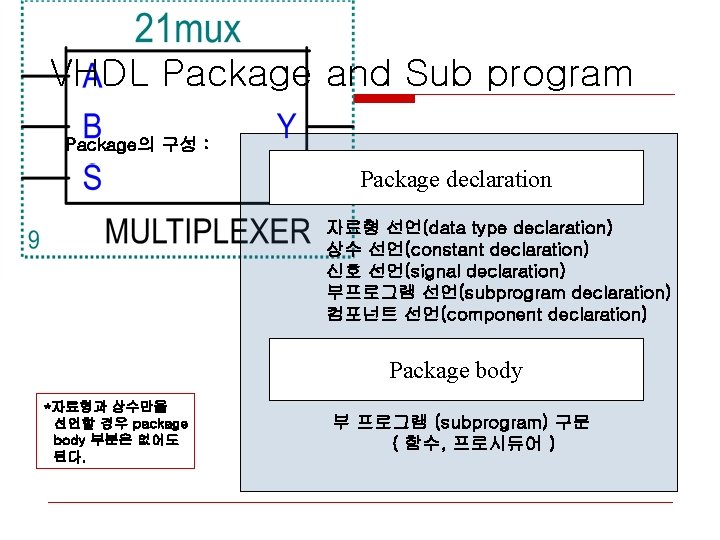

VHDL Package and Sub program Package의 구성 : Package declaration 자료형 선언(data type declaration) 상수 선언(constant declaration) 신호 선언(signal declaration) 부프로그램 선언(subprogram declaration) 컴포넌트 선언(component declaration) Package body *자료형과 상수만을 선언할 경우 package body 부분은 없어도 된다. 부 프로그램 (subprogram) 구문 ( 함수, 프로시듀어 )

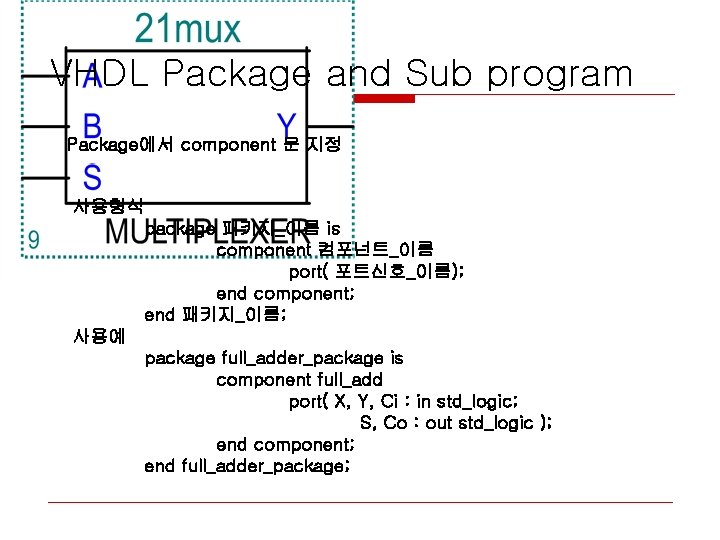

VHDL Package and Sub program Package에서 component 문 지정 사용형식 package 패키지_이름 is component 컴포넌트_이름 port( 포트신호_이름); end component; end 패키지_이름; 사용예 package full_adder_package is component full_add port( X, Y, Ci : in std_logic; S, Co : out std_logic ); end component; end full_adder_package;

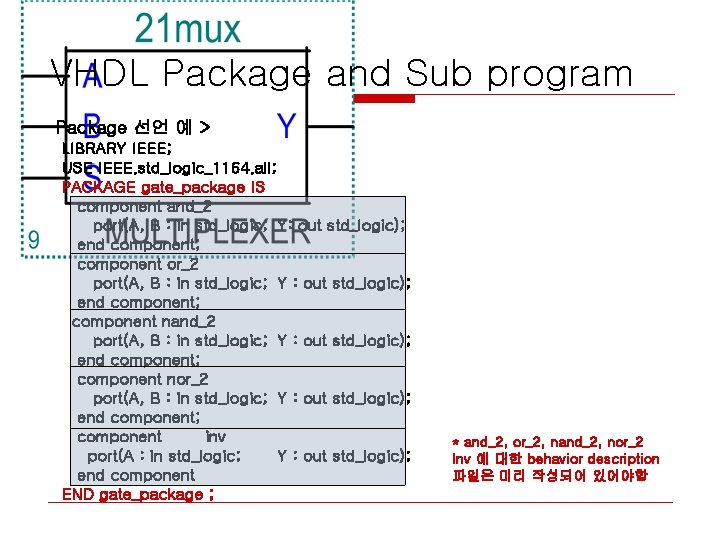

VHDL Package and Sub program Package 선언 예 > LIBRARY IEEE; USE IEEE. std_logic_1164. all; PACKAGE gate_package IS component and_2 port(A, B : in std_logic; Y: out std_logic); end component; component or_2 port(A, B : in std_logic; Y : out std_logic); end component; component nand_2 port(A, B : in std_logic; Y : out std_logic); end component; component nor_2 port(A, B : in std_logic; Y : out std_logic); end component; component inv port(A : in std_logic; Y : out std_logic); end component END gate_package ; * and_2, or_2, nand_2, nor_2 Inv 에 대한 behavior description 파일은 미리 작성되어 있어야함

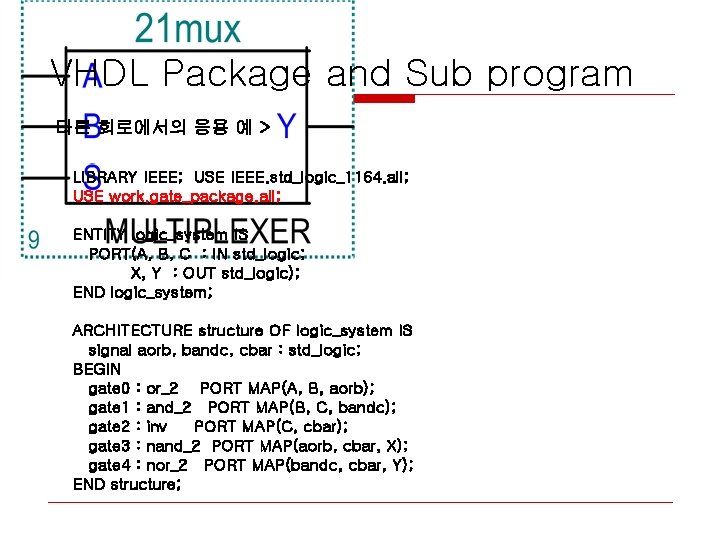

VHDL Package and Sub program 다른 회로에서의 응용 예 > LIBRARY IEEE; USE IEEE. std_logic_1164. all; USE work. gate_package. all; ENTITY logic_system IS PORT(A, B, C : IN std_logic; X, Y : OUT std_logic); END logic_system; ARCHITECTURE structure OF logic_system IS signal aorb, bandc, cbar : std_logic; BEGIN gate 0 : or_2 PORT MAP(A, B, aorb); gate 1 : and_2 PORT MAP(B, C, bandc); gate 2 : inv PORT MAP(C, cbar); gate 3 : nand_2 PORT MAP(aorb, cbar, X); gate 4 : nor_2 PORT MAP(bandc, cbar, Y); END structure;

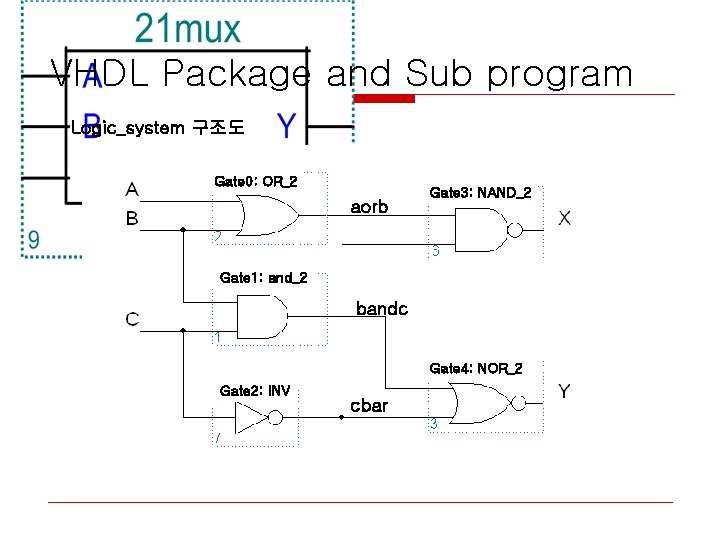

VHDL Package and Sub program Logic_system 구조도 Gate 0: OR_2 aorb Gate 3: NAND_2 Gate 1: and_2 bandc Gate 4: NOR_2 Gate 2: INV cbar

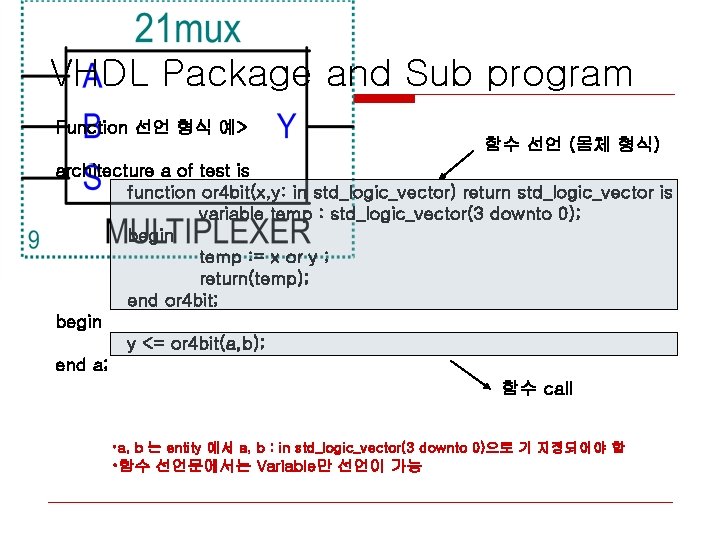

VHDL Package and Sub program Function 선언 형식 예> 함수 선언 (몸체 형식) architecture a of test is function or 4 bit(x, y: in std_logic_vector) return std_logic_vector is variable temp : std_logic_vector(3 downto 0); begin temp : = x or y ; return(temp); end or 4 bit; begin y <= or 4 bit(a, b); end a; 함수 call • a, b 는 entity 에서 a, b : in std_logic_vector(3 downto 0)으로 기 지정되어야 함 • 함수 선언문에서는 Variable만 선언이 가능

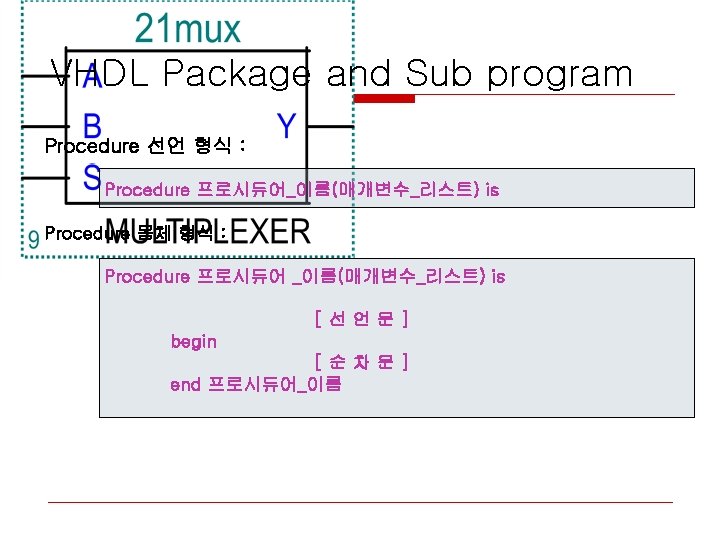

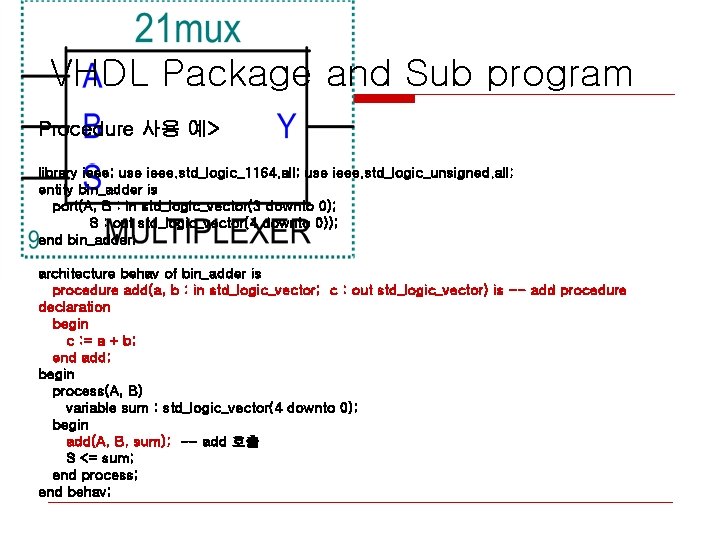

VHDL Package and Sub program Procedure 사용 예> library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; entity bin_adder is port(A, B : in std_logic_vector(3 downto 0); S : out std_logic_vector(4 downto 0)); end bin_adder; architecture behav of bin_adder is procedure add(a, b : in std_logic_vector; c : out std_logic_vector) is -- add procedure declaration begin c : = a + b; end add; begin process(A, B) variable sum : std_logic_vector(4 downto 0); begin add(A, B, sum); -- add 호출 S <= sum; end process; end behav;

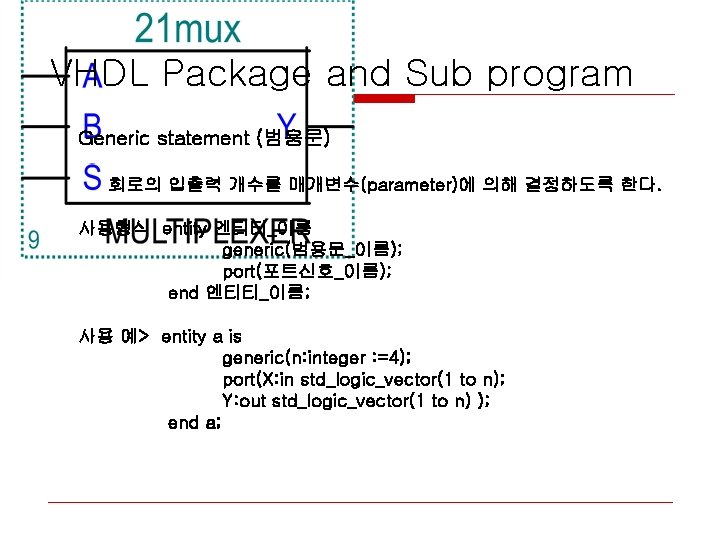

VHDL Package and Sub program Generic statement (범용문) 회로의 입출력 개수를 매개변수(parameter)에 의해 결정하도록 한다. 사용형식 entity 엔티티_이름 generic(범용문_이름); port(포트신호_이름); end 엔티티_이름; 사용 예> entity a is generic(n: integer : =4); port(X: in std_logic_vector(1 to n); Y: out std_logic_vector(1 to n) ); end a;

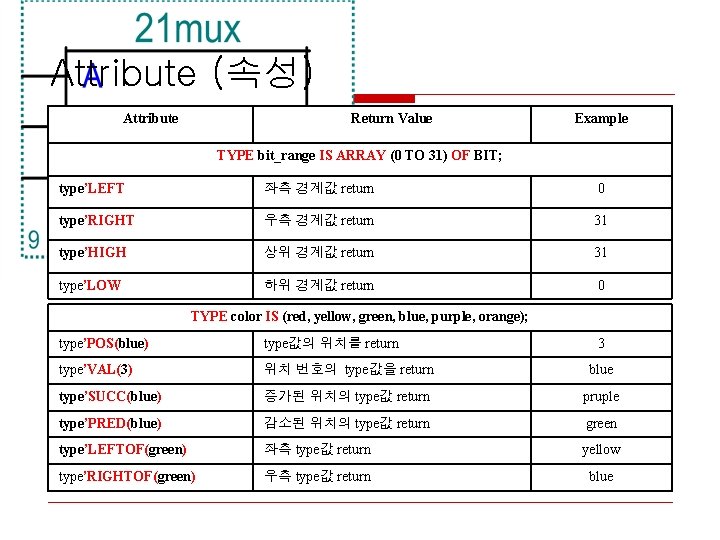

Attribute (속성) Attribute Return Value Example TYPE bit_range IS ARRAY (0 TO 31) OF BIT; type’LEFT 좌측 경계값 return 0 type’RIGHT 우측 경계값 return 31 type’HIGH 상위 경계값 return 31 type’LOW 하위 경계값 return 0 TYPE color IS (red, yellow, green, blue, purple, orange); type’POS(blue) type값의 위치를 return 3 type’VAL(3) 위치 번호의 type값을 return blue type’SUCC(blue) 증가된 위치의 type값 return pruple type’PRED(blue) 감소된 위치의 type값 return green type’LEFTOF(green) 좌측 type값 return yellow type’RIGHTOF(green) 우측 type값 return blue

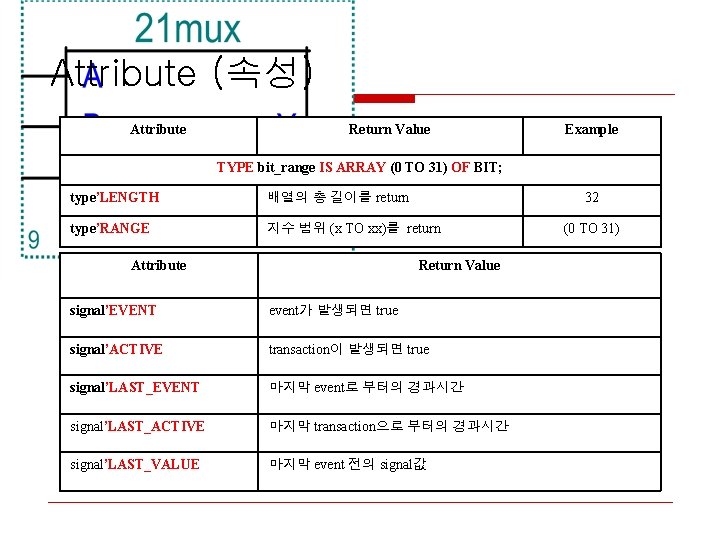

Attribute (속성) Attribute Return Value Example TYPE bit_range IS ARRAY (0 TO 31) OF BIT; type’LENGTH 배열의 총 길이를 return type’RANGE 지수 범위 (x TO xx)를 return Attribute 32 Return Value signal’EVENT event가 발생되면 true signal’ACTIVE transaction이 발생되면 true signal’LAST_EVENT 마지막 event로 부터의 경과시간 signal’LAST_ACTIVE 마지막 transaction으로 부터의 경과시간 signal’LAST_VALUE 마지막 event 전의 signal값 (0 TO 31)

- Slides: 16