VHDL Hierarchy in XILINX 9262008 ECE 561 Lecture

- Slides: 20

VHDL Hierarchy in XILINX 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 1

VHDL Hierarchy in XILINX • How do you do component instantiation in a tool such as XILINX • Outline and initial code of another application that includes a system controller 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 2

The Spec • Design a 2 digit timer that has user inputs of – Start/STOP – S digit 1 – S digit 2 • And the digital circuit also has outside input/outputs of – Clk – Alarm output signal 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 3

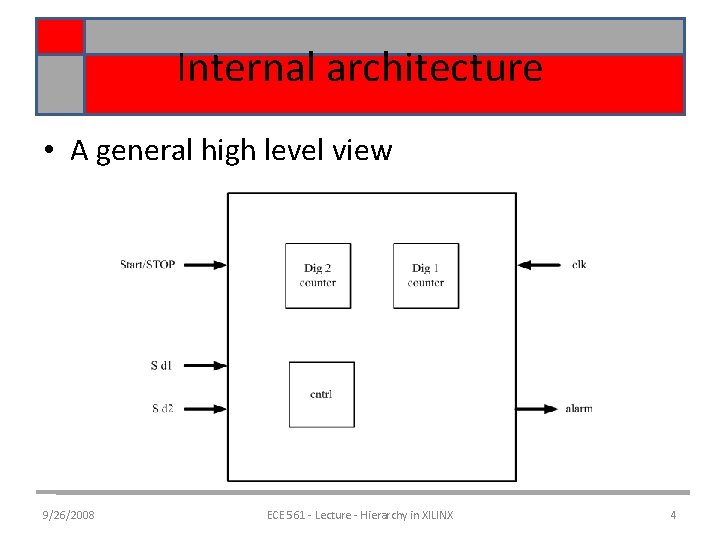

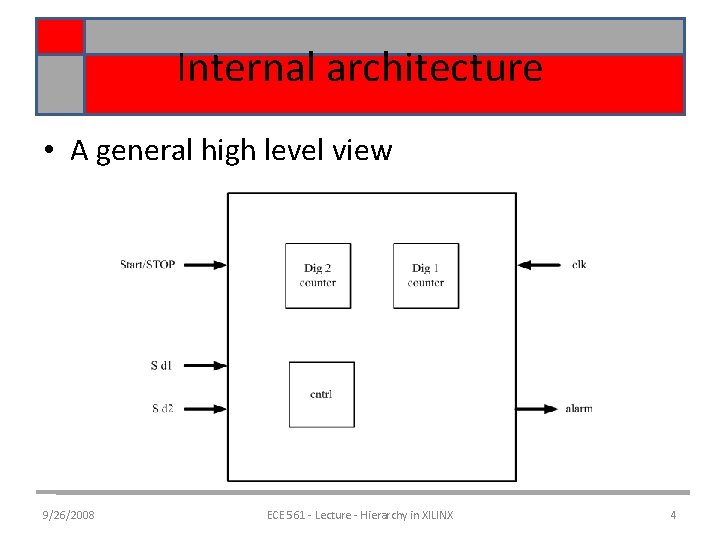

Internal architecture • A general high level view 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 4

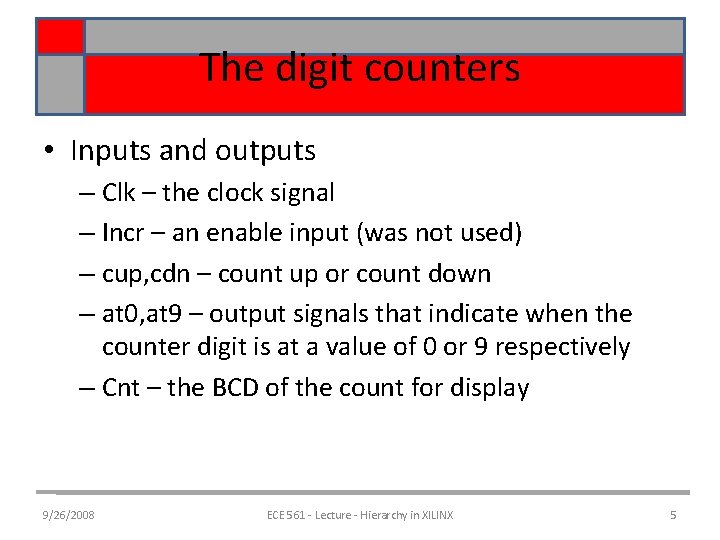

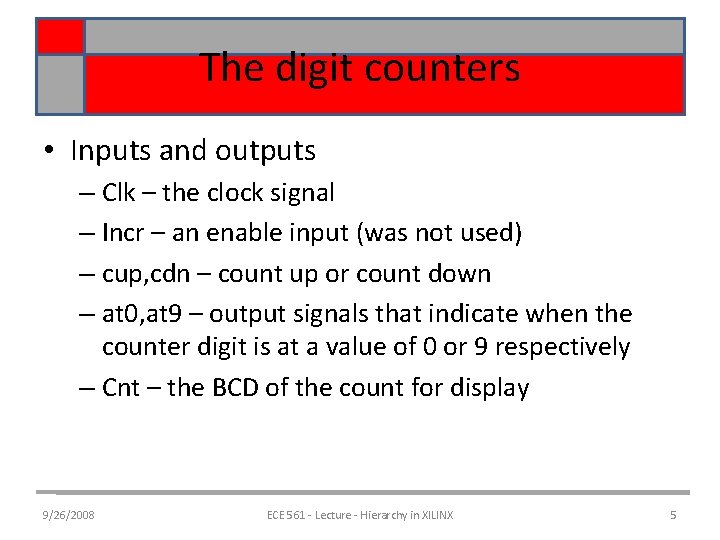

The digit counters • Inputs and outputs – Clk – the clock signal – Incr – an enable input (was not used) – cup, cdn – count up or count down – at 0, at 9 – output signals that indicate when the counter digit is at a value of 0 or 9 respectively – Cnt – the BCD of the count for display 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 5

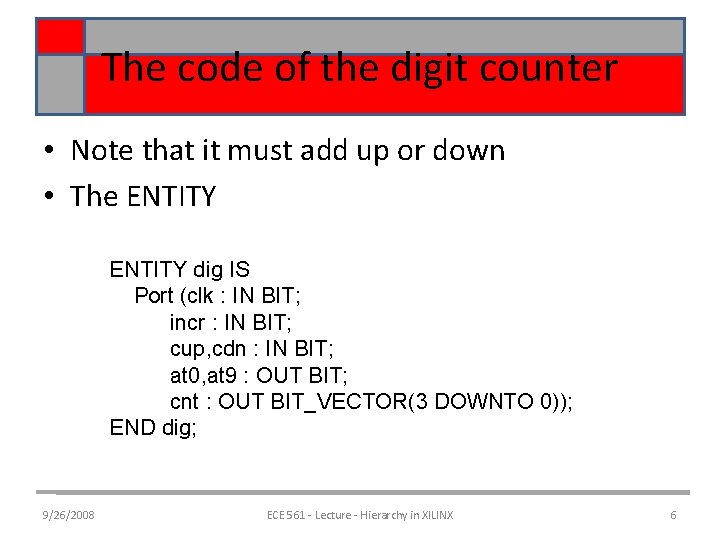

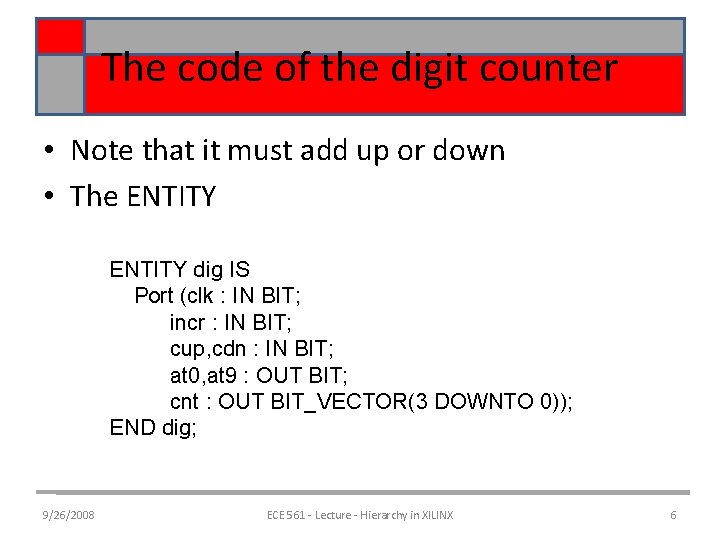

The code of the digit counter • Note that it must add up or down • The ENTITY dig IS Port (clk : IN BIT; incr : IN BIT; cup, cdn : IN BIT; at 0, at 9 : OUT BIT; cnt : OUT BIT_VECTOR(3 DOWNTO 0)); END dig; 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 6

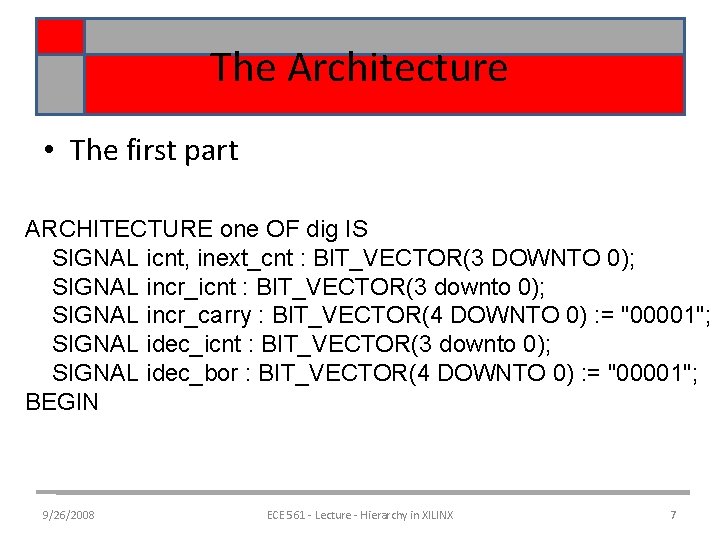

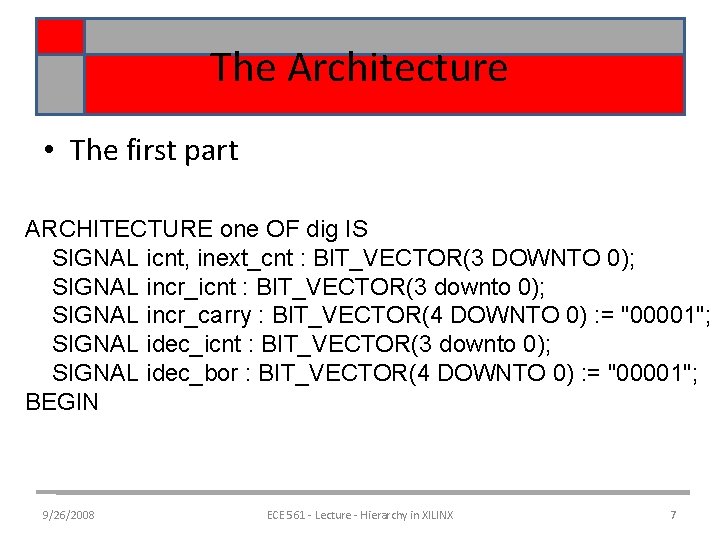

The Architecture • The first part ARCHITECTURE one OF dig IS SIGNAL icnt, inext_cnt : BIT_VECTOR(3 DOWNTO 0); SIGNAL incr_icnt : BIT_VECTOR(3 downto 0); SIGNAL incr_carry : BIT_VECTOR(4 DOWNTO 0) : = "00001"; SIGNAL idec_icnt : BIT_VECTOR(3 downto 0); SIGNAL idec_bor : BIT_VECTOR(4 DOWNTO 0) : = "00001"; BEGIN 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 7

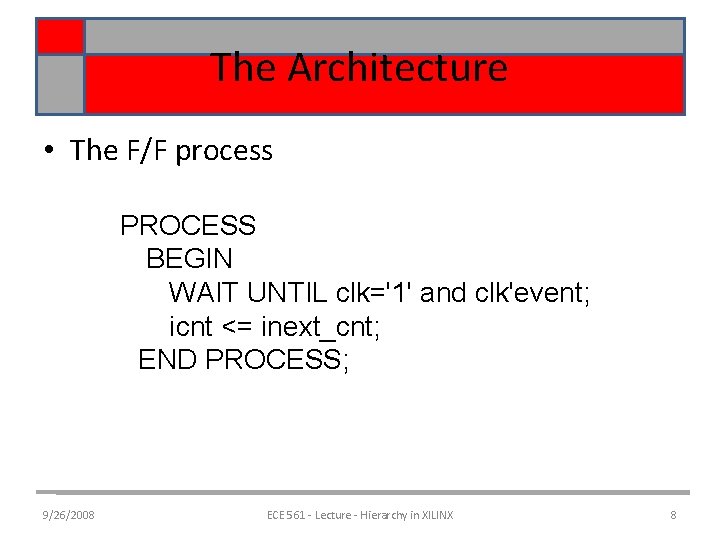

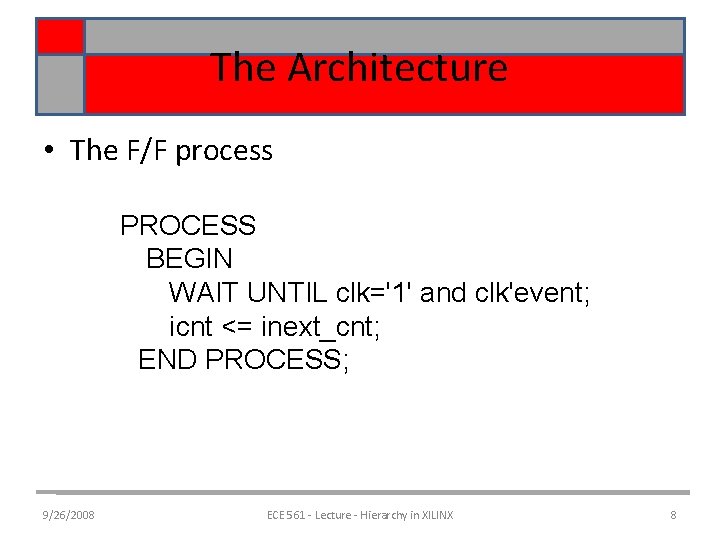

The Architecture • The F/F process PROCESS BEGIN WAIT UNTIL clk='1' and clk'event; icnt <= inext_cnt; END PROCESS; 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 8

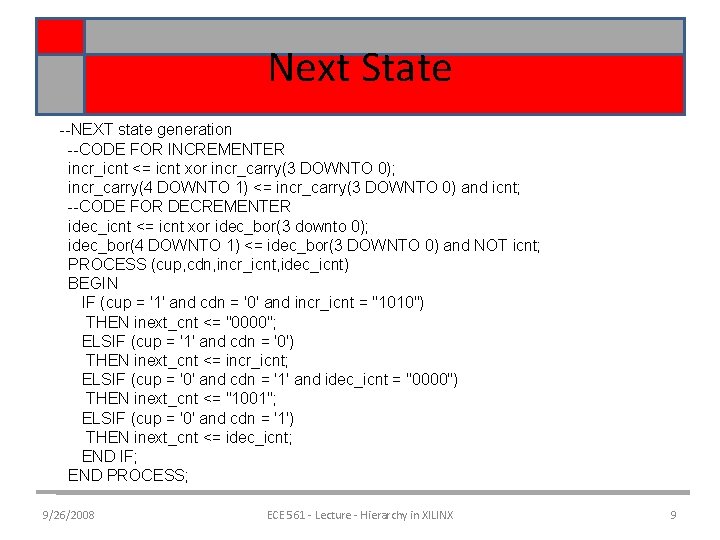

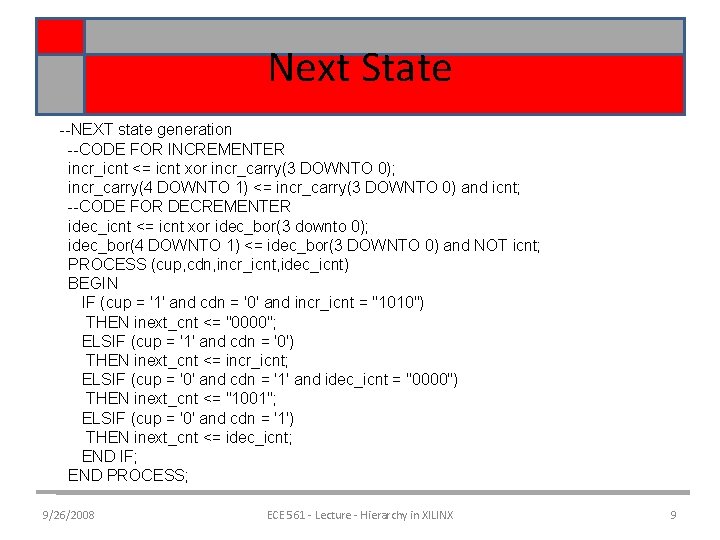

Next State --NEXT state generation --CODE FOR INCREMENTER incr_icnt <= icnt xor incr_carry(3 DOWNTO 0); incr_carry(4 DOWNTO 1) <= incr_carry(3 DOWNTO 0) and icnt; --CODE FOR DECREMENTER idec_icnt <= icnt xor idec_bor(3 downto 0); idec_bor(4 DOWNTO 1) <= idec_bor(3 DOWNTO 0) and NOT icnt; PROCESS (cup, cdn, incr_icnt, idec_icnt) BEGIN IF (cup = '1' and cdn = '0' and incr_icnt = "1010") THEN inext_cnt <= "0000"; ELSIF (cup = '1' and cdn = '0') THEN inext_cnt <= incr_icnt; ELSIF (cup = '0' and cdn = '1' and idec_icnt = "0000") THEN inext_cnt <= "1001"; ELSIF (cup = '0' and cdn = '1') THEN inext_cnt <= idec_icnt; END IF; END PROCESS; 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 9

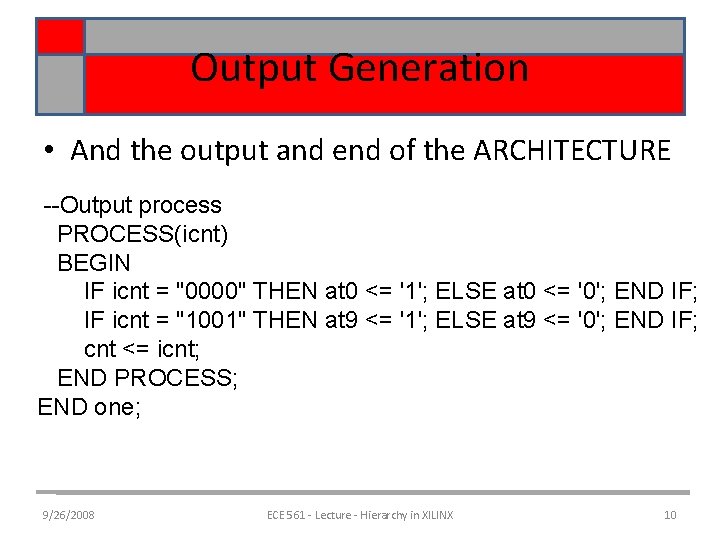

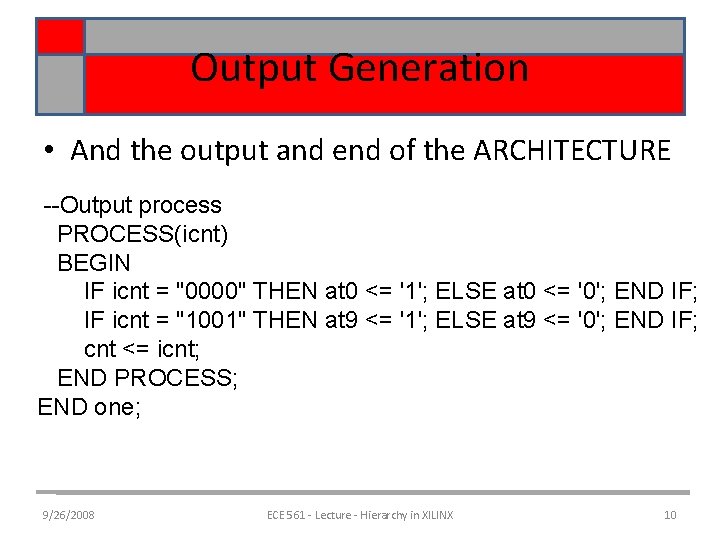

Output Generation • And the output and end of the ARCHITECTURE --Output process PROCESS(icnt) BEGIN IF icnt = "0000" THEN at 0 <= '1'; ELSE at 0 <= '0'; END IF; IF icnt = "1001" THEN at 9 <= '1'; ELSE at 9 <= '0'; END IF; cnt <= icnt; END PROCESS; END one; 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 10

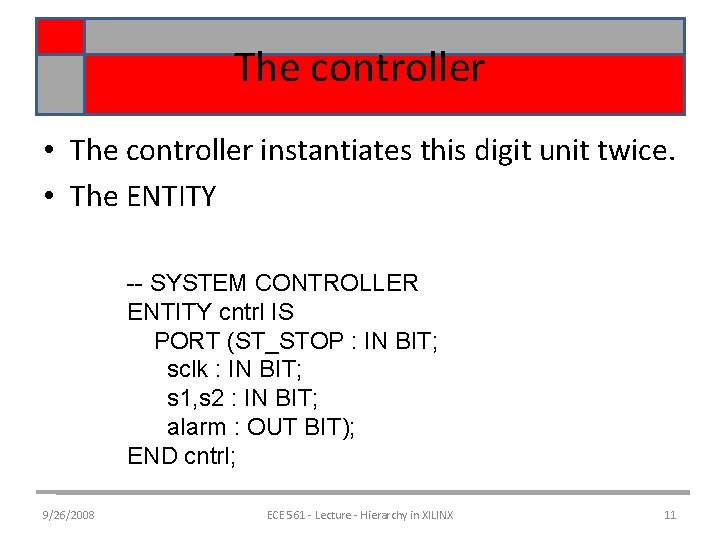

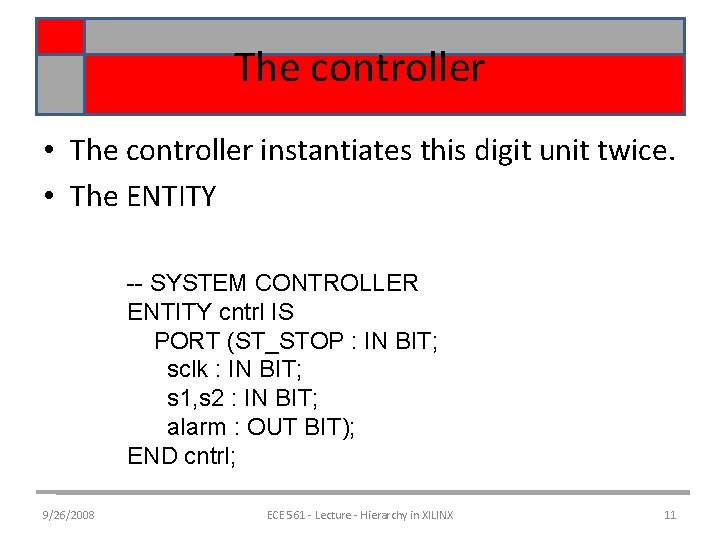

The controller • The controller instantiates this digit unit twice. • The ENTITY -- SYSTEM CONTROLLER ENTITY cntrl IS PORT (ST_STOP : IN BIT; sclk : IN BIT; s 1, s 2 : IN BIT; alarm : OUT BIT); END cntrl; 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 11

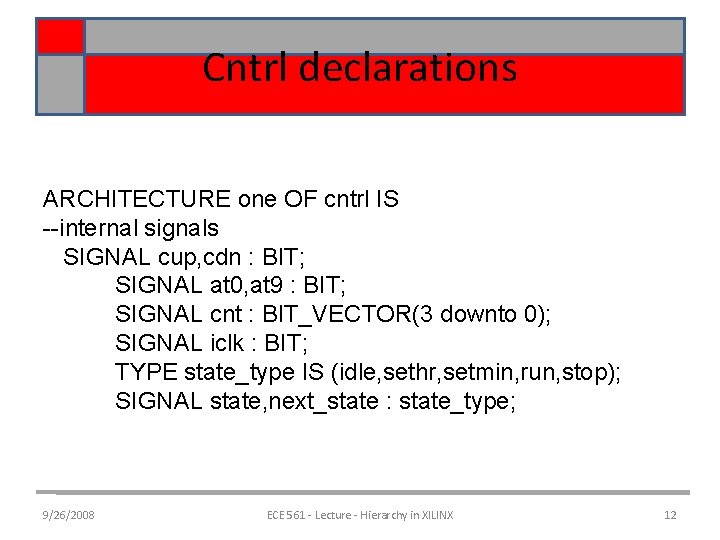

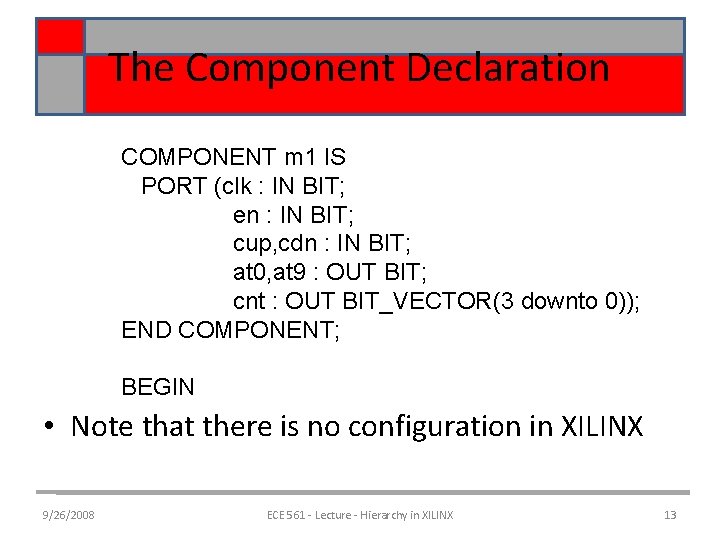

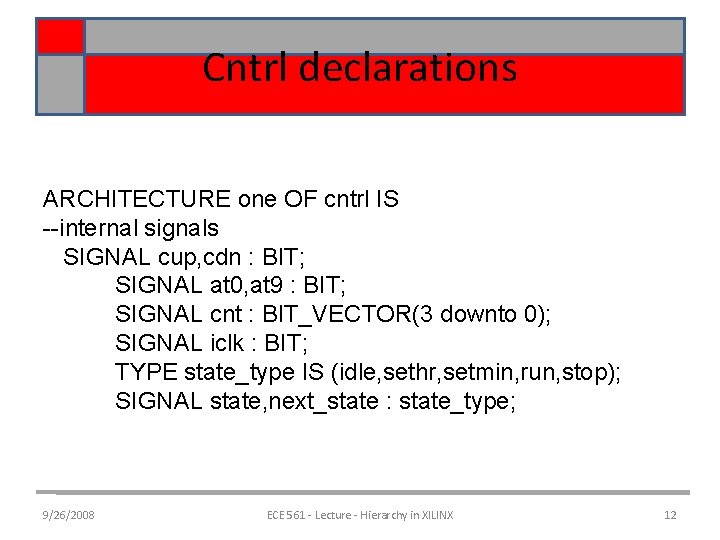

Cntrl declarations ARCHITECTURE one OF cntrl IS --internal signals SIGNAL cup, cdn : BIT; SIGNAL at 0, at 9 : BIT; SIGNAL cnt : BIT_VECTOR(3 downto 0); SIGNAL iclk : BIT; TYPE state_type IS (idle, sethr, setmin, run, stop); SIGNAL state, next_state : state_type; 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 12

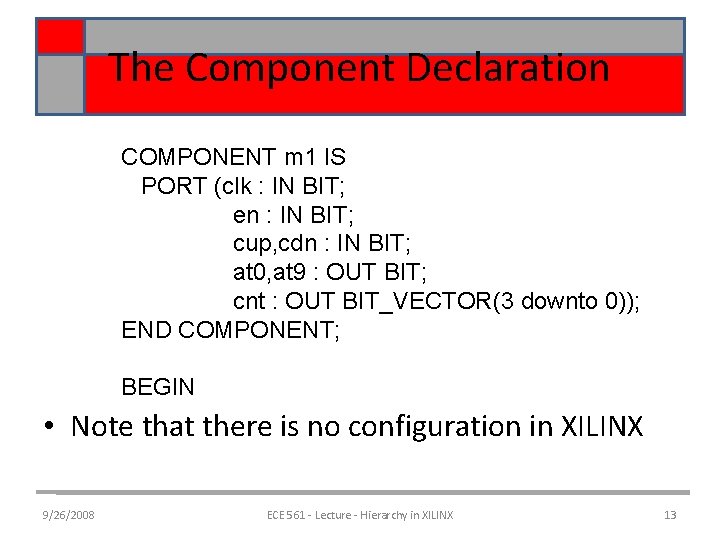

The Component Declaration COMPONENT m 1 IS PORT (clk : IN BIT; en : IN BIT; cup, cdn : IN BIT; at 0, at 9 : OUT BIT; cnt : OUT BIT_VECTOR(3 downto 0)); END COMPONENT; BEGIN • Note that there is no configuration in XILINX 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 13

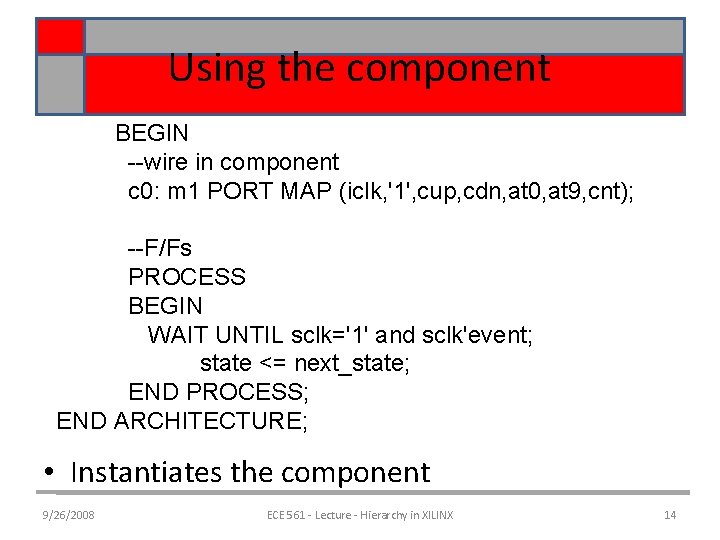

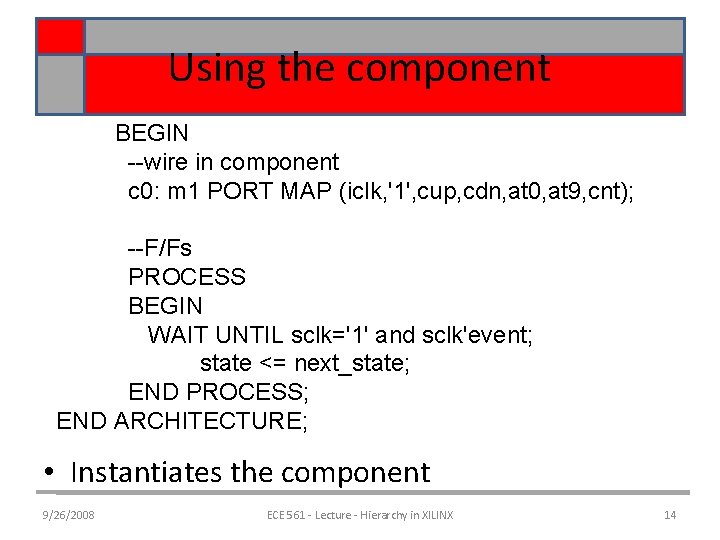

Using the component BEGIN --wire in component c 0: m 1 PORT MAP (iclk, '1', cup, cdn, at 0, at 9, cnt); --F/Fs PROCESS BEGIN WAIT UNTIL sclk='1' and sclk'event; state <= next_state; END PROCESS; END ARCHITECTURE; • Instantiates the component 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 14

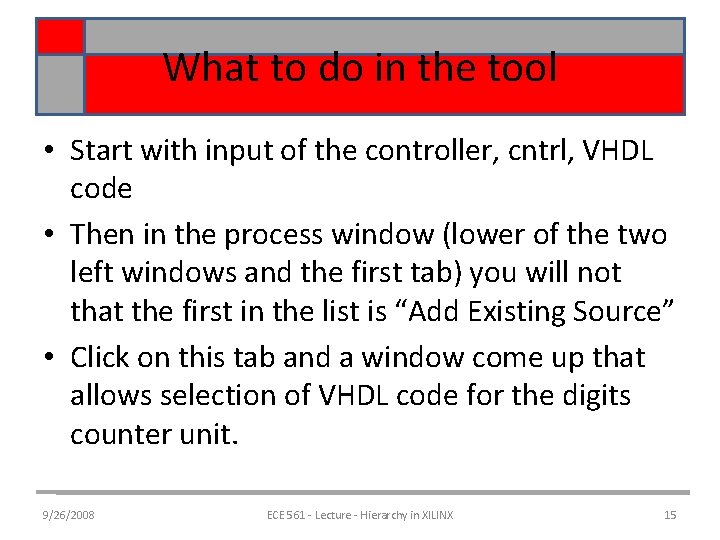

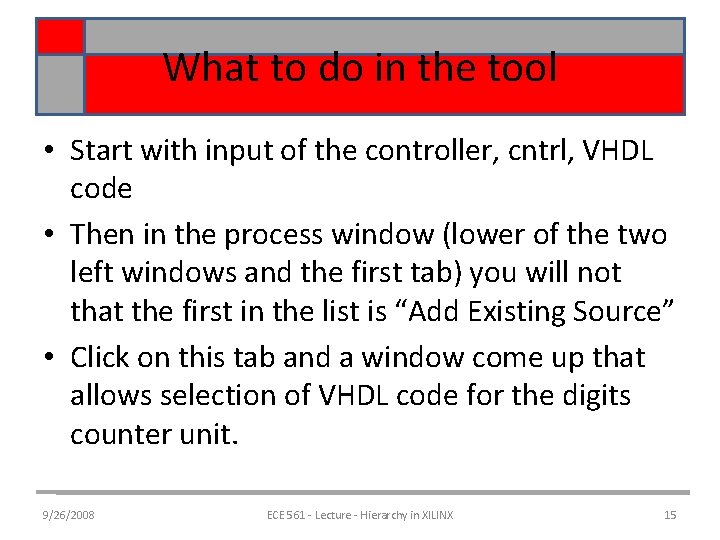

What to do in the tool • Start with input of the controller, cntrl, VHDL code • Then in the process window (lower of the two left windows and the first tab) you will not that the first in the list is “Add Existing Source” • Click on this tab and a window come up that allows selection of VHDL code for the digits counter unit. 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 15

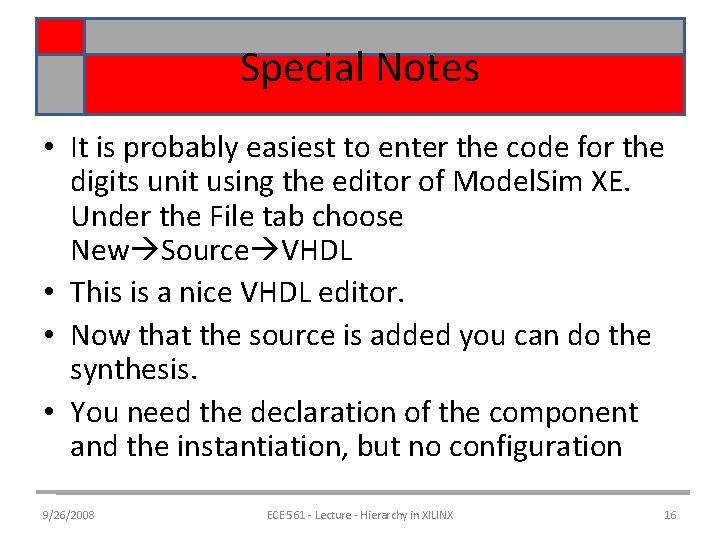

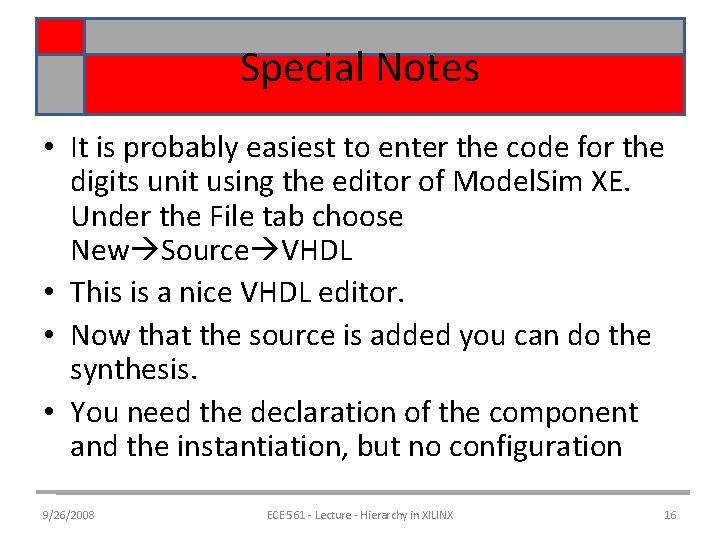

Special Notes • It is probably easiest to enter the code for the digits unit using the editor of Model. Sim XE. Under the File tab choose New Source VHDL • This is a nice VHDL editor. • Now that the source is added you can do the synthesis. • You need the declaration of the component and the instantiation, but no configuration 9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 16

9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 17

9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 18

9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 19

9/26/2008 ECE 561 - Lecture - Hierarchy in XILINX 20