Projektowanie systemw cyfrowych z wykorzystaniem jzyka VHDL Podstawy

- Slides: 17

Projektowanie systemów cyfrowych z wykorzystaniem języka VHDL Podstawy syntezy układów sekwencyjnych

Automaty – tradycyjne projektowanie • Etapy tradycyjnej metodologii projektowania skończonych automatów stanu: 1. 2. 3. 4. 5. 6. Utworzenie grafu stanu Utworzenie tablicy stanów Określenie funkcji wzbudzeń Utworzenie tablicy wyjść Określenie funkcji wyjść Narysowanie schematu Otrzymany w powyższy sposób schemat automatu można zapisać w języku VHDL używając opisu strukturalnego. Ten sposób opisu automatu jest bardzo czasochłonny.

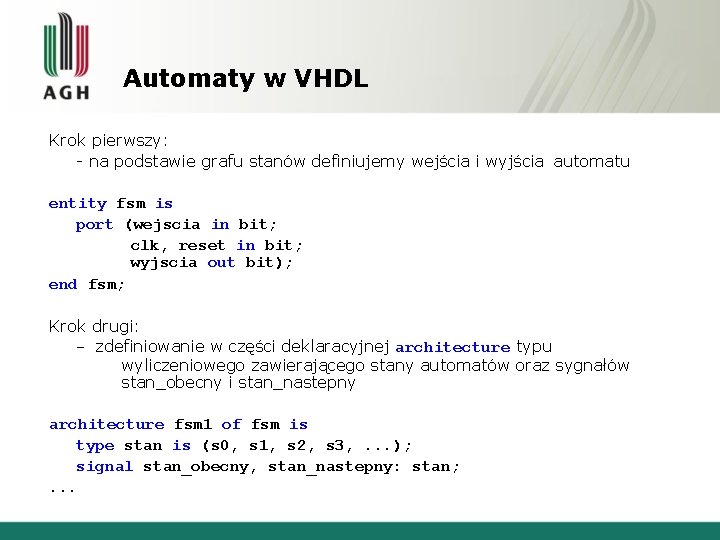

Automaty w VHDL Krok pierwszy: - na podstawie grafu stanów definiujemy wejścia i wyjścia automatu entity fsm is port (wejscia in bit; clk, reset in bit; wyjscia out bit); end fsm; Krok drugi: - zdefiniowanie w części deklaracyjnej architecture typu wyliczeniowego zawierającego stany automatów oraz sygnałów stan_obecny i stan_nastepny architecture fsm 1 of fsm is type stan is (s 0, s 1, s 2, s 3, . . . ); signal stan_obecny, stan_nastepny: stan; . . .

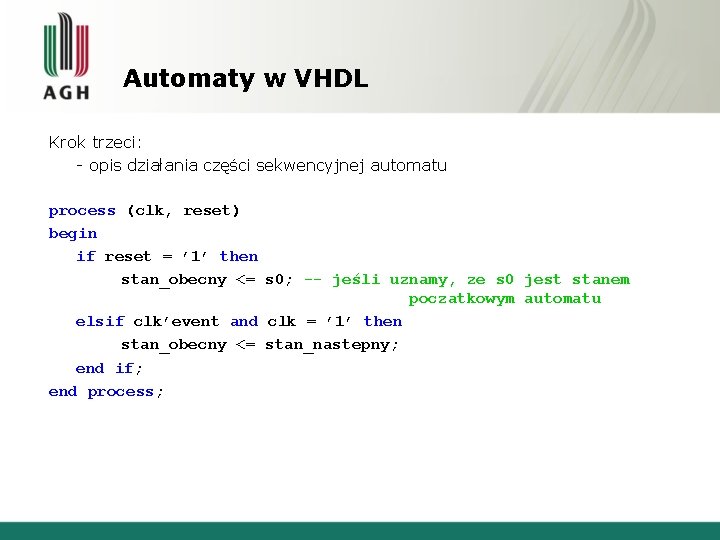

Automaty w VHDL Krok trzeci: - opis działania części sekwencyjnej automatu process (clk, reset) begin if reset = ’ 1’ then stan_obecny <= s 0; -- jeśli uznamy, ze s 0 jest stanem poczatkowym automatu elsif clk’event and clk = ’ 1’ then stan_obecny <= stan_nastepny; end if; end process;

Automaty w VHDL Krok czwarty: - opis działania części kombinacyjnej automatu process (wejscie, stan_obecny) begin case stan_obecny is when s 0 => if wejscie =. . . then wyjscie <= wartosc_wyjsciowa; stan_nastepny <= s 1; else. . . end if; when s 1 =>. . . end case; end process;

Automat Moore’a

Przykład – automat Moore’a Krok pierwszy: wejścia: - clk - reset -x wyjścia: -y . . . entity fsm is port (x in bit; clk, reset in bit; y out bit); end fsm; . . .

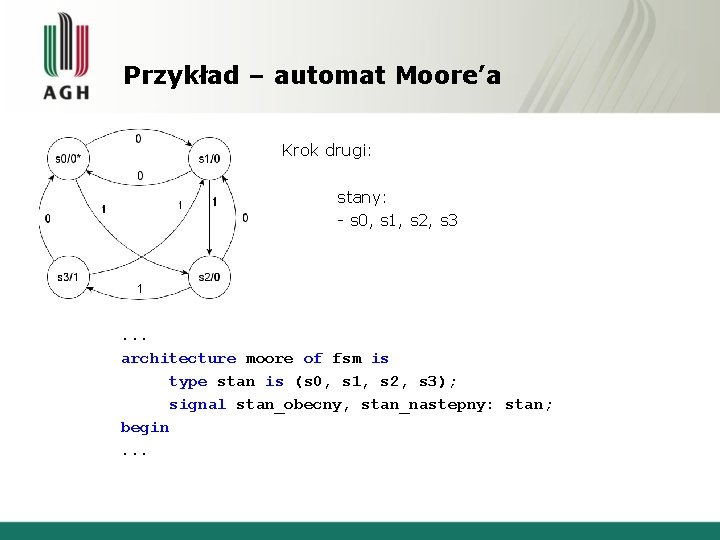

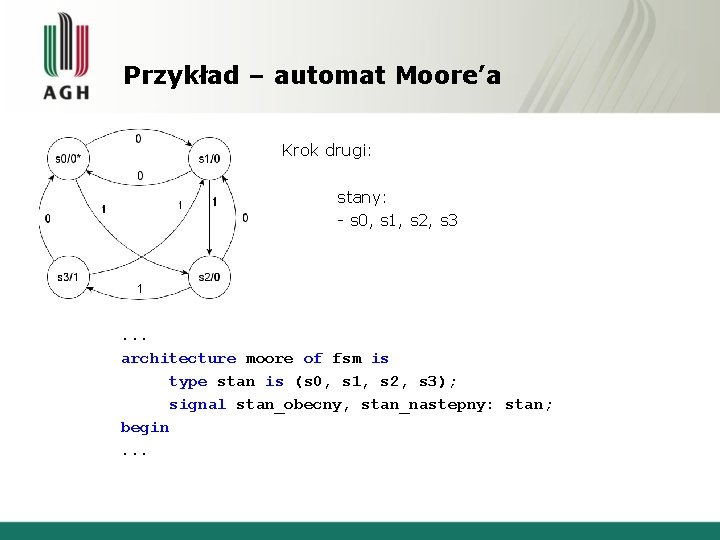

Przykład – automat Moore’a Krok drugi: stany: - s 0, s 1, s 2, s 3 . . . architecture moore of fsm is type stan is (s 0, s 1, s 2, s 3); signal stan_obecny, stan_nastepny: stan; begin. . .

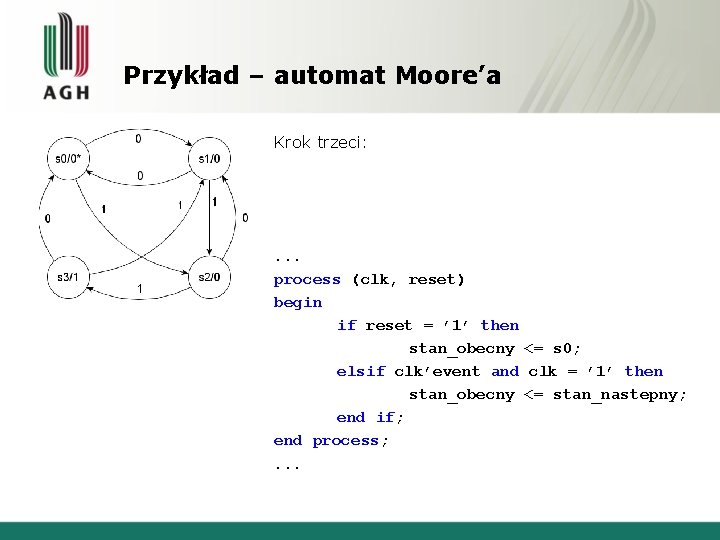

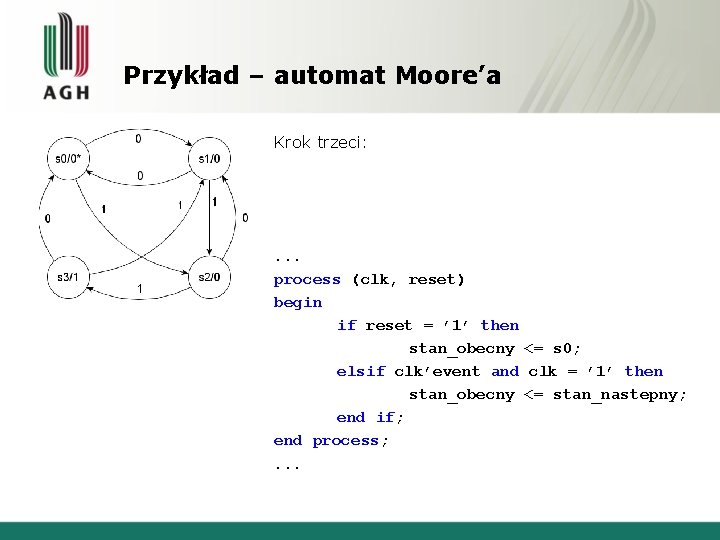

Przykład – automat Moore’a Krok trzeci: . . . process (clk, reset) begin if reset = ’ 1’ then stan_obecny <= s 0; elsif clk’event and clk = ’ 1’ then stan_obecny <= stan_nastepny; end if; end process; . . .

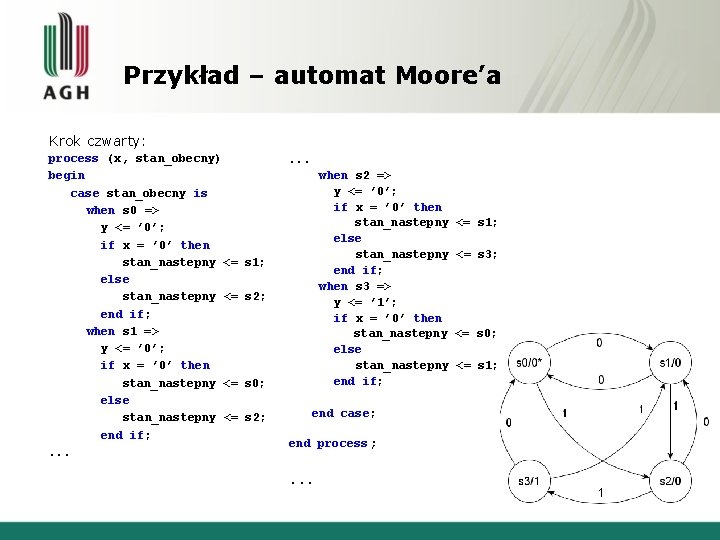

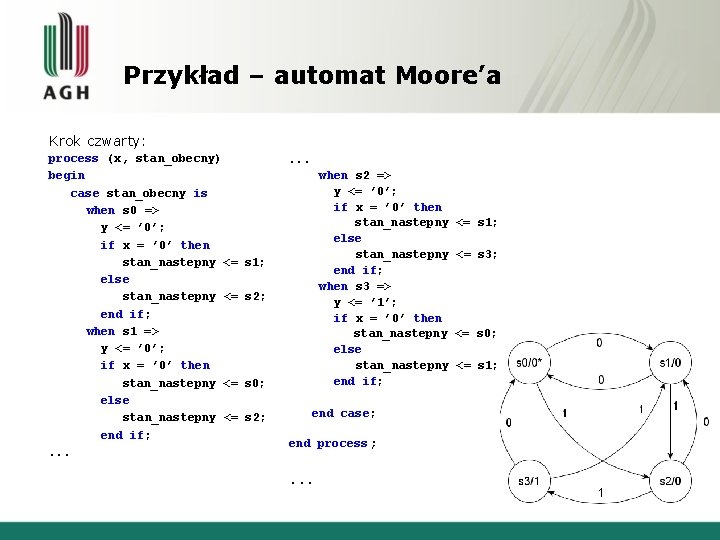

Przykład – automat Moore’a Krok czwarty: process (x, stan_obecny) begin case stan_obecny is when s 0 => y <= ’ 0’; if x = ’ 0’ then stan_nastepny <= else stan_nastepny <= end if; when s 1 => y <= ’ 0’; if x = ’ 0’ then stan_nastepny <= else stan_nastepny <= end if; . . . when s 2 => y <= ’ 0’; if x = ’ 0’ then stan_nastepny else stan_nastepny end if; when s 3 => y <= ’ 1’; if x = ’ 0’ then stan_nastepny else stan_nastepny end if; s 1; s 2; s 0; s 2; end case; end process ; . . . <= s 1; <= s 3; <= s 0; <= s 1;

Automat Mealy’ego

Przykład – automat Mealy’ego , Krok pierwszy: wejścia: - clk - reset -x wyjścia: -y . . . entity fsm is port (x in bit_vector(1 downto 0); clk, reset in bit; y out bit); end fsm; . . .

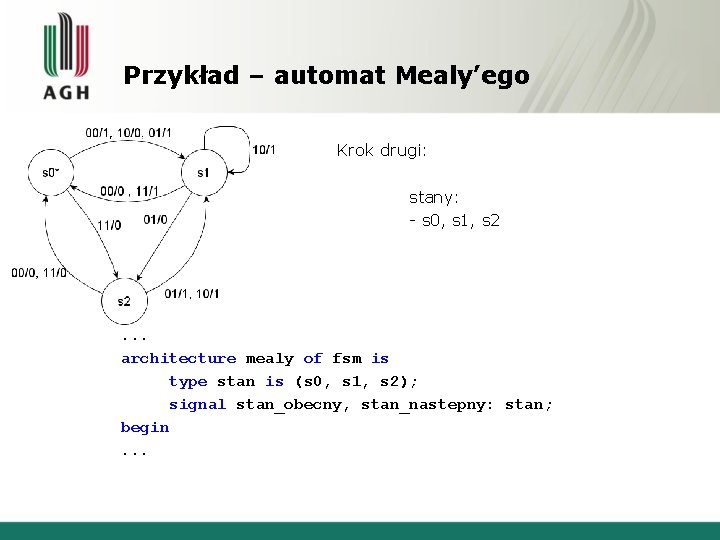

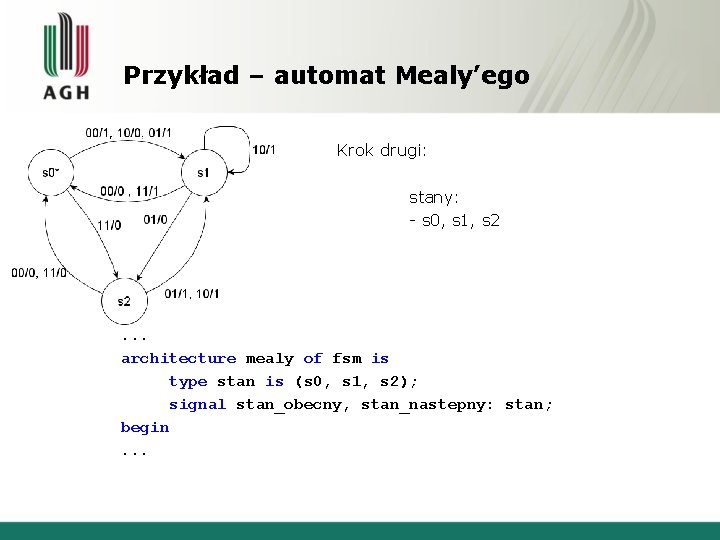

Przykład – automat Mealy’ego , Krok drugi: stany: - s 0, s 1, s 2 . . . architecture mealy of fsm is type stan is (s 0, s 1, s 2); signal stan_obecny, stan_nastepny: stan; begin. . .

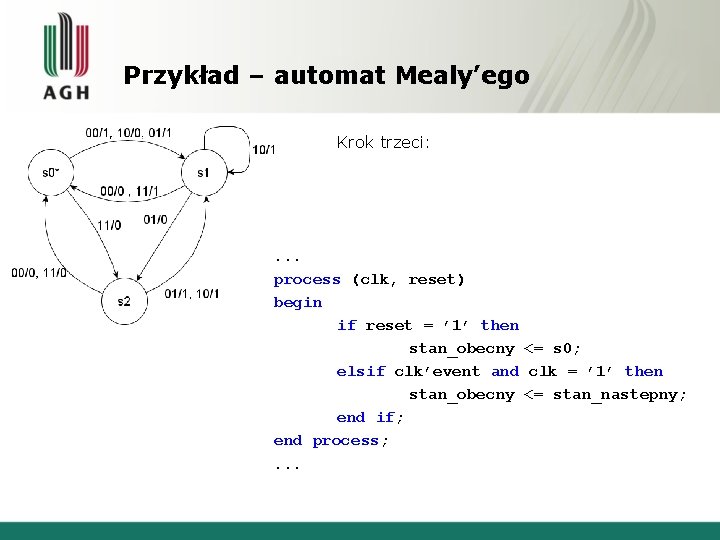

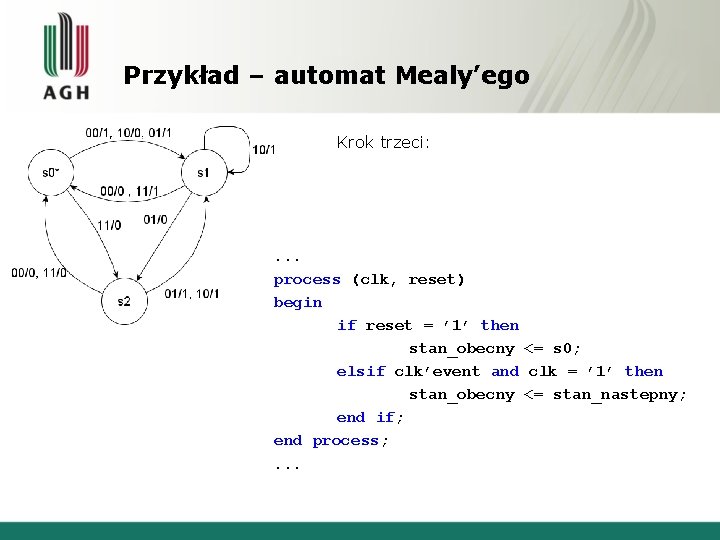

Przykład – automat Mealy’ego , Krok trzeci: . . . process (clk, reset) begin if reset = ’ 1’ then stan_obecny <= s 0; elsif clk’event and clk = ’ 1’ then stan_obecny <= stan_nastepny; end if; end process; . . .

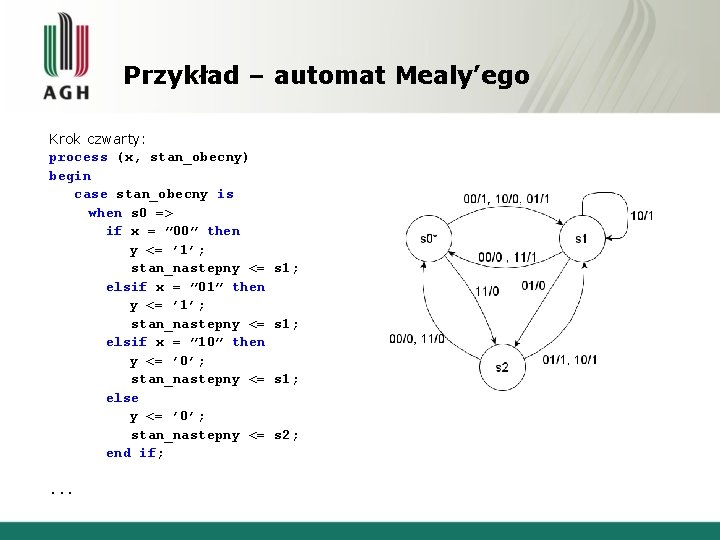

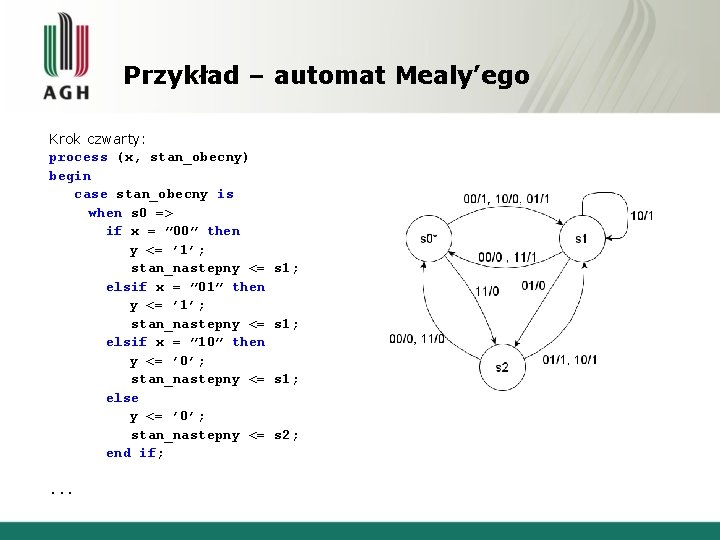

Przykład – automat Mealy’ego Krok czwarty: process (x, stan_obecny) begin case stan_obecny is when s 0 => if x = ” 00” then y <= ’ 1’; stan_nastepny <= elsif x = ” 01” then y <= ’ 1’; stan_nastepny <= elsif x = ” 10” then y <= ’ 0’; stan_nastepny <= else y <= ’ 0’; stan_nastepny <= end if; . . . , s 1; s 2;

Przykład – automat Mealy’ego Krok czwarty: . . . when s 1 => if x = ” 00” then y <= ’ 0’; stan_nastepny <= elsif x = ” 01” then y <= ’ 0’; stan_nastepny <= elsif x = ” 10” then y <= ’ 1’; stan_nastepny <= else y <= ’ 1’; stan_nastepny <= end if; . . . , s 0; s 2; s 1; s 0;

Przykład – automat Mealy’ego Krok czwarty: . . . when s 2 => if x = ” 00” then y <= ’ 0’; stan_nastepny <= elsif x = ” 01” then y <= ’ 1’; stan_nastepny <= elsif x = ” 10” then y <= ’ 1’; stan_nastepny <= else y <= ’ 0’; stan_nastepny <= end if; end case; end process; . . . , s 0; s 1; s 0;

Odpowiedź impulsowa filtru

Odpowiedź impulsowa filtru Vhdl automat

Vhdl automat Federacja bibliotek cyfrowych

Federacja bibliotek cyfrowych Zasada działania aparatu fotograficznego

Zasada działania aparatu fotograficznego Technik cyfrowych procesów graficznych praca

Technik cyfrowych procesów graficznych praca Projektowanie magazynów

Projektowanie magazynów Plan lan

Plan lan Projektowanie systemów logistycznych

Projektowanie systemów logistycznych Projektowanie aplikacji webowych

Projektowanie aplikacji webowych Wodożądność kruszywa

Wodożądność kruszywa Mikroteoria

Mikroteoria Projektowanie relacyjnych baz danych

Projektowanie relacyjnych baz danych Planowanie bazy danych

Planowanie bazy danych Projektowanie case

Projektowanie case Projektowanie konceptualne

Projektowanie konceptualne Projektowanie aplikacji internetowych

Projektowanie aplikacji internetowych Miernik elektrodynamiczny

Miernik elektrodynamiczny Wzór pole powierzchni graniastosłupa

Wzór pole powierzchni graniastosłupa