Projektowanie systemw cyfrowych z wykorzystaniem jzyka VHDL Ukady

![Entity - składnia entity nazwa_jednostki is -- deklaracja jednostki [generic (lista_deklarowanych_stalych); ] [port (lista_sygnalow_wej. Entity - składnia entity nazwa_jednostki is -- deklaracja jednostki [generic (lista_deklarowanych_stalych); ] [port (lista_sygnalow_wej.](https://slidetodoc.com/presentation_image_h2/655d4e5a52b5e93a0b74e657e0263f91/image-6.jpg)

![Architecture – składnia architecture nazwa_architektury of nazwa_jednostki is [czesc_deklaracyjna: typy, sygnaly_wewnetrzne, stale] begin instrukcja_wspolbiezna; Architecture – składnia architecture nazwa_architektury of nazwa_jednostki is [czesc_deklaracyjna: typy, sygnaly_wewnetrzne, stale] begin instrukcja_wspolbiezna;](https://slidetodoc.com/presentation_image_h2/655d4e5a52b5e93a0b74e657e0263f91/image-14.jpg)

- Slides: 22

Projektowanie systemów cyfrowych z wykorzystaniem języka VHDL Układy kombinacyjne

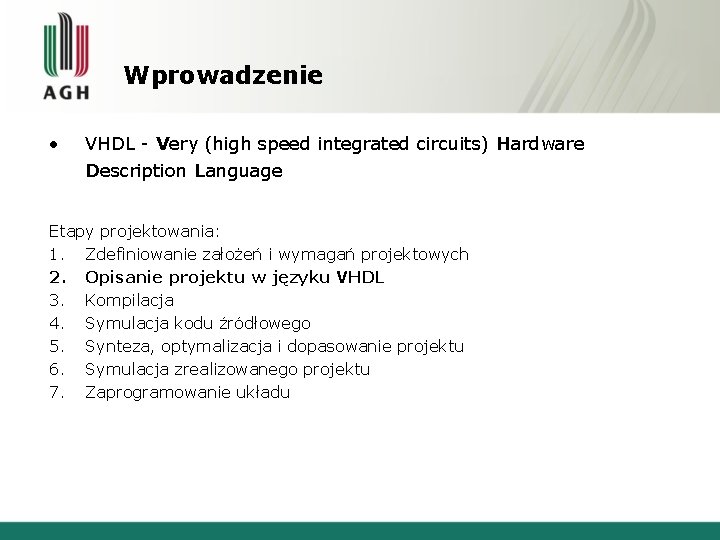

Wprowadzenie • VHDL - Very (high speed integrated circuits) Hardware Description Language Etapy projektowania: 1. Zdefiniowanie założeń i wymagań projektowych 2. Opisanie projektu w języku VHDL 3. Kompilacja 4. Symulacja kodu źródłowego 5. Synteza, optymalizacja i dopasowanie projektu 6. Symulacja zrealizowanego projektu 7. Zaprogramowanie układu

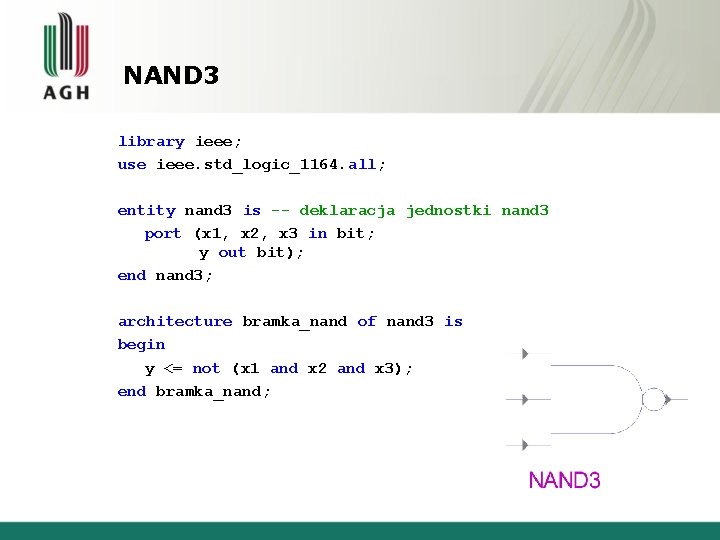

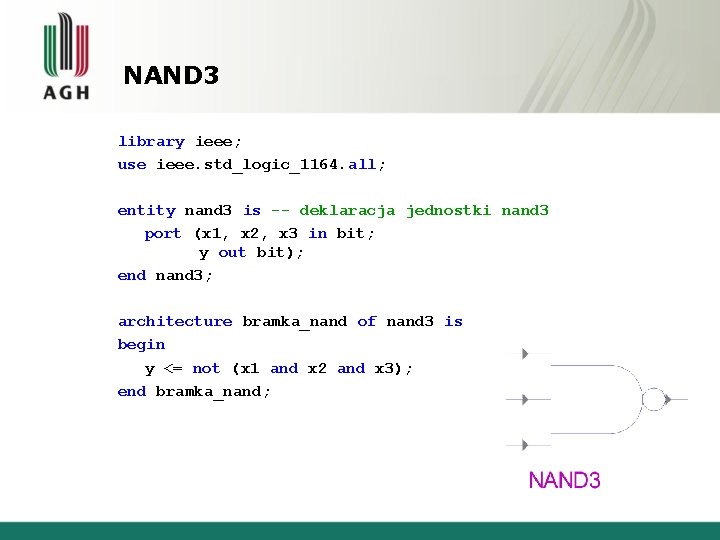

NAND 3 library ieee; use ieee. std_logic_1164. all; entity nand 3 is -- deklaracja jednostki nand 3 port (x 1, x 2, x 3 in bit; y out bit); end nand 3; architecture bramka_nand of nand 3 is begin y <= not (x 1 and x 2 and x 3); end bramka_nand;

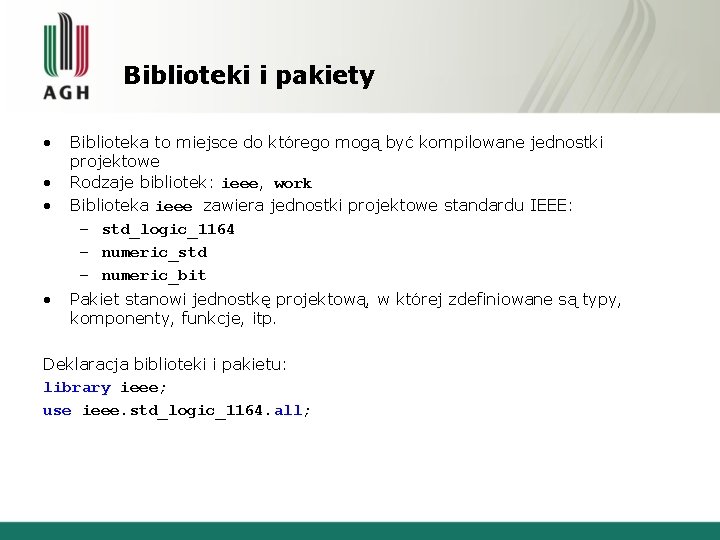

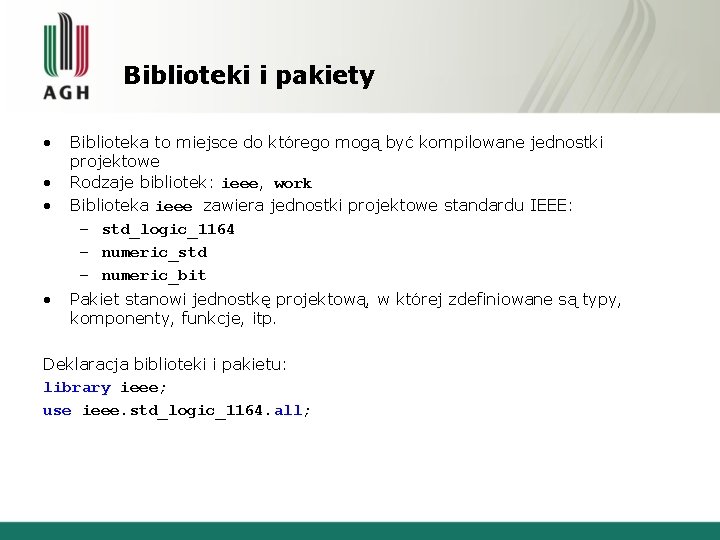

Biblioteki i pakiety • • Biblioteka to miejsce do którego mogą być kompilowane jednostki projektowe Rodzaje bibliotek: ieee, work Biblioteka ieee zawiera jednostki projektowe standardu IEEE: – std_logic_1164 – numeric_std – numeric_bit Pakiet stanowi jednostkę projektową, w której zdefiniowane są typy, komponenty, funkcje, itp. Deklaracja biblioteki i pakietu: library ieee; use ieee. std_logic_1164. all;

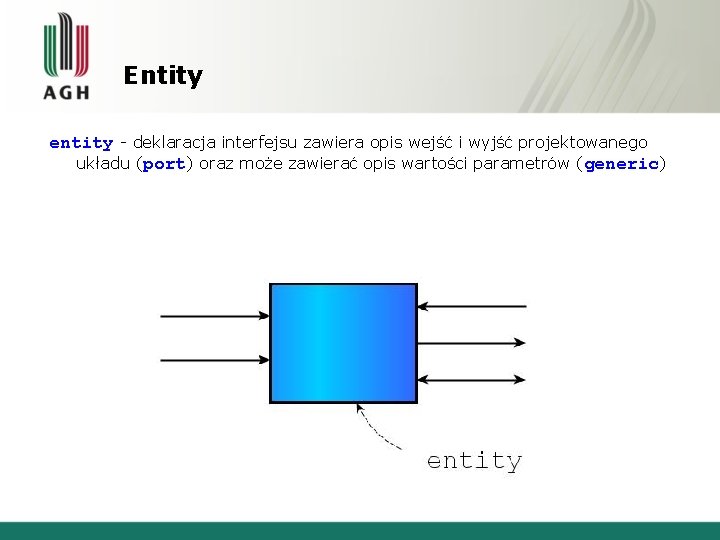

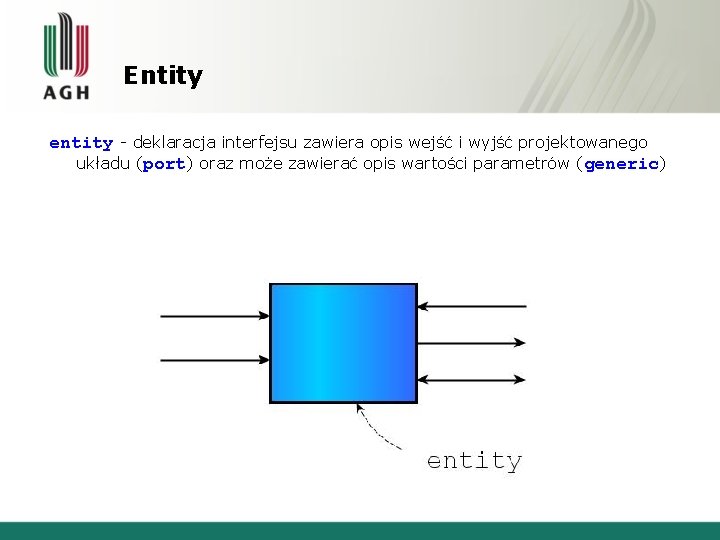

Entity entity - deklaracja interfejsu zawiera opis wejść i wyjść projektowanego układu (port) oraz może zawierać opis wartości parametrów (generic)

![Entity składnia entity nazwajednostki is deklaracja jednostki generic listadeklarowanychstalych port listasygnalowwej Entity - składnia entity nazwa_jednostki is -- deklaracja jednostki [generic (lista_deklarowanych_stalych); ] [port (lista_sygnalow_wej.](https://slidetodoc.com/presentation_image_h2/655d4e5a52b5e93a0b74e657e0263f91/image-6.jpg)

Entity - składnia entity nazwa_jednostki is -- deklaracja jednostki [generic (lista_deklarowanych_stalych); ] [port (lista_sygnalow_wej. in|inout nazwa_typu; lista_ sygnalow_wyj. out|buffer|inout nazwa_typu); ] end nazwa_jednostki; Przykład: entity nand 3 is -- deklaracja jednostki nand 3 port (x 1, x 2, x 3 in bit; y out bit); end nand 3;

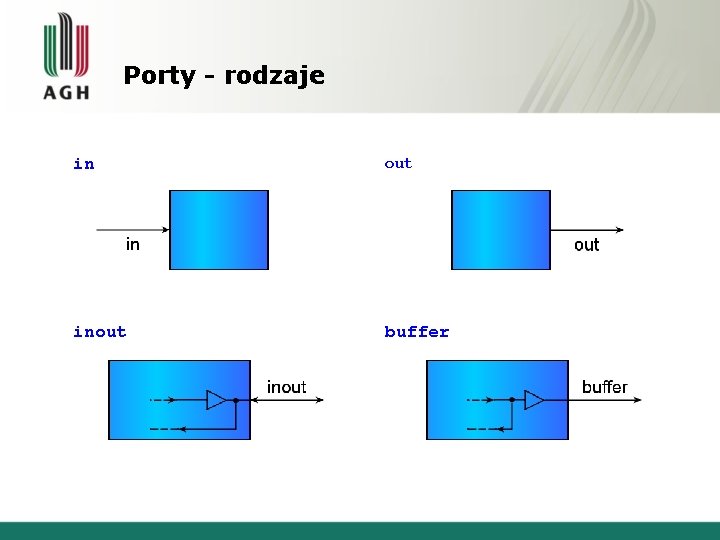

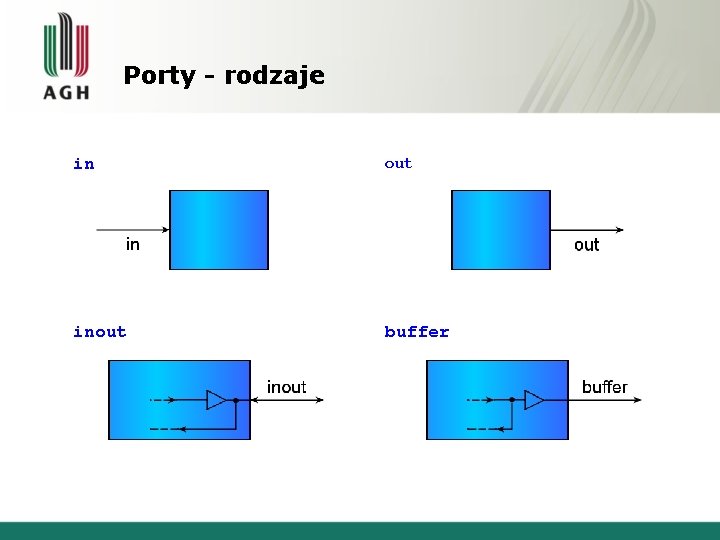

Porty - rodzaje in out inout buffer

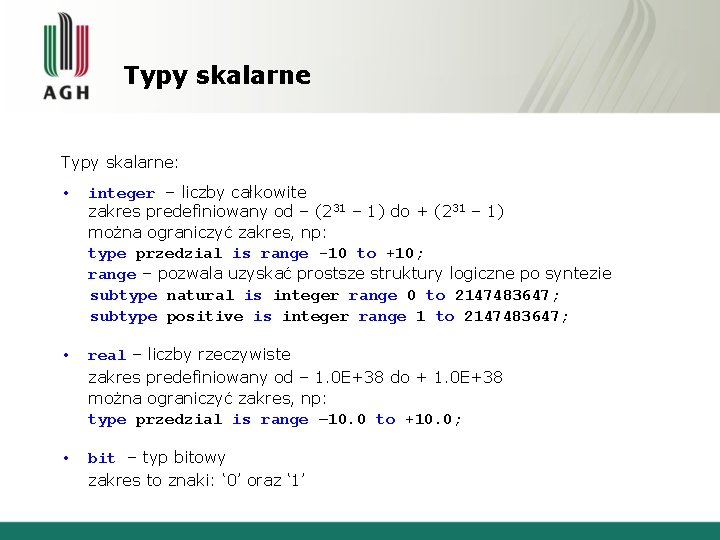

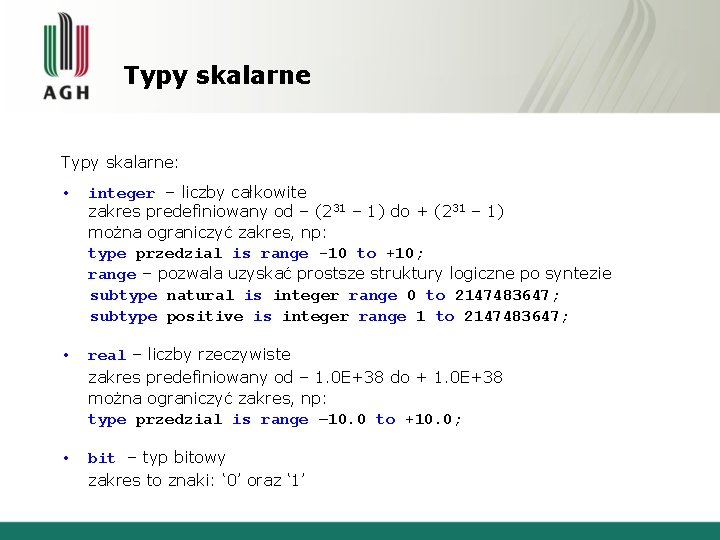

Typy skalarne: • integer – liczby całkowite zakres predefiniowany od – (231 – 1) do + (231 – 1) można ograniczyć zakres, np: type przedzial is range -10 to +10; range – pozwala uzyskać prostsze struktury logiczne po syntezie subtype natural is integer range 0 to 2147483647; subtype positive is integer range 1 to 2147483647; • real – liczby rzeczywiste zakres predefiniowany od – 1. 0 E+38 do + 1. 0 E+38 można ograniczyć zakres, np: type przedzial is range – 10. 0 to +10. 0; • bit – typ bitowy zakres to znaki: ‘ 0’ oraz ‘ 1’

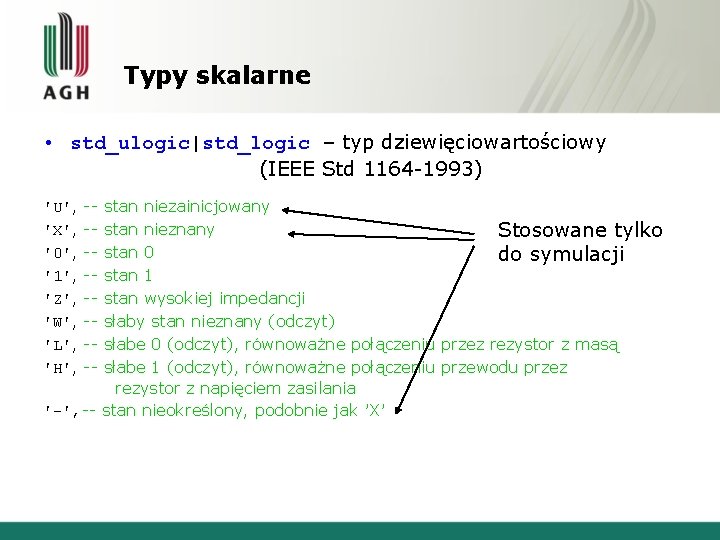

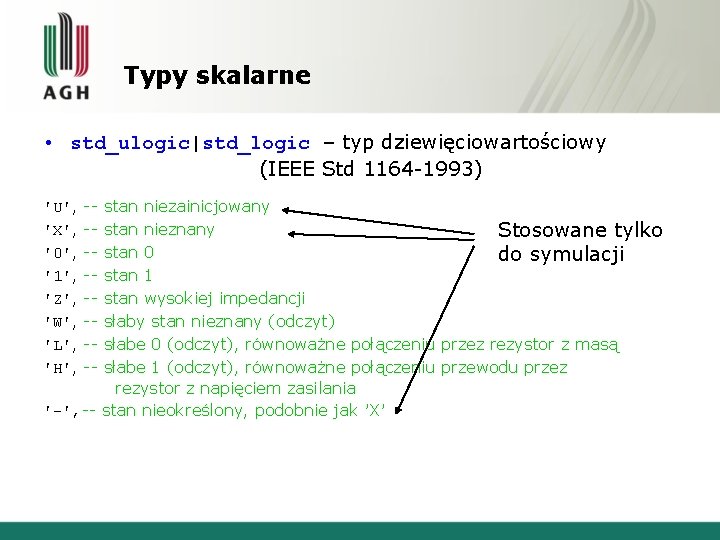

Typy skalarne • std_ulogic|std_logic – typ dziewięciowartościowy (IEEE Std 1164 -1993) stan niezainicjowany stan nieznany Stosowane tylko stan 0 do symulacji stan 1 stan wysokiej impedancji słaby stan nieznany (odczyt) słabe 0 (odczyt), równoważne połączeniu przez rezystor z masą słabe 1 (odczyt), równoważne połączeniu przewodu przez rezystor z napięciem zasilania ′-′, -- stan nieokreślony, podobnie jak ′X′ ′U′, ′X′, ′ 0′, ′ 1′, ′Z′, ′W′, ′L′, ′H′, -----

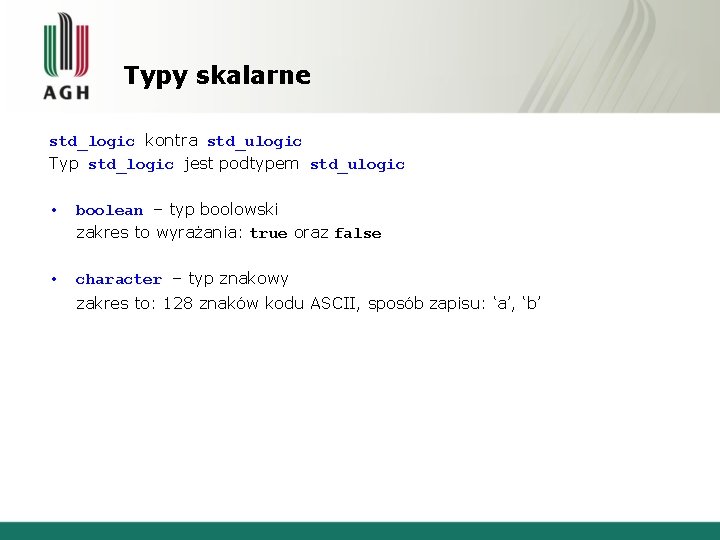

Typy skalarne std_logic kontra std_ulogic Typ std_logic jest podtypem std_ulogic • boolean – typ boolowski zakres to wyrażania: true oraz false • character – typ znakowy zakres to: 128 znaków kodu ASCII, sposób zapisu: ‘a’, ‘b’

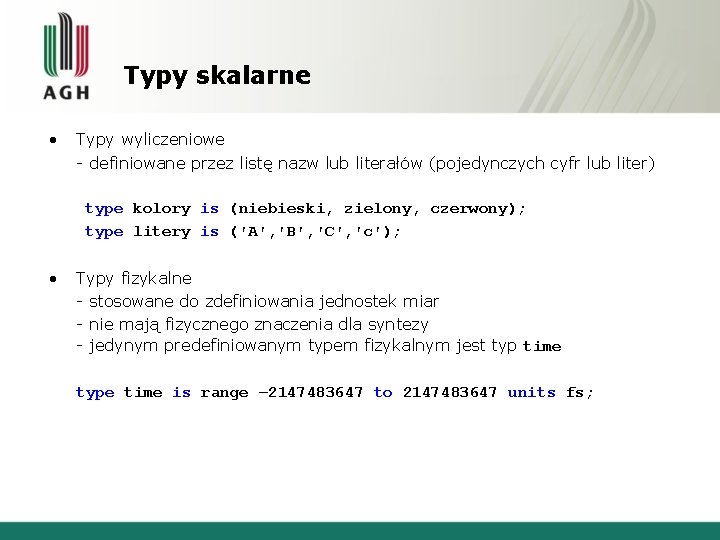

Typy skalarne • Typy wyliczeniowe - definiowane przez listę nazw lub literałów (pojedynczych cyfr lub liter) type kolory is (niebieski, zielony, czerwony); type litery is (′A′, ′B′, ′C′, ′c′); • Typy fizykalne - stosowane do zdefiniowania jednostek miar - nie mają fizycznego znaczenia dla syntezy - jedynym predefiniowanym typem fizykalnym jest typ time type time is range – 2147483647 to 2147483647 units fs;

Typy złożone • array - typy macierzowe (tablicowe) - obiekt składa się z wielu elementów tego samego typu - najczęściej stosowane: type bit_vector is array (natural range <>) of bit; type std_logic_vector is array (natural range <>) of std_logic; type std_ulogic_vector is array (natural range <>) of std_ulogic; - definicja magistrali: signal a: std_logic_vector(3 downto 0); - macierz dwuwymiarowa: type table_8 x 4 is array (0 to 7, 0 to 3) of bit;

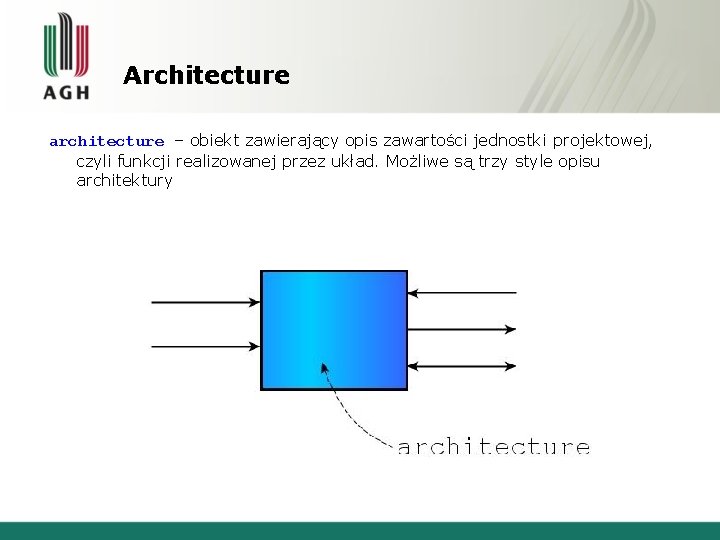

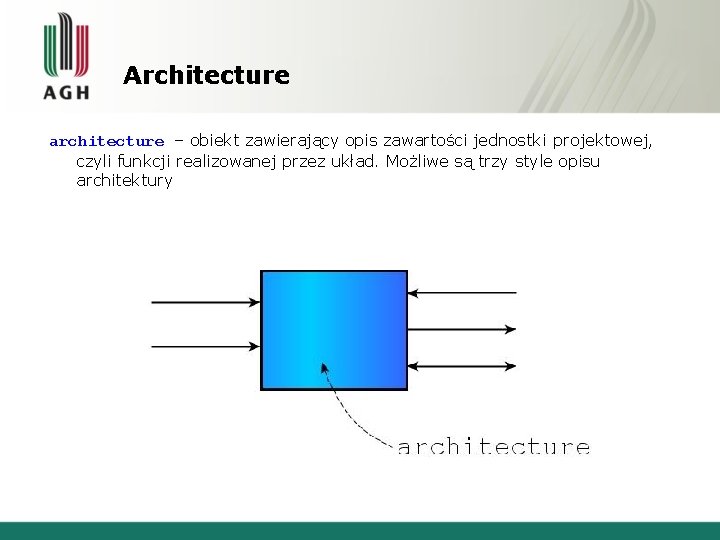

Architecture architecture – obiekt zawierający opis zawartości jednostki projektowej, czyli funkcji realizowanej przez układ. Możliwe są trzy style opisu architektury

![Architecture składnia architecture nazwaarchitektury of nazwajednostki is czescdeklaracyjna typy sygnalywewnetrzne stale begin instrukcjawspolbiezna Architecture – składnia architecture nazwa_architektury of nazwa_jednostki is [czesc_deklaracyjna: typy, sygnaly_wewnetrzne, stale] begin instrukcja_wspolbiezna;](https://slidetodoc.com/presentation_image_h2/655d4e5a52b5e93a0b74e657e0263f91/image-14.jpg)

Architecture – składnia architecture nazwa_architektury of nazwa_jednostki is [czesc_deklaracyjna: typy, sygnaly_wewnetrzne, stale] begin instrukcja_wspolbiezna; --cialo architektury end nazwa_architektury; Przykład: architecture bramka_nand of nand 3 is begin y <= not (x 1 and x 2 and x 3); end bramka_nand;

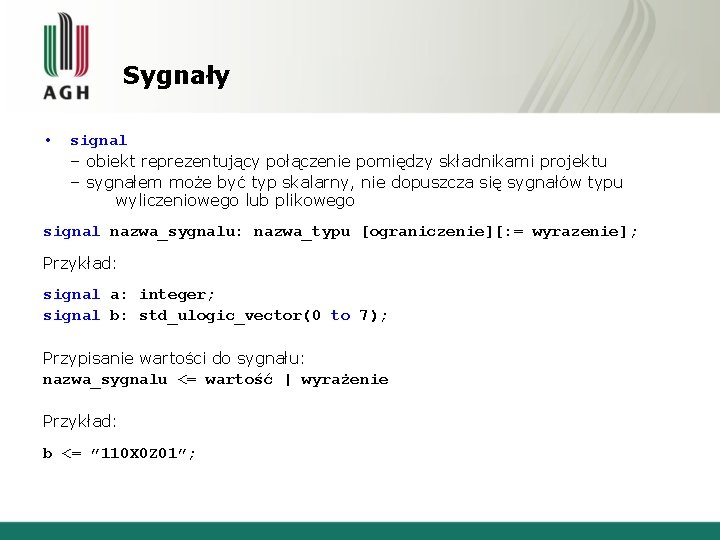

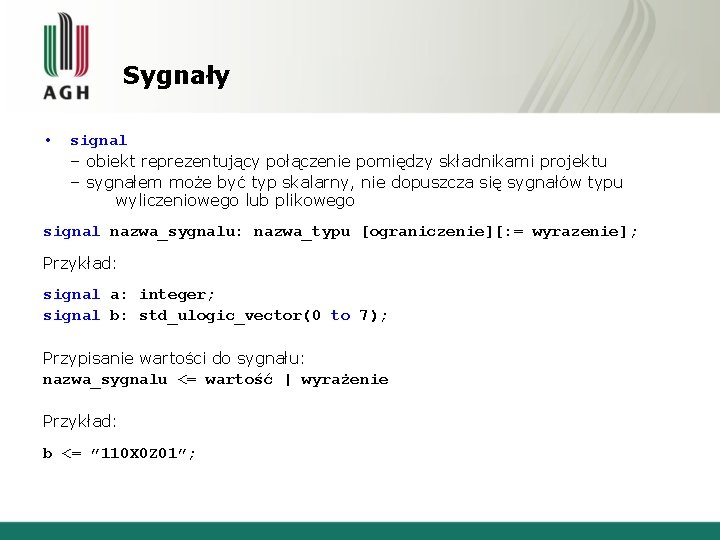

Sygnały • signal – obiekt reprezentujący połączenie pomiędzy składnikami projektu – sygnałem może być typ skalarny, nie dopuszcza się sygnałów typu wyliczeniowego lub plikowego signal nazwa_sygnalu: nazwa_typu [ograniczenie][: = wyrazenie]; Przykład: signal a: integer; signal b: std_ulogic_vector(0 to 7); Przypisanie wartości do sygnału: nazwa_sygnalu <= wartość | wyrażenie Przykład: b <= ” 110 X 0 Z 01”;

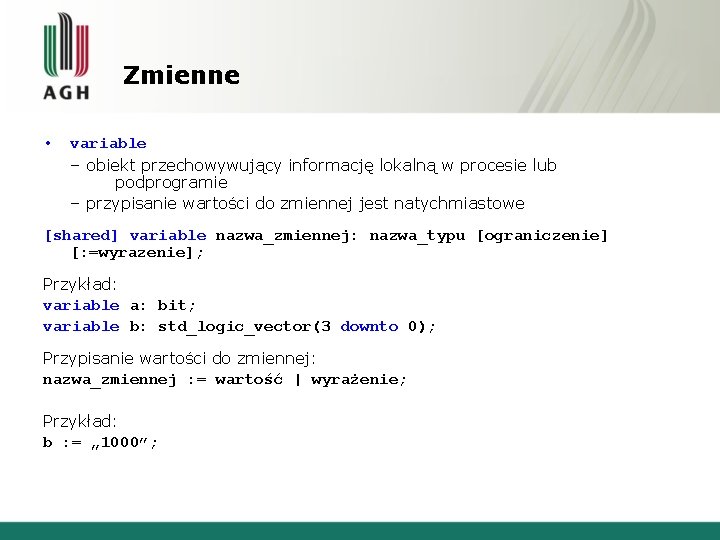

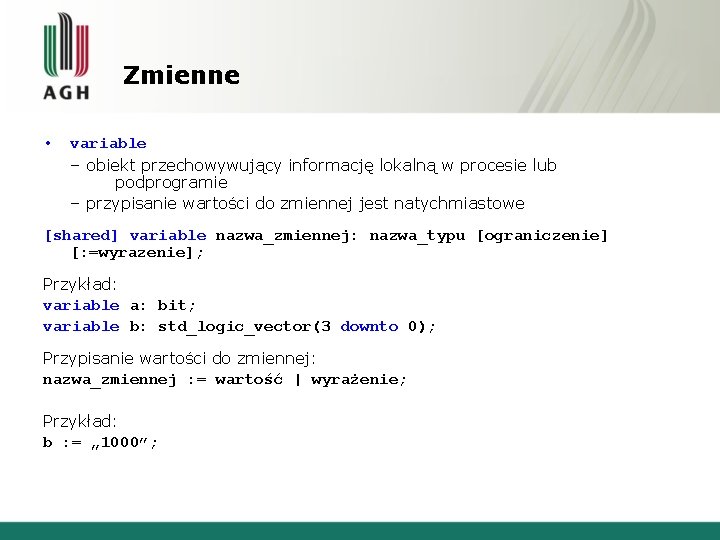

Zmienne • variable – obiekt przechowywujący informację lokalną w procesie lub podprogramie – przypisanie wartości do zmiennej jest natychmiastowe [shared] variable nazwa_zmiennej: nazwa_typu [ograniczenie] [: =wyrazenie]; Przykład: variable a: bit; variable b: std_logic_vector(3 downto 0); Przypisanie wartości do zmiennej: nazwa_zmiennej : = wartość | wyrażenie; Przykład: b : = „ 1000”;

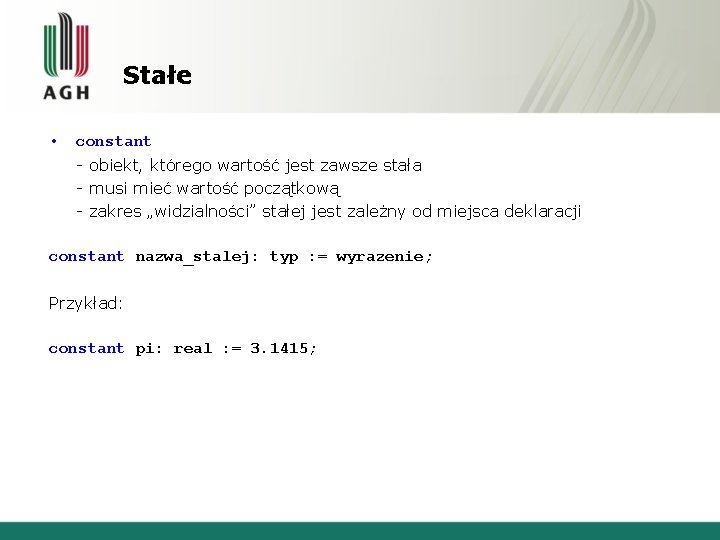

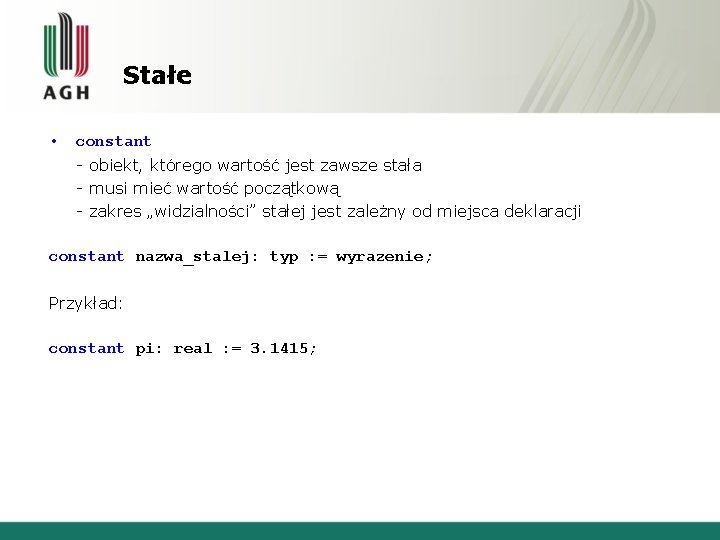

Stałe • constant - obiekt, którego wartość jest zawsze stała - musi mieć wartość początkową - zakres „widzialności” stałej jest zależny od miejsca deklaracji constant nazwa_stalej: typ : = wyrazenie; Przykład: constant pi: real : = 3. 1415;

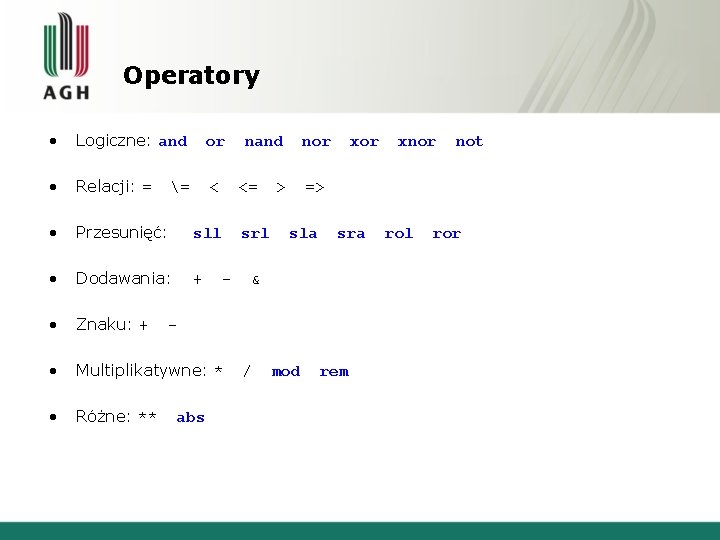

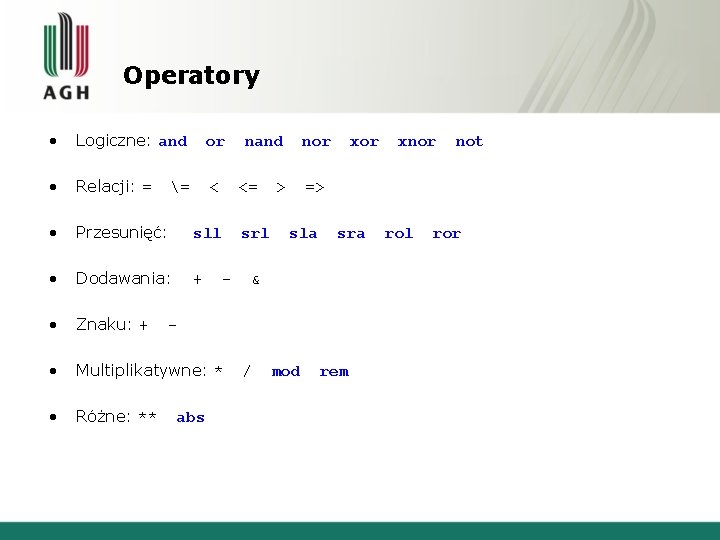

Operatory • Logiczne: and or • Relacji: = < • Przesunięć: sll • Dodawania: + • Znaku: + • Multiplikatywne: * • Różne: ** = nand <= srl - nor > xor sla sra - abs not => & / xnor mod rem rol ror

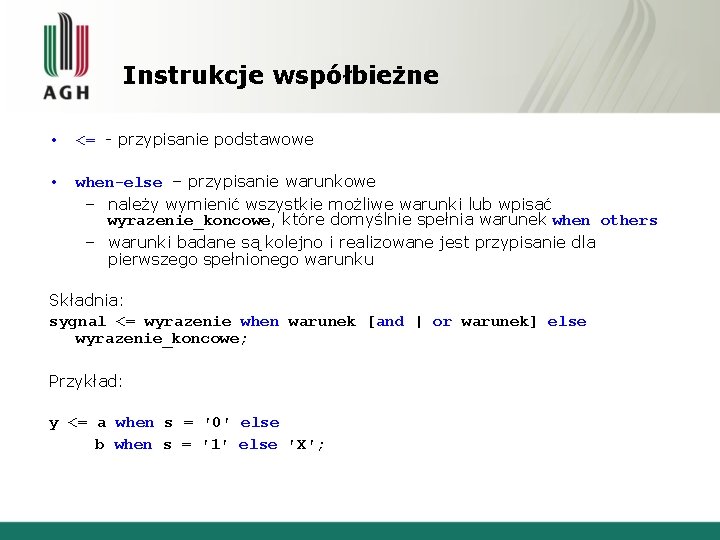

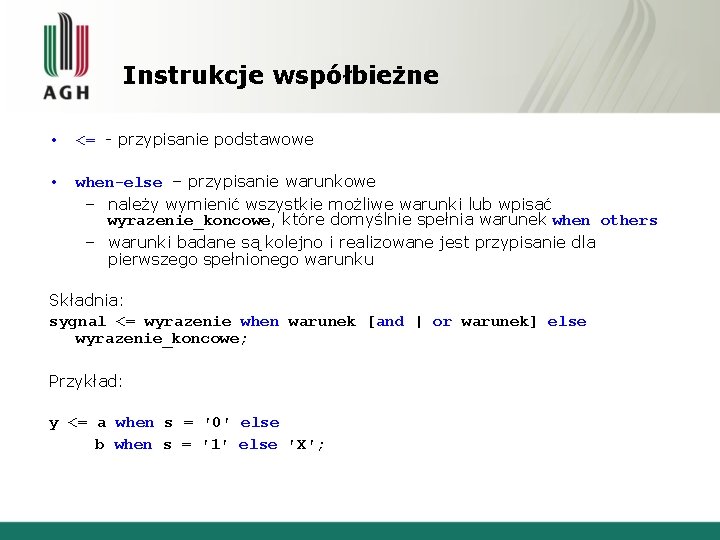

Instrukcje współbieżne • <= - przypisanie podstawowe • when-else – przypisanie warunkowe – należy wymienić wszystkie możliwe warunki lub wpisać wyrazenie_koncowe, które domyślnie spełnia warunek when others – warunki badane są kolejno i realizowane jest przypisanie dla pierwszego spełnionego warunku Składnia: sygnal <= wyrazenie when warunek [and | or warunek] else wyrazenie_koncowe; Przykład: y <= a when s = ′ 0′ else b when s = ′ 1′ else ′X′;

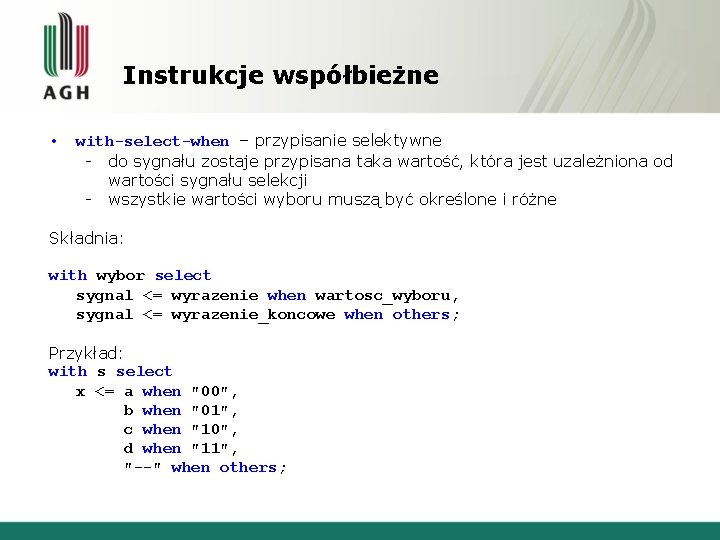

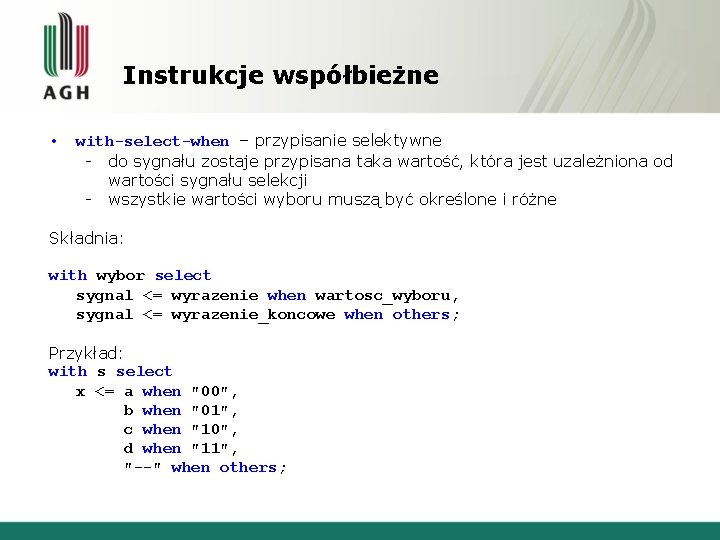

Instrukcje współbieżne • with-select-when – przypisanie selektywne - do sygnału zostaje przypisana taka wartość, która jest uzależniona od wartości sygnału selekcji - wszystkie wartości wyboru muszą być określone i różne Składnia: with wybor select sygnal <= wyrazenie when wartosc_wyboru, sygnal <= wyrazenie_koncowe when others; Przykład: with s select x <= a when ″ 00″, b when ″ 01″, c when ″ 10″, d when ″ 11″, ″--″ when others;

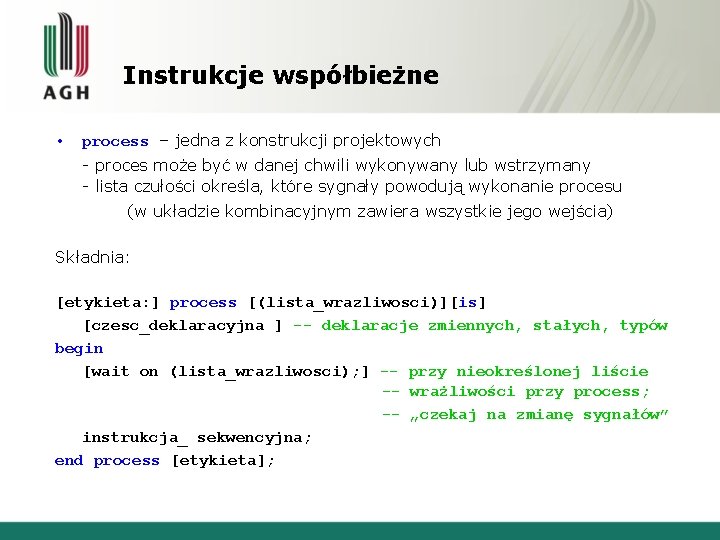

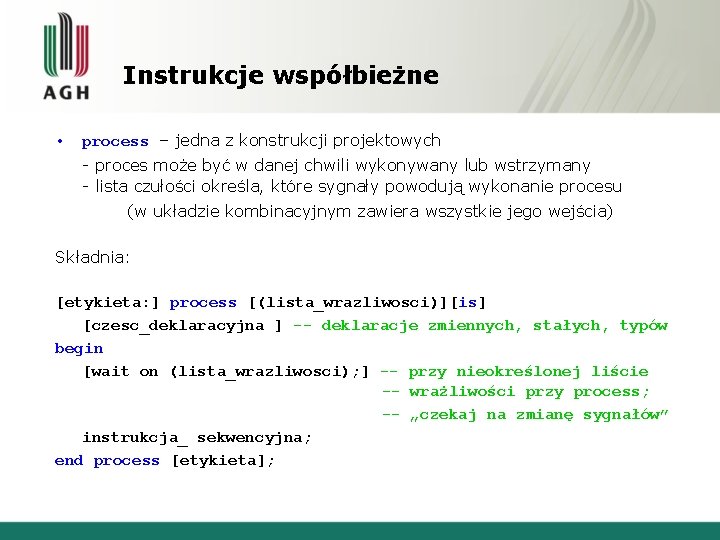

Instrukcje współbieżne • process – jedna z konstrukcji projektowych - proces może być w danej chwili wykonywany lub wstrzymany - lista czułości określa, które sygnały powodują wykonanie procesu (w układzie kombinacyjnym zawiera wszystkie jego wejścia) Składnia: [etykieta: ] process [(lista_wrazliwosci)][is] [czesc_deklaracyjna ] -- deklaracje zmiennych, stałych, typów begin [wait on (lista_wrazliwosci); ] -- przy nieokreślonej liście -- wrażliwości przy process; -- „czekaj na zmianę sygnałów” instrukcja_ sekwencyjna; end process [etykieta];

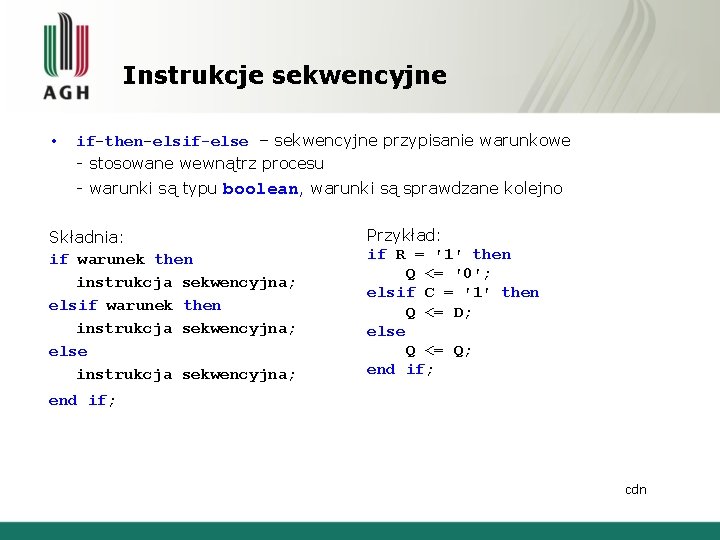

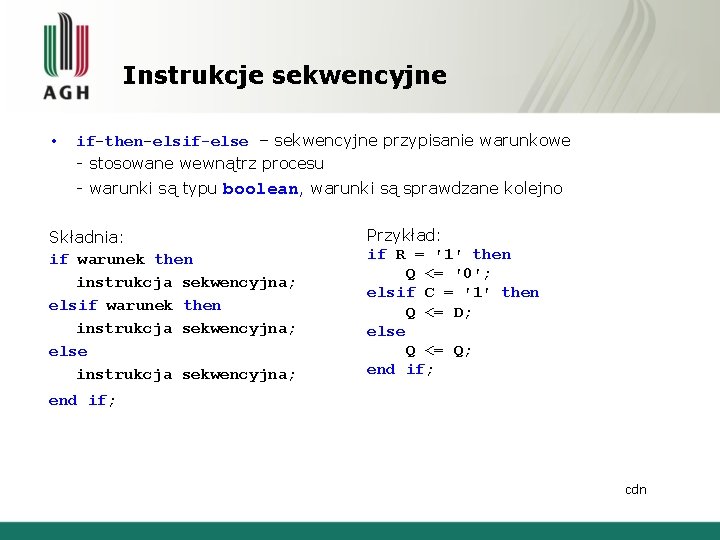

Instrukcje sekwencyjne • if-then-elsif-else – sekwencyjne przypisanie warunkowe - stosowane wewnątrz procesu - warunki są typu boolean, warunki są sprawdzane kolejno Składnia: if warunek then instrukcja sekwencyjna; else instrukcja sekwencyjna; Przykład: if R = ′ 1′ then Q <= ′ 0′; elsif C = ′ 1′ then Q <= D; else Q <= Q; end if; cdn

Filtr iir

Filtr iir Federacja bibliotek cyfrowych

Federacja bibliotek cyfrowych Zasada działania aparatu cyfrowego

Zasada działania aparatu cyfrowego Technik cyfrowych procesów graficznych praca

Technik cyfrowych procesów graficznych praca Projektowanie konceptualne

Projektowanie konceptualne Projektowanie aplikacji internetowych

Projektowanie aplikacji internetowych Projektowanie magazynów

Projektowanie magazynów Cechy sieci komputerowej

Cechy sieci komputerowej Projektowanie systemów logistycznych

Projektowanie systemów logistycznych Projektowanie aplikacji webowych

Projektowanie aplikacji webowych Projektowanie betonu metodą trzech równań przykłady

Projektowanie betonu metodą trzech równań przykłady Mikroteoria

Mikroteoria Postacie normalne

Postacie normalne Planowanie bazy danych

Planowanie bazy danych Komputerowe wspomaganie projektowania

Komputerowe wspomaganie projektowania Simulador vhdl

Simulador vhdl Vhdl programlama

Vhdl programlama Modelsim tutorial vhdl

Modelsim tutorial vhdl Vhdl entity declaration

Vhdl entity declaration Finite state machine vhdl testbench

Finite state machine vhdl testbench Ece 561

Ece 561 Vhdl

Vhdl Combinational logic vhdl

Combinational logic vhdl