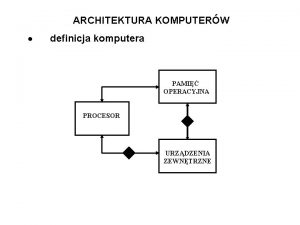

Ukady wejciawyjcia Magistrala Procesor Pami Ukady IO Ukady

- Slides: 26

Układy wejścia/wyjścia

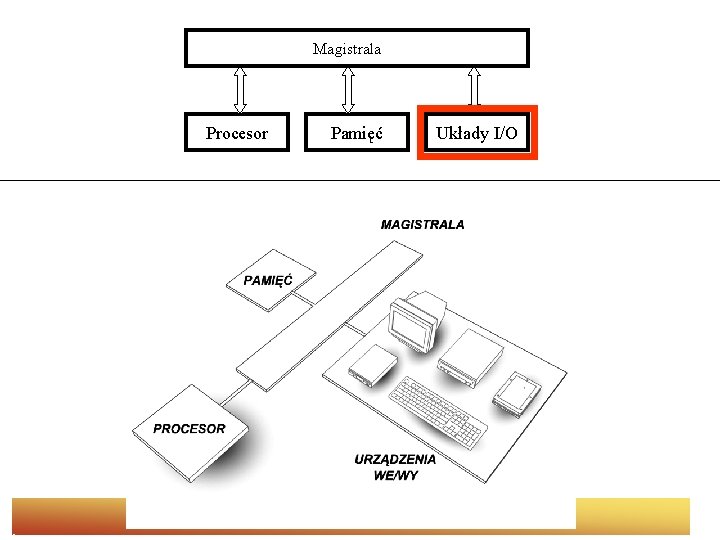

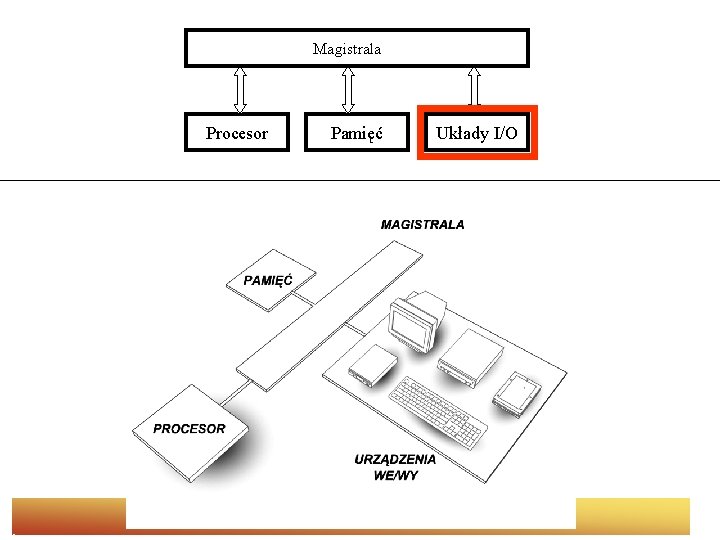

Magistrala Procesor Pamięć Układy I/O

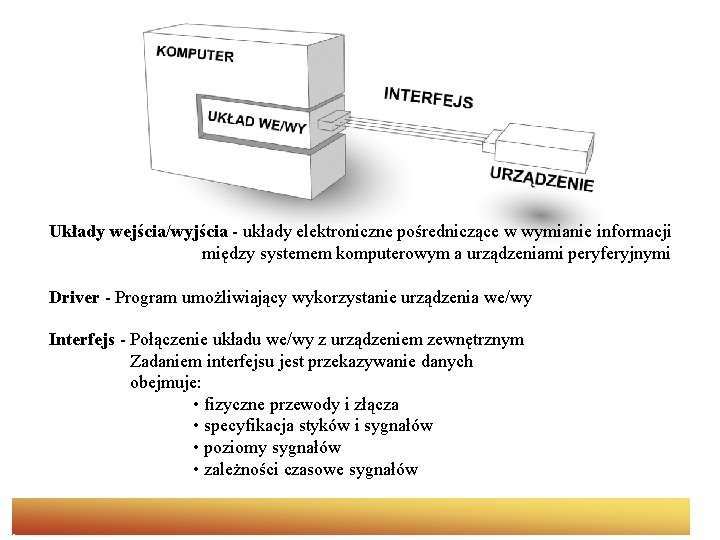

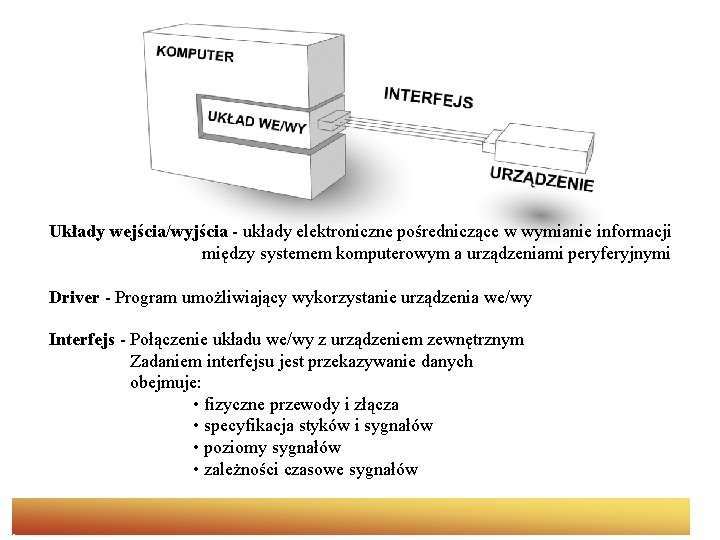

Układy wejścia/wyjścia - układy elektroniczne pośredniczące w wymianie informacji między systemem komputerowym a urządzeniami peryferyjnymi Driver - Program umożliwiający wykorzystanie urządzenia we/wy Interfejs - Połączenie układu we/wy z urządzeniem zewnętrznym Zadaniem interfejsu jest przekazywanie danych obejmuje: • fizyczne przewody i złącza • specyfikacja styków i sygnałów • poziomy sygnałów • zależności czasowe sygnałów

Organizacje normalizujące sprzęt komputerowy Organizacje międzynarodowe Organizacje krajowe Zrzeszenia producentów Producenci ISO - International Organization for Standarization (od gr. isos - równy) Międzynarodowa Organizacja Normalizacyjna http: //www. iso. org/ ISO jest pozarządową organizacją non-profit. Jej członkami mogą być wyłącznie agencje rządowe zajmujące się standaryzacją lub podobne do samego ISO pozarządowe organizacje standaryzacyjne, po jednej z każdego kraju. ISO nie posiada żadnej "mocy prawnej" do egzekwowania swoich norm.

ITU - International Telecommunications Union Międzynarodowa Unia Telekomunikacyjna http: //www. itu. int/ IEC - International Electrotechnical Commision Międzynarodowa Komisja Elektrotechniczna przygotowuje i publikuje standardy związane z elektrotechniką i elektroniką http: //www. iec. ch/ IEEE - Institute of Electrical and Electronics Engineers Instytut Inżynierów Elektryków i Elektroników http: //www. ieee. org/ ANSI - American National Standards Intitute - instytucja ustalająca normy http: //www. ansi. org/ VESA - Video Electronics Standards Association http: //www. vesa. org/ PN - Polskie Normy http: //www. pkn. pl/

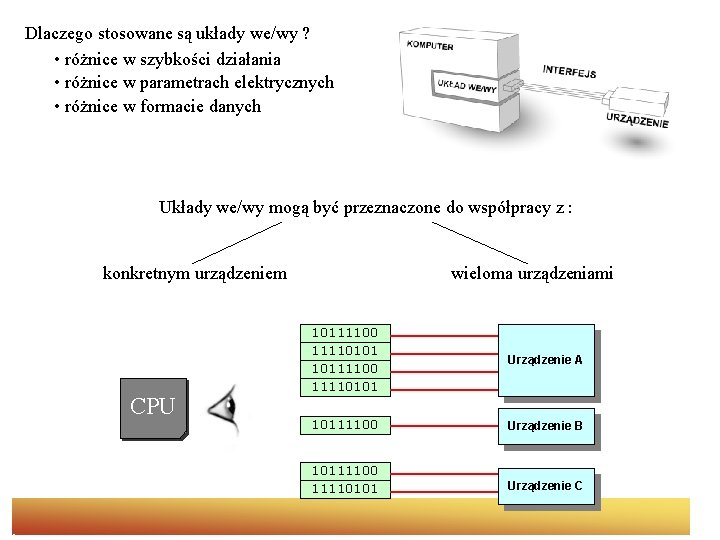

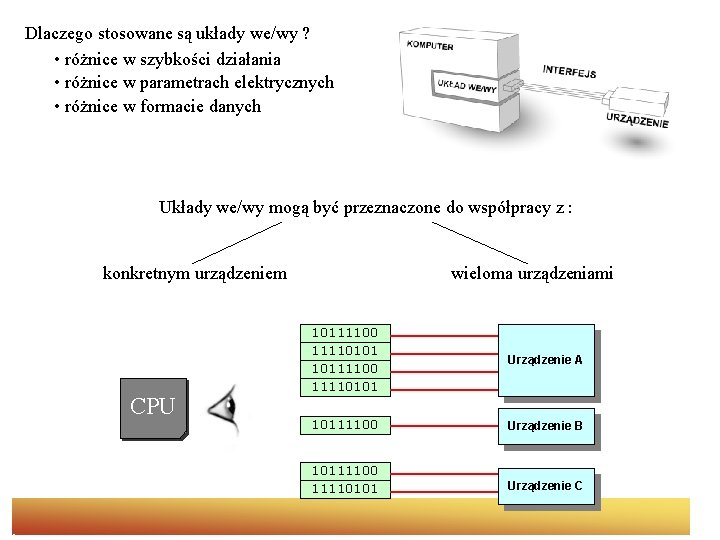

Dlaczego stosowane są układy we/wy ? • różnice w szybkości działania • różnice w parametrach elektrycznych • różnice w formacie danych Układy we/wy mogą być przeznaczone do współpracy z : konkretnym urządzeniem CPU wieloma urządzeniami 10111100 11110101 Urządzenie A 10111100 Urządzenie B 10111100 11110101 Urządzenie C

W zależności od sposobu komunikowania się z systemem układy we/wy dzielimy na : • układy współadresowalne z pamięcią operacyjną sterowanie Urządzenie pamięć CPU magistrala adresowa Urządzenie • układy izolowane pamięć sterowanie CPU magistrala adresowa I/O

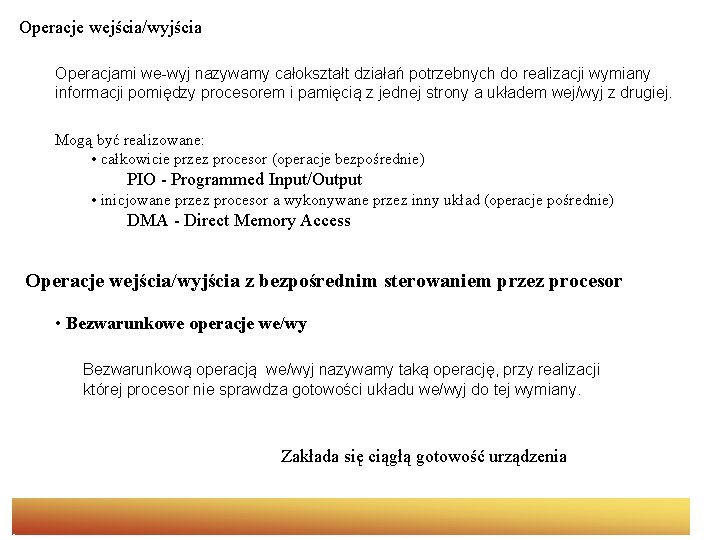

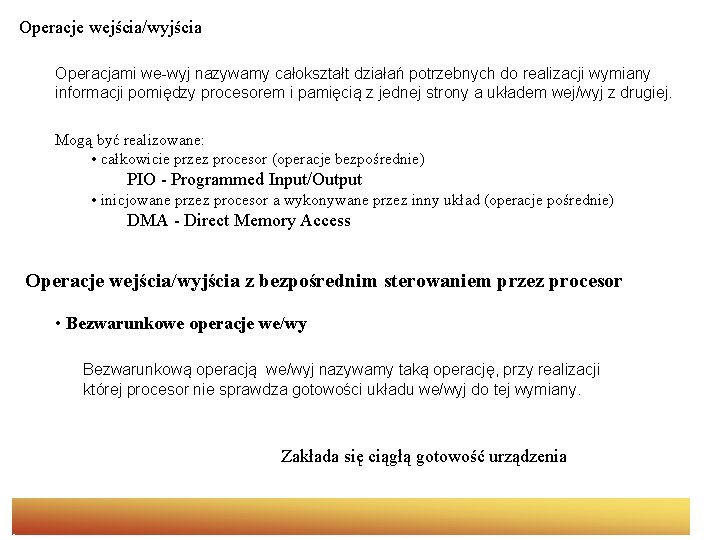

Operacje wejścia/wyjścia Operacjami we-wyj nazywamy całokształt działań potrzebnych do realizacji wymiany informacji pomiędzy procesorem i pamięcią z jednej strony a układem wej/wyj z drugiej. Mogą być realizowane: • całkowicie przez procesor (operacje bezpośrednie) PIO - Programmed Input/Output • inicjowane przez procesor a wykonywane przez inny układ (operacje pośrednie) DMA - Direct Memory Access Operacje wejścia/wyjścia z bezpośrednim sterowaniem przez procesor • Bezwarunkowe operacje we/wy Bezwarunkową operacją we/wyj nazywamy taką operację, przy realizacji której procesor nie sprawdza gotowości układu we/wyj do tej wymiany. Zakłada się ciągłą gotowość urządzenia

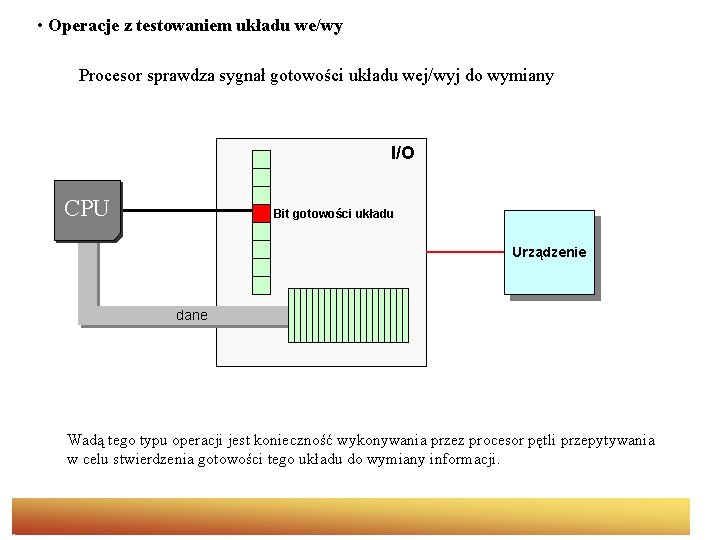

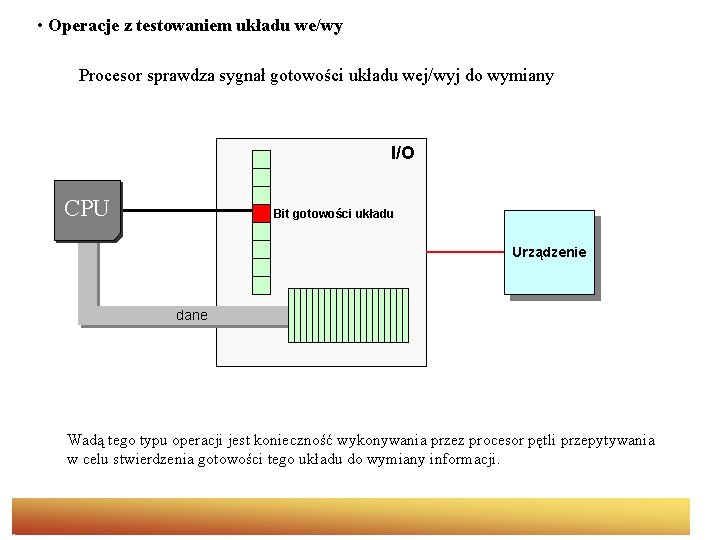

• Operacje z testowaniem układu we/wy Procesor sprawdza sygnał gotowości układu wej/wyj do wymiany I/O CPU Bit gotowości układu Urządzenie dane Wadą tego typu operacji jest konieczność wykonywania przez procesor pętli przepytywania w celu stwierdzenia gotowości tego układu do wymiany informacji.

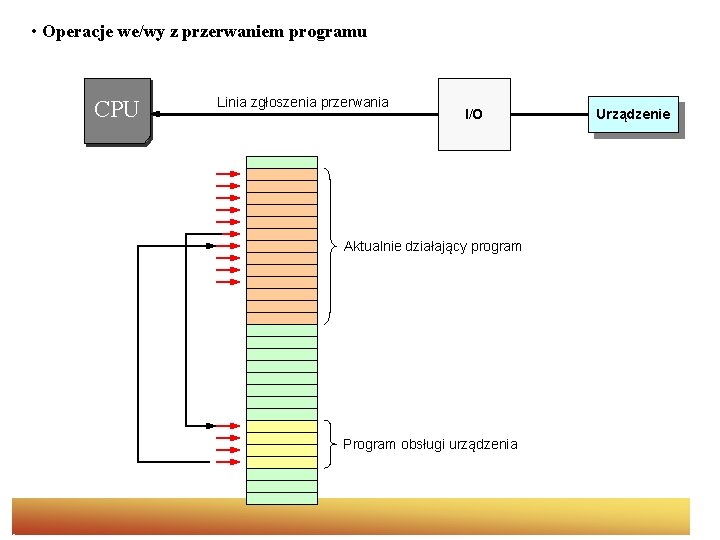

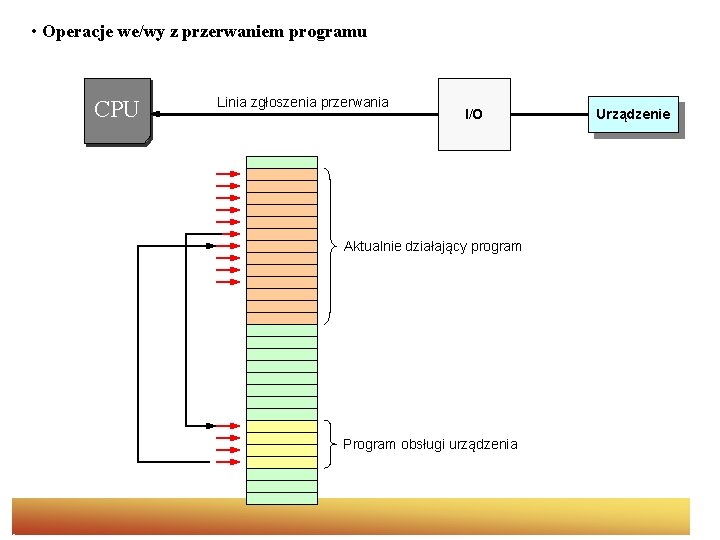

• Operacje we/wy z przerwaniem programu CPU Linia zgłoszenia przerwania I/O Aktualnie działający program Program obsługi urządzenia Urządzenie

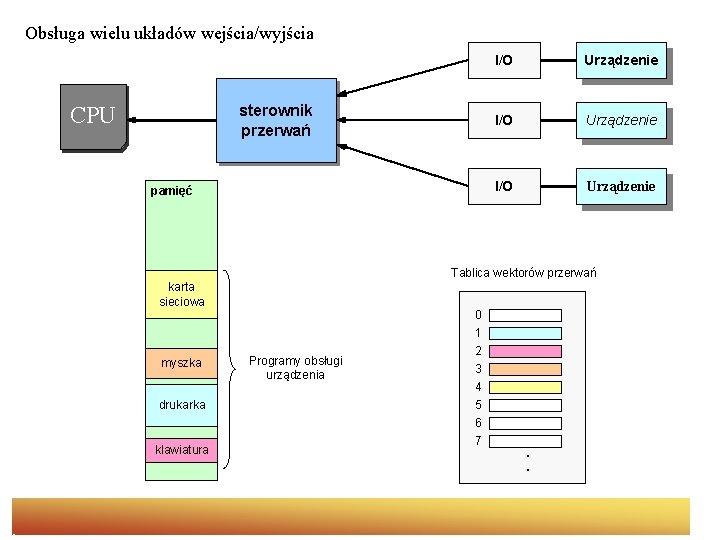

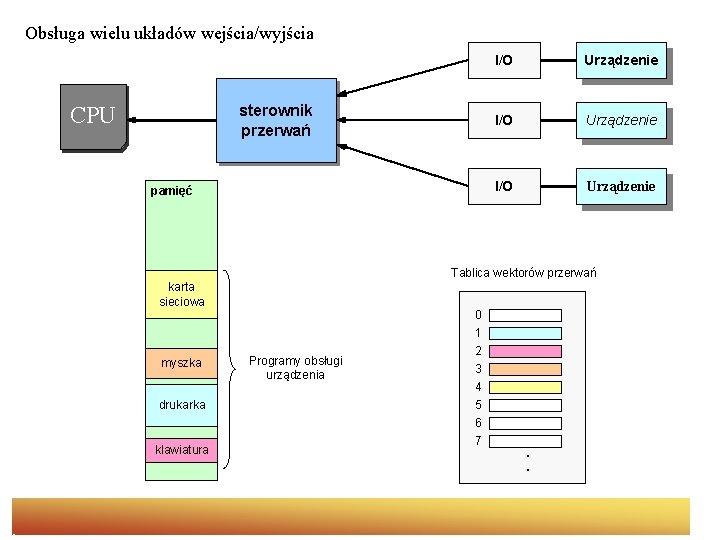

Obsługa wielu układów wejścia/wyjścia CPU sterownik przerwań pamięć I/O Urządzenie Tablica wektorów przerwań karta sieciowa myszka drukarka klawiatura Programy obsługi urządzenia 0 1 2 3 4 5 6 7 . .

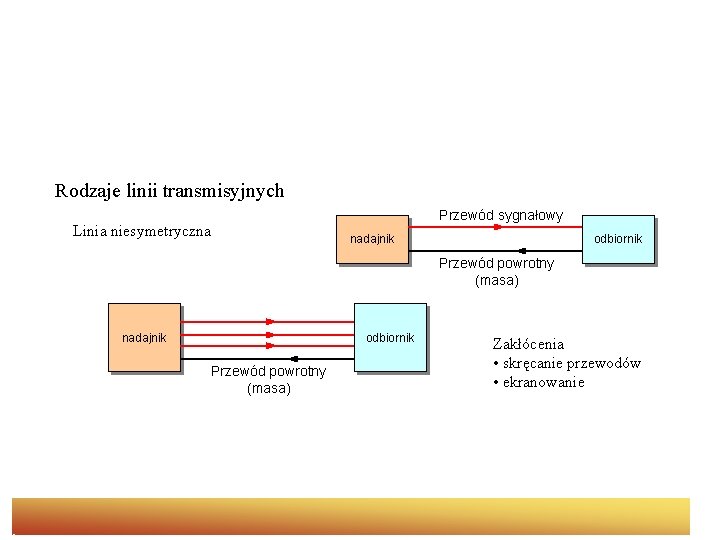

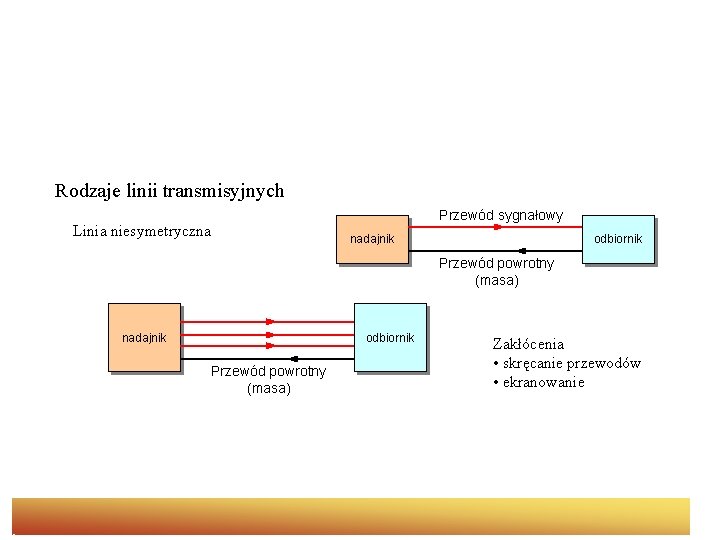

Rodzaje linii transmisyjnych Linia niesymetryczna Przewód sygnałowy nadajnik odbiornik Przewód powrotny (masa) Zakłócenia • skręcanie przewodów • ekranowanie

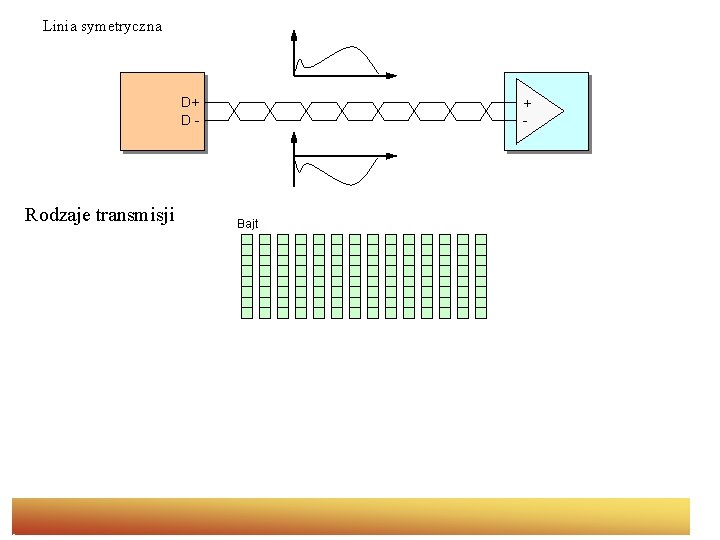

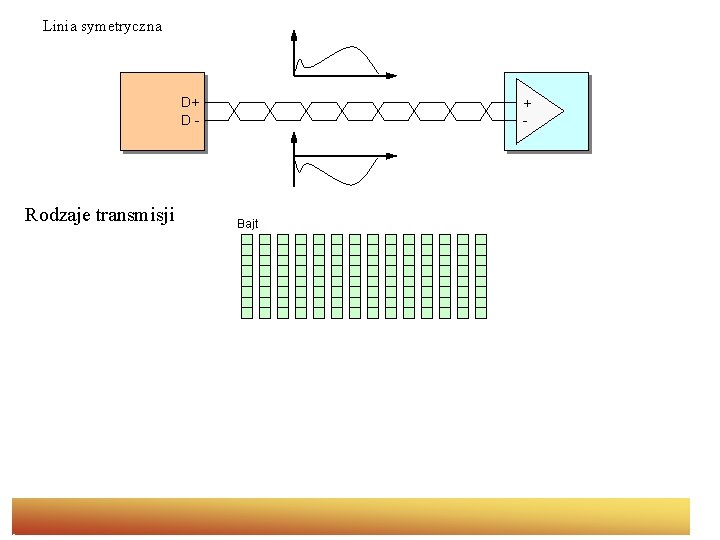

Linia symetryczna D+ D- Rodzaje transmisji + - Bajt

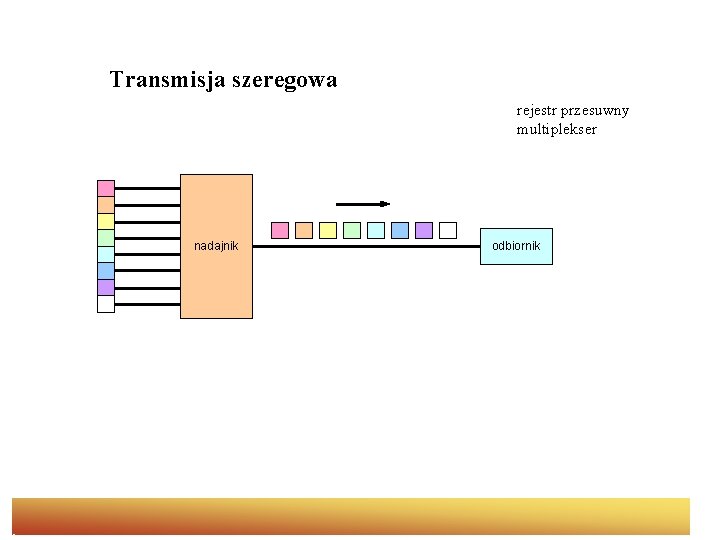

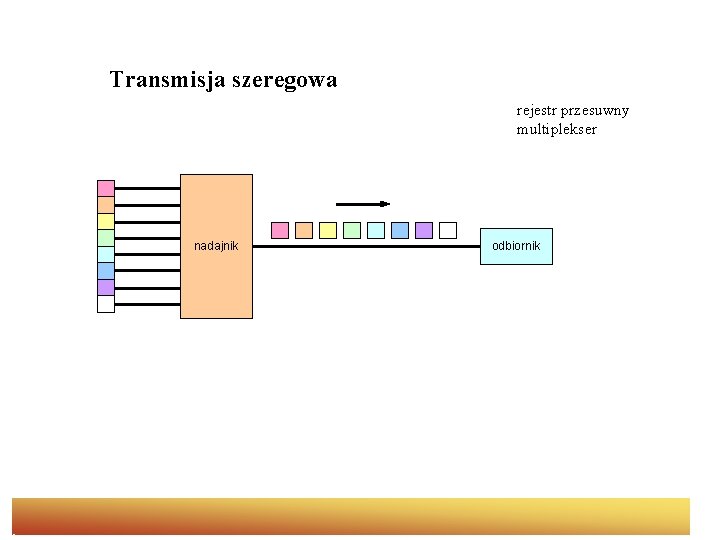

Transmisja szeregowa rejestr przesuwny multiplekser nadajnik odbiornik

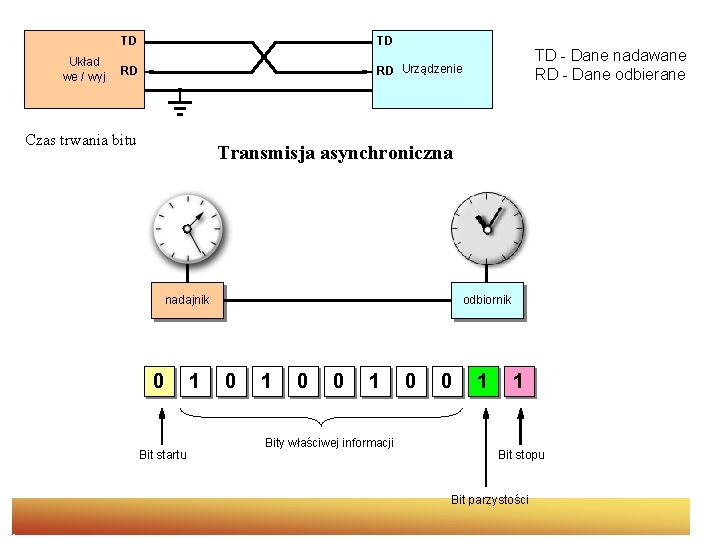

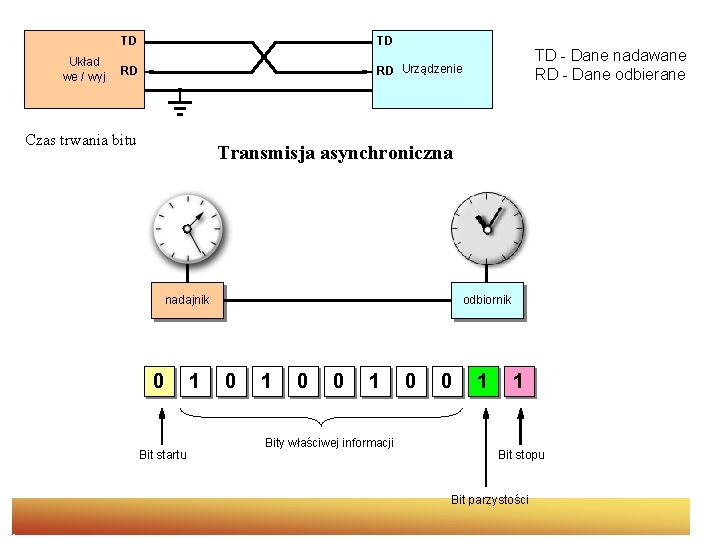

Układ we / wyj TD TD RD RD Urządzenie Czas trwania bitu TD - Dane nadawane RD - Dane odbierane Transmisja asynchroniczna nadajnik 0 Bit startu 1 odbiornik 0 1 0 0 1 Bity właściwej informacji 0 0 1 1 Bit stopu Bit parzystości

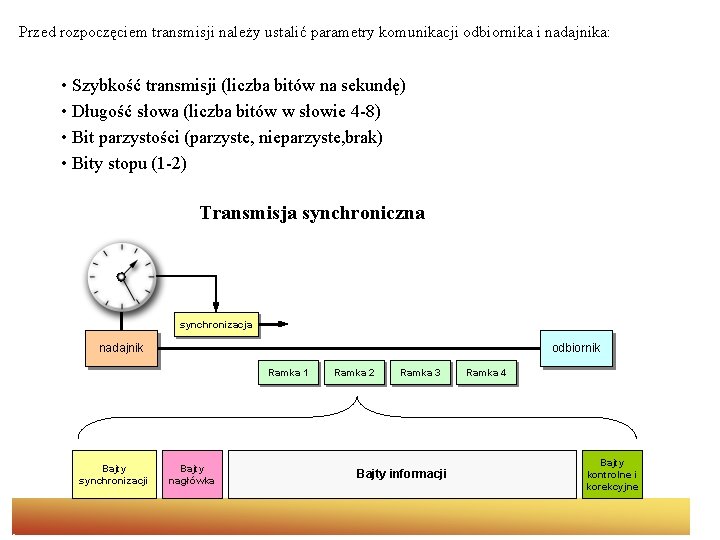

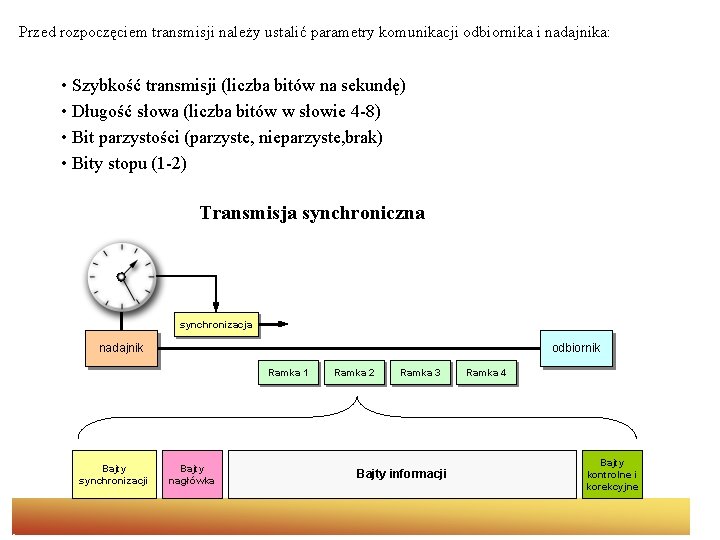

Przed rozpoczęciem transmisji należy ustalić parametry komunikacji odbiornika i nadajnika: • Szybkość transmisji (liczba bitów na sekundę) • Długość słowa (liczba bitów w słowie 4 -8) • Bit parzystości (parzyste, nieparzyste, brak) • Bity stopu (1 -2) Transmisja synchroniczna synchronizacja nadajnik odbiornik Ramka 1 Bajty synchronizacji Bajty nagłówka Ramka 2 Ramka 3 Bajty informacji Ramka 4 Bajty kontrolne i korekcyjne

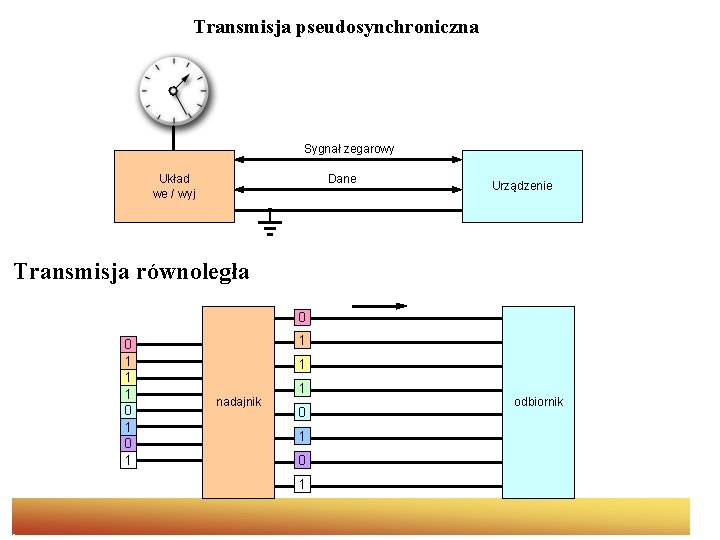

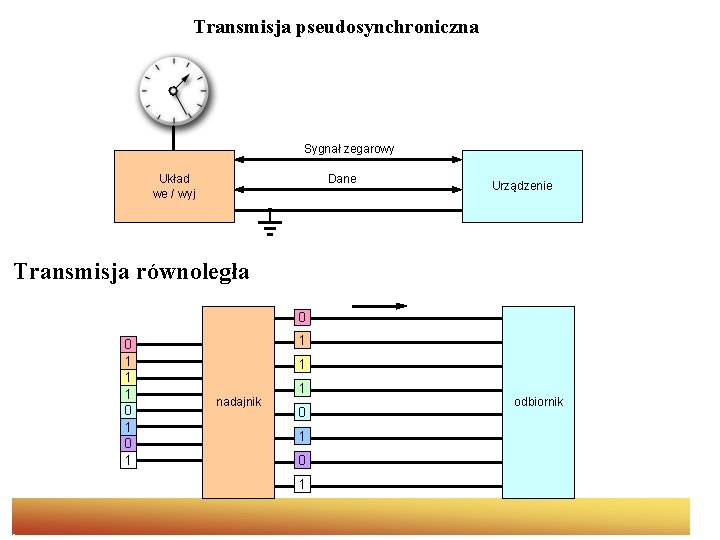

Transmisja pseudosynchroniczna Sygnał zegarowy Dane Układ we / wyj Urządzenie Transmisja równoległa 0 0 1 1 1 nadajnik 1 0 1 odbiornik

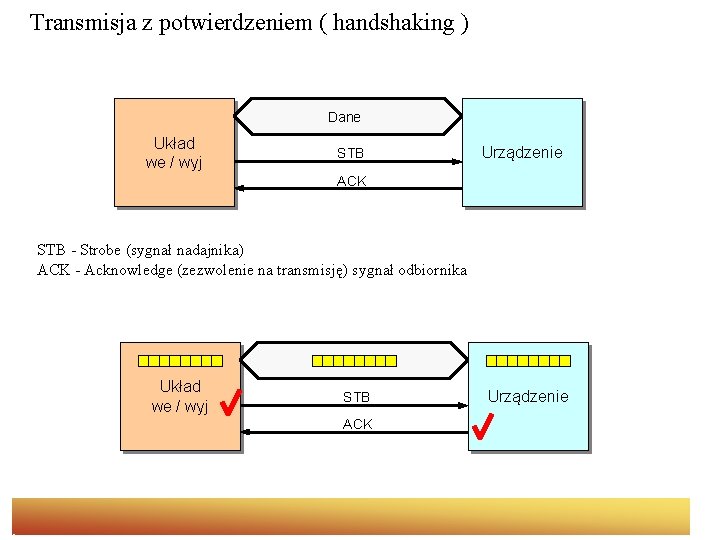

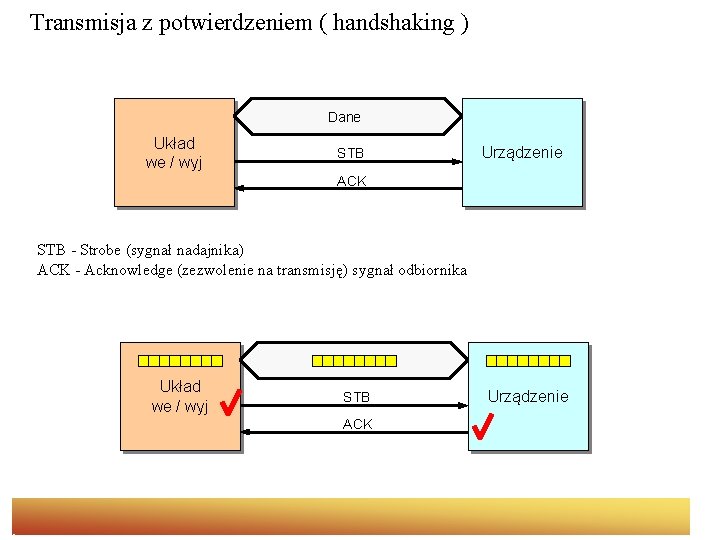

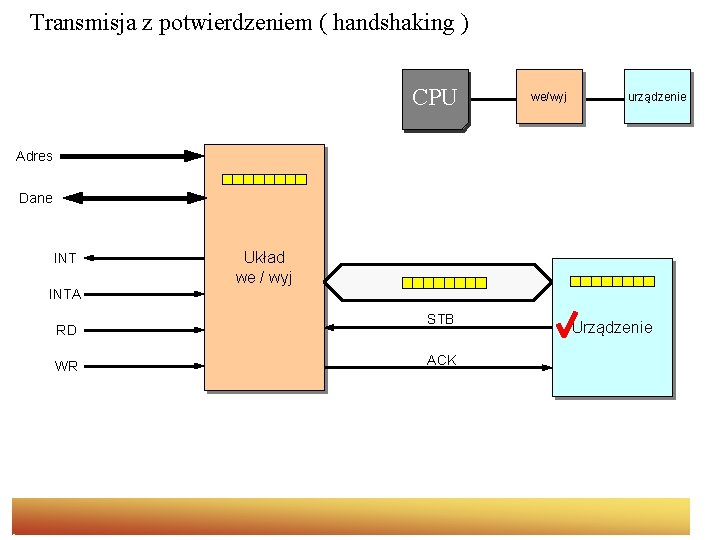

Transmisja z potwierdzeniem ( handshaking ) Dane Układ we / wyj STB Urządzenie ACK STB - Strobe (sygnał nadajnika) ACK - Acknowledge (zezwolenie na transmisję) sygnał odbiornika Dane Układ we / wyj STB ACK Urządzenie

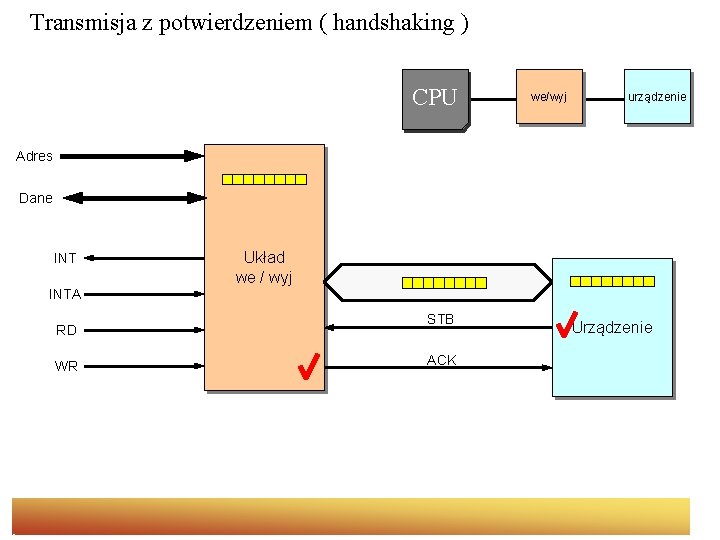

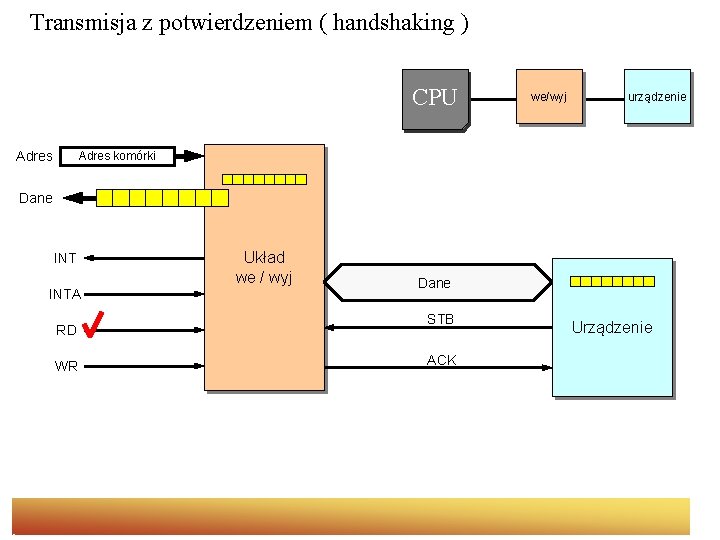

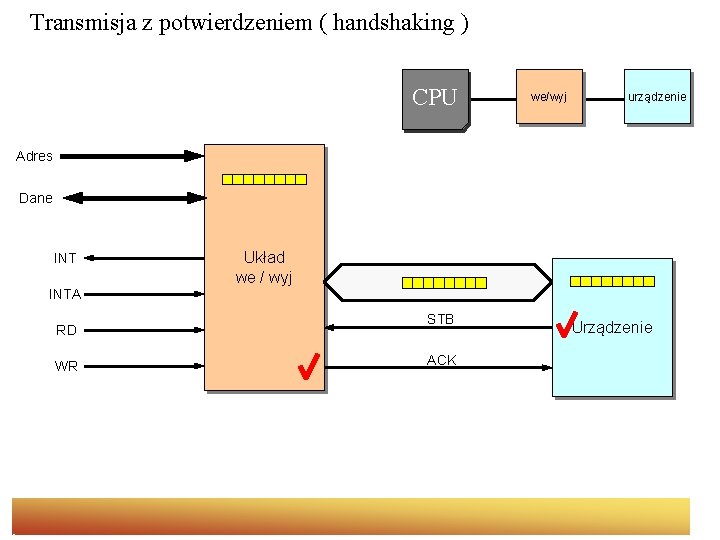

Transmisja z potwierdzeniem ( handshaking ) CPU we/wyj urządzenie Adres Dane INTA RD WR Układ we / wyj Dane STB ACK Urządzenie

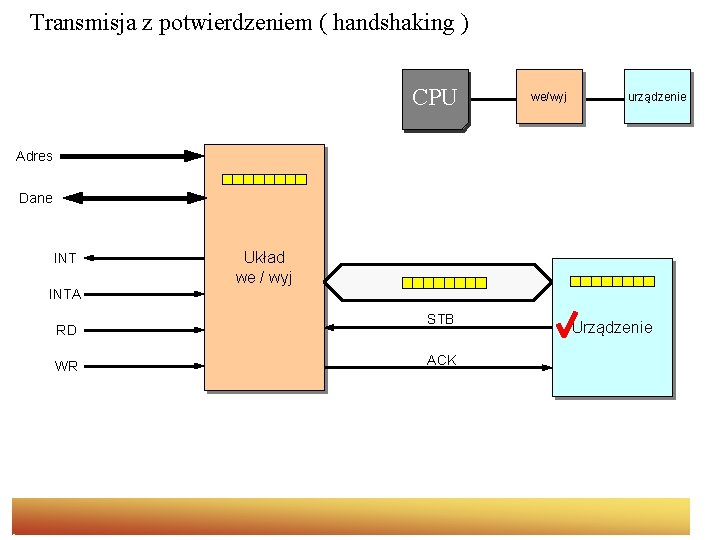

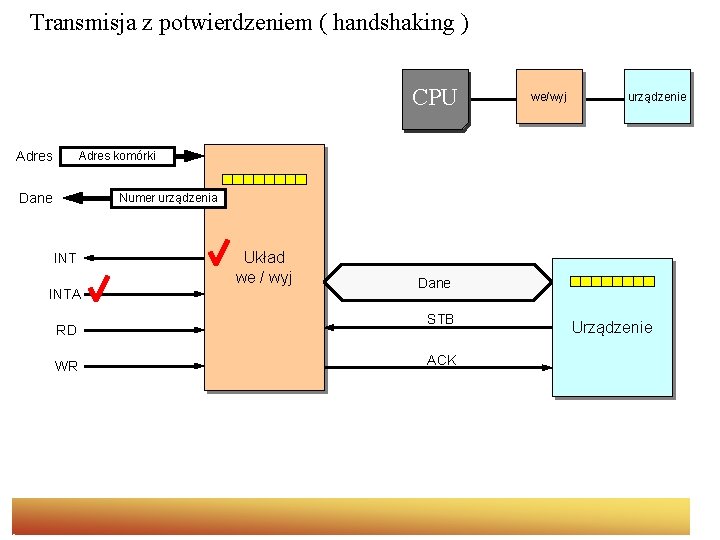

Transmisja z potwierdzeniem ( handshaking ) CPU we/wyj urządzenie Adres Dane INTA RD WR Układ we / wyj Dane STB ACK Urządzenie

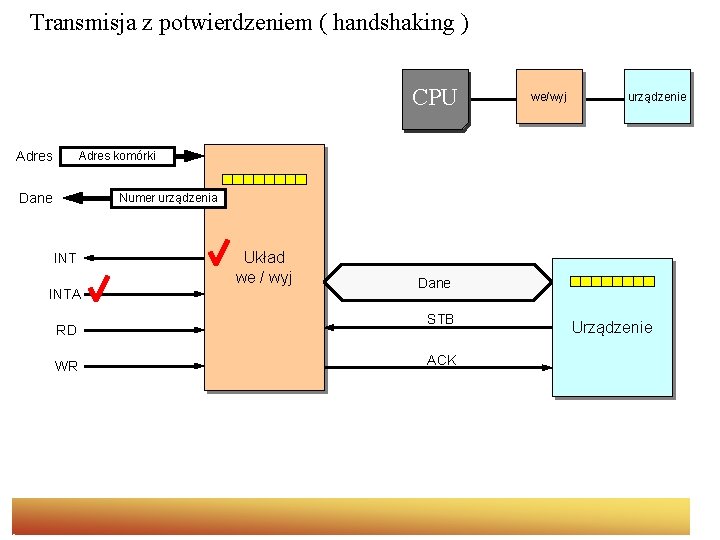

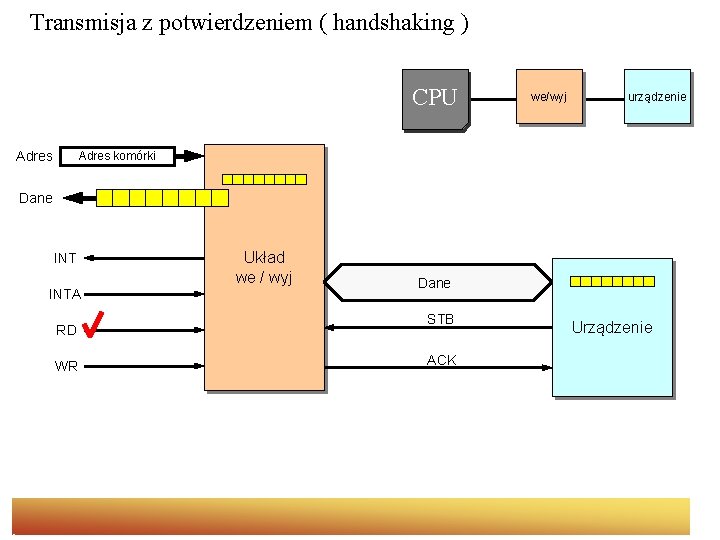

Transmisja z potwierdzeniem ( handshaking ) CPU Adres we/wyj urządzenie Adres komórki Dane Numer urządzenia INTA RD WR Układ we / wyj Dane STB ACK Urządzenie

Transmisja z potwierdzeniem ( handshaking ) CPU Adres we/wyj urządzenie Adres komórki Dane INTA RD WR Układ we / wyj Dane STB ACK Urządzenie

Przerwanie (ang. interrupt) lub żądanie przerwania (IRQ Interrupt Re. Quest) Przerwanie (ang. interrupt) lub żądanie przerwania (IRQ - Interrupt Re. Quest) – sygnał powodujący zmianę przepływu sterowania, niezależnie od aktualnie wykonywanego programu. Pojawienie się przerwania powoduje wstrzymanie aktualnie wykonywanego programu i wykonanie przez procesor kodu procedury obsługi przerwania (ang. interrupt handler).

Sprzętowe: 1. Zewnętrzne – sygnał przerwania pochodzi z zewnętrznego układu obsługującego przerwania sprzętowe; przerwania te służą do komunikacji z urządzeniami zewnętrznymi, np. z klawiaturą, napędami dysków itp. 2. Wewnętrzne, nazywane wyjątkami (ang. exceptions) – zgłaszane przez procesor dla sygnalizowania sytuacji wyjątkowych (np. dzielenie przez zero); dzielą się na trzy grupy:

dzielą się na trzy grupy: 1. faults (niepowodzenie) – sytuacje, w których aktualnie wykonywana instrukcja powoduje błąd; gdy procesor powraca do wykonywania przerwanego kodu wykonuje następną, po tej która wywołała wyjątek, instrukcję; 2. traps (pułapki) – sytuacja, która nie jest błędem, jej wystąpienie ma na celu wykonanie określonego kodu; wykorzystywane przede wszystkim w debugerach; gdy procesor powraca do wykonywania przerwanego kodu tę samą instrukcję która wywołała wyjątek; 3. aborts – błędy, których nie można naprawić.

Programowe – z kodu programu wywoływana jest procedura obsługi przerwania; najczęściej wykorzystywane do komunikacji z systemem operacyjnym, który w procedurze obsługi przerwania (np. w DOS 21 h, 2 fh, Windows 2 fh, Linux x 86 przerwanie 80 h) umieszcza kod wywołujący odpowiednie funkcje systemowe w zależności od zawartości rejestrów ustawionych przez program wywołujący, lub oprogramowaniem wbudowanym jak procedury BIOS lub firmware.

Pami katalog

Pami katalog Pami ram

Pami ram Pami?? ta?mowa

Pami?? ta?mowa Pci magistrala

Pci magistrala Magistrala informatika

Magistrala informatika Vrste magistrala

Vrste magistrala Magistrala isa

Magistrala isa Servisna magistrala organa

Servisna magistrala organa Magistrala lin bmw

Magistrala lin bmw Budowa komputera prezentacja

Budowa komputera prezentacja Magistrale rodzaje

Magistrale rodzaje Vrste magistrala

Vrste magistrala Magistrala

Magistrala Magistrale pci

Magistrale pci Apa yang dimaksud dengan pipeline

Apa yang dimaksud dengan pipeline Procesor je

Procesor je Centralni procesor

Centralni procesor Procesor cisc

Procesor cisc Procesor cpu

Procesor cpu Componentele software ale unui calculator

Componentele software ale unui calculator Co je to procesor

Co je to procesor Co jest sercem komputera

Co jest sercem komputera процесор

процесор Mips procesor

Mips procesor Zion procesor

Zion procesor