Projektowanie cyfrowych systemw w oparciu o ukady VLSI

![Koszt [CLB] dla różnych szerokości K wejścia i współczynnika mnożenia ekwiwalentny koszt 1 BSR Koszt [CLB] dla różnych szerokości K wejścia i współczynnika mnożenia ekwiwalentny koszt 1 BSR](https://slidetodoc.com/presentation_image/5f1914ab703cae237da101a7683b46f8/image-17.jpg)

- Slides: 30

Projektowanie cyfrowych systemów w oparciu o układy (VLSI i) PLD Ernest Jamro Kat. Elektroniki AGH, Kraków Układy mnożące, konwolwery

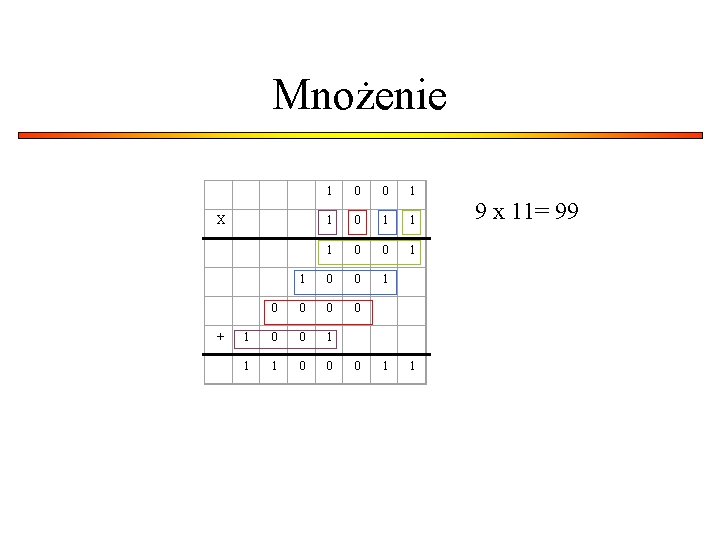

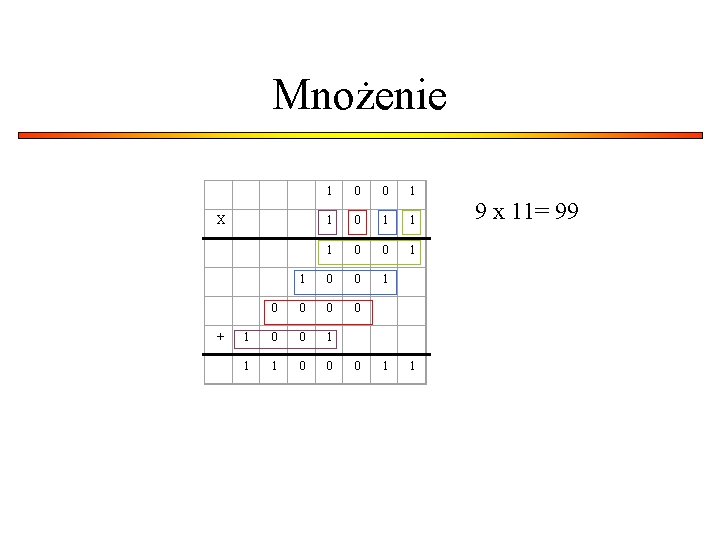

Mnożenie 1 0 0 1 X 1 0 1 1 1 0 0 1 0 0 + 1 0 0 1 1 1 0 0 0 1 1 9 x 11= 99

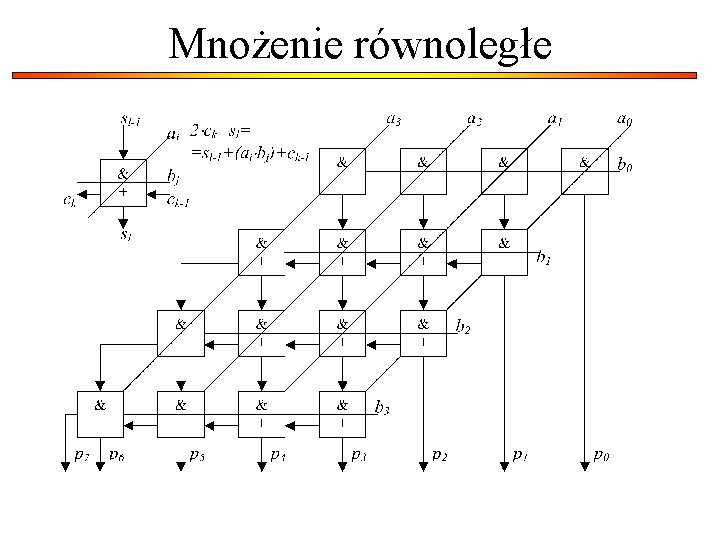

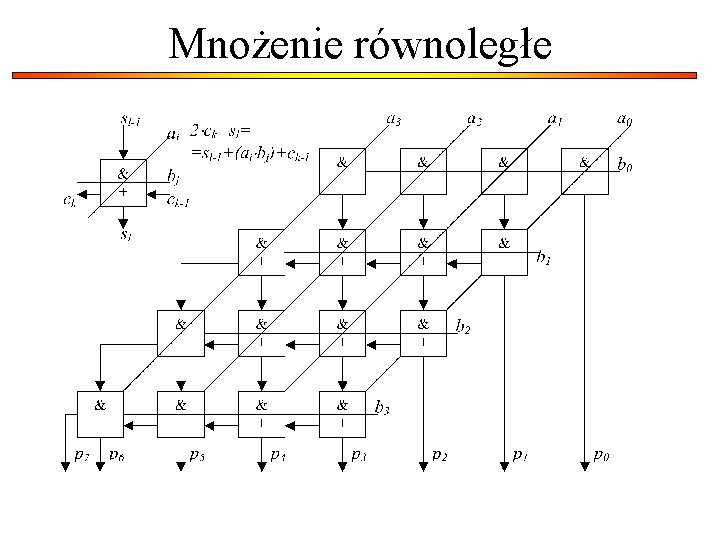

Mnożenie równoległe

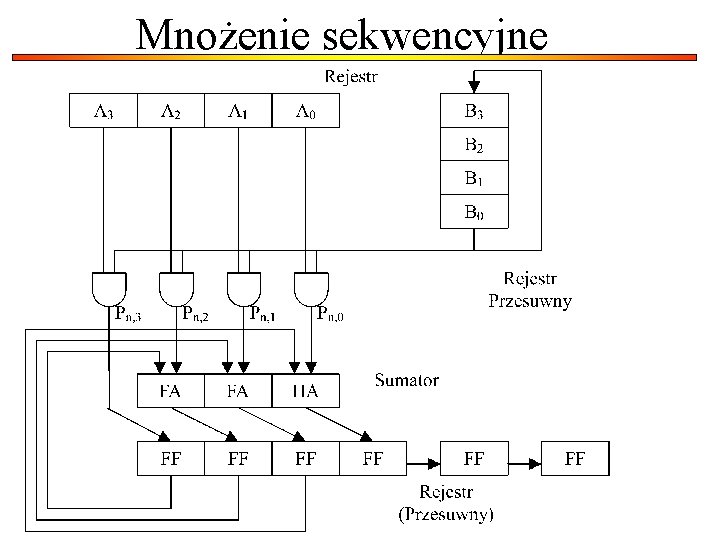

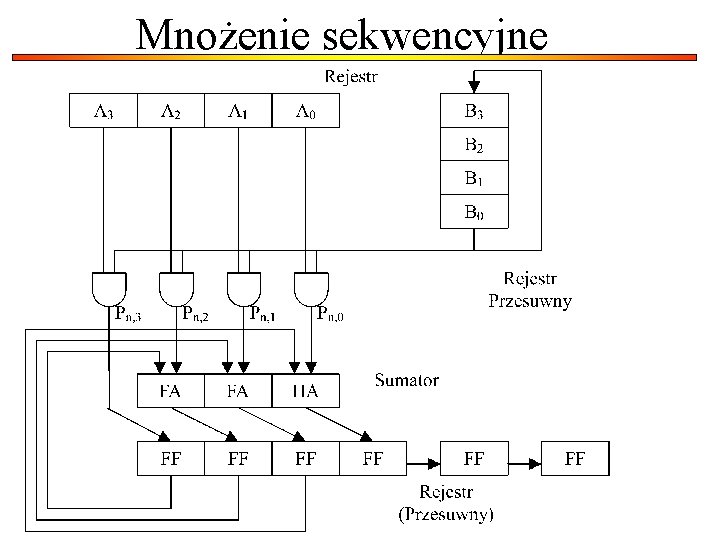

Mnożenie sekwencyjne

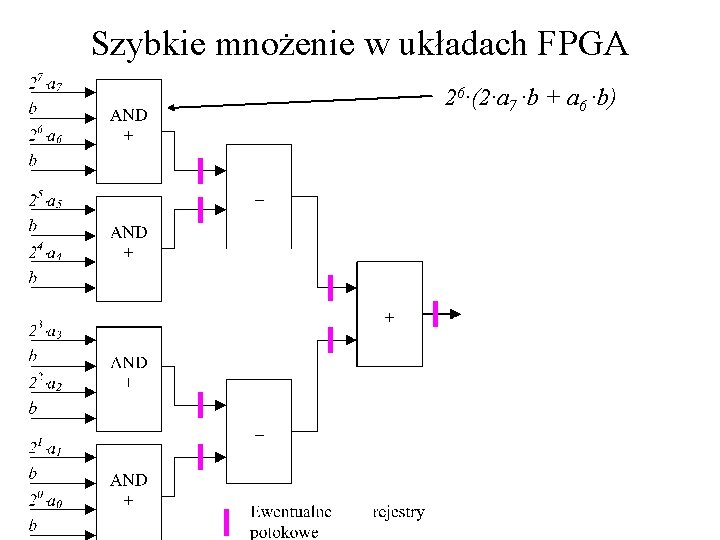

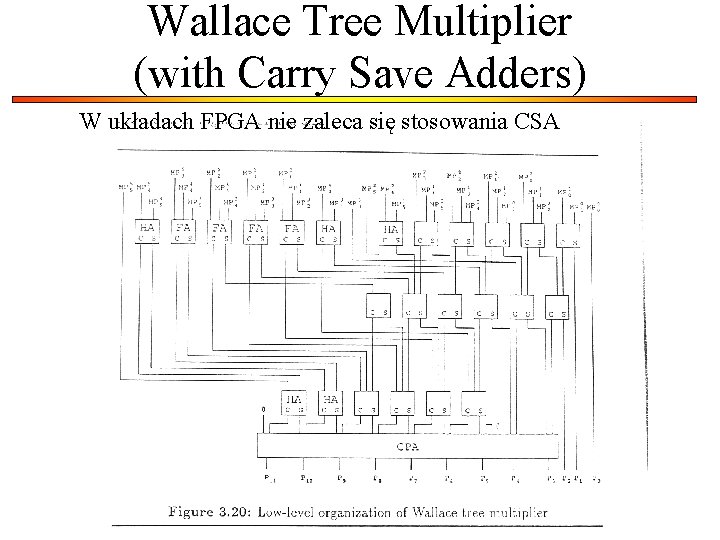

Wallace Tree Multiplier (with Carry Save Adders) W układach FPGA nie zaleca się stosowania CSA

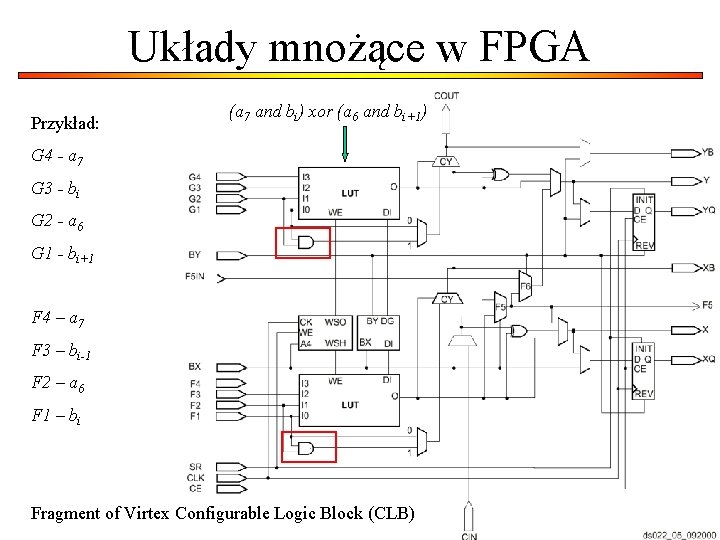

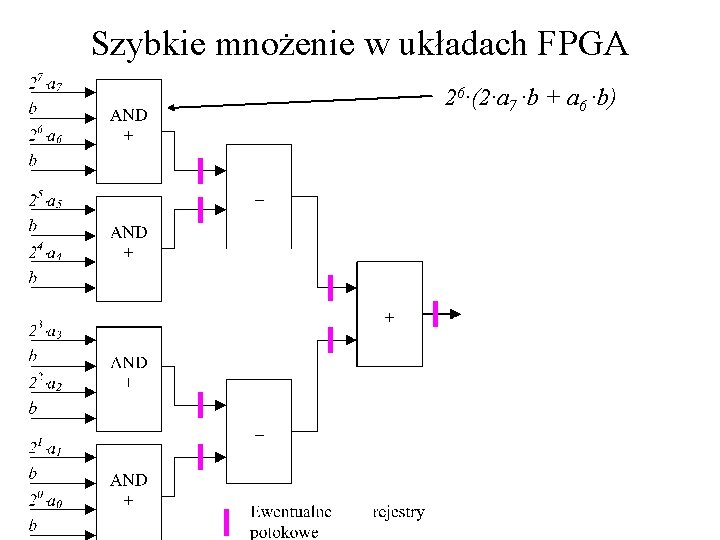

Szybkie mnożenie w układach FPGA 26·(2·a 7 ·b + a 6 ·b)

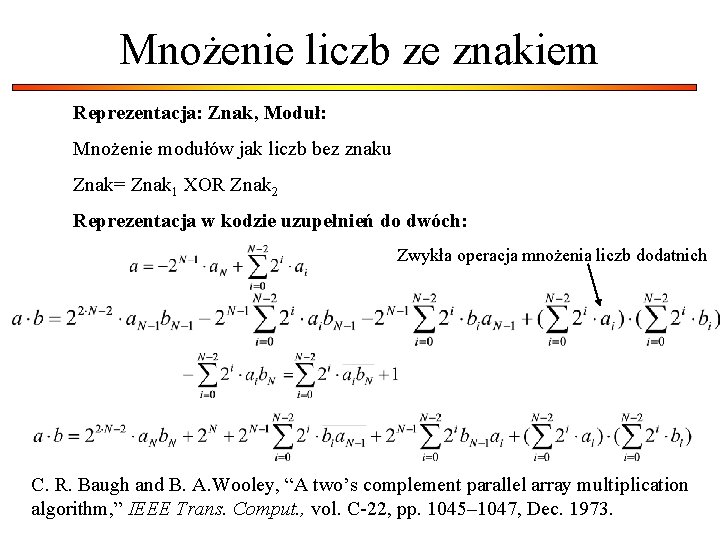

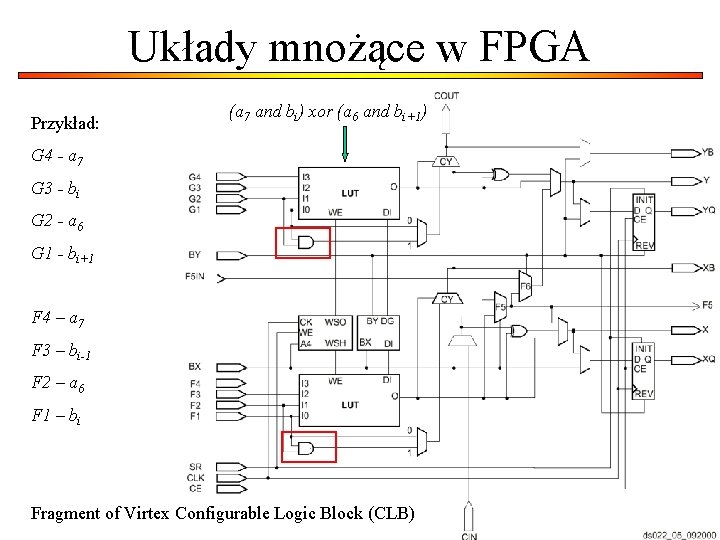

Układy mnożące w FPGA Przykład: (a 7 and bi) xor (a 6 and bi+1) G 4 - a 7 G 3 - bi G 2 - a 6 G 1 - bi+1 F 4 – a 7 F 3 – bi-1 F 2 – a 6 F 1 – bi Fragment of Virtex Configurable Logic Block (CLB)

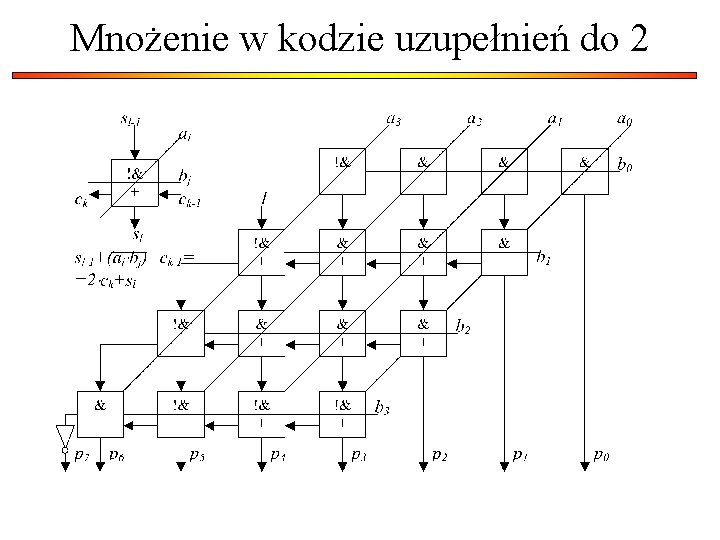

Mnożenie liczb ze znakiem Reprezentacja: Znak, Moduł: Mnożenie modułów jak liczb bez znaku Znak= Znak 1 XOR Znak 2 Reprezentacja w kodzie uzupełnień do dwóch: Zwykła operacja mnożenia liczb dodatnich C. R. Baugh and B. A. Wooley, “A two’s complement parallel array multiplication algorithm, ” IEEE Trans. Comput. , vol. C-22, pp. 1045– 1047, Dec. 1973.

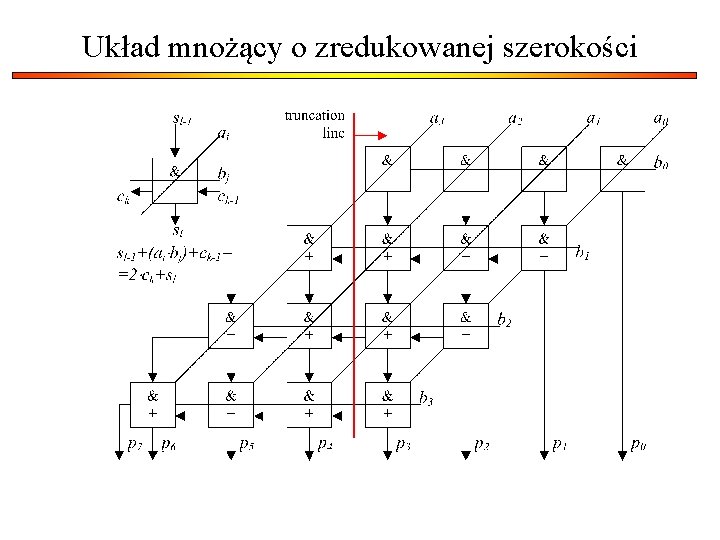

Mnożenie w kodzie uzupełnień do 2

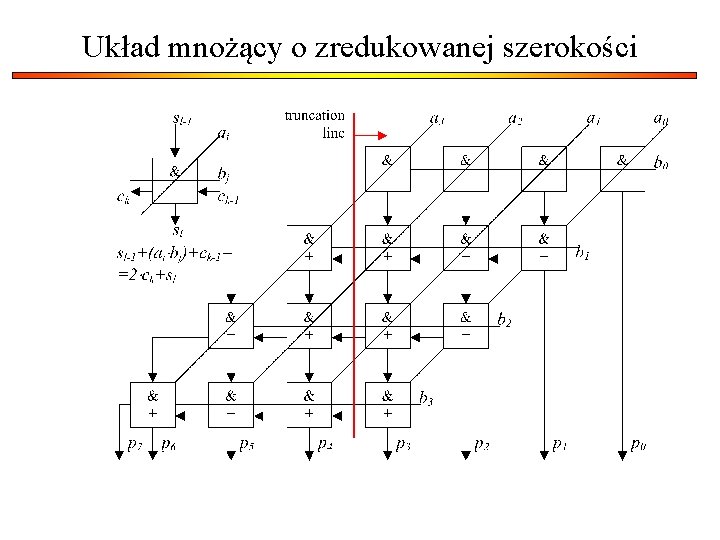

Układ mnożący o zredukowanej szerokości

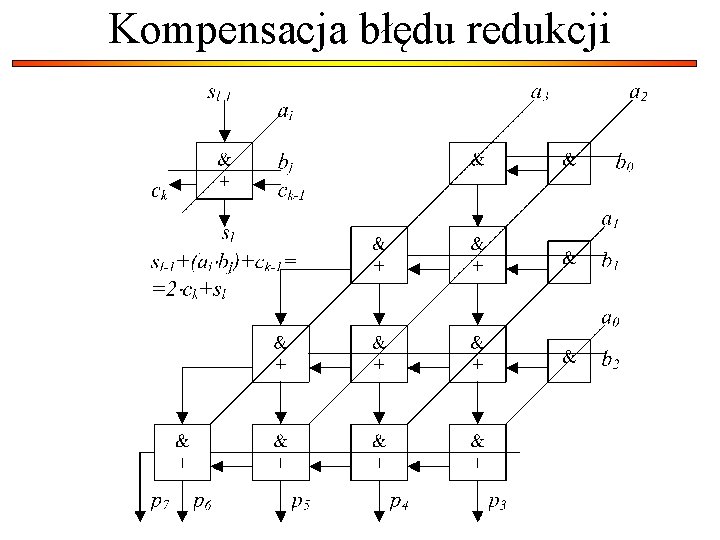

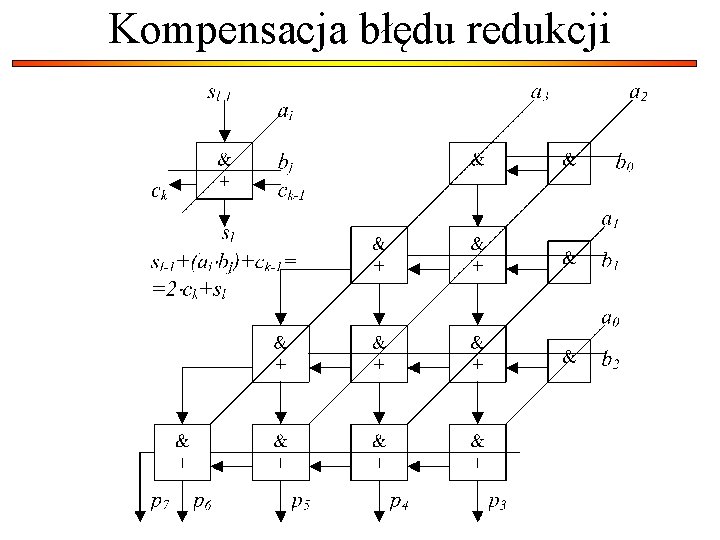

Kompensacja błędu redukcji

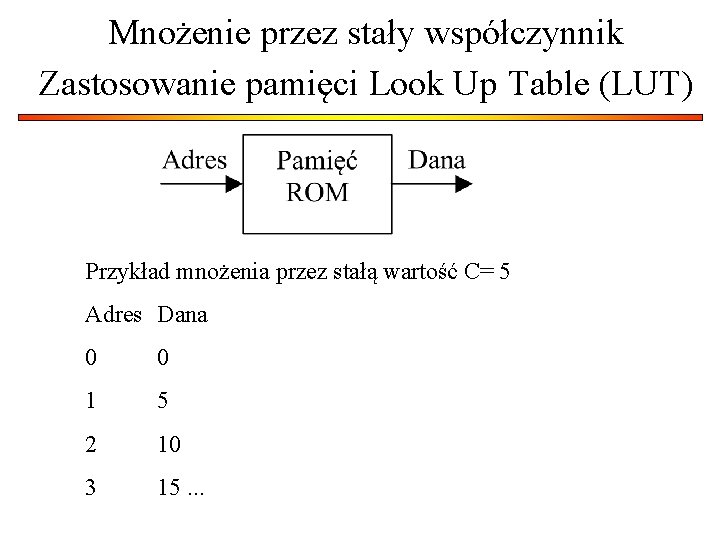

Mnożenie przez stały współczynnik Zastosowanie pamięci Look Up Table (LUT) Przykład mnożenia przez stałą wartość C= 5 Adres Dana 0 0 1 5 2 10 3 15. . .

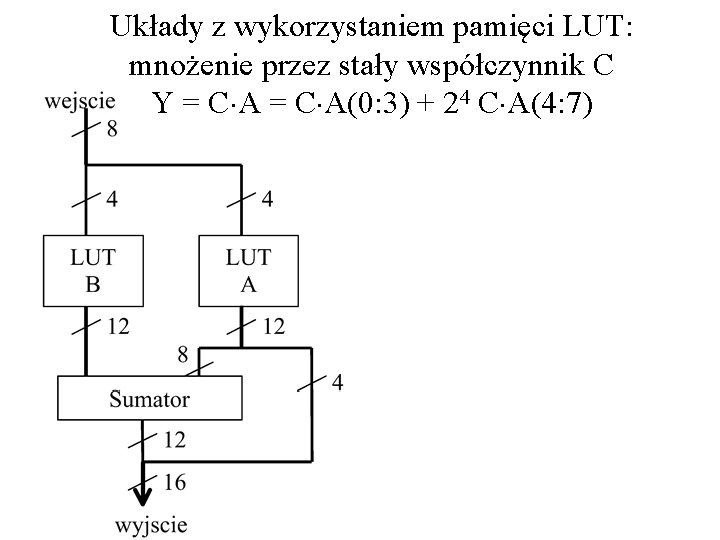

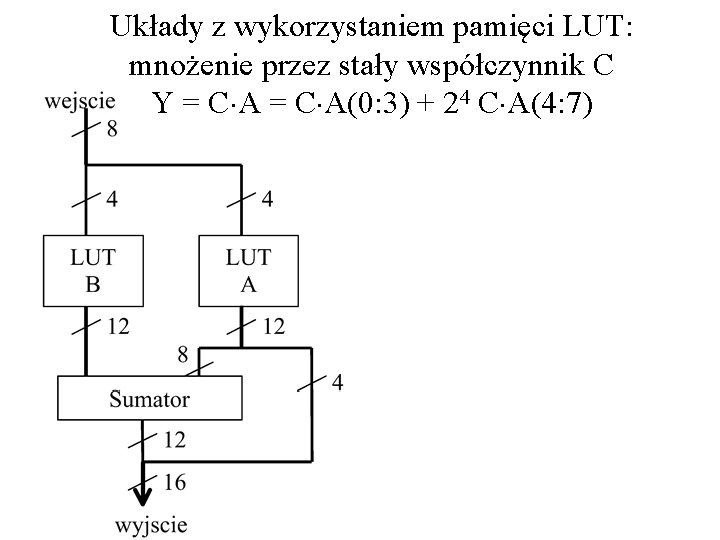

Układy z wykorzystaniem pamięci LUT: mnożenie przez stały współczynnik C Y = C A(0: 3) + 24 C A(4: 7)

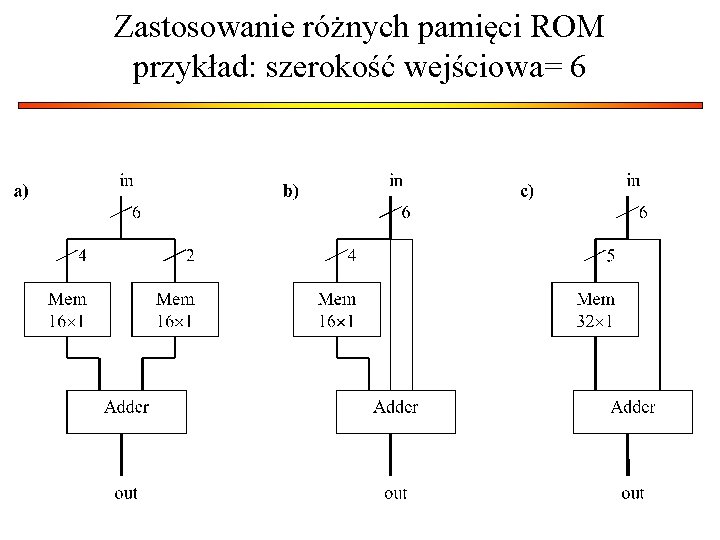

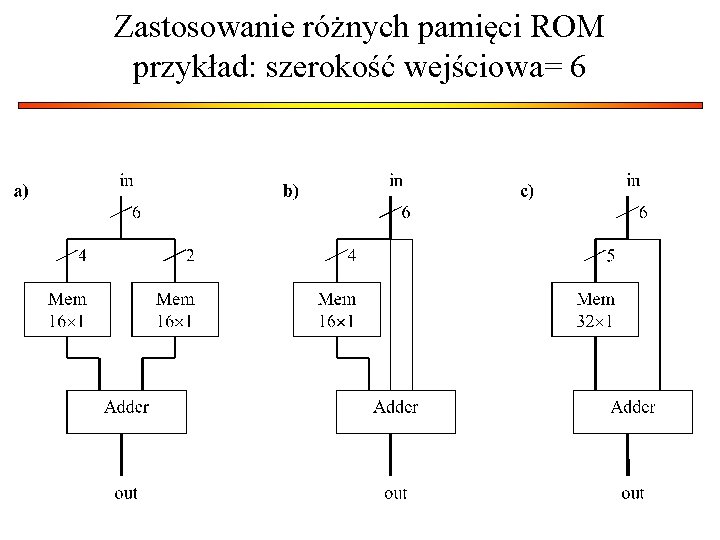

Zastosowanie różnych pamięci ROM przykład: szerokość wejściowa= 6

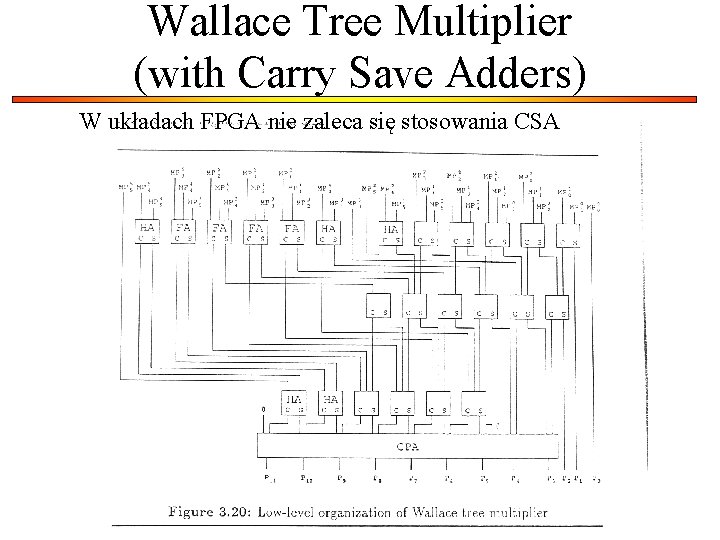

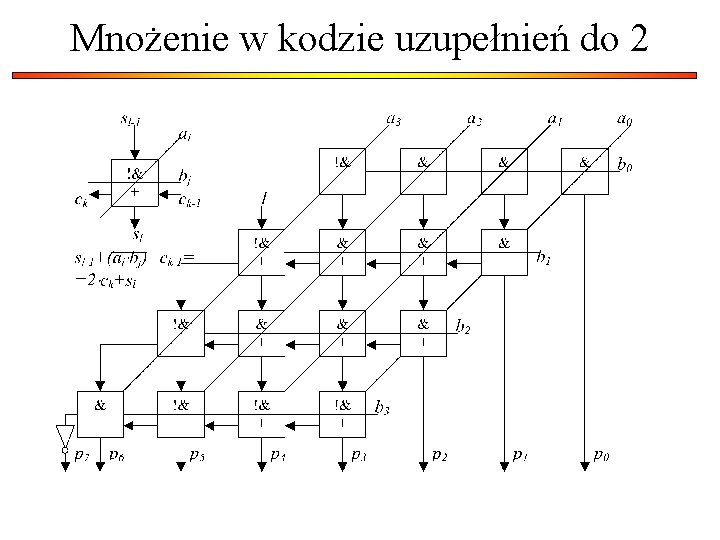

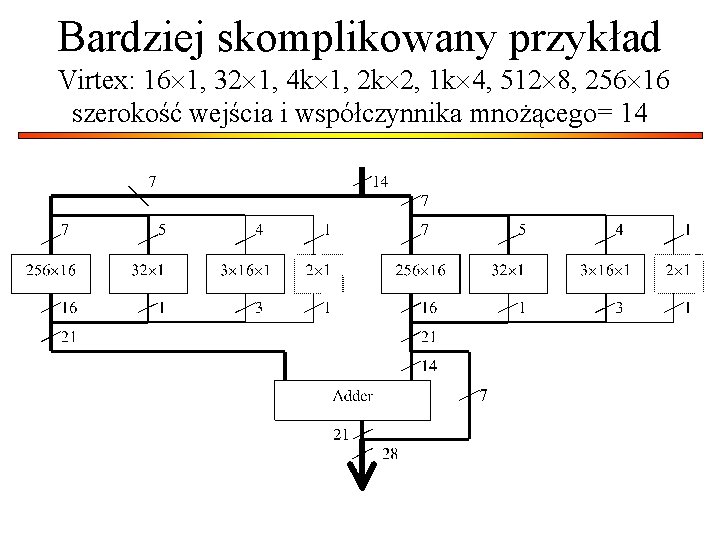

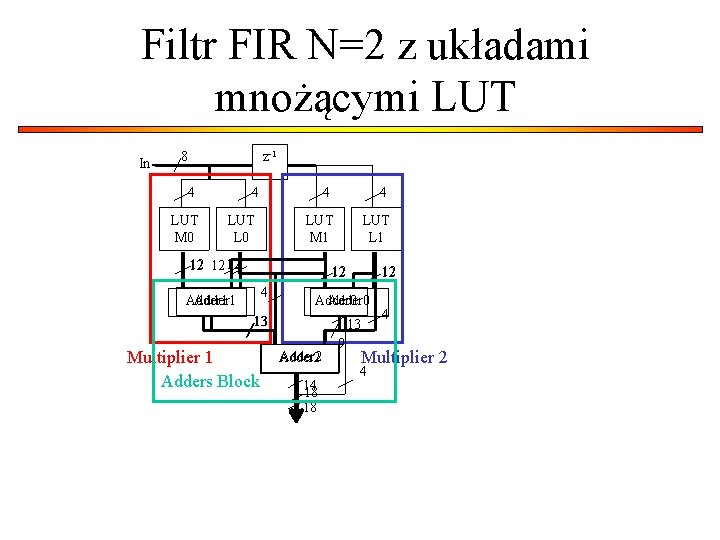

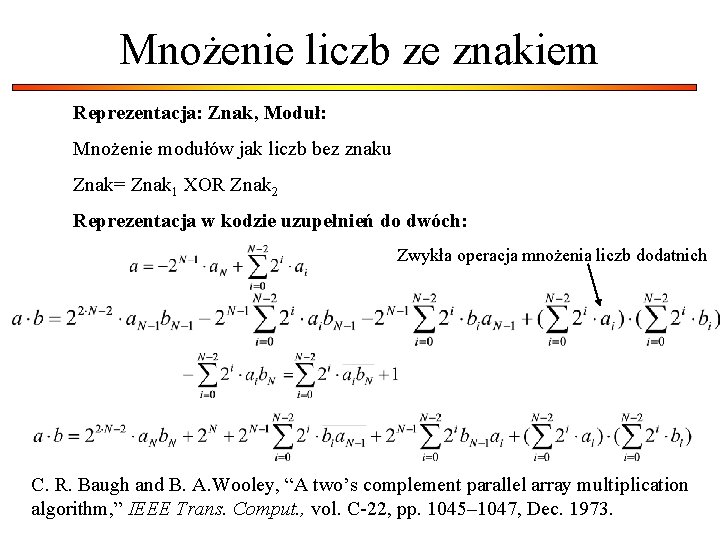

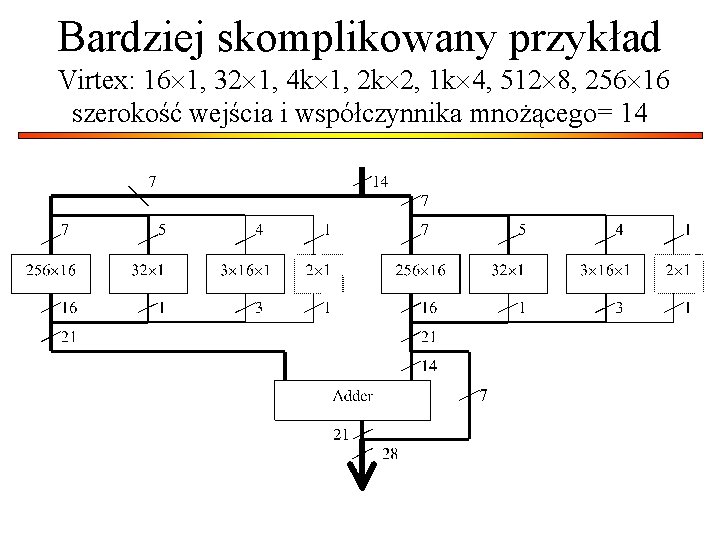

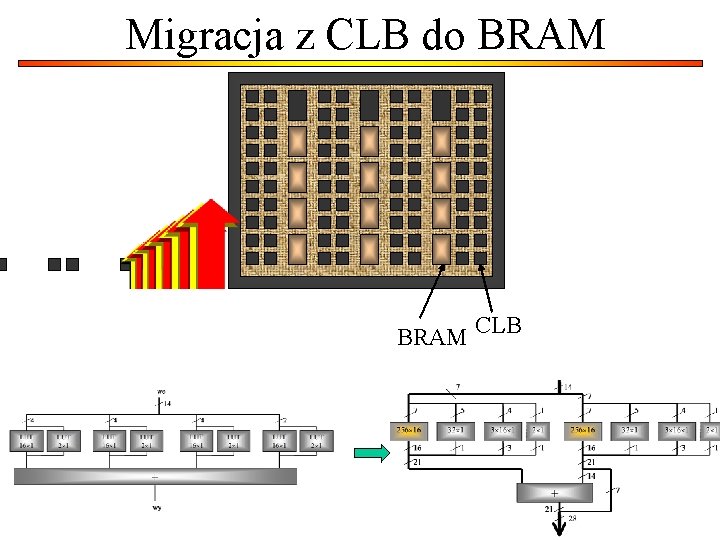

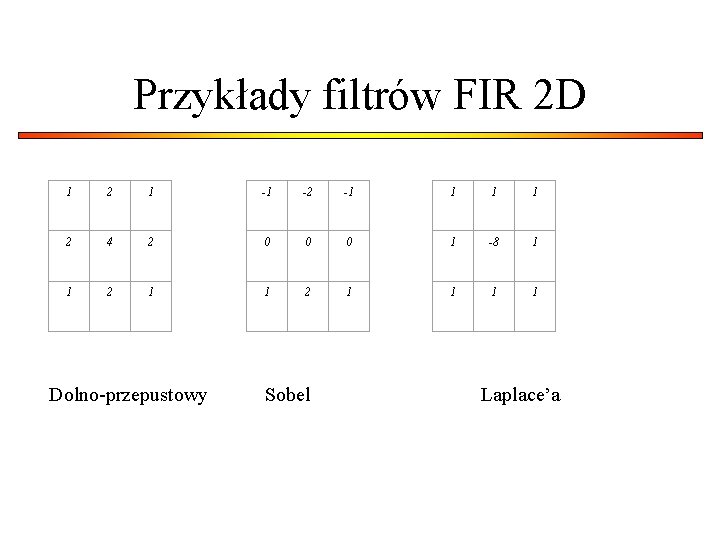

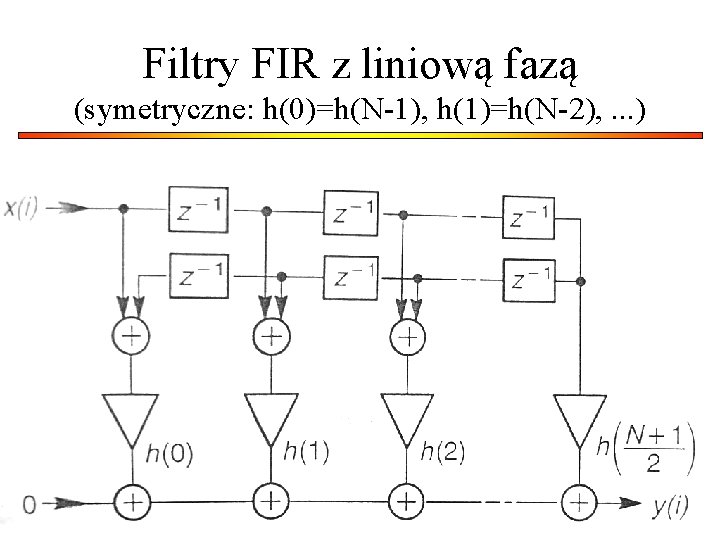

Bardziej skomplikowany przykład Virtex: 16 1, 32 1, 4 k 1, 2 k 2, 1 k 4, 512 8, 256 16 szerokość wejścia i współczynnika mnożącego= 14

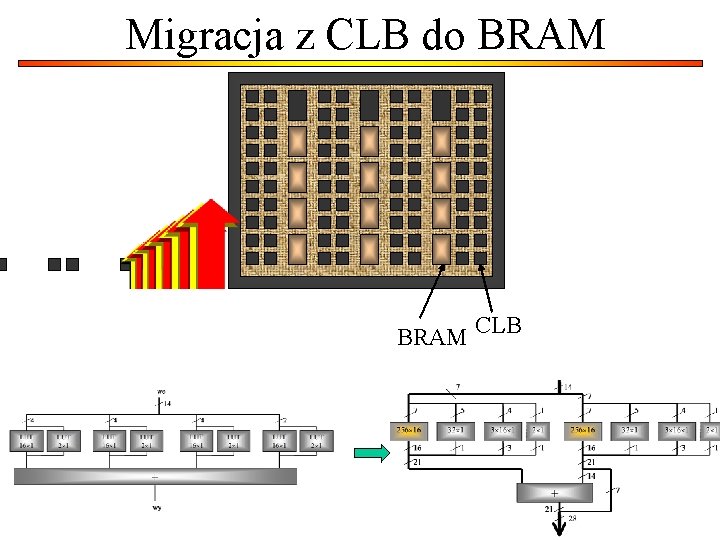

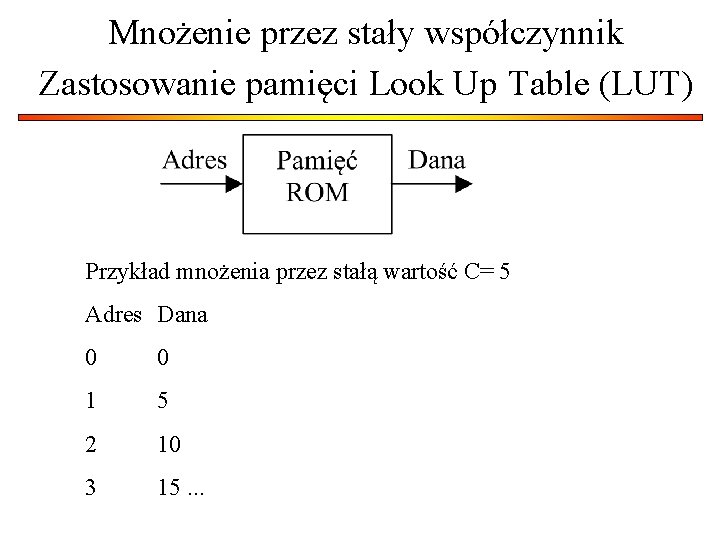

Migracja z CLB do BRAM CLB

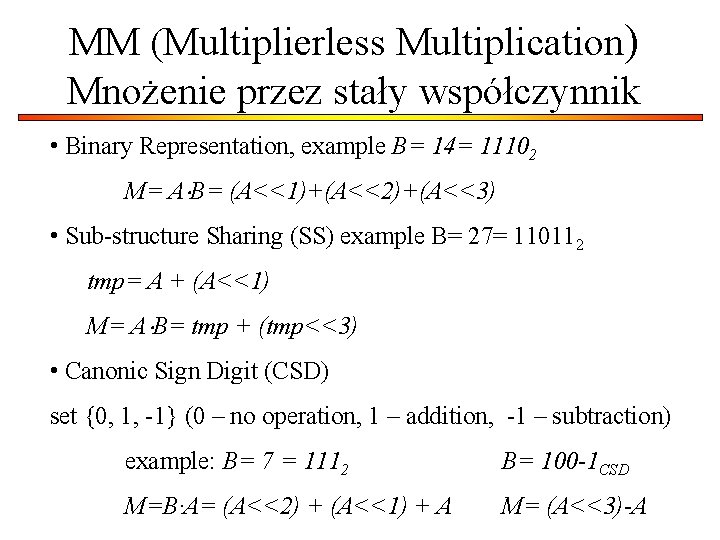

![Koszt CLB dla różnych szerokości K wejścia i współczynnika mnożenia ekwiwalentny koszt 1 BSR Koszt [CLB] dla różnych szerokości K wejścia i współczynnika mnożenia ekwiwalentny koszt 1 BSR](https://slidetodoc.com/presentation_image/5f1914ab703cae237da101a7683b46f8/image-17.jpg)

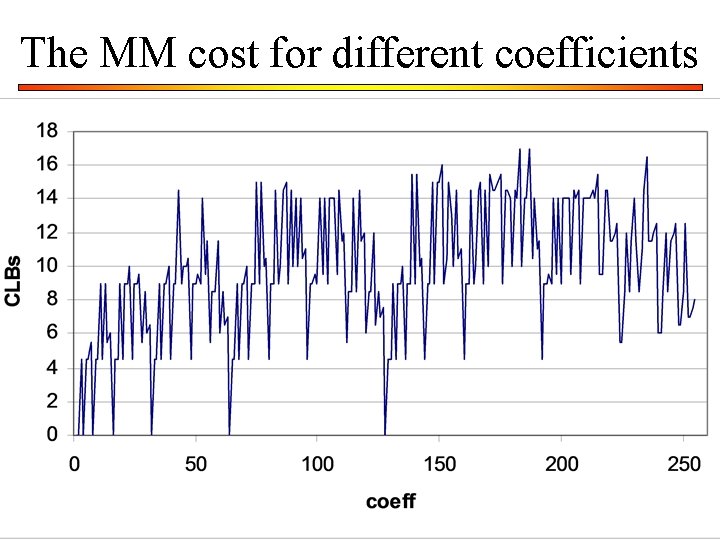

Koszt [CLB] dla różnych szerokości K wejścia i współczynnika mnożenia ekwiwalentny koszt 1 BSR tylko CLB, skala 1: 10 liczna użytych BSR

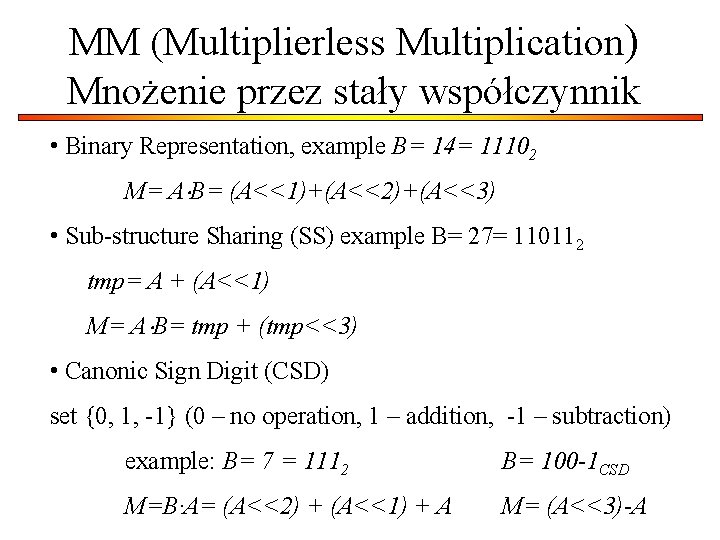

MM (Multiplierless Multiplication) Mnożenie przez stały współczynnik • Binary Representation, example B= 14= 11102 M= A B= (A<<1)+(A<<2)+(A<<3) • Sub-structure Sharing (SS) example B= 27= 110112 tmp= A + (A<<1) M= A B= tmp + (tmp<<3) • Canonic Sign Digit (CSD) set {0, 1, -1} (0 – no operation, 1 – addition, -1 – subtraction) example: B= 7 = 1112 B= 100 -1 CSD M=B·A= (A<<2) + (A<<1) + A M= (A<<3)-A

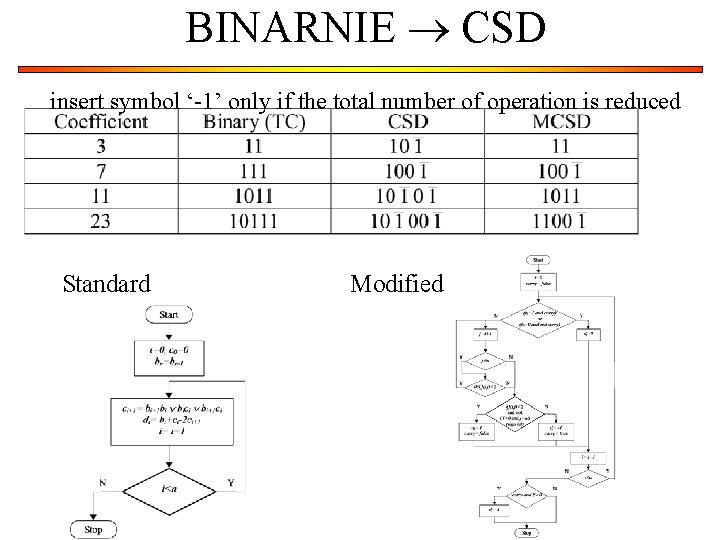

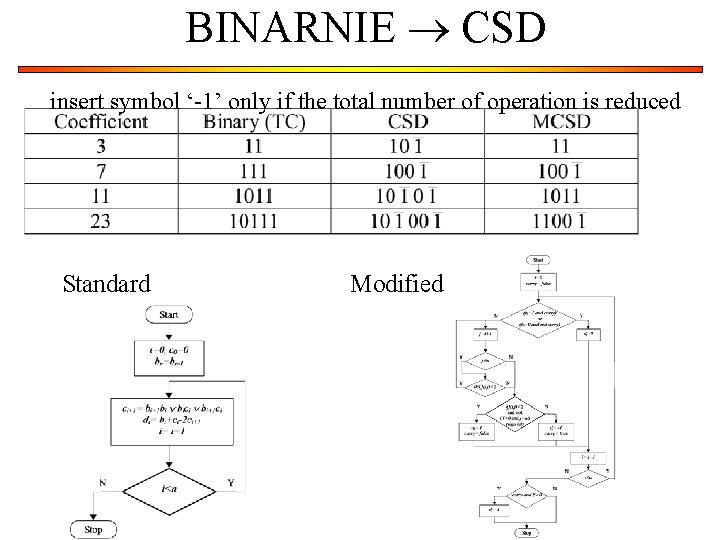

BINARNIE CSD insert symbol ‘-1’ only if the total number of operation is reduced Standard Modified

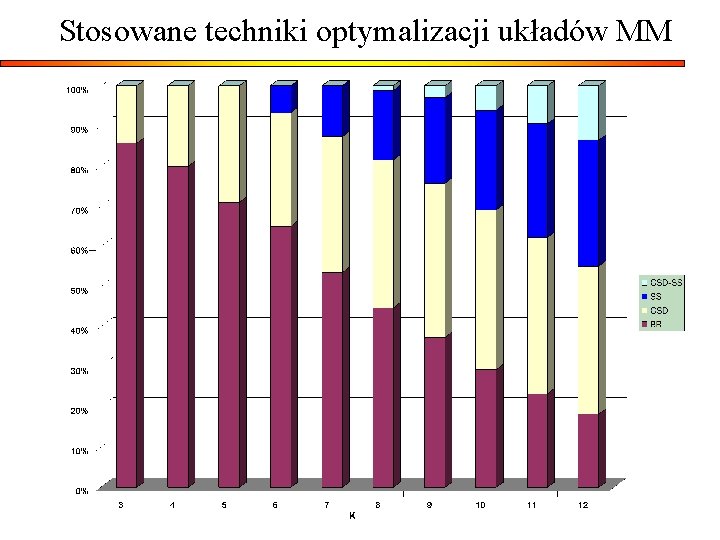

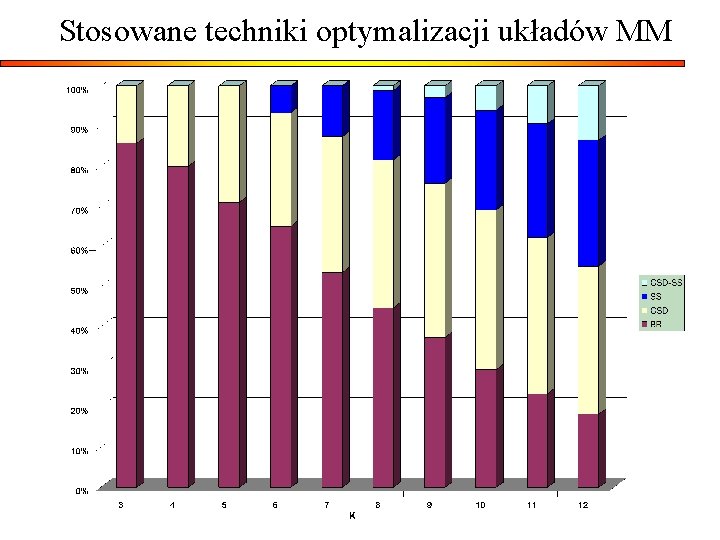

Stosowane techniki optymalizacji układów MM

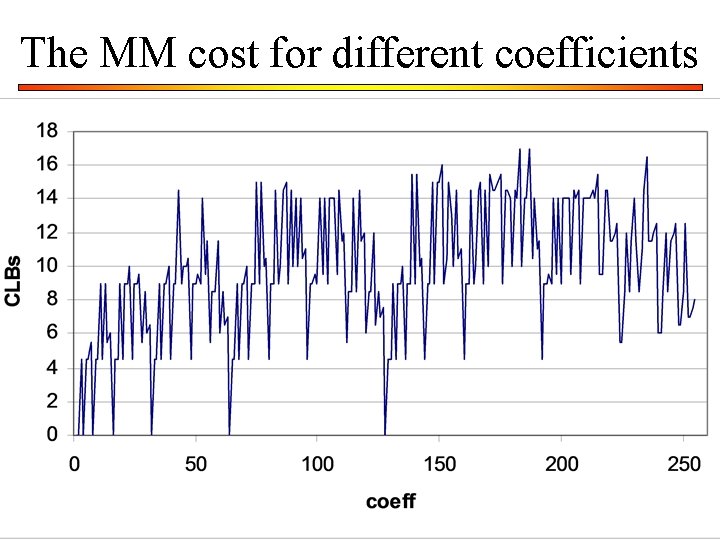

The MM cost for different coefficients

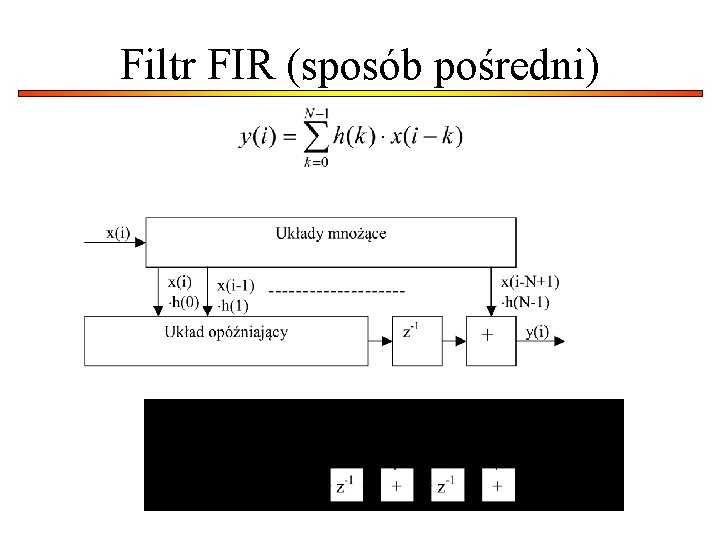

Filtr FIR

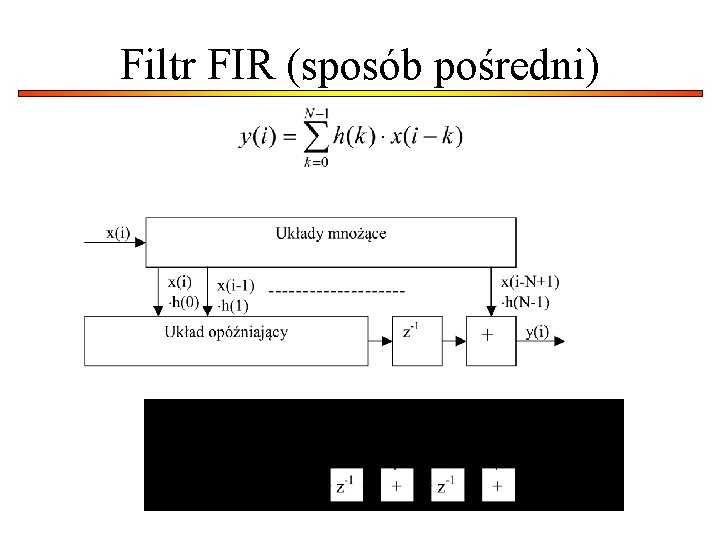

Filtr FIR (sposób pośredni)

FIR 2 D

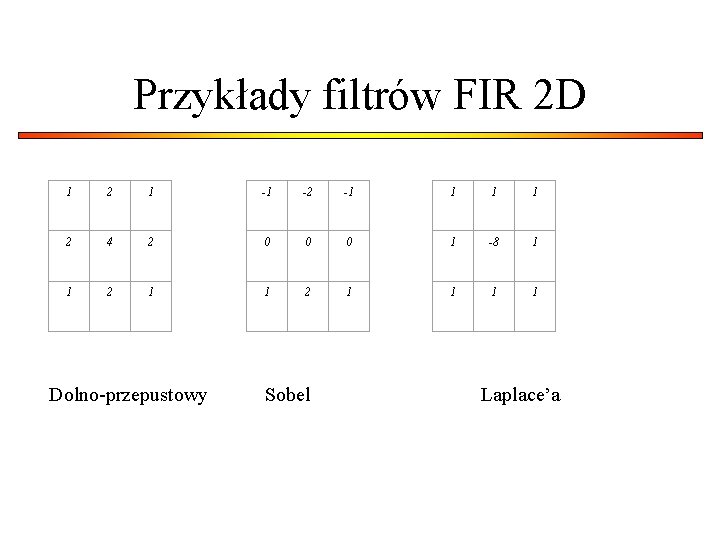

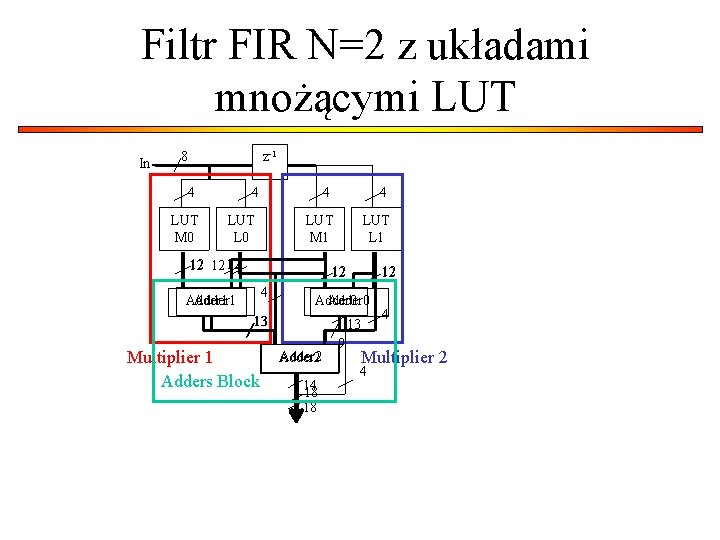

Przykłady filtrów FIR 2 D 1 2 1 -1 -2 -1 1 2 4 2 0 0 0 1 -8 1 1 2 1 1 Dolno-przepustowy Sobel Laplace’a

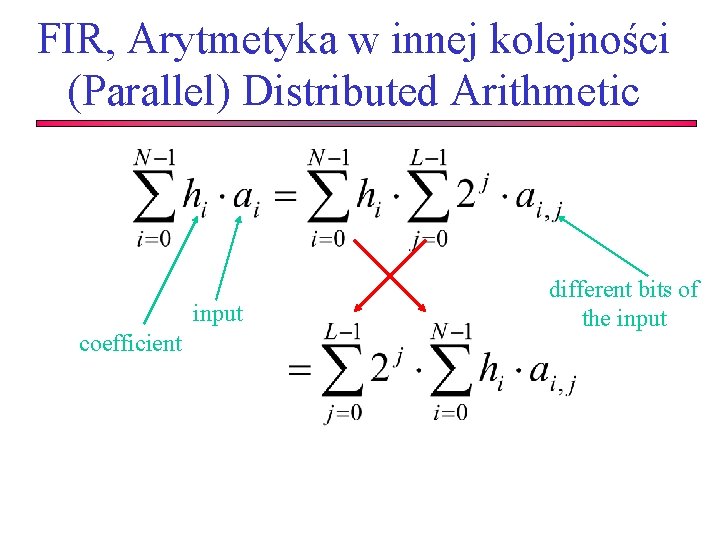

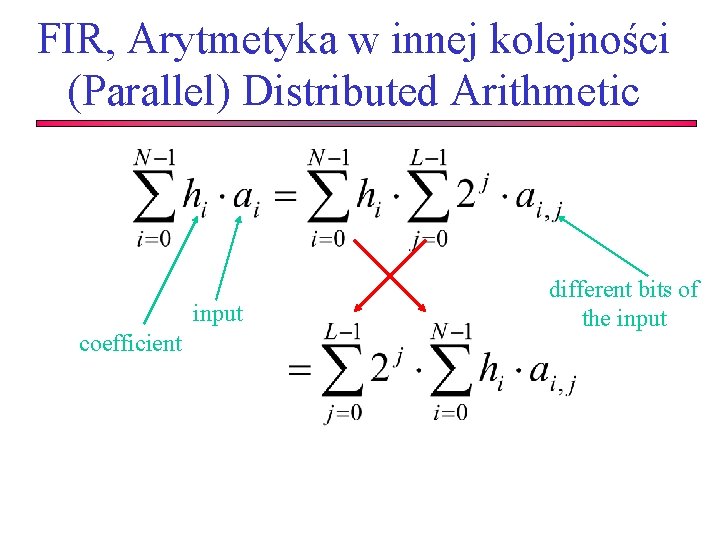

Filtr FIR N=2 z układami mnożącymi LUT In 8 z-1 4 4 LUT M 0 LUT L 0 LUT M 1 LUT L 1 12 12 4 Adder 1 Adder 0 13 Multiplier 1 Adders Block 12 13 Adder 2 14 18 18 9 4 Multiplier 2 4

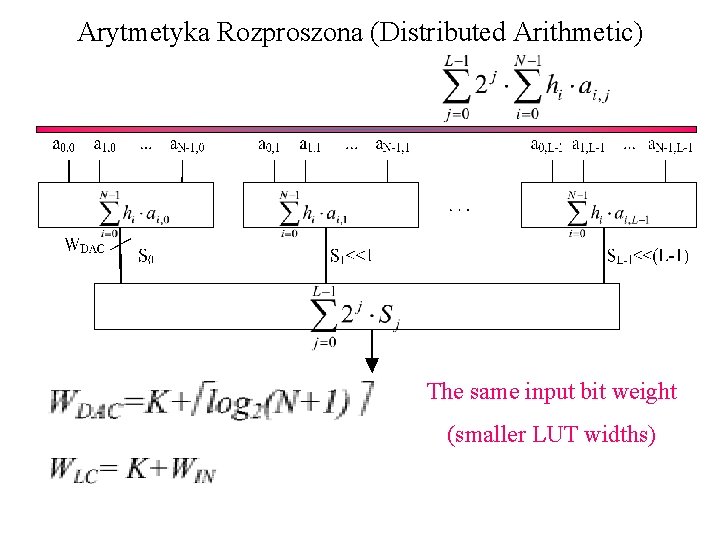

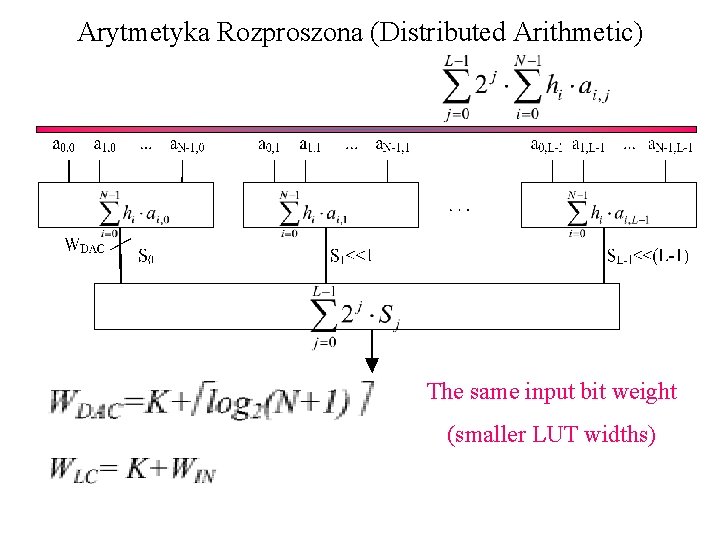

FIR, Arytmetyka w innej kolejności (Parallel) Distributed Arithmetic input coefficient different bits of the input

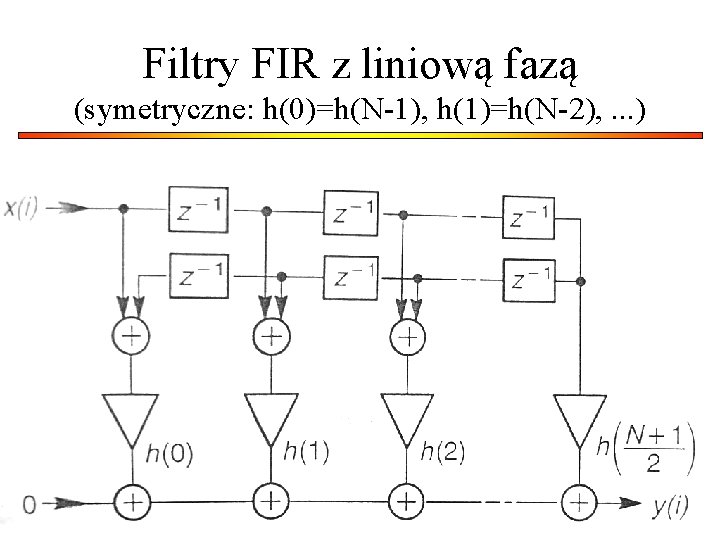

Arytmetyka Rozproszona (Distributed Arithmetic) The same input bit weight (smaller LUT widths)

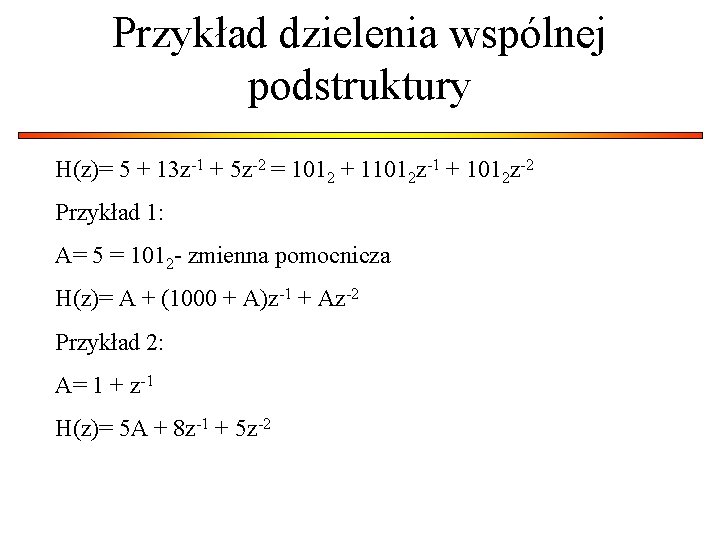

Filtry FIR z liniową fazą (symetryczne: h(0)=h(N-1), h(1)=h(N-2), . . . )

Przykład dzielenia wspólnej podstruktury H(z)= 5 + 13 z-1 + 5 z-2 = 1012 + 11012 z-1 + 1012 z-2 Przykład 1: A= 5 = 1012 - zmienna pomocnicza H(z)= A + (1000 + A)z-1 + Az-2 Przykład 2: A= 1 + z-1 H(z)= 5 A + 8 z-1 + 5 z-2