Design and Implementation of VLSI Systems EN 1600

- Slides: 12

Design and Implementation of VLSI Systems (EN 1600) Lecture 27: Datapath Subsystems 3/4 Prof. Sherief Reda Division of Engineering, Brown University Spring 2008 [sources: Weste/Addison Wesley – Rabaey/Pearson]

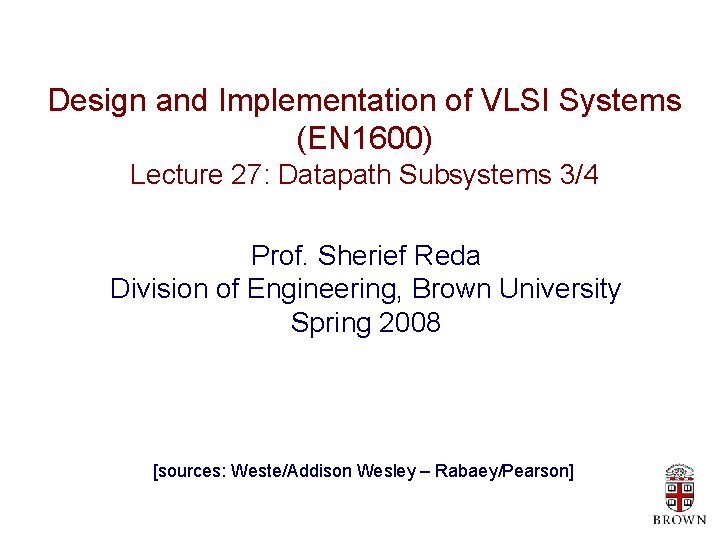

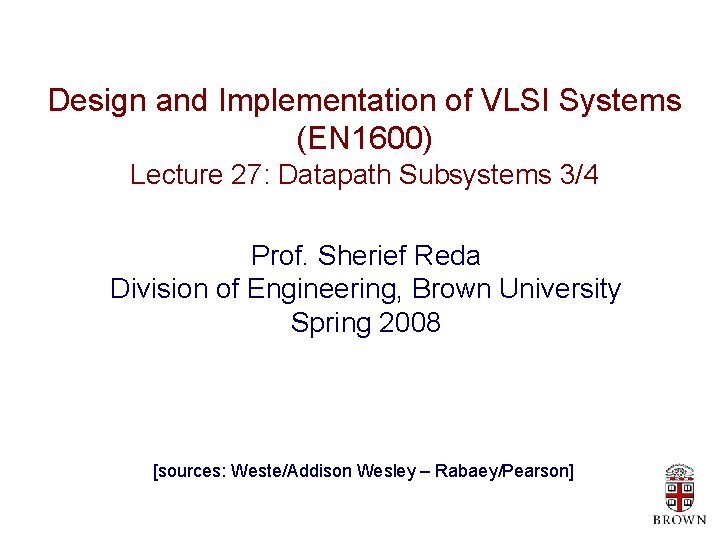

Manchester carry adder • Using transmission gates • Using dynamic gates

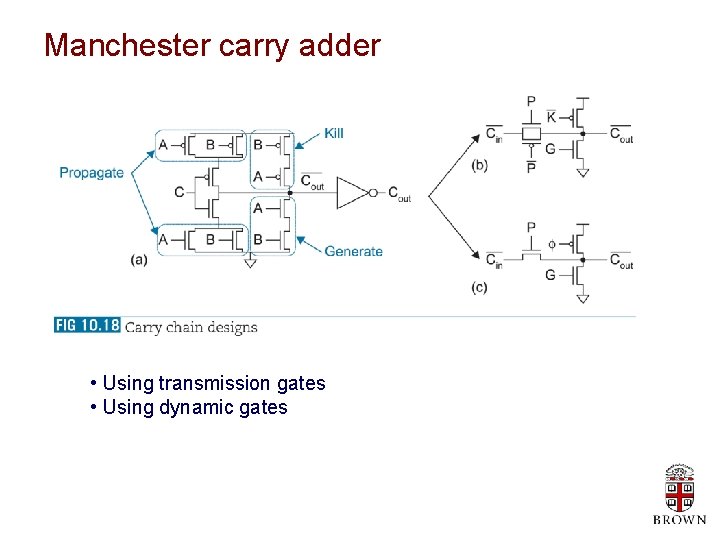

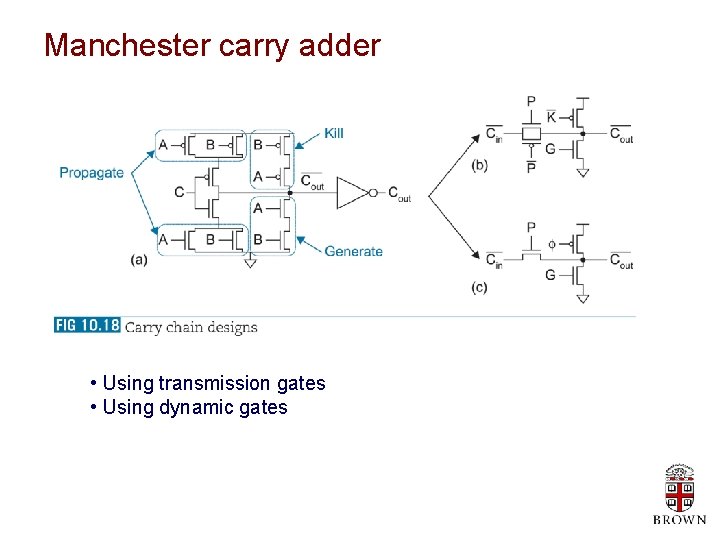

Manchester carry chains Critical path involves a series propagate transistor for each bit a significant over carry-ripple (which used majority or AND-OR gate)

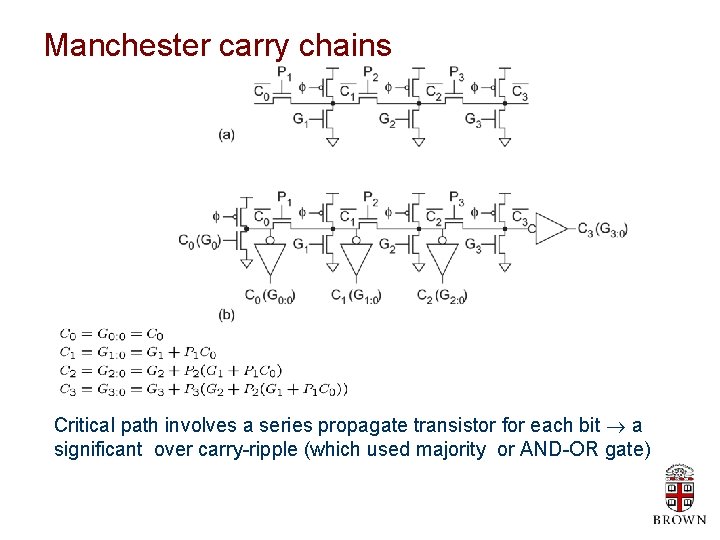

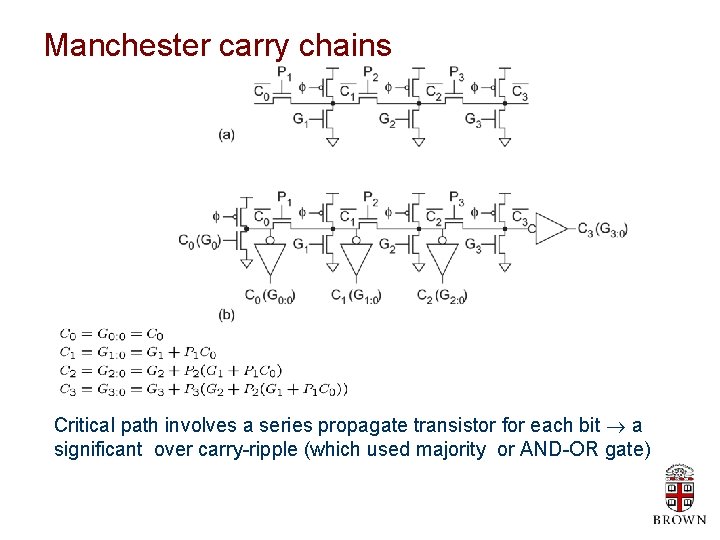

Equivalence circuits for Manchester carry chain

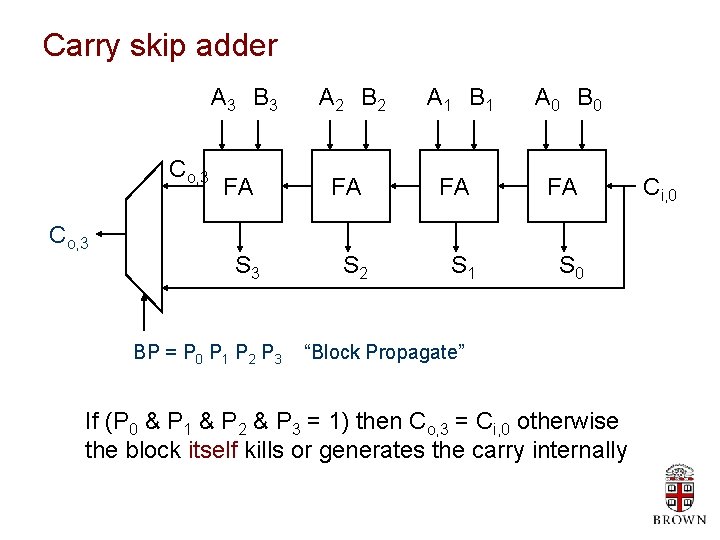

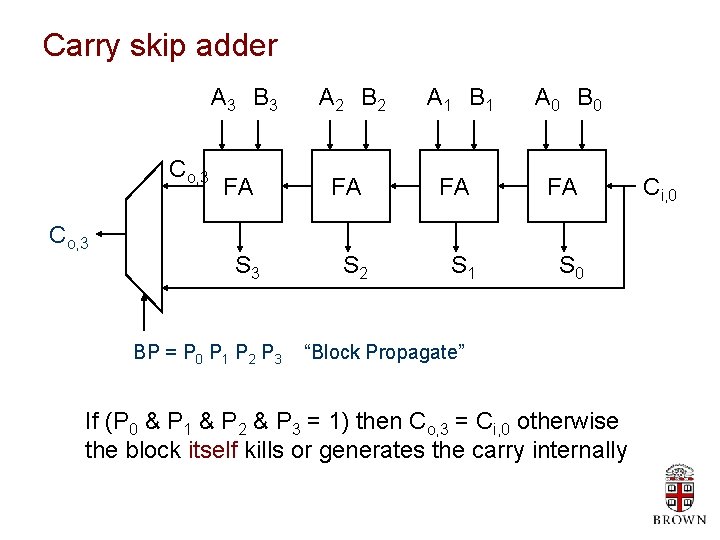

Carry skip adder Co, 3 A 3 B 3 A 2 B 2 A 1 B 1 A 0 B 0 FA FA S 3 S 2 S 1 S 0 BP = P 0 P 1 P 2 P 3 “Block Propagate” If (P 0 & P 1 & P 2 & P 3 = 1) then Co, 3 = Ci, 0 otherwise the block itself kills or generates the carry internally Ci, 0

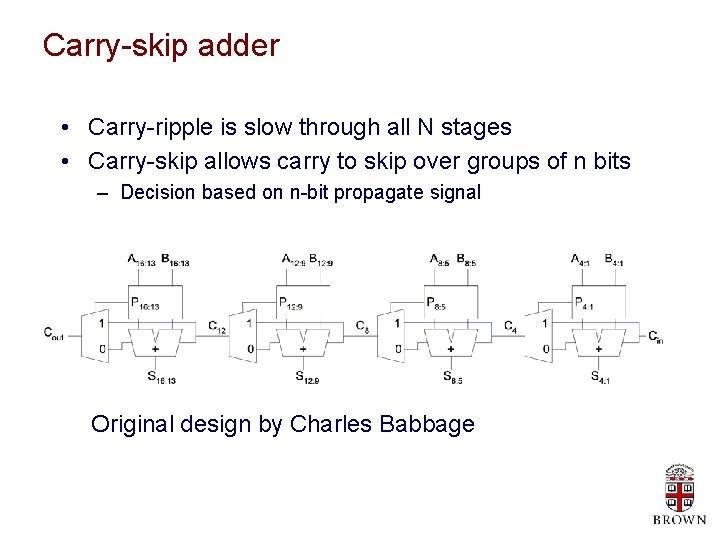

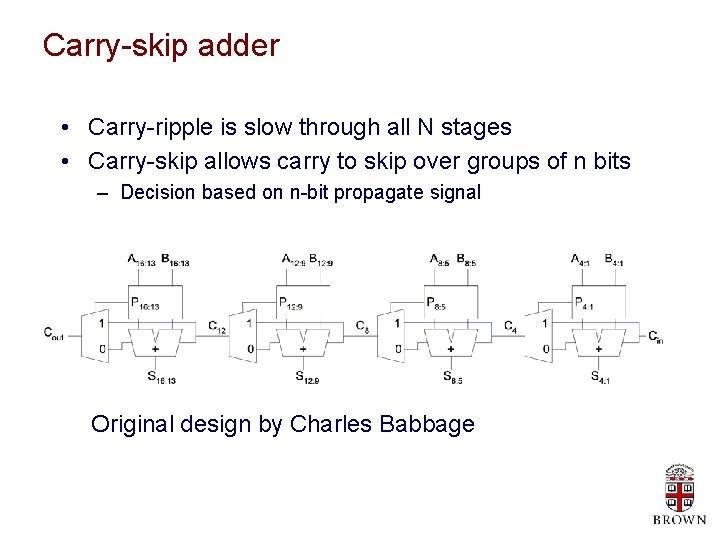

Carry-skip adder • Carry-ripple is slow through all N stages • Carry-skip allows carry to skip over groups of n bits – Decision based on n-bit propagate signal Original design by Charles Babbage

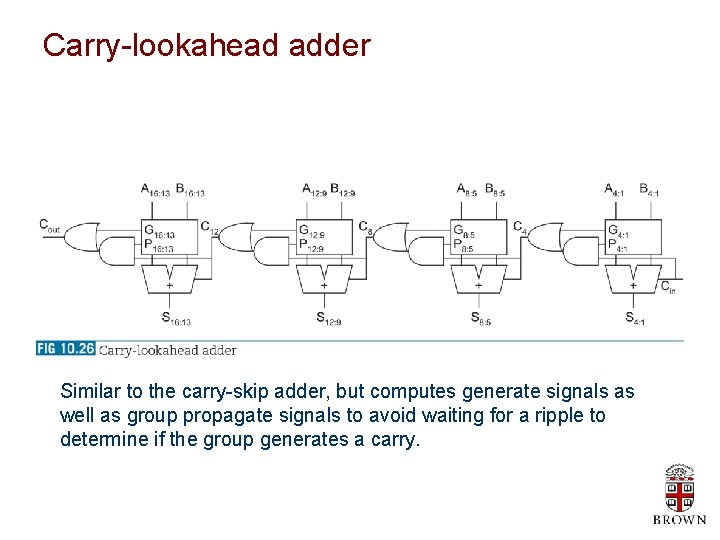

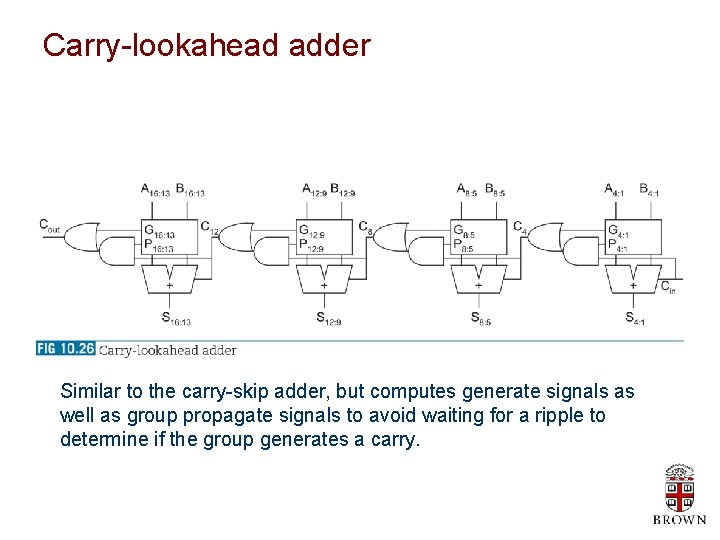

Carry-lookahead adder Similar to the carry-skip adder, but computes generate signals as well as group propagate signals to avoid waiting for a ripple to determine if the group generates a carry.

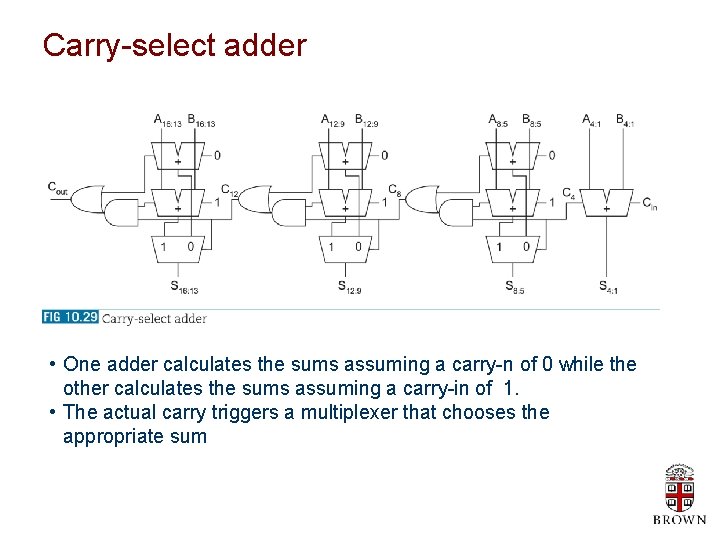

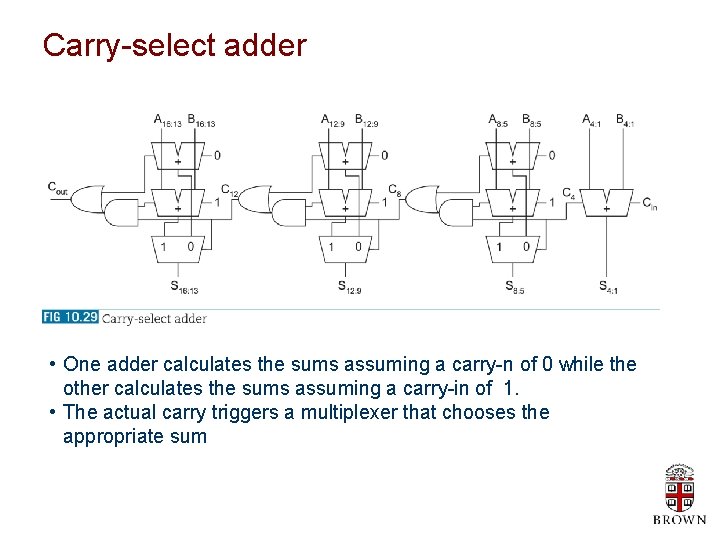

Carry-select adder • One adder calculates the sums assuming a carry-n of 0 while the other calculates the sums assuming a carry-in of 1. • The actual carry triggers a multiplexer that chooses the appropriate sum

II. Comparators A. 0’s detector and 1’s detectors B. Equality comparator: A = B C. Magnitude comparator: A < B

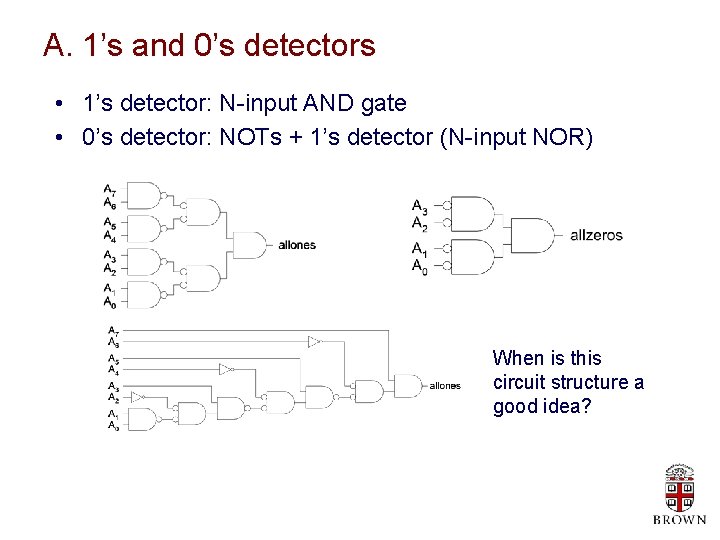

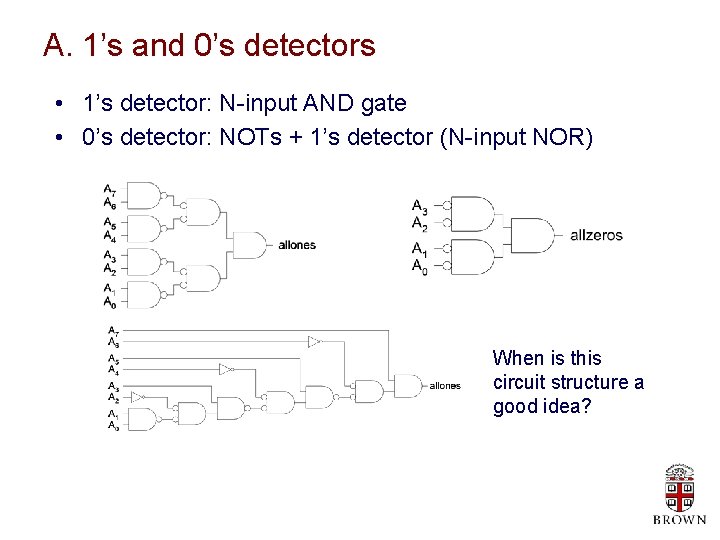

A. 1’s and 0’s detectors • 1’s detector: N-input AND gate • 0’s detector: NOTs + 1’s detector (N-input NOR) When is this circuit structure a good idea?

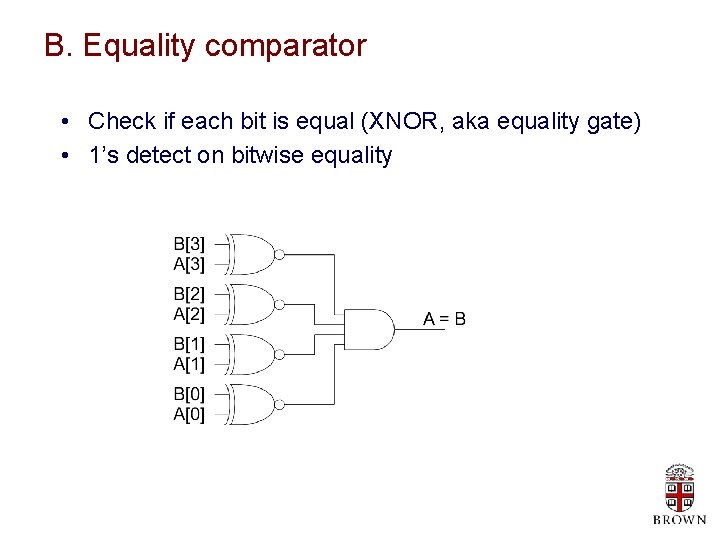

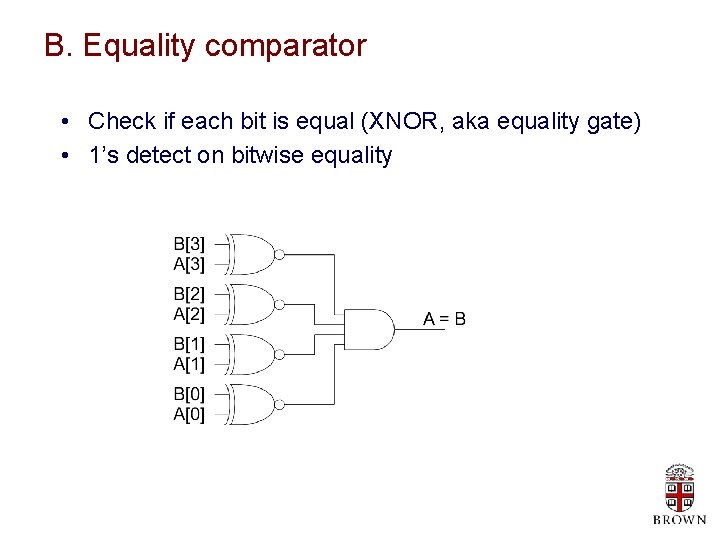

B. Equality comparator • Check if each bit is equal (XNOR, aka equality gate) • 1’s detect on bitwise equality

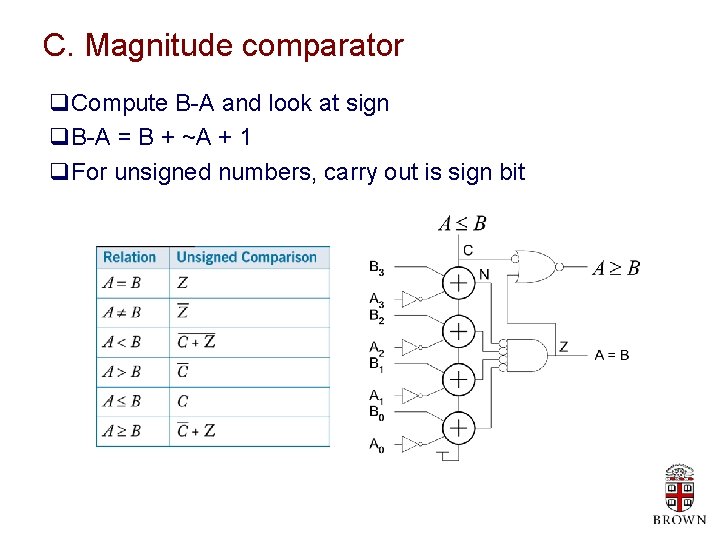

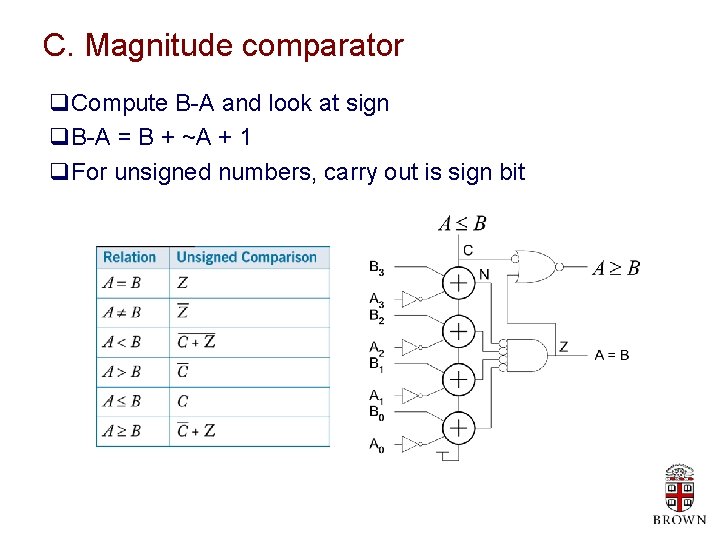

C. Magnitude comparator q. Compute B-A and look at sign q. B-A = B + ~A + 1 q. For unsigned numbers, carry out is sign bit