Design and Implementation of VLSI Systems EN 1600

- Slides: 16

Design and Implementation of VLSI Systems (EN 1600) lecture 02 Sherief Reda Division of Engineering, Brown University Spring 2008 [sources: Weste/Addison Wesley – Rabaey Pearson]

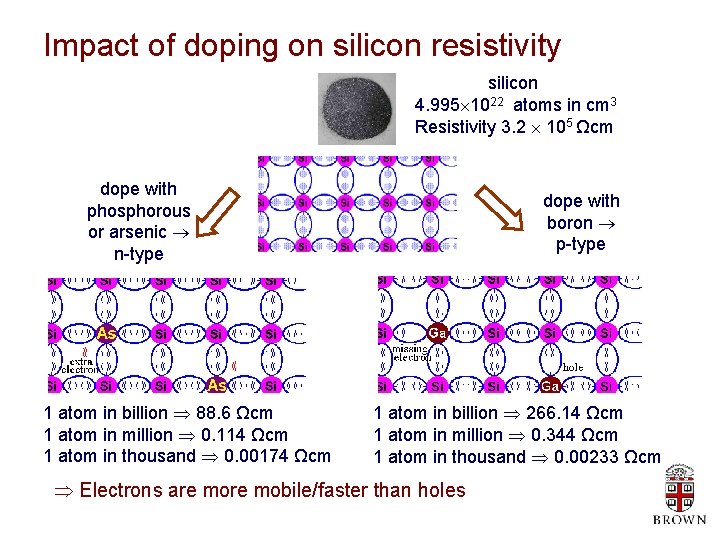

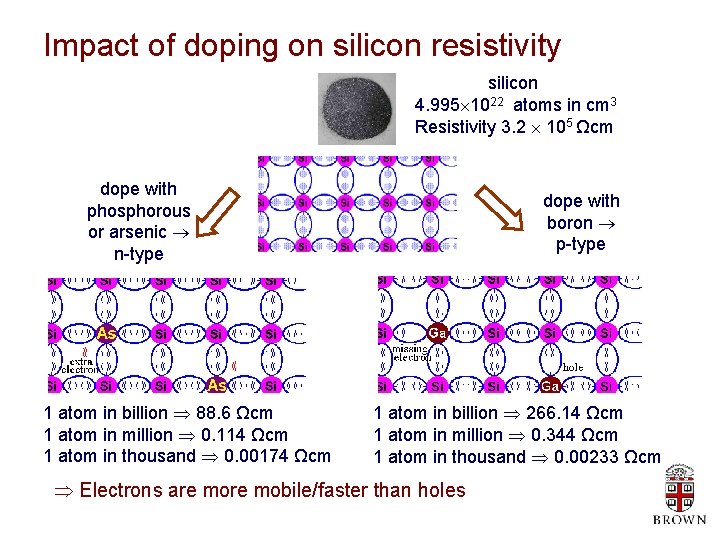

Impact of doping on silicon resistivity silicon 4. 995 1022 atoms in cm 3 Resistivity 3. 2 105 Ωcm dope with phosphorous or arsenic n-type 1 atom in billion 88. 6 Ωcm 1 atom in million 0. 114 Ωcm 1 atom in thousand 0. 00174 Ωcm dope with boron p-type 1 atom in billion 266. 14 Ωcm 1 atom in million 0. 344 Ωcm 1 atom in thousand 0. 00233 Ωcm Electrons are mobile/faster than holes

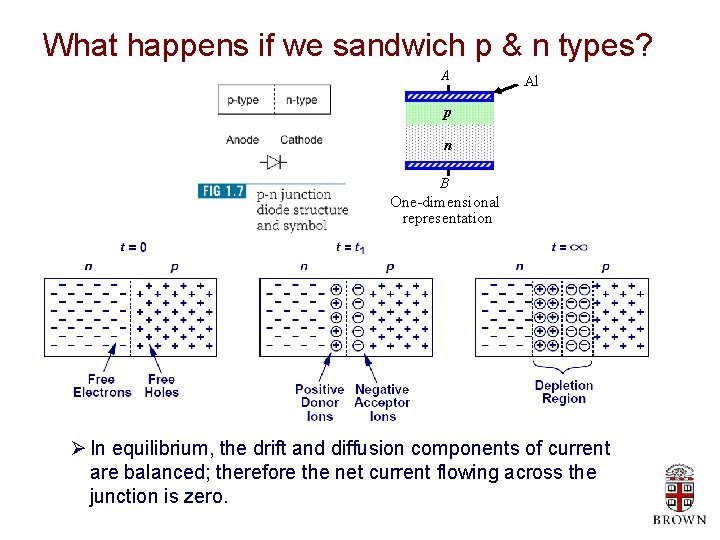

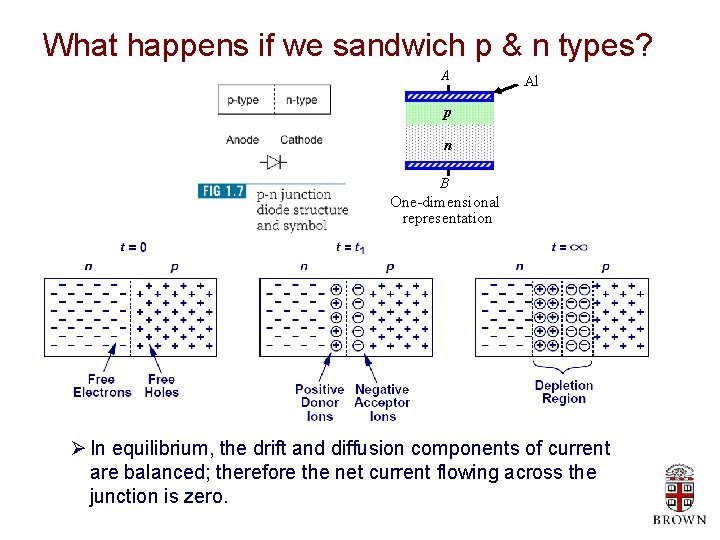

What happens if we sandwich p & n types? A Al p n B One-dimensional representation Ø In equilibrium, the drift and diffusion components of current are balanced; therefore the net current flowing across the junction is zero.

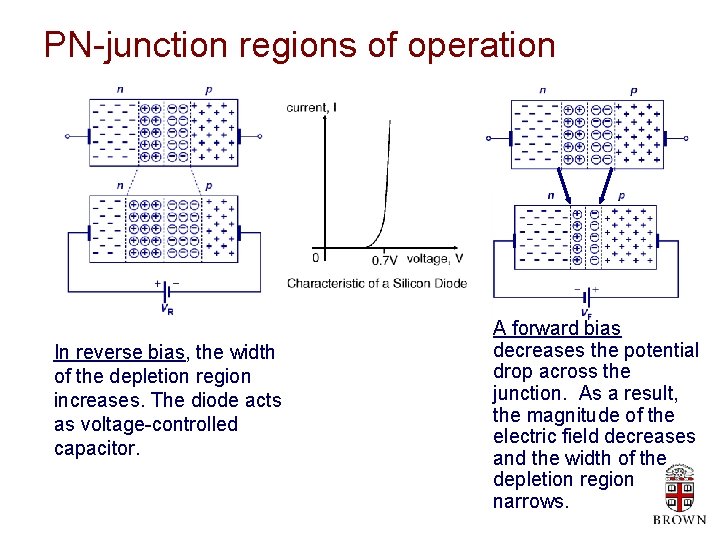

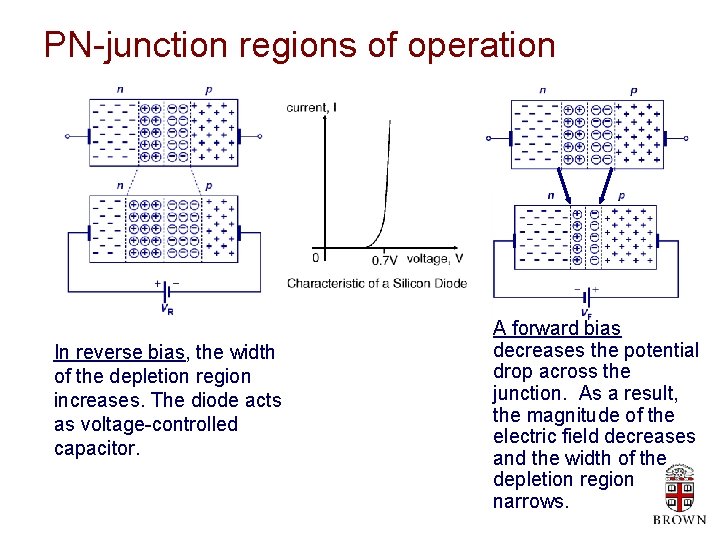

PN-junction regions of operation In reverse bias, the width of the depletion region increases. The diode acts as voltage-controlled capacitor. A forward bias decreases the potential drop across the junction. As a result, the magnitude of the electric field decreases and the width of the depletion region narrows.

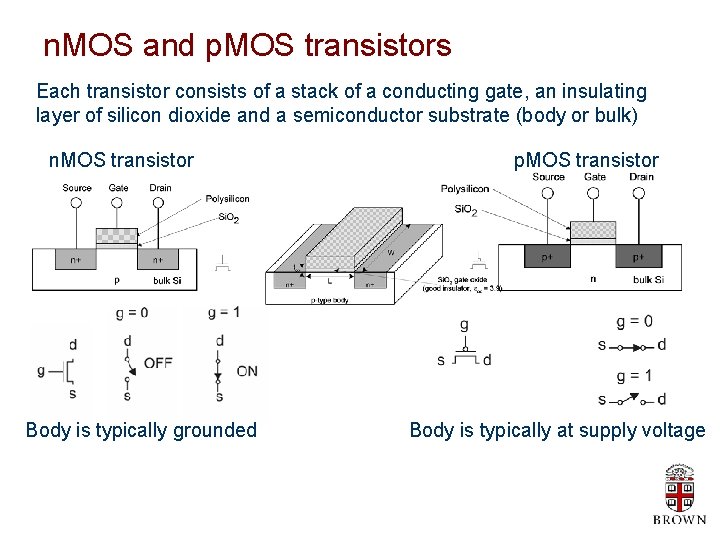

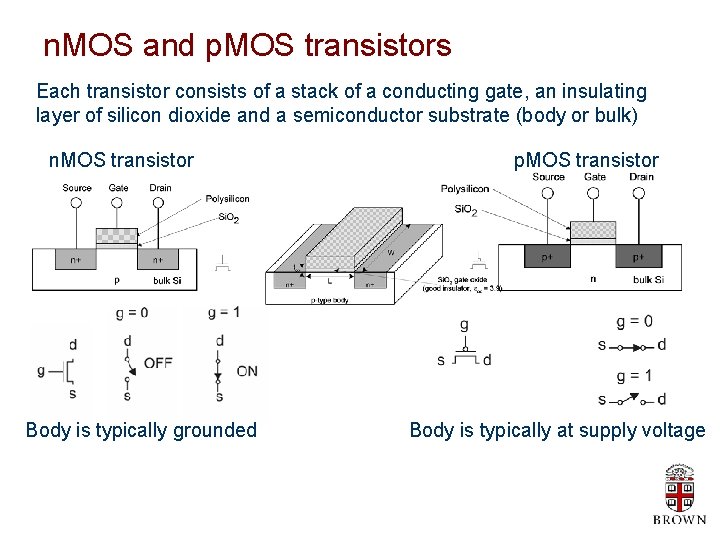

n. MOS and p. MOS transistors Each transistor consists of a stack of a conducting gate, an insulating layer of silicon dioxide and a semiconductor substrate (body or bulk) n. MOS transistor Body is typically grounded p. MOS transistor Body is typically at supply voltage

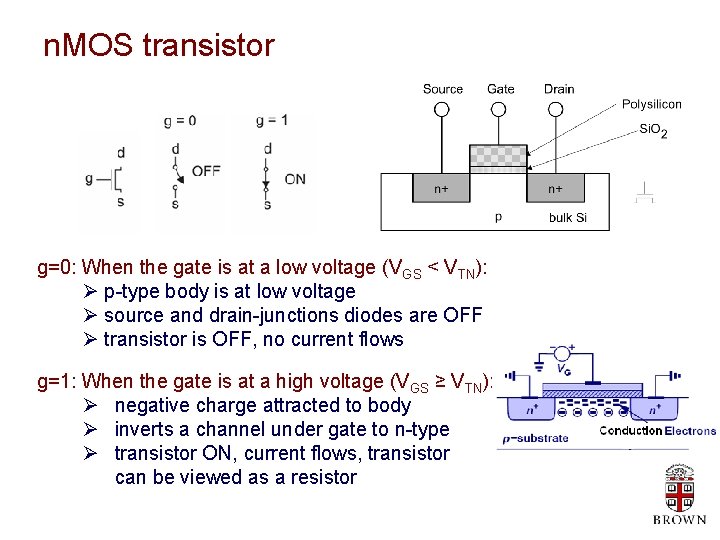

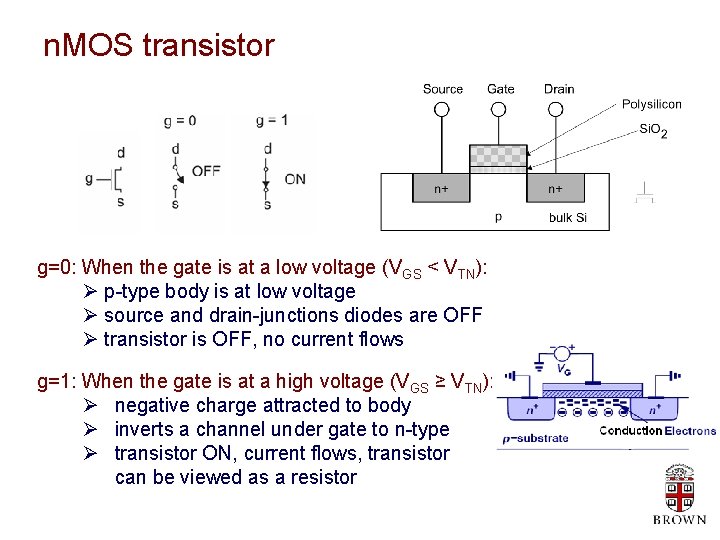

n. MOS transistor g=0: When the gate is at a low voltage (VGS < VTN): Ø p-type body is at low voltage Ø source and drain-junctions diodes are OFF Ø transistor is OFF, no current flows g=1: When the gate is at a high voltage (VGS ≥ VTN): Ø negative charge attracted to body Ø inverts a channel under gate to n-type Ø transistor ON, current flows, transistor can be viewed as a resistor

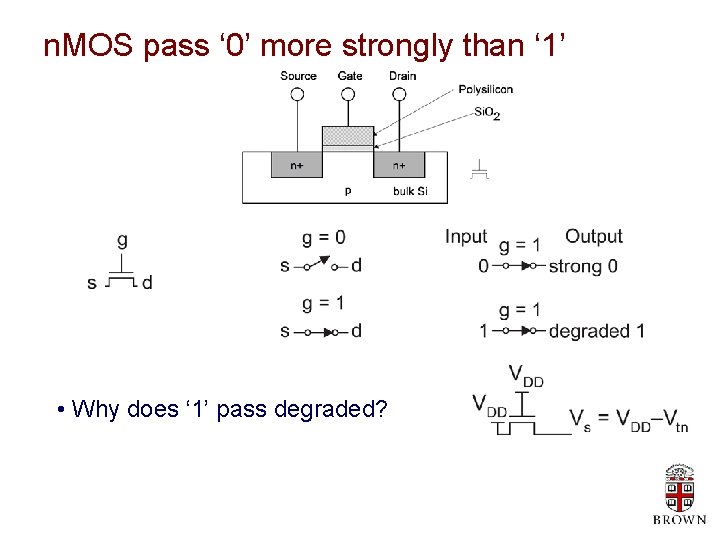

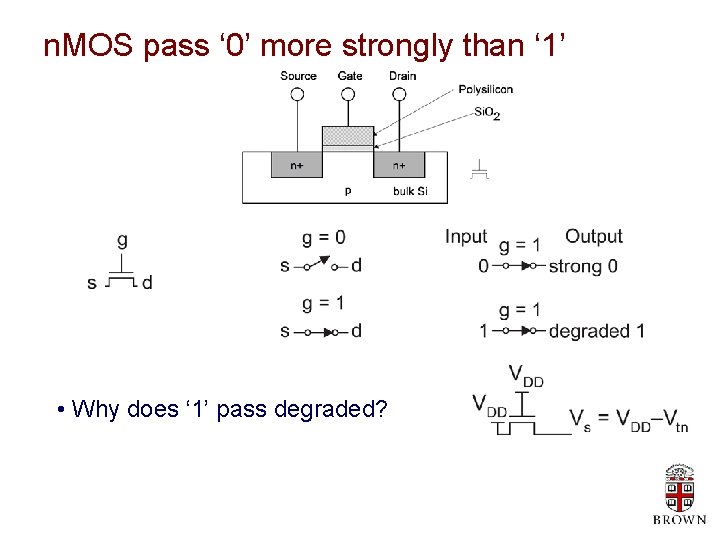

n. MOS pass ‘ 0’ more strongly than ‘ 1’ • Why does ‘ 1’ pass degraded?

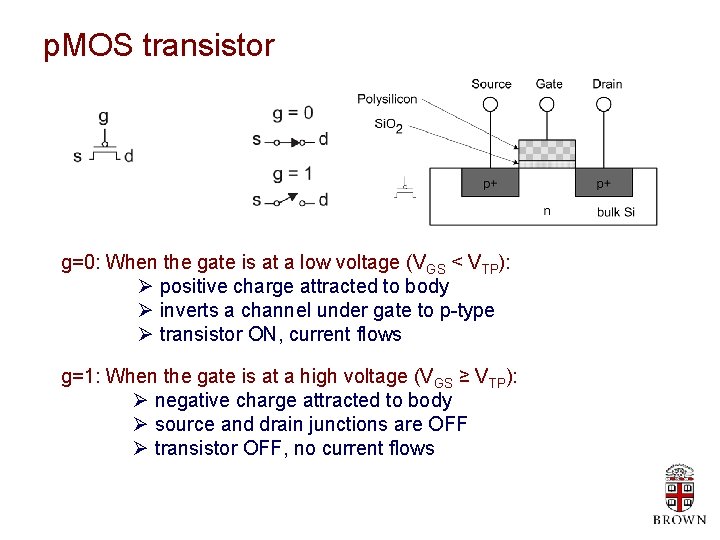

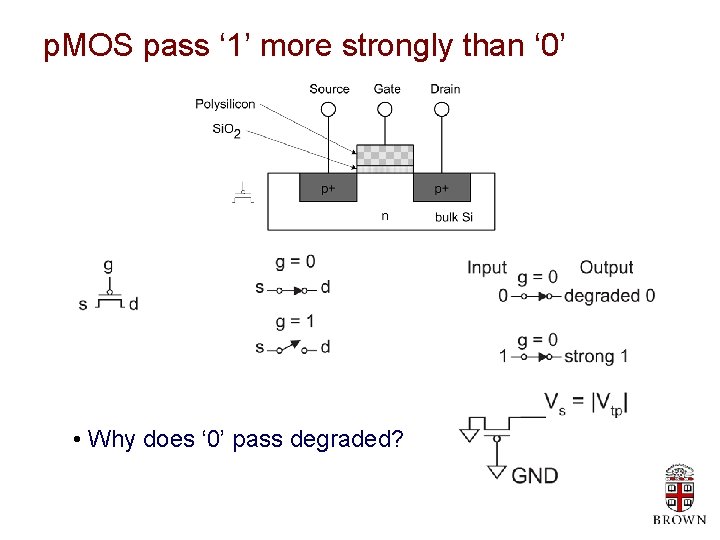

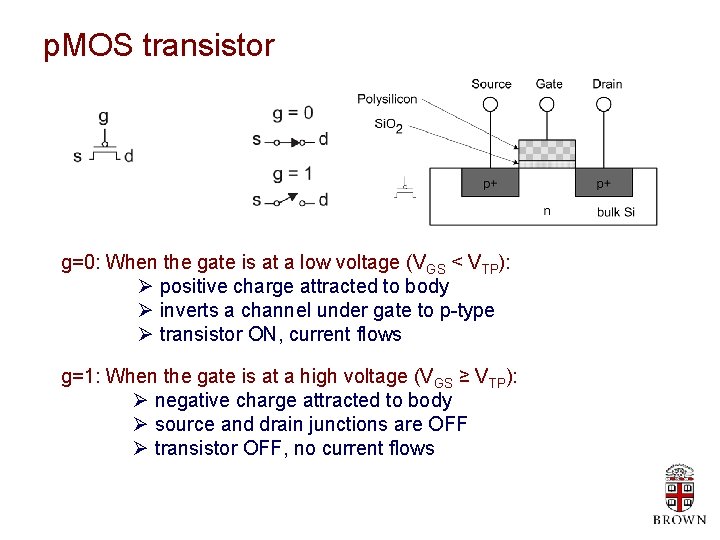

p. MOS transistor g=0: When the gate is at a low voltage (VGS < VTP): Ø positive charge attracted to body Ø inverts a channel under gate to p-type Ø transistor ON, current flows g=1: When the gate is at a high voltage (VGS ≥ VTP): Ø negative charge attracted to body Ø source and drain junctions are OFF Ø transistor OFF, no current flows

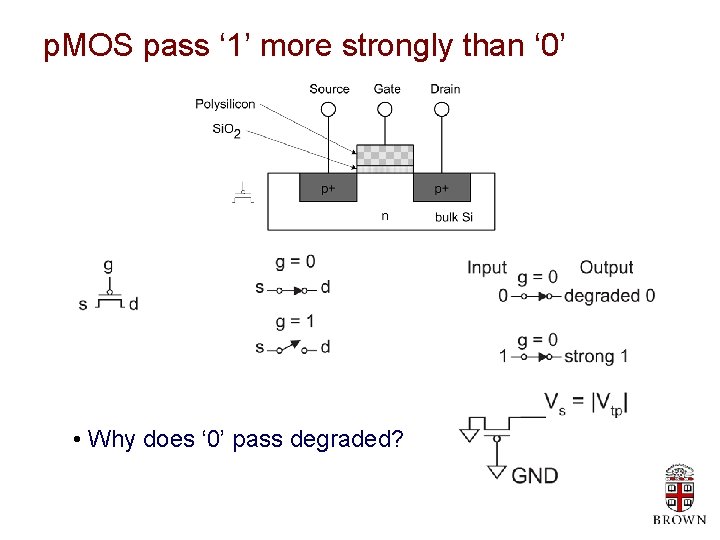

p. MOS pass ‘ 1’ more strongly than ‘ 0’ • Why does ‘ 0’ pass degraded?

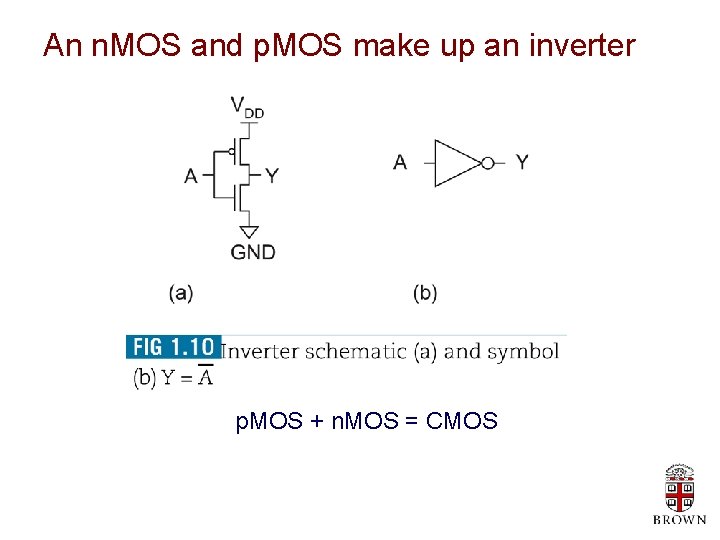

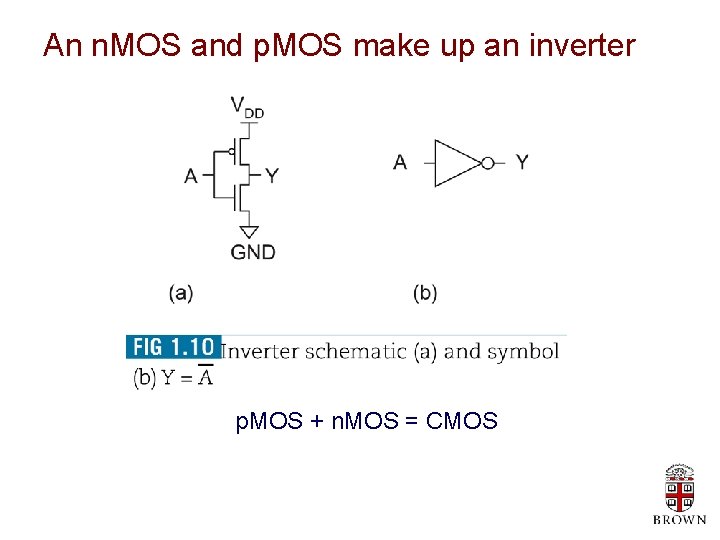

An n. MOS and p. MOS make up an inverter p. MOS + n. MOS = CMOS

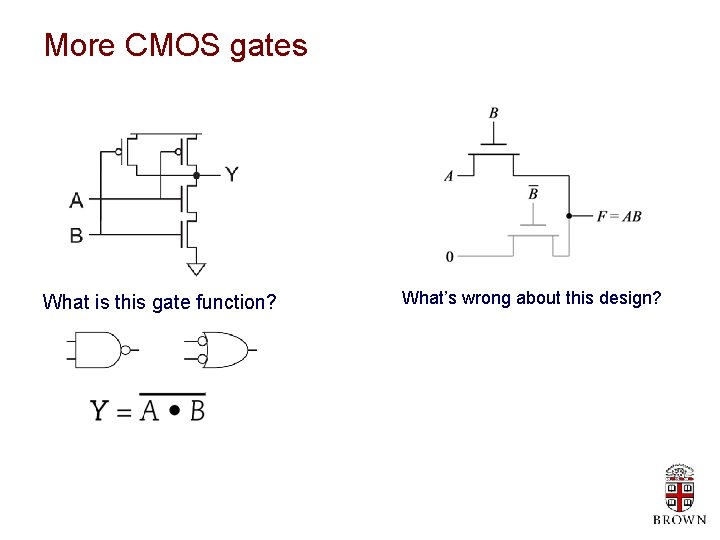

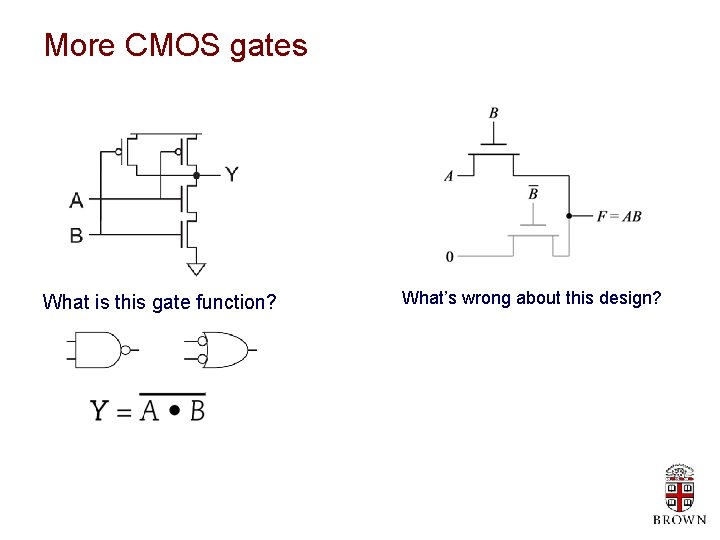

More CMOS gates What is this gate function? What’s wrong about this design?

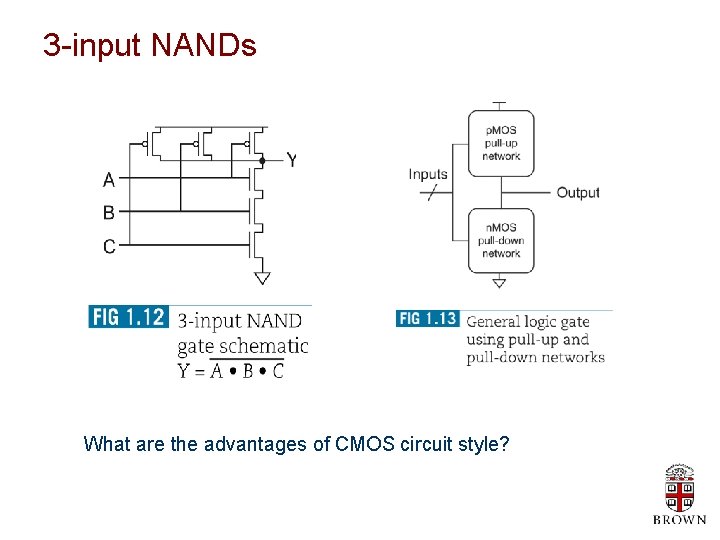

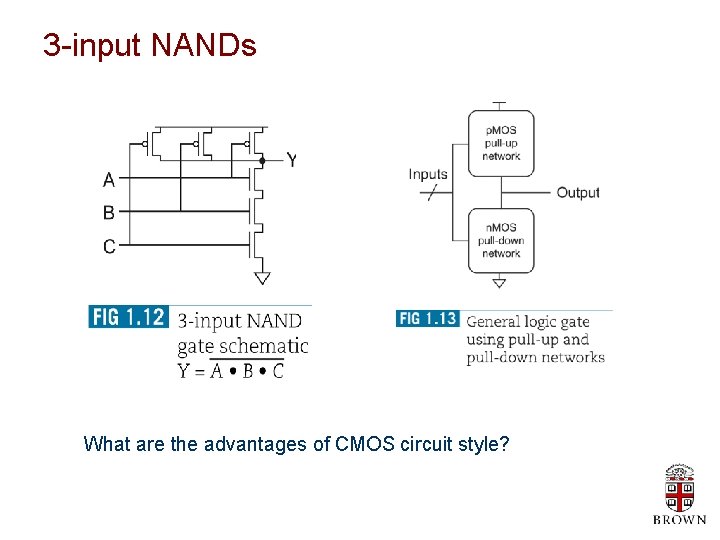

3 -input NANDs What are the advantages of CMOS circuit style?

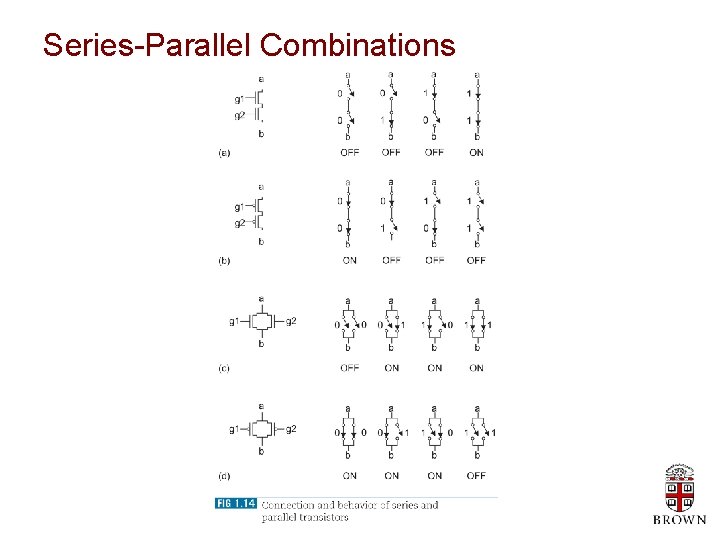

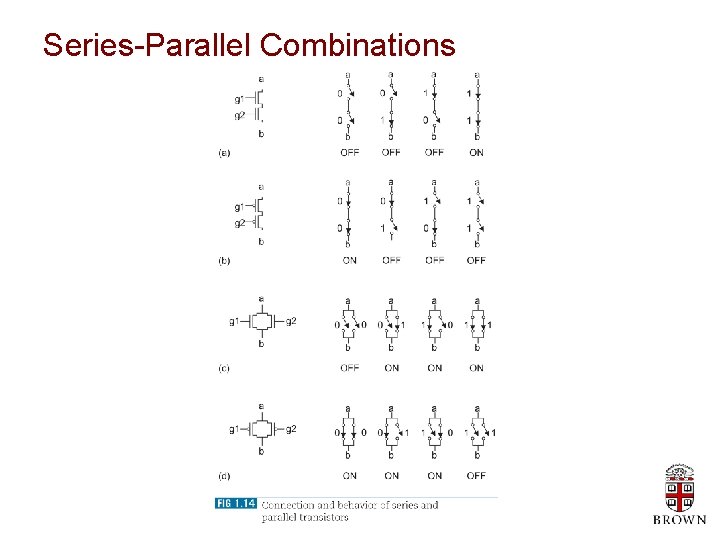

Series-Parallel Combinations

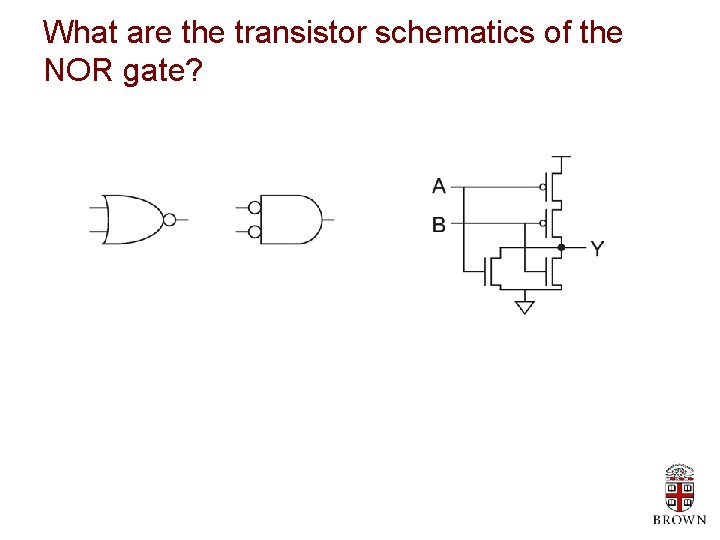

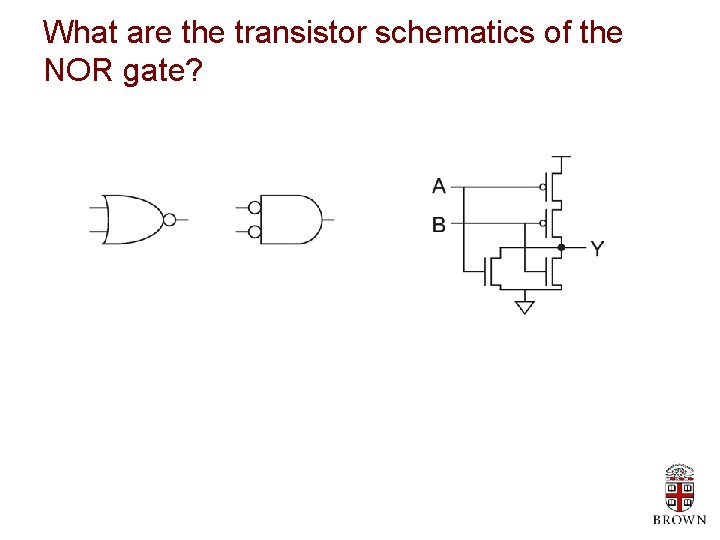

What are the transistor schematics of the NOR gate?

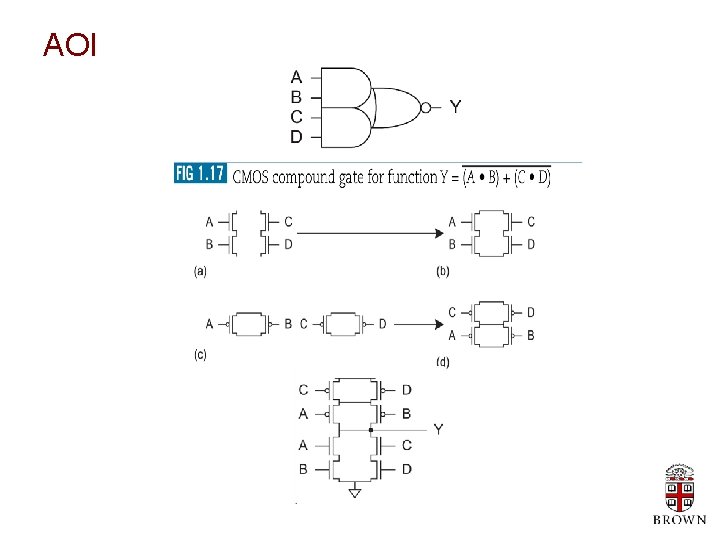

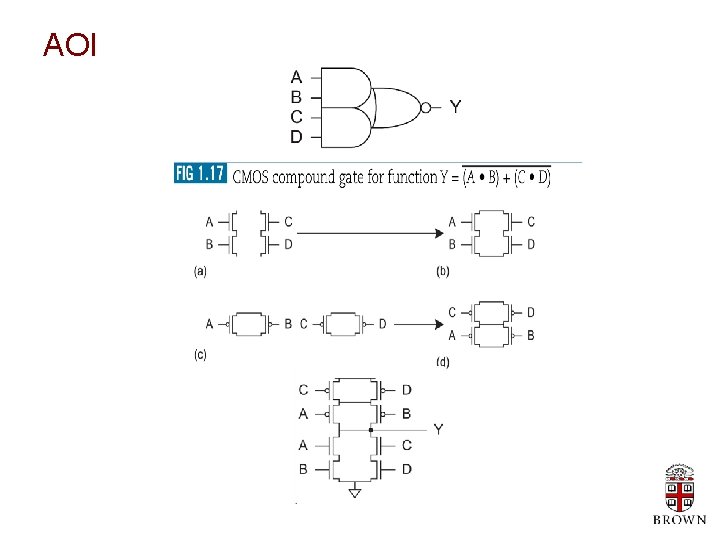

AOI

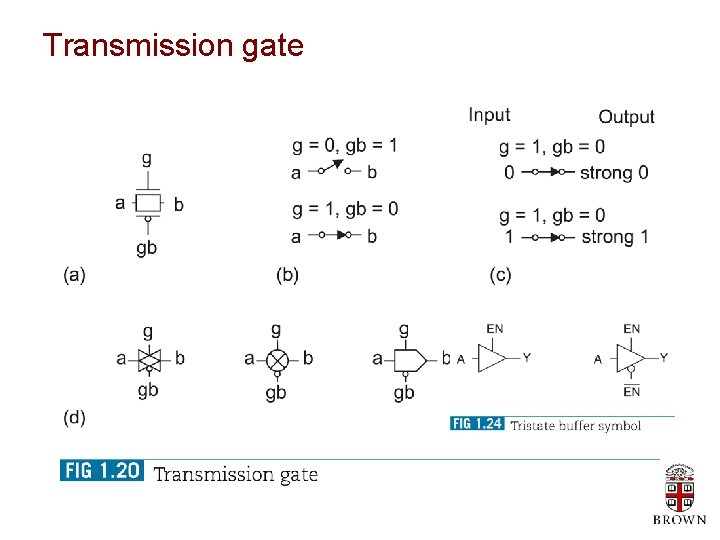

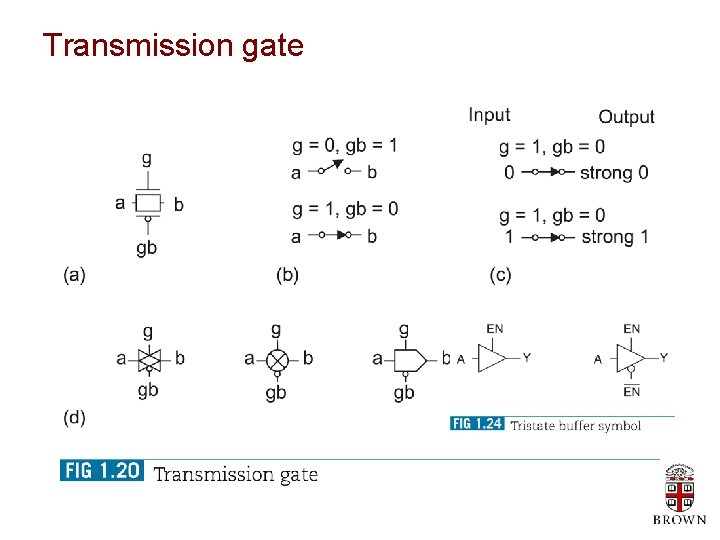

Transmission gate