Design and Implementation of VLSI Systems EN 1600

- Slides: 16

Design and Implementation of VLSI Systems (EN 1600) Lecture 29: Array Subsystems (SRAM) Prof. Sherief Reda Division of Engineering, Brown University Spring 2008 [sources: Weste/Addison Wesley – Rabaey/Pearson] S. Reda EN 1600 SP’ 08

Array subsystems • • • SRAM DRAM ROM FLASH PLA/FPGA S. Reda EN 1600 SP’ 08

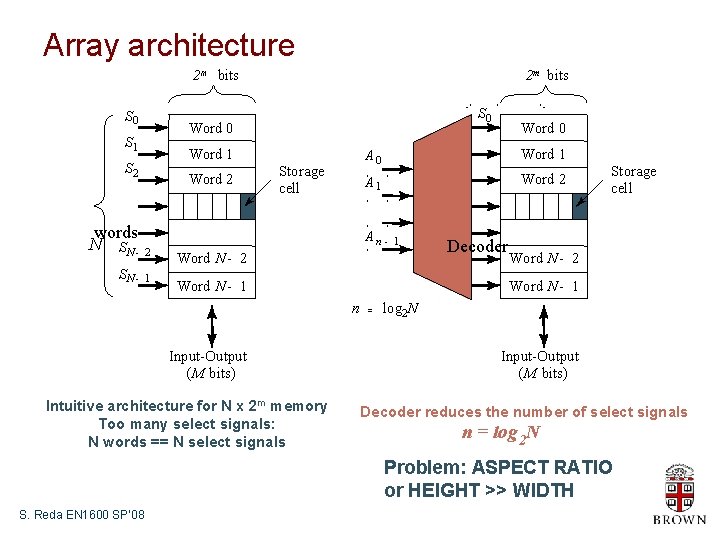

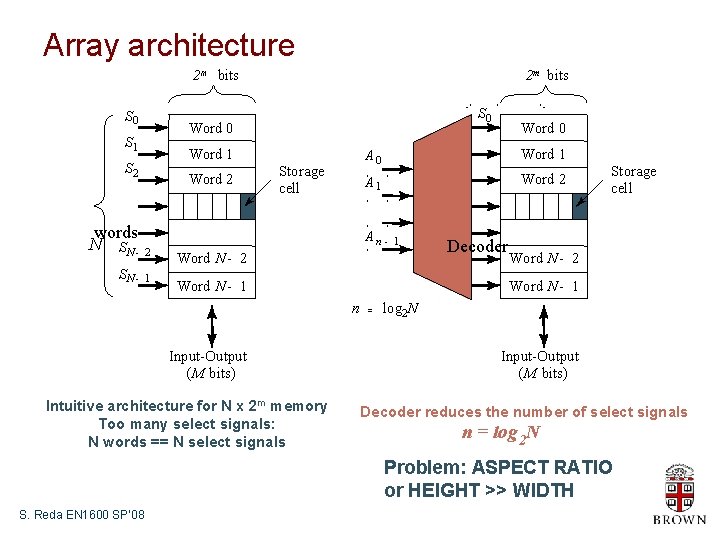

Array architecture 2 m bits S 0 Word 0 S 1 Word 1 S 2 Word 2 words N SN - 2 SN - 1 Storage cell Word 0 A 0 Word 1 A 1 Word 2 An - 1 Word N - 2 Word N - 1 Decoder Storage cell Word N - 2 Word N - 1 n = log 2 N Input-Output (M bits) Intuitive architecture for N x 2 m memory Too many select signals: N words == N select signals Input-Output (M bits) Decoder reduces the number of select signals n = log 2 N Problem: ASPECT RATIO or HEIGHT >> WIDTH S. Reda EN 1600 SP’ 08

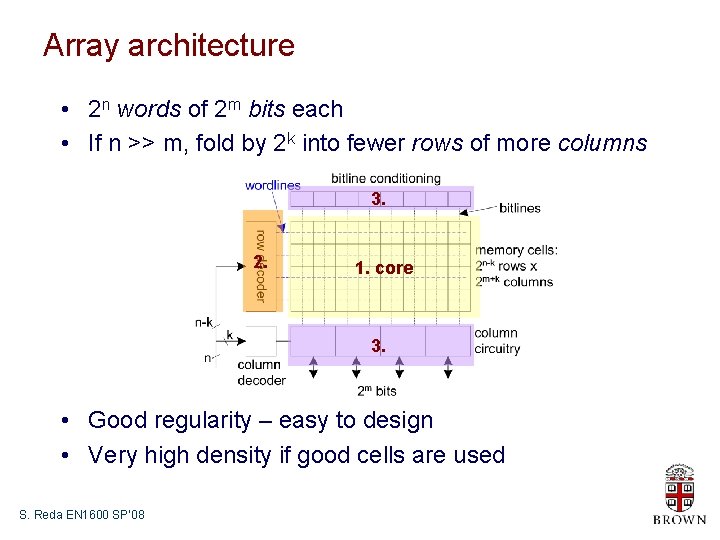

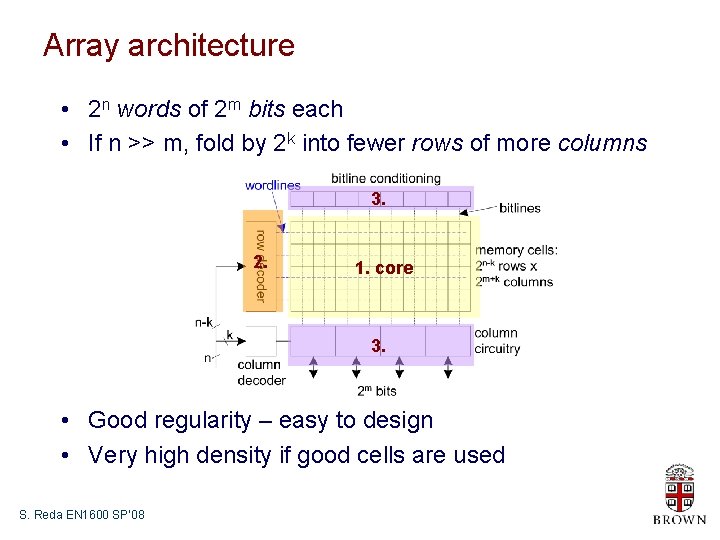

Array architecture • 2 n words of 2 m bits each • If n >> m, fold by 2 k into fewer rows of more columns 3. 2. 1. core 3. • Good regularity – easy to design • Very high density if good cells are used S. Reda EN 1600 SP’ 08

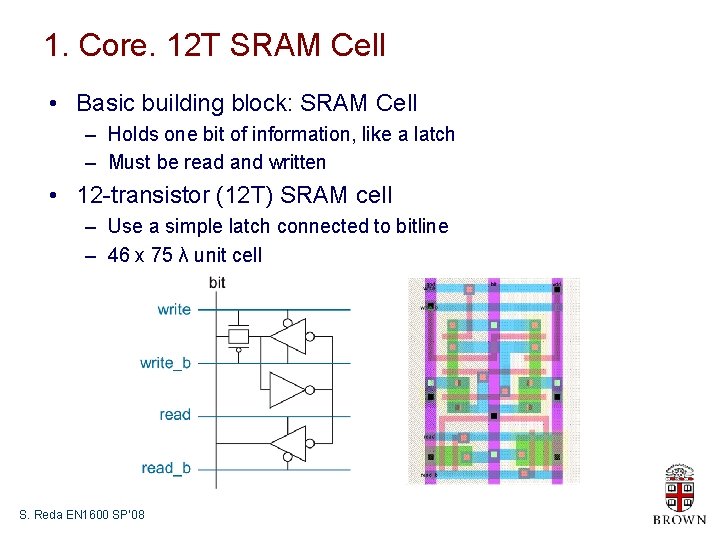

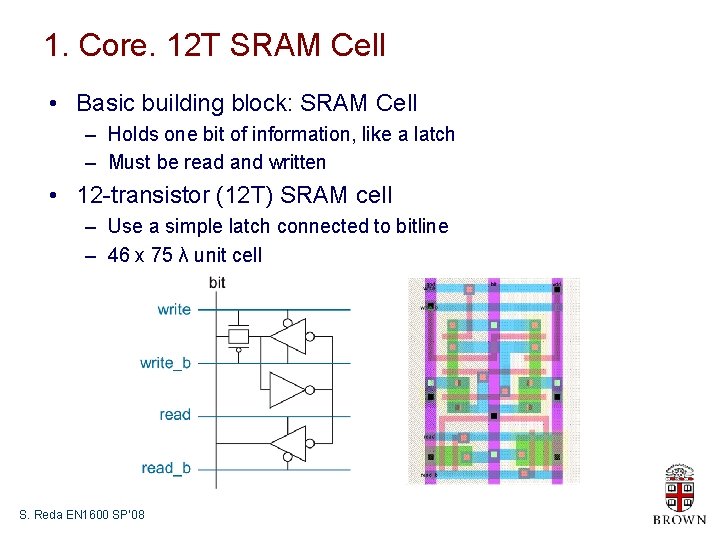

1. Core. 12 T SRAM Cell • Basic building block: SRAM Cell – Holds one bit of information, like a latch – Must be read and written • 12 -transistor (12 T) SRAM cell – Use a simple latch connected to bitline – 46 x 75 λ unit cell S. Reda EN 1600 SP’ 08

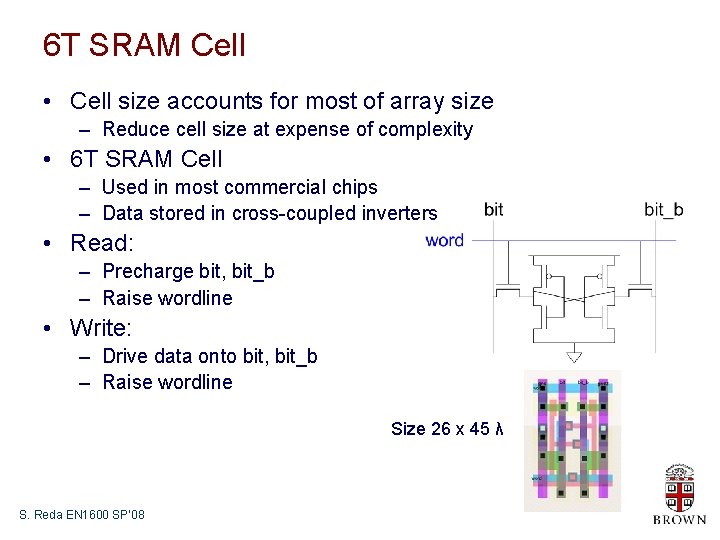

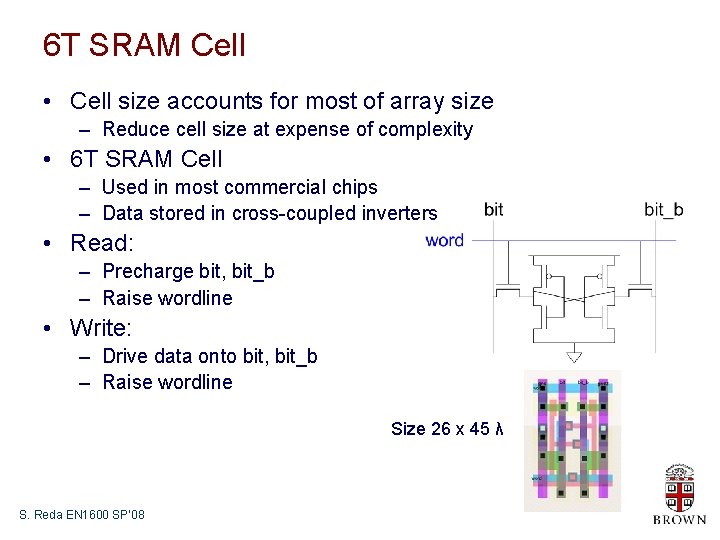

6 T SRAM Cell • Cell size accounts for most of array size – Reduce cell size at expense of complexity • 6 T SRAM Cell – Used in most commercial chips – Data stored in cross-coupled inverters • Read: – Precharge bit, bit_b – Raise wordline • Write: – Drive data onto bit, bit_b – Raise wordline Size 26 x 45 λ S. Reda EN 1600 SP’ 08

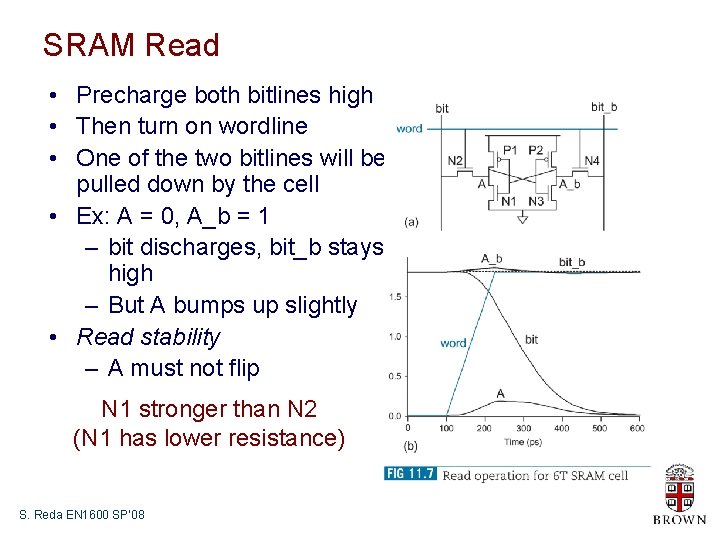

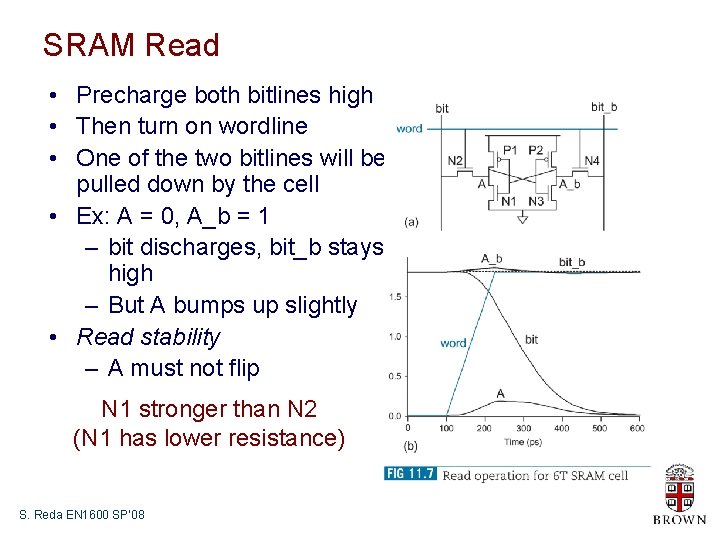

SRAM Read • Precharge both bitlines high • Then turn on wordline • One of the two bitlines will be pulled down by the cell • Ex: A = 0, A_b = 1 – bit discharges, bit_b stays high – But A bumps up slightly • Read stability – A must not flip N 1 stronger than N 2 (N 1 has lower resistance) S. Reda EN 1600 SP’ 08

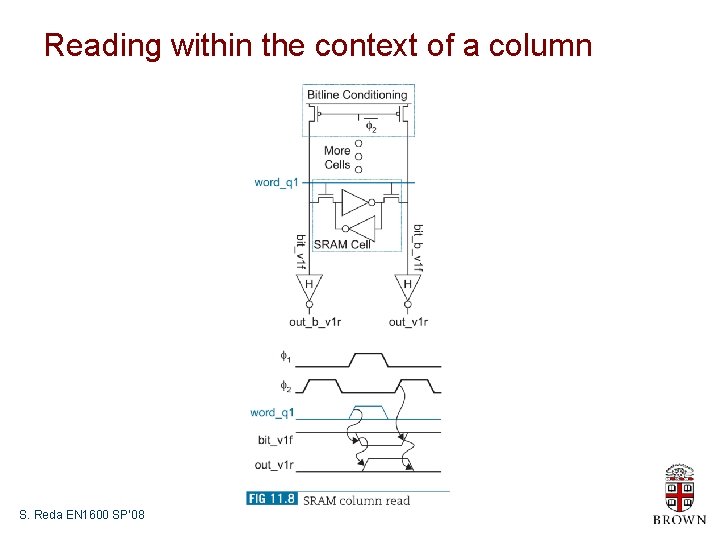

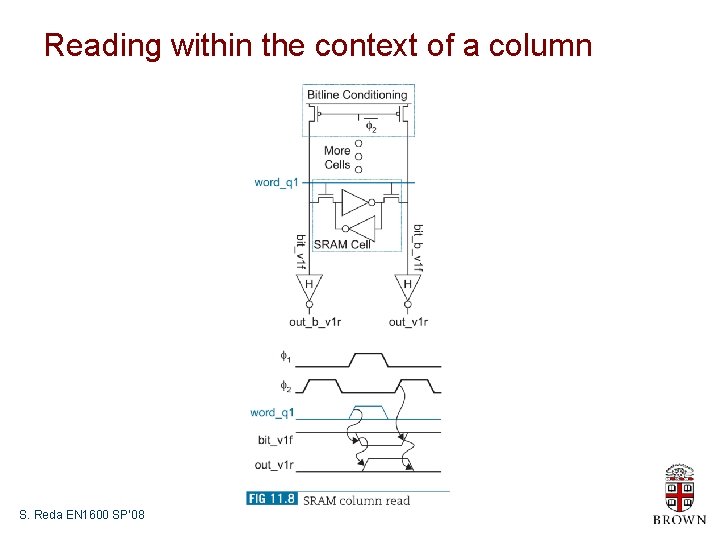

Reading within the context of a column S. Reda EN 1600 SP’ 08

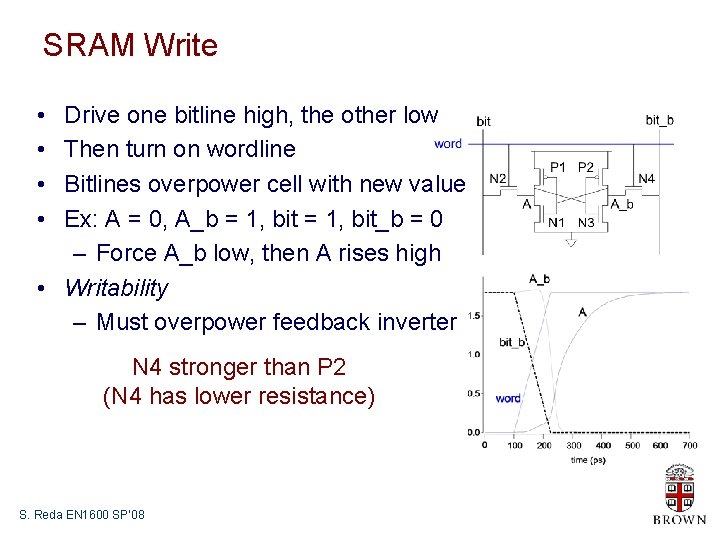

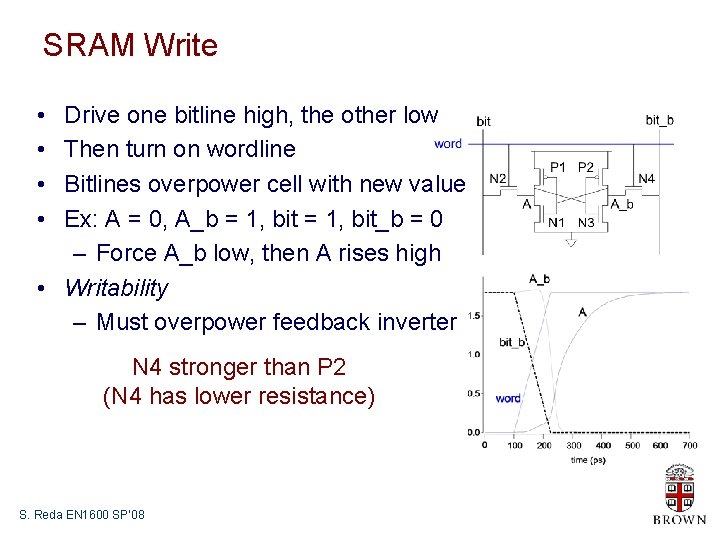

SRAM Write • • Drive one bitline high, the other low Then turn on wordline Bitlines overpower cell with new value Ex: A = 0, A_b = 1, bit_b = 0 – Force A_b low, then A rises high • Writability – Must overpower feedback inverter N 4 stronger than P 2 (N 4 has lower resistance) S. Reda EN 1600 SP’ 08

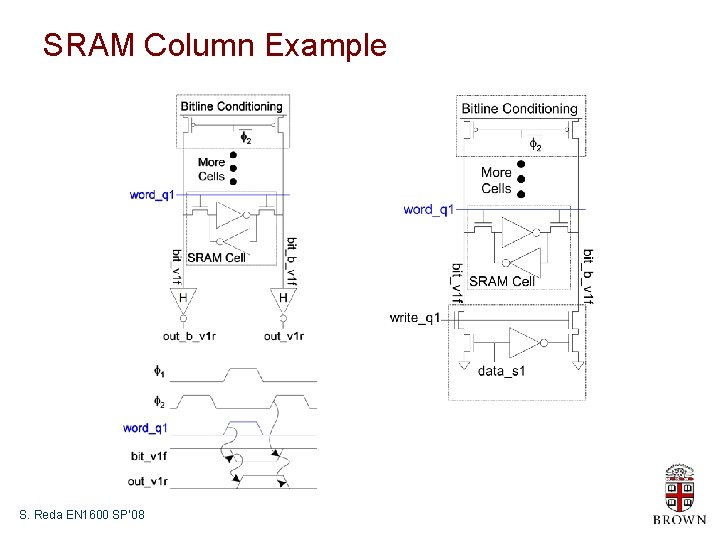

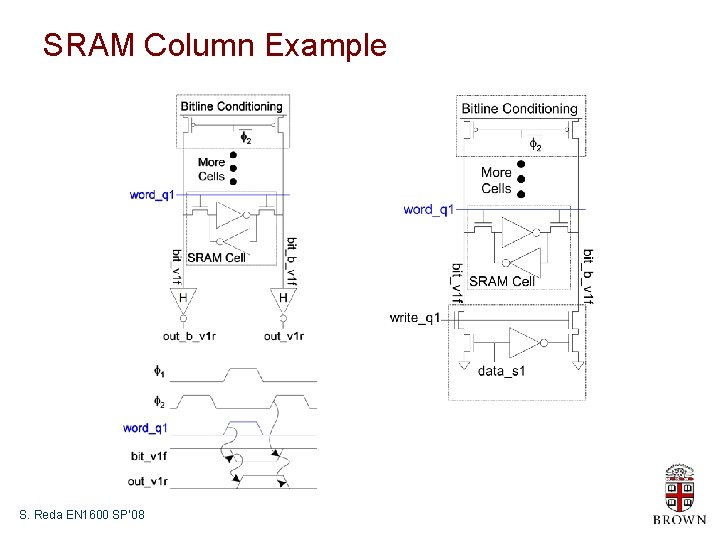

SRAM Column Example S. Reda EN 1600 SP’ 08

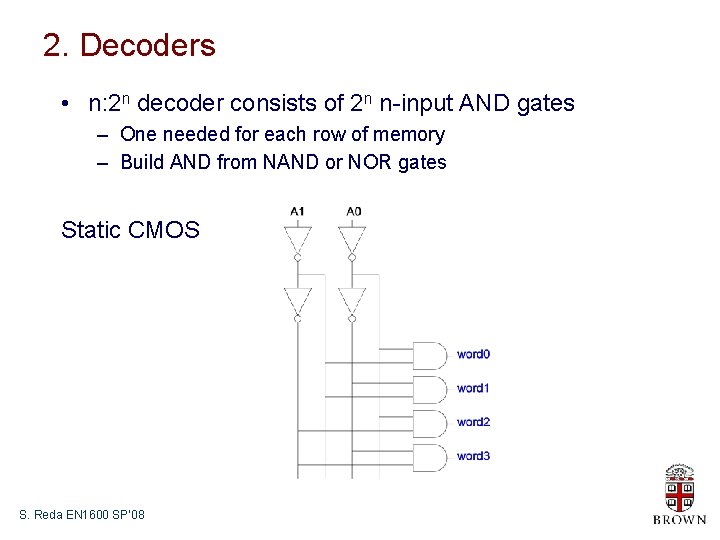

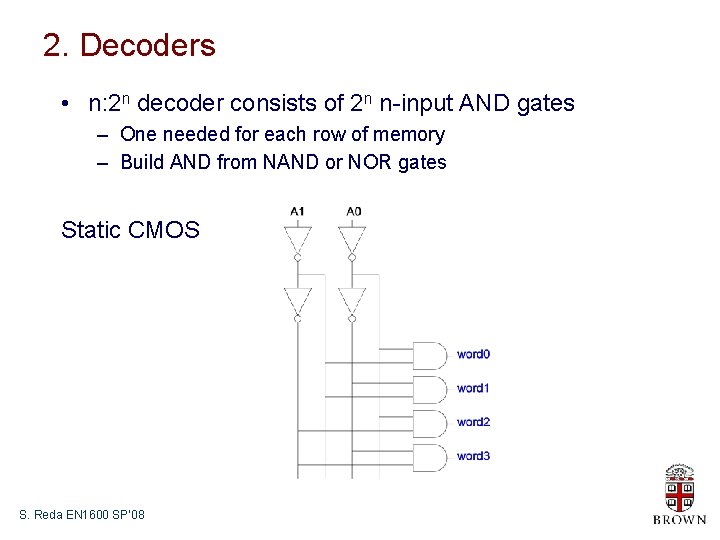

2. Decoders • n: 2 n decoder consists of 2 n n-input AND gates – One needed for each row of memory – Build AND from NAND or NOR gates Static CMOS S. Reda EN 1600 SP’ 08

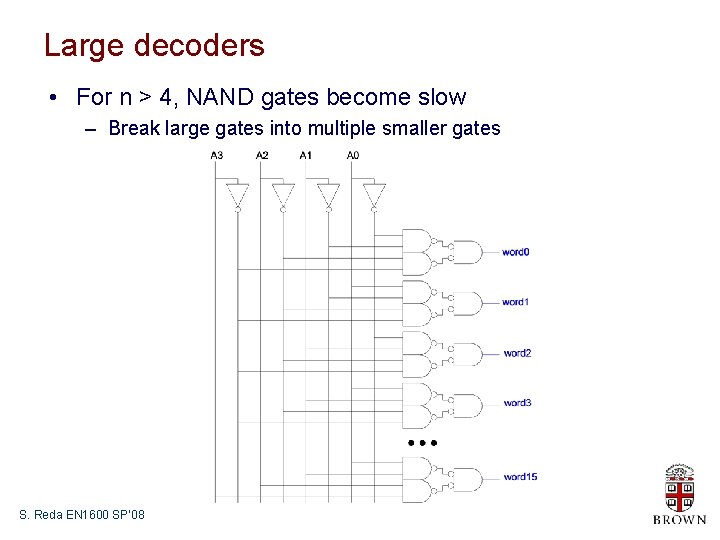

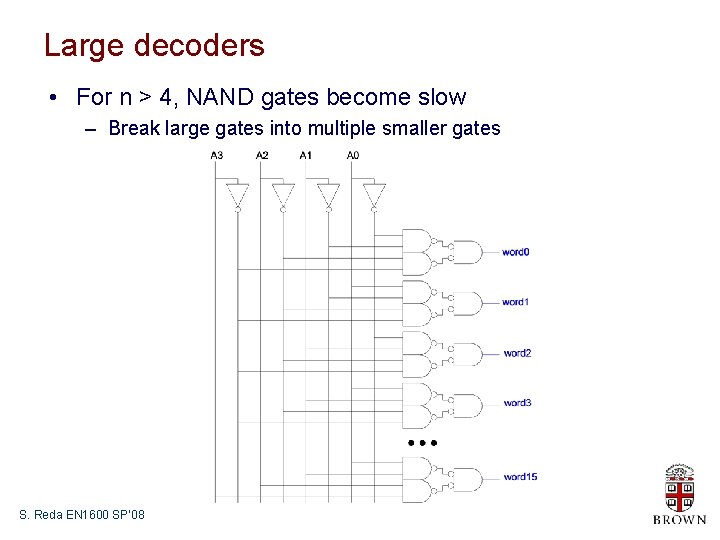

Large decoders • For n > 4, NAND gates become slow – Break large gates into multiple smaller gates S. Reda EN 1600 SP’ 08

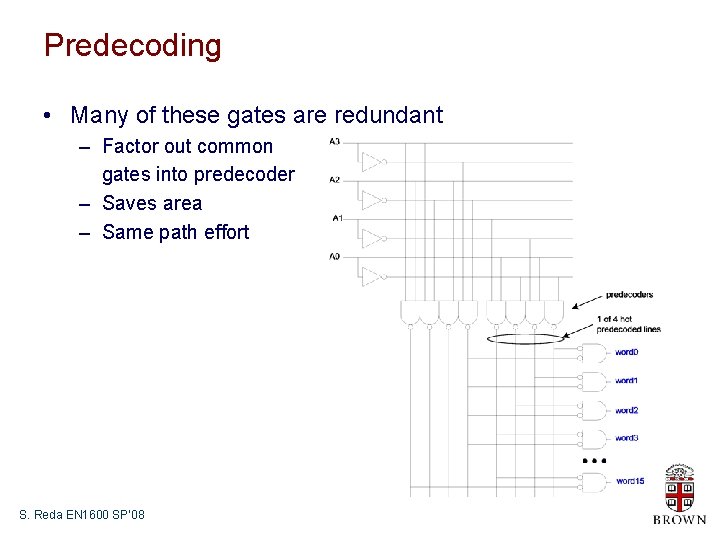

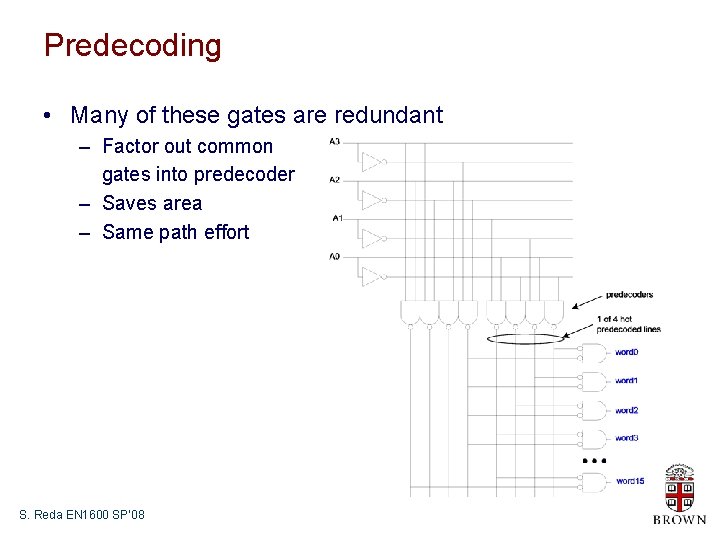

Predecoding • Many of these gates are redundant – Factor out common gates into predecoder – Saves area – Same path effort S. Reda EN 1600 SP’ 08

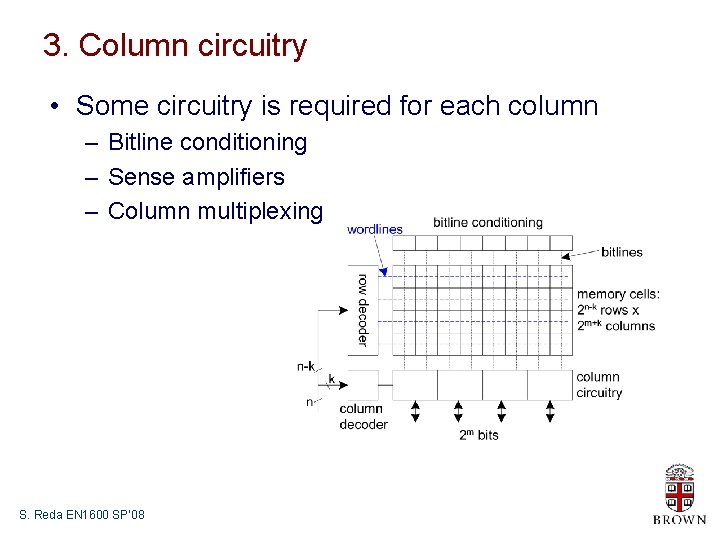

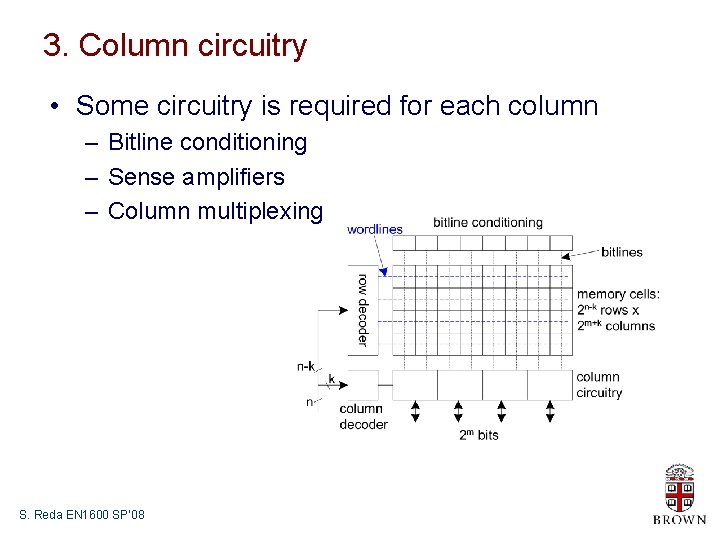

3. Column circuitry • Some circuitry is required for each column – Bitline conditioning – Sense amplifiers – Column multiplexing S. Reda EN 1600 SP’ 08

Bit preconditioning and sense amplifiers • Precharge bitlines high before reads • Many words in memory ® bit capacitance is huge ® slow reading (large memory access time) • Sense amplifiers are triggered on small voltage swing (reduce DV) S. Reda EN 1600 SP’ 08

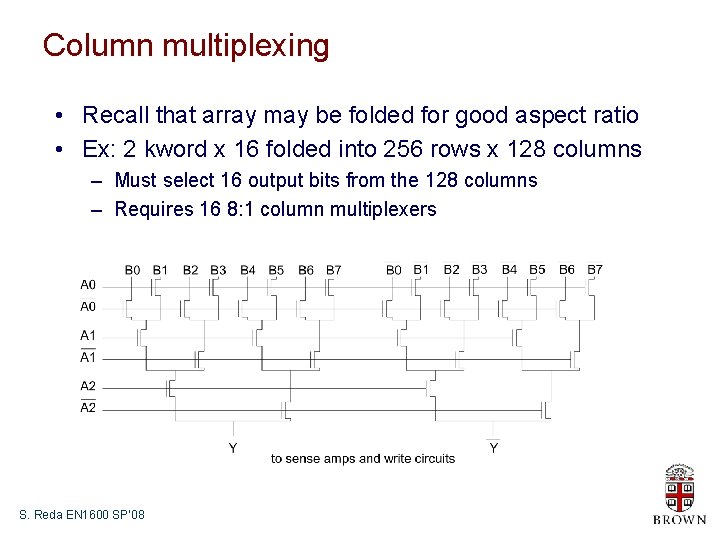

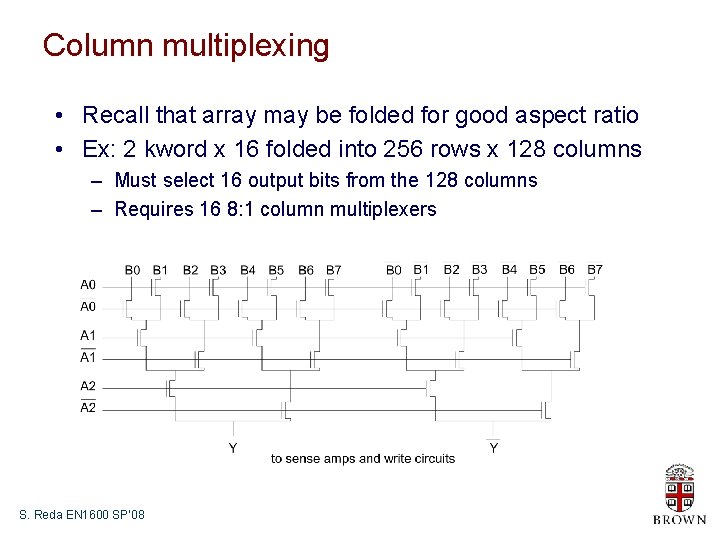

Column multiplexing • Recall that array may be folded for good aspect ratio • Ex: 2 kword x 16 folded into 256 rows x 128 columns – Must select 16 output bits from the 128 columns – Requires 16 8: 1 column multiplexers S. Reda EN 1600 SP’ 08